# INTERTEK TESTING SERVICES

Report No. : HK11081225-1

Sample No. : 1/2

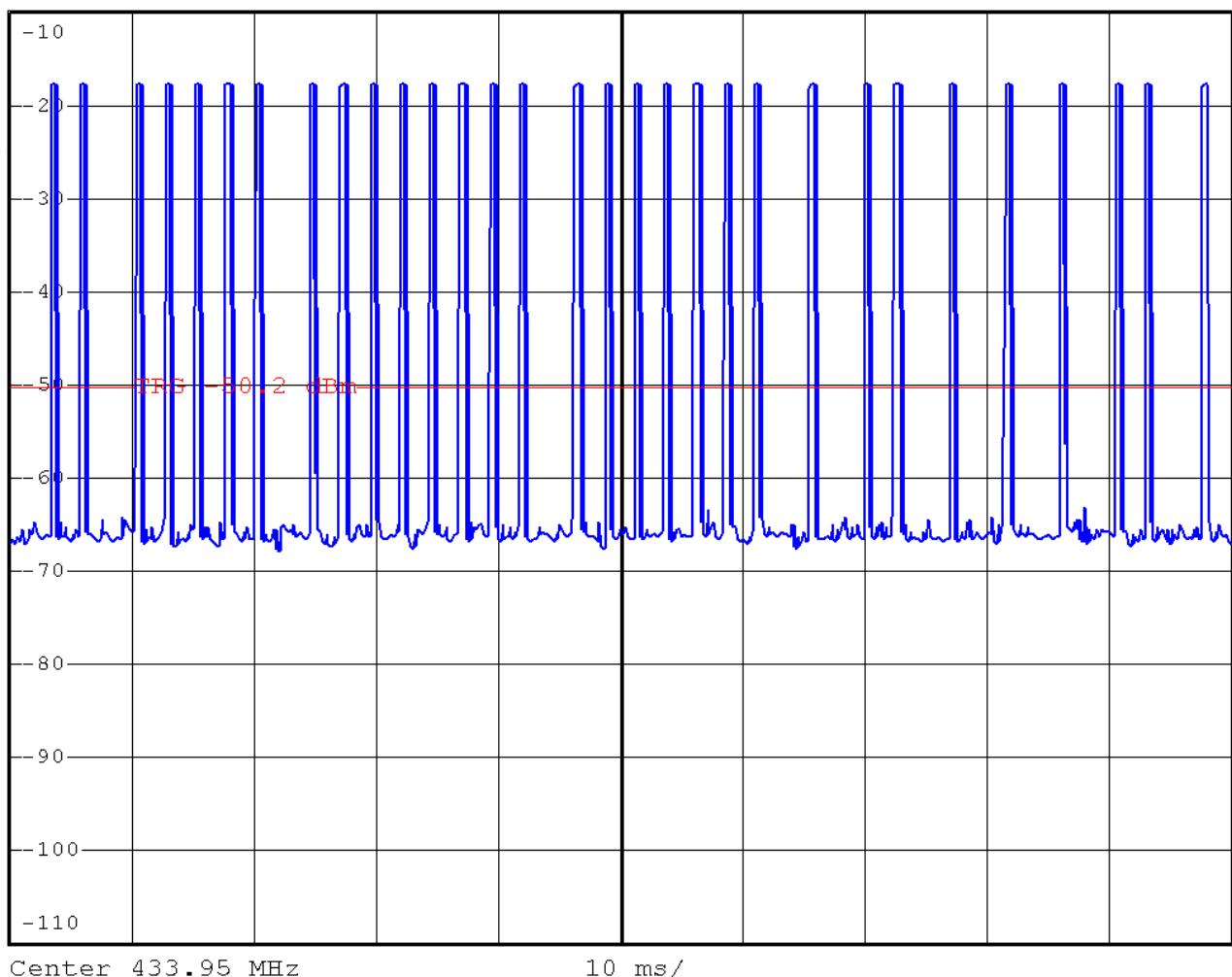

Ref -10 dBm

Att 20 dB

RBW 1 MHz

VBW 3 MHz

SWT 100 ms

T PK \*

VIEW

A

SGL

TRG

Timing Plot – Pursuant to FCC Part 15 Section 15. 231 Requirement

# INTERTEK TESTING SERVICES

Report No. : HK11081225-1

Sample No. : 1/2

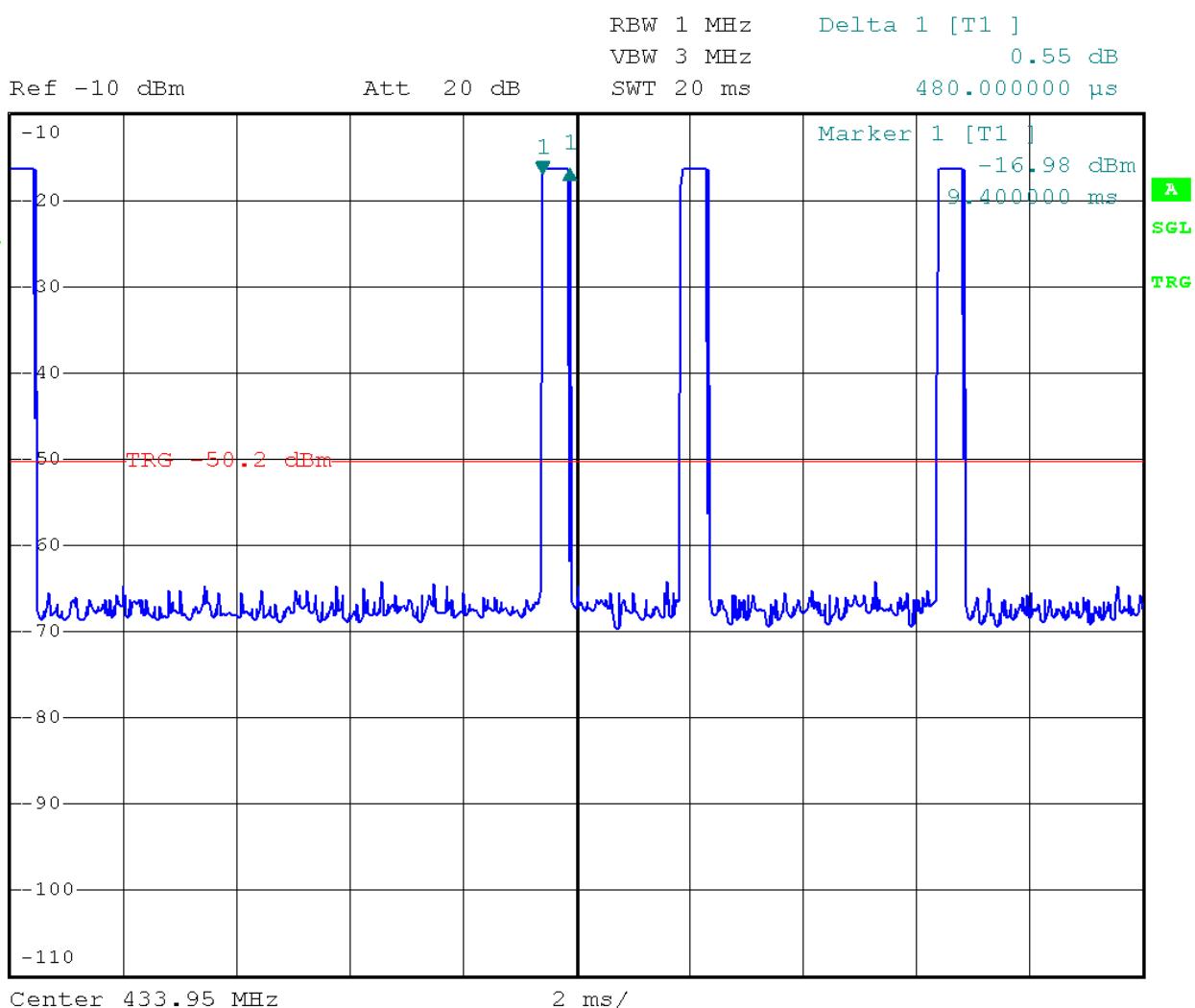

Duration of one cycle = 100ms

Effective Period of the cycle =  $31 \times 480\text{us} = 14880\text{us} = 14.88\text{ms}$

Duty Cycle = Effective Period / Duration of one cycle

$$= 14.88\text{ms} / 100\text{ms}$$

$$= 0.1488$$

Average Factor =  $20 \times \log (\text{Duty Cycle})$

$$= 20 \times \log (0.1488)$$

$$= -16.5479\text{dB}$$

Timing Plot – Pursuant to FCC Part 15 Section 15.231 Requirement