Prestige, Quality and Innovation.

MM516

JULY 2011

# MM516

Bluetooth QD ID : B018234 (End Product Listing)

FCC ID : ZDSMM516

IC : 9583A-MM516

Class 2 BC05-ext Multimedia Module

## Wireless Modules

**User's Manual**

Hardware Description

Revision 1.4

|                         |   |

|-------------------------|---|

| Table of Contents ..... | 2 |

| List of Figures .....   | 4 |

| List of Tables .....    | 4 |

## Table of Contents

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| 1. General Device Overview .....                                            | 5  |

| 1.1 Features .....                                                          | 5  |

| 1.2 Block Diagram .....                                                     | 6  |

| 1.3 Pin Configuration .....                                                 | 7  |

| 1.4 Pin Description .....                                                   | 7  |

| 1.5 Firmware .....                                                          | 10 |

| 2 Basic Operating Information .....                                         | 10 |

| 2.1 Power Supply .....                                                      | 10 |

| 2.2 Clocking .....                                                          | 10 |

| 3 Physical Description .....                                                | 11 |

| 3.1 RF Receive .....                                                        | 11 |

| 3.1.1 Low Noise Amplifier .....                                             | 11 |

| 3.1.2 Analog to Digital Converter .....                                     | 11 |

| 3.2 RF Transmitter .....                                                    | 11 |

| 3.2.1 IQ Modulator .....                                                    | 11 |

| 3.2.2 Power Amplifier .....                                                 | 11 |

| 3.3 RF Synthesizer .....                                                    | 11 |

| 3.4 Clock Input and Generation .....                                        | 11 |

| 3.5 Baseband and Logic .....                                                | 12 |

| 3.5.1 Memory Management Unit .....                                          | 12 |

| 3.5.2 Burst Mode Controller .....                                           | 12 |

| 3.5.3 Physical Layer Hardware Engine DSP .....                              | 12 |

| 3.5.4 System RAM .....                                                      | 12 |

| 3.5.5 External Memory Driver .....                                          | 12 |

| 3.5.6 USB .....                                                             | 12 |

| 3.5.7 Synchronous Serial Interface .....                                    | 13 |

| 3.5.8 UART .....                                                            | 13 |

| 3.6 Microcontroller .....                                                   | 13 |

| 3.6.1 Programmable I/O .....                                                | 13 |

| 3.6.2 802.11 Coexistence Interface .....                                    | 13 |

| 4 Bluetooth Software Stacks .....                                           | 14 |

| 4.1 BlueCore HCI Stack .....                                                | 14 |

| 4.1.1 Key Features of the HCI Stack: Standard Bluetooth Functionality ..... | 15 |

| 4.2 Key Features of the HCI Stack: Extra Functionality .....                | 16 |

| 4.3 Additional Software for Other Embedded Applications .....               | 17 |

| 4.4 CSR Development Systems .....                                           | 17 |

| 5 Interfaces .....                                                          | 18 |

| 5.1 UART Interface .....                                                    | 18 |

| 5.1.1 UART Configuration While RESET is Active .....                        | 21 |

| 5.1.2 UART Bypass Mode .....                                                | 21 |

| 5.1.3 Current Consumption in UART Bypass Mode .....                         | 21 |

| 5.2 USB Interface .....                                                     | 22 |

| 5.2.1 USB Data Connections .....                                            | 22 |

| 5.2.2 USB Pull-Up Resistor .....                                            | 22 |

| 5.2.3 USB Power Supply .....                                                | 22 |

| 5.2.4 Self-Powered Mode .....                                               | 22 |

| 5.2.5 Bus-Powered Mode .....                                                | 24 |

| 5.2.6 Suspend Current .....                                                 | 25 |

| 5.2.7 Detach and Wake_Up Signaling .....                                    | 25 |

| 5.2.8 USB Driver .....                                                      | 25 |

|                                                             |    |

|-------------------------------------------------------------|----|

| 5.2.9 USB v2.0 Compliance . . . . .                         | 26 |

| 5.2.10 USB 2.0 Compatibility . . . . .                      | 26 |

| 5.3 Serial Peripheral Interface . . . . .                   | 26 |

| 5.3.1 Instruction Cycle . . . . .                           | 26 |

| 5.3.2 Writing to the Device . . . . .                       | 28 |

| 5.3.3 Reading from the Device . . . . .                     | 28 |

| 5.3.4 Multi-Slave Operation . . . . .                       | 29 |

| 5.4 PCM Codec Interface . . . . .                           | 29 |

| 5.4.1 PCM Interface Master/Slave . . . . .                  | 29 |

| 5.4.2 Long Frame Sync . . . . .                             | 30 |

| 5.4.3 Short Frame Sync . . . . .                            | 31 |

| 5.4.4 Multi-slot Operation . . . . .                        | 31 |

| 5.4.5 GCI Interface . . . . .                               | 32 |

| 5.4.6 Slots and Sample Formats . . . . .                    | 32 |

| 5.4.7 Additional Features . . . . .                         | 33 |

| 5.4.8 PCM Timing Information . . . . .                      | 34 |

| 5.4.9 PCM_CLK and PCM_SYNC Generation . . . . .             | 38 |

| 5.4.10 PCM Configuration . . . . .                          | 38 |

| 5.5 I/O Parallel Ports . . . . .                            | 40 |

| 5.5.1 PIO Defaults . . . . .                                | 40 |

| 5.6 I2C Interface . . . . .                                 | 40 |

| 5.7 TCXO Enable OR Function . . . . .                       | 41 |

| 5.8 Reset . . . . .                                         | 41 |

| 5.8.1 Pin States on Reset . . . . .                         | 42 |

| 5.8.2 Status after Reset . . . . .                          | 43 |

| 5.9 Power Supply . . . . .                                  | 43 |

| 5.9.1 Switch-mode Regulator . . . . .                       | 43 |

| 5.9.2 Low-voltage Linear Regulator . . . . .                | 43 |

| 5.9.3 Low-voltage Audio Linear Regulator . . . . .          | 43 |

| 6 Electrical Characteristics . . . . .                      | 44 |

| 6.1 Absolute Maximum Ratings . . . . .                      | 44 |

| 6.2 DC Characteristics . . . . .                            | 44 |

| 6.3 Radio Characteristics - Basic Data Rate . . . . .       | 45 |

| 6.4 Radio Characteristics - Enhanced Data Rate . . . . .    | 46 |

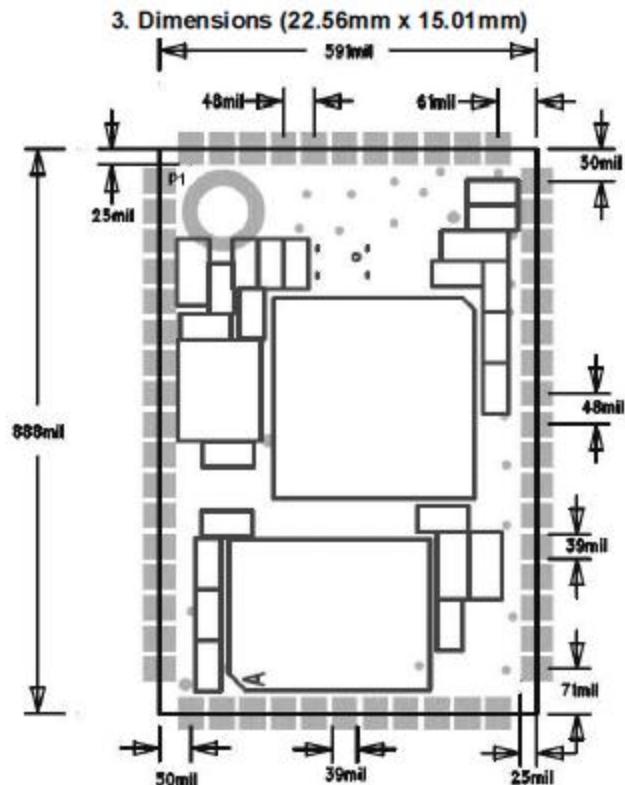

| 7 Package Information . . . . .                             | 49 |

| 7.1 Package Marking . . . . .                               | 49 |

| 8 Important Application Information . . . . .               | 50 |

| 8.1 Antenna Trace and Connector Information . . . . .       | 50 |

| 8.2 Antenna Information . . . . .                           | 50 |

| 8.4 FCC Class B Digital Devices Regulatory Notice . . . . . | 52 |

| 8.5 FCC Wireless Notice . . . . .                           | 52 |

| 8.6 FCC Interference Statement . . . . .                    | 53 |

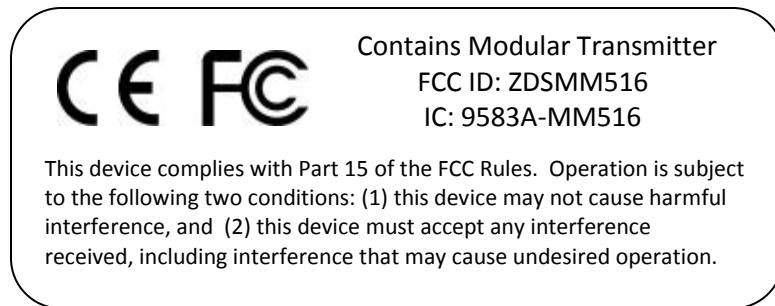

| 8.7 FCC Identifier . . . . .                                | 53 |

| 8.8 European R&TTE Declaration of Conformity . . . . .      | 53 |

| 8.8 Unauthorized Changes to Equipment Statement . . . . .   | 53 |

| 8.9 Bluetooth Qualified Design ID . . . . .                 | 54 |

| 8.10 Industry Canada Certification . . . . .                | 54 |

| 8.11 Label Design of the Host Product . . . . .             | 55 |

| 8.12 End User Product Manual Requirements . . . . .         | 57 |

## List of Figures

|           |                                                                 |    |

|-----------|-----------------------------------------------------------------|----|

| Figure 1  | Simplified Block Diagram of MM516                               | 6  |

| Figure 2  | Pin Configuration for the MM516 and PCB Layout                  | 7  |

| Figure 3  | BlueCore HCI Stack                                              | 14 |

| Figure 4  | Universal Asynchronous Receiver/Transmitter                     | 18 |

| Figure 5  | Break Signal                                                    | 19 |

| Figure 6  | UART Bypass Architecture                                        | 21 |

| Figure 7  | USB Connections for Self-Powered Mode                           | 23 |

| Figure 8  | USB Connections for Bus-Powered Mode                            | 24 |

| Figure 9  | USB_DETACH and USB_WAKE_UP Signals                              | 25 |

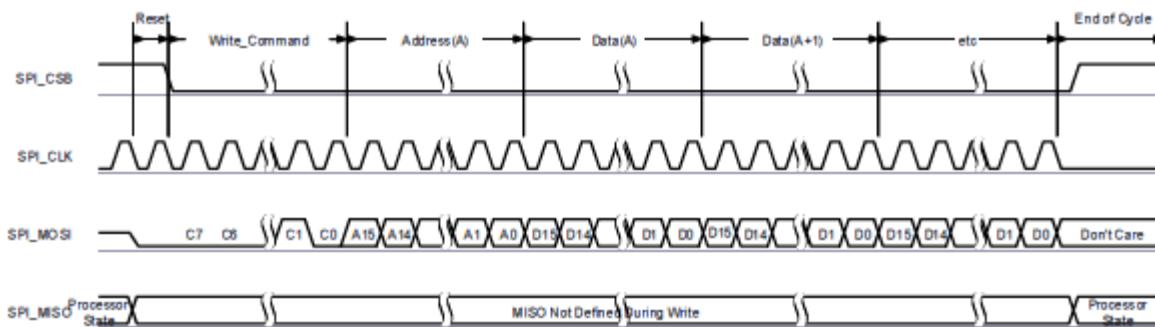

| Figure 10 | SPI Write Operation                                             | 27 |

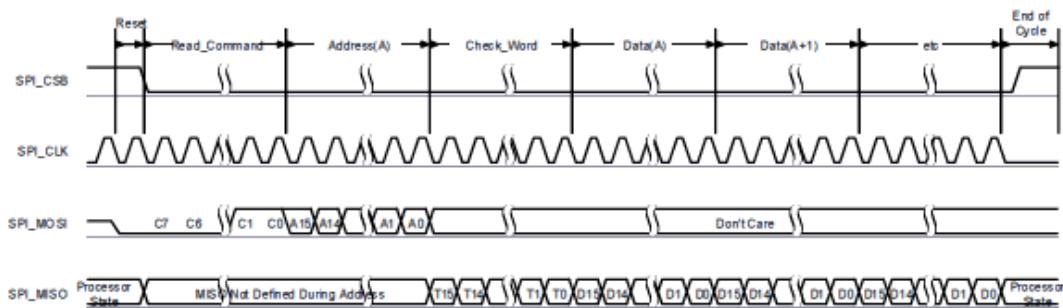

| Figure 11 | SPI Read Operation                                              | 27 |

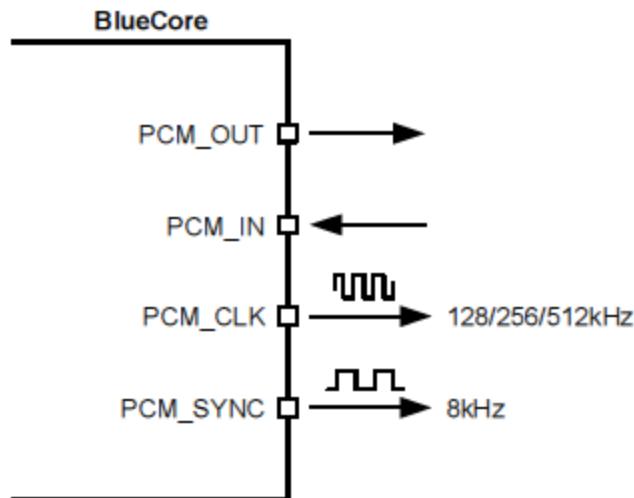

| Figure 12 | PCM Configured as a Master                                      | 28 |

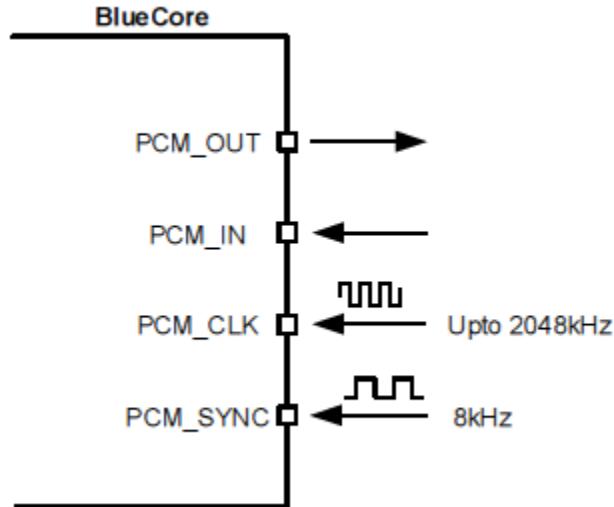

| Figure 13 | PCM Configured as a Slave                                       | 29 |

| Figure 14 | Long Frame Sync (Shown with 8-bit Companded Sample)             | 29 |

| Figure 15 | Short Frame Sync (Shown with 16-bit Sample)                     | 30 |

| Figure 16 | Multi-slot Operation with Two Slots and 8-bit Companded Samples | 30 |

| Figure 17 | GCI Interface                                                   | 31 |

| Figure 18 | 16-bit Slot Length and Sample Format                            | 32 |

| Figure 19 | PCM Master Timing Long Frame Sync                               | 34 |

| Figure 20 | PM Master Timing Short Frame Sync                               | 34 |

| Figure 21 | PCM Slave Timing Long Frame Sync                                | 36 |

| Figure 22 | PCM Slave Timing Short Frame Sync                               | 36 |

| Figure 23 | Example of OR Function                                          | 40 |

| Figure 24 | Package Dimensions and Pin 1 Marking                            | 49 |

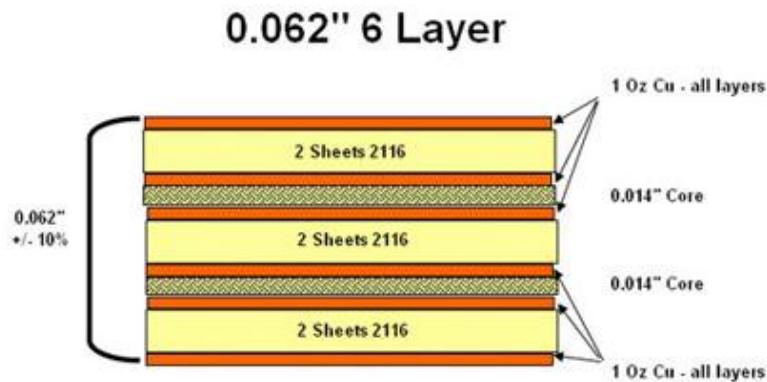

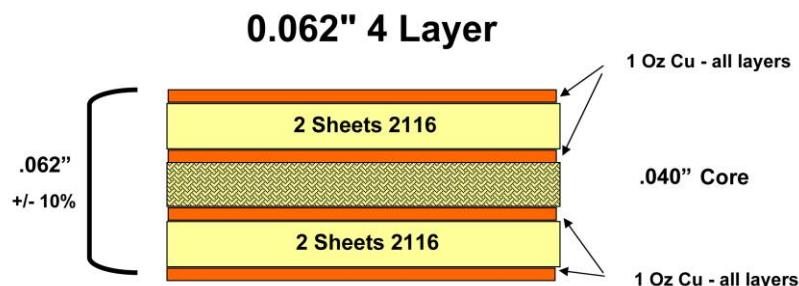

| Figure 25 | Six Layer Stackup                                               | 50 |

| Figure 26 | Four Layer Stackup                                              | 50 |

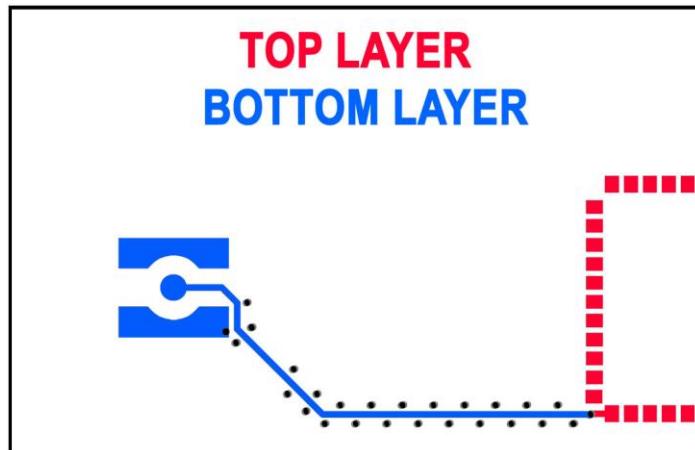

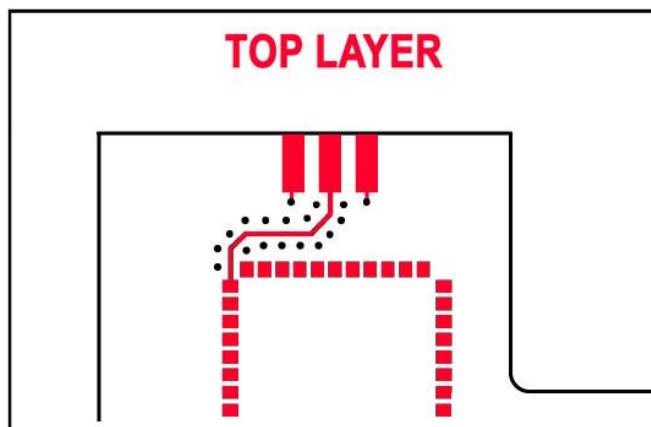

| Figure 27 | Long Micro-Strip Trace                                          | 51 |

| Figure 28 | Short Micro-Strip Trace                                         | 51 |

| Figure 29 | Declaration of Conformity                                       | 54 |

| Figure 31 | Equipment Label                                                 | 56 |

## List of Tables

|          |                                          |    |

|----------|------------------------------------------|----|

| Table 1  | Pin Description                          | 7  |

| Table 2  | UART Settings                            | 19 |

| Table 3  | Standard Data Rates                      | 20 |

| Table 3  | USB Interface Component Values           | 23 |

| Table 4  | Instruction Cycle for an SPI Transaction | 26 |

| Table 5  | PCM Master Timing                        | 33 |

| Table 6  | PCM Slave Timing                         | 35 |

| Table 7  | PSKEY_PCM_CONFIG32 Description           | 37 |

| Table 8  | PSKEY_PCM_LOW_JITTER_CONFIG Description  | 39 |

| Table 9  | Pin States on Reset                      | 41 |

| Table 10 | Absolute Maximum Ratings                 | 44 |

| Table 11 | Typical DC Characteristics               | 44 |

| Table 12 | Radio Characteristics - Basic Data Rate  | 46 |

| Table 13 | Antennas                                 | 52 |

MM510

## 1. General Device Overview

### 1.1 Features

#### General

- The module is a Max.4dBm( Class2 ) module.

- Low current consumption : Hold,Sniff,Park,Deep sleep Mode

- Interface: USB,UART&PCM(for voice CODEC)

- Support for 802.11 Co-Exsistence

- 16-bit Internal Stereo CODEC 95dB SNR for DAC

- Integrated 1.5V and 1.8V Linear Regulators

- Integrated Battery Charger

- RoHS compliant

- Small outline. 22.56 x 15.01 mm

#### Interfaces

- USB v2.0

- Standard RS232 UART for communicating with other devices : 1200 baud to 3Mbaud

- Serial Peripheral Interface (SPI)

- Multi-Configurable I2S, PCM or SPDIF Interface

#### RF

- Transmit power typ. 2.0 dBm

- Receiver sensitivity typ. -87 to -20 dBm

- Integrated channel filters

- Supports pi/4 DQPSK (2Mbps) and 8DPSK (3Mbps) modulation

#### Bluetooth

- Bluetooth standard Ver. 2.1 + EDR compliant.

- Support for up to seven slaves : SCO links<3>,ACL links,Piconet<7>

- HCI or SPP,HSP/HFP,HID,DUN firmware is available

## 1.2 Block Diagram

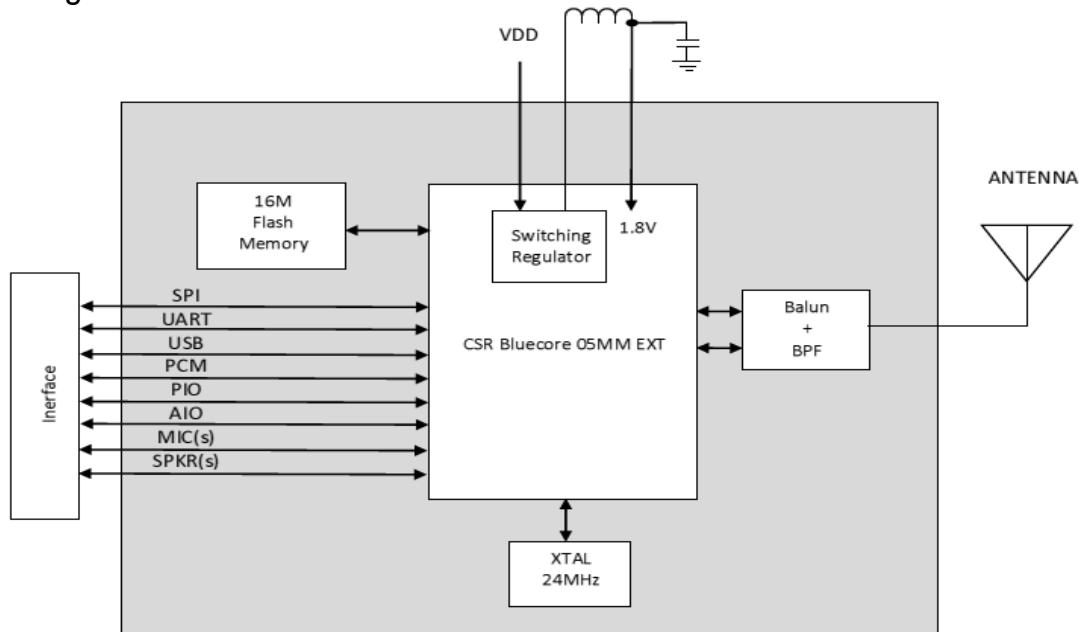

Figure 1 Simplified Block Diagram of MM516

### 1.3 Pin Configuration

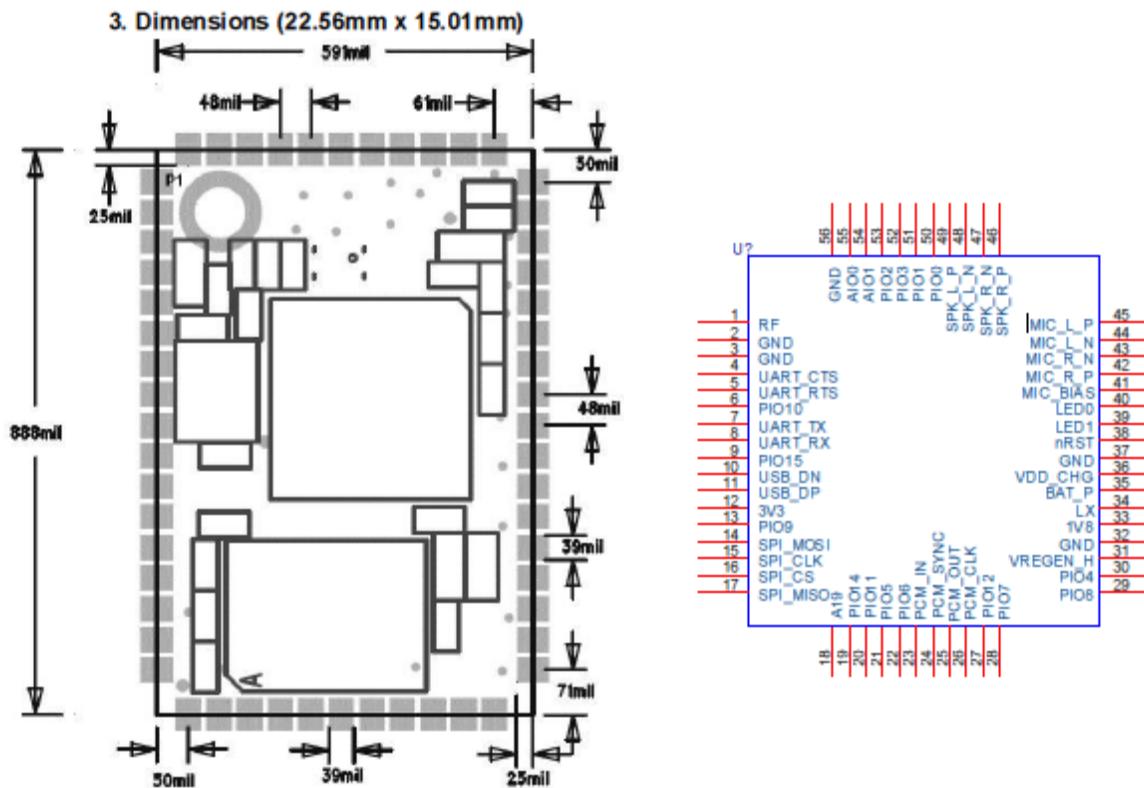

Figure 2 Pin Configuration for the MM516 and PCB Layout

### 1.4 Pin Description

| No. | Symbol   | I/O | Description                                    |

|-----|----------|-----|------------------------------------------------|

| 1   | RF       | I/O | RF input/output                                |

| 2   | GND      | -   | Ground                                         |

| 3   | GND      | -   | Ground                                         |

| 4   | UART_CTS | I   | UART clear to send, active low                 |

| 5   | UART_RTS | O   | UART request to send, active low               |

| 6   | PIO(10)  | I/O | Programmable I/O line                          |

| 7   | UART_TX  | I   | UART data output, active low                   |

| 8   | UART_RX  | O   | UART data input, active low (idle status high) |

| 9   | PIO(15)  | I/O | Programmable I/O line                          |

| 10  | USB_DN   | I/O | USB Data Negative                              |

|    |          |     |                                              |

|----|----------|-----|----------------------------------------------|

| 11 | USB_DP   | I/O | USB Data Positive                            |

| 12 | 3V3      | I   | 3.3V input                                   |

| 13 | PIO(9)   | I/O | Programmable I/O line                        |

| 14 | SPI_MOSI | I   | Synchronous serial interface data input      |

| 15 | SPI_CLK  | I   | Synchronous serial interface Clock           |

| 16 | SPI_CSB  | I   | Chip select for Synchronous Serial interface |

| 17 | SPI_MISO | O   | Synchronous serial interface data output     |

| 18 | A19      | I   | Dual mode selection (8Mb default pull low)   |

| 19 | PIO(14)  | I/O | Programmable I/O line                        |

| 20 | PIO(11)  | I/O | Programmable I/O line                        |

| 21 | PIO(5)   | I/O | Programmable I/O line                        |

| 22 | PIO(6)   | I/O | Programmable I/O line                        |

| 23 | PCM_IN   | I   | Synchronous PCM data input                   |

| 24 | PCM_SYNC | I/O | Synchronous PCM data strobe                  |

| 25 | PCM_OUT  | O   | Synchronous PCM data output                  |

| 26 | PCM_CLK  | I/O | Synchronous PCM data clock                   |

| 27 | PIO(12)  | I/O | Programmable I/O line                        |

| 28 | PIO(7)   | I/O | Programmable I/O line                        |

| 29 | PIO(8)   | I/O | Programmable I/O line                        |

| 30 | PIO(4)   | I/O | Programmable I/O line                        |

| 31 | VREGEN_H | I   | Internal SMPS 1.8v enable                    |

| 32 | GND      | -   | Ground                                       |

| 33 | 1V8      | I   | 1.8V Voltage input                           |

|    |          |     |                                |

|----|----------|-----|--------------------------------|

| 34 | LX       | O   | Internal SMPS 1.8V output      |

| 35 | BAT_P    | I   | Battery input                  |

| 36 | VDD_CHG  | I   | Internal Battery Charger input |

| 37 | GND      | -   | Ground                         |

| 38 | nRST     | I   | Reset (Low Active)             |

| 39 | LED1     | O   | LED1                           |

| 40 | LED0     | O   | LED0                           |

| 41 | MIC_BIAS | O   | Microphone Bias                |

| 42 | MIC_R_P  | I   | Microphone Right Positive      |

| 43 | MIC_R_N  | I   | Microphone Right Negative      |

| 44 | MIC_L_N  | I   | Microphone Left Negative       |

| 45 | MIC_L_P  | I   | Microphone Left Positive       |

| 46 | SPK_R_P  | O   | Speaker Right Positive         |

| 47 | SPK_R_N  | O   | Speaker Right Negative         |

| 48 | SPK_L_N  | O   | Speaker Left Negative          |

| 49 | SPK_L_P  | O   | Speaker Left Positive          |

| 50 | PIO(0)   | I/O | Programmable I/O line          |

| 51 | PIO(1)   | I/O | Programmable I/O line          |

| 52 | PIO(3)   | I/O | Programmable I/O line          |

| 53 | PIO(2)   | I/O | Programmable I/O line          |

| 54 | AIO(1)   | I/O | Programmable I/O line          |

| 55 | AIO(0)   | I/O | Programmable I/O line          |

| 56 | GND      | -   | Ground                         |

Table 1 Pin Description

## 1.5 Firmware

The on-board BlueCore 5 chip made by CSR, is supplied with Bluetooth v2.1 + EDR compliant stack firmware, which runs on the internal RISC microcontroller.

The BlueCore 5 chip software architecture allows Bluetooth processing and the application program to be shared in different ways between the internal RISC microcontroller and an external host processor. The upper layers of the Bluetooth stack (above HCI) can be run either on-chip or on the host processor.

# 2 Basic Operating Information

## 2.1 Power Supply

The MM516 is supplied from a single external regulated 3.3V supply voltage (VDD). This supply voltage must always be present.

The BlueCore 5 chip contains an internal 1.8 V switch mode power supply which is enabled by connecting pin 31 (VREGEN\_H) to VDD. The output of the regulator is on pin 34 (LX) and needs to be connected to pin 33 (1V8) with a low pass filter comprised of a 22uH inductor (Taiyo Yuden LBR2518T220K or equivalent) between the pins and a 10uF, low ESR ceramic capacitor on pin 33.

The 1.8V voltage may not be used for supplying other components in the host system.

## 2.2 Clocking

The MM516 module contains a 24 MHz crystal from which the internal system clock for the BlueCore 5 chip is generated.

## 3 Physical Description

### 3.1 RF Receiver

The receiver features a near-zero IF architecture that allows the channel filters to be integrated onto the die. Sufficient out-of-band blocking specification at the LNA input allows the radio to be used in close proximity to GSM and WCDMA cellular phone transmitters without being desensitized. The use of a digital FSK discriminator means that no discriminator tank is needed and its excellent performance in the presence of noise allows BlueCore 5 chip to exceed the Bluetooth requirements for co-channel and adjacent channel rejection.

For EDR, an ADC is used to digitize the IF received signal.

#### 3.1.1 Low Noise Amplifier

The LNA can be configured to operate in single-ended or differential mode. Single-ended mode is used for Class 1 Bluetooth operation; differential mode is used for Class 2 operation.

#### 3.1.2 Analog to Digital Converter

The ADC is used to implement fast AGC. The ADC samples the RSSI voltage on a slot-by-slot basis. The front-end LNA gain is changed according to the measured RSSI value, keeping the first mixer input signal within a limited range. This improves the dynamic range of the receiver, improving performance in interference limited environments.

### 3.2 RF Transmitter

#### 3.2.1 IQ Modulator

The transmitter features a direct IQ modulator to minimize the frequency drift during a transmit timeslot, which results in a controlled modulation index. Digital baseband transmit circuitry provides the required spectral shaping.

#### 3.2.2 Power Amplifier

The internal PA has a maximum output power of 6dBm. This allows BlueCore 5 chip to be used in Class 2 and Class 3 radios without an external RF PA.

Support for transmit power control allows a simple implementation for Class 1 with an external RF PA.

### 3.3 RF Synthesizer

The radio synthesizer is fully integrated onto the die with no requirement for an external VCO screening can, varactor tuning diodes, LC resonators or loop filter. The synthesizer is guaranteed to lock in sufficient time across the guaranteed temperature range to meet the Bluetooth v2.1 + EDR specification.

### 3.4 Clock Input and Generation

The reference clock for the system is generated from a crystal input of 24MHz. All internal reference clocks are generated using a phase locked loop, which is locked to the external reference frequency.

### 3.5 Baseband and Logic

#### 3.5.1 Memory Management Unit

The MMU provides a number of dynamically allocated ring buffers that hold the data that is in transit between the host and the air. The dynamic allocation of memory ensures efficient use of the available RAM and is performed by a hardware MMU to minimize the overheads on the processor during data/voice transfers.

#### 3.5.2 Burst Mode Controller

During radio transmission the BMC constructs a packet from header information previously loaded into memory mapped registers by the software and payload data/voice taken from the appropriate ring buffer in the RAM. During radio reception, the BMC stores the packet header in memory-mapped registers and the payload data in the appropriate ring buffer in RAM. This architecture minimizes the intervention required by the processor during transmission and reception.

#### 3.5.3 Physical Layer Hardware Engine DSP

Dedicated logic is used to perform the following:

- Forward error correction

- Header error control

- Cyclic redundancy check

- Encryption

- Data whitening

- Access code correlation

- Audio transcoding

The following voice data translations and operations are performed by firmware:

- A-law/μ-law/linear voice data (from host)

- A-law/μ-law/CVSD (over the air)

- Voice interpolation for lost packets

- Rate mismatch correction

The hardware supports all optional and mandatory features of Bluetooth v2.1 + EDR including AFH and eSCO.

#### 3.5.4 System RAM

48KB of on-chip RAM is provided to support the RISC MCU and is shared between the ring buffers used to hold voice/data for each active connection and the general purpose memory required by the Bluetooth stack.

#### 3.5.5 External Memory Driver

The External Memory Driver interface can be used to connect to the external Flash memory and also to the optional external RAM for memory intensive applications.

#### 3.5.6 Kalimba DSP RAM

Additional on-chip RAM is provided to support the Kalimba DSP:

- 16K x 24-bit for data memory 1 (DM1)

- 12K x 24-bit for data memory 2 (DM2)

- 6K x 32-bit for program memory (PM)

DSP can also execute directly from external Flash, using a 64-instruction on-chip cache.

#### 3.5.7 USB

This is a full-speed USB interface for communicating with other compatible digital devices. BlueCore 5 chip acts as a USB peripheral, responding to requests from a master host controller such as a PC.

### 3.5.8 Synchronous Serial Interface

### 3.5.9 UART

This is a standard UART interface for communicating with other serial devices.

## 3.6 Microcontroller

The MCU, interrupt controller and event timer run the Bluetooth software stack and control the radio and host interfaces. A 16-bit RISC microcontroller is used for low power consumption and efficient use of memory.

### 3.6.1 Programmable I/O

BlueCore 5 chip has a total of 18 programmable I/O terminals (16 digital and 2 analog). These are controlled by firmware running on the device.

### 3.6.2 802.11 Coexistence Interface

Dedicated hardware is provided to implement a variety of 802.11 (Wi-Fi) coexistence schemes. Channel skipping AFH, priority signalling, channel signalling and host passing of channel instructions are all supported. The features are configured in firmware. The details of some methods are proprietary. Contact CSR for details.

## 4 Bluetooth Software Stacks

The BlueCore 5 chip is supplied with Bluetooth v2.1 + EDR compliant stack firmware, which runs on the internal RISC microcontroller.

The BlueCore 5 chip software architecture allows Bluetooth processing and the application program to be shared in different ways between the internal RISC microcontroller and an external host processor (if any). The upper layers of the Bluetooth stack (above HCI) can be run either on-chip or on the host processor.

### 4.1 BlueCore HCI Stack

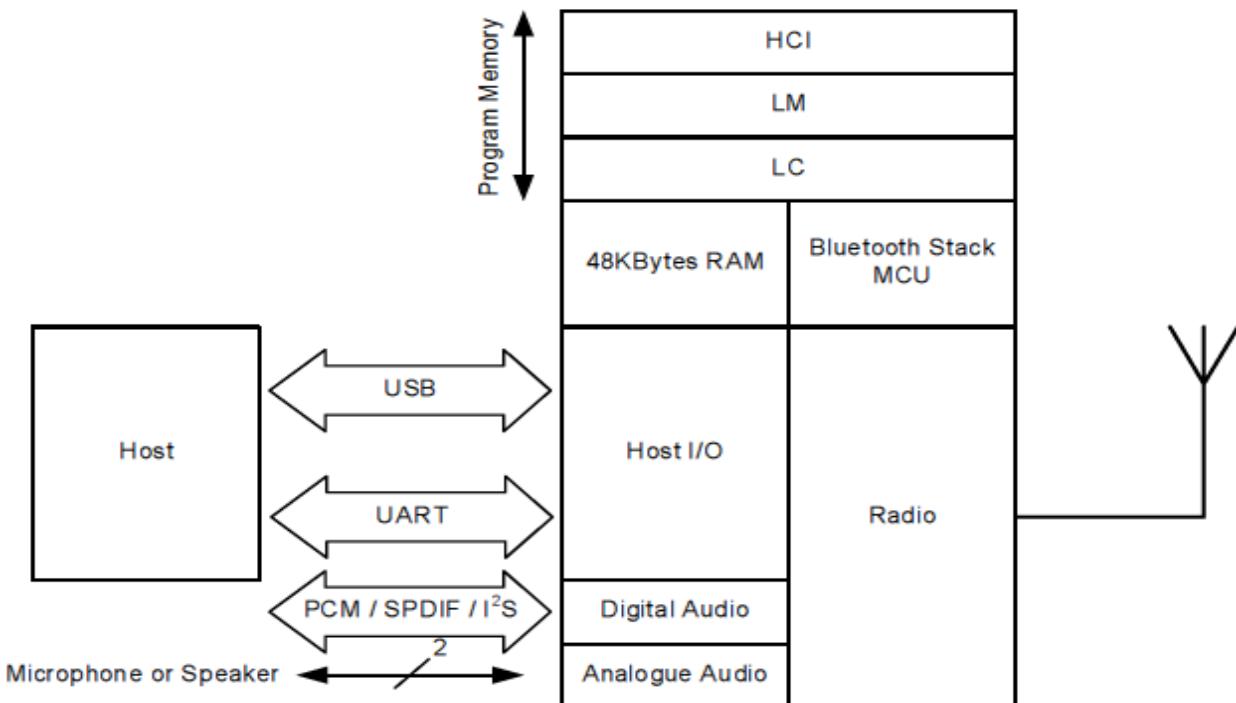

Figure 3 BlueCore HCI Stack

In the implementation shown in Figure 3 the internal processor runs the Bluetooth stack up to the HCI. The Host processor must provide all upper layers including the application.

#### 4.1.1 Key Features of the HCI Stack: Standard Bluetooth Functionality

Bluetooth v2.1 + EDR mandatory functionality:

- AFH, including classifier

- Faster connection - enhanced inquiry scan (immediate FHS response)

- LMP improvements

- Parameter ranges

Optional Bluetooth v2.1 + EDR functionality supported:

- AFH as Master and Automatic Channel Classification

- Fast Connect: Interlaced Inquiry and Page Scan plus RSSI during Inquiry

- eSCO, eV3 +CRC, eV4, eV5

- SCO handle

- Synchronization

The firmware was written against the Bluetooth v2.1 + EDR specification.

- Bluetooth components:

- Baseband (including LC)

- LM

- HCI

- Standard USB v2.0 and UART HCI Transport Layers

- All standard radio packet types

- Full Bluetooth data rate, enhanced data rates of 2 and 3Mbps

- Operation with up to seven active slaves<sup>1</sup>

- Scatternet v2.5 operation

- Maximum number of simultaneous active ACL connections: 7

- Maximum number of simultaneous active SCO connections: 3<sup>2</sup>

- Operation with up to three SCO links, routed to one or more slaves

- All standard SCO voice coding, plus transparent SCO

- Standard operating modes: Page, Inquiry, Page-Scan and Inquiry-Scan

- All standard pairing, authentication, link key and encryption operations

- Standard Bluetooth power saving mechanisms: Hold, Sniff and Park modes, including Forced Hold

- Dynamic control of peers' transmit power via LMP

- Master/Slave switch

- Broadcast

- Channel quality driven data rate

- All standard Bluetooth test modes

- A block of radio test or BIST commands allows direct control of the chip's radio. This aids the development of modules' radio designs, and can be used to support Bluetooth qualification.

- VM. The firmware provides the VM environment in which to run application-specific code. Although the is mainly used with BlueLab and RFCOMM builds (alternative firmware builds providing L2CAP, SDP and RFCOMM), the VM can be used with this build to perform simple tasks such as flashing LEDs via the chip's PIO port.

- Hardware low power modes: Shallow Sleep and Deep Sleep. The chip drops into modes that significantly reduce power consumption when the software goes idle.

- SCO channels are normally routed via HCI (over BCSP). However, up to three SCO channels can be routed over the chip's single PCM port (at the same time as routing any remaining SCO channels over HCI).

---

<sup>1</sup>

This is the maximum allowed by Bluetooth v2.1 + EDR specification.

<sup>2</sup>

BlueCore 5 chip supports all combinations of active ACL and SCO channels for both master and slave operation, as specified by the Bluetooth v2.1 + EDR specification.

The firmware's supported Bluetooth features are detailed in the standard PICS documents, available from [www.csr.com](http://www.csr.com).

## 4.2 Key Features of the HCI Stack: Extra Functionality

The firmware extends the standard Bluetooth functionality with the following features:

- Supports BlueCore Serial Protocol (BCSP), a proprietary, reliable alternative to the standard Bluetooth UART Host Transport

- Supports H4 Deep Sleep (H4DS), a proprietary alternative to the standard Bluetooth UART Host Transport, supporting Deep Sleep for low-power applications

- Provides a set of approximately 50 manufacturer-specific HCI extension commands. This command set, called BlueCore Command (BCCMD), provides:

- Access to BlueCore5-Multimedia External general-purpose PIO port

- The negotiated effective encryption key length on established Bluetooth links

- Access to the firmware random number generator

- Controls to set the default and maximum transmit powers; these can help minimise interference between overlapping, fixed-location piconets

- Dynamic UART configuration

- Bluetooth radio transmitter enable/disable. A simple command connects to a dedicated hardware switch that determines whether the radio can transmit.

- The firmware can read the voltage on a pair of BlueCore5-Multimedia External external pins. This is normally used to build a battery monitor

- A block of BCCMD commands provides access to the BlueCore5-Multimedia External Persistent Store (PS) configuration database. The database sets the BlueCore5-Multimedia External Bluetooth address, Class of Device, Bluetooth radio (transmit class) configuration, SCO routing, link manager (LM), etc.

- A UART break condition can be used in three ways:

- Presenting a UART break condition to the chip can force the chip to perform a hardware reboot

- Presenting a break condition at boot time can hold the chip in a low power state, preventing normal initialization while the condition exists

- With BCSP, the firmware can be configured to send a break to the host before sending data. (This is normally used to wake the host from a Deep Sleep state.)

- A block of Bluetooth radio test or BIST commands allows direct control of the BlueCore5-Multimedia External radio. This aids the development of modules' radio designs, and can be used to support Bluetooth qualification.

- Hardware low power modes: Shallow Sleep and Deep Sleep. The chip drops into modes that significantly reduce power consumption when the software goes idle.

- SCO channels are normally routed via HCI (over BCSP). However, up to three SCO channels can be routed over the PCM interface (at the same time as routing any remaining SCO channels over HCI).

MM516

#### 4.3 Additional Software for Other Embedded Applications

When the upper layers of the Bluetooth protocol stack are run as firmware on BlueCore 5 chip, a UART software driver is supplied that presents the L2CAP, RFCOMM and SDP APIs to higher Bluetooth stack layers running on the host. The code is provided as C source or object code.

#### 4.4 CSR Development Systems

CSR's BlueLab Multimedia and Casira development kits are available to allow the evaluation of the BlueCore 5-External hardware and software, and as toolkits for developing on-chip and host software.

## 5 Interfaces

### 5.1 UART Interface

This is a standard UART interface for communicating with other serial devices.

BlueCore 5 chip UART interface provides a simple mechanism for communicating with other serial devices using the RS232 protocol.

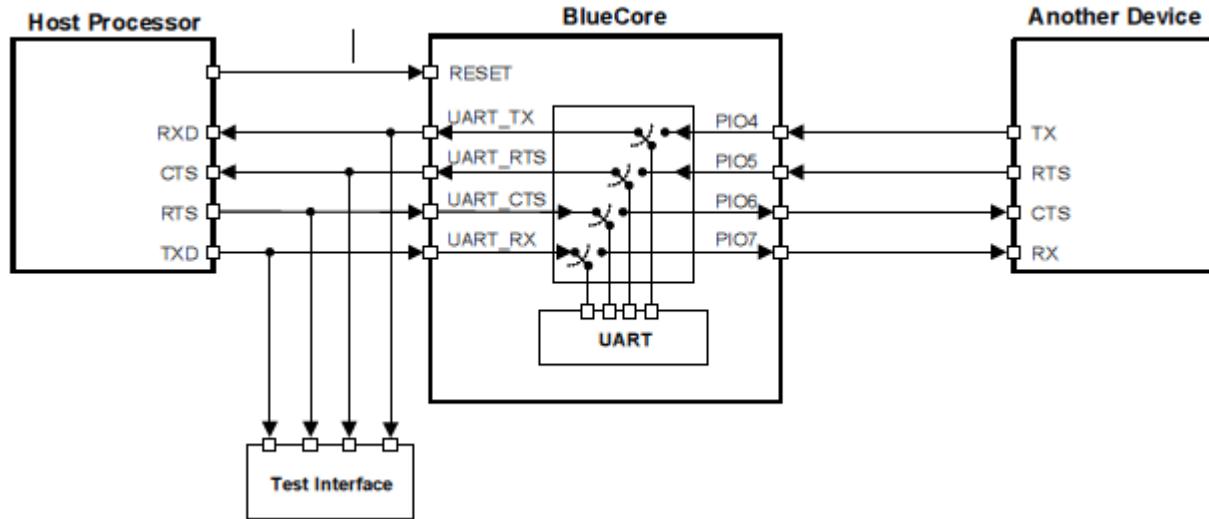

Figure 4 Universal Asynchronous Receiver/Transmitter

Four signals are used to implement the UART function, as shown in Figure 4. When BlueCore 5 chip is connected to another digital device, UART\_RX and UART\_TX transfer data between the two devices. The remaining two signals, UART\_CTS and UART\_RTS, can be used to implement RS232 hardware flow control where both are active low indicators. All UART connections are implemented using CMOS technology and have signalling levels of 0V and VDD\_USB.

UART configuration parameters, such as data rate and packet format, are set using BlueCore 5 chip software.

Note:

In order to communicate with the UART at its maximum data rate using a standard PC, an accelerated serial port adapter card is required for the PC.

| Parameter           | Possible Values   |                       |

|---------------------|-------------------|-----------------------|

| Data Rate           | Minimum           | 1200 bits/s (2%Error) |

|                     |                   | 9600 bits/s (1%Error) |

|                     | Maximum           | 3M bit/s (1%Error)    |

| Flow Control        | RTS/CTS or None   |                       |

| Parity              | None, Odd or Even |                       |

| Number of Stop Bits | 1 or 2            |                       |

| Bits per Channel    | 8                 |                       |

Table 2 UART Settings

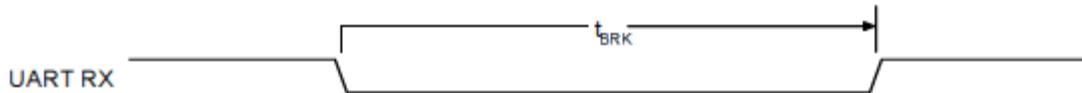

The UART interface is capable of resetting BlueCore 5 chip upon reception of a break signal. A break is identified by a continuous logic low (0V) on the UART\_RX terminal, as shown in Figure 5. If t\_BRK is longer than the value, defined by PSKEY\_HOST\_IO\_UART\_RESET\_TIMEOUT, (0x1a4), a reset will occur. This feature allows a host to initialize the system to a known state. Also, BlueCore 5 chip can emit a break character that may be used to wake the host.

Figure 5 Break Signal

**Note:**

The DFU boot loader must be loaded into the Flash device before the UART or USB interfaces can be used. This initial flash programming can be done via the SPI.

Table 3 shows a list of commonly used data rates and their associated values for PSKEY\_UART\_BAUD\_RATE (0x204). There is no requirement to use these standard values. Any data rate within the supported range can be set in the PS Key according to the formula

$$\text{Data Rate} = \text{PSKEY_UART_BAUDRATE}/0.004096$$

| Data Rate (bits/s) | Persistent Store Value | Error | Dec    |

|--------------------|------------------------|-------|--------|

|                    | Hex                    |       |        |

| 1200               | 0x0005                 | 5     | 1.73%  |

| 2400               | 0x000a                 | 10    | 1.73%  |

| 4800               | 0x0014                 | 20    | 1.73%  |

| 9600               | 0x0027                 | 39    | -0.82% |

| 19200              | 0x004f                 | 79    | 0.45%  |

| 38400              | 0x009d                 | 157   | -0.18% |

| 57600              | 0x00ec                 | 236   | 0.03%  |

| 76800              | 0x013b                 | 315   | 0.14%  |

| 115200             | 0x01d8                 | 472   | 0.03%  |

| 230400             | 0x03b0                 | 944   | 0.03%  |

| 460800             | 0x075f                 | 1887  | -0.02% |

| 921600             | 0x0ebf                 | 3775  | 0.00%  |

| 1382400            | 0x161e                 | 5662  | -0.01% |

| 1843200            | 0x1d7e                 | 7550  | 0.00%  |

| 2764800            | 0x2c3d                 | 11325 | 0.00%  |

Table 3 Standard Data Rates

Figure 6      UART Bypass Architecture

### 5.1.1 UART Configuration While RESET is Active

The UART interface for BlueCore 5 chip while the chip is being held in reset is tristate. This will allow the user to daisy chain devices onto the physical UART bus. The constraint on this method is that any devices connected to this bus must tristate when BlueCore 5 chip reset is de-asserted and the firmware begins to run.

### 5.1.2 UART Bypass Mode

Alternatively, for devices that do not tristate the UART bus, the UART bypass mode on BlueCore 5 chip can be used. The default state of BlueCore 5 chip after reset is de-asserted; this is for the host UART bus to be connected to the BlueCore 5 chip UART, thereby allowing communication to BlueCore 5 chip via the UART. All UART bypass mode connections are implemented using CMOS technology and have signalling levels of 0V and VDD\_PADS.

In order to apply the UART bypass mode, a BCCMD command will be issued to BlueCore 5 chip. Upon this issue, it will switch the bypass to PIO[7:4] as Figure 7 indicates. Once the bypass mode has been invoked, BlueCore 5 chip will enter the Deep Sleep state indefinitely.

In order to re-establish communication with BlueCore 5 chip, the chip must be reset so that the default configuration takes effect.

It is important for the host to ensure a clean Bluetooth disconnection of any active links before the bypass mode is invoked. Therefore, it is not possible to have active Bluetooth links while operating the bypass mode.

### 5.1.3 Current Consumption in UART Bypass Mode

The current consumption for a device in UART bypass mode is equal to the values quoted for a device in standby mode.

## 5.2 USB Interface

This is a full speed (12Mbits/s) USB interface for communicating with other compatible digital devices. BlueCore 5-External acts as a USB peripheral, responding to requests from a master host controller such as a PC. The USB interface is capable of driving a USB cable directly. No external USB transceiver is required. The device operates as a USB peripheral, responding to requests from a master host controller such as a PC. Both the OHCI and the UHCI standards are supported. The set of USB endpoints implemented can behave as specified in the USB section of the Bluetooth v2.1 + EDR specification or alternatively can appear as a set of endpoints appropriate to USB audio devices such as speakers.

As USB is a master/slave oriented system (in common with other USB peripherals), BlueCore 5 chip only supports USB Slave operation.

### 5.2.1 USB Data Connections

The USB data lines emerge as pins USB\_DP and USB\_DN. These terminals are connected to the internal USB I/O buffers of the BlueCore 5 chip, therefore, have a low output impedance. To match the connection to the characteristic impedance of the USB cable, resistors must be placed in series with USB\_DP/USB\_DN and the cable.

### 5.2.2 USB Pull-Up Resistor

BlueCore 5 chip features an internal USB pull-up resistor. This pulls the USB\_DP pin weakly high when BlueCore 5 chip is ready to enumerate. It signals to the PC that it is a full speed (12Mbits/s) USB device. The USB internal pull-up is implemented as a current source, and is compliant with section 7.1.5 of the USB specification v1.2. The internal pull-up pulls USB\_DP high to at least 2.8V when loaded with a 15k 5% pull-down resistor (in the hub/host) when VDD\_PADS = 3.1V. This presents a Thevenin resistance to the host of at least 900. Alternatively, an external 1.5k pull-up resistor can be placed between a PIO line and D+ on the USB cable. The firmware must be alerted to which mode is used by setting PSKEY\_USB\_PIO\_PULLUP appropriately. The default setting uses the internal pull-up resistor.

### 5.2.3 USB Power Supply

The USB specification dictates that the minimum output high voltage for USB data lines is 2.8V. To safely meet the USB specification, the voltage on the VDD\_USB supply terminals must be an absolute minimum of 3.1V. CSR recommends 3.3V for optimal USB signal quality.

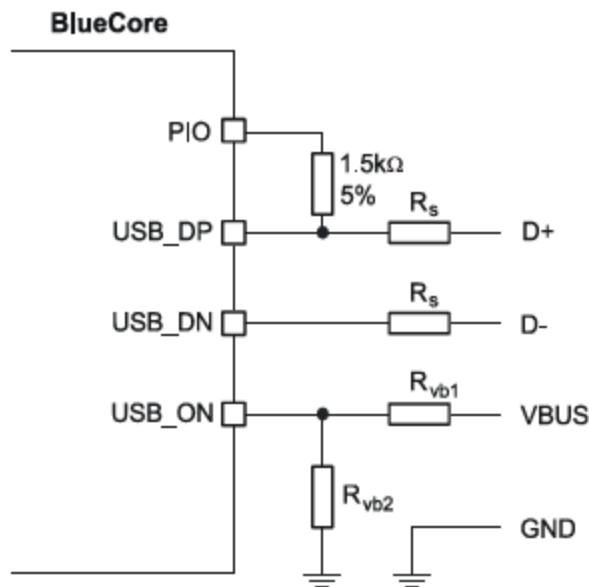

### 5.2.4 Self-Powered Mode

In self-powered mode, the circuit is powered from its own power supply and not from the VBUS (5V) line of the USB cable. It draws only a small leakage current (below 0.5mA) from VBUS on the USB cable. This is the easier mode for which to design, as the design is not limited by the power that can be drawn from the USB hub or root port. However, it requires that VBUS be connected to BlueCore 5 chip via a resistor network (R\_vb1 and R\_vb2), so BlueCore 5 chip can detect when VBUS is powered up. BlueCore 5 chip will not pull USB\_DP high when VBUS is off.

Self-powered USB designs (powered from a battery or PSU) must ensure that a PIO line is allocated for USB pullup purposes. A 1.5k 5% pull-up resistor between USB\_DP and the selected PIO line should be fitted to the design. Failure to fit this resistor may result in the design failing to be USB compliant in self-powered mode. The internal pull-up in BlueCore is only suitable for bus-powered USB devices, e.g., dongles.

Figure 7 USB Connections for Self-Powered Mode

The terminal marked USB\_ON can be any free PIO pin. The PIO pin selected must be registered by setting PSKEY\_USB\_PIO\_VBUS to the corresponding pin number.

**Note:**

USB\_ON is shared with BlueCore 5 chip PIO terminals.

| Identifier | Value      | Function                        |

|------------|------------|---------------------------------|

| $R_s$      | 27 nominal | Impedance matching to USB cable |

| $R_{vb1}$  | 22k 5%     | VBUS ON sense divider           |

| $R_{vb2}$  | 47k 5%     | VBUS ON sense divider           |

Table 3 USB Interface Component Values

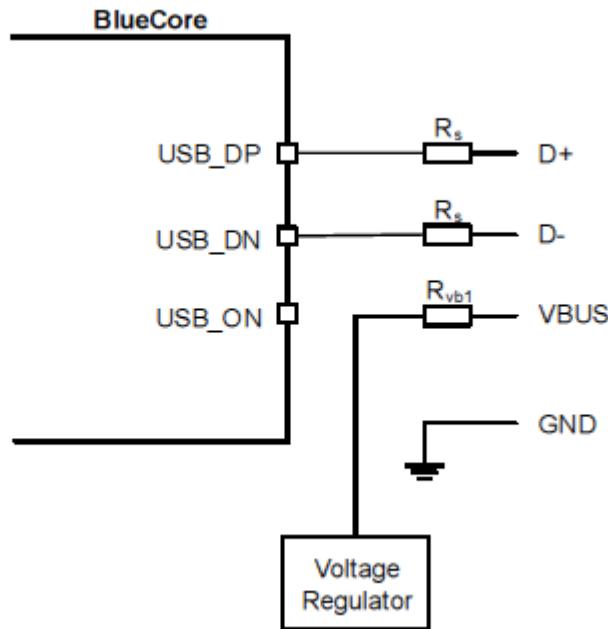

### 5.2.5 Bus-Powered Mode

In bus-powered mode, the application circuit draws its current from the 5V VBUS supply on the USB cable. BlueCore 5 chip negotiates with the PC during the USB enumeration stage about how much current it is allowed to consume. For Class 2 Bluetooth applications, CSR recommends that the regulator used to derive 3.3V from VBUS is rated at 100mA average current and should be able to handle peaks of 120mA without foldback or limiting. In bus-powered mode, BlueCore 5 chip requests 100mA during enumeration. For Class 1 Bluetooth applications, the USB power descriptor should be altered to reflect the amount of power required. This is accomplished by setting PSKEY\_USB\_MAX\_POWER (0x2c6). This is higher than for a Class 2 application due to the extra current drawn by the Transmit RF PA. When selecting a regulator, be aware that VBUS may go as low as 4.4V. The inrush current (when charging reservoir and supply decoupling capacitors) is limited by the USB specification. See the USB Specification. Some applications may require soft start circuitry to limit inrush current if more than 10F is present between VBUS and GND. The 5V VBUS line emerging from a PC is often electrically noisy. As well as regulation down to 3.3V and 1.8V, applications should include careful filtering of the 5V line to attenuate noise that is above the voltage regulator bandwidth. Excessive noise on the 1.8V supply to the analog supply pins of BlueCore 5 chip will result in reduced receive sensitivity and a distorted RF transmit signal.

Figure 8      USB Connections for Bus-Powered Mode

### 5.2.6 Suspend Current

All USB devices must permit the USB controller to place them in a USB suspend mode. While in USB Suspend, bus-powered devices must not draw more than 0.5mA from USB VBUS (self-powered devices may draw more than 0.5mA from their own supply). This current draw requirement prevents operation of the radio by bus-powered devices during USB Suspend.

The voltage regulator circuit itself should draw only a small quiescent current (typically less than 100A) to ensure adherence to the suspend current requirement of the USB specification. This is not normally a problem with modern regulators. Ensure that external LEDs and/or amplifiers can be turned off by BlueCore 5 chip. The entire circuit must be able to enter the suspend mode. Refer to separate CSR documentation for more details on USB Suspend.

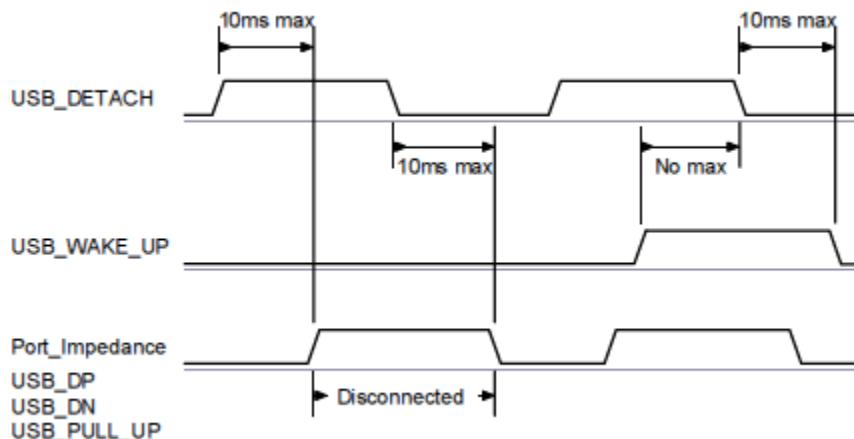

### 5.2.7 Detach and Wake\_Up Signaling

BlueCore 5 chip can provide out-of-band signaling to a host controller by using the control lines called USB\_DETACH and USB\_WAKE\_UP. These are outside the USB specification (no wires exist for them inside the USB cable), but can be useful when embedding BlueCore 5 chip into a circuit where no external USB is visible to the user. Both control lines are shared with PIO pins and can be assigned to any PIO pin by setting PSKEY\_USB\_PIO\_DETACH and PSKEY\_USB\_PIO\_WAKEUP to the selected PIO number.

USB\_DETACH is an input which, when asserted high, causes BlueCore 5 chip to put USB\_DN and USB\_DP in a high impedance state and turns off the pull-up resistor on DP. This detaches the device from the bus and is logically equivalent to unplugging the device. When USB\_DETACH is taken low, BlueCore 5 chip will connect back to USB and await enumeration by the USB host.

USB\_WAKE\_UP is an active high output (used only when USB\_DETACH is active) to wake up the host and allow USB communication to recommence. It replaces the function of the software USB\_WAKE\_UP message (which runs over the USB cable) and cannot be sent while BlueCore 5 chip is effectively disconnected from the bus.

Figure 9        USB\_DETACH and USB\_WAKE\_UP Signals

### 5.2.8 USB Driver

A USB Bluetooth device driver is required to provide a software interface between BlueCore 5 chip and Bluetooth software running on the host computer. Suitable drivers are available from <http://www.csrsupport.com>.

### 5.2.9 USB v2.0 Compliance

BlueCore 5 chip is qualified to USB Specification v2.0, details of which are available from <http://www.usb.org>. The specification contains valuable information on aspects such as PCB track impedance, supply inrush current and product labeling.

Although BlueCore 5 chip meets the USB specification, CSR cannot guarantee that an application circuit designed around the chip is USB compliant. The choice of application circuit, component choice and PCB layout all affect USB signal quality and electrical characteristics. The information in this document is intended as a guide and should be read in association with the USB specification, with particular attention being given to Chapter 7.

Independent USB qualification must be sought before an application is deemed USB compliant and can bear the USB logo. Such qualification can be obtained from a USB plugfest or from an independent USB test house.

Terminals USB\_DP and USB\_DN adhere to the USB Specification v2.0 (Chapter 7) electrical requirements.

### 5.2.10 USB 2.0 Compatibility

BlueCore 5 chip is compatible with USB v2.0 host controllers; under these circumstances the two ends agree the mutually acceptable rate of 12Mbits/s according to the USB v2.0 specification.

## 5.3 Serial Peripheral Interface

BlueCore 5 chip uses 16-bit data and 16-bit address serial peripheral interface, where transactions may occur when the internal processor is running or is stopped. This section details the considerations required when interfacing to BlueCore 5 chip via the four dedicated serial peripheral interface terminals. Data may be written or read one word at a time or the auto increment feature may be used to access blocks.

### 5.3.1 Instruction Cycle

The BlueCore 5 chip is the slave and receives commands on SPI\_MOSI and outputs data on SPI\_MISO. Table 4 shows the instruction cycle for an SPI transaction.

|   |                          |                                                             |

|---|--------------------------|-------------------------------------------------------------|

| 1 | Reset the SPI interface  | Hold SPI_CS <sub>B</sub> high for two SPI_CLK cycles        |

| 2 | Write the command word   | Take SPI_CS <sub>B</sub> low and clock in the 8 bit command |

| 3 | Write the address        | Clock in the 16-bit address word                            |

| 4 | Write or read data words | Clock in or out 16-bit data word(s)                         |

| 5 | Termination              | Take SPI_CS <sub>B</sub> high                               |

Table 4 Instruction Cycle for an SPI Transaction

With the exception of reset, SPI\_CS<sub>B</sub> must be held low during the transaction. Data on SPI\_MOSI is clocked into the BlueCore 5 chip on the rising edge of the clock line SPI\_CLK. When reading, BlueCore 5 chip will reply to the master on SPI\_MISO with the data changing on the falling edge of the SPI\_CLK. The master provides the clock on SPI\_CLK. The transaction is terminated by taking SPI\_CS<sub>B</sub> high.

Sending a command word and the address of a register for every time it is to be read or written is a significant overhead, especially when large amounts of data are to be transferred. To overcome this BlueCore 5 chip offers increased data transfer efficiency via an auto increment operation. To invoke auto increment, SPI\_CS<sub>B</sub> is kept low, which auto increments the address, while providing an extra 16 clock cycles for each extra word to be written or read.

Prestige, Quality and Innovation.

MM516

### 5.3.2 Writing to the Device

To write to BlueCore 5 chip, the 8-bit write command (00000010) is sent first (C[7:0]) followed by a 16-bit address (A[15:0]). The next 16-bits (D[15:0]) clocked in on SPI\_MOSI are written to the location set by the address (A). Thereafter for each subsequent 16-bits clocked in, the address (A) is incremented and the data written to consecutive locations until the transaction terminates when SPI\_CSB is taken high.

Figure 10 SPI Write Operation

### 5.3.3 Reading from the Device

Reading from BlueCore 5 chip is similar to writing to it. An 8-bit read command (00000011) is sent first (C[7:0]), followed by the address of the location to be read (A[15:0]). BlueCore 5 chip then outputs on SPI\_MISO a check word during T[15:0] followed by the 16-bit contents of the addressed location during bits D[15:0].

The check word is composed of {command, address [15:8]}. The check word may be used to confirm a read operation to a memory location. This overcomes the problems encountered with typical serial peripheral interface slaves, whereby it is impossible to determine whether the data returned by a read operation is valid data or the result of the slave device not responding.

If SPI\_CSB is kept low, data from consecutive locations is read out on SPI\_MISO for each subsequent 16 clocks, until the transaction terminates when SPI\_CSB is taken high.

Figure 11 SPI Read Operation

### 5.3.4 Multi-Slave Operation

BlueCore 5 chip should not be connected in a multi-slave arrangement by simple parallel connection of slave MISO lines. When BlueCore 5 chip is deselected (SPI\_CSB = 1), the SPI\_MISO line does not float. Instead, BlueCore 5 chip outputs 0 if the processor is running or 1 if it is stopped.

## 5.4 PCM Codec Interface

PCM is a standard method used to digitize audio (particularly voice) for transmission over digital communication channels. Through its PCM interface, BlueCore 5 chip has hardware support for continual transmission and reception of PCM data, thus reducing processor overhead for wireless headset applications. BlueCore 5 chip offers a bidirectional digital audio interface that routes directly into the baseband layer of the on-chip firmware. It does not pass through the HCI protocol layer.

Hardware on BlueCore 5 chip allows the data to be sent to and received from a SCO connection.

Up to three SCO connections can be supported by the PCM interface at any one time.

BlueCore 5 chip can operate as the PCM interface master generating an output clock of 128, 256 or 512kHz. When configured as PCM interface slave, it can operate with an input clock up to 2048kHz. BlueCore 5 chip is compatible with a variety of clock formats, including Long Frame Sync, Short Frame Sync and GCI timing environments.

It supports 13-bit or 16-bit linear, 8-bit  $\mu$ -law or A-law companded sample formats at 8ksamples/s and can receive and transmit on any selection of three of the first four slots following PCM\_SYNC. The PCM configuration options are enabled by setting PSKEY\_PCM\_CONFIG32.

BlueCore 5 chip interfaces directly to PCM audio devices.

### 5.4.1 PCM Interface Master/Slave

When configured as the master of the PCM interface, BlueCore 5 chip generates PCM\_CLK and PCM\_SYNC.

Figure 12      PCM Configured as a Master

When configured as the Slave of the PCM interface, BlueCore 5 chip accepts PCM\_CLK rates up to 2048kHz.

Figure 13 PCM Configured as a Slave

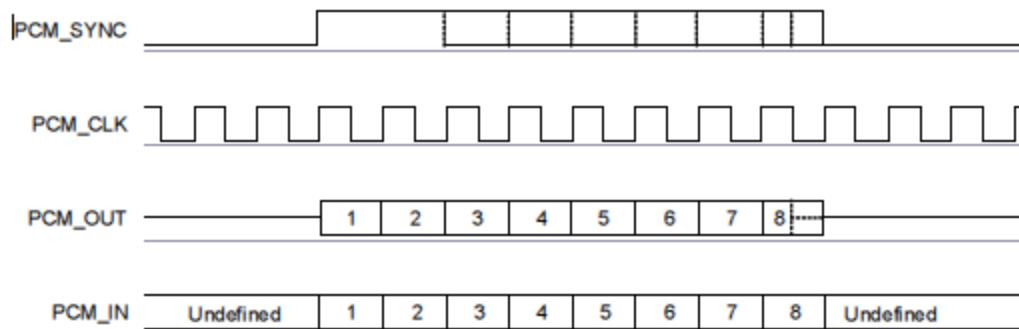

#### 5.4.2 Long Frame Sync

Long Frame Sync is the name given to a clocking format that controls the transfer of PCM data words or samples. In Long Frame Sync, the rising edge of PCM\_SYNC indicates the start of the PCM word. When BlueCore 5 chip is configured as PCM master, generating PCM\_SYNC and PCM\_CLK, then PCM\_SYNC is 8-bits long. When BlueCore 5 chip is configured as PCM Slave, PCM\_SYNC may be from two consecutive falling edges of PCM\_CLK to half the PCM\_SYNC rate, i.e., 62.5s long.

Figure 14 Long Frame Sync (Shown with 8-bit Companded Sample)

BlueCore 5 chip samples PCM\_IN on the falling edge of PCM\_CLK and transmits PCM\_OUT on the rising edge. PCM\_OUT may be configured to be high impedance on the falling edge of PCM\_CLK in the LSB position or on the rising edge.

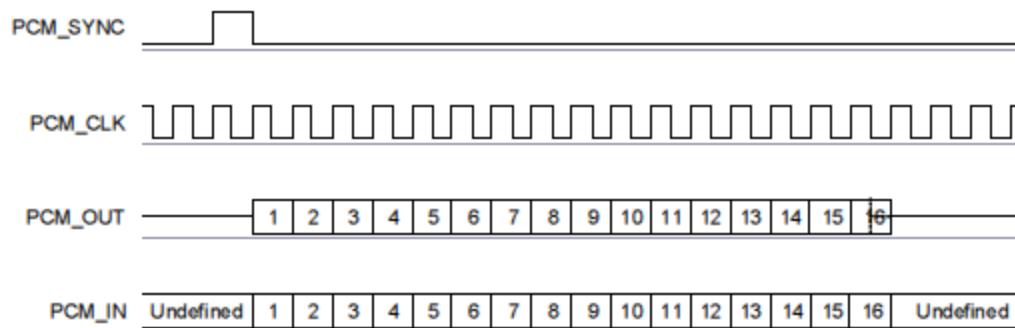

### 5.4.3 Short Frame Sync

In Short Frame Sync, the falling edge of PCM\_SYNC indicates the start of the PCM word. PCM\_SYNC is always one clock cycle long.

When configured as the Slave of the PCM interface, BlueCore 5 chip accepts PCM\_CLK rates up to 2048kHz.

Figure 15      Short Frame Sync (Shown with 16-bit Sample)

As with Long Frame Sync, BlueCore 5 chip samples PCM\_IN on the falling edge of PCM\_CLK and transmits PCM\_OUT on the rising edge. PCM\_OUT may be configured to be high impedance on the falling edge of PCM\_CLK in the LSB position or on the rising edge.

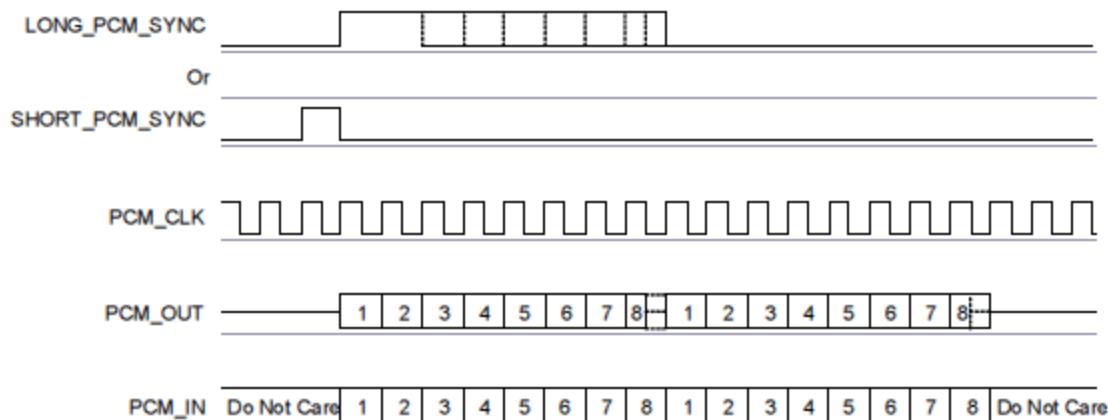

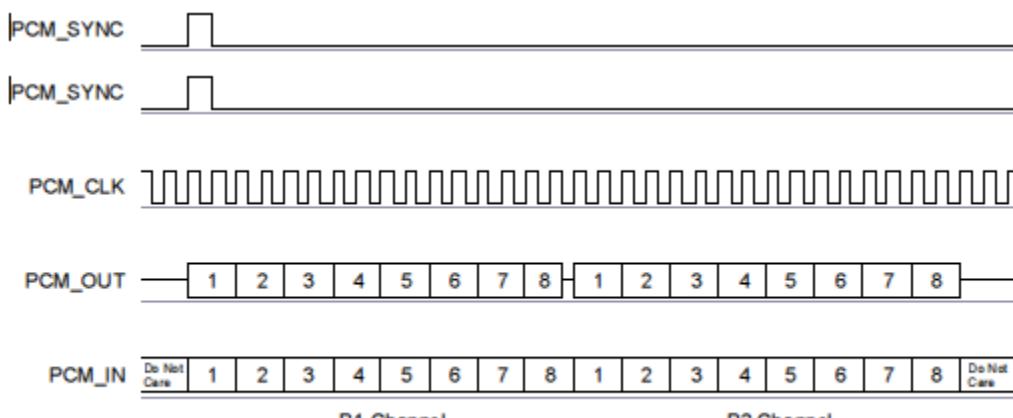

### 5.4.4 Multi-slot Operation

More than one SCO connection over the PCM interface is supported using multiple slots. Up to three SCO connections can be carried over any of the first four slots.

Figure 16      Multi-slot Operation with Two Slots and 8-bit Companded Samples

### 5.4.5 GCI Interface

BlueCore 5 chip is compatible with the GCI, a standard synchronous 2B+D ISDN timing interface. The two 64kbit/s B channels can be accessed when this mode is configured.

Figure 18 GCI Interface

Figure 17 GCI Interface

The start of frame is indicated by the rising edge of PCM\_SYNC and runs at 8kHz. With BlueCore 5 chip in Slave mode, the frequency of PCM\_CLK can be up to 4.096MHz.

### 5.4.6 Slots and Sample Formats

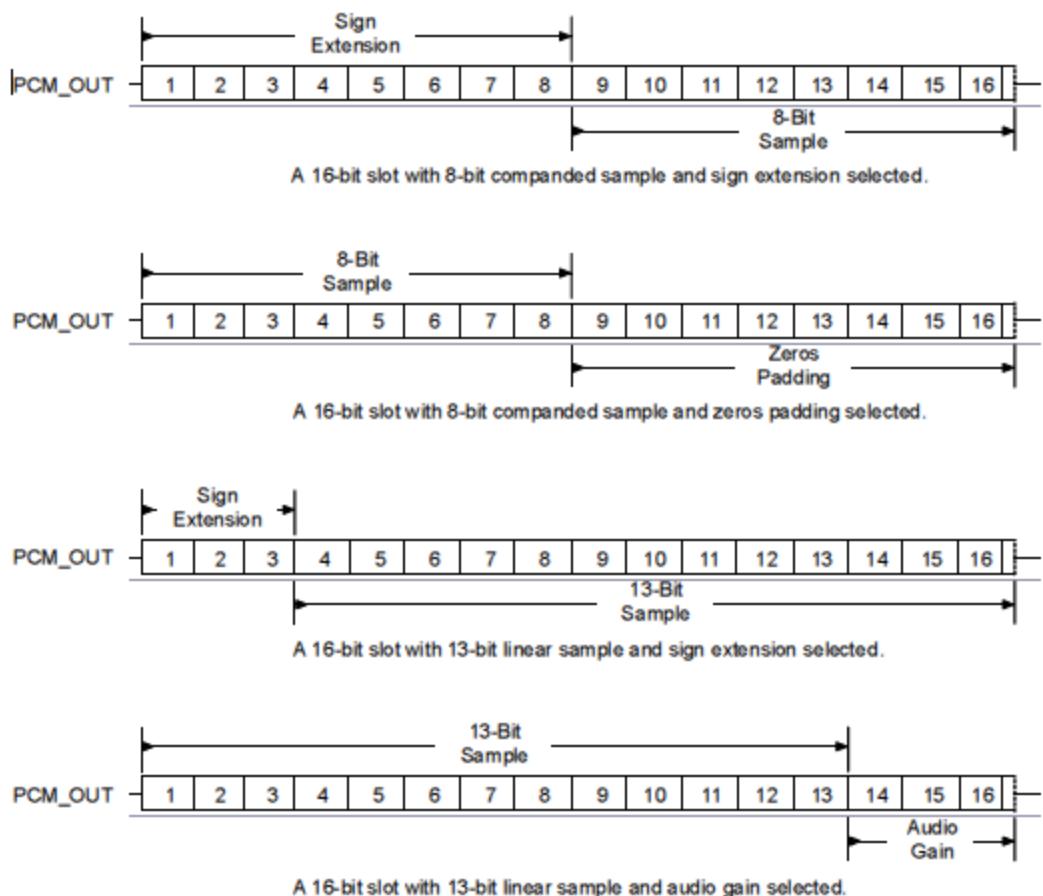

BlueCore 5 chip can receive and transmit on any selection of the first four slots following each sync pulse. Slot durations can be either 8 or 16 clock cycles. Durations of 8 clock cycles may only be used with 8-bit sample formats. Durations of 16 clocks may be used with 8-bit, 13-bit or 16-bit sample formats.

BlueCore 5 chip supports 13-bit linear, 16-bit linear and 8-bit -law or A-law sample formats. The sample rate is 8ksamples/s. The bit order may be little or big endian. When 16-bit slots are used, the 3 or 8 unused bits in each slot may be filled with sign extension, padded with zeros or a programmable 3-bit audio attenuation compatible with some Motorola codecs.

Figure 18 16-bit Slot Length and Sample Format

#### 5.4.7 Additional Features

BlueCore 5 chip has a mute facility that forces **PCM\_OUT** to be 0. In master mode, **PCM\_SYNC** may also be forced to 0 while keeping **PCM\_CLK** running which some codecs use to control power down.

| Symbol            | Parameter                                                          |                                                                                                 | Min | Typ | Max | Unit     |

|-------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|----------|

| $f_{mclk}$        | PCM_CLK frequency                                                  | 4MHz DDS generation. Selection of frequency is programmable. See Table 7.16.                    | -   | 128 | -   | kHz      |

|                   |                                                                    | 48MHz DDS generation. Selection of frequency is programmable. See Table 7.17 and Section 7.8.9. |     | 256 |     |          |

|                   |                                                                    | PCM_SYNC frequency                                                                              |     | 512 |     |          |

| $t_{mclkh}$ (a)   | PCM_CLK high                                                       | 4MHz DDS generation                                                                             | 980 | -   | -   | ns       |

| $t_{mclkl}$ (a)   | PCM_CLK low                                                        | 4MHz DDS generation                                                                             | 730 | -   | -   | ns       |

|                   | PCM_CLK jitter                                                     | 48MHz DDS generation                                                                            | -   | -   | 21  | ns pk-pk |

| $t_{dmclksynch}$  | Delay time from PCM_CLK high to PCM_SYNC high                      |                                                                                                 | -   | -   | 20  | ns       |

| $t_{dmclkpout}$   | Delay time from PCM_CLK high to valid PCM_OUT                      |                                                                                                 | -   | -   | 20  | ns       |

| $t_{dmclklsynd}$  | Delay time from PCM_CLK low to PCM_SYNC low (Long Frame Sync only) |                                                                                                 | -   | -   | 20  | ns       |

| $t_{dmclkhsynd}$  | Delay time from PCM_CLK high to PCM_SYNC low                       |                                                                                                 | -   | -   | 20  | ns       |

| $t_{dmclklpoutz}$ | Delay time from PCM_CLK low to PCM_OUT high impedance              |                                                                                                 | -   | -   | 20  | ns       |

| $t_{dmclkhpoutz}$ | Delay time from PCM_CLK high to PCM_OUT high impedance             |                                                                                                 | -   | -   | 20  | ns       |

| $t_{supinclk}$    | Set-up time for PCM_IN valid to PCM_CLK low                        |                                                                                                 | 30  | -   | -   | ns       |

| $t_{hpinclk}$     | Hold time for PCM_CLK low to PCM_IN invalid                        |                                                                                                 | 10  | -   | -   | ns       |

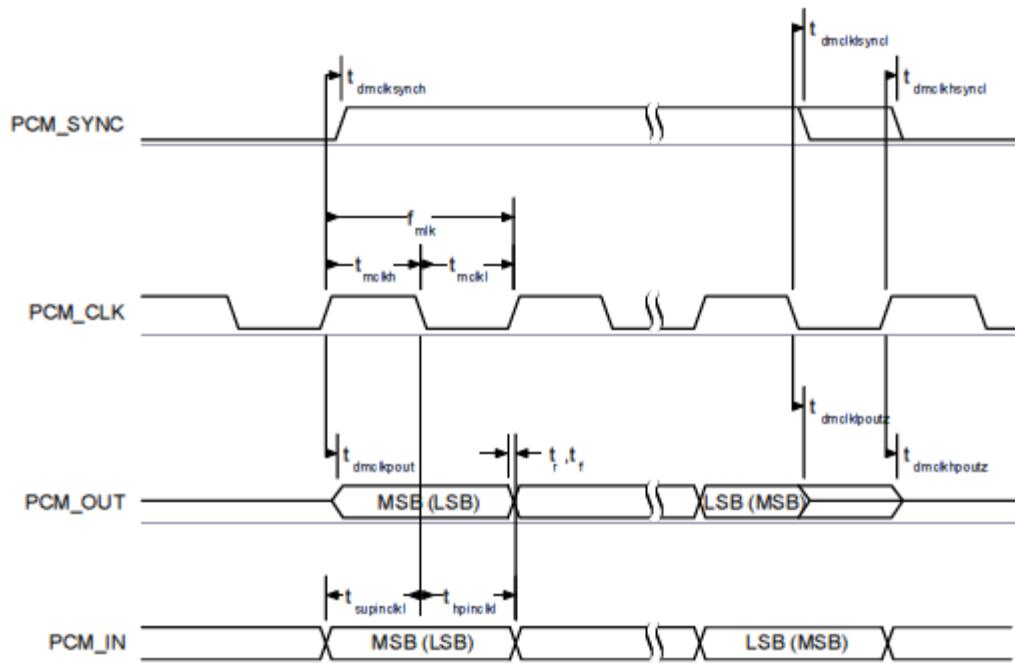

#### 5.4.8 PCM Timing Information

Table 5 PCM Master Timing

(a) Assumes normal system clock operation. Figures will vary during low power modes, when system clock speeds are reduced.

Figure 19      PCM Master Timing Long Frame Sync

Figure 20      PM Master Timing Short Frame Sync

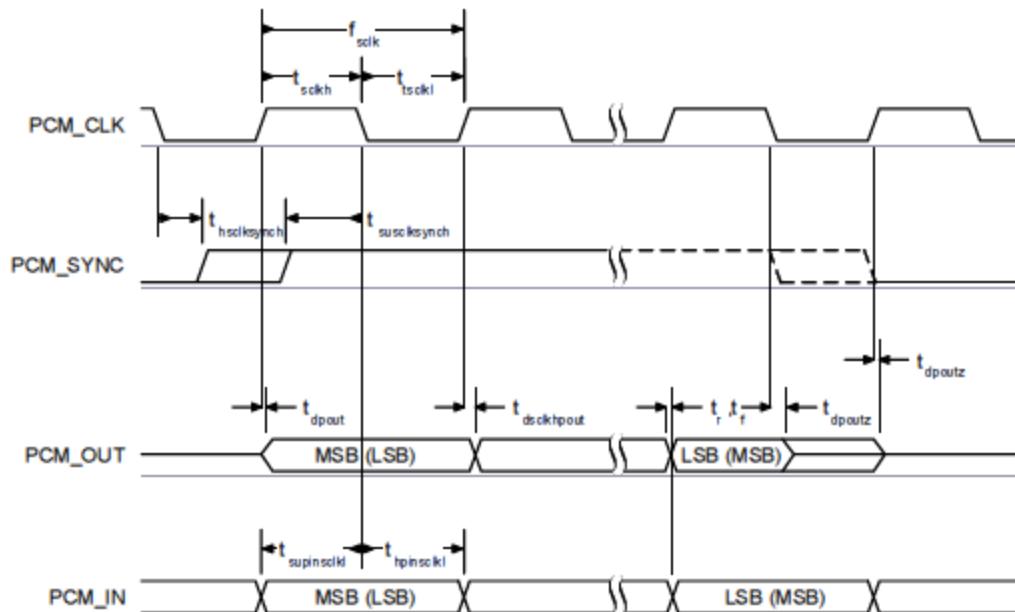

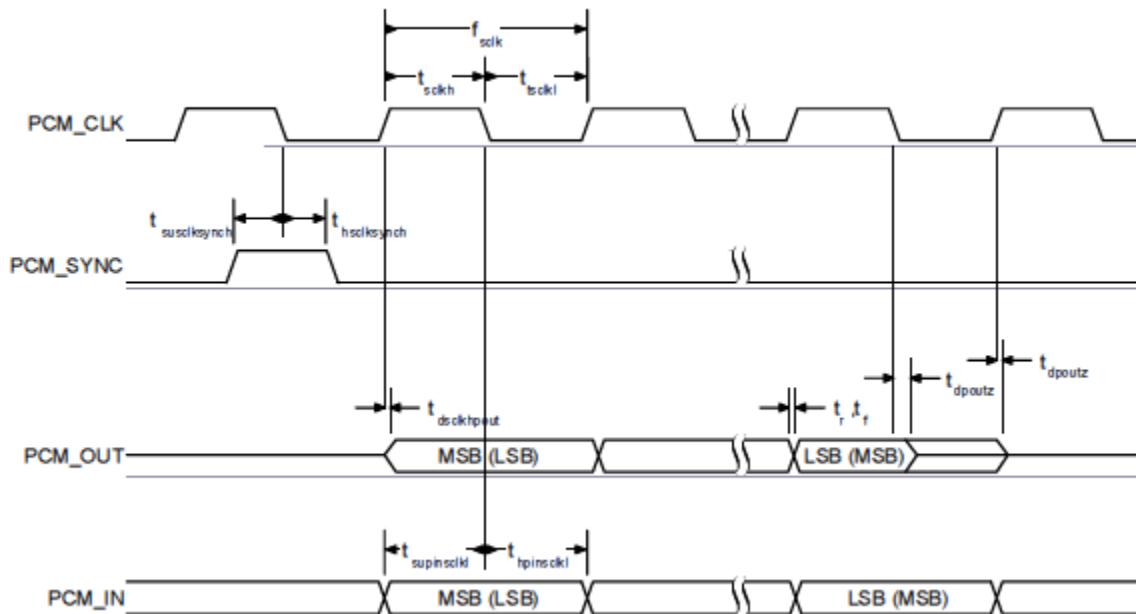

| Symbol           | Parameter                                                                                            | Min | Typ | Max  | Unit |

|------------------|------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| $f_{sclk}$       | PCM clock frequency (Slave mode: input)                                                              | 64  | -   | 2048 | kHz  |

| $f_{sclk}$       | PCM clock frequency (GCI mode)                                                                       | 128 | -   | 4096 | kHz  |

| $t_{sclkI}$      | PCM_CLK low time                                                                                     | 200 | -   | -    | ns   |

| $t_{sclkH}$      | PCM_CLK high time                                                                                    | 200 | -   | -    | ns   |

| $t_{hscksynch}$  | Hold time from PCM_CLK low to PCM_SYNC high                                                          | 30  | -   | -    | ns   |

| $t_{suscksynch}$ | Set-up time for PCM_SYNC high to PCM_CLK low                                                         | 30  | -   | -    | ns   |

| $t_{dpout}$      | Delay time from PCM_SYNC or PCM_CLK whichever is later, to valid PCM_OUT data (Long Frame Sync only) | -   | -   | 20   | ns   |

| $t_{dsckhdpout}$ | Delay time from CLK high to PCM_OUT valid data                                                       | -   | -   | 20   | ns   |

| $t_{dpoutz}$     | Delay time from PCM_SYNC or PCM_CLK low, whichever is later, to PCM_OUT data line high impedance     | -   | -   | 20   | ns   |

| $t_{supinsclkI}$ | Set-up time for PCM_IN valid to CLK low                                                              | 30  | -   | -    | ns   |

| $t_{hpinsclkI}$  | Hold time for PCM_CLK low to PCM_IN invalid                                                          | 30  | -   | -    | ns   |

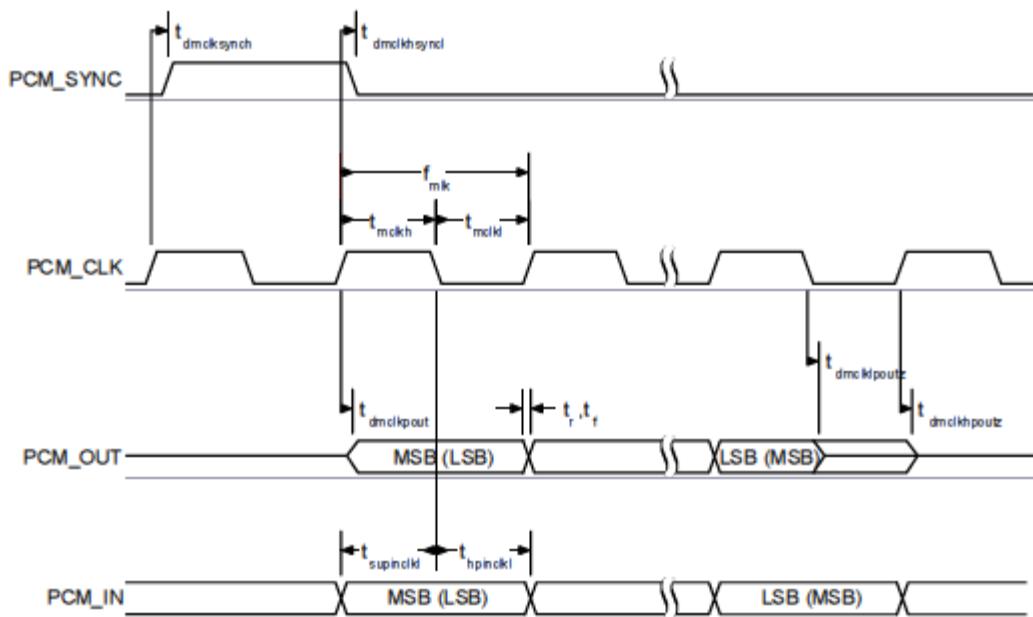

Table 6 PCM Slave Timing

Figure 21 PCM Slave Timing Long Frame Sync

Figure 22 PCM Slave Timing Short Frame Sync

#### 5.4.9 PCM\_CLK and PCM\_SYNC Generation

BlueCore 5 chip has two methods of generating PCM\_CLK and PCM\_SYNC in master mode. The first is generating these signals by DDS from BlueCore 5 chip internal 4MHz clock (which is used in BlueCore2-External). Using this mode limits PCM\_CLK to 128, 256 or 512kHz and PCM\_SYNC to 8kHz. The second is generating PCM\_CLK and PCM\_SYNC by DDS from an internal 48MHz clock (which allows a greater range of frequencies to be generated with low jitter but consumes more power). This second method is selected by setting bit 48M\_PCM\_CLK\_GEN\_EN in PSKEY\_PCM\_CONFIG32. When in this mode and with long frame sync, the length of PCM\_SYNC can be either 8 or 16 cycles of PCM\_CLK, determined by LONG\_LENGTH\_SYNC\_EN in PSKEY\_PCM\_CONFIG32.

This equation describes PCM\_CLK frequency when being generated using the internal 48MHz clock:

$$f = (\text{CNT\_RATE}/\text{CNT\_LIMIT}) \times 24\text{MHz}$$

The frequency of PCM\_SYNC relative to PCM\_CLK can be set using :

$$f = \text{PCM\_CLK}/\text{SYNC\_LIMIT} \times 8$$

CNT\_RATE, CNT\_LIMIT and SYNC\_LIMIT are set using PSKEY\_PCM\_LOW\_JITTER\_CONFIG. As an example, to generate PCM\_CLK at 512kHz with PCM\_SYNC at 8kHz, set PSKEY\_PCM\_LOW\_JITTER\_CONFIG to 0x08080177.

#### 5.4.10 PCM Configuration

The PCM configuration is set using two PS Keys, PSKEY\_PCM\_CONFIG32 detailed in Table 7.16 and PSKEY\_PCM\_LOW\_JITTER\_CONFIG in Table 7.17. The default for PSKEY\_PCM\_CONFIG32 is 0x00800000

, i.e., first slot following sync is active, 13-bit linear voice format, long frame sync and interface master generating 256kHz PCM\_CLK from 4MHz internal clock with no tristate of PCM\_OUT.

| Name           | Bit Position | Description                                                                                                                                                                                                                                                   |

|----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -              | 0            | Set to 0                                                                                                                                                                                                                                                      |

| SLAVE_MODE_EN  | 1            | 0 = master mode with internal generation of PCM_CLK and PCM_SYNC.<br>1 = slave mode requiring externally generated PCM_CLK and PCM_SYNC.                                                                                                                      |

| SHORT_SYNC_EN  | 2            | 0 = long frame sync (rising edge indicates start of frame).<br>1 = short frame sync (falling edge indicates start of frame).                                                                                                                                  |

| -              | 3            | Set to 0.                                                                                                                                                                                                                                                     |

| SIGN_EXTEND_EN | 4            | 0 = padding of 8 or 13-bit voice sample into a 16-bit slot by inserting extra LSBs. When padding is selected with 13-bit voice sample, the 3 padding bits are the audio gain setting; with 8-bit sample the 8 padding bits are zeroes.<br>1 = sign-extension. |

Table 7 PSKEY\_PCM\_CONFIG32 Description

|                            |         |                                                                                                                                                                                                |

|----------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSB_FIRST_EN               | 5       | 0 = MSB first of transmit and receive voice samples.<br>1 = LSB first of transmit and receive voice samples.                                                                                   |

| TX_TRISTATE_EN             | 6       | 0 = drive PCM_OUT continuously.<br>1 = tristate PCM_OUT immediately after falling edge of PCM_CLK in the last bit of an active slot, assuming the next slot is not active.                     |

| TX_TRISTATE_RISING_EDGE_EN | 7       | 0 = tristate PCM_OUT immediately after falling edge of PCM_CLK in last bit of an active slot, assuming the next slot is also not active.<br>1 = tristate PCM_OUT after rising edge of PCM_CLK. |

| SYNC_SUPPRESS_EN           | 8       | 0 = enable PCM_SYNC output when master.<br>1 = suppress PCM_SYNC whilst keeping PCM_CLK running. Some codecs utilise this to enter a low power state.                                          |

| GCI_MODE_EN                | 9       | 1 = enable GCI mode                                                                                                                                                                            |

| MUTE_EN                    | 10      | 1 = force PCM_OUT to 0                                                                                                                                                                         |

| 48M_PCM_CLK_GEN_EN         | 11      | 0 = set PCM_CLK and PCM_SYNC generation via DDS from internal 4MHz clock.<br>1 = set PCM_CLK and PCM_SYNC generation via DDS from internal 48MHz clock.                                        |

| LONG_LENGTH_SYNC_EN        | 12      | 0 = set PCM_SYNC length to 8 PCM_CLK cycles.<br>1 = set length to 16 PCM_CLK cycles.<br>Only applies for long frame sync and with 48M_PCM_CLK_GEN_EN set to 1.                                 |

| -                          | [20:16] | Set to 0b00000                                                                                                                                                                                 |

| MASTER_CLK_RATE            | [22:21] | Selects 128 (0b01), 256 (0b00), 512 (0b10) kHz<br>PCM_CLK frequency when master and 48M_PCM_CLK_GEN_EN (bit 11) is low.                                                                        |

| ACTIVE_SLOT                | [26:23] | Default is 0001. Ignored by firmware.                                                                                                                                                          |

| SAMPLE_FORMAT              | [28:27] | Selects between 13 (0b00), 16 (0b01), 8 (0b10) bit sample with 16 cycle slot duration or 8 (0b11) bit sample with 8 cycle slot duration.                                                       |

| Name       | Bit Position | Description                                |

|------------|--------------|--------------------------------------------|

| CNT_LIMIT  | [12:0]       | Sets PCM_CLK counter limit                 |

| CNT_RATE   | [23:16]      | Sets PCM_CLK count rate                    |

| SYNC_LIMIT | [31:24]      | Sets PCM_SYNC division relative to PCM_CLK |

Table 8 PSKEY\_PCM\_LOW\_JITTER\_CONFIG Description

## 5.5 I/O Parallel Ports

Fifteen lines of programmable bidirectional input/outputs (I/O) are provided. PIO[11:8] and PIO[3:0] are powered from VDD\_PIO. PIO[7:4] are powered from VDD\_PADS. AIO [2:0] are powered from VDD\_MEM.

PIO lines can be configured through software to have either weak or strong pull-ups or pull-downs. All PIO lines are configured as inputs with weak pull-downs at reset.

PIO[0] and PIO[1] are normally dedicated to RXEN and TXEN respectively, but they are available for general use. Any of the PIO lines can be configured as interrupt request lines or as wake-up lines from sleep modes. PIO[6] or PIO[2] can be configured as a request line for an external clock source. This is useful when the clock to BlueCore 5-External is provided from a system ASIC. Using PSKEY\_CLOCK\_REQUEST\_ENABLE (0x246), this terminal can be configured to be low when BlueCore 5 chip is in Deep Sleep and high when a clock is required. The clock must be supplied within 4ms of the rising edge of PIO[6] or PIO[2] to avoid losing timing accuracy in certain Bluetooth operating modes.

BlueCore 5 chip has three general purpose analog interface pins, AIO[0], AIO[1] and AIO[2]. These are used to access internal circuitry and control signals. One pin is allocated to decoupling for the on-chip band gap reference voltage, the other two may be configured to provide additional functionality.

Auxiliary functions available via these pins include an 8-bit ADC and an 8-bit DAC. Typically the ADC is used for battery voltage measurement. Signals selectable at these pins include the band gap reference voltage and a variety of clock signals: 48, 24, 16, 8MHz and the XTAL clock frequency. When used with analog signals, the voltage range is constrained by the analog supply voltage (1.8V). When configured to drive out digital level signals (e.g., clocks), the output voltage level is determined by VDD\_MEM (1.8V).

### 5.5.1 PIO Defaults

CSR, maker of the BlueCore 5 chip, cannot guarantee that these terminal functions remain the same. Refer to the software release note for the implementation of these PIO lines, as they are firmware build-specific.

## 5.6 I2C Interface

PIO[8:6] can be used to form a master I2C interface. The interface is formed using software to drive these lines. Therefore, it is suited only to relatively slow functions such as driving a dot matrix LCD, keyboard scanner or EEPROM.

Any three PIOs can be used as a master I2C interface by configuring the hardware bit serializer with suitable firmware. The strong pull-ups in the PIO pads eliminate the need for external pull-up resistors.

Note:

PIO lines need to be pulled-up through 2.2k resistors.

PIO[7:6] dual functions, UART bypass and EEPROM support, therefore, devices using an EEPROM cannot support UART bypass mode.

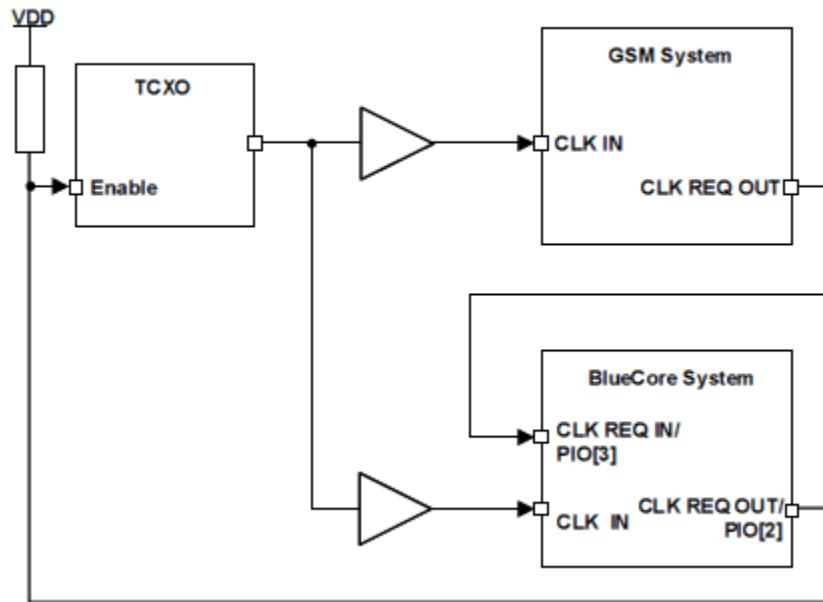

## 5.7 TCXO Enable OR Function

An OR function exists for clock enable signals from a host controller and BlueCore 5 chip where either device can turn on the clock without having to wake up the other device. PIO[3] can be used as the host clock enables input and PIO[2] can be used as the OR output with the TCXO enable signal from BlueCore 5 chip.

Figure 23      Example of OR Function

On reset and up to the time the PIO has been configured, PIO[2] will be tristate. Ensure that the circuitry connected to this pin is pulled via a 470k resistor to the appropriate power rail. This ensures that the TCXO is oscillating at start up.

## 5.8 Reset

BlueCore 5 chip may be reset from several sources: RESETB pin, power on reset, a UART break character or via a software configured watchdog timer.

The RESETB pin is an active low reset and is internally filtered using the internal low frequency clock oscillator. A reset will be performed between 1.5 and 4.0ms following RESETB being active. It is recommended that RESETB be applied for a period greater than 5ms.

The power on reset occurs when the VDD\_CORE supply falls below typically 1.26V and is released when VDD\_CORE rises above typically 1.31V. At reset the digital I/O pins are set to inputs for bidirectional pins and outputs are tristate. The PIOs have weak pull-downs. Following a reset, BlueCore 5 chip assumes the maximum XTAL\_IN frequency, which ensures that the internal clocks run at a safe (low) frequency until BlueCore 5 chip is configured for the actual XTAL\_IN frequency. If no clock is present at XTAL\_IN, the oscillator in BlueCore 5 chip free runs, again at a safe frequency.

## 5.8.1 Pin States on Reset

| Pin Name / Group      | I/O Type                              | No Core Voltage Reset | Full Chip Reset |

|-----------------------|---------------------------------------|-----------------------|-----------------|

| USB_DP                | Digital bi-directional                | N/a                   | N/a             |

| USB_DN                | Digital bi-directional                | N/a                   | N/a             |

| UART_RX               | Digital input with PD                 | PD                    | PD              |

| UART_CTS              | Digital input with PD                 | PD                    | PD              |

| UART_TX               | Digital bi-directional with PU        | PU                    | PU              |

| UART_RTS              | Digital bi-directional with PU        | PU                    | PU              |

| SPI_MOSI              | Digital input with PD                 | PD                    | PD              |

| SPI_CLK               | Digital input with PD                 | PD                    | PD              |

| SPI_CS#               | Digital input with PU                 | PU                    | PU              |

| SPI_MISO              | Digital tri-state output with PD      | PD                    | PD              |

| PCM_IN                | Digital input with PD                 | PD                    | PD              |

| PCM_CLK               | Digital bi-directional with PD        | PD                    | PD              |

| PCM_SYNC              | Digital bi-directional with PD        | PD                    | PD              |

| PCM_OUT               | Digital tri-state output with PD      | PD                    | PD              |

| RST#                  | Digital input with PU                 | PU                    | PU              |

| TEST_EN               | Digital input with PD                 | PD                    | PD              |

| PIO[15:4]<br>PIO[3:0] | Digital bi-directional with PU/<br>PD | PD                    | PD              |

Table 9 Pin States on Reset

### 5.8.2 Status after Reset

The chip status after a reset is as follows:

- Warm Reset: Data rate and RAM data remain available

- Cold Reset: Data rate and RAM data not available

## 5.9 Power Supply

### 5.9.1 Switch-mode Regulator

The on-chip switch-mode 1.8V regulator, may be used to power a 1.8V rail which can drive the chip I/O supplies, and the input to the low-voltage regulators. An external filter circuit of a low-resistance  $22\mu\text{H}$  series inductor with an effective series resistance in the range  $0.4\text{--}0.8\Omega$ , followed by a low ESR  $4.7\mu\text{F}$  shunt capacitor is required between the LX terminal and the 1.8V supply rail, which should also be connected to the pin VDD\_SMP\_CORE. A decoupling capacitor of at least  $2.2\mu\text{F}$  is required between BAT\_P and BAT\_N. It is essential that the series resistance of tracks between the BAT\_P and BAT\_N terminals, the filter and decoupling components, and the external voltage source are minimised to maintain high-efficiency power conversion, and low supply ripple.

The regulator may be enabled by the VREGENABLE\_H pin, by the device firmware, or by the internal battery charger. The regulator is switched into a low-power pulse skipping mode when the device is sent into deep-sleep mode, or in reset.

When this regulator is not used the terminals BAT\_P and LX must be grounded or left unconnected.

### 5.9.2 Low-voltage Linear Regulator