# RM502Q-GL Hardware Design

#### **5G Module Series**

Rev. RM502Q-GL\_Hardware\_Design\_V1.0

Date: 2020-07-06

Status: Preliminary

Our aim is to provide customers with timely and comprehensive services. For any assistance, please contact our company headquarters:

#### **Quectel Wireless Solutions Co., Ltd.**

Building 5, Shanghai Business Park Phase III (Area B), No.1016 Tianlin Road, Minhang District, Shanghai 200233, China

Email: info@quectel.com

#### Or our local office. For more information, please visit:

http://www.quectel.com/support/sales.htm

#### For technical support, or to report documentation errors, please visit:

http://www.quectel.com/support/technical.htm

Or email to: support@quectel.com

#### **GENERAL NOTES**

QUECTEL OFFERS THE INFORMATION AS A SERVICE TO ITS CUSTOMERS. THE INFORMATION PROVIDED IS BASED UPON CUSTOMERS' REQUIREMENTS. QUECTEL MAKES EVERY EFFORT TO ENSURE THE QUALITY OF THE INFORMATION IT MAKES AVAILABLE. QUECTEL DOES NOT MAKE ANY WARRANTY AS TO THE INFORMATION CONTAINED HEREIN, AND DOES NOT ACCEPT ANY LIABILITY FOR ANY INJURY, LOSS OR DAMAGE OF ANY KIND INCURRED BY USE OF OR RELIANCE UPON THE INFORMATION. ALL INFORMATION SUPPLIED HEREIN IS SUBJECT TO CHANGE WITHOUT PRIOR NOTICE.

#### **COPYRIGHT**

THE INFORMATION CONTAINED HERE IS PROPRIETARY TECHNICAL INFORMATION OF QUECTEL WIRELESS SOLUTIONS CO., LTD. TRANSMITTING, REPRODUCTION, DISSEMINATION AND EDITING OF THIS DOCUMENT AS WELL AS UTILIZATION OF THE CONTENT WITHOUT PERMISSION ARE FORBIDDEN. OFFENDERS WILL BE HELD LIABLE FOR PAYMENT OF DAMAGES. ALL RIGHTS ARE RESERVED IN THE EVENT OF A PATENT GRANT OR REGISTRATION OF A UTILITY MODEL OR DESIGN.

Copyright © Quectel Wireless Solutions Co., Ltd. 2020. All rights reserved.

## **About the Document**

## **Revision History**

| Version | Date Author |                             | Description |  |

|---------|-------------|-----------------------------|-------------|--|

| 1.0     | 2020-07-06  | Kingson ZHANG/<br>Qiqi WANG | Initial     |  |

## **Contents**

| Ab  | out the Document                                          | 2  |

|-----|-----------------------------------------------------------|----|

| Со  | ontents                                                   | 3  |

| Та  | ble Index                                                 | 5  |

| Fig | gure Index                                                | 6  |

| 1   | Introduction                                              | 8  |

|     | 1.1. Safety Information                                   | 9  |

| 2   | Product Concept                                           | 10 |

| _   | 2.1. General Description                                  |    |

|     | 2.2. Key Features                                         |    |

|     | 2.3. Functional Diagram                                   |    |

|     | 2.4. Evaluation Board                                     | 14 |

| 3   | Application Interfaces                                    | 15 |

|     | 3.1. Pin Assignment                                       |    |

|     | 3.2. Pin Description                                      | 17 |

|     | 3.3. Power Supply                                         | 21 |

|     | 3.3.1. Decrease Voltage Drop                              | 21 |

|     | 3.3.2. Reference Design for Power Supply                  | 22 |

|     | 3.4. Turn on and off Scenarios                            | 23 |

|     | 3.4.1. Turn on the Module                                 | 23 |

|     | 3.4.1.1. Turn on the Module with a Host GPIO              | 24 |

|     | 3.4.1.2. Turn on the Module Automatically                 | 24 |

|     | 3.4.1.3. Turn on the Module with Compatible Design        | 25 |

|     | 3.4.2. Turn off the Module                                | 26 |

|     | 3.4.2.1. Turn off the Module through FULL_CARD_POWER_OFF# | 26 |

|     | 3.4.2.2. Turn off the Module through AT Command           | 26 |

|     | 3.5. Reset                                                |    |

|     | 3.6. (U)SIM Interfaces                                    | 30 |

|     | 3.7. USB Interface                                        | 32 |

|     | 3.8. PCIe Interface                                       |    |

|     | 3.8.1. Endpoint Mode                                      |    |

|     | 3.8.2. USB Version and PCIe Version                       |    |

|     | 3.9. PCM Interface*                                       |    |

|     | 3.10. Control and Indication Interfaces                   |    |

|     | 3.10.1. W_DISABLE1#*                                      |    |

|     | 3.10.2. W_DISABLE2#*                                      |    |

|     | 3.10.3. WWAN_LED#*                                        |    |

|     | 3.10.4. WAKE_ON_WAN#*                                     |    |

|     | 3.10.5. DPR*                                              |    |

|     | 3.10.6. STATUS*                                           |    |

|     | 3.11. Cellular/WLAN Interface*                            | 45 |

|   | 3.12. Antenna Tui                   | ner Control Interface*                         | 45 |  |

|---|-------------------------------------|------------------------------------------------|----|--|

|   | 3.13. Configuration                 | on Pins                                        | 46 |  |

| 4 | GNSS Receiver                       |                                                | 47 |  |

|   | 4.1. General Des                    | scription                                      | 47 |  |

|   | 4.2. GNSS Perfo                     | ormance                                        | 48 |  |

| 5 | Antenna Connect                     | ion                                            | 49 |  |

|   | 5.1. RF Antenna                     | 49                                             |    |  |

|   | 5.1.1. Anter                        | nna Pin Definition                             | 49 |  |

|   | 5.1.2. RF A                         | ntenna Port Mapping                            | 50 |  |

|   | 5.1.3. Opera                        | ating Frequency                                | 50 |  |

|   | 5.1.4. Refer                        | rence Design of RF Antenna Interface           | 52 |  |

|   | 5.2. GNSS Anter                     | nna Interface                                  | 52 |  |

|   |                                     | Design of RF Layout                            |    |  |

|   | 5.4. Antenna Co                     | nnectors                                       | 55 |  |

|   | 5.4.1 RF Band                       | ds Supported by Antenna Connectors             | 56 |  |

|   | 5.5. Antenna Ins                    | stallation                                     | 57 |  |

|   | 5.5.1. Anter                        | nna Requirements                               | 57 |  |

|   | 5.5.2. Reco                         | ommended RF Connector for Antenna Installation | 57 |  |

| 6 |                                     | ility and Radio Characteristics                |    |  |

|   |                                     | aximum Ratings                                 |    |  |

|   |                                     | oly Requirements                               |    |  |

|   | ·                                   | ments                                          |    |  |

|   | 6.4. Operation a                    | nd Storage Temperatures                        | 61 |  |

|   |                                     | nsumption                                      |    |  |

|   | •                                   | Power                                          |    |  |

|   | 6.7. RF Receivin                    | ng Sensitivity                                 | 67 |  |

|   |                                     | cteristics                                     |    |  |

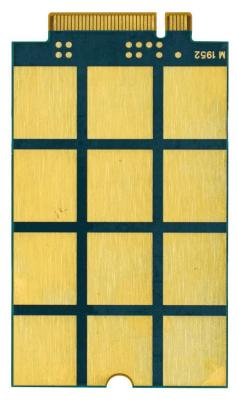

|   | 6.9. Thermal Dis                    | ssipation                                      | 70 |  |

| 7 | Mechanical Dimensions and Packaging |                                                |    |  |

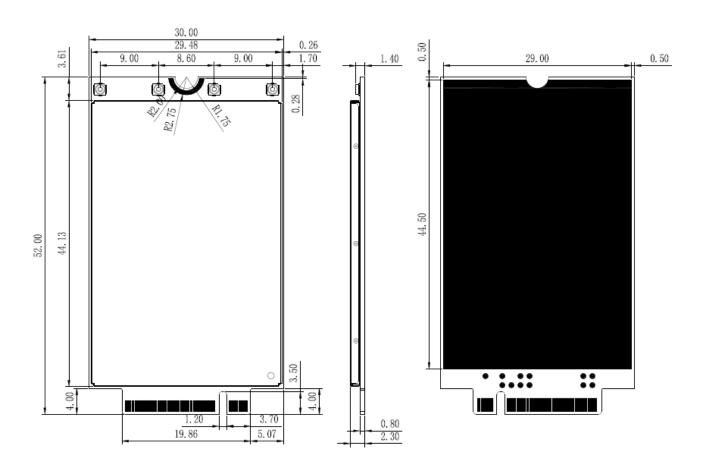

|   |                                     | Dimensions of the Module                       |    |  |

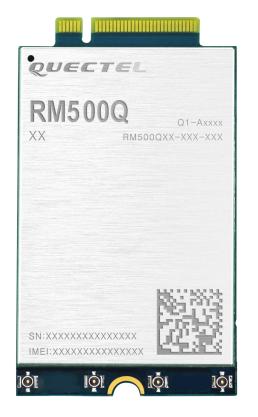

|   | •                                   | ttom Views of the Module                       |    |  |

|   |                                     | ctor                                           |    |  |

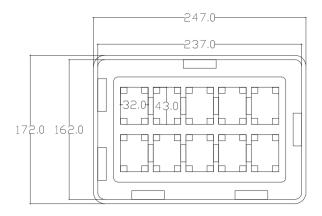

|   | 7.4. Packaging                      |                                                | 75 |  |

| 8 | Appendix Referer                    | nces                                           | 76 |  |

## **Table Index**

| Table 1: Frequency Bands and GNSS Type of RM502Q-GL Module                           | 10 |

|--------------------------------------------------------------------------------------|----|

| Table 2: Key Features of RM502Q-GL                                                   | 11 |

| Table 3: Definition of I/O Parameters                                                | 17 |

| Table 4: Pin Description                                                             | 17 |

| Table 5: Definition of VCC and GND Pins                                              | 21 |

| Table 6: Definition of FULL_CARD_POWER_OFF# Pin                                      | 23 |

| Table 7: Definition of RESET_N Pin                                                   | 28 |

| Table 8: Pin Definition of (U)SIM Interfaces                                         | 30 |

| Table 9: Pin Definition of USB Interface                                             | 33 |

| Table 10: Pin Definition of PCIe Interface                                           | 35 |

| Table 11: Pin Definition of PCM Interface*                                           | 40 |

| Table 12: Pin Definition of Control and Indication Interfaces                        | 40 |

| Table 13: RF Function Status                                                         | 41 |

| Table 14: GNSS Function Status                                                       | 42 |

| Table 15: Network Status Indications of WWAN_LED# Signal                             | 43 |

| Table 16: State of the WAKE_ON_WAN# Signal                                           | 43 |

| Table 17: Function of the DPR Signal                                                 | 44 |

| Table 18: Pin Definition of COEX Interface                                           | 45 |

| Table 20: Pin Definition of Antenna Tuner Control Interface                          | 45 |

| Table 21: Definition of Configuration Pins                                           | 46 |

| Table 22: Configuration Pins List of M.2 Specification                               |    |

| Table 23: GNSS Performance                                                           | 48 |

| Table 24: Pin Definition of RF Antenna Interfaces                                    | 49 |

| Table 25: RM502Q-GL RF Antenna Mapping                                               | 50 |

| Table 26: RM502Q-GL Module Operating Frequencies                                     | 50 |

| Table 27: GNSS Frequency                                                             | 53 |

| Table 28: RF Bands Supported by RM502Q-GL Antenna Connectors                         | 56 |

| Table 29: Antenna Requirements                                                       | 57 |

| Table 30: Major Specifications of the RF Connector                                   | 58 |

| Table 31: Absolute Maximum Ratings                                                   | 60 |

| Table 32: Power Supply Requirements                                                  | 60 |

| Table 33: I/O Requirements                                                           | 61 |

| Table 34: Operation and Storage Temperatures                                         | 61 |

| Table 35: RM502Q-GL Current Consumption                                              | 62 |

| Table 36: RF Output Power                                                            |    |

| Table 37: RM502Q-GL Conducted RF Receiving Sensitivity                               | 68 |

| Table 38: Electrostatic Discharge Characteristics (Temperature: 25°C, Humidity: 40%) | 70 |

| Table 39: Related Documents                                                          | 76 |

| Table 40: Terms and Abbreviations                                                    | 76 |

## Figure Index

| Figure 1: Functional Diagram                                                            | 13 |

|-----------------------------------------------------------------------------------------|----|

| Figure 2: Pin Assignment                                                                | 16 |

| Figure 3: Power Supply Limits during Radio Transmission                                 | 22 |

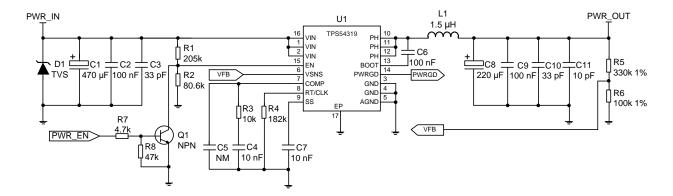

| Figure 4: Reference Circuit of VCC Pins                                                 | 22 |

| Figure 5: Reference Design of Power Supply                                              | 23 |

| Figure 6: Turn on the Module with a Host GPIO                                           | 24 |

| Figure 7: Turn on the Module Automatically                                              | 24 |

| Figure 8: Turn on the Module with Compatible Design                                     | 25 |

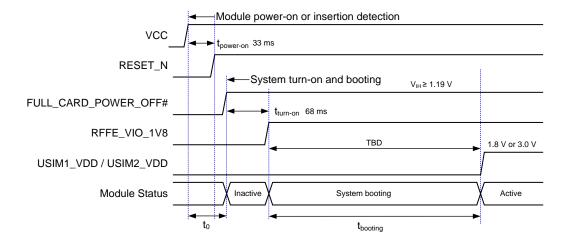

| Figure 9: Turn-on Timing of the Module                                                  |    |

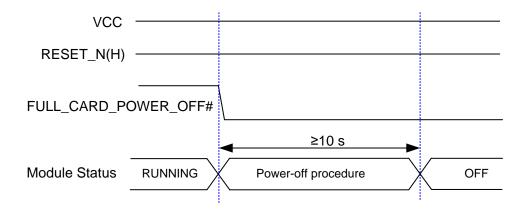

| Figure 10: Turn-off Timing through FULL_CARD_POWER_OFF#                                 | 26 |

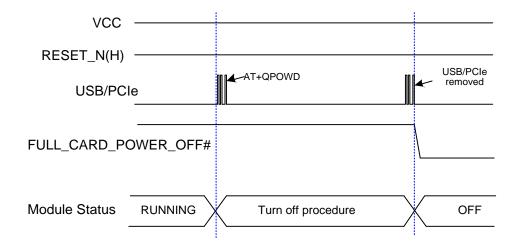

| Figure 11: Turn-off Timing through AT Command and FULL_CARD_POWER_OFF#                  | 27 |

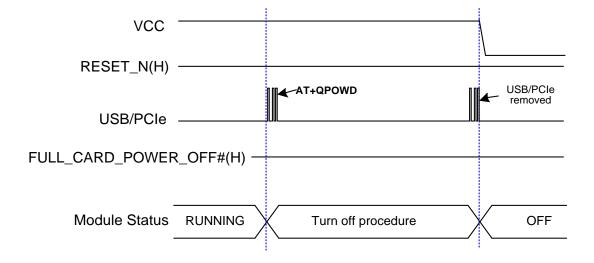

| Figure 12: Turn-off Timing through AT Command and Power Supply                          | 27 |

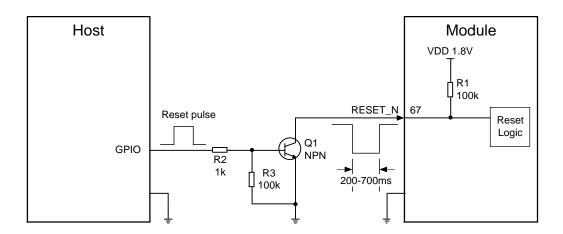

| Figure 13: Reference Circuit of RESET_N with NPN Driving Circuit                        | 28 |

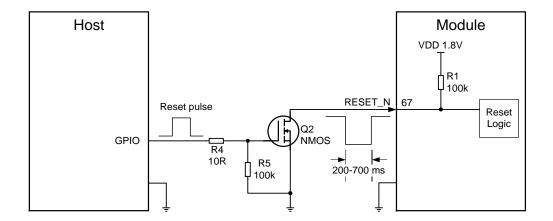

| Figure 14: Reference Circuit of RESET_N with NMOS Driving Circuit                       | 29 |

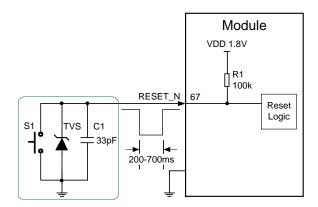

| Figure 15: Reference Circuit of RESET_N with Button                                     | 29 |

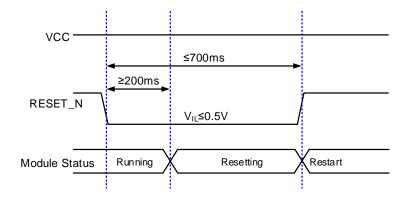

| Figure 16: Resetting Timing of the Module                                               | 29 |

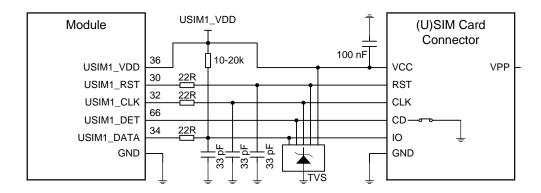

| Figure 17: Reference Circuit of Normally Closed (U)SIM Card Connector                   | 31 |

| Figure 18: Reference Circuit of Normally Open (U)SIM Card Connector                     | 31 |

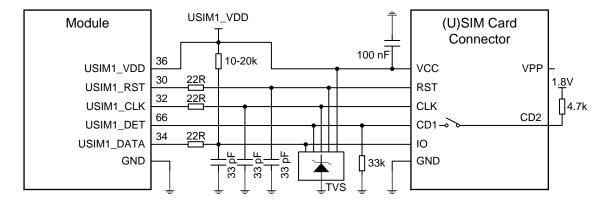

| Figure 19: Reference Circuit of a 6-Pin (U)SIM Card Connector                           | 32 |

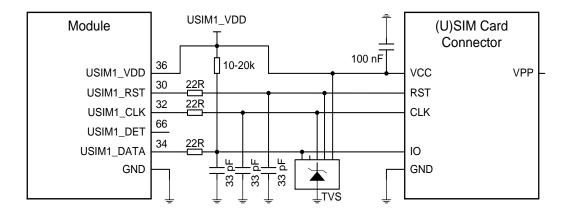

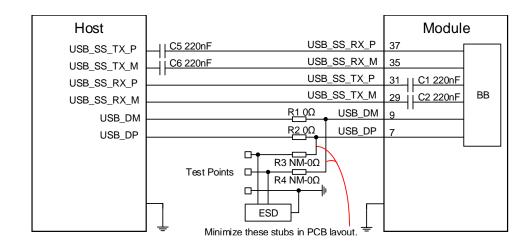

| Figure 20: Reference Circuit of USB 3.1 & 2.0 Interface                                 | 33 |

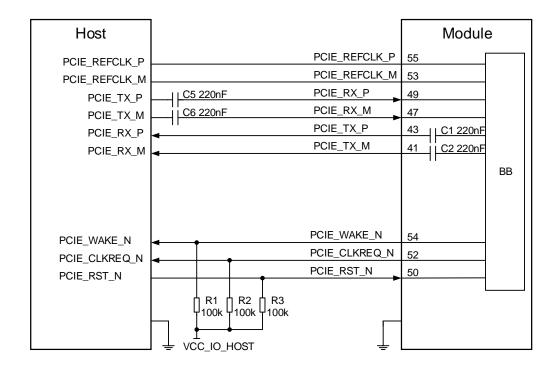

| Figure 21: PCIe Interface Reference Circuit (EP Mode)                                   | 36 |

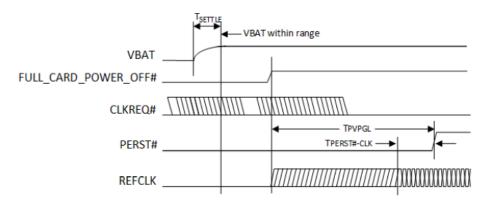

| Figure 22: PCIe Power-on Timing Requirements of M.2 Specification                       | 36 |

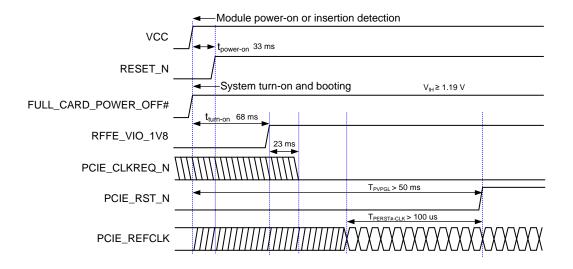

| Figure 23: PCIe Power-on Timing Requirements of the Module                              | 37 |

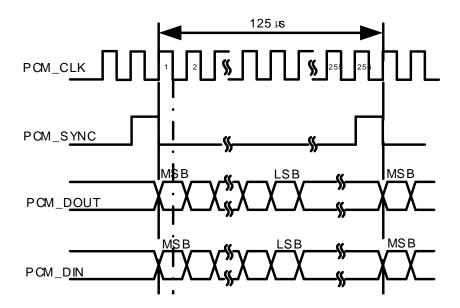

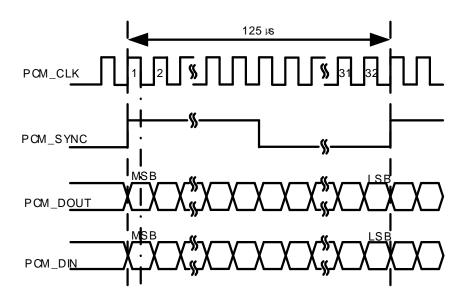

| Figure 24: Primary Mode Timing                                                          | 39 |

| Figure 25: Auxiliary Mode Timing                                                        | 39 |

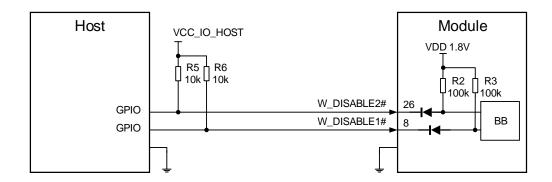

| Figure 26: W_DISABLE1# and W_DISABLE2# Reference Circuit                                | 42 |

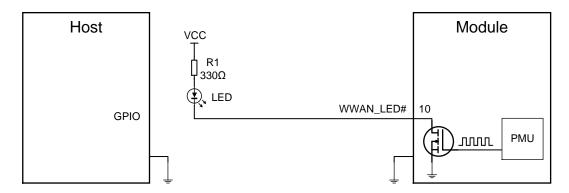

| Figure 27: WWAN_LED# Reference Circuit                                                  | 43 |

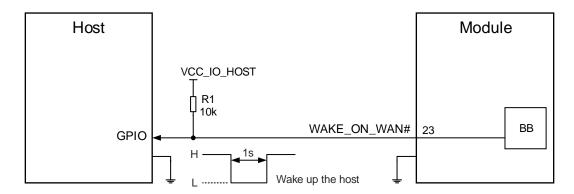

| Figure 28: WAKE_ON_WAN# Signal Reference Circuit                                        | 44 |

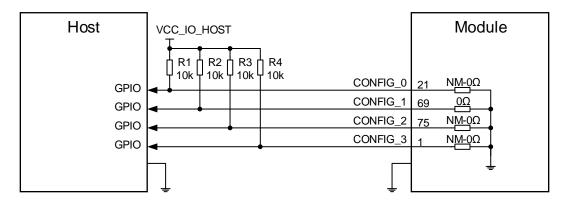

| Figure 29: Recommended Circuit of Configuration Pins                                    | 46 |

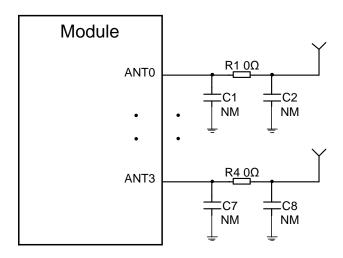

| Figure 30: Reference Circuit of RF Antenna                                              | 52 |

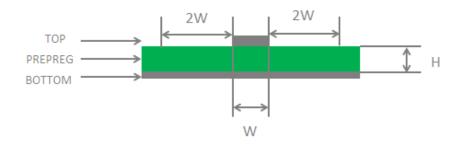

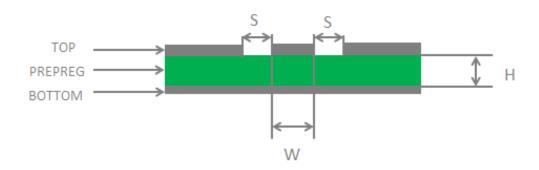

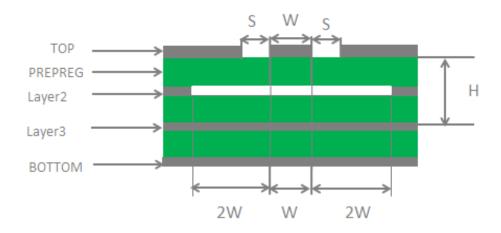

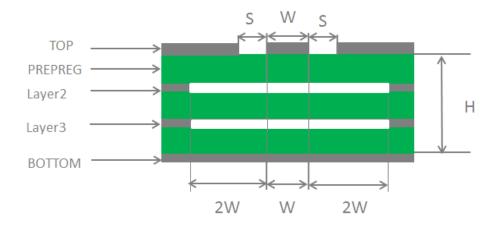

| Figure 31: Microstrip Design on a 2-layer PCB                                           | 54 |

| Figure 32: Coplanar Waveguide Design on a 2-layer PCB                                   | 54 |

| Figure 33: Coplanar Waveguide Design on a 4-layer PCB (Layer 3 as Reference Ground)     | 54 |

| Figure 34: Coplanar Waveguide Design on a 4-layer PCB (Layer 4 as Reference Ground)     | 55 |

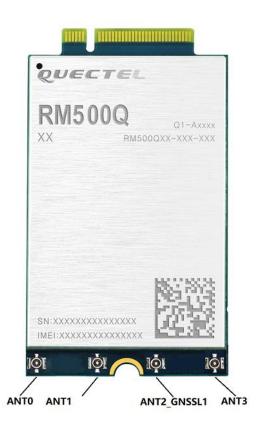

| Figure 35: Antenna Connectors on the Module                                             |    |

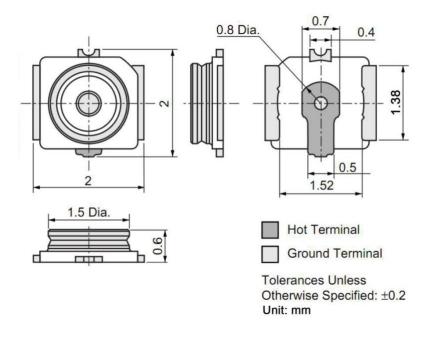

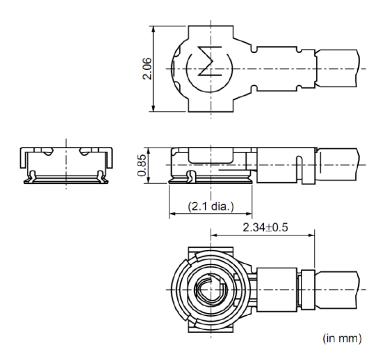

| Figure 36: RM502Q-GL RF Connector Dimensions (Unit: mm)                                 | 58 |

| Figure 37: Specifications of Mating Plugs Using Ø0.81 mm Coaxial Cables                 | 58 |

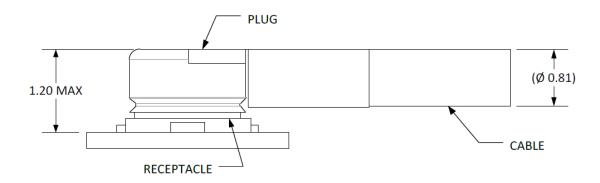

| Figure 38: Connection between RF Connector and Mating Plug Using Ø0.81 mm Coaxial Cable | 59 |

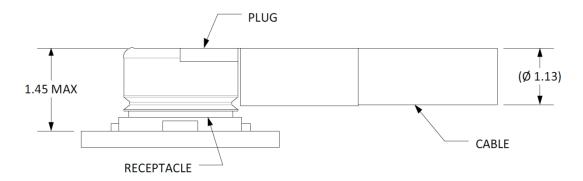

| Figure 39: Connection between RF Connector and Mating Plug Using Ø1.13 mm Coaxial Cable | 59 |

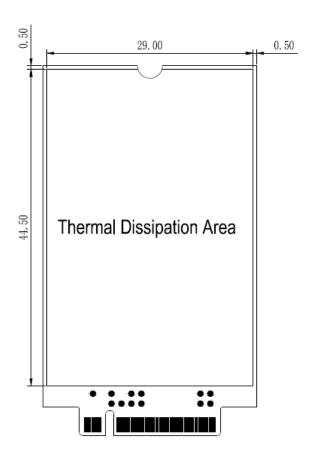

| Figure 40: Thermal Dissipation Area on Bottom Side of Module (Bottom View)              | 71 |

| Figure 41: Mechanical Dimensions of RM502Q-GL (Unit: mm)                                | 73 |

| Figure 42: Top and Bottom Views of the Module | 74 |

|-----------------------------------------------|----|

| Figure 43: Tray Size (Unit: mm)               | 75 |

| Figure 44: Tray Packaging Procedure           | 75 |

## 1 Introduction

This document defines RM502Q-GL module and describes its air interface and hardware interfaces which are connected with customers' applications.

This document helps customers quickly understand the interface specifications, electrical and mechanical details, as well as other related information of RM502Q-GL module. To facilitate its application in different fields, reference design is also provided for reference. Associated with application notes and user guides, customers can use the module to design and set up mobile applications easily.

### 1.1. Safety Information

The following safety precautions must be observed during all phases of operation, such as usage, service or repair of any cellular terminal or mobile incorporating RM502Q-GL module. Manufacturers of the cellular terminal should notify users and operating personnel of the following safety information by incorporating these guidelines into all manuals of the product. Otherwise, Quectel assumes no liability for customers' failure to comply with these precautions.

Full attention must be given to driving at all times in order to reduce the risk of an accident. Using a mobile while driving (even with a handsfree kit) causes distraction and can lead to an accident. Please comply with laws and regulations restricting the use of wireless devices while driving.

Switch off the cellular terminal or mobile before boarding an aircraft. The operation of wireless appliances in an aircraft is forbidden to prevent interference with communication systems. If the device offers an Airplane Mode, then it should be enabled prior to boarding an aircraft. Please consult the airline staff for more restrictions on the use of wireless devices on boarding the aircraft.

Wireless devices may cause interference on sensitive medical equipment, so please be aware of the restrictions on the use of wireless devices when in hospitals, clinics or other healthcare facilities.

Cellular terminals or mobiles operating over radio signals and cellular network cannot be guaranteed to connect in all possible conditions (for example, with unpaid bills or with an invalid (U)SIM card). When emergent help is needed in such conditions, please remember using emergency call. In order to make or receive a call, the cellular terminal or mobile must be switched on in a service area with adequate cellular signal strength.

The cellular terminal or mobile contains a transmitter and receiver. When it is ON, it receives and transmits radio frequency signals. RF interference can occur if it is used close to TV set, radio, computer or other electric equipment.

In locations with potentially explosive atmospheres, obey all posted signs to turn off wireless devices such as your phone or other cellular terminals. Areas with potentially explosive atmospheres include fueling areas, below decks on boats, fuel or chemical transfer or storage facilities, areas where the air contains chemicals or particles such as grain, dust or metal powders, etc.

## **2** Product Concept

## 2.1. General Description

RM502Q-GL is a 5G NR/LTE-A/UMTS/HSPA+ wireless communication module with receive diversity. It provides data connectivity on 5G NR SA and NSA, LTE-FDD, LTE-TDD, DC-HSDPA, HSPA+, HSDPA, HSUPA and WCDMA networks with standard PCI Express M.2 interface.

It supports embedded operating systems such as Windows, Linux and Android, and also provides GNSS and voice functionality to meet specific application demands.

The following table shows the frequency bands and GNSS type of RM502Q-GL module.

Table 1: Frequency Bands and GNSS Type of RM502Q-GL Module

| Mode    | RM502Q-GL                                                                           |

|---------|-------------------------------------------------------------------------------------|

| 5G NR   | n1/n2/n3/n5/n7/n8/n12/n20/n25/n28/n38/n40/n41/n48/n66/n71/n77/n78                   |

| LTE-FDD | B1/B2/B3/B4/B5/B7/B8/B9/B12/B13/B14/B17/B18/B19/B20/B25/B26/B28/B29/B30/B32/B66/B71 |

| LTE-TDD | B34/B38/B39/B40/B41/B42/B43/B46/B48                                                 |

| WCDMA   | B1/B2/B3/B4/B5/B8/B19                                                               |

| GNSS    | GPS/GLONASS/BeiDou/Galileo                                                          |

NOTE

LTE-FDD B29/B32 and LTE-TDD B46 support receving only.

RM502Q-GL can be applied in the following fields:

- Rugged tablet PC and laptop computer

- Remote monitor system

- Vehicle system

- Wireless POS system

- Smart metering system

- Wireless router and switch

- Other wireless terminal devices

## 2.2. Key Features

The following table describes key features of RM502Q-GL.

Table 2: Key Features of RM502Q-GL

| Feature            | Details                                                                   |  |  |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Function Interface | PCI Express M.2 Interface                                                 |  |  |  |  |  |  |  |

| Power Supply       | Supply voltage: 3.135–4.4 V                                               |  |  |  |  |  |  |  |

|                    | Typical supply voltage: 3.7 V                                             |  |  |  |  |  |  |  |

|                    | Class 3 (24 dBm +1/-3 dB) for WCDMA bands                                 |  |  |  |  |  |  |  |

|                    | Class 3 (23 dBm ±2 dB) for LTE bands                                      |  |  |  |  |  |  |  |

| Transmitting Power | Class 3 (23 dBm ±2 dB) for 5G NR bands                                    |  |  |  |  |  |  |  |

|                    | Class 2 (26 dBm ±2 dB) for LTE B38/B40/B41/B42/B43 bands HPUE 1)          |  |  |  |  |  |  |  |

|                    | Class 2 (26 dBm +2/-3 dB) for 5G NR n41/n77/n78 bands HPUE 1)             |  |  |  |  |  |  |  |

|                    | Support 3GPP Rel.15                                                       |  |  |  |  |  |  |  |

|                    | Support uplink 256QAM and downlink 256QAM                                 |  |  |  |  |  |  |  |

|                    | Support downlink 4 x 4 MIMO on n1/n2/n3/n7/25/n38/n40/n41/n48/n66/n77/n78 |  |  |  |  |  |  |  |

|                    | Support uplink 2 x 2 UL MIMO on n41/n77/n78                               |  |  |  |  |  |  |  |

| 5G NR Features     | Support SCS 15 kHz and 30 kHz                                             |  |  |  |  |  |  |  |

| 3G NK Features     | Support SA and NSA operation modes                                        |  |  |  |  |  |  |  |

|                    | Support NSA on n41/n77/n78                                                |  |  |  |  |  |  |  |

|                    | Support SA on all the 5G bandsSupport Option 3X, 3 A, and Option 2        |  |  |  |  |  |  |  |

|                    | NSA TDD: Max 2.5 Gbps(DL)/650 Mbps (UL)                                   |  |  |  |  |  |  |  |

|                    | SA TDD: Max 2.1 Gbps(DL)/900 Mbps (UL)                                    |  |  |  |  |  |  |  |

|                    | Support up to CA Cat 16 FDD and TDD                                       |  |  |  |  |  |  |  |

|                    | Support uplink QPSK, 16QAM and 64QAM and 256QAM modulation                |  |  |  |  |  |  |  |

| LTE Features       | Support downlink QPSK, 16QAM and 64QAM and 256QAM modulation              |  |  |  |  |  |  |  |

|                    | Support 1.4 MHz to 20 MHz (5 x CA) RF bandwidth                           |  |  |  |  |  |  |  |

|                    | Support downlink 4 × 4 MIMO on                                            |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                  | B1/B2/B3/B4/B7/B25/B30/B38/B39/B40/B41/B42/B43/B48/B66 LTE: Max 1.0 Gbps(DL)/200 Mbps (UL)                                                                                                                                                                                                                                                                                                                            |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| UMTS Features                                                                                                                                                                                                                                    | Support 3GPP R8 DC-HSDPA, HSPA +, HSDPA, HSUPA and WCDMA Support QPSK, 16QAM and 64QAM modulation DC-HSDPA: Max 42 Mbps (DL) HSUPA: Max 5.76 Mbps (UL) WCDMA: Max 384 kbps (DL)/384 kbps (UL)                                                                                                                                                                                                                         |  |  |  |

| Internet Protocol                                                                                                                                                                                                                                | Support QMI/NTP* protocols                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Features                                                                                                                                                                                                                                         | Support the protocols PAP and EIRP usually used for PPP connections                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| SMS                                                                                                                                                                                                                                              | Text and PDU modes Point-to-point MO and MT SMS cell broadcast SMS storage: ME by default                                                                                                                                                                                                                                                                                                                             |  |  |  |

| (U)SIM Interfaces                                                                                                                                                                                                                                | <ul> <li>Support (U)SIM card: Class B (3.0 V) and Class C(1.8 V)</li> <li>(U)SIM1 and (U)SIM2 interfaces</li> <li>Support Dual SIM Single Standby*</li> </ul>                                                                                                                                                                                                                                                         |  |  |  |

| USB Interface                                                                                                                                                                                                                                    | <ul> <li>Compliant with USB 3.1 and 2.0 specifications, with maximum transmission rates up to 10 Gbps on USB 3.1 and 480 Mbps on USB 2.0.</li> <li>Used for AT command communication, data transmission, firmware upgrade, software debugging, GNSS NMEA sentence output and voice over USB*</li> <li>Support USB serial drivers for: Windows 7/8/8.1/10, Linux 2.6–5.4 Android 4.x/5.x/6.x/7.x/8.x/9.x/10</li> </ul> |  |  |  |

| PCIe × 1 Interface                                                                                                                                                                                                                               | Complaint with PCIe GEN3, support 8 Gbps per lane, PCIe x 1.  Used for AT command communication, data transmission, firmware upgrade software debugging, GNSS NMEA sentence output                                                                                                                                                                                                                                    |  |  |  |

| Rx-diversity                                                                                                                                                                                                                                     | Support 5G NR/LTE/WCDMA Rx-diversity                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| GNSS Features                                                                                                                                                                                                                                    | Gen9 Lite of Qualcomm Protocol: NMEA 0183 Data Update Rate: 1 Hz                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| AT Commands                                                                                                                                                                                                                                      | Compliant with 3GPP TS 27.007, 27.005 and Quectel enhanced AT commands                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Antenna Interfaces                                                                                                                                                                                                                               | ANT0, ANT1, ANT2_GNSSL1, and ANT3                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Physical<br>Characteristics                                                                                                                                                                                                                      | Size: (52.0 ±0.15) mm × (30.0 ±0.15) mm × (2.3 ±0.2) mm<br>Weight: approx. 8.6 g                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Operation temperature range: -30°C to +60°C <sup>2)</sup> Restricted Operation temperature range: -30°C to -20°C, +60°C to +  Extended temperature range: -40°C to -30°C, +75°C to +85°C <sup>3)</sup> Storage temperature range: -40°C to +90°C |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                                                                                                                                                                                                                                  | Storage temperature range: -40°C to +90°C                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

RoHS

All hardware components are fully compliant with EU RoHS directive

## NOTES

- 1. 1) HPUE is only for single carrier.

- 2. <sup>2)</sup> Within operation temperature range, the module meets 3GPP specifications.

- 3. <sup>3)</sup> Within extended temperature range, the module remains the ability to establish and maintain functions such as voice, SMS, data transmission without any unrecoverable malfunction. Radio spectrum and radio network will not be influenced, while one or more specifications, such as P<sub>out</sub> may undergo a reduction in value, exceeding the specified tolerances of 3GPP. When the temperature returns to the normal operating temperature level, the module will meet 3GPP specifications again.

- 4. "\*" means under development.

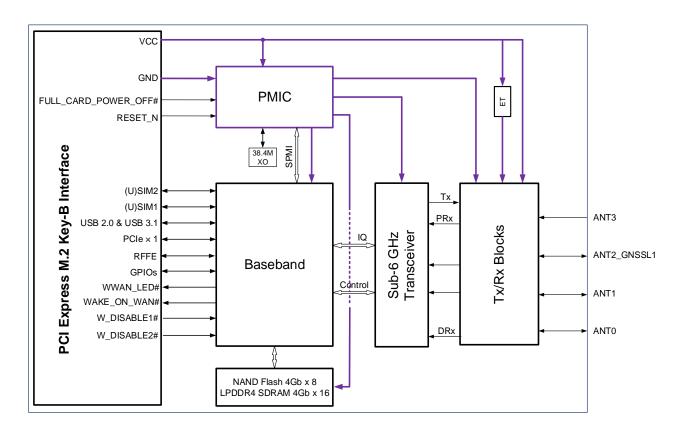

### 2.3. Functional Diagram

The following figure shows a block diagram of RM502Q-GL.

Figure 1: Functional Diagram

#### 2.4. Evaluation Board

To help with the development of applications conveniently with RM502Q-GL, Quectel supplies the evaluation board (PCIe Card EVB), a USB to RS-232 converter cable, a USB type-C cable, antennas and other peripherals to control or test the module. For more details, please refer to **document [1]**.

## **3** Application Interfaces

The physical connections and signal levels of RM502Q-GL comply with *PCI Express M.2 specification*. This chapter mainly describes the definition and application of the following interfaces/pins of RM502Q-GL:

- Power supply

- (U)SIM interfaces

- USB interface

- PCle interface

- PCM interface\*

- Control and indication interfaces\*

- COEX UART interface\*

- Antenna tuner control interface\*

- Configuration pins

**NOTE**

"\*" means under development.

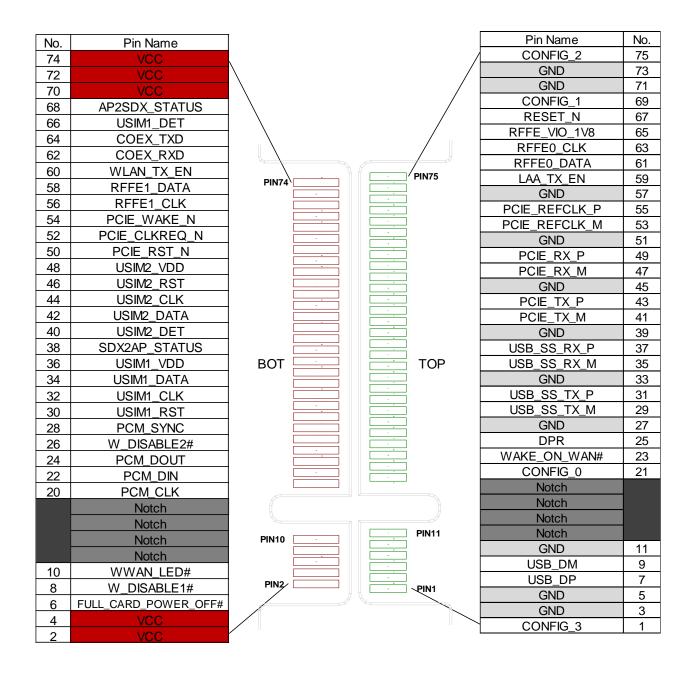

## 3.1. Pin Assignment

The following figure shows the pin assignment of RM502Q-GL. The top side contains RM502Q-GL module and antenna connectors.

Figure 2: Pin Assignment

## 3.2. Pin Description

**Table 3: Definition of I/O Parameters**

| Description    |

|----------------|

| Analog Input   |

| Analog Output  |

| Digital Input  |

| Digital Output |

| Bidirectional  |

| Open Drain     |

| Power Input    |

| Power Output   |

|                |

The following table shows the pin definition and description of RM502Q-GL.

**Table 4: Pin Description**

| Pin<br>No. | M.2 Socket 2<br>PCle-based<br>Pinout | RM502Q-GL<br>Pin Name    | I/O | Description                                             | Comment                                                                          |

|------------|--------------------------------------|--------------------------|-----|---------------------------------------------------------|----------------------------------------------------------------------------------|

| 1          | CONFIG_3                             | CONFIG_3                 | DO  | Not connected internally                                |                                                                                  |

| 2          | 3.3 V                                | VCC                      | PI  | Power supply                                            | $V_{min} = 3.135 \text{ V}$ $V_{norm} = 3.7 \text{ V}$ $V_{max} = 4.4 \text{ V}$ |

| 3          | GND                                  | GND                      |     | Ground                                                  |                                                                                  |

| 4          | 3.3 V                                | VCC                      | PI  | Power supply                                            | $V_{min} = 3.135 \text{ V}$ $V_{norm} = 3.7 \text{ V}$ $V_{max} = 4.4 \text{ V}$ |

| 5          | GND                                  | GND                      |     | Ground                                                  |                                                                                  |

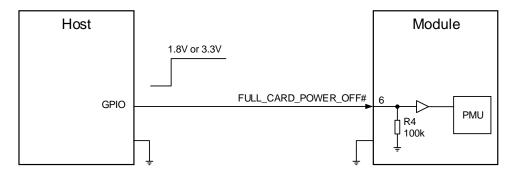

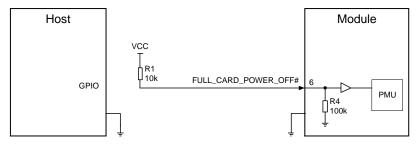

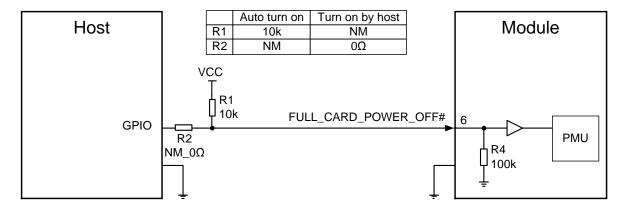

| 6          | FULL_CARD_<br>POWER_OFF#             | FULL_CARD_<br>POWER_OFF# | DI  | Turn on/off of the module. When it is at low level, the | Internally pulled down with a                                                    |

|    | (I)(0/1.8 V)                   |              |           | module is turned off.  When it is at high level, the module is turned on. | 100k Ω resistor                            |

|----|--------------------------------|--------------|-----------|---------------------------------------------------------------------------|--------------------------------------------|

| 7  | USB_D+                         | USB_DP       | AI,<br>AO | USB 2.0 differential data (+)                                             |                                            |

| 8  | W_DISABLE1#<br>(I)(0/1.8 V)    | W_DISABLE1#  | DI        | Airplane mode control. Active LOW.                                        | 1.8/3.3 V power domain                     |

| 9  | USB_D-                         | USB_DM       | AI,<br>AO | USB 2.0 differential data (-)                                             |                                            |

| 10 | GPIO_9/LED_1#<br>(OD)(0/3.3 V) | WWAN_LED#    | OD        | RF status indication LED                                                  | It is an open drain and active LOW signal. |

| 11 | GND                            | GND          |           | Ground                                                                    |                                            |

| 12 | Key                            | Notch        |           | Notch                                                                     |                                            |

| 13 | Key                            | Notch        |           | Notch                                                                     |                                            |

| 14 | Key                            | Notch        |           | Notch                                                                     |                                            |

| 15 | Key                            | Notch        |           | Notch                                                                     |                                            |

| 16 | Key                            | Notch        |           | Notch                                                                     |                                            |

| 17 | Key                            | Notch        |           | Notch                                                                     |                                            |

| 18 | Key                            | Notch        |           | Notch                                                                     |                                            |

| 19 | Key                            | Notch        |           | Notch                                                                     |                                            |

| 20 | GPIO_5<br>/AUDIO_0             | PCM_CLK      | Ю         | PCM data bit clock                                                        | 1.8 V power<br>domain                      |

| 21 | CONFIG_0                       | CONFIG_0     | DO        | Not connected internally                                                  |                                            |

| 22 | GPIO_6<br>/AUDIO_1             | PCM_DIN      | DI        | PCM data input                                                            | 1.8 V power<br>domain                      |

| 23 | GPIO_11<br>/WOWWAN#            | WAKE_ON_WAN# | OD        | Wake up the host.<br>Active LOW.                                          | Open drain                                 |

| 24 | GPIO_7<br>/AUDIO_2             | PCM_DOUT     | DO        | PCM data output                                                           | 1.8 V power<br>domain                      |

| 25 | DPR<br>(I)(0/1.8 V)            | DPR          | DI        | Dynamic power reduction. High level by default.                           | 1.8 V power<br>domain                      |

| 26 | GPIO_10<br>/W_DISABLE2#        | W_DISABLE2#  | DI        | GNSS disable control. Active LOW.                                         | 1.8/3.3 V power domain                     |

| 27 | GND                            | GND          |           | Ground                                                                    |                                            |

| 28 | GPIO_8<br>/AUDIO_3   | PCM_SYNC      | Ю  | PCM data frame sync              | 1.8 V power<br>domain         |

|----|----------------------|---------------|----|----------------------------------|-------------------------------|

| 29 | PETn1                | USB_SS_TX_M   | AO | USB 3.1 transmit data (-)        |                               |

| 30 | UIM_RESET(O)         | USIM1_RST     | DO | (U)SIM1 card reset               | 1.8/3.0 V power domain        |

| 31 | PETp1                | USB_SS_TX_P   | AO | USB 3.1 transmit data (+)        |                               |

| 32 | UIM_CLK(O)           | USIM1_CLK     | DO | (U)SIM1 card clock               | 1.8/3.0 V power domain        |

| 33 | GND                  | GND           |    | Ground                           |                               |

| 34 | UIM_DATA(I/O)        | USIM1_DATA    | Ю  | (U)SIM1 card data                | 1.8/3.0 V power domain        |

| 35 | PERn1                | USB_SS_RX_M   | Al | USB 3.1 receive data (-)         |                               |

| 36 | UIM_PWR(O)           | USIM1_VDD     | РО | Power supply for (U)SIM1 card    | 1.8/3.0 V power domain        |

| 37 | PERp1                | USB_SS_RX_P   | AI | USB 3.1 receive data (+)         |                               |

| 38 | NC                   | SDX2AP_STATUS | DO | Status indication to AP          | 1.8 V power<br>domain         |

| 39 | GND                  | GND           |    | Ground                           |                               |

| 40 | GPIO_0<br>/SIM_DET2  | USIM2_DET     | DI | (U)SIM2 card insertion detection | Internally pulled up to 1.8 V |

| 41 | PETn0                | PCIE_TX_M     | AO | PCIe transmit data (-)           |                               |

| 42 | GPIO_1<br>/SIM_DAT2  | USIM2_DATA    | Ю  | (U)SIM2 card data                | 1.8/3.0 V power domain        |

| 43 | PETp0                | PCIE_TX_P     | AO | PCIe transmit data (+)           |                               |

| 44 | GPIO_2<br>/SIM_CLK2  | USIM2_CLK     | DO | (U)SIM2 card clock               | 1.8/3.0 V power domain        |

| 45 | GND                  | GND           |    | Ground                           |                               |

| 46 | GPIO_3<br>/SIM_RST2  | USIM2_RST     | DO | (U)SIM2 card reset               | 1.8/3.0 V power domain        |

| 47 | PERn0                | PCIE_RX_M     | AI | PCIe receive data (-)            |                               |

| 48 | GPIO_4<br>(SIM_PWR2) | USIM2_VDD     | РО | Power supply for (U)SIM2 card    | 1.8/3.0 V power<br>domain     |

| 49 | PERp0                | PCIE_RX_P     | AI | PCIe receive data (+)            |                               |

| 50 | PERST#               | PCIE_RST_N    | DI | PCIe reset.<br>Active LOW.       | Open drain                    |

|    |                      |               |    |                                  |                               |

| GND  CLKREQ#  REFCLKn  PEWAKE#  REFCLKp  NC  GND | GND  PCIE_CLKREQ_N  PCIE_REFCLK_M  PCIE_WAKE_N  PCIE_REFCLK_P  RFFE1_CLK  GND                                                                                  | DO AI, AO DO AI, AO                                                                                                                                                                                                                                                                                                | Ground  PCIe clock request. Active LOW.  PCIe reference clock (-)  PCIe PME wake. Active LOW.  PCIe reference clock (+)  RFFE1 serial interface clock                                                                                                                                                                                                                                | Open drain  Open drain  1.8 V power domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFCLKn PEWAKE# REFCLKp NC GND                   | PCIE_REFCLK_M  PCIE_WAKE_N  PCIE_REFCLK_P  RFFE1_CLK                                                                                                           | AI,<br>AO<br>DO<br>AI,<br>AO                                                                                                                                                                                                                                                                                       | Active LOW.  PCIe reference clock (-)  PCIe PME wake. Active LOW.  PCIe reference clock (+)                                                                                                                                                                                                                                                                                          | Open drain  1.8 V power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PEWAKE#  REFCLKp  NC  GND                        | PCIE_WAKE_N PCIE_REFCLK_P RFFE1_CLK                                                                                                                            | AO<br>DO<br>AI,<br>AO                                                                                                                                                                                                                                                                                              | PCIe PME wake. Active LOW.  PCIe reference clock (+)                                                                                                                                                                                                                                                                                                                                 | 1.8 V power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| REFCLKp<br>NC<br>GND                             | PCIE_REFCLK_P RFFE1_CLK                                                                                                                                        | AI,<br>AO                                                                                                                                                                                                                                                                                                          | Active LOW.  PCle reference clock (+)                                                                                                                                                                                                                                                                                                                                                | 1.8 V power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NC<br>GND                                        | RFFE1_CLK                                                                                                                                                      | AO                                                                                                                                                                                                                                                                                                                 | . ,                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND                                              |                                                                                                                                                                | DO                                                                                                                                                                                                                                                                                                                 | RFFE1 serial interface clock                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                  | GND                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NC                                               |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                    | Ground                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NC                                               | RFFE1_DATA                                                                                                                                                     | DO                                                                                                                                                                                                                                                                                                                 | RFFE1 serial interface data                                                                                                                                                                                                                                                                                                                                                          | 1.8 V power<br>domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ANTCTL0<br>(O)(0/1.8 V)                          | LAA_TX_EN                                                                                                                                                      | DO                                                                                                                                                                                                                                                                                                                 | Notification from SDR to WL when LTE transmitting                                                                                                                                                                                                                                                                                                                                    | 1.8 V power<br>domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| COEX3                                            | WLAN_TX_EN                                                                                                                                                     | DI                                                                                                                                                                                                                                                                                                                 | Notification from WL to SDR while transmitting                                                                                                                                                                                                                                                                                                                                       | 1.8 V power<br>domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ANTCTL1<br>(O)(0/1.8 V)                          | RFFE0_DATA                                                                                                                                                     | DO                                                                                                                                                                                                                                                                                                                 | RFFE0 serial interface data                                                                                                                                                                                                                                                                                                                                                          | 1.8 V power<br>domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| COEX2                                            | COEX_RXD                                                                                                                                                       | DI                                                                                                                                                                                                                                                                                                                 | LTE/WLAN coexistence receive data                                                                                                                                                                                                                                                                                                                                                    | 1.8 V power<br>domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ANTCTL2<br>(O)(0/1.8 V)                          | RFFE0_CLK                                                                                                                                                      | DO                                                                                                                                                                                                                                                                                                                 | RFFE0 serial interface clock                                                                                                                                                                                                                                                                                                                                                         | 1.8 V power<br>domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| COEX1                                            | COEX_TXD                                                                                                                                                       | DO                                                                                                                                                                                                                                                                                                                 | LTE/WLAN coexistence transmit data                                                                                                                                                                                                                                                                                                                                                   | 1.8 V power<br>domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ANTCTL3<br>(O)(0/1.8 V)                          | RFFE_VIO_1V8                                                                                                                                                   | РО                                                                                                                                                                                                                                                                                                                 | Power supply for RFFE                                                                                                                                                                                                                                                                                                                                                                | 1.8 V power output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SIM_DETECT                                       | USIM1_DET                                                                                                                                                      | DI                                                                                                                                                                                                                                                                                                                 | (U)SIM1 card insertion detection                                                                                                                                                                                                                                                                                                                                                     | Internally pulled up to 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

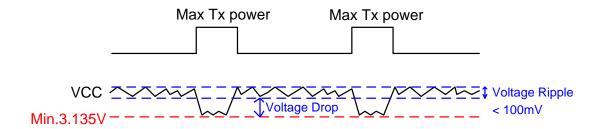

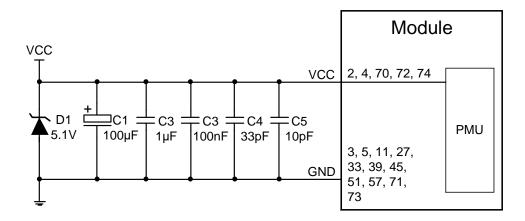

| RESET#<br>(I)(0/1.8 V)                           | RESET_N                                                                                                                                                        | DI                                                                                                                                                                                                                                                                                                                 | Reset the module. Active LOW.                                                                                                                                                                                                                                                                                                                                                        | Internally pulled up to 1.8 V with a 100k Ω resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |