Note: "\*" means that the fail frequency has been verified by the plot of "Channel Power < 13dBm Pass"

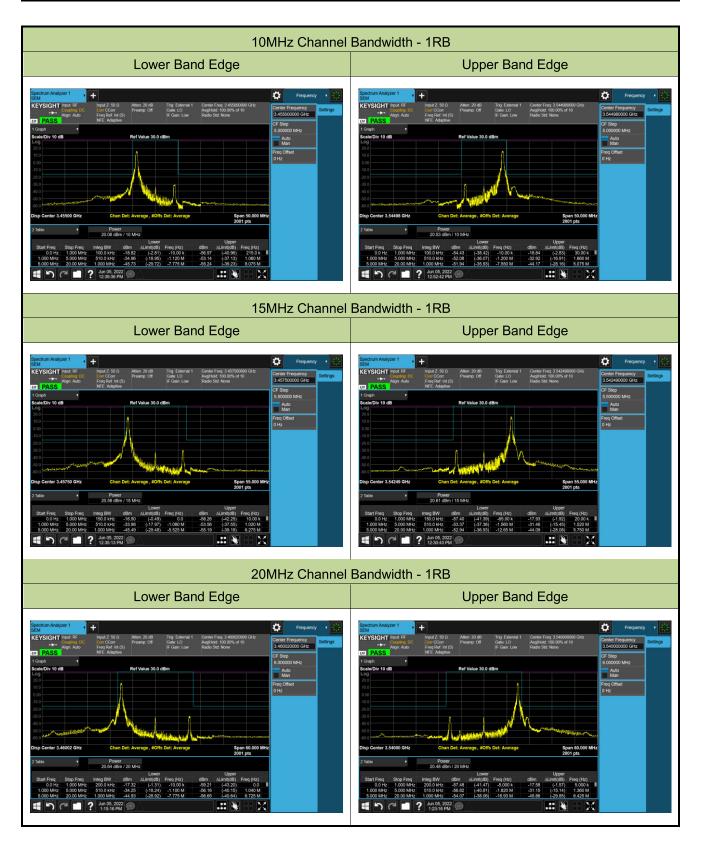

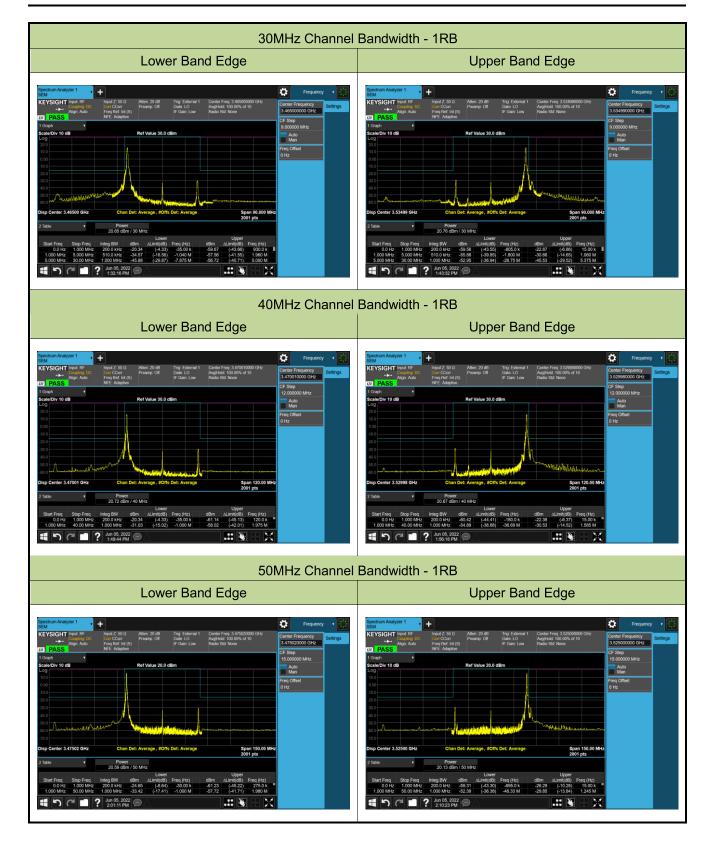

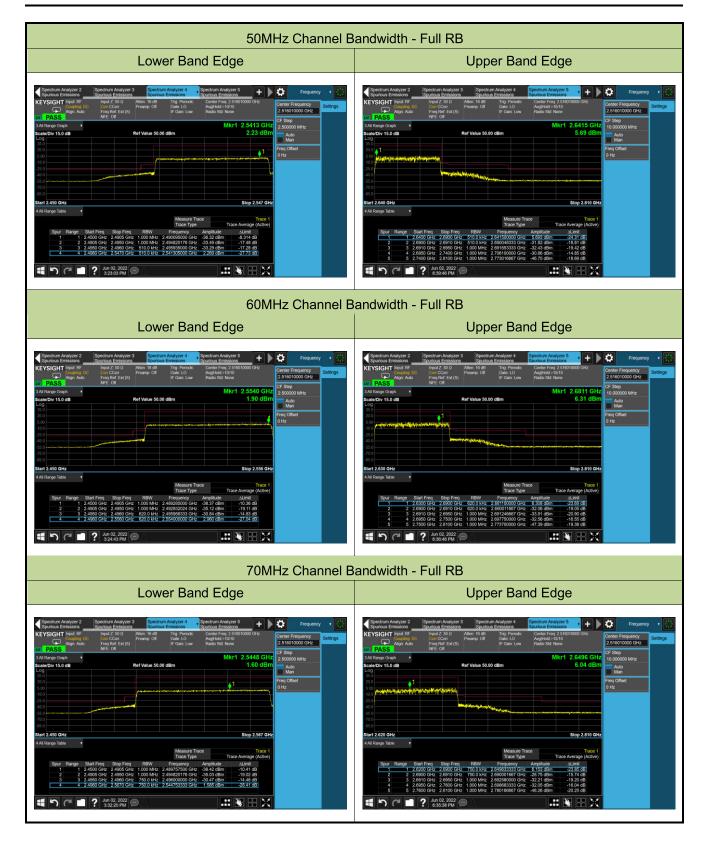

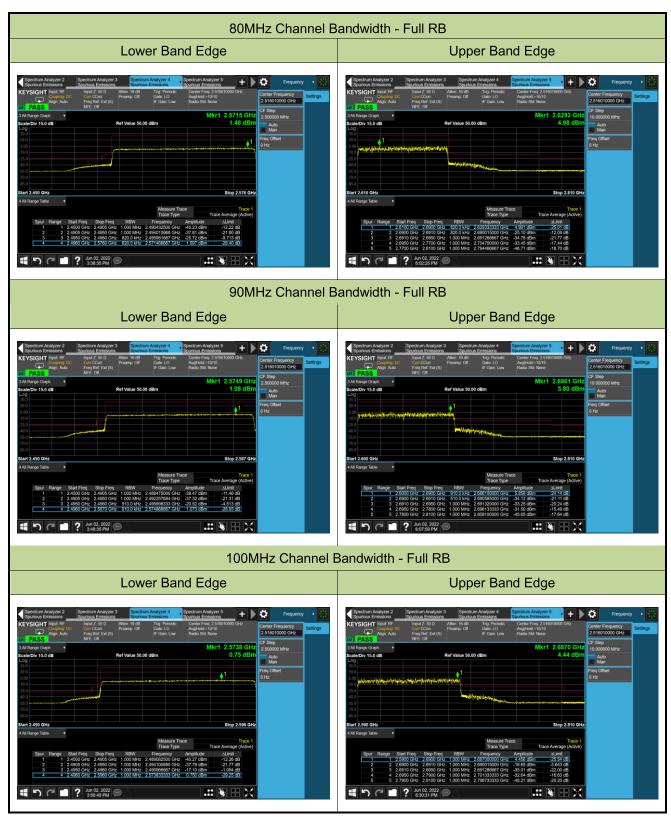

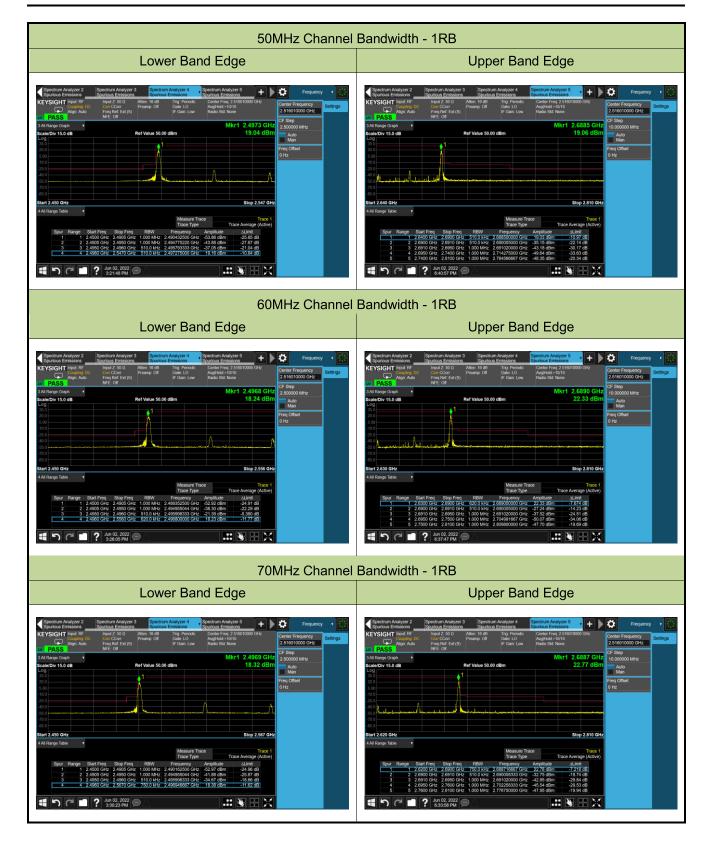

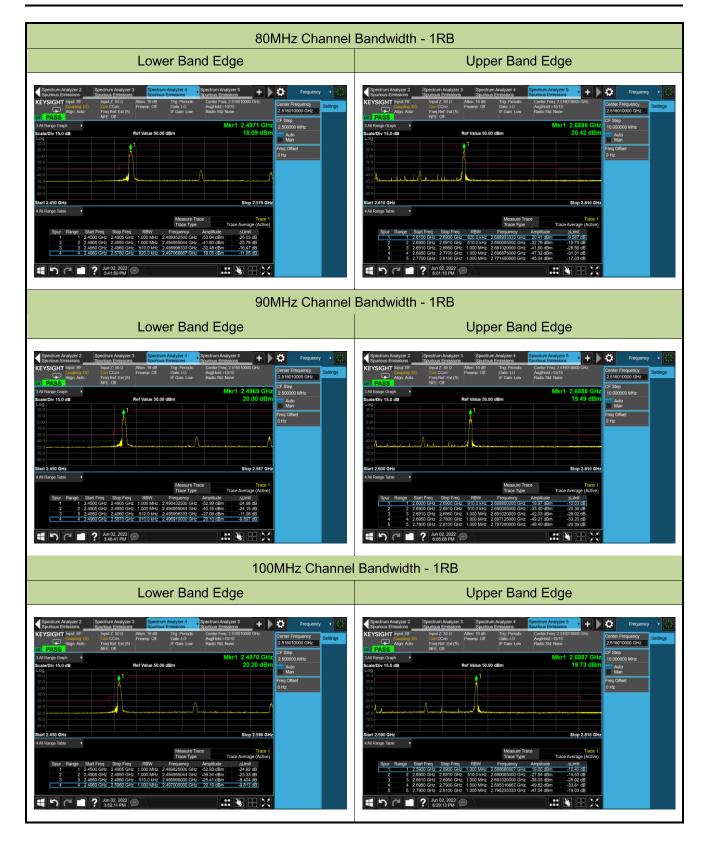

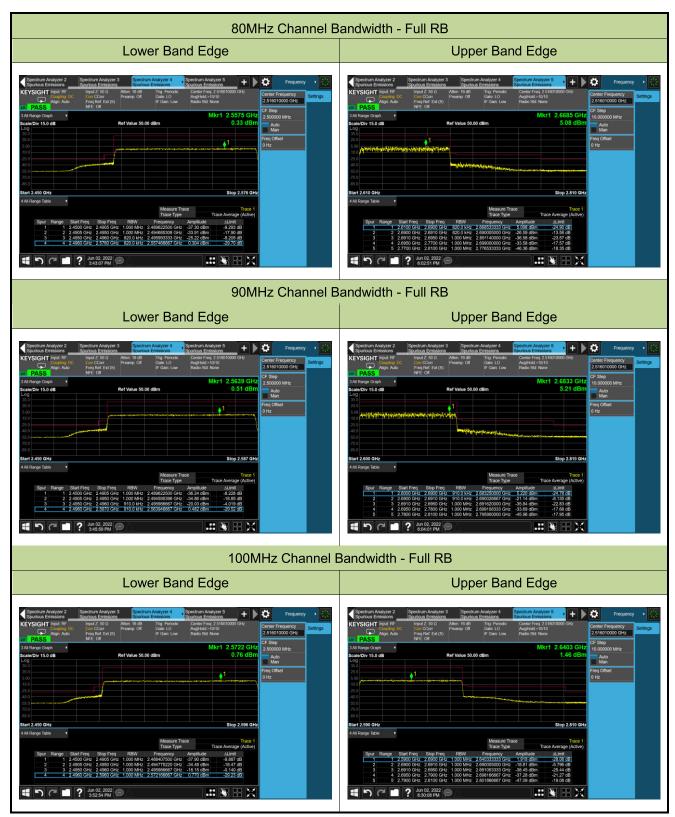

| Test Site | SIP-SR1    | Test Engineer | Candy Luo              |

|-----------|------------|---------------|------------------------|

| Test Date | 2022/06/02 | Test Band     | n41_MIMO_HPUE (Port 2) |

Note: "\*" means that the fail frequency has been verified by the plot of "Channel Power < 13dBm Pass"

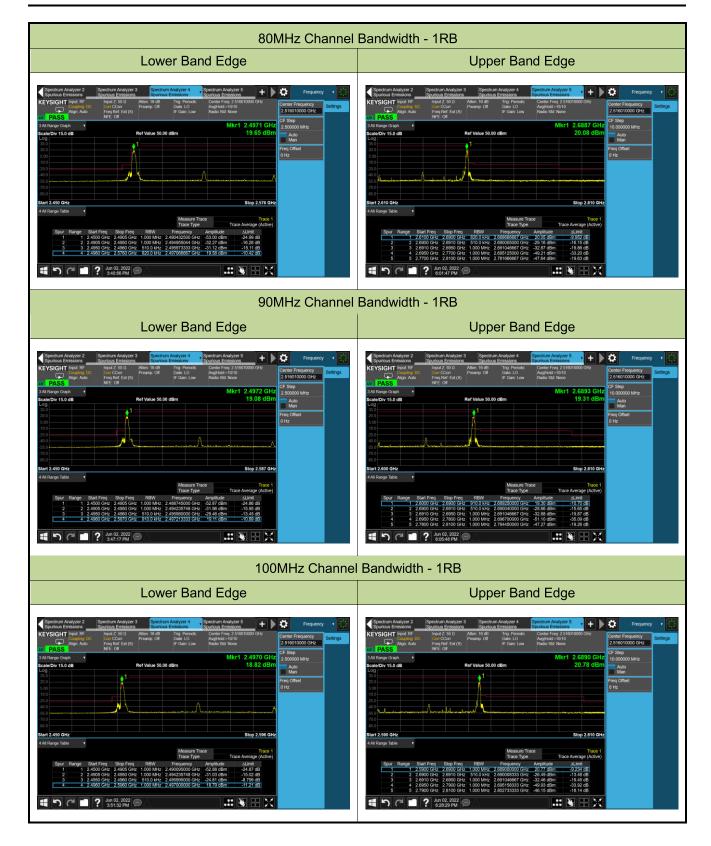

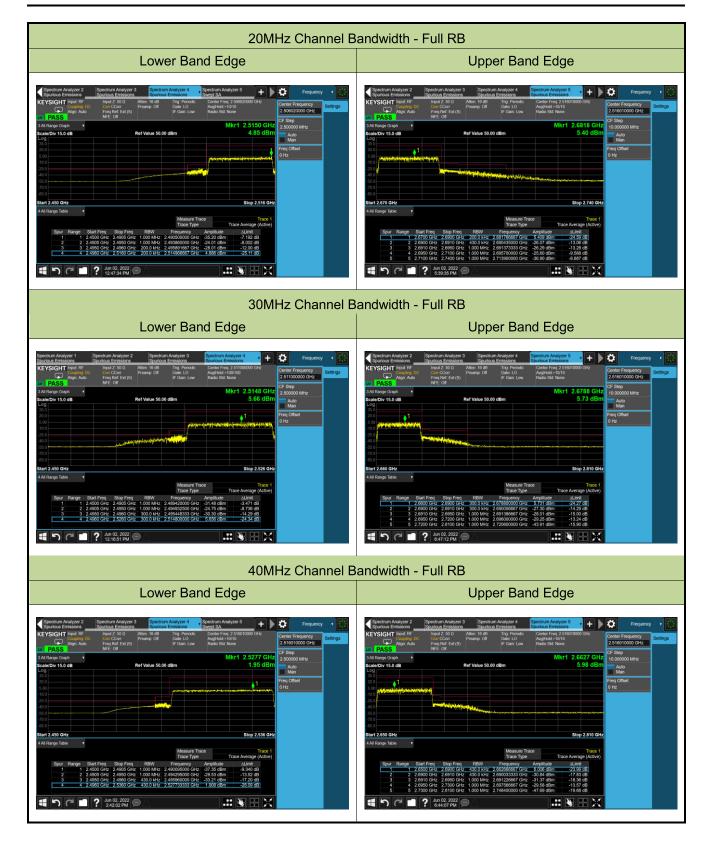

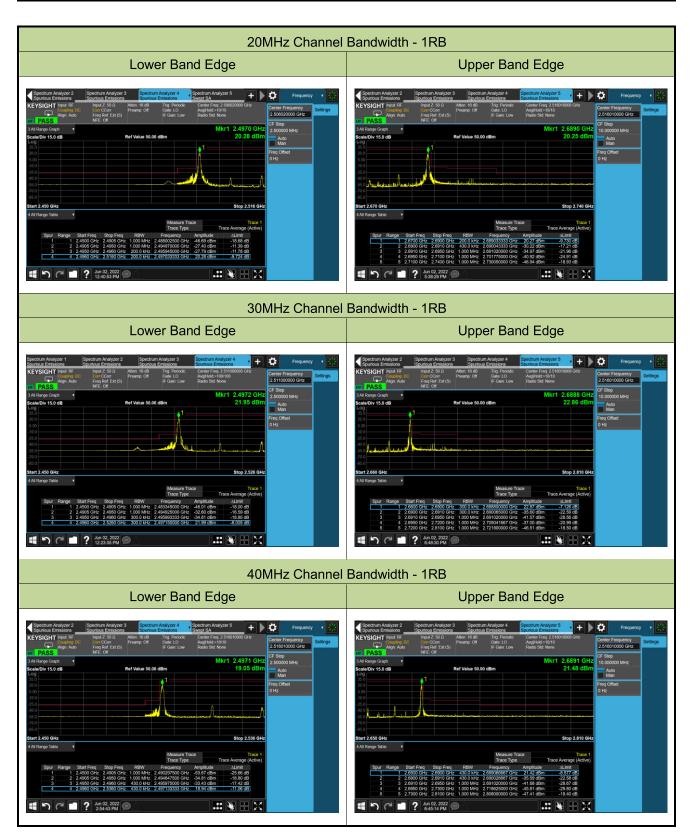

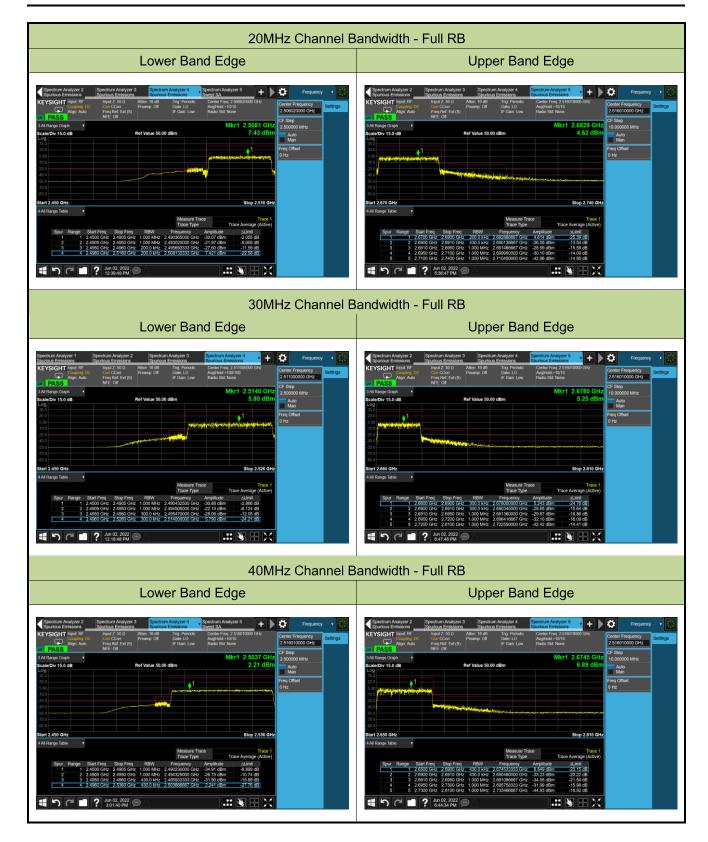

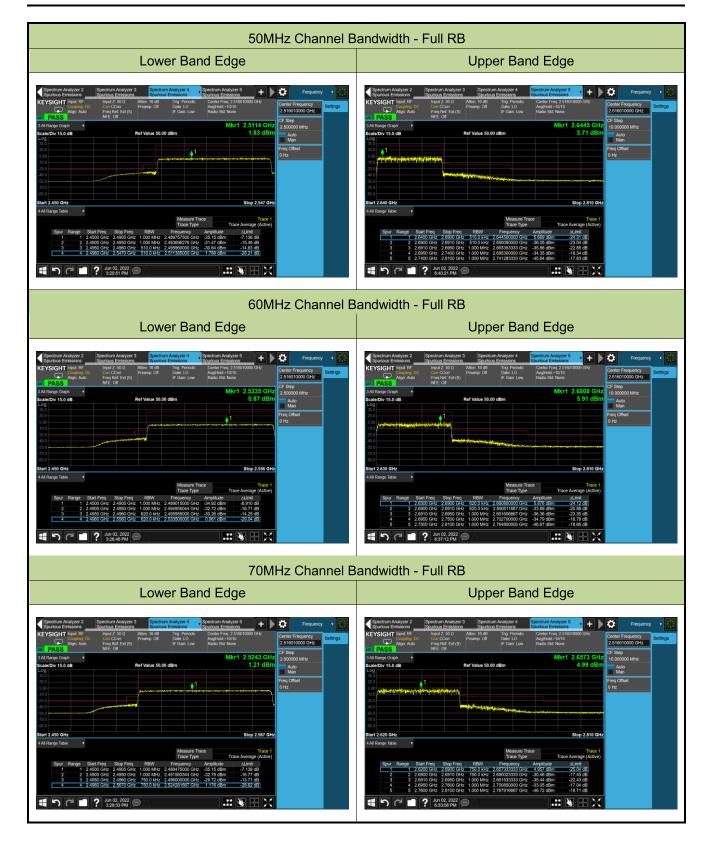

| Test Site | SIP-SR1    | Test Engineer | Candy Luo                 |

|-----------|------------|---------------|---------------------------|

| Test Date | 2022/06/05 | Test Band     | n77/n78_MIMO_HPUE         |

|           |            |               | (Port 0) (3450 ~ 3550MHz) |