## Features

- Integrated 2.45 GHz, IEEE 802.15.4 compliant transceiver

- 100mW (20dBm) TX output power

- Adjustable output power (45dB dynamic range)

- Selectable LNA for added range or increased noise immunity

- -92dBm RX sensitivity with LNA disabled

- -98dBm RX sensitivity with LNA enabled

- RX and TX filtering for co-existence with IEEE 802.11g and Bluetooth devices

- Integrated IEEE 802.15.4 PHY and MAC

- 128 kB Embedded Flash and 5 kB SRAM for program and data storage

- 7 multi-purpose GPIO pins (GPIO, UART, I2C, SPI, ADC)

- Through-Hole Test Points to allow a custom wiring harness connecting VIN, GND, TTL-RXD and TTL-TXD for non-SMT integration of the module.

- Design based on the Ember EM250 or the STMicroelectronics SN250

- Integrated RC oscillator (10 kHz) for low power operation

- Less than 3uA current consumption in Deep Sleep mode

- Pins available for non-intrusive debug interface (SIF)

- Wide input voltage range (3.4 – 9 VDC) (alternate configuration for 2.2-3.6VDC)

- FCC Compliant

## Applications

- Sensor networks

- Remote monitoring and security

- Industrial and Lighting controls

- Home automation and control

## Description

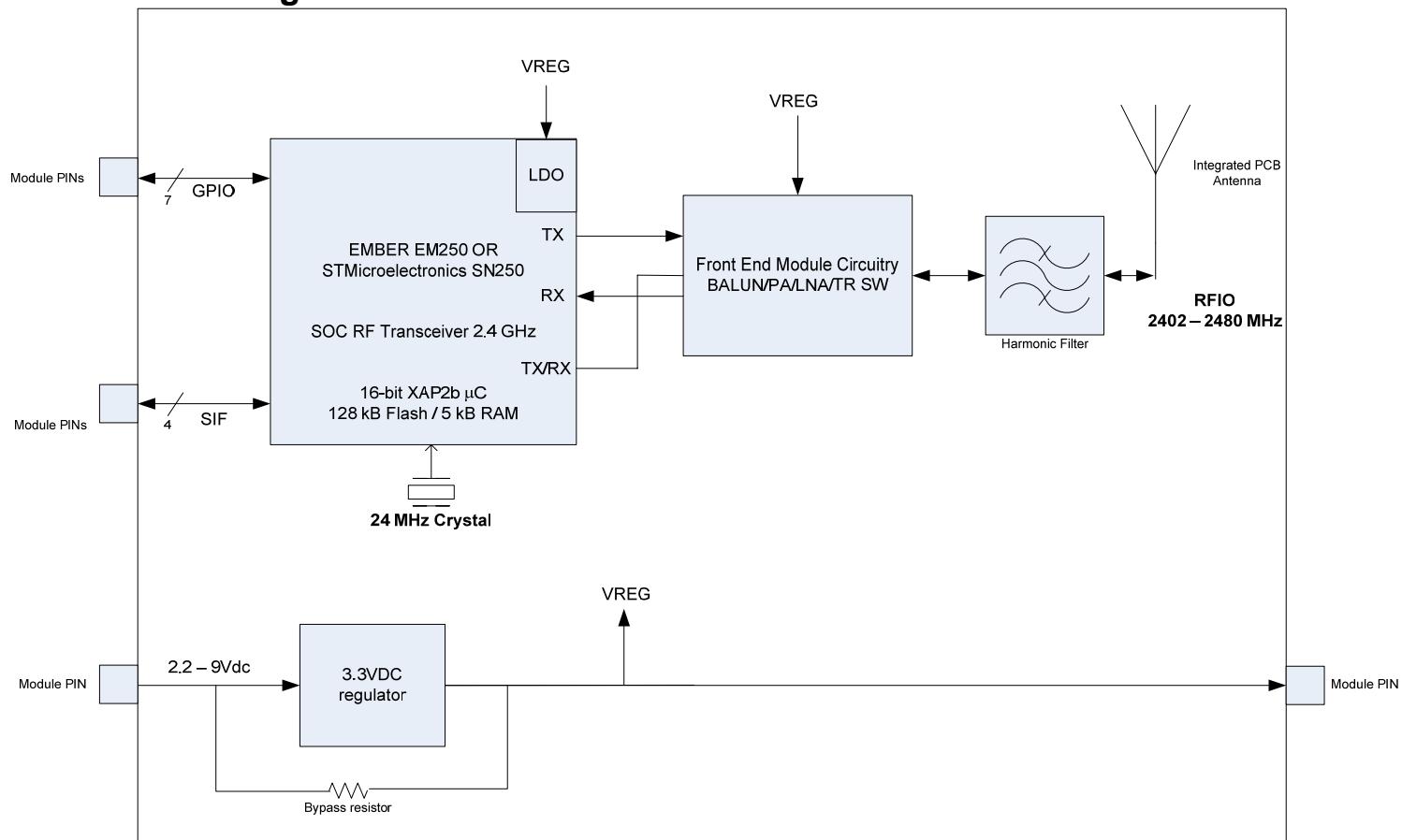

Cipher's URMA-2450 is a high power output, low power consumption ZigBee® module based on the EM250 or SN250 ZigBee® Network Processor which integrates a 2.4 GHz, IEEE 802.15.4-compliant transceiver with built-in PHY and MAC, along with an adjustable Power Amplifier (PA) and Low Noise Amplifier (LNA). This ZigBee® module enables OEMs to easily add wireless networking capability to their electronic devices, providing a comprehensive solution to create sensor and control networks with meshing and self healing capabilities.

A 24 MHz high stability crystal provides the timing requirements as per ZigBee® specifications. An internal RC oscillator allows low power operation. The Deep Sleep mode, with power consumption less than 3  $\mu$ A, allows applications where the battery life is a key point. An on board regulator (LDO) allows input voltage up to 9VDC. For applications supplying power at less than 3.6V, an alternate configuration of the module (without the regulator) allows for input supply voltage as low as 2.2VDC with minimal reduction in output power. The URMA-2450 module includes an integrated 2.45 GHz PCB "Inverted-F" antenna.

128 kB Flash and 5 kB of static RAM are available for data and program storage. To support user defined applications, a number of peripherals such as GPIO, UART, I2C, ADC and general purpose timers are available and user selectable. The module can be controlled by means of a standard serial interface allowing the connection to a variety of host microcontrollers.

For additional information and details, please refer to the EM250 datasheet available at:

<http://portal.ember.com/em250/datasheet>

## Block Diagram

URMA-2450 Block Diagram

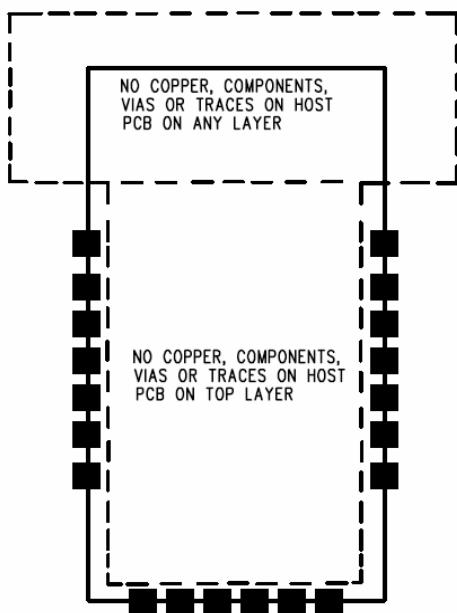

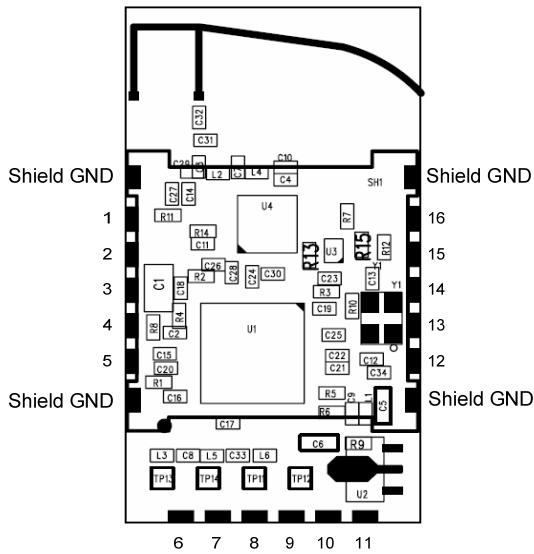

## PCB Footprint Keep-outs

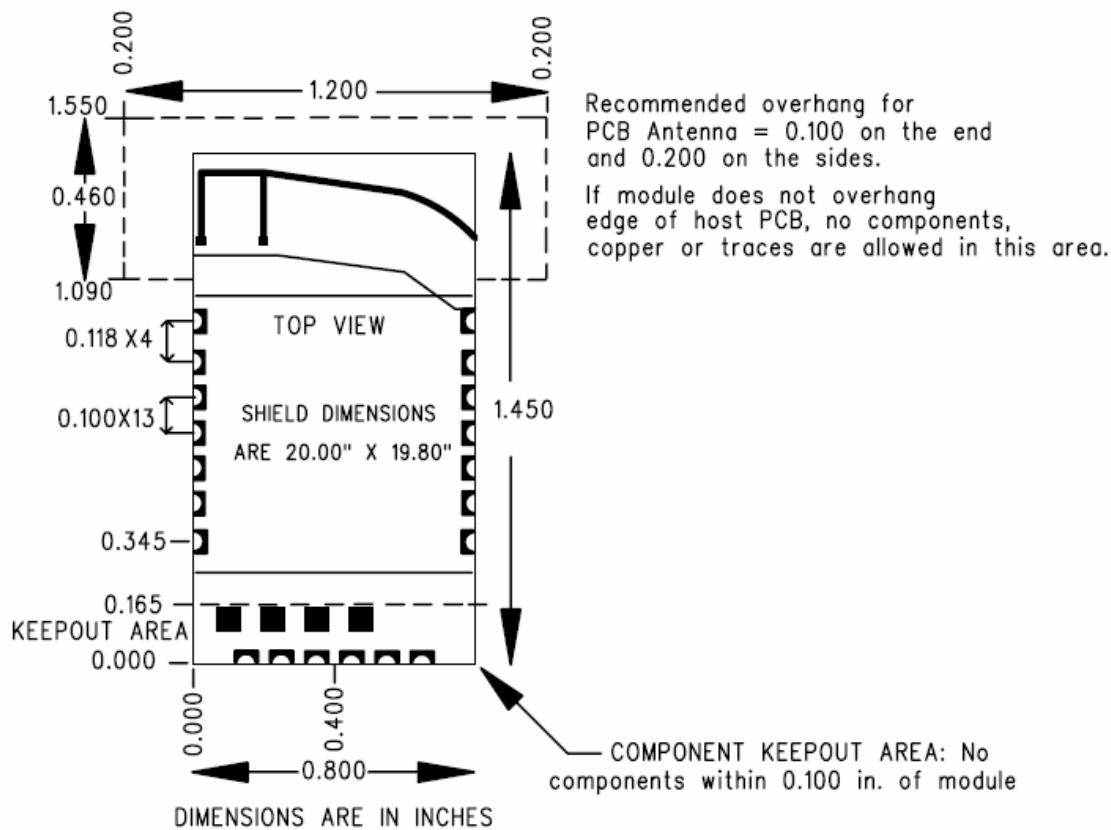

## PCB Footprint Dimensions

| Pin #                           | Function  | Direction     | Description                                                                                                              |

|---------------------------------|-----------|---------------|--------------------------------------------------------------------------------------------------------------------------|

| 1                               | RFIO      | bidirectional | RF signal optional input/output                                                                                          |

| 2 (TP12) 4<br>Shield<br>Grounds | RF GND    | n/a           | RF signal ground                                                                                                         |

| 3                               | nCTS      | I             | UART CTS handshake of Serial Controller SC1                                                                              |

|                                 | GPIO11    | I/O           | Digital I/O                                                                                                              |

|                                 | MCLK      | O             | SPI master clock of Serial Controller SC1                                                                                |

|                                 | TMR2IA.1  | I             | Capture Input A of Timer 2                                                                                               |

| 4                               | nRTS      | O             | UART RTS handshake of Serial Controller SC1                                                                              |

|                                 | GPIO12    | I/O           | Digital I/O                                                                                                              |

|                                 | TMR2IB.1  | I             | Capture Input B for Timer 2                                                                                              |

|                                 | GPIO5     | I/O           | Digital I/O                                                                                                              |

| 5                               | ADC1      | I             | ADC Input 1                                                                                                              |

|                                 | PTI_DATA  | O             | Data signal of Packet Trace Interface (PTI)                                                                              |

|                                 | GPIO6     | I/O           | Digital I/O                                                                                                              |

| 6                               | ADC2      | I             | ADC Input 2                                                                                                              |

|                                 | TMR2CLK   | I             | External clock input of Timer 2                                                                                          |

|                                 | TMR1ENMSK | I             | External enable mask of Timer 1                                                                                          |

|                                 | ZBTXD     | O             | UART transmit data of Serial Controller SC1                                                                              |

| 7 (TP13)                        | GPIO9     | I/O           | Digital I/O                                                                                                              |

|                                 | MO        | O             | SPI master data out of Serial Controller SC1                                                                             |

|                                 | MSDA      | I/O           | I2C data of Serial Controller SC1                                                                                        |

|                                 | TMR1IA.2  | I             | Capture Input A of Timer 1                                                                                               |

|                                 | ZBRXD     | I             | UART receive data of Serial Controller SC1                                                                               |

| 8 (TP14)                        | GPIO10    | I/O           | Digital I/O                                                                                                              |

|                                 | MI        | I             | SPI master data in of Serial Controller SC1                                                                              |

|                                 | MSCL      | I/O           | I2C clock of Serial Controller SC1                                                                                       |

|                                 | TMR1IB.2  | I             | Capture Input B of Timer 1                                                                                               |

| 9 (TP11)                        | VIN       | I             | Input Voltage: 3.4 - 9Vdc                                                                                                |

| 10                              | SIF_CLK   | I             | Programming and debug interface clock (internal pull-down)                                                               |

| 11                              | SIF_MISO  | O             | Programming and debug interface, master in/slave out                                                                     |

| 12                              | SIF_MOSI  | I             | Programming and debug interface, master out/slave in (external pull-down required to guarantee state in Deep Sleep Mode) |

| 13                              | NSIF_LOAD | I/O           | Programming and debug interface, load strobe (open-collector with internal pull-up)                                      |

| 14                              | NRESET    | I             | Active low chip reset (internal pull-up)                                                                                 |

| 15                              | IRQB      | I             | External interrupt source B                                                                                              |

|                                 | GPIO14    | I/O           | Digital I/O                                                                                                              |

|                                 | TMR2OB    | O             | Waveform Output B of Timer 2                                                                                             |

|                                 | TMR1IB.3  | I             | Capture Input B of Timer 1                                                                                               |

| 16                              | VDD       | O             | Internal Regulator 3.3V Output                                                                                           |

## Maximum Ratings

### Absolute Maximum Ratings

| Symbol    | Parameter                        | Values |     |               | Unit |

|-----------|----------------------------------|--------|-----|---------------|------|

|           |                                  | Min    | Typ | Max           |      |

| $V_{IN}$  | Regulator input voltage          | -0.3   |     | 18            | V    |

| $V_{DD}$  | EM250 & PA supply voltage        | -0.3   |     | 3.6           | V    |

| $V_{IN}$  | Input voltage on any digital pin | -0.3   |     | $V_{DD} +0.3$ | V    |

| $T_{stg}$ | Storage temperature              | -40    |     | 85            | °C   |

## Physical Characteristics

| Dimension | Typical Value | Unit |

|-----------|---------------|------|

| Width     | 0.85          | inch |

| Height    | 1.5           | inch |

| Thickness | 0.15          | inch |

| Weight    | 3.5           | gram |

### Operating Range

| Symbol   | Parameter                | Values |     |     | Unit |

|----------|--------------------------|--------|-----|-----|------|

|          |                          | Min    | Typ | Max |      |

| $V_{IN}$ | Regulator input voltage  | 3.4    |     | 9   | V    |

| $V_{DD}$ | Regulator output voltage |        | 3.3 |     | V    |

| $V_{DD}$ | Module supply voltage    | 2.2    | 3.3 | 3.6 | V    |

| $T_{op}$ | Operating temperature    | -40    |     | 85  | °C   |

## Electrical Characteristics

### DC Electrical Characteristics

| Symbol | Parameter                          | Conditions | Values |     |     | Unit |

|--------|------------------------------------|------------|--------|-----|-----|------|

|        |                                    |            | Min    | Typ | Max |      |

| IRX    | RX current (boost mode)            | At 25°C    |        | 36  |     | mA   |

| IRX    | RX current (normal mode)           | At 25°C    |        | 38  |     | mA   |

| ITX    | TX current (boost mode)            | At 25°C    |        | 150 |     | mA   |

| ITX    | TX current (normal mode)           | At 25°C    |        | 42  |     | mA   |

| IDS    | Deep sleep current (RC oscillator) | At 25°C    |        | 3   |     | µA   |

**DC I/O Specification**

| Symbol | Parameter                         | Values                |     |                       | Unit |

|--------|-----------------------------------|-----------------------|-----|-----------------------|------|

|        |                                   | Min                   | Typ | Max                   |      |

| VIL    | Low Level Input Voltage           | 0                     |     | 0.2* V <sub>DD</sub>  | V    |

| VIH    | High Level Input Voltage          | 0.8* V <sub>DD</sub>  |     | V <sub>DD</sub>       | V    |

| IIL    | Input current for logic 0         |                       |     | -0.5                  | µA   |

| IIH    | Input current for logic 1         |                       |     | 0.5                   | µA   |

| Ripu   | Input pull-up resistor            |                       | 30  |                       | kΩ   |

| Ripd   | Input pull-down resistor          |                       | 30  |                       | kΩ   |

| VOL    | Low level output voltage          | 0                     |     | 0.18* V <sub>DD</sub> | V    |

| VOH    | High level output voltage         | 0.82* V <sub>DD</sub> |     | V <sub>DD</sub>       | V    |

| IOHS   | Output source current (GPIO 12:5) |                       |     | 4                     | mA   |

| IOLS   | Output sink current (GPIO 12:5)   |                       |     | 4                     | mA   |

| IOHH   | Output source current (GPIO 14)   |                       |     | 8                     | mA   |

| IOLH   | Output sink current (GPIO 14)     |                       |     | 8                     | mA   |

| IOTot  | Total output current for I/O      |                       |     | 40                    | mA   |

**RF Electrical Characteristics**

| Symbol | Parameter                  | Conditions                  | Values |     |      | Unit |

|--------|----------------------------|-----------------------------|--------|-----|------|------|

|        |                            |                             | Min    | Typ | Max  |      |

|        | Frequency Range            |                             | 2400   |     | 2500 | MHz  |

| TX     | Output power               |                             | -25    |     | 20   | dBm  |

| RX     | Sensitivity                |                             | -98    |     | -92  | dBm  |

| CFE    | Carrier frequency error    |                             | -40    |     | +40  | ppm  |

|        | Error Vector magnitude     | As defined by IEEE 802.15.4 |        | 5   | 15   | %    |

|        | Adjacent channel rejection |                             |        | 35  |      | dB   |

## Appendix A      FCC Statement

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Note: This equipment has been tested and found to comply with the limits of a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna

- Increase the separation between the equipment and the receiver

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected

Consult the dealer or an experienced radio/TV technician for help.

## Antenna

Cipher's URMA-2450 is for OEM integrations only. The end-user product will be professionally installed in such a manner that only the authorized antennas are used.

## Caution

Any changes or modifications not expressly approved by the party responsible for compliance could cause the module to cease to comply with FCC rules part 15, and thus void the user's authority to operate the equipment.

## A.1 Label instruction

## Instruction manual for FCC ID Label

**Module type:** ZigBee® module **URMA-2450**

**FCC-ID:** WJU-URMA2450

This intends to inform you how to specify the FCC ID of our ZigBee® module URMA-2450 on your final product. Based on the Public Notice from FCC, the product into which our transmitter module is installed must display reference to the enclosed module. The label should use wording such as "Contains Transmitter Module FCC ID: WJU-URMA2450" or "Contains FCC ID: WJU-URMA2450", any similar wording that expressed the same meaning may be used.

Example label:

Contains FCC ID: WJU-URMA2450

## A.2 Integration Requirements

Operate the module according to specifications listed in this data sheet.

On the exterior of the product include a clearly visible label stating: "Contains FCC ID: WJU-URMA2450"

## Terms and Conditions

Information in this document is provided exclusively in connection with Cipher Systems wireless products. Cipher Systems reserves the right to make changes, corrections, modifications, or improvements to this document, and the products and services described herein at any time, without notice and without recourse.

Unless expressly approved in writing by an authorized Cipher Systems representative, any purchase and/or implementation of Cipher Systems wireless products implies that the parties involved understand and accept Cipher Systems terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of Cipher Systems Wireless Products and services described herein and Cipher Systems assumes no liability whatsoever relating to the choice, selection or use of Cipher Systems products and services described herein.

## Document Revision History

| Revision History |                  |                  |

|------------------|------------------|------------------|

| Release          | Date             | Revision         |

| Initial Release  | February 2, 2009 | Preliminary - 01 |

|                  |                  |                  |