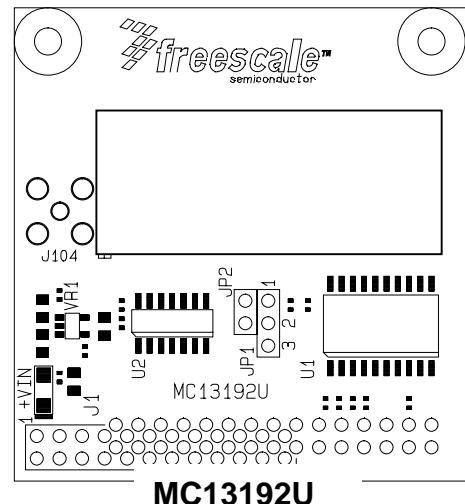

# MC13192U

## Application Module for the Freescale MC13192 2.4GHz RF Transceiver

### Hardware User Guide

#### Table of Contents

|                                                                          |   |

|--------------------------------------------------------------------------|---|

| Cautionary Notes: .....                                                  | 2 |

| Terminology .....                                                        | 2 |

| Module Features .....                                                    | 3 |

| Module Option Jumpers .....                                              | 4 |

| JP1 - Select Signal Option .....                                         | 4 |

| JP2 – Clock-Out Enable Option .....                                      | 4 |

| J1 Connector – Default Host I/O Connection .....                         | 4 |

| J2 Connector .....                                                       | 5 |

| J104 – SMA Test Connector .....                                          | 5 |

| Installation .....                                                       | 5 |

| MCU Project Board - Module Installation .....                            | 6 |

| CSM, DEMO or Host MCU Board - Module Installation on Socket Header ..... | 6 |

| CSM, DEMO or Host MCU Board - Module Installation on Ribbon Cable .....  | 7 |

| Supporting Platforms and Signal Charts .....                             | 7 |

| CSM-12C32 Module Platform: .....                                         | 8 |

| DEMO9S08RG60 Module Platform: .....                                      | 8 |

# MC13192U Transceiver Module

## User Guide

### Cautionary Notes:

- 1) Electrostatic Discharge (ESD) prevention measures should be applied whenever handling this product. ESD damage is not a warranty repair item.

- 2) Axiom Manufacturing reserves the right to make changes without further notice to any products to improve reliability, function or design. Axiom Manufacturing does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under patent rights or the rights of others.

- 3) EMC Information on the MC13192U Module:

- a) This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- 1) This device may not cause harmful interference, and

- 2) This device must accept any interference received, including interference that may cause undesired operation.

TX FCC ID# TFY1105AXM0361

- b) Changes or modifications to this unit not expressly approved by Axiom Manufacturing, could void the user's authority to operate this equipment under FCC or other regulatory agency rules.

- c) This product is designed and intended for use as an application platform for software development in an educational / professional laboratory. ~~Use as a communication device in end user equipment must follow the recommended application in this manual.~~

- d) In a domestic environment this product may cause radio interference in which case the user may be required to take adequate prevention measures.

- e) RF Exposure – This device exceeds the FCC requirements for RF exposure when the antenna used for this transmitter has a separation distance of at least 20cm from all persons and must not be co-located or operating in conjunction with any other antenna or transmitter.

### Terminology

This module applies option selection jumpers. Terminology for application of the option jumpers is as follows:

Jumper on, in, or installed = jumper is a plastic shunt that fits across 2 pins and the shunt is installed so that the 2 pins are connected with the shunt.

# MC13192U Transceiver Module

## User Guide

Jumper off, out, or idle = jumper or shunt is installed so that only 1 pin holds the shunt, no 2 pins are connected, or jumper is removed. It is recommended that the jumpers be placed idle by installing on 1 pin so they will not be lost.

Signal names in this document that are followed by an asterisk (\*) denote an active-low signal.

### Module Features

The MC13192U Transceiver module is a low cost demonstration or application module for the Freescale MC13192 Zigbee™ capable transceiver device. Module operation is controlled by any host microcontroller with a Serial Peripheral Interface (SPI) port. Interface connections are compatible with several Freescale microcontroller DEMO and EVB development boards. Development of applications for several microcontrollers is quick and easy with the included demonstration example software.

- ◆ MC13192 Transceiver

- \* SPI interface

- \* 2.4GHz RF operation

- \* Optional clock output 32KHz to 8MHz (JP2)

- ◆ 16Mhz reference Crystal

- ◆ On Board "F" antenna with TX/RX switch

- ◆ SMA test jack connection

- ◆ Regulated +3.0V power supply

- ◆ SPI Slave operation, 2 optional chip selects (JP1).

- ◆ J1 I/O connector standard, 2x12 R/A pins

MCU DEMO module or SLK series compatible

- ◆ J2\_GP PORT connector optional, 2x 15 R/A pins

M68EVB9S08GB60 board compatible

- ◆ Power ON Indicator

- ◆ Size: 2 x 2.1 inches with 2 x 4-40 size mounting holes

- ◆ +3.3V to +5.5V input supply on I/O connector

- ◆ I/O Level translation for 3.3 to 5V systems

- ◆ 60ma maximum with TX on.

- ◆ FCC registered when applied with provided software examples.

- ◆ Supplied in Module pairs with Documentation (CD),

User Manual, and SMAC example software

The MC13192U provides a low cost method to apply RF communication to any system. Supporting application software examples are available for Freescale Coldfire™, HC(S)12, and HCS08 targets. Modules are provided in pairs in the standard kit and are certified with the FCC for application in other systems.

Standard installation places module at 90 degrees vertical to controller or host platform. Versatile connection to host controller boards will allow stacking in different configurations or connection by ribbon cable, contact Axiom with special requirements. Module applies an embedded antenna and derives the 3.3V to 5.5V DC input power from the supporting host platform so no other accessories are required. Mounting holes are provided opposite from the connector to secure the module if required, 4-40 size nylon hardware should be applied for this purpose.

# MC13192U Transceiver Module

## User Guide

### Module Option Jumpers

#### *JP1 - Select Signal Option*

JP1 provides the Serial Peripheral Interface (SPI) device select signal option on the J1 connector. Two select signals maybe optioned incase the default connection is in use by another peripheral. The SMAC software example will need to be configured to apply the secondary signal. See the connection charts for the host controller to determine the signal applied.

**Position 1-2 (default):** Enables the host MCU SPI port SS\* signal or J1 pin 23 as the MC13192U select signal.

**Position 2-3:** Enables the host MCU secondary select signal or J1 pin 24 as the MC13192U select signal. See the connection charts to determine signal name applied for particular host MCU.

#### *JP2 – Clock-Out Enable Option*

JP2 enables the MC13192 device optional clock output signal to connector J2 pin 14. The clock output signal is not applied to the default application connector J1. See the MC13192 device user guide and the SMAC software example for configuration of the clock output signal if required.

### J1 Connector – Default Host I/O Connection

J1 is the default application interface connector and it provides all power, communication and status signals between the module and the host controller. Connector organization is for a compatible installation in the Freescale DEMO series or SLK series boards, and the Axiom CSM series. User should verify compatibility by referring to the MC13192U Host controller signal chart.

| Signal Name     | J1 Pin | Signal Name     |

|-----------------|--------|-----------------|

| VDD (3.3 - 5)   | 1      | 2               |

| GND (vss)       | 3      | 4               |

| x               | 5      | 6               |

| x               | 7      | 8               |

| IDLE (GPIO1)    | 9      | 10              |

| V_CRC (GPIO2)   | 11     | 12              |

| RESET_IN*       | 13     | 14              |

| ATTN_IN*        | 15     | 16              |

| SIN             | 17     | 18              |

| SOUT            | 19     | 20              |

| SCK             | 21     | 22              |

| (JP1 1-2) SEL1* | 23     | 24              |

|                 |        | SEL2* (JP1 2-3) |

Notes:

- 1) Signal names refer to the MC13192U operation.

- 2) The '\*' symbol indicates low active signal.

# MC13192U Transceiver Module

## User Guide

### J2 Connector

J2 is an alternate application interface connector provided for applications on the MC68EVB9S08GB60 development board GP Port connector or to replace the MC13192RFC module in application. This connector is not installed or applied in the standard kit, contact the factory for a module version to apply this connector.

| Signal Name  | MC13192U<br>J2 Pin |    | Signal Name     |

|--------------|--------------------|----|-----------------|

| ANTCTL       | 1                  | 2  | x               |

| IDLE (GPIO1) | 3                  | 4  | V_CRC (GPIO2)   |

| x            | 5                  | 6  | x               |

| x            | 7                  | 8  | x               |

| IRQ_OUT*     | 9                  | 10 | x               |

| x            | 11                 | 12 | x               |

| x            | 13                 | 14 | CLOCK OUT (JP2) |

| x            | 15                 | 16 | x               |

| x            | 17                 | 18 | x               |

| x            | 19                 | 20 | x               |

| RXTXEN       | 21                 | 22 | RESET_IN*       |

| x            | 23                 | 24 | ATTN_IN*        |

| SIN          | 25                 | 26 | SCK             |

| SEL*         | 27                 | 28 | SOUT            |

| VDD (3.3)    | 29                 | 30 | GND (vss)       |

Notes:

- 1) Signal names refer to the MC13192U operation.

- 2) The '\*' symbol indicates low active signal.

- 3) J2 will align with the bottom half of GP Port pins 11 – 40 on the MC68EVB9S08GB60 board.

### J104 – SMA Test Connector

J104 is provided for factory testing and verification. It is possible for the user to modify the MC13192U module to apply this connection for testing purposes or to apply an external antenna.

**Any modification to the module or application of an external antenna is prohibited. Any change to the module from factory standard will render the provided FCC registration void and possibly all other provided agency certifications void. The user must assume full responsibility for module operation and pursue the proper regulatory testing and agency registrations in this case!**

### Installation

The module applies the J1 connector, a 24 pin (2x12) right angle .1 inch space pin header, for connection to the host controlling platform by default. This connector is configured for compatibility with many Freescale DEMO series MCU boards or Axiom CSM series microcontroller application boards, and the MCUSLK Project Board. User should review the Supporting Platform section for standard connections to host controller platforms.

# MC13192U Transceiver Module

## User Guide

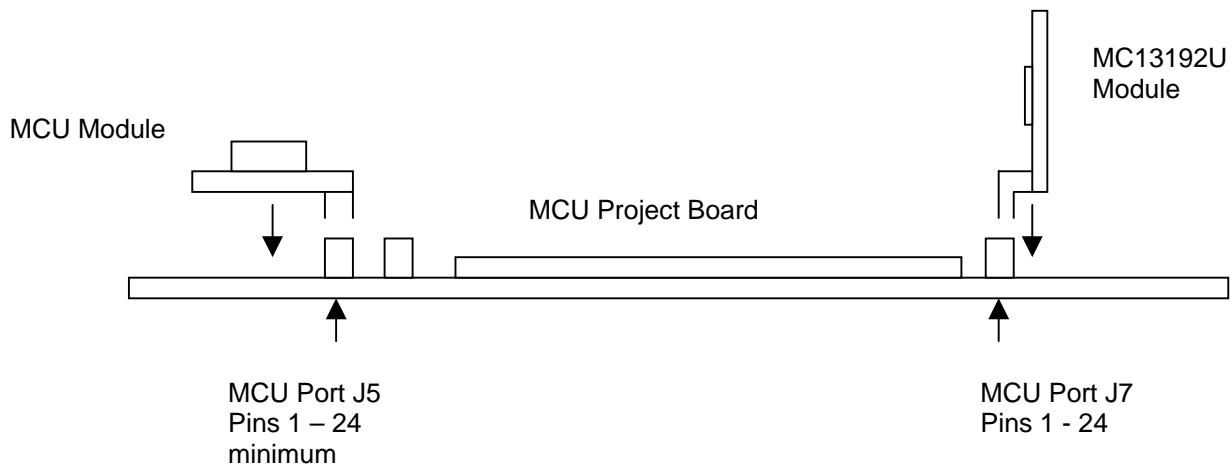

### ***MCU Project Board - Module Installation***

### ***Project Board Installation notes:***

- 1) MCU Project board MCU PORT connector J6 (next to J5) may also be applied to install the MC13192U module.

- 2) See the MCU Project board User Manual for correctly installing and powering the host microcontroller (MCU) module in Port J5.

- 3) The MC13192 module will input power from pins 1 and 3 of the mating connector, the MCU Project board or host MCU Module must be configured to provide this power supply to the module. See associated User Manuals for configuration details.

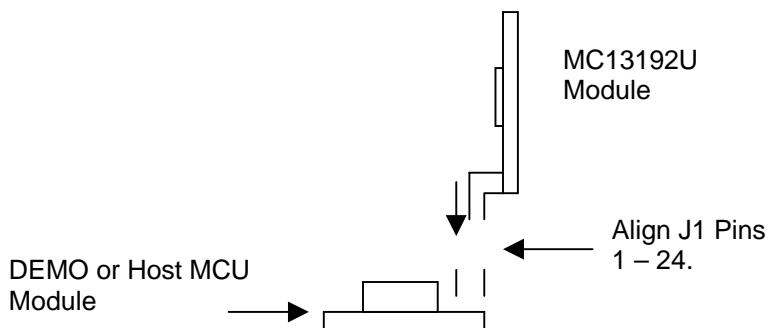

### ***CSM, DEMO or Host MCU Board - Module Installation on Socket Header***

### ***DEMO or Host MCU Board Installation notes:***

- 1) Host MCU board MCU Port and MC13192U Module J1 connectors align for pins 1 – 24.

- 2) The Host Board must be configured to supply regulated power on J1 pin 1 (+3.3V to +5.5V) and pin 3 (Ground).

- 3) Host board must apply the SMAC software package to operate the MC13192U module.

# MC13192U Transceiver Module

## User Guide

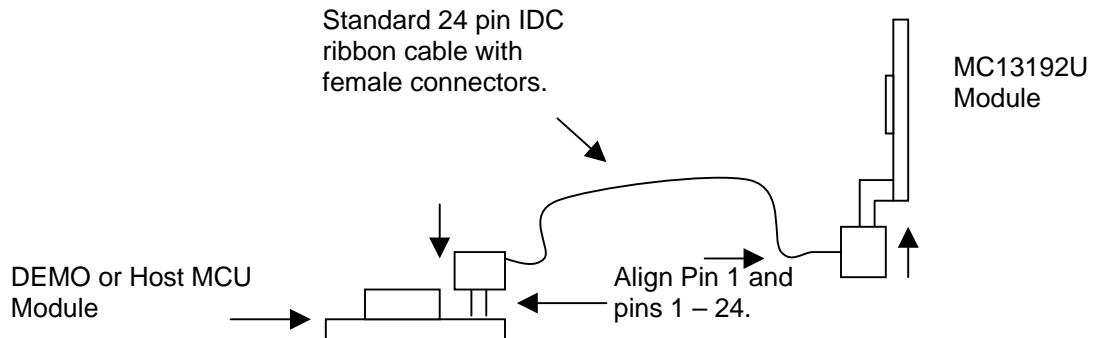

### *CSM, DEMO or Host MCU Board - Module Installation on Ribbon Cable*

#### **Ribbon Cable Installation notes:**

- 1) Host MCU board MCU Port and MC13192U Module J1 connectors align for pins 1 – 24 into and out of the ribbon cable.

- 2) The Host Board must be configured to supply regulated power on J1 pin 1 (+3.3V to +5.5V) and pin 3 (Ground).

- 3) Host board must apply the SMAC software package to operate the MC13192U module.

- 4) SPI interface bus clock should be reduced to 125KHz to compensate for cable loading of signals.

- 5) Use a pin header to convert socket style MCU Port on Demo boards to pin connector, example part number: Sullins #PTC36DACP cut to 24 pins, or Samtec #TSW-1-12-25-T-D

## **Supporting Platforms and Signal Charts**

The following charts provide reference for the MC13912U module and various host platform signal connections. The example platforms are supported by the SMAC version 4.2 or later example software. New platforms can be easily added by generating appropriate the connection I/O header file in the SMAC example software and applying operation with the standard interface signal names.

# MC13192U Transceiver Module

## User Guide

### ***CSM-12C32 Module Platform:***

| CSM12C32<br>I/O Signal | J1 Signal<br>Name | J1 Pin |    | J1 Signal<br>Name | CSM12C32<br>I/O Signal |

|------------------------|-------------------|--------|----|-------------------|------------------------|

| +VX                    | VDD (3.3 - 5)     | 1      | 2  | IRQ_OUT*          | PE1/IRQ*               |

| GND                    | GND (vss)         | 3      | 4  | x                 |                        |

|                        |                   | x      | 5  | 6                 | x                      |

|                        |                   | x      | 7  | 8                 | x                      |

| PP5/KWP5               | IDLE (GPIO1)      | 9      | 10 | x                 |                        |

| PE0/XIRQ*              | V_CRC<br>(GPIO2)  | 11     | 12 | x                 |                        |

| PT0                    | RESET_IN*         | 13     | 14 | x                 |                        |

| PT1                    | ATTN_IN*          | 15     | 16 | x                 |                        |

| PM4/MOSI               | SIN               | 17     | 18 | x                 |                        |

| PM2/MISO               | SOUT              | 19     | 20 | RXTXEN            | PAD1                   |

| PM5/SCK                | SCK               | 21     | 22 | ANTCTL            | PB4                    |

| PM3/SS*                | SEL1*             | 23     | 24 | SEL2*             | PA0                    |

### ***DEMO9S08RG60 Module Platform:***

| DEMO-<br>9S08RG60 I/O<br>Signal | J1 Signal<br>Name | J1 Pin |    | J1 Signal<br>Name | DEMO-<br>9S08RG60 I/O<br>Signal |

|---------------------------------|-------------------|--------|----|-------------------|---------------------------------|

| +V1                             | VDD (3.3 - 5)     | 1      | 2  | IRQ_OUT*          | PTD2/IRQ*                       |

| GND                             | GND (vss)         | 3      | 4  | x                 |                                 |

|                                 |                   | x      | 5  | 6                 | x                               |

|                                 |                   | x      | 7  | 8                 | x                               |

| PC0/KBI2P0                      | IDLE (GPIO1)      | 9      | 10 | x                 |                                 |

| PC1/KBI2P1                      | V_CRC<br>(GPIO2)  | 11     | 12 | x                 |                                 |

| PTD6/TPMCH0                     | RESET_IN*         | 13     | 14 | x                 |                                 |

| PTB7/TPMCH1                     | ATTN_IN*          | 15     | 16 | x                 |                                 |

| PTC4/MOSI                       | SIN               | 17     | 18 | x                 |                                 |

| PTC5/MISO                       | SOUT              | 19     | 20 | RXTXEN            | PTD5/ACMP+                      |

| PTC6/SPSCK                      | SCK               | 21     | 22 | ANTCTL            | PTA0/KBI1P0                     |

| PTC7/SS*                        | SEL1*             | 23     | 24 | SEL2*             | PTA1/KBI1P1                     |