## Features

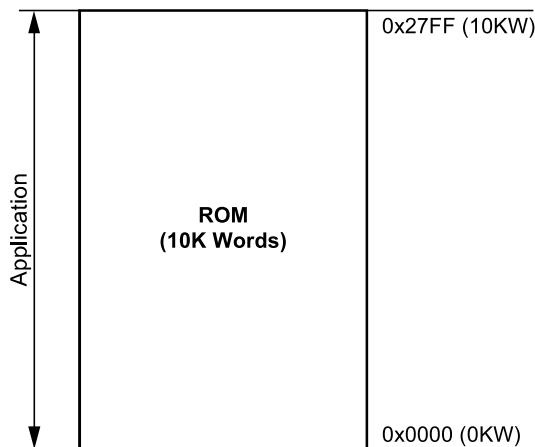

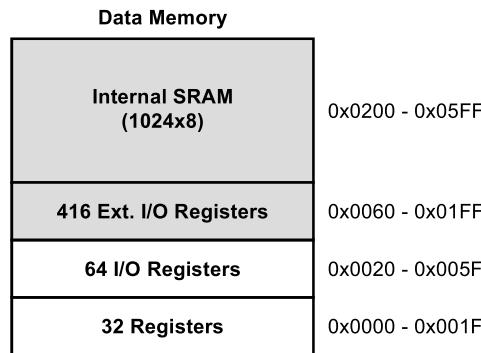

- AVR® microcontroller core with 1Kbyte SRAM and 24Kbyte RF library in firmware (ROM)

- Supported frequency ranges

- Low-Band 310MHz to 318MHz, 418MHz to 477MHz

- 315.00MHz/433.92MHz with one 24.305MHz crystal

- Low current consumption

- 9.8mA for RXMode (Low-Band), 1.2mA for 21ms cycle three-channel polling

- Typical OFFMode current of 5nA (maximum 600nA at Vs = 3.6V and T = 85°C)

- Input 1dB compression point

- -48dBm (full sensitivity level)

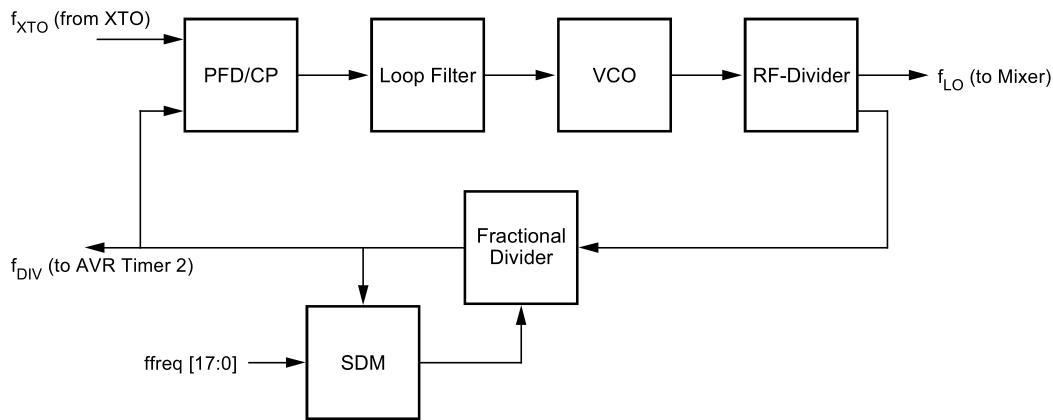

- Programmable channel frequency with fractional-N PLL

- 93Hz resolution for Low-Band

- FSK deviation  $\pm 0.375\text{kHz}$  to  $\pm 93\text{kHz}$

- FSK sensitivity (Manchester coded) at 433.92MHz

- -108.5dBm at 20Kbit/s       $\Delta f = \pm 20\text{kHz}$       BWIF = 165kHz

- -111dBm at 10Kbit/s       $\Delta f = \pm 10\text{kHz}$       BWIF = 165kHz

- -114dBm at 5Kbit/s       $\Delta f = \pm 5\text{kHz}$       BWIF = 165kHz

- -122.5dBm at 0.75Kbit/s       $\Delta f = \pm 0.75\text{kHz}$       BWIF = 25kHz

- ASK sensitivity (Manchester coded) at 433.92MHz

- -110.5dBm at 20Kbit/s      BWIF = 80kHz

- -125dBm at 0.5Kbit/s      BWIF = 25kHz

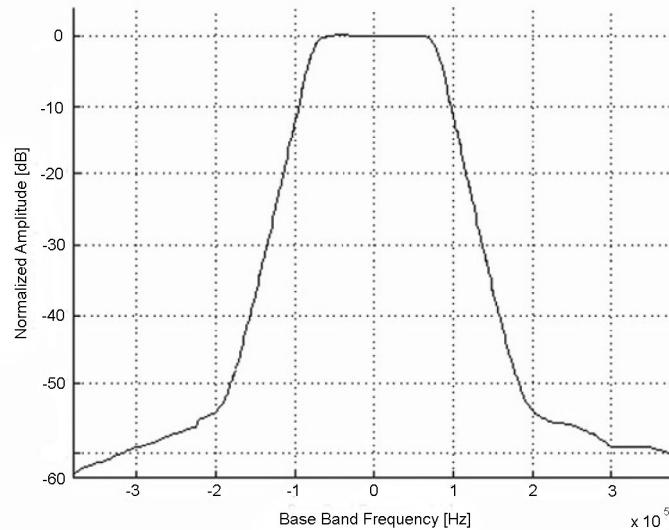

- Programmable Rx-IF bandwidth 25kHz to 366kHz (approximately 10% steps)

- Blocking (BWIF = 165kHz): 64dBc at frequency offset = 1MHz and 48dBc at 225kHz

- High image rejection: 55dB at 315MHz/433.92MHz without calibration

- Supported data rate in buffered mode 0.5Kbit/s to 80Kbit/s (120Kbit/s NRZ)

- Supports pattern-based wake-up and start of frame identification

- Flexible service configuration concept with on-the-fly (OTF) modification (in IDLEMode) of SRAM service parameters (data rate, ...)

- Two service configurations are located in SRAM and can be modified via SPI

- Digital RSSI with very high relative accuracy of  $\pm 1\text{dB}$  thanks to digitized IF processing

- Programmable clock output derived from crystal frequency

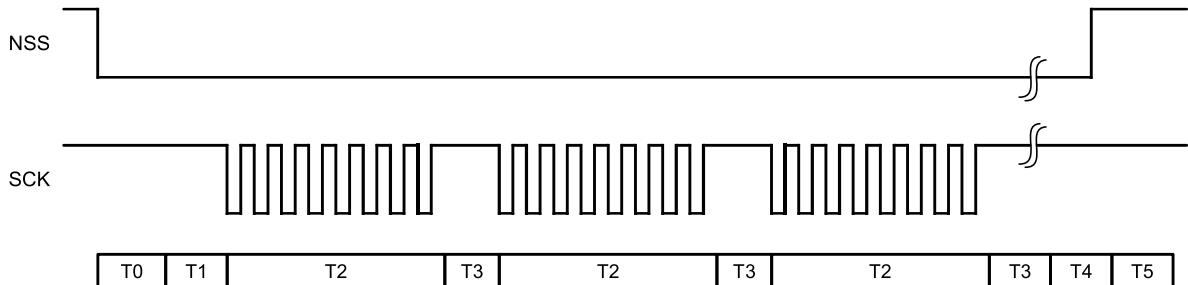

- SPI interface for Rx data access and receiver configuration

- 500Kbit SPI data rate for short periods on SPI bus and host controller

- Configurable EVENT signal indicates the status of the IC to an external microcontroller

- Automatic low-power channel polling with flexible configuration concerning timing, order and participating channels

- Fast reaction time

- Support of mixed ASK/FSK telegrams

- Non-byte aligned data reception

- Supply voltage ranges 1.9V to 5.5V

- Temperature range  $-40^\circ\text{C}$  to  $+105^\circ\text{C}$

- ESD protection at all pins ( $\pm 4\text{kV}$  HBM,  $\pm 200\text{V}$  MM,  $\pm 750\text{V}$  FCDM)

- Small 5×5mm QFN32 package/pitch 0.5mm

- Package and pin-to-pin compatibility with Atmel® ATA5780N and ATA5781/2/3

- Backward RF matching compatibility with Atmel ATA5780N and ATA5781/2/3 (RF redesign not needed)

- Suitable for applications governed by EN 300 220 and FCC part 15, title 47

# 1. General Product Description

## 1.1 Introduction

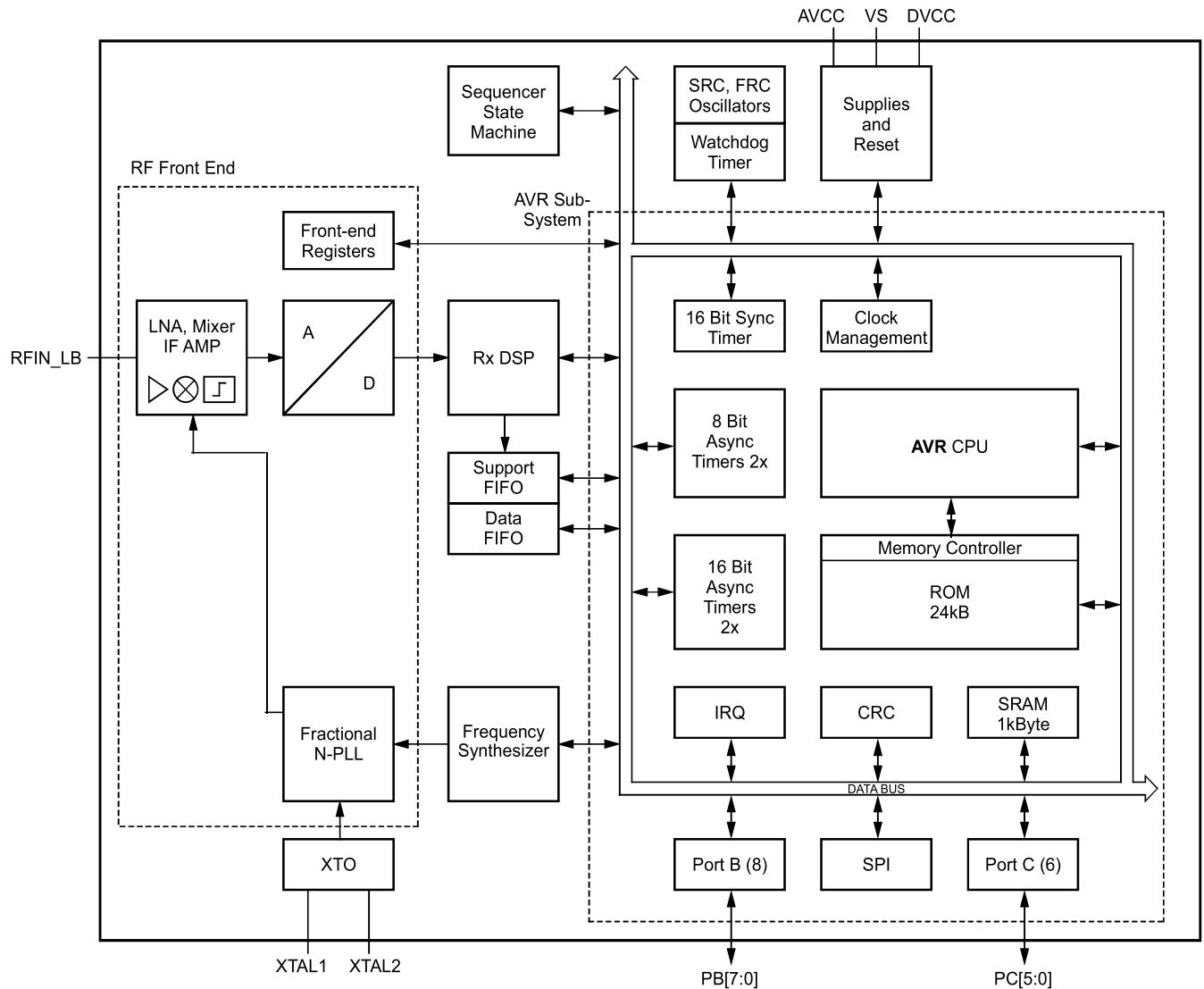

The Atmel® ATA5785 is a highly integrated, low-power UHF ASK/FSK RF receiver with an integrated AVR® microcontroller. It is package and pin-to-pin compatible with the previous generation of RF receivers (Atmel ATA5780N and ATA5781/2/3).

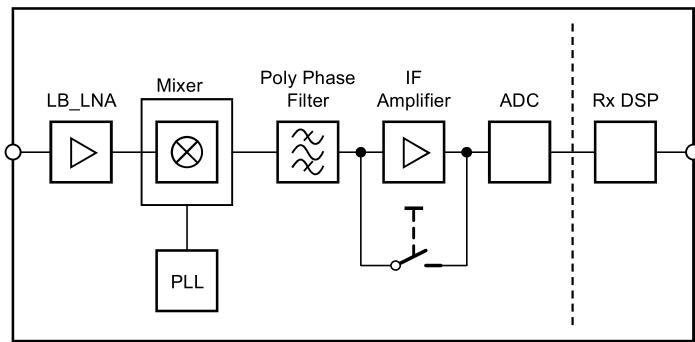

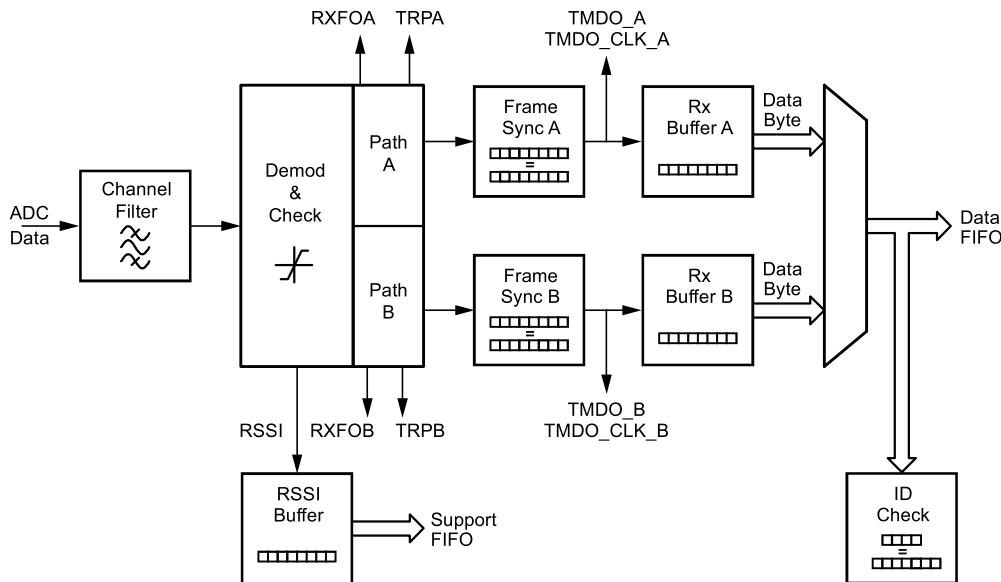

The Atmel ATA5785 is partitioned into three sections; an RF front end, a digital baseband and the low-power 8-bit AVR microcontroller. The product is designed for the ISM frequency bands in the ranges of 310MHz to 318MHz and 418MHz to 477MHz. The external part count is kept to a minimum due to the very high level of integration in this device. By combining outstanding RF performance with highly sophisticated baseband signal processing, robust wireless communication can be easily achieved. The receive path uses a low-IF architecture with an integrated double quadrature receiver and digitized IF processing. This results in high image rejection and excellent blocking performance. In addition, highly flexible and configurable baseband signal processing allows the receiver to operate in several scanning, wake-up and automatic self-polling scenarios. For example, during polling the IC can scan for specific message content (IDs) and save valid telegram data in the FIFO buffer for later retrieval. The device integrates two receive paths that enable a parallel search for two telegrams with different modulations, data rates, wake-up conditions, etc.

The Atmel ATA5785 implements a flexible service configuration concept and supports up to 6 channels. The channels are grouped into two service configurations with three channels each. The service configurations are located in the SRAM and allow on-the-fly modifications during IDLEMode via SPI commands. Highly configurable and autonomous scanning capability enables flexible polling scenarios with up to 15 channels. The SPI interface allows external control and device configuration.

## 1.2 Document Guide

### **Chapter 1 “General Product Description”**

Chapter 1 provides an initial overview of the functionality, features, and application areas of the Atmel® ATA5785. Pin descriptions are included in this chapter.

### **Chapter 2 “System Functional Description”**

Chapter 2 provides a functional description of the entire system. All features, operating modes, and configuration options are described. This chapter will interest

- Standard users who want to gain a functional understanding of the IC

- Users who want set up a configuration for a specific application

- Users who want to use the built-in firmware library by controlling the IC via the SPI interface

### **Chapter 3 “Hardware”**

Chapter 3 provides a detailed description of the Atmel ATA5785 hardware. Every hardware block is described including all registers. This chapter will interest

- Advanced users who want to gain a deep understanding of the IC

- Users who want to manipulate internal hardware settings during operation to achieve customized behavior of the IC

### **Chapter 4 “Application”**

Chapter 4 covers the application board design and general information on Rx-Tx system design. The chapter includes examples and will interest

- Application engineers

- System engineers who design the overall Rx-Tx link of the transmission system

### **Chapter 5 “Electrical Characteristics”**

Chapter 5 lists all parameters of the Atmel ATA5785 including absolute maximum ratings, supply voltages, current consumption, and RF characteristics.

### **Chapter 6 “Timing Characteristics”**

Chapter 6 contains sample timing values for start-up of operating modes and switch between operating modes.

### **Chapter 7 “Appendix”**

The Appendix contains a list of abbreviations, SPI commands, and tables with various memory maps. The chapter is intended to be a quick reference guide for commands, variables, and registers.

### **Chapter 8 “Ordering Information”**

Chapter 8 provides the order numbers for the Atmel ATA5785.

### **Chapter 9 “Package Information”**

Chapter 9 shows the precise dimensions of the Atmel ATA5785 package. This information is useful for the application board design.

### **Chapter 10 “Revision History”**

Chapter 10 contains the version history and change notes of all releases of this document.

### **Chapter 11 “Table of Contents”**

Chapter 11 shows an outline of this document down to the third heading level. A complete bookmark list with all heading levels is included in the PDF version of this document.

## 1.3 System Overview

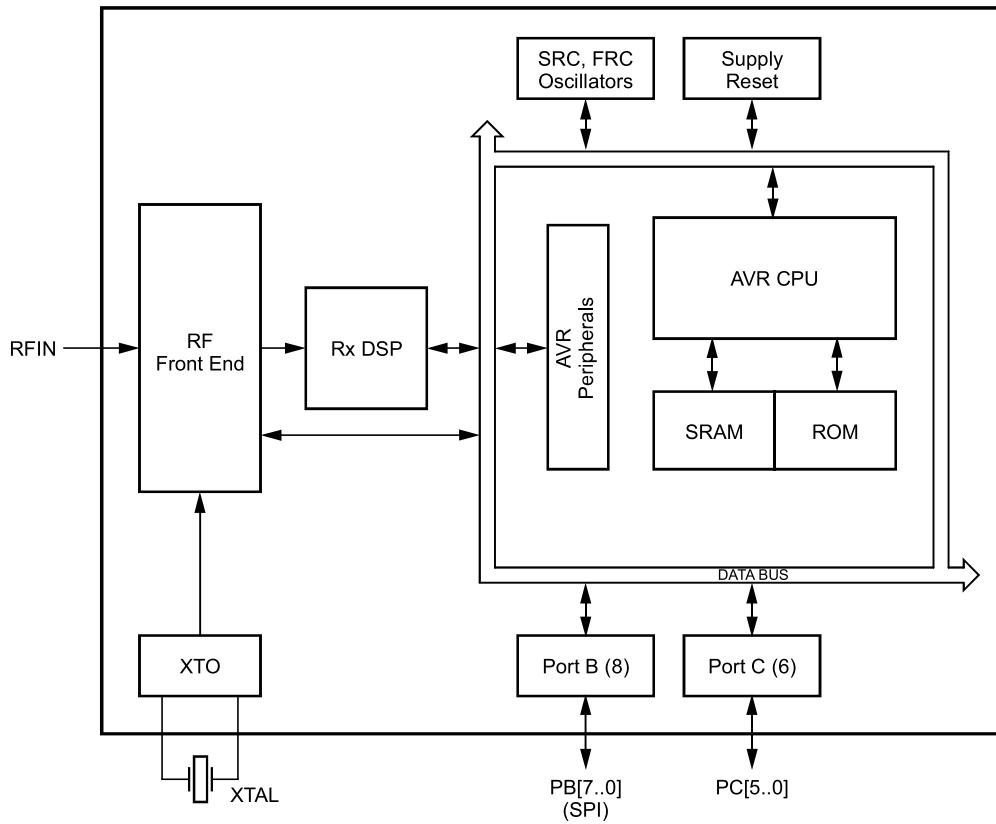

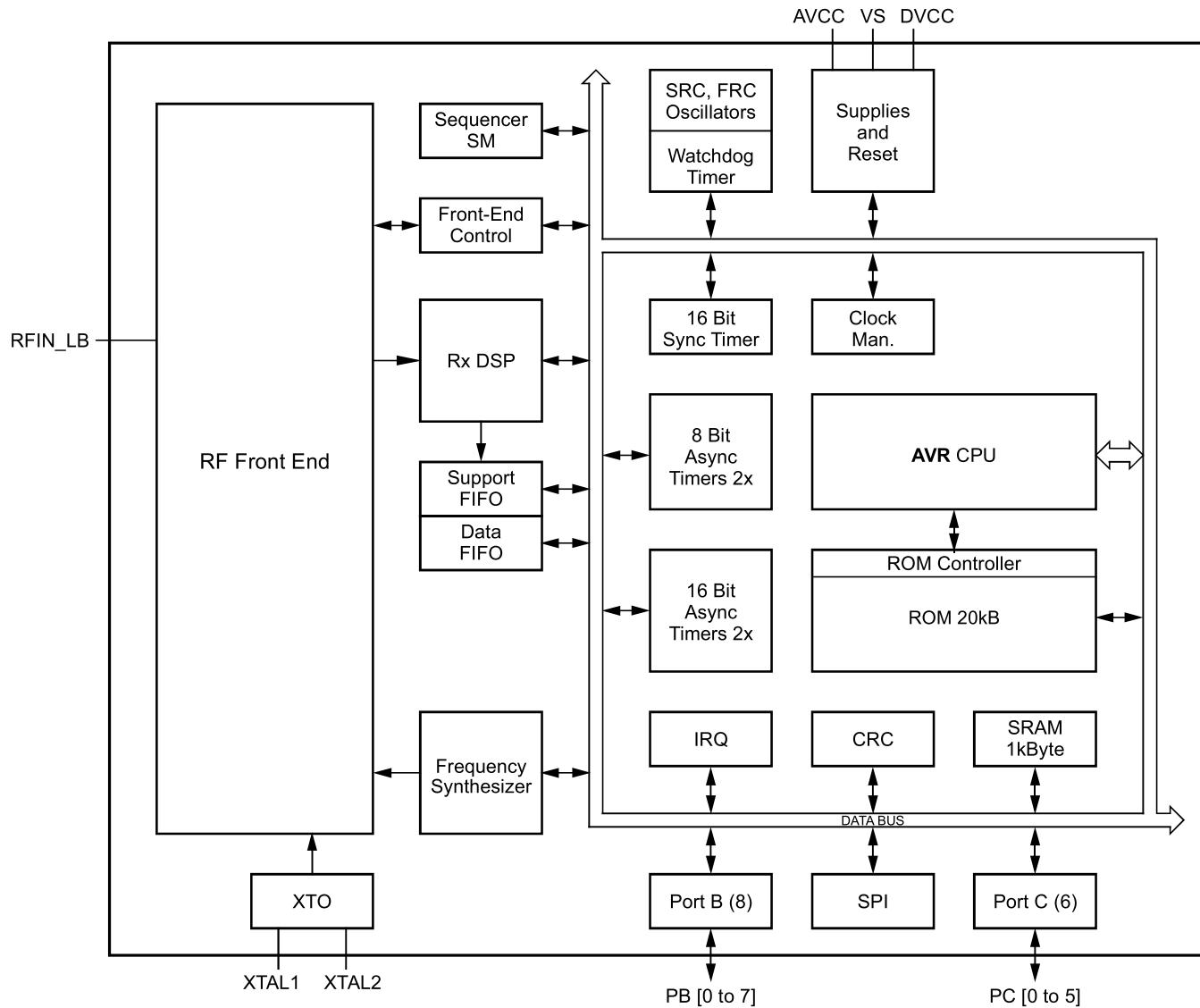

Figure 1-1. Circuit Overview

Figure 1-1 on page 5 shows an overview of the main functional blocks of the Atmel® ATA5785. External configuration and control of the Atmel ATA5785 is performed through the SPI pins SCK, MOSI, MISO, and NSS on port B. A large portion of the functionality is defined by the firmware located in the ROM and processed by the AVR®. The service configuration is written to the SRAM via SPI after power-on by an external host microcontroller. A subsequent SPI command can trigger the AVR to configure the hardware according to these settings and start up a given system mode (e.g., RXMode, or PollingMode). Internal events such as “Start of Telegram” or “FIFO empty” are signaled to the external microcontroller on pin 28 (PB6/EVENT).

It is important to note that all PWRON and NPWRON pins (PC1..5, PB4, PB7) are active in OFFMode. This means that even if the Atmel ATA5785 is in OFFMode and the DVCC voltage is switched off, the power management circuitry within the Atmel ATA5785 biases these pins with VS.

AVR ports can be used as button inputs, external LNA supply voltage (RX\_ACTIVE), LED drivers, EVENT pin, general purpose digital inputs, or wake-up inputs, etc.

## 1.4 Pinning

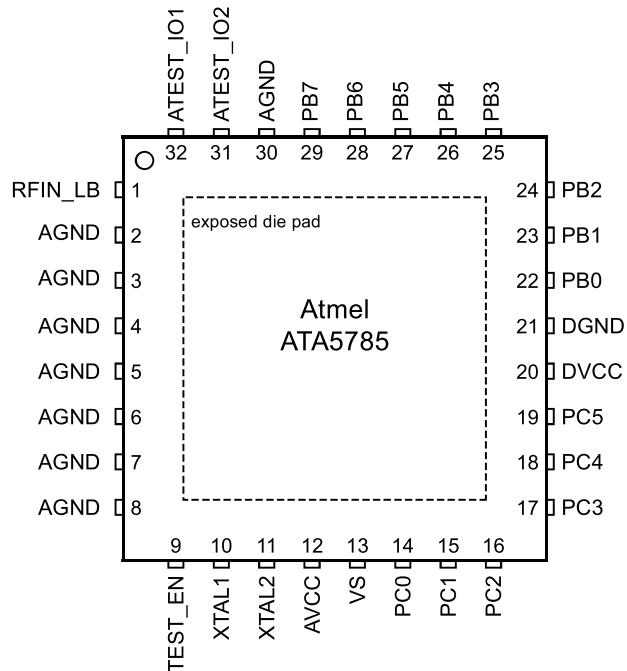

Figure 1-2. Pin Diagram

Note: The exposed die pad is connected to the internal die.

Table 1-1. Pin Description

| Pin No. | Pin Name | Type   | Equivalent Circuit | Description                                       |

|---------|----------|--------|--------------------|---------------------------------------------------|

| 1       | RFIN_LB  | Analog |                    | LNA input for Low-Band frequency range (< 500MHz) |

| 2-8     | AGND     | —      |                    | Connect to GND in application                     |

| 9       | TEST_EN  | —      |                    | Test enable, connected to GND in application      |

**Table 1-1. Pin Description (Continued)**

| Pin No. | Pin Name | Type    | Equivalent Circuit                                                                | Description                       |                                                                                   |

|---------|----------|---------|-----------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------|

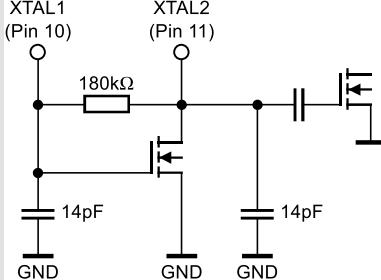

| 10      | XTAL1    | Analog  |                                                                                   |                                   | Crystal oscillator pin 1 (input)                                                  |

| 11      | XTAL2    | Analog  |  | Crystal oscillator pin 2 (output) |                                                                                   |

| 12      | AVCC     | Analog  |                                                                                   |                                   | RF front end supply regulator output                                              |

| 13      | VS       | Analog  |                                                                                   |                                   | Main supply voltage input                                                         |

| 14      | PC0      | Digital |                                                                                   |                                   | Main : AVR Port C0<br>Alternate : PCINT8 / NRESET                                 |

| 15      | PC1      | Digital |                                                                                   |                                   | Main : AVR Port C1<br>Alternate : NPWRON1 / PCINT9 / EXT_CLK                      |

| 16      | PC2      | Digital |                                                                                   |                                   | Main : AVR Port C2<br>Alternate : NPWRON2 / PCINT10 / TRPA                        |

| 17      | PC3      | Digital |                                                                                   |                                   | Main : AVR Port C3<br>Alternate : NPWRON3 / PCINT11 / TMDO                        |

| 18      | PC4      | Digital |                                                                                   |                                   | Main : AVR Port C4<br>Alternate : NPWRON4 / PCINT12 / INTO                        |

| 19      | PC5      | Digital |                                                                                   |                                   | Main : AVR Port C5<br>Alternate : NPWRON5 / PCINT13 / TRPB / TMDO_CLK             |

| 20      | DVCC     | —       |                                                                                   |                                   | Digital supply voltage regulator output                                           |

| 21      | DGND     | —       |                                                                                   |                                   | Digital ground                                                                    |

| 22      | PB0      | Digital |                                                                                   |                                   | Main : AVR Port B0<br>Alternate : PCINT0 / CLK_OUT                                |

| 23      | PB1      | Digital |                                                                                   |                                   | Main : AVR Port B1<br>Alternate : PCINT1 / SCK                                    |

| 24      | PB2      | Digital |                                                                                   |                                   | Main : AVR Port B2<br>Alternate : PCINT2 / MOSI (SPI Master Out Slave In)         |

| 25      | PB3      | Digital |                                                                                   |                                   | Main : AVR Port B3<br>Alternate : PCINT3 / MISO (SPI Master In Slave Out)         |

| 26      | PB4      | Digital |                                                                                   |                                   | Main : AVR Port B4<br>Alternate : PWRON / PCINT4 / LED1 (strong high side driver) |

**Table 1-1. Pin Description (Continued)**

| Pin No. | Pin Name  | Type    | Equivalent Circuit | Description                                             |                                                                                        |

|---------|-----------|---------|--------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------|

| 27      | PB5       | Digital |                    | Main                                                    | : AVR Port B5                                                                          |

|         |           |         |                    | Alternate                                               | : PCINT5 / INT1 / NSS                                                                  |

| 28      | PB6       | Digital |                    | Main                                                    | : AVR Port B6                                                                          |

|         |           |         |                    | Alternate                                               | : PCINT6 / EVENT (firmware controlled external microcontroller event flag)             |

| 29      | PB7       | Digital |                    | Main                                                    | : AVR Port B7                                                                          |

|         |           |         |                    | Alternate                                               | : NPWRON6/ PCINT7/ RX_ACTIVE (strong high side driver) / LED0 (strong low side driver) |

| 30      | AGND      | –       |                    | Analog ground                                           |                                                                                        |

| 31      | ATEST_IO2 | –       |                    | RF front end test I/O 2 connected to GND in application |                                                                                        |

| 32      | ATEST_IO1 | –       |                    | RF front end test I/O 1 connected to GND in application |                                                                                        |

|         | GND       | –       |                    | Ground/backplane on exposed die pad                     |                                                                                        |

## 1.5 Typical Applications

The receiver is designed to be used in the following application areas:

- Remote keyless entry system (RKE)

- Passive entry go system (PEG)

- Tire pressure monitoring system (TPM, TPMS)

- Remote start system (RS)

- Remote control systems, e.g., garage door openers

- Smart RF applications

- Telemetering systems

### 1.5.1 Typical 5V Application Circuit with External Microcontroller

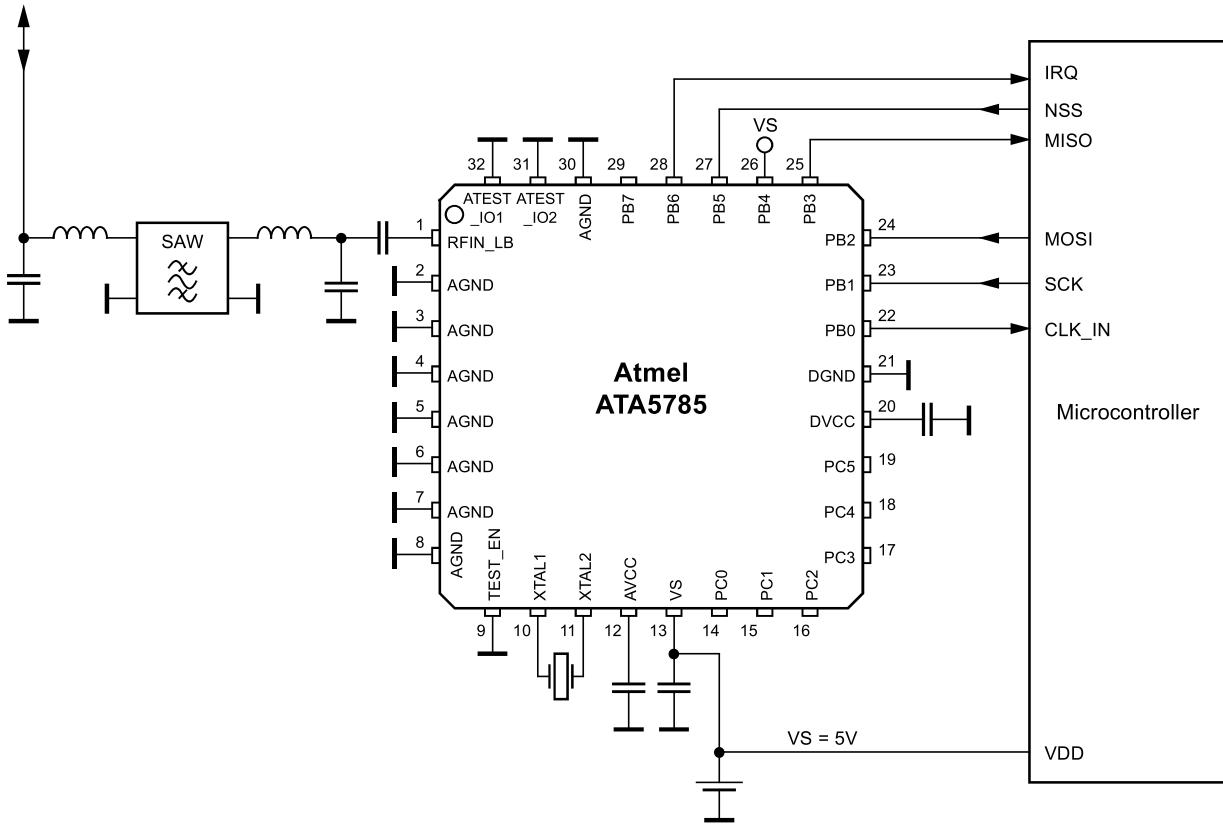

Figure 1-3. Typical 5V Application Circuit with External Microcontroller

Figure 1-3 shows a typical vehicle side application circuit with an external host microcontroller running from a 5V voltage regulator. The pin PB4 (PWRON) is directly connected to VS and the Atmel® ATA5785 enters the IDLEMode after power-on. In this configuration the Atmel ATA5785 can work autonomously and the µC stays powered down to keep current consumption low while remaining sensitive to RF telegrams and SPI communication.

To achieve a low current in IDLEMode the Atmel ATA5785 can be configured to work with the RC oscillator. The Atmel ATA5785 can also be configured for autonomous multi-channel and multi-application PollingMode. The external µC is notified by an event on pin 28 (EVENT) if an appropriate RF message is received. Until this event, the Atmel ATA5785 periodically switches to RXMode, checks the configured services and channels, and returns to power-down while the external host microcontroller is still in deep sleep mode to keep average current low. Once a valid RF message is detected, it can be buffered inside of the Atmel ATA5785 to enable a µC wake-up and retrieval of buffered data.

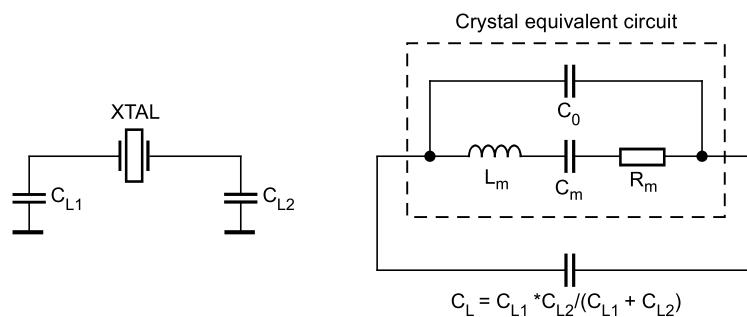

The impedance of the SAW filter is transformed with LC matching circuits to the RFIN\_LB port and also to the antenna. An external crystal, together with the fractional-N PLL within the Atmel ATA5785 is used to fix the RX frequency. Accurate load capacitors for this crystal are integrated, to reduce system part count and cost. Only three supply blocking capacitors are needed to decouple the different supply voltages AVCC, DVCC and VS of the Atmel ATA5785. The exposed die pad is the RF and analog ground of the Atmel ATA5785. It is directly connected to AGND via a fused lead. The Atmel ATA5785 is controlled using specific SPI commands via the SPI interface for application specific configuration.

## 2. System Functional Description

### 2.1 Overview

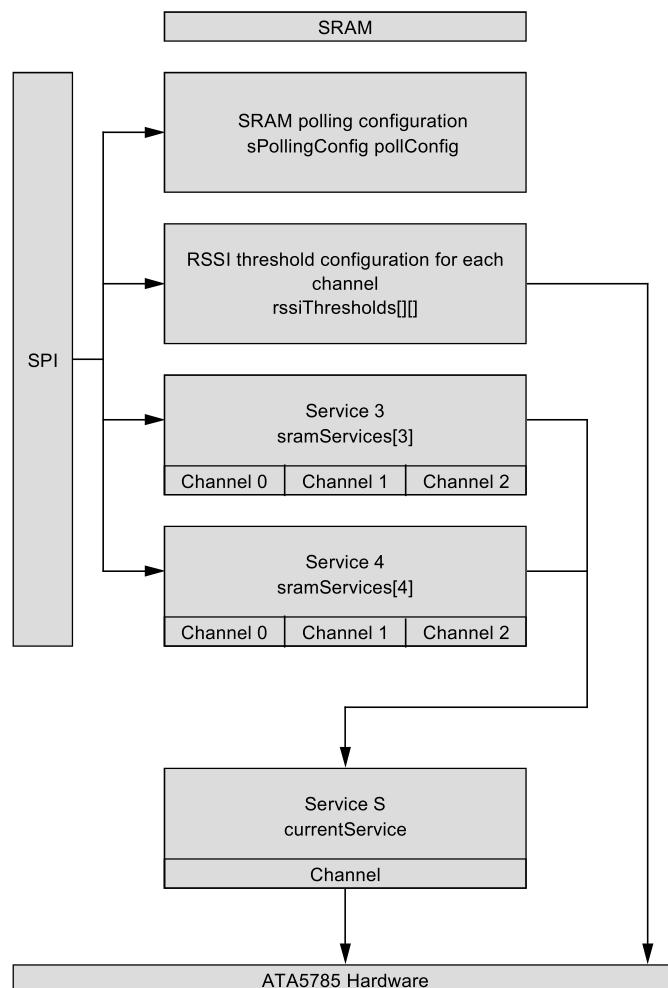

#### 2.1.1 Service-based Concept

The Atmel® ATA5785 is a highly configurable UHF receiver. General chip-wide settings and service configurations must be written via SPI to the internal SRAM and hardware registers after system initialization. During start-up of a receive mode the specific settings are loaded to the current service in the SRAM and from there to the corresponding hardware registers by the firmware.

A complete configuration set of the receiver is called “service” and includes RF settings, demodulation settings, and telegram handling information. Each service contains three channels which differ in the RF receive frequencies.

The Atmel ATA5785 supports two services which can be configured in various ways to meet customer requirements.

The service configurations are located in the SRAM space and can be modified by an SPI command during IDLEMode.

A service consists of

- One service-specific configuration part

- Three channel-specific configuration parts

Further configurations for PollingMode and RSSI are available and can be also modified in IDLEMode via SPI commands.

Figure 2-1 on page 10 gives an overview on the service based-concept.

**Figure 2-1. Service-based Concept Overview**

## 2.1.2 Supported Telegrams

### 2.1.2.1 Telegram Structure

The Atmel® ATA5785 supports the reception of a wide variety of telegrams and protocols. Generally no special structure is required from a telegram to be received by the Atmel ATA5785. However, designated hardware and software features are built in for the blocks that are depicted in Figure 2-2. Using this structure or parts of it can increase the sensitivity and robustness of the broadcast.

Figure 2-2. Telegram Structure

| Desync | Preamble | Data Payload | Checksum | Stop Sequence |

|--------|----------|--------------|----------|---------------|

|--------|----------|--------------|----------|---------------|

#### Desync:

The de-synchronization is usually a coding violation with a length of several symbols that should provoke a defined restart of the receiver. The use of a de-synchronization leads to more deterministic receiver behavior, reducing the required preamble length. This can be favorable in timing-critical and energy-critical applications.

#### Preamble:

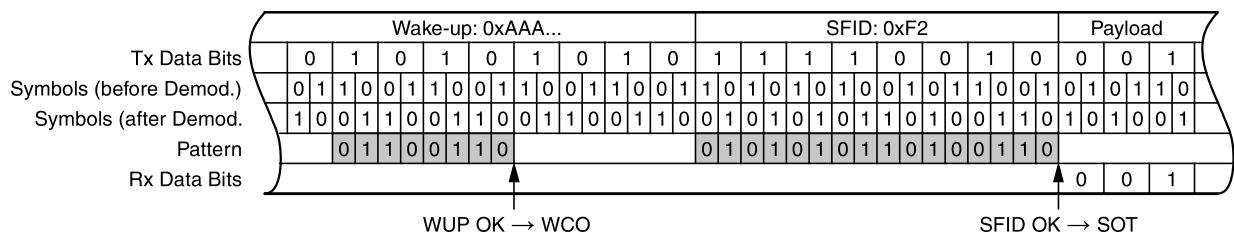

The preamble is a pattern that is sent before the actual data payload to synchronize the receiver and provide the starting point of the payload. A very regular pattern (e.g., 1-0-1-0...) is recommended for synchronization (“wake-up pattern, WUP”, sometimes also called “pre-burst”) while a unique, well-defined pattern of up to 32 symbols is required to mark the start of the data payload (“start frame identifier, SFID” or “start bit”). In polling scenarios the WUP can be tens or hundreds of ms long.

#### Data Payload:

The data payload contains the actual information content of the telegram. It can be NRZ or Manchester-coded. The length of the payload is application dependent, typically 1..64 bytes.

#### Checksum:

A checksum can be calculated across the data payload to verify that the data have been received correctly. A typical example is an 8-bit CRC checksum. Data bits at the beginning of the payload can be excluded from the CRC calculation.

#### Stop Sequence:

The stop sequence is a short data pattern (typically 2 to 6 symbols) to mark the end of the telegram. A coding violation can be used to prevent additional (non-deterministic) data from being received.

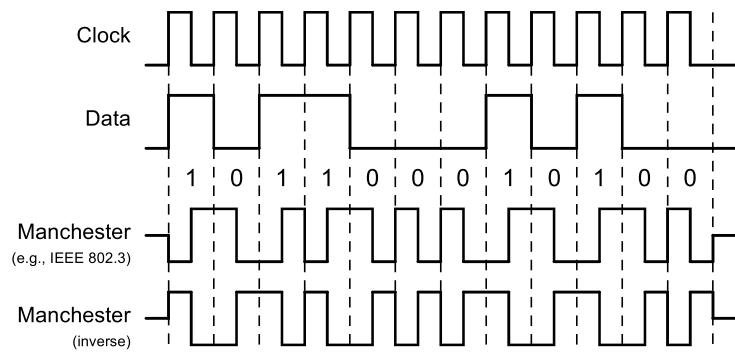

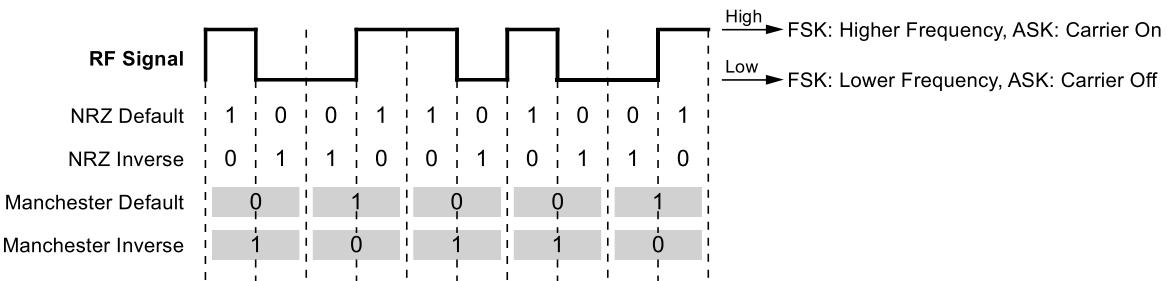

### 2.1.2.2 NRZ and Manchester Coding

Within this document the following wording is used:

The expression data “bit” describes the real information content that is to be broadcast. This information can be coded in “symbols” (sometimes also called “chips” or “bauds”) which are then physically transmitted from sender to receiver. The receiver has to decode the “symbols” back into data “bits” to access the information. The “symbol rate” is therefore always greater or equal to the “bit rate”.

The Atmel ATA5785 supports two coding modes: Manchester coding and non-return-to-zero (NRZ) coding.

NRZ coding is implemented in a straightforward manner: One bit is represented by one symbol.

Manchester coding implements two symbols per data bit. There is always a transition between the two symbols of one data bit so that one data bit always consists of a “0” and a “1”. The polarity can be either way as shown in Figure 2-3 on page 12.

**Figure 2-3. Manchester Code**

Manchester coding has many advantages such as simple clock recovery, no DC component, and error detection by code violation. Drawbacks are the coding/decoding effort and the increased symbol rate which is twice the data rate.

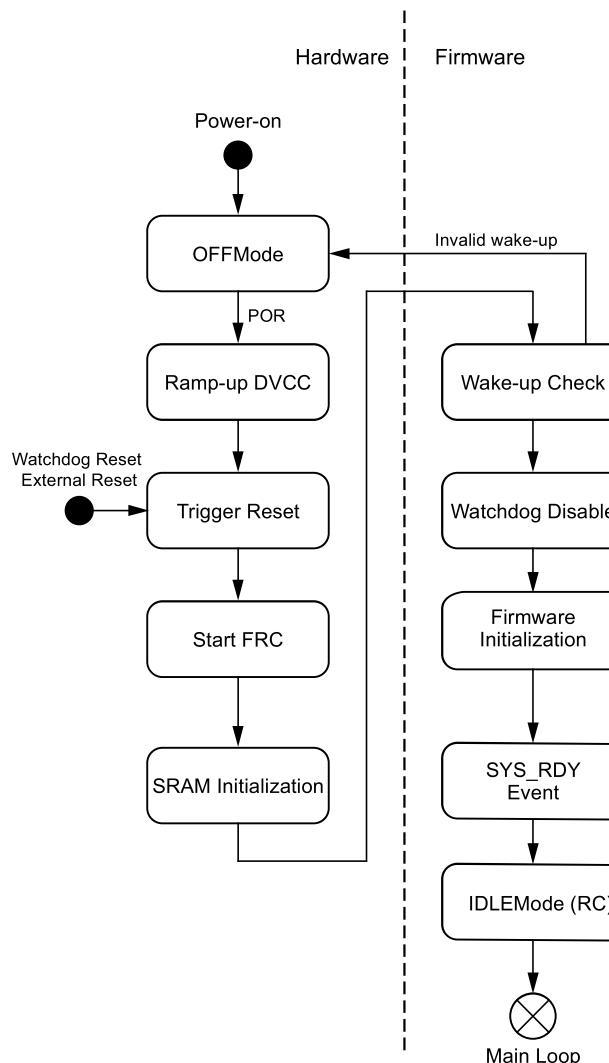

## 2.2 System Start-up

Figure 2-4 shows the system start-up flow, consisting of hardware and firmware initialization, after power-on.

**Figure 2-4. System Start-up**

After connecting the supply voltage to the VS pin, the Atmel® ATA5785 always starts in OFFMode. All internal circuits are disconnected from the power supply. The Atmel ATA5785 can be woken up by one of the following power-on reset (POR) events:

- Setting the PWRON pin to HIGH

- Setting one of the NPWRON1..6 pins to LOW

For more information on the OFFMode refer to Section 2.6 “OFFMode” on page 18. A POR enables the DVCC regulator. The FRC oscillator is started when the DVCC voltage reaches the operating voltage. At the same time the internal AVR® reset is triggered. After reaching stable operation conditions the FRC provides the clock for the hardware initialization state machine. The initialization state machine resets the SRAM content to “0x00”. The internal AVR reset is released when the hardware initialization is done. The system is now controlled by the firmware.

The firmware steps through the following tasks:

- Check for a correct wake-up condition. This is done by reading the pin registers (PINB and PINC) to identify the wake-up source. If a correct wake-up is detected, the wake-up source is signalled as an event. If no wake-up source is detected the wake-up is considered as invalid and the ATA5785 is switched back to OFFMode. Reset sources like watchdog reset, external reset or brown-out reset are not checked. This implies that the chip goes to OFFMode if, e.g., a watchdog reset occurred and no (N) PWRON pin is triggered.

- Disable the watchdog timer to avoid repeated watchdog resets

- Set EVENT pin (pin 28/PB6) to low to signal system ready event to the external host.

The operating mode after system start is the IDLEMode (RC). The firmware is executing the main loop.

The system is now ready to receive the configuration and service data via SPI.

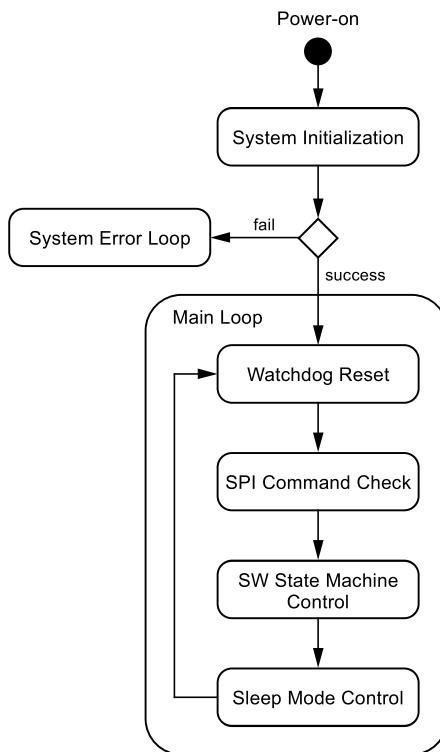

## 2.3 Main Loop

The main loop is executed periodically after successful system start-up. As shown in Figure 2-5, the main loop executes the following steps:

- Resetting the watchdog timer if activated

- Checking for external requests from SPI interface and configuration of the software state machines

- Controlling the software state machines during switch to operating modes

- Checking for the sleep mode conditions and entering sleep mode if necessary

A main loop cycle takes approximately 25µs at a standard FRC clock.

**Figure 2-5. Main Loop Flow**

## 2.4 System Configuration

### 2.4.1 Clock Configuration

If they are not used by at least one module, the FRC and SRC oscillators are automatically switched off by default. This mechanism can be deactivated, if required. The oscillators are then running permanently, which can decrease the start-up time from sleep mode. The feature can be activated by the FRC always on (FRCAO) and SRC always on (SRCAO) bits in the systemConfig SRAM variable. For more information, see Section 2.12.4.1 “systemConfig” on page 67.

| Address | Name         | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                    | Bit 2                    | Bit 1                       | Bit 0 |

|---------|--------------|-------|-------|-------|-------|--------------------------|--------------------------|-----------------------------|-------|

| 0x02E5  | systemConfig | -     | -     | SRCAO | FRCAO | SFIFO_OFL_UFL_RX_disable | DFIFO_OFL_UFL_RX_disable | Current idle mode selection | -     |

A system clock can be output on the CLK\_OUT pin. Available clock sources are SRC, FRC and XTO. The clock divider must be configured to result in an output clock of less than 4.5MHz (see parameter no. 15.90 in Section 5. “Electrical Characteristics” on page 300). The external clock output can be configured and activated in the CLKOCR and CLKOD hardware registers with the SPI command “Write SRAM/Register”, the following sequence shall be used:

- Disable clock output (CLKOCR.CLKOEN=0)

- Write clock output divider (CLKOD) and source select (CLKOCR.CLKOS[1:0])

- Enable clock output (CLKOCR.CLKOEN=1)

For more information, see Section 3.8.4 “System Clock and Clock Options” on page 201.

| Address | Name   | Bit 7      | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1      | Bit 0 |

|---------|--------|------------|-------|-------|-------|-------|--------|------------|-------|

| 0x00C4  | CLKOCR | -          | -     | -     | -     | -     | CLKOEN | CLKOS[1:0] |       |

| 0x00C3  | CLKOD  | CLKOD[7:0] |       |       |       |       |        |            |       |

Note: If the clock output is enabled, the I/O port configuration of pin PB0 must be set to output

## 2.4.2 AVR Sleep Mode Configuration

The AVR® has an integrated sleep mode to reduce power consumption during inactive periods (e.g., the sleep period of a polling cycle). The firmware controlled sleep mode feature can be configured in the SRAM variable sleepModeConfig. One of four different sleep modes can be selected. After start-up the sleep mode IDLE is active. For more information, see Section 3.8.5 “Sleep Modes and Active Power Reduction” on page 210.

| Address | Name          | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 |

|---------|---------------|-----------|-------|-------|-------|---------|-------|-------|-------|

| 0x02EB  | sleepModeConf | SLEEP_ENA | -     | -     | -     | SM[2:0] |       | -     |       |

## 2.4.3 Watchdog Configuration

The Atmel® ATA5785 integrates a watchdog timer that prevents the system from stalling. The time-out period can be configured in eight steps between 1ms and 268s. The reference clock for the watchdog timer is the SRC; therefore the watchdog timer also works in all sleep modes.

If enabled, the watchdog timer has to be reset by a watchdog reset (WDR) AVR instruction before a time-out occurs. Otherwise a full system reset is triggered. The WDR is done by the firmware during the main loop. Due to the fact that in PollingMode the main loop has a low priority, the time-out value of the watchdog should be at least twice as long as the active period in PollingMode. If PollingMode is configured with an AVR sleep mode, the WDR is disabled during the sleep period. As a result, the time-out value of the watchdog must be set longer than the sleep period in PollingMode. If the system runs in a receive mode, the WDR is not executed as long as the system is waiting for wake check ok (WCO) signalization and the time-out value of the watchdog has to be set longer than the maximum demodulator/WCO time-out.

The watchdog is disabled after system start-up. It can be enabled by the SPI command “Set Watchdog”, see Section 7.4 “SPI Command Reference” on page 345.

A detailed description of the watchdog timer hardware IP is given in Section 3.8.7.1 “Timer0 – Watchdog/Interval Timer” on page 233.

## 2.4.4 IO Port Configuration

The initial start-up configuration of port B and port C is done according to Table 2-1.

**Table 2-1. I/O Port Configuration after System Start-up**

| Pin                                 | Definition      |

|-------------------------------------|-----------------|

| Pin14/PC0 (NRESET)                  | Input pull-up   |

| Pin15/PC1 (NPWRON1)                 | Input pull-up   |

| Pin16/PC2 (NPWRON2, TRPA)           | Output low      |

| Pin17/PC3 (NPWRON3, TMDO)           | Output low      |

| Pin18/PC4 (NPWRON4)                 | Input pull-up   |

| Pin19/PC5 (NPWRON5, TRPB, TMDO_CLK) | Output low      |

| Pin22/PB0 (CLK_OUT)                 | Output low      |

| Pin23/PB1 (SCK)                     | Input tri-state |

| Pin24/PB2 (MOSI)                    | Input tri-state |

| Pin25/PB3 (MISO)                    | Output high     |

| Pin26/PB4 (PWRON)                   | Input tri-state |

| Pin27/PB5 (NSS)                     | Input tri-state |

| Pin28/PB6 (EVENT)                   | Output high     |

| Pin29/PB7 (NPWRON6, RX_ACTIVE)      | Output low      |

The port settings can be changed by SPI access to the corresponding hardware registers.

This implies

- Definition of the data direction of each digital I/O pin (input/output)

- Definition of the output value (high/low) if a pin is defined as output

- Enabling/disabling of a pull-up resistor if a pin is defined as input

- Enabling/disabling of the high/low side drivers on PB7 and the high side driver on PB4

- Pin change interrupt configuration

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4       | Bit 3     | Bit 2 | Bit 1 | Bit 0     |

|---------|--------|-------|-------|-------|-------------|-----------|-------|-------|-----------|

| 0x0006  | DDRB   |       |       |       |             | DDRB[7:0] |       |       |           |

| 0x0009  | DDRC   |       |       |       |             | DDRC[7:0] |       |       |           |

| 0x000E  | MCUCR  | PB7HS | PB7LS | PB4HS | PUD         | ENPS      | SPIIO | IVSEL | IVCE      |

| 0x0026  | PCICR  | -     | -     | -     | -           | -         | -     | -     | PCIE[1:0] |

| 0x006C  | PCMSK0 |       |       |       | PCMSK0[7:0] |           |       |       |           |

| 0x006D  | PCMSK1 |       |       |       | PCMSK1[7:0] |           |       |       |           |

| 0x0007  | PORTB  |       |       |       | PORTB[7:0]  |           |       |       |           |

| 0x000A  | PORTC  |       |       |       | PORTC[7:0]  |           |       |       |           |

The I/O port configuration is automatically overwritten by the firmware if certain modes and functions are selected. A detailed description of the I/O ports hardware IP is given in Section 3.8.6 “I/O Ports” on page 215.

#### 2.4.5 Port Debounce Configuration

The ports of the Atmel® ATA5785 feature hardware debouncing that can be used to avoid false events coming from bouncing mechanical switches or bus glitches. A common debounce timer is used for all ports. The debouncing can be activated and deactivated independently on every digital I/O port. The debouncing time is configurable in the range of approximately 2µs to 250ms (see Table 3-61 on page 231), allowing key debouncing as well as LIN bus debouncing, for example. A level change on any port with activated debouncing resets the debounce timer.

There are two modes for debouncing: fast mode and stable mode. In stable mode a port event is transmitted to the AVR® only if the selected ports are stable (unchanged) for the configured debouncing time and the port values are not the same as the values before the first change. In fast mode a port event is transmitted to the AVR immediately. All following events are ignored for the configured debouncing time.

If debouncing is selected for any pin the only allowed sleep mode is “idle”. Other combinations are forbidden.

Debouncing can be configured and enabled by SPI access to the corresponding hardware registers. A detailed description is given in Section 3.8.6.2 “Port Debouncing” on page 219.

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|------------|-------|-------|-------|-------|

| 0x0153  | DBCR  | -     | -     | -     | -          | -     | DBTMS | DBCS  | DBMD  |

| 0x0154  | DBTC  |       |       |       | DBTC[7:0]  |       |       |       |       |

| 0x0155  | DBENB |       |       |       | DBENB[7:0] |       |       |       |       |

| 0x0156  | DBENC |       |       |       | DBENC[7:0] |       |       |       |       |

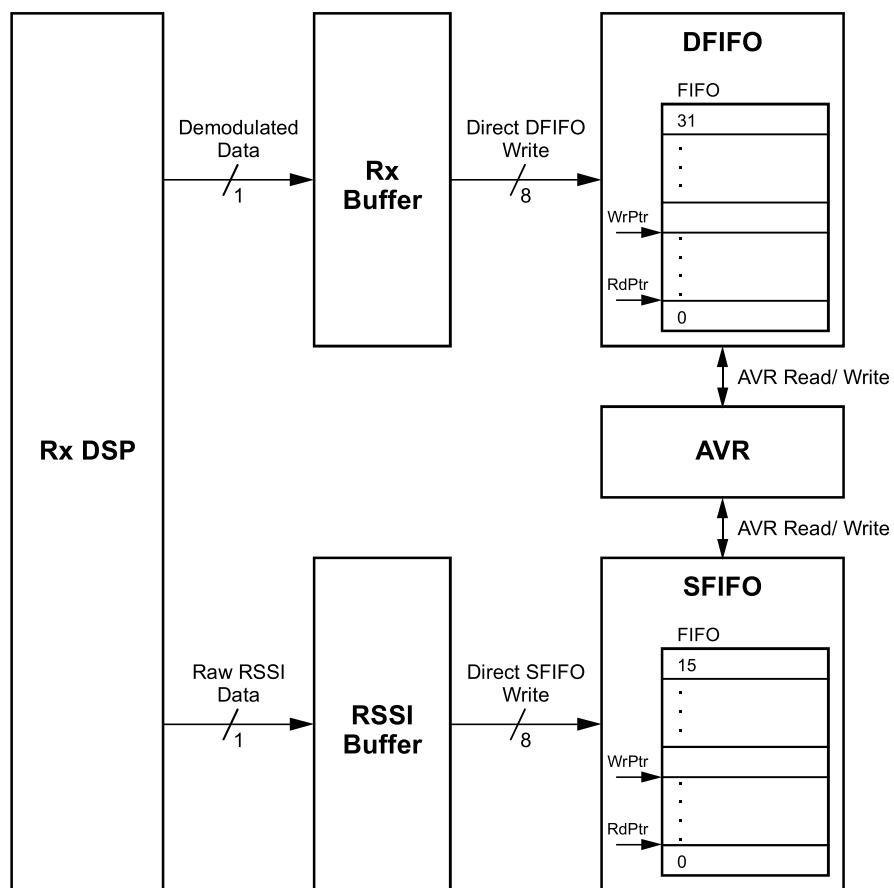

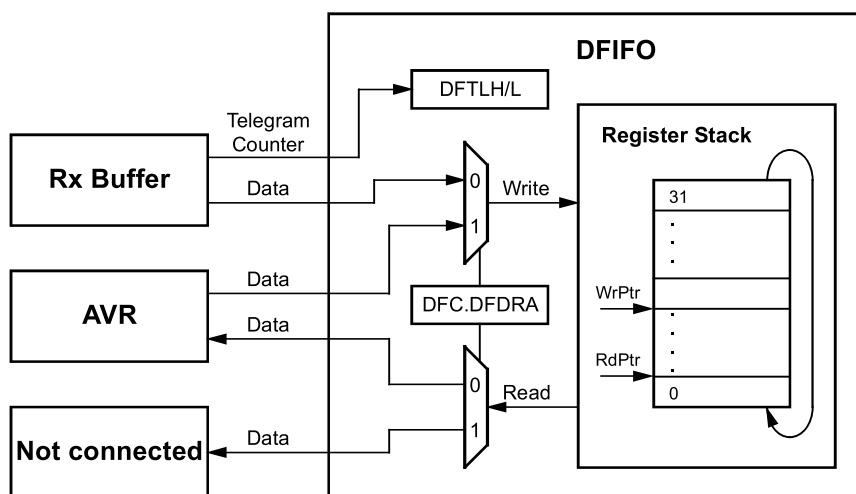

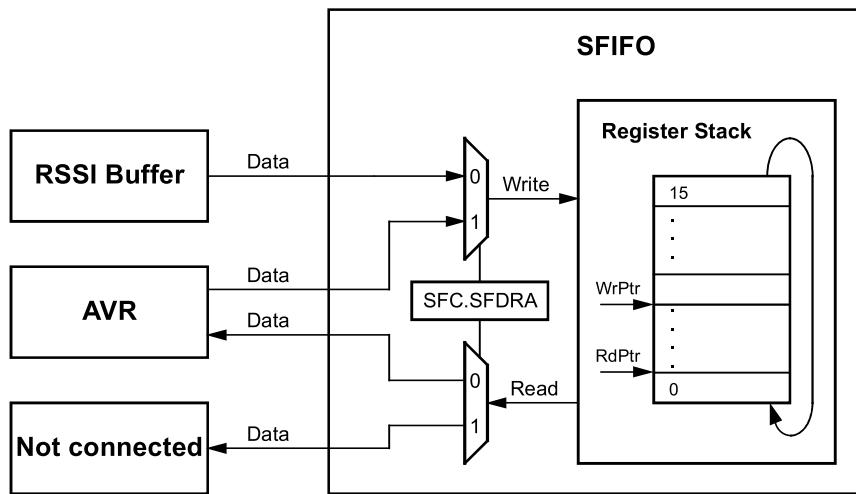

#### 2.4.6 FIFO Interrupt Initialization

The support FIFO (SFIFO) and the data FIFO (DFIFO) implement error interrupts for overflow and underflow events. These interrupts can be switched off by setting the SRAM variables `systemConfig.SFIFO_OFL_UFL_RX_disable` and `systemConfig.DFIFO_OFL_UFL_RX_disable` to “1”, respectively. For more information, see Section 3.5 “Data and Support FIFOs” on page 162

| Address | Name         | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                    | Bit 2                    | Bit 1                       | Bit 0 |

|---------|--------------|-------|-------|-------|-------|--------------------------|--------------------------|-----------------------------|-------|

| 0x02E5  | systemConfig | -     | -     | SRCAO | FRCAO | SFIFO_OFL_UFL_RX_disable | DFIFO_OFL_UFL_RX_disable | Current idle mode selection | -     |

Atmel Confidential: For Release Only Under Non-Disclosure Agreement (NDA)

#### 2.4.7 AVCC Low Interrupt Configuration

if the analog voltage (AVCC) drops below a certain threshold voltage (typically 100mV below the nominal AVCC voltage), the event flag “AVCCLOW” in the event byte “system” can be raised and an event to the external host can be triggered. The event flag can be enabled by setting the AVCCLM bit in the SUPCR hardware register to “1”, the external event can additionally be enabled in the sysEventMask SRAM variable.

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  |

|---------|-------|-------|-------|-------|-------|-------|-------|--------|--------|

| 0x00CB  | SUPCR | -     | AVDIC | AVEN  | DVDIS |       |       | AVCCLM | AVCCRM |

| Address |              | Bit 7   | Bit 6   | Bit 5   | Bit 4    | Bit 3 | Bit 2        | Bit 1         | Bit 0   |

|---------|--------------|---------|---------|---------|----------|-------|--------------|---------------|---------|

| 0x020E  | sysEventMask | SYS_ERR | CMD_RDY | SYS_RDY | AVCCLOWM |       | RX_ACTIVE_EN | RX_ACTIVE_POL | IRQ_POL |

## 2.5 Operating Modes Overview

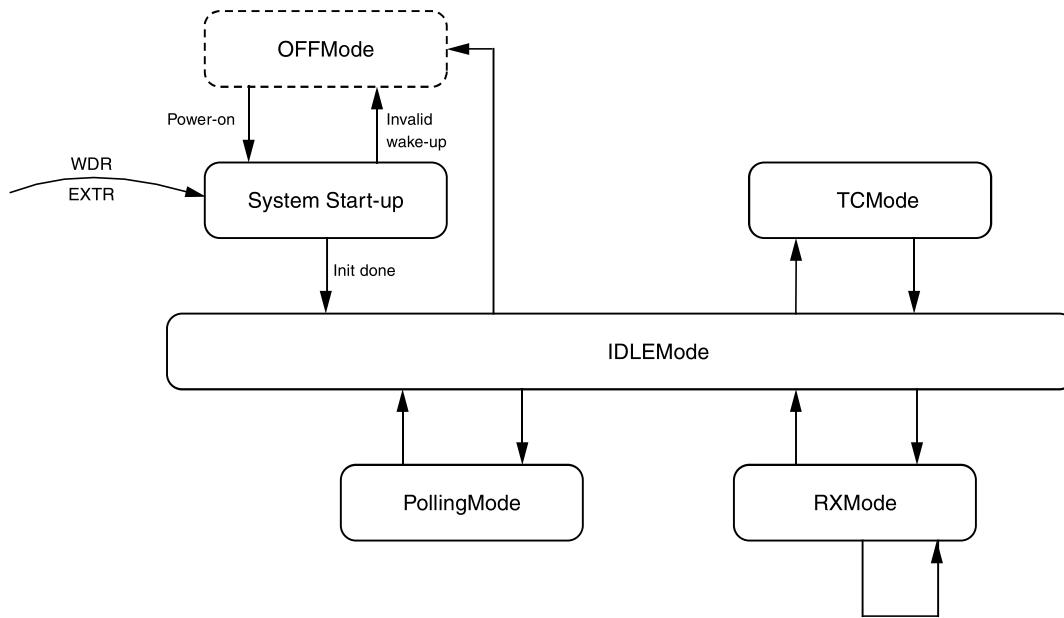

This section gives an overview of the operating modes supported by the Atmel® ATA5785 as shown in Figure 2-6. For a more detailed description of the operating modes and their transitions, see later sections.

Figure 2-6. Operating Modes Overview

After connecting the supply voltage to the VS pin, the Atmel ATA5785 always starts in OFFMode. All internal circuits are disconnected from the power supply. Therefore, no SPI communication is supported. The Atmel ATA5785 can be woken up by activating the PWRON pin or one of the NPWRONx pins. This triggers the power-on sequence. After the system initialization the Atmel ATA5785 reaches the IDLEMode (RC).

The IDLEMode is the basic system mode supporting SPI communication and transitions to all other operating modes. There are two options of the IDLEMode:

- IDLEMode(RC) with low power consumption using the fast RC (FRC) oscillator for processing

- IDLEMode(XTO) with active crystal oscillator for high accuracy clock output or timing measurements

The receive mode (RXMode) provides data reception on the selected service/channel configuration. The precondition for data reception is a valid preamble. The receiver continuously scans for a valid telegram and receives the data if all pre-configured checks are successful. The RXMode is enabled by the SPI command “Set System Mode” as described in Section 7.4 “SPI Command Reference” on page 345.

In PollingMode the receiver is activated for a short period of time to check for a valid telegram on the selected service/channel configurations. The receiver is deactivated if no valid telegram is found and a sleep period with very low power consumption elapses. This process is repeated periodically in accordance with the polling configuration.

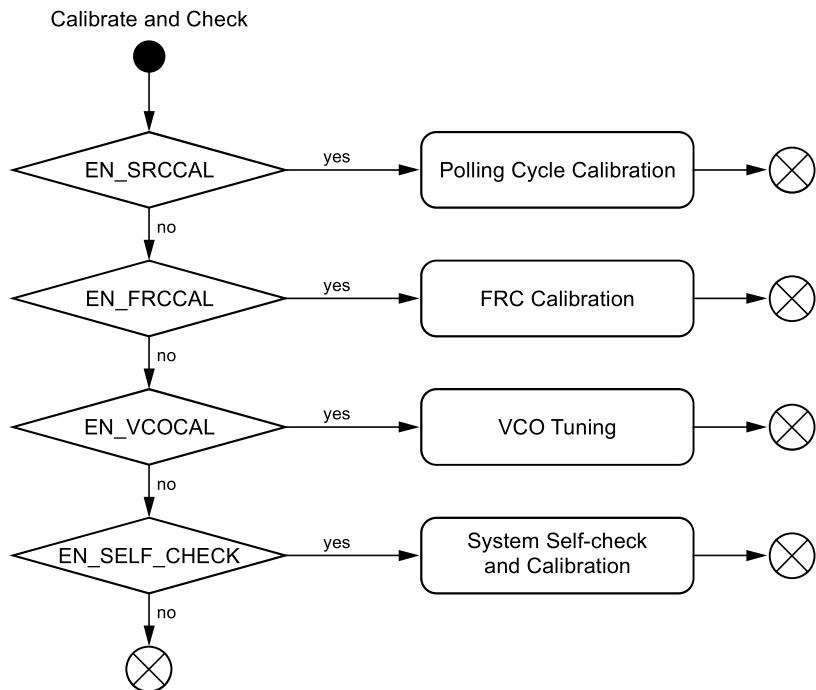

The tune and check mode (TCMode) offers calibration and self-checking functionality for the VCO and FRC oscillators as well as for polling cycle accuracy. This mode is activated via the SPI command “Calibrate and Check” described in [Section 7.4 “SPI Command Reference” on page 345](#). Tune and check tasks can also be activated periodically during PollingMode.

Table 2-2 on page 18 shows the relations between the operating modes and their corresponding power supplies, clock sources, and sleep mode settings.

**Table 2-2. Operating Modes versus Power Supplies and Oscillators**

| Operation Mode                                        | AVR Sleep Mode                           | DVCC | AVCC | XTO | SRC | FRC |

|-------------------------------------------------------|------------------------------------------|------|------|-----|-----|-----|

| OFFMode                                               | -                                        | off  | off  | off | off | off |

| IDLEMode(RC)                                          | Active mode<br>Power-down <sup>(1)</sup> | on   | off  | off | on  | on  |

| IDLEMode(XTO)                                         | Active mode<br>Power-down <sup>(1)</sup> |      | off  | on  | on  | off |

| RXMode                                                | Active mode                              |      | on   | on  | on  | off |

| PollingMode(RC)<br>- Active period<br>- Sleep period  | Active mode<br>Power-down <sup>(1)</sup> |      | on   | on  | on  | on  |

| PollingMode(XTO)<br>- Active period<br>- Sleep period | Active mode<br>Power-down <sup>(1)</sup> |      | off  | off | on  | off |

|                                                       |                                          |      | on   | on  | on  | off |

|                                                       |                                          |      | on   | on  | on  | off |

Notes: 1. During IDLEMode(RC) and IDLEMode(XTO) the AVR® microcontroller enters sleep mode to reduce current consumption. The power-down mode is recommended for keeping current consumption low.

## 2.6 OFFMode

The OFFMode is the mode with the lowest current consumption. Typically 5nA can be expected for an application driven by a 3V battery. In the OFFMode all internal circuitries are disconnected from the power supply. The device is not receptive for RF signals or SPI commands. Furthermore the ports are set to be inputs with or without pull-up resistors.

The Atmel® ATA5785 is in OFFMode after connecting the external power supply under the condition that no NPWRONx pin is set to “0” and the PWRON pin is not set to “1”. During operation a transition to OFFMode is initiated by the SPI command “OFF Command”.

The OFFMode can be left by setting one of the NPWRON1..6 pins to LOW or the PWRON pin to HIGH. This starts the transition to the IDLEMode.

## 2.7 IDLEMode

The IDLEMode is the basic system mode. From this mode all supported operating modes can be started. Most circuits are deactivated in IDLEMode.

The IDLEMode follows up the OFFMode at system start-up and system reset. It is used as the default mode after leaving other system modes and can be activated at any time by the SPI command “Set System Mode”.

To help attain a system with low power consumption, various AVR sleep modes are possible during the inactive period of the IDLEMode. The sleep mode configuration after start-up is the idle sleep mode. For the lowest current consumption it is recommended to set the AVR core to power-down mode. For more information, see [Section 3.8.5 “Sleep Modes and Active Power Reduction” on page 210](#).

The Atmel ATA5785 offers two different idle modes: IDLEMode(RC) and IDLEMode(XTO).

In IDLEMode(RC) only the DVCC voltage regulator, the FRC oscillator (active period) and the SRC oscillator (power-down period) are switched on. If enabled, the AVR automatically uses a sleep mode to achieve very low current consumption.

In the IDLEMode(XTO) the AVCC voltage domain and the XTO are additionally activated to provide a high accuracy system clock derived from the crystal oscillator. This increases power consumption compared to the IDLEMode(RC), but the start-up time of receive modes is decreased because the XTO is already running.

During system operation the IDLEMode can be selected by the SPI command “Set System Mode”.

If the IDLEModeSelector parameter is set to “1”, the system switches to IDLEMode(XTO) after the active operating mode has finished, otherwise to IDLEMode(RC). For more information see [Section 7.4 “SPI Command Reference” on page 345](#).

Note:

- The IDLEMode neither provides any internal status information nor generates external events.

- The IDLEMode is the only mode that allows reading/writing from/to SRAM, and hardware registers.

## 2.8 Data Reception

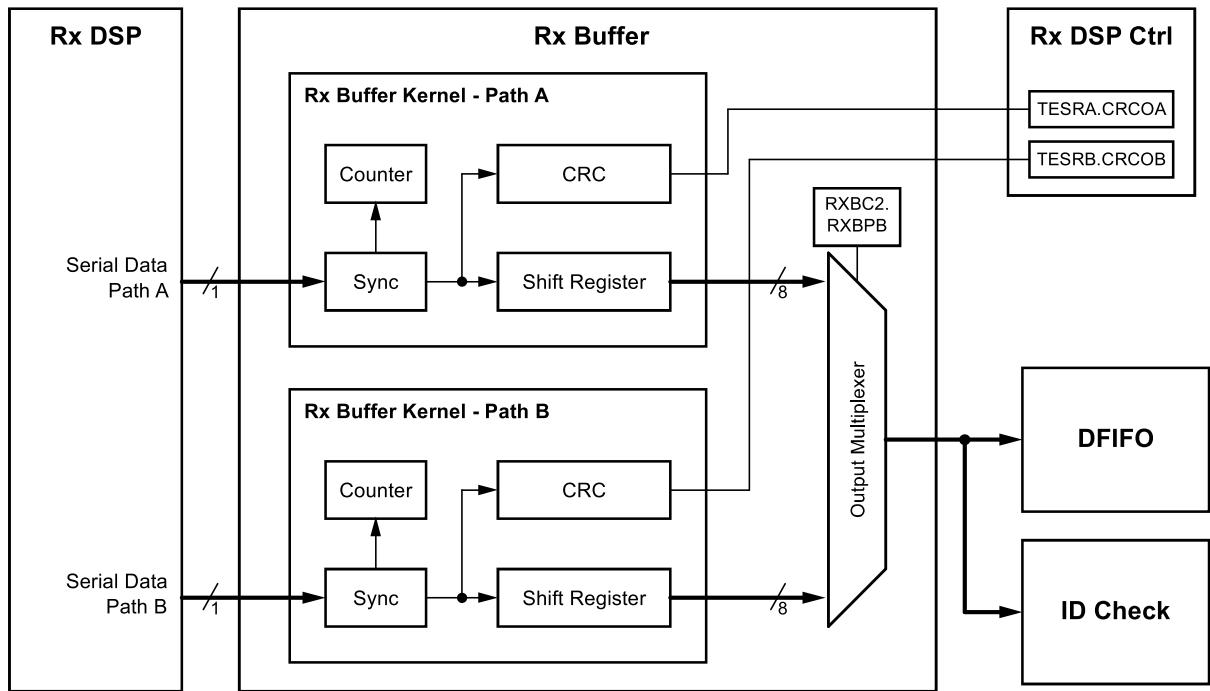

### 2.8.1 Rx Overview

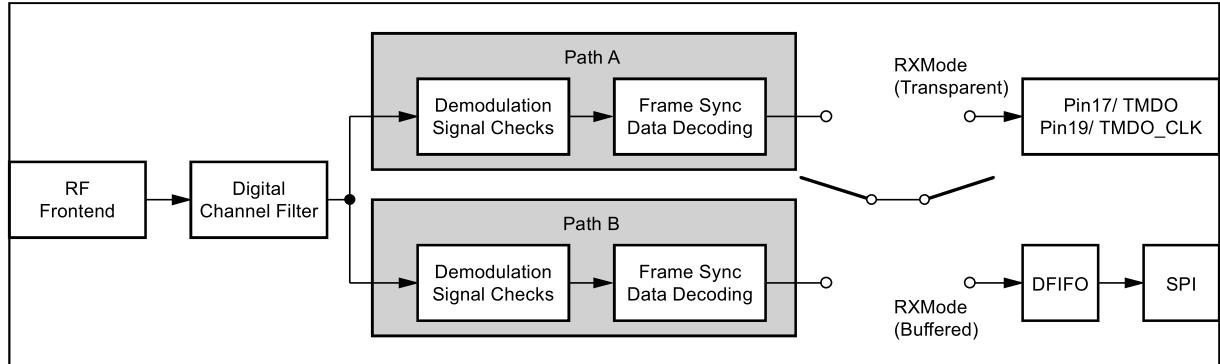

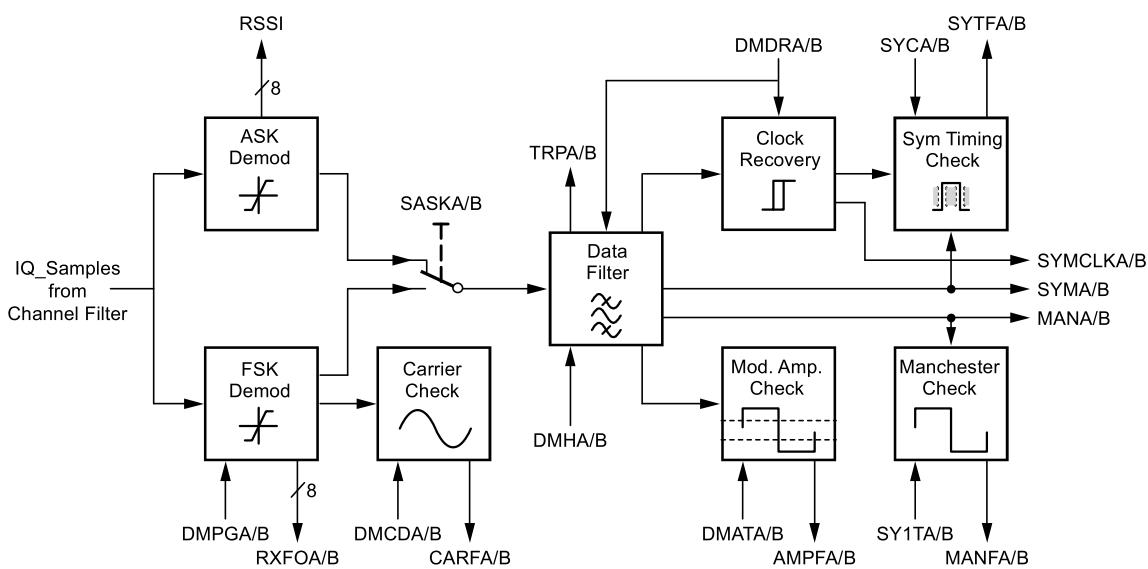

The Atmel® ATA5785 contains two receive paths A and B whose parameters, such as the modulation type, data rate, and telegram settings, can be set separately and are described in more detail in [Section 2.8.6 “Rx Telegram Handling” on page 30](#) and [Section 2.8.7 “General Rx Settings” on page 35](#). If individual settings are possible for the two paths, this is marked with a small “x” instead of an “A” or “B” in the subsequent sections.

The receive unit is split after the digital channel filter and merged again after the data decoding. This implies that:

- It is possible to search in parallel for telegrams with different modulation (ASK/FSK)

- It is possible to search in parallel for telegrams with different data rates

- It is possible to search in parallel for telegrams with different FSK deviations as long as the channel filter setting suits for both

- It is possible to configure signal checks and error handling individually for both paths

- It is possible to configure the preamble settings (WUP, SFID pattern) individually for both paths

- It is NOT possible to search in parallel for telegrams on different RF carrier frequencies

- It's NOT possible to receive in parallel the data payload on both paths, because one path is switched off after WUP or SFID detections on the other path.

Figure 2-7 gives a high-level functional overview of the receive mode.

**Figure 2-7. Receive Mode Overview**

The data receive mode (RXMode) can be activated by using the “Set System Mode” SPI command if the OPM bits in the systemModeConfig parameter are set to “0b10”. The required service/channel configuration as well as additional settings such as VCO tuning during mode ramp-up, are part of the SPI command. For more information, see [Section 7.4.8 “Set System Mode” on page 349](#).

| Name                 | Bit 7    | Bit 6    | Bit 5    | Bit 4            | Bit 3 | Bit 2 | Bit 1    | Bit 0 |

|----------------------|----------|----------|----------|------------------|-------|-------|----------|-------|

| systemModeConfig     | RF_CAL   | -        | VCO_TUNE | IDLEModeSelector | -     | TMDEN | OPM[1:0] |       |

| serviceChannelConfig | enaPathB | enaPathA | ch[1:0]  |                  | -     |       | ser[2:0] |       |

The data reception is split into RXMode(transparent) and RXMode(buffered), selectable by the transparent mode data enable (TMDEN) bit. Both modes are described in more detail in the following subsections.

The RXMode can be used for all services without any restrictions. It supports service independent features such as:

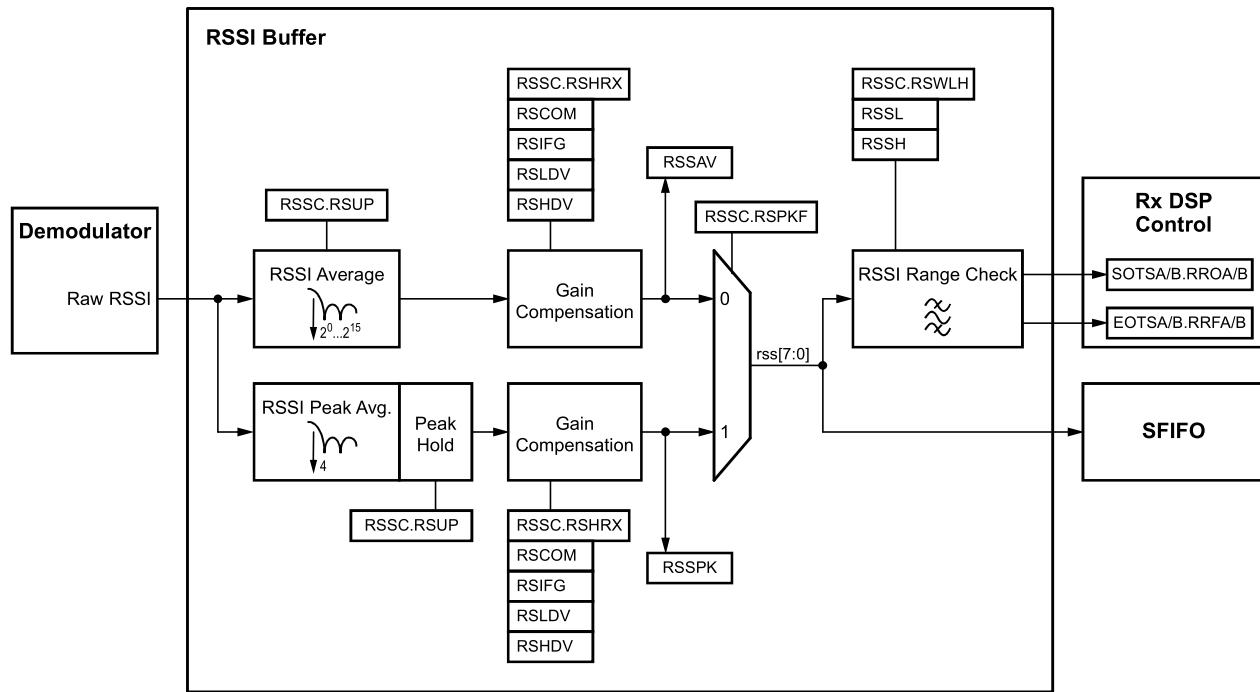

- RSSI measurement (see Section 2.8.7.6 “RSSI Measurement” on page 47 for more information)

RXMode generally generates external events on pin 28 (EVENT) if a certain event occurs and the corresponding event mask in rxSysEvent is enabled. Events which are only relevant for the RXMode(transparent) and RXMode(buffered) are described in the associated sections. Commonly used events to indicate internal status information are located in the system (R15) and events (R14) as shown below.

| Name                          | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3  | Bit 2 | Bit 1    | Bit 0 |

|-------------------------------|---------|---------|---------|---------|--------|-------|----------|-------|

| System (R15)<br>events.system | SYS_ERR | CMD_RDY | SYS_RDY | AVCCLOW | -      | SFIFO | DFIFO_RX | -     |

| Events (R14)<br>events.events | IDCHKA  | WCOKA   | SOTA    | EOTA    | IDCHKB | WCOKB | SOTB     | EOTB  |

| Address | Name       | Bit 7           | Bit 6          | Bit 5         | Bit 4         | Bit 3           | Bit 2          | Bit 1         | Bit 0         |

|---------|------------|-----------------|----------------|---------------|---------------|-----------------|----------------|---------------|---------------|

| 0x0344  | rxSysEvent | IDCHKA<br>_Mask | WCOKA<br>_Mask | SOTA<br>_Mask | EOTA<br>_Mask | IDCHKB<br>_Mask | WCOKB<br>_Mask | SOTB<br>_Mask | EOTB<br>_Mask |

In RXMode pin 29 (PB7) can be configured as the RX\_ACTIVE signal to monitor the status of the RF front end. The RX\_ACTIVE pin can be configured in the events.sysEventMask.RX\_ACTIVE\_EN and RX\_ACTIVE\_POL SRAM variables. The RX\_ACTIVE signal can also be used for biasing an external LNA, see Section 2.8.7.9 “External LNA Control” on page 49 for details.

| Address | Name         | Bit 7   | Bit 6   | Bit 5   | Bit 4        | Bit 3 | Bit 2            | Bit 1             | Bit 0   |

|---------|--------------|---------|---------|---------|--------------|-------|------------------|-------------------|---------|

| 0x020E  | sysEventMask | SYS_ERR | CMD_RDY | SYS_RDY | AVCC<br>LOWM | -     | RX_ACTIVE<br>_EN | RX_ACTIVE<br>_POL | IRQ_POL |

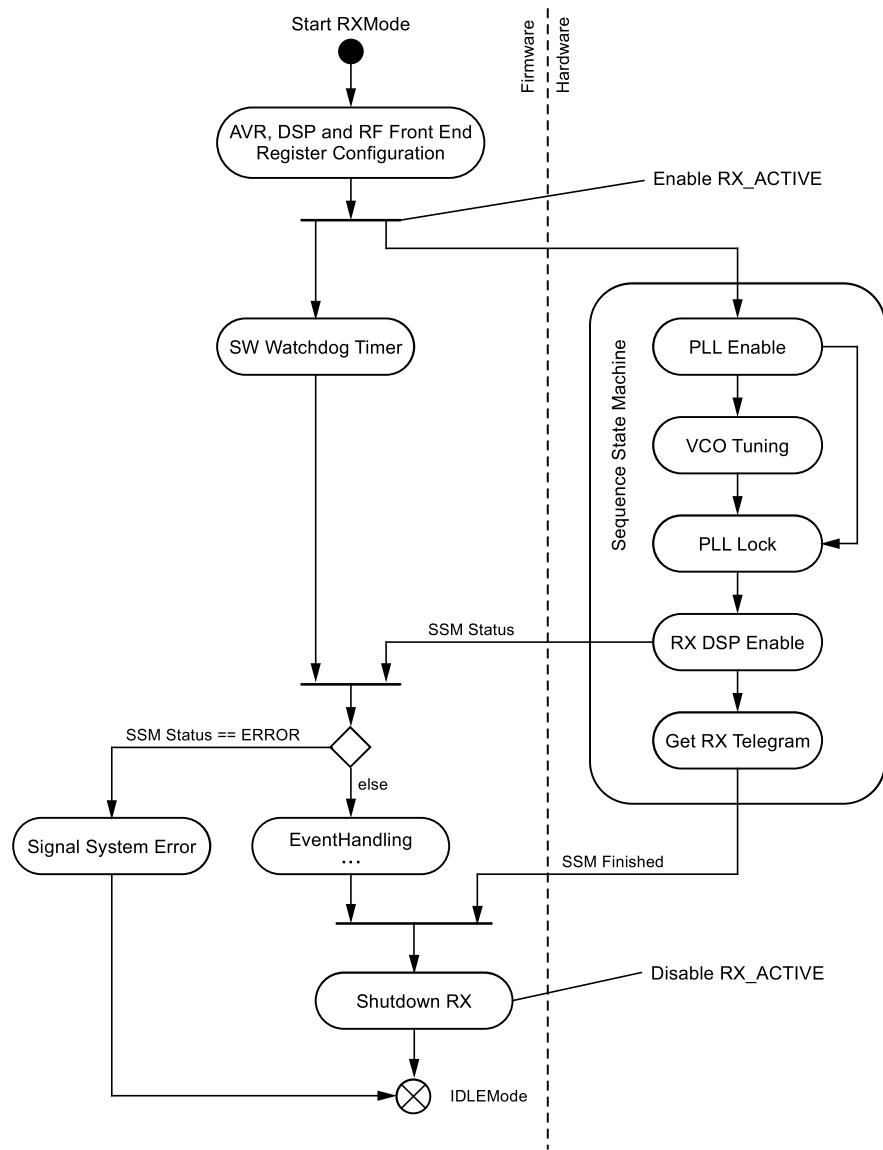

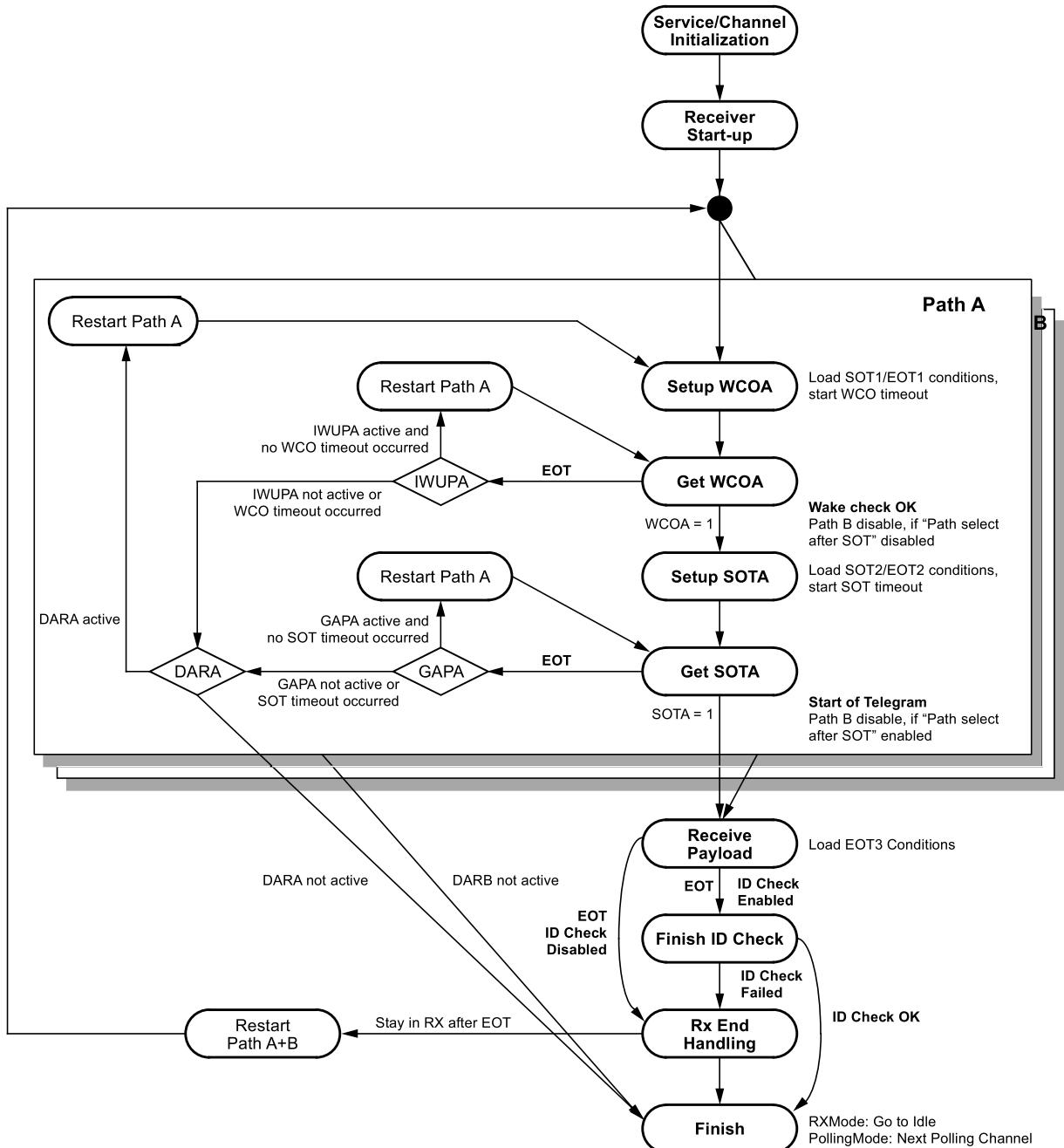

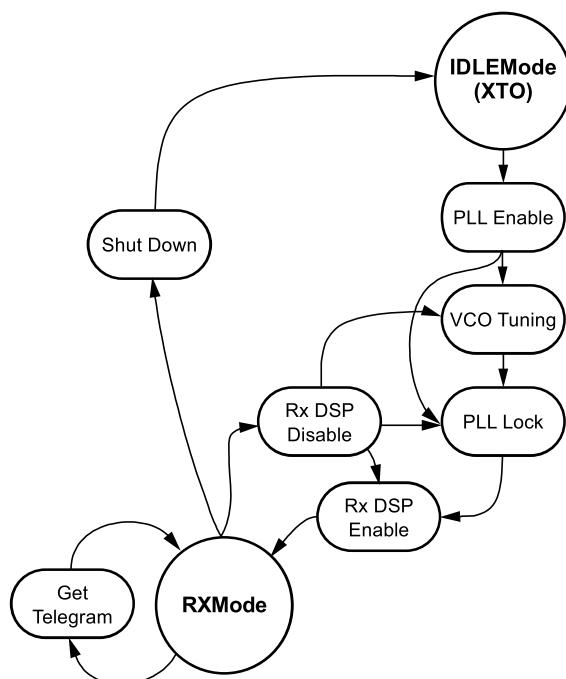

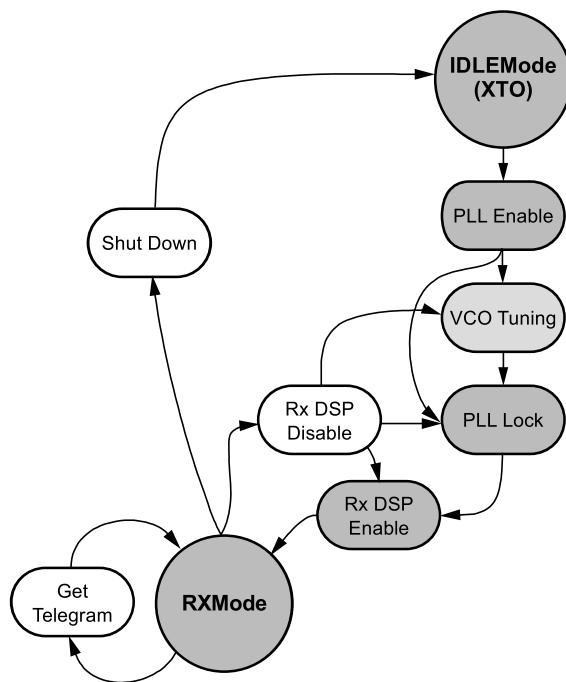

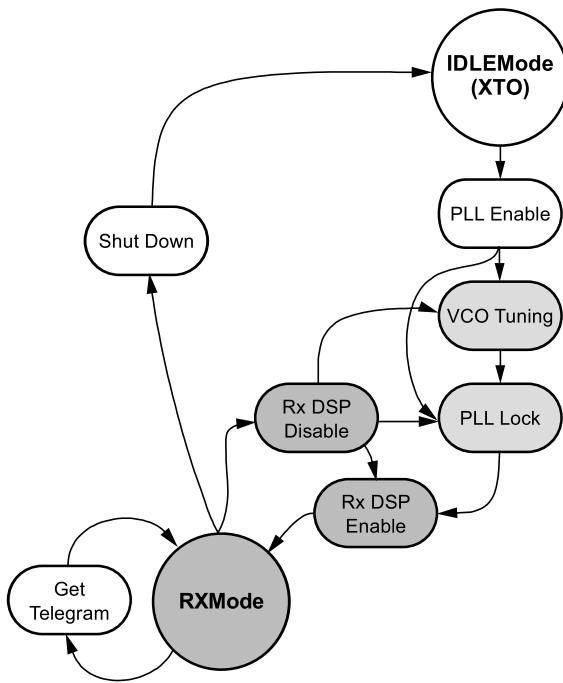

The RXMode is controlled mainly by the sequencer state machine (SSM) which is located in the hardware and performs the start-up procedure. The firmware does the configuration and control of the SSM. Figure 2-8 shows the entire RXMode flow.

**Figure 2-8. Receive Mode Flow**

After the RXMode is activated, the firmware initializes the registers based on the settings in the selected service/channel configuration and configures the sequencer state machine for RXMode. If an RF calibration is selected, a temperature calibration of the XTO is carried out based on the latest available temperature value. If enabled, the RX\_ACTIVE pin is set after the service/channel configuration is done and before the RF frontend is activated.

Start-up of the RF front end is done by the SSM and controlled by the firmware via a software watchdog (Timer2 is used). If there is no hardware response or an error message from the SSM, the firmware sets the SYS\_ERR bit in the events.system event byte. The error code is stored in the SRAM variable debug, which contains the firmware error code (debug.errorCode) and the SSM error code (debug.ssmErrorCode). For more information, see Section 7.5 “Error Codes” on page 359.

It is possible to start-up the RXMode with or without VCO tuning at RXMode start-up. For more information see the “Set System Mode” SPI command.

After a successful start-up of the RF front end the Rx DSP is enabled and the Get RX Telegram state machine is started. This state machine controls the entire telegram reception process including synchronization, signal checking, data reception and decoding. In RXMode(transparent) the received payload data are routed to pins PC3 (TMDO) and PC5 (TMDO\_CLK), in RXMode(buffered) the data are written to the data FIFO (DFIFO) for later retrieval. A detailed description of the Get RX Telegram state machine is given in section [Section 2.8.6 “Rx Telegram Handling” on page 30](#).

The event handling is performed by the firmware in parallel to the telegram reception.

During shutdown of RXMode the RX\_ACTIVE pin is disabled and the system returns to IDLEMode.

## 2.8.2 RXMode(transparent)

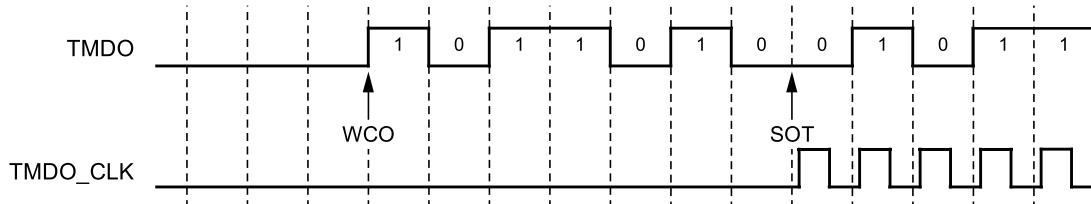

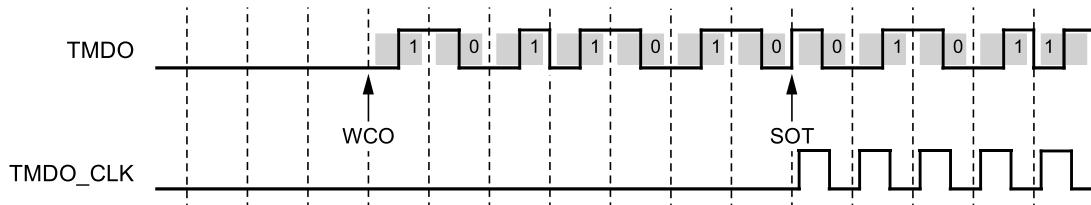

In the RXMode(transparent) the receiver provides the received data stream on pin 17 (TMDO) after a wake check OK (WCO) and a corresponding data clock on pin 19 (TMDO\_CLK) after a valid start of telegram (SOT).

Figure 2-9 shows a timing diagram of TMDO and TMDO\_CLK in NRZ mode. TMDO\_CLK has a 50% duty cycle, therefore, the data can be sampled either at the rising or the falling edge. Before a WCO the TMDO line is LOW.

**Figure 2-9. Timing Diagram for TMDO and TMDO\_CLK in NRZ Mode**

Figure 2-10 shows a timing diagram for TMDO and TMDO\_CLK in Manchester mode. TMDO\_CLK has a 50% duty cycle, therefore, the data can be sampled either at the rising or the falling edge.

If default polarity is selected (see [Section “Data Polarity” on page 38](#)), inverted data are received at the rising edge and correct data are received on the falling edge of TMDO\_CLK. If inverted polarity is selected, correct data are received at the rising edge and inverted data are received on the falling edge of TMDO\_CLK. Before WCO the TMDO line is LOW.

**Figure 2-10. Timing Diagram for TMDO and TMDO\_CLK in Manchester Mode**

If both demodulator receive paths are activated, the signals generated on pins TMDO and TMDO\_CLK come from the path which has recognized the first WCO.

Exception:

If the `sramServices.rxSysSet.PathValidAfterSOT_ENA` SRAM variable is set to “1”, TMDO and TMDO\_CLK are provided simultaneously for the path which recognized the first SOT. A WCO detection does not provoke a TMDO output in this case.

On detection of valid data on path A and path B at the same time, path A is used for data reception.

RXMode(transparent) provides internal status information using the event flags of the `event.system` (R15) and `event.events` (R14) as shown in the general part of RXMode.

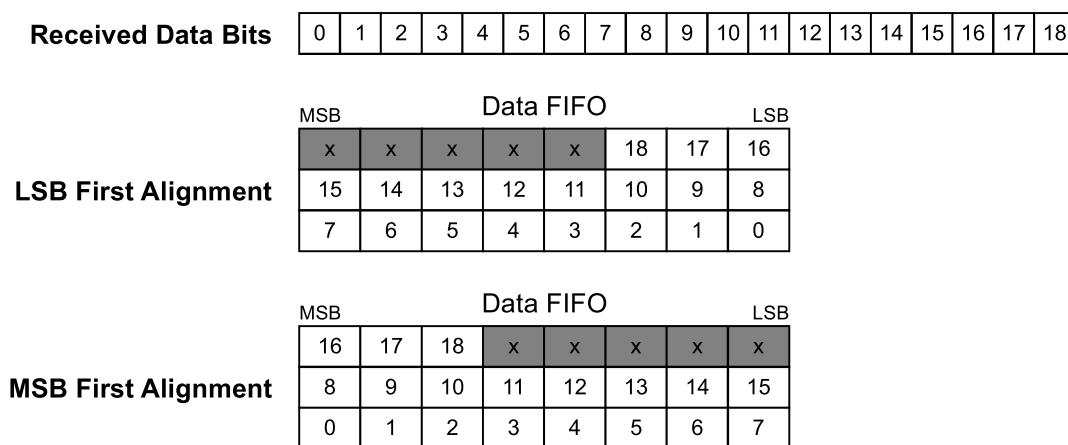

### 2.8.3 RXMode(buffered)

In RXMode(buffered) the received data stream is stored in the 32 bytes deep data FIFO (DFIFO). The fill level can be read out by using the “Read Fill Level Rx FIFO” SPI command.

Note: The content of the DFIFO is overwritten if the incoming data stream exceeds 32 bytes in length and has not been read out by using the “Read Rx FIFO” SPI command as described in Section 7.4.5 “Read Rx FIFO” on page 347.

In the buffered data reception mode, the current DFIFO fill level is compared to a configurable buffer threshold for path A or path B. These thresholds can be set up independently for path A and path B of each service using the `sramServices.rxSetPathx.RXbufx[5:0]` variables.

| Address Service3 | Name          | Bit 7 | Bit 6         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0       |

|------------------|---------------|-------|---------------|-------|-------|-------|-------|-------|-------------|

| 0x0340           | rxSetPathA[0] | -     | rxBufEv MaskA |       |       |       |       |       | RXbufA[5:0] |

| 0x0342           | rxSetPathB[0] | -     | rxBufEv MaskB |       |       |       |       |       | RXbufB[5:0] |

Any time the fill level reaches the threshold of the current receive path, a DFIFO fill level match condition becomes true. In that case the firmware indicates its occurrence by setting the event flag DFIFO\_RX in `events.system` (R15).

| Name                                       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1    | Bit 0 |

|--------------------------------------------|---------|---------|---------|---------|-------|-------|----------|-------|

| System (R15)<br><code>events.system</code> | SYS_ERR | CMD_RDY | SYS_RDY | AVCCLOW | -     | SFIFO | DFIFO_RX | -     |

Note: Every time the RXMode(buffered) starts, a reset of the DFIFO and its related pointers takes place.

Depending on the telegram requirements, the receiver can be configured to swap the incoming bytes (MSB-first or LSB-first) before storing them to the DFIFO. The associated settings for path A and path B are located in the `sramServices.RXBC1` variable.

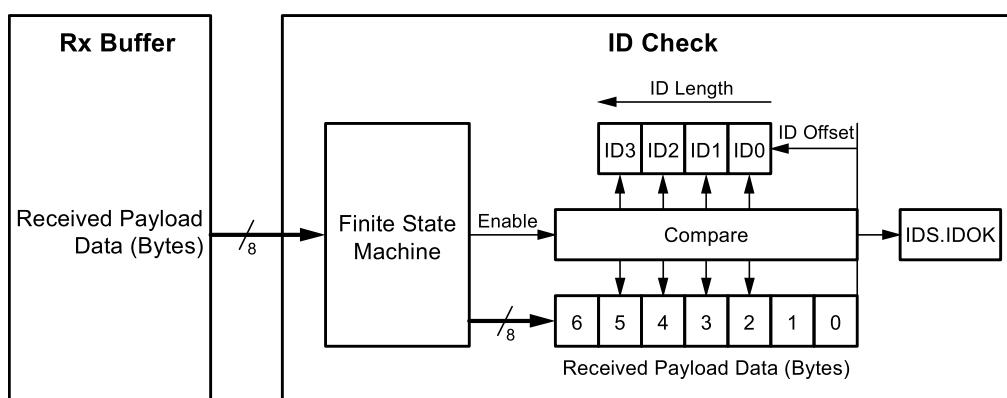

The ID check feature is supported in RXMode(buffered). This feature is described in more detail in Section 2.8.7.5 “ID Check” on page 46.

The RXMode(buffered) provides internal status information using the event flags of `events.system` (R15) and `events.events` (R14) as shown in the general part of the RXMode. In addition, the event flags DFIFO\_RX and IDCHKA/B are supported, which might be used to generate an external event on pin 28 (EVENT), if the mask bits `rxBufEvMaskA/B` and `IDCHKA/B_Mask` in `rxSetPathA/B[0]` and `rxSysEvent` are enabled and the associated event occurs.

| Name                                       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3  | Bit 2 | Bit 1    | Bit 0 |

|--------------------------------------------|---------|---------|---------|---------|--------|-------|----------|-------|

| System (R15)<br><code>events.system</code> | SYS_ERR | CMD_RDY | SYS_RDY | AVCCLOW | -      | SFIFO | DFIFO_RX | -     |

| Events (R14)<br><code>events.events</code> | IDCHKA  | WCOKA   | SOTA    | EOTA    | IDCHKB | WCOKB | SOTB     | EOTB  |

| Address Service3 | Name          | Bit 7           | Bit 6          | Bit 5         | Bit 4         | Bit 3           | Bit 2          | Bit 1         | Bit 0         |

|------------------|---------------|-----------------|----------------|---------------|---------------|-----------------|----------------|---------------|---------------|

| 0x0340           | rxSetPathA[0] | -               | rxBufEv MaskA  |               |               |                 |                |               | RXbufA[5:0]   |

| 0x0342           | rxSetPathB[0] | -               | rxBufEv MaskB  |               |               |                 |                |               | RXbufB[5:0]   |

| 0x0344           | rxSysEvent    | IDCHKA<br>_Mask | WCOKA<br>_Mask | SOTA<br>_Mask | EOTA<br>_Mask | IDCHKB<br>_Mask | WCOKB<br>_Mask | SOTB<br>_Mask | EOTB<br>_Mask |

The demodulated data can additionally be output on pin 17/TMDO and pin 19/TMDO\_CLOCK as reshaped transparent output. If `sramServices.rxSysSet.PathValidAfterSOT_ENA` is set to "0", the data of the active path is output on the TMDO pin after a WCO and the corresponding clock is output on pin TMDO\_CLOCK after an SOT.

If `sramServices.rxSysSet.PathValidAfterSOT_ENA` is set to "1", both the data and clock of the active path are output on the pins together after an SOT.

The reshaped transparent output can be activated independently for each service by setting at least one of the `sramServices.RDOCR.TMDS[1:0]` bits to "1".

| Address Service3 | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1 | Bit 0 |

|------------------|-------|-------|-------|-------|-------|-------|-----------|-------|-------|

| 0x033E           | RDOCR | -     | 0     | 0     | ETRPB | ETRPA | TMDS[1:0] | -     | -     |

## 2.8.4 PollingMode

The Atmel® ATA5785 offers a special receive mode that includes all the features of RXMode. It is called PollingMode.

In PollingMode the receiver path is switched so that it alternates between an active period and a sleep period. In fastPollingMode, described in more detail in Section 2.8.4.3 "fastPollingMode" on page 27, the sleep time is zero. During the active period the device seeks valid telegrams on the participating service/channel configurations. The internal wake check logic verifies the incoming signal by checking the telegram for a valid wake check (WCO<sub>x</sub>) condition and then for a valid start of telegram condition (SOT<sub>x</sub>). If all participating service/channel configurations are checked and no valid telegram could be detected, the receiver re-enters the sleep period or otherwise remains active in the selected configuration.

PollingMode can be activated by using the "Set System Mode" SPI command, if the OPM bits in the `systemModeConfig` parameter are set to "0b11". It also includes additional settings, such as VCO tuning during the ramp-up of the mode, IDLEMode selection and transparent mode enable. The service/channel configuration to start PollingMode is defined by `startPollingIndex` located in the `serviceChannelConfig` parameter.

Switching from PollingMode to IDLEMode during initialization of a new polling channel can produce a switching delay of ~200µs. This delay is required to guarantee correct service/channel configuration of the system. For more information, see Section 7.4.8 "Set System Mode" on page 349.

| Name                              | Bit 7  | Bit 6 | Bit 5    | Bit 4             | Bit 3 | Bit 2 | Bit 1             | Bit 0 |

|-----------------------------------|--------|-------|----------|-------------------|-------|-------|-------------------|-------|

| <code>systemModeConfig</code>     | RF_CAL | -     | VCO_TUNE | IDLEMode Selector | -     | TMDEN | OPM[1:0]          |       |

| <code>serviceChannelConfig</code> | -      | -     | -        | -                 |       |       | startPollingIndex |       |

In PollingMode, the data rate, channel filter bandwidth, RF modulation, frequency, and signal check severity can be set independently for each service/channel configuration and are described in more detail in Section 2.8.7 "General Rx Settings" on page 35.

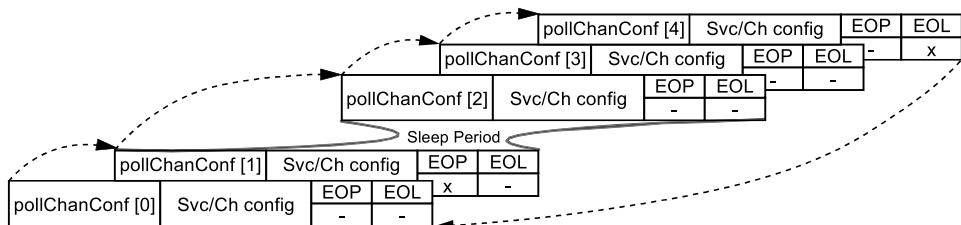

### 2.8.4.1 Polling Service and Channel Configuration

The polling service and channel configuration defines the different service/channel combinations checked during the active polling period. Up to 16 different configurations can be set up using the SRAM address range from 0x02F8 to 0x0317.

**Table 2-3. Polling Array**

| Address | Name                         | Bit 7    | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2     | Bit 1 | Bit 0 |

|---------|------------------------------|----------|----------|----------|-------|-------|-----------|-------|-------|

| 0x02F8  | pollChanConf[0].config       | RfCalib  | -        | VCOtune  | -     | -     | -         | EOL   | EOP   |

| 0x02F9  | pollChanConf[0].svcChConfig  | enaPathB | enaPathA | Ch[1..0] |       | -     | Ser[2..0] |       |       |

| ...     |                              |          |          |          |       |       |           |       |       |

| 0x0316  | pollChanConf[15].config      | RfCalib  | -        | VCOtune  | -     | -     | -         | EOL   | EOP   |

| 0x0317  | pollChanConf[15].svcChConfig | enaPathB | enaPathA | Ch[1..0] |       | -     | Ser[2..0] |       |       |

Each configuration consists of two bytes as shown in Table 2-3. The first byte contains general settings, such as tuning and RF calibration, which are executed during ramp-up of the associated service/channel configuration if enabled. The first byte also includes control information which is described in more detail in Section 2.8.4.2 “Polling Cycle” on page 25. The second byte defines the service/channel configuration directly, including the path information. For more information, see Section 2.12.7 “Polling Configuration Section” on page 68. The polling array can be changed by writing to this SRAM location using an SPI command during IDLEMode.

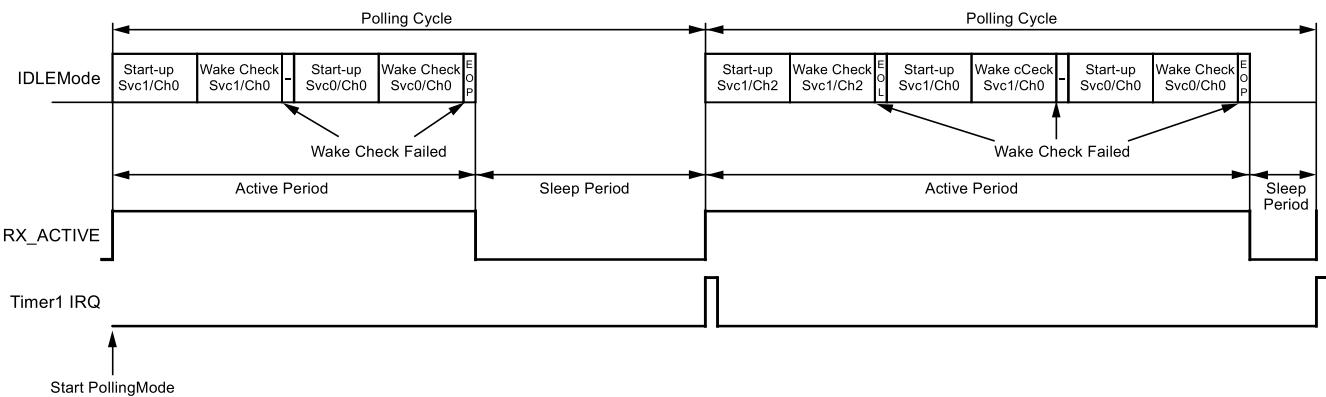

### 2.8.4.2 Polling Cycle

The polling cycle consists of the active polling period and the sleep period, as illustrated in Figure 2-11 on page 25. The timing interval to start the next polling cycle is programmable between 0ms and 4.000ms and controlled by Timer1.

The clock source for the polling timer is defined in an SRAM variable. To select the clock source for Timer1 as well as to adjust a proper polling cycle, the PollConfig.confT1MR, PollConfig.confT1COR, calib.srcCorVal and calib.srcRes variables must be modified (see Section 2.12.7 “Polling Configuration Section” on page 68).

| Address | Name      | Bit 7     | Bit 6 | Bit 5     | Bit 4      | Bit 3 | Bit 2     | Bit 1 | Bit 0 |  |  |  |

|---------|-----------|-----------|-------|-----------|------------|-------|-----------|-------|-------|--|--|--|

| 0x02F6  | confT1COR |           |       |           | T1COR[7:0] |       |           |       |       |  |  |  |

| 0x02F7  | confT1MR  | T1DC[1:0] |       | T1PS[3:0] |            |       | T1CS[1:0] |       |       |  |  |  |

| 0x02C4  | srcRes    |           |       |           | T1COR[7:0] |       |           |       |       |  |  |  |

| 0x02C5  | srcCorVal |           |       |           | T1COR[7:0] |       |           |       |       |  |  |  |

The duration of the active polling period depends on several factors such as the number of participated service/channel configurations, telegram time-outs, RF conditions, etc. The duration may vary for each polling cycle.

**Figure 2-11. Polling Cycle Definition**

The RX\_ACTIVE pin (PB7) can be configured to monitor the status of the RF front end during receive mode. The polarity of the pin can be adjusted in the SRAM setting as described in Section 2.12.1.2 “sysEventMask” on page 63.

The sleep period is primarily intended to keep current consumption at the lowest possible level. The Atmel® ATA5785 turns the receiver path off during the sleep period for this reason. Only the polling timer together with the selected oscillator remain active. Using the SRC oscillator to clock the polling timer is recommended due to its low power consumption and cyclical calibration of the polling cycle.

If the configured timing interval of the polling timer is shorter than the required time to check all the participated polling service/channel configurations, the effective polling cycle is extended until the next Timer1 IRQ, as shown in Figure 2-12.

**Figure 2-12. Effective Polling Cycle Definition**

Note: If the polling period is set to 0ms the fastPollingMode is activated.

#### End Of Polling Cycle (EOP)

A service/channel configuration with an activated EOP label defines the last configuration in the active polling period. When detecting this label, the firmware enters the polling sleep period. Otherwise the next configuration is triggered.

Note: In fastPollingMode the EOP labels are ignored.

#### End Of Polling Loop (EOL)

A service/channel configuration with an activated EOL label defines the last valid configuration used for polling. All subsequent configurations are ignored. After detecting this label, the firmware triggers the first configuration of the pollChanConf array as the next applicable service/channel configuration. Figure 2-13 shows an example of a polling configuration.

**Figure 2-13. Polling Configuration Example**

Note: If both the EOP and EOL labels are activated for the current service/channel configuration, first the polling sleep period is entered and then the next polling cycle uses the first array setting.

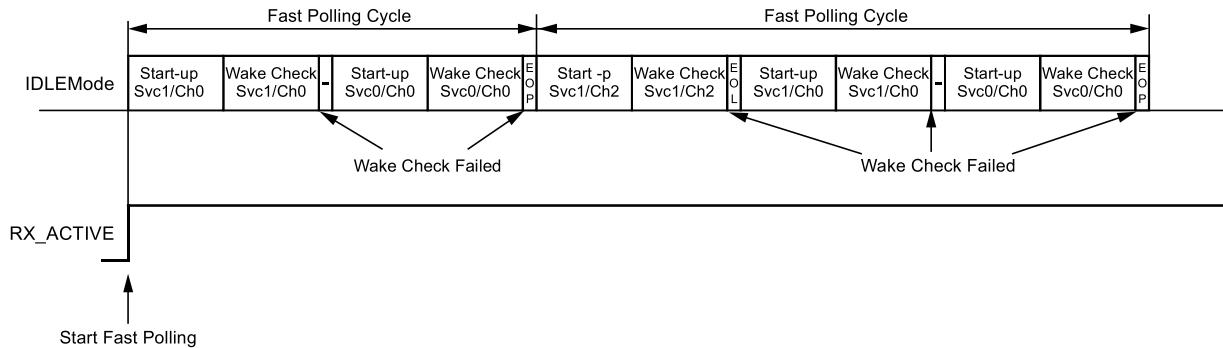

### 2.8.4.3 fastPollingMode

The purpose of fastPollingMode is to continuously check all participating service/channel configurations for valid telegrams without any interruption. This mode is very similar to the PollingMode but there is no support of the self check functionality and no sleep period is executed as shown in Figure 2-14. Fast polling is also known as “scanning”.

**Figure 2-14. Fast Polling Cycle Definition**

If the polling period is set to 0ms in the confT1COR SRAM setting, fastPollingMode is activated. During operation fastPollingMode can be enabled by overwriting the confT1COR SRAM variable manually with 0x00 by using the “Write SRAM/Register” SPI command if the system is in IDLEMode. For more information, see Section 7.4.6 “Write SRAM / Register” on page 348.

**Note:** EOP signals are ignored in this mode. Furthermore, VCO tuning on the initial service/channel configuration is not supported. For more information, see Section 2.8.4.6 “VCO Tuning” on page 28.

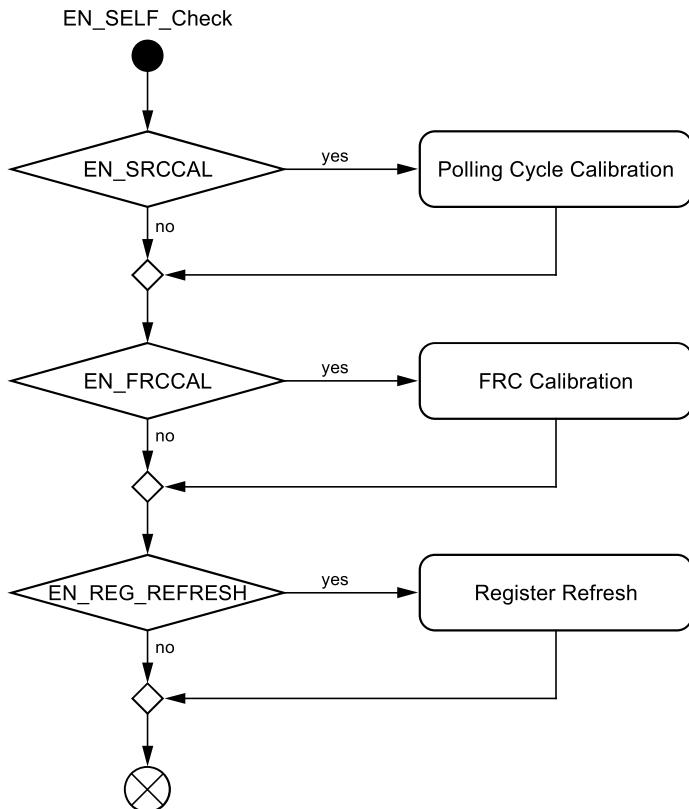

### 2.8.4.4 Self Check

During PollingMode the firmware is able to periodically start the system self check and calibration procedure. The number of polling cycles between two self check procedures can be modified via the trxCalibConfiguration.selfChk variable in the SRAM settings, as described in more detail in Section 2.12.3.5 “trxCalibConfiguration” on page 65.

| Address | Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|---------|-------|-------|-------|---------|-------|-------|-------|-------|

| 0x02E0  | selfChk |       |       |       | SC[7:0] |       |       |       |       |

The self check functionality is always executed at the end of a polling cycle. PollingMode is interrupted and the tune and check task is triggered. After the task has finished, PollingMode resumes.

The following four options are supported and can be activated independently in the trxCalibConfiguration.calConf1 SRAM variable.

- Polling cycle calibration/slow RC calibration

- Fast RC calibration

- Service refresh

| Address | Name     | Bit 7 | Bit 6 | Bit 5     | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0          |

|---------|----------|-------|-------|-----------|-----------|-------|-------|-------|----------------|

| 0x02DE  | calConf1 | -     | -     | EN_SRCCAL | EN_FRCCAL | -     | -     | -     | EN_REG_REFRESH |

For more information about the system self check and calibration as well as the individual options, see Section 2.9 “Tune and Check” on page 50.

**Notes:**

1. The self check functionality is NOT supported for fastPollingMode.

2. The self check functionality is also executed once at the end of the first polling cycle after starting PollingMode.

#### 2.8.4.5 Polling Cycle Calibration

The Atmel® ATA5785 offers a calibration procedure to ensure high accuracy of the adjusted polling cycle. The polling cycle is calibrated with the SPI command “Calibrate and Check” or periodically as a sub-task of system self check and calibration. This applies only if the clock source of Timer1 is set to SRC. The EN\_SRCCAL bit in the calConf1 SRAM variable must be set in order to enable polling cycle calibration during the system self check and calibration procedure.

| Address | Name     | Bit 7 | Bit 6 | Bit 5     | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0          |

|---------|----------|-------|-------|-----------|-----------|-------|-------|-------|----------------|

| 0x02DE  | calConf1 | -     | -     | EN_SRCCAL | EN_FRCCAL | -     | -     | -     | EN_REG_REFRESH |

The polling cycle calibration requires additional time. For more information about the polling cycle calibration, see Section 2.9 “Tune and Check” on page 50.

#### 2.8.4.6 VCO Tuning

The VCO can be tuned during the PollingMode and is optionally selectable for each service/channel configuration. To enable the VCO tuning for a specific service/channel configuration, set the VCOtune bit in the associated pollChanConf[x].config SRAM configuration.

| Name                   | Bit 7   | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------------------|---------|-------|---------|-------|-------|-------|-------|-------|

| pollChanConf[x].config | RfCalib | -     | VCOtune | -     | -     | -     | EOL   | EOP   |

To force VCO tuning on the first used service/channel configuration regardless of its pollChanConf setting, activate the VCO\_TUNE bit in the systemModeConfig parameter of the “Set System Mode” SPI command.

| Name             | Bit 7  | Bit 6 | Bit 5    | Bit 4             | Bit 3 | Bit 2 | Bit 1    | Bit 0 |

|------------------|--------|-------|----------|-------------------|-------|-------|----------|-------|

| systemModeConfig | RF_CAL | -     | VCO_TUNE | IDLEModeS elector | -     | TMDEN | OPM[1:0] |       |

Table 2-4 shows the relationship between the bit VCO\_TUNE and VCO tuning on the first used service/channel configuration.

Table 2-4. Activation of VCO Tuning in Polling Mode

|                                          | Bit VCO_TUNE                |             | VCO Tuning During   |                                        |

|------------------------------------------|-----------------------------|-------------|---------------------|----------------------------------------|

|                                          | Polling Array Configuration | SPI Command | First Polling Cycle | Second - X <sup>th</sup> Polling Cycle |

| First Used Service/Channel Configuration | 0                           | 0           | -                   | -                                      |

|                                          | 0                           | 1           | x                   | -                                      |

|                                          | 1                           | 0           | x                   | x                                      |

|                                          | 1                           | 1           | x                   | x                                      |

Note: Activating the VCO\_TUNE bit only affects the mode ramp-up behavior of the first used service/channel configuration during the first polling cycle. This feature is not supported in fastPollingMode.

VCO tuning requires additional time. For more information, see Section 2.9 “Tune and Check” on page 50.

#### 2.8.4.7 RF Calibration

The temperature-dependent drift of the XTAL-based RF frequency can be optionally corrected for each service/channel configuration. A periodical temperature measurement by the host and update of the calib.tempMeas variable is recommended when the RF calibration feature is used. To enable the RF calibration for a specific service/channel configuration, set the RfCalib bit in the associated pollLoopConf[x].config configuration.

| Name                   | Bit 7   | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------------------|---------|-------|---------|-------|-------|-------|-------|-------|

| pollLoopConf[x].config | RfCalib | -     | VCOtune | -     | -     | -     | EOL   | EOP   |

The RF calibration requires additional time. For more information about the RF calibration, see Section 2.9 “Tune and Check” on page 50.

#### 2.8.5 Transitions to RXMode

The Atmel® ATA5785 firmware supports switching to RXMode(buffered) and RXMode(transparent) from

- IDLEMode(RC) and IDLEMode(XTO)

- RXMode (direct switch, not via IDLEMode)

The mode switching is completely controlled by firmware. The SFIFO and DFIFO are cleared during all direct switch operations.

A transition to PollingMode is only available from IDLEMode(RC) or IDLEMode(XTO).

## 2.8.6 Rx Telegram Handling

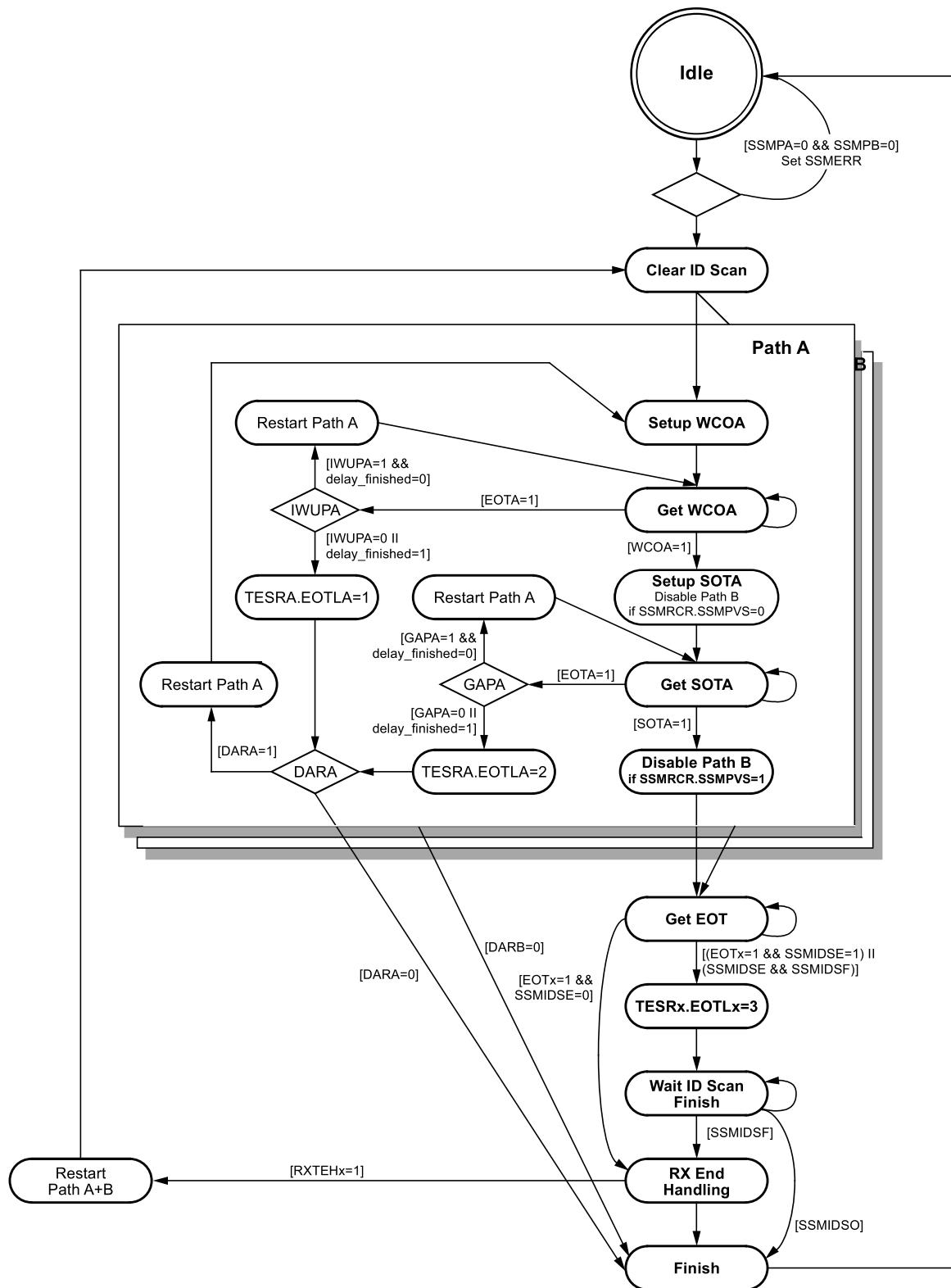

The reception of a telegram is performed in several phases within the Atmel® ATA5785. After the initialization and start-up phase the receiver checks for a valid RF signal which results in a wake check OK (WCO). The next step is to search the start frame ID (SFID) pattern that marks the beginning of the payload (start of telegram, SOT). The payload reception is terminated if an end of telegram (EOT) condition becomes true. Figure 2-15 on page 30 gives an overview of the receive telegram handling process.

**Figure 2-15. Receive Telegram Handling**

Note: Figure 2-15 shows the logical sequence of the telegram handling and does not reflect the implementation in firmware functions.

### 2.8.6.1 Initialization and Start-up

The initialization and start-up phase is used to

- Configure the internal hardware register according to the selected service and channel settings

- Configure the receive state machine according to the selected receive mode

- Enable the internal modules and monitor the PLL lock and filter settling times

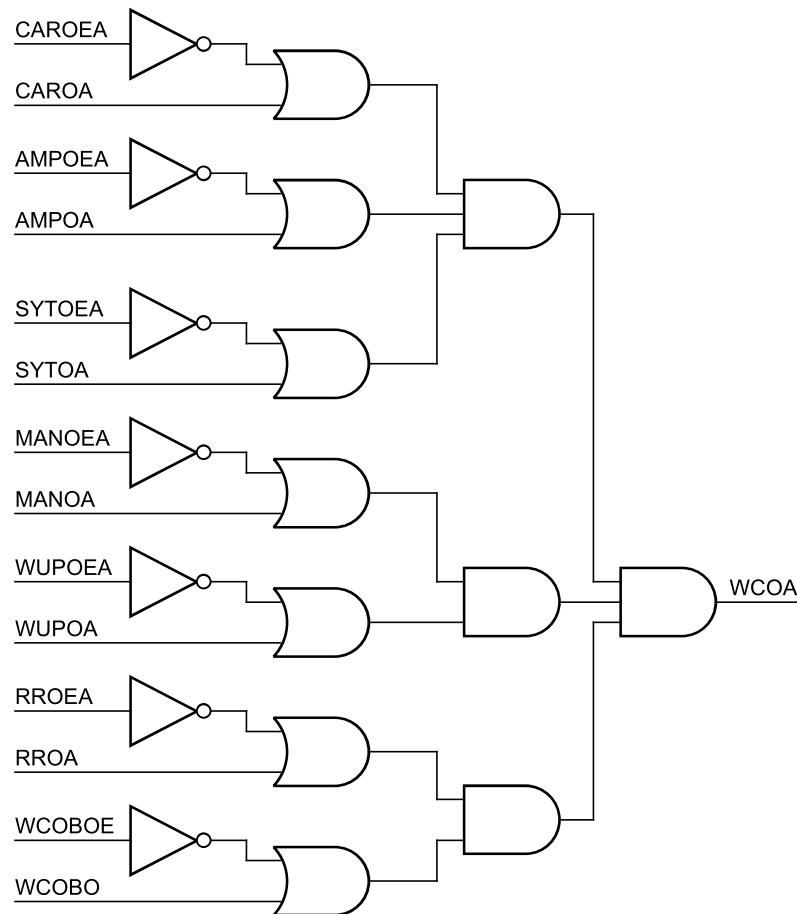

### 2.8.6.2 Wake Check OK (WCO)

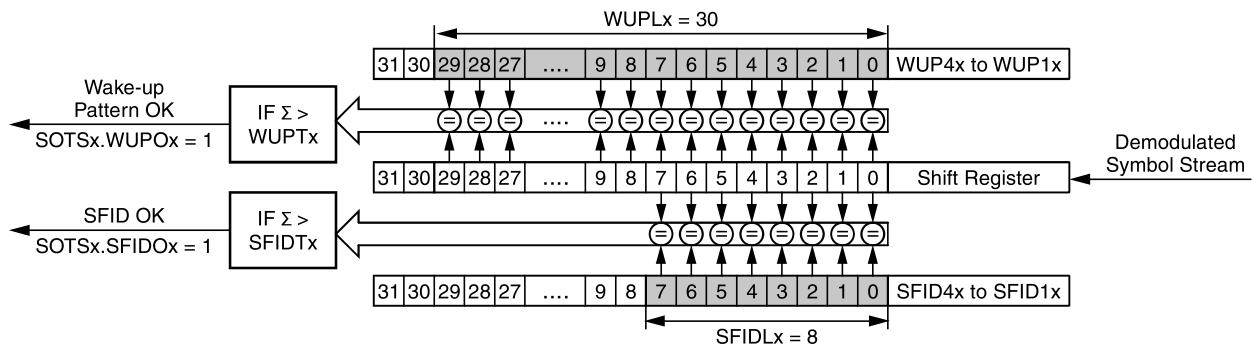

After the receiver is initialized and running, the RF input is checked for a valid signal. The detection of such a signal is called wake check OK (WCO). Several check conditions can be enabled independently for path A and path B of each service in the sramServices.SOT1x variables:

- Manchester coding check (MANOEx)

- Symbol timing check (SYTOEx)

- Modulation amplitude check (AMPOEx)

- Carrier check (CAROEx)

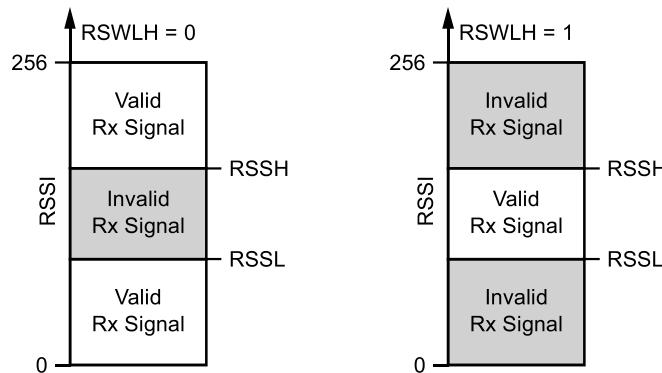

- RSSI range check (RROEx)

- Wake-up pattern check (WUPEx)

- Wake check OK from other path (WCOxOE)

| Address Service3 | Name  | Bit 7  | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|------------------|-------|--------|-------|--------|-------|--------|--------|--------|--------|

| 0x0352           | SOT1A | WCOBOE | RROEA | SFIDEA | WUPEA | MANOEA | SYTOEA | AMPOEA | CAROEA |

| 0x0353           | SOT1B | WCOAOE | RROEB | SFIDEB | WUPEB | MANOEB | SYTOEB | AMPOEB | CAROEB |

By default the Manchester, symbol timing, modulation amplitude, carrier (FSK only), and wake-up pattern checks are activated as a WCO condition. The SFID check cannot be activated as a WCO condition, but still the SFIDEx bit must always be set to "1" to avoid erroneous behavior of the internal state machine of the Atmel® ATA5785.

The functionality and configuration of the checks is described in detail in Section 2.8.7.3 "Telegram Settings and Signal Checks" on page 39.

If any of the following checks is enabled as a WCO check in the SOT1x variable, the corresponding EOT1x check (compare Section 2.8.6.5 "End of Telegram (EOT)" on page 33) must be activated: Manchester coding, symbol timing, modulation amplitude, carrier check, or RSSI range check.

| Address Service3 | Name  | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|------------------|-------|--------|-------|--------|--------|--------|--------|--------|--------|

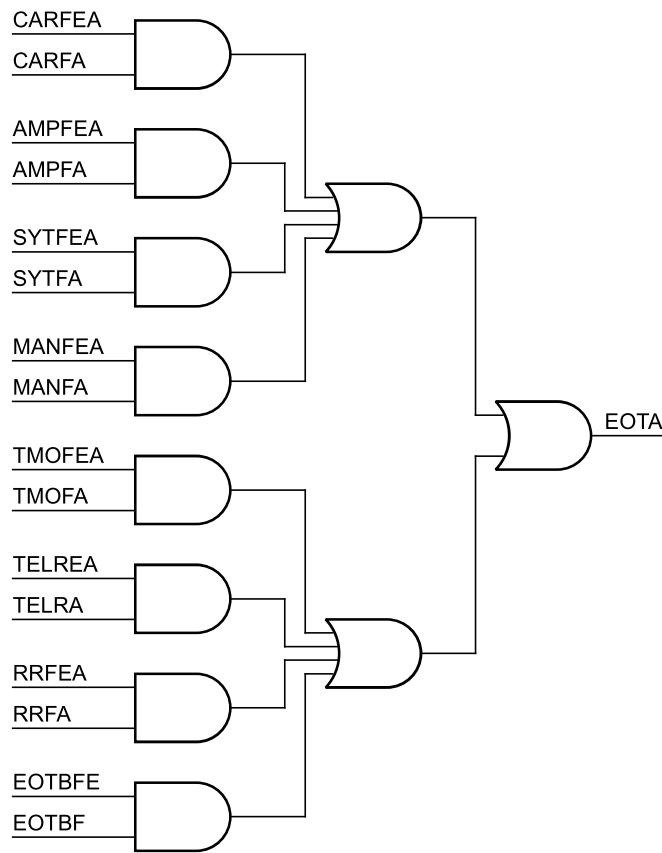

| 0x0327           | EOT1A | EOTBFE | RRFEA | TELREA | TMOFEA | MANFEA | SYTFEA | AMPFEA | CARFEA |

| 0x0328           | EOT1B | EOTAFE | RRFEB | TELREB | TMOFEB | MANFEB | SYTFEB | AMPFEB | CARFEB |

A WCO is triggered as soon as all enabled checks have passed; therefore, the time period from receiver start-up until a WCO is determined by the longest check.

If a WCO is received on one path, the other path is switched off unless the sramServices.rxSysSet.PathValidAfterSOT\_ENA SRAM variable is set to "1". Then the other path is switched off not before the SOT event. If both paths receive the WCO/SOT event at the same clock cycle, path A wins.

| Address Service3 | Name     | Bit 7 | Bit 6      | Bit 5           | Bit 4                  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------------|----------|-------|------------|-----------------|------------------------|-------|-------|-------|-------|

| 0x0345           | rxSysSet | -     | IdScan_ENA | IFAmplifier_ENA | PathValid AfterSOT_ENA | -     | -     | -     | -     |

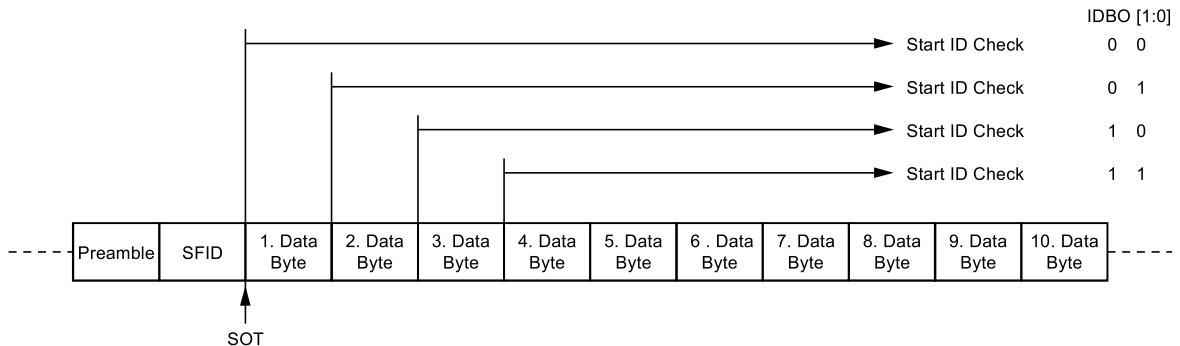

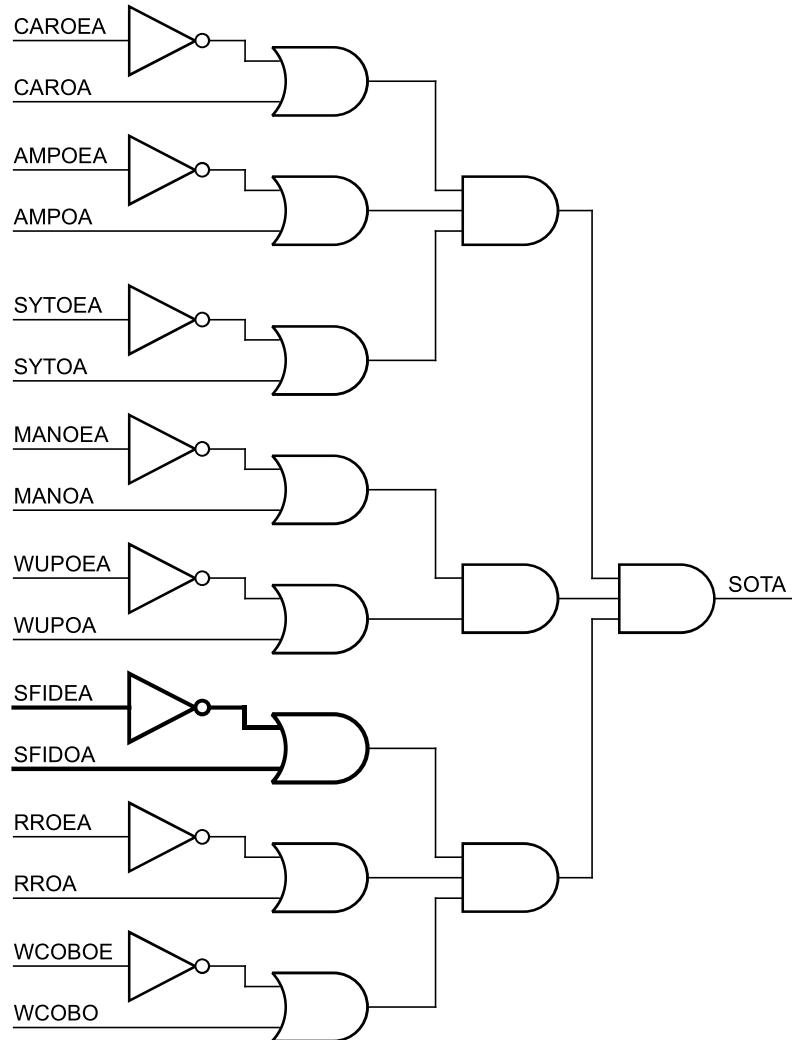

### 2.8.6.3 Start of Telegram (SOT)

A WCO indicates that a valid RF signal is present. Now the precise start of the data payload must be determined. This event is called start of telegram (SOT). The SOT is usually determined by a well-defined start frame ID (SFID) pattern. The following SOT check conditions can be enabled independently for path A and path B of each service in the sramServices.SOT2x variables:

- Manchester coding check (MANOEx)

- Symbol timing check (SYTOEx)

- Modulation amplitude check (AMPOEx)

- Carrier check (CAROEx)

- RSSI range check (RROEx)

- Wake-up pattern check (WUPEx)

- Start frame ID pattern check (SFIDEx)

- Wake check OK from other path (WCOxOE)

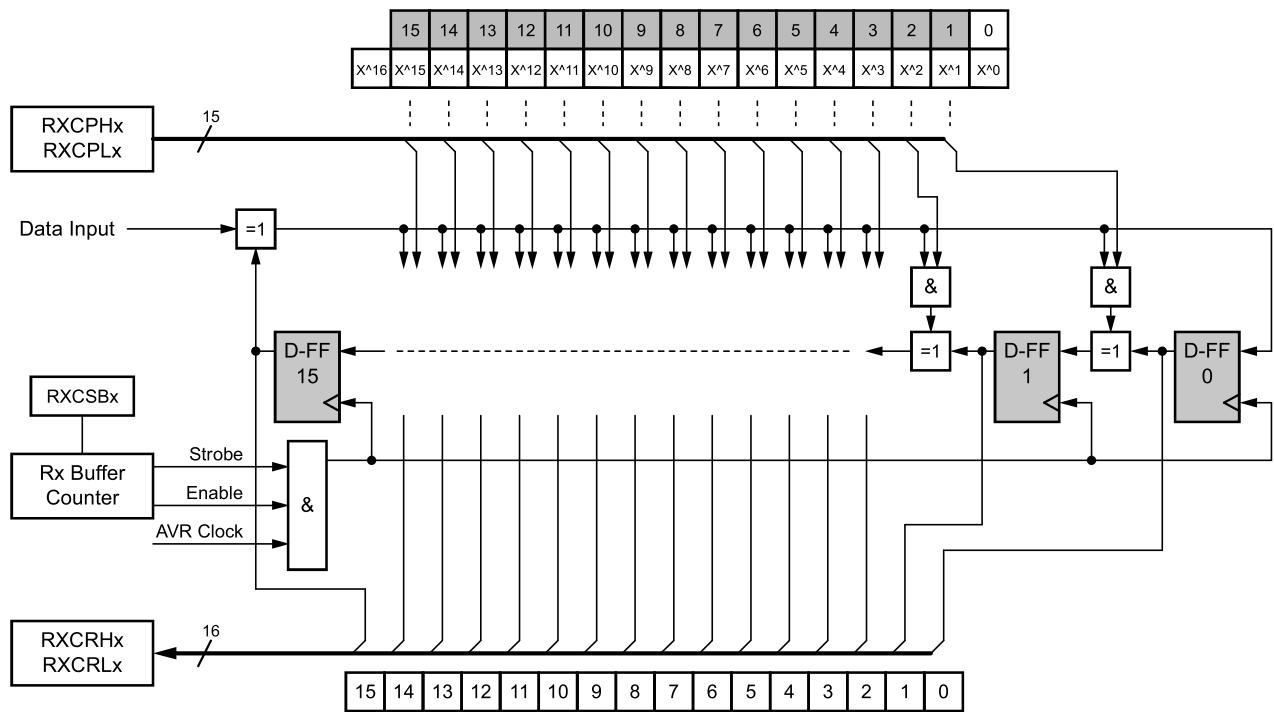

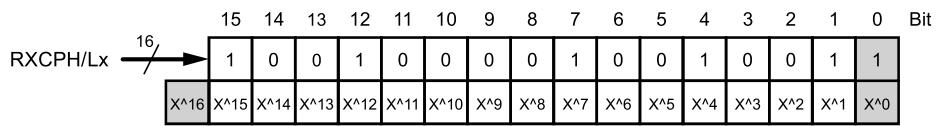

| Address Service3 | Name  | Bit 7  | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |