### **Attendo Classic Main PCBA Circuit Description**

U101 is telephone specific function MCU SH93P426, it performs Battery Management, Charging control, RF Receiver Module Control, Speakerphone IC control, Telephone Line inteface control and DTMF decoding/Encoding.

U103 HT24LC04 is EEPROM for storing the telephone number. U102 G699 monitor the power supply voltage level for MCU.

The Telephone Line Interface circuit is consisted of J201, J202, F201, D201, D204~D207, Q201~Q208. F201 and D201 performs the transient voltage suppression function; Q204, Q205 and U201-D performs the Ringing signal detect function; U201-A, U201-B and U201-C performes the telephone line state monitoring function; Q201, Q202 and Q203 performs the Hook On/Off control function; Q206, Q207, Q208 and their peripherals perform the Tx audio signal and Rx audio signal amplifying, echol cancelling.

U301 U4082B, U303 MC34119 and their peripherals constitute the Speakerphone Duplexer circuit. U4082B is consisted of Audio Signal Level Detector of Tx and Rx, Attenuator and MIC AMP, it can switch between Tx path and Rx path according the audio signal level detected. MC34119 is audio AMP to drive speaker.

D402~D405 and LM317MDT performs the AC input power supply rectifying and regulating. This is the powe supply for whole product and

Battery charging circuit.

Q401, Q402, U403-A, U403-B and their peripherals perform the Battery voltage level monitoring and battery re-charging. Once the low battery voltage level signal is sent to MCU, then MCU can control the charging circuit to charge the battery. The MCU will terminate the charging process once the battery high voltage level detected and charging timing is out.

U402 XC6201T331, Q403 and Q404 performs the DC power supply control and distribution. U402 is LDO to provide Vcc for MCU circuit. Q403 and Q404 switch on or off the power supply for Speakerphone Circuit under the control of MCU.

### **Attendo Classic RF Receiver Module Circuit Description**

U1 LP2985 is LDO to provide Vcc voltage for MCU ATTiny26L and RF transceiver IC CC1021.

U2 CC1021 is the RF transceiver IC, it consists of below parts:

- two stage LNA with gain controlled externally;

- Quadrature down converter, IF BPF and AMP;

- VCO and quatrature divider;

- PLL Loop and PLL controller;

- Digital Demodulator.

The external LNA consists BFG425W and it's peripheral circuits.

The SAW filter prevent interference and increase the EMS performance of the units.

The antenna is a wire type quarter wave length antenna, it is permanently attached on RF Module.

Crystal 14.7456MHz is for CC1021.

MCU ATTiny26L performs the RF Transceiver control, it is also the interface with Main PCBA MCU.

### **CC1021** Single Chip Low Power RF Transceiver for Narrowband Systems

### **Applications**

- Low power UHF wireless data transmitters and receivers with channel spacings of 50 kHz or higher

- 433, 868 and 915 MHz ISM/SRD band systems

- AMR Automatic Meter Reading

- Wireless alarm and security systems

- Home automation

- Low power telemetry

- Automotive (RKE/TPMS)

### **Product Description**

*CC1021* is a true single-chip UHF transceiver designed for very low power and very low voltage wireless applications. The circuit is mainly intended for the ISM (Industrial, Scientific and Medical) and SRD (Short Range Device) frequency bands at 433, 868 and 915 MHz, but can easily be programmed for multi-channel operation at other frequencies in the 402 - 470 and 804 - 940 MHz range.

The *CC1021* is especially suited for narrowband systems with channel spacings of 50 kHz and higher complying with EN 300 220 and FCC CFR47 part 15.

The *CC1021* main operating parameters can be programmed via a serial bus, thus making *CC1021* a very flexible and easy to use transceiver.

In a typical system *CC1021* will be used together with a microcontroller and a few external passive components.

*CC1021* is based on Chipcon's SmartRF $^{\otimes}$ -02 technology in 0.35  $\mu m$  CMOS.

#### **Features**

- True single chip UHF RF transceiver

- Frequency range 402 MHz 470 MHz and 804 MHz - 940 MHz

- High sensitivity (up to -112 dBm for 38.4 kHz and -106 dBm for 102.4 kHz receiver channel filter bandwidths respectively)

- Programmable output power

- Low current consumption (RX: 19.9 mA)

- Low supply voltage (2.3 V to 3.6 V)

- Very few external components required

- Small size (QFN 32 package)

- · Pb-free package

- · Digital RSSI and carrier sense indicator

- Data rate up to 153.6 kBaud

- OOK, FSK and GFSK data modulation

- Integrated bit synchronizer

- · Image rejection mixer

- Programmable frequency

- Automatic frequency control (AFC)

- Suitable for frequency hopping systems

- Suited for systems targeting compliance with EN 300 220 and FCC CFR47 part 15

- Development kit available

- Easy-to-use software for generating the *CC1021* configuration data

- Fully compatible with CC1020 for receiver channel filter bandwidths of 38.4 kHz and higher

### **Table of Contents**

| 1.  | Abbre  | viations                                                       | 4  |

|-----|--------|----------------------------------------------------------------|----|

| 2.  | Absol  | ute Maximum Ratings                                            | 5  |

| 3.  | Opera  | ting Conditions                                                | 5  |

| 4.  | Electr | ical Specifications                                            | 5  |

|     | 4.1.   | RF Transmit Section                                            | 6  |

|     | 4.2.   | RF Receive Section                                             | 8  |

|     | 4.3.   | RSSI / Carrier Sense Section                                   | 11 |

|     | 4.4.   | IF Section                                                     | 11 |

|     | 4.5.   | Crystal Oscillator Section                                     | 12 |

|     | 4.6.   | Frequency Synthesizer Section                                  | 13 |

|     | 4.7.   | Digital Inputs / Outputs                                       | 14 |

|     | 4.8.   | Current Consumption                                            | 15 |

| 5.  | Pin As | ssignment                                                      | 15 |

| 6.  | Circui | t Description                                                  | 17 |

| 7.  | Applic | cation Circuit                                                 | 18 |

| 8.  | Config | guration Overview                                              | 21 |

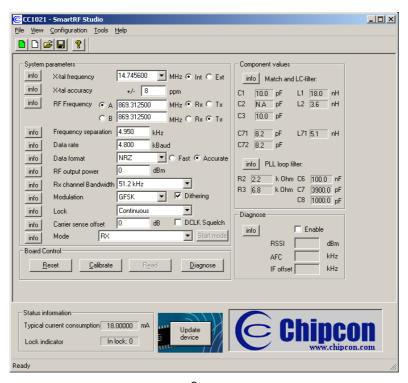

|     | 8.1.   | Configuration Software                                         | 21 |

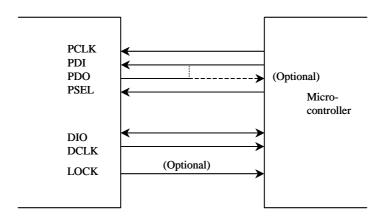

| 9.  | Micro  | controller Interface                                           | 22 |

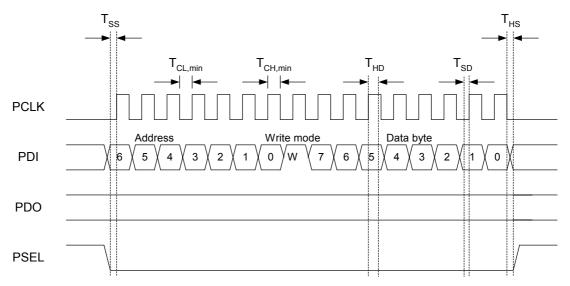

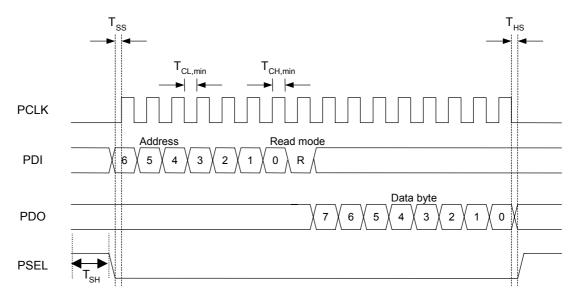

|     | 9.1.   | 4-wire Serial Configuration Interface                          | 23 |

|     | 9.2.   | Signal Interface                                               | 25 |

| 10. | Data F | Rate Programming                                               | 27 |

| 11. | Frequ  | ency Programming                                               | 28 |

|     | 11.1.  | Dithering                                                      | 29 |

| 12. | Recei  | ver                                                            | 30 |

|     | 12.1.  | IF Frequency                                                   | 30 |

|     | 12.2.  | Receiver Channel Filter Bandwidth                              | 30 |

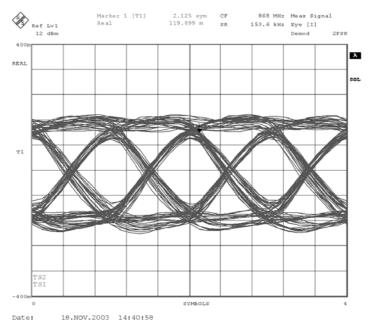

|     | 12.3.  | Demodulator, Bit Synchronizer and Data Decision                | 31 |

|     | 12.4.  | Receiver Sensitivity versus Data Rate and Frequency Separation | 32 |

|     | 12.5.  | RSSI                                                           | 33 |

|     | 12.6.  | Image Rejection Calibration                                    | 35 |

|     | 12.7.  | Blocking and Selectivity                                       | 36 |

|     | 12.8.  | Linear IF Chain and AGC Settings                               | 38 |

|     | 12.9.  | AGC Settling                                                   | 40 |

|     | 12.10. | Preamble Length and Sync Word                                  | 40 |

|     | 12.11. | Carrier Sense                                                  | 41 |

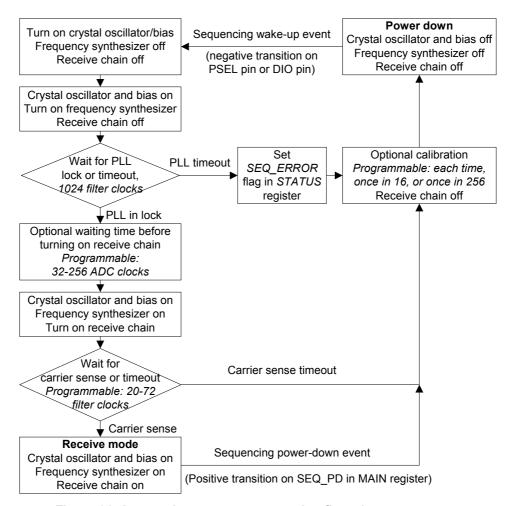

|     | 12.12. | Automatic Power-up Sequencing                                  | 41 |

|     | 12.13. | Automatic Frequency Control                                    | 42 |

|             | 12.14.   | Digital FM                                          | 43 |

|-------------|----------|-----------------------------------------------------|----|

| 13.         | Transn   | nitter                                              | 44 |

|             | 13.1.    | FSK Modulation Formats                              | 44 |

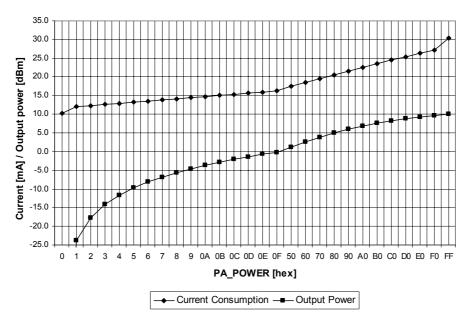

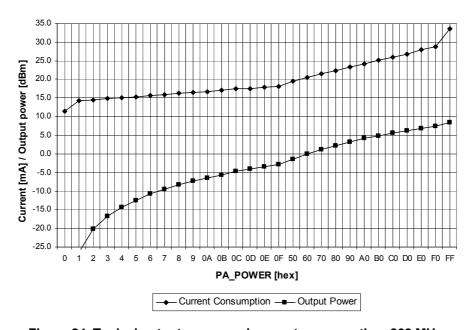

|             | 13.2.    | Output Power Programming                            | 44 |

|             | 13.3.    | Reducing Spurious Emission and Modulation Bandwidth | 46 |

| 14.         | Input /  | Output Matching and Filtering                       | 46 |

| 15.         | Freque   | ency Synthesizer                                    | 50 |

|             | 15.1.    | VCO, Charge Pump and PLL Loop Filter                | 50 |

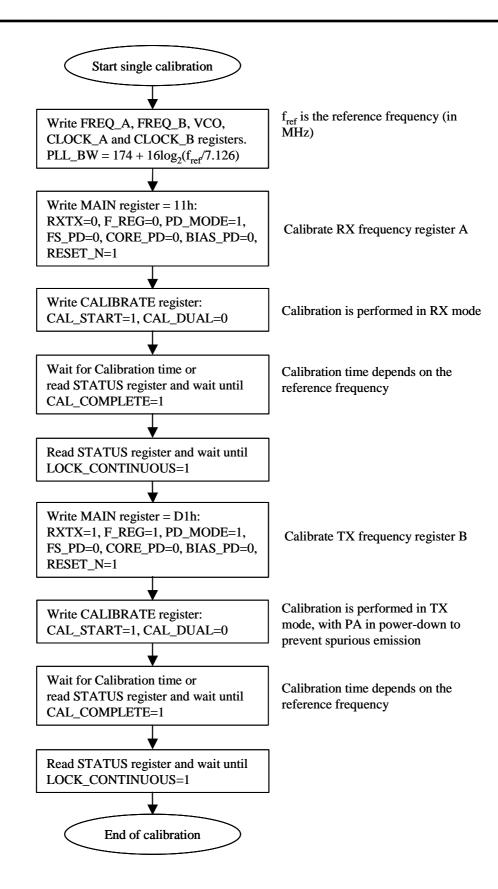

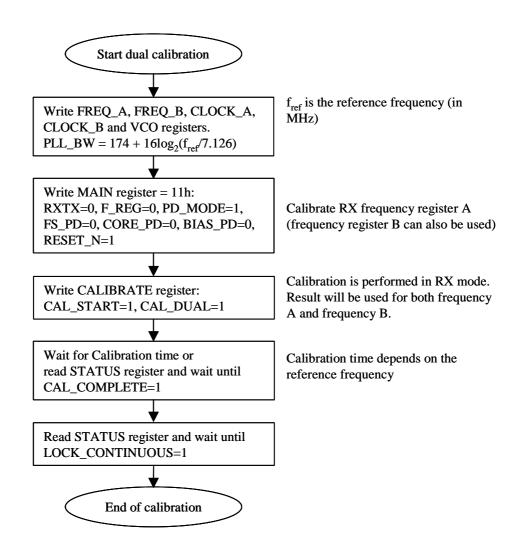

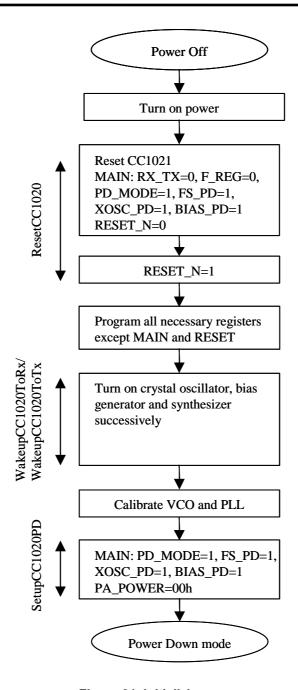

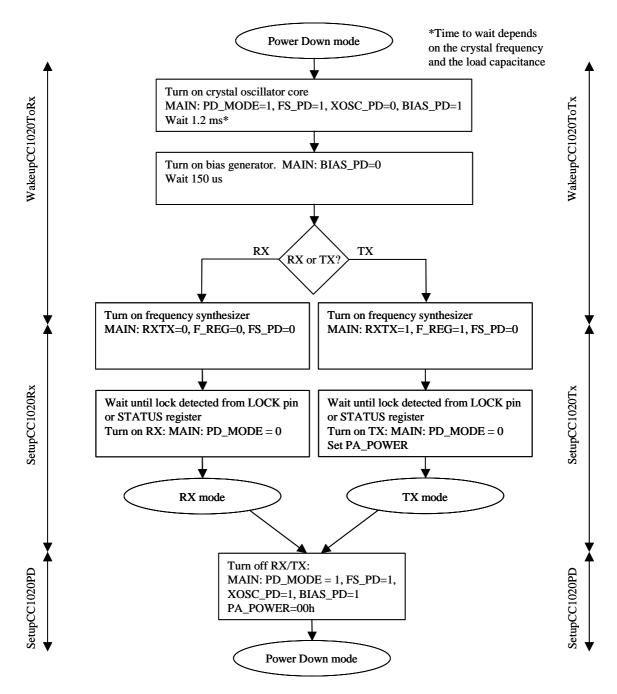

|             | 15.2.    | VCO and PLL Self-Calibration                        | 51 |

|             | 15.3.    | PLL Turn-on Time versus Loop Filter Bandwidth       | 54 |

|             | 15.4.    | PLL Lock Time versus Loop Filter Bandwidth          | 54 |

| 16.         | VCO a    | nd LNA Current Control                              | 54 |

| 17.         | Power    | Management                                          | 55 |

| 18.         | On-Off   | Keying (OOK)                                        | 57 |

| 19.         | Crysta   | l Oscillator                                        | 59 |

| 20.         | Built-ir | n Test Pattern Generator                            | 60 |

| 21.         | Interru  | pt on Pin DCLK                                      | 61 |

|             | 21.1.    | Interrupt upon PLL Lock                             | 61 |

|             | 21.2.    | Interrupt upon Received Signal Carrier Sense        | 61 |

| <b>22</b> . | PA_EN    | I and LNA_EN Digital Output Pins                    | 62 |

|             | 22.1.    | Interfacing an External LNA or PA                   | 62 |

|             | 22.2.    | General Purpose Output Control Pins                 | 62 |

|             | 22.3.    | PA_EN and LNA_EN Pin Drive                          | 62 |

| 23.         | Systen   | n Considerations and Guidelines                     | 63 |

| 24.         | PCB La   | ayout Recommendations                               | 65 |

| <b>25</b> . | Antenr   | na Considerations                                   | 65 |

| 26.         | Config   | uration Registers                                   | 66 |

|             | 26.1.    | CC1021 Register Overview                            | 67 |

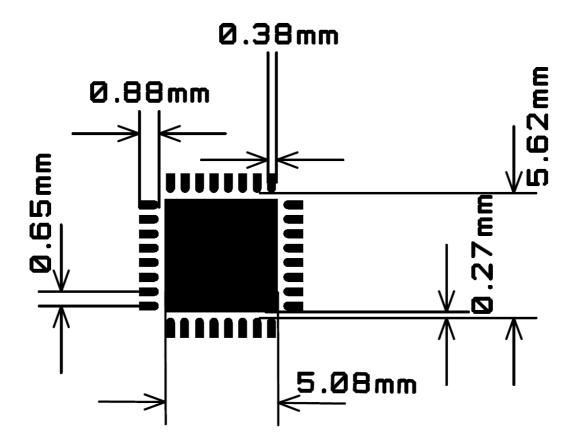

| <b>27</b> . | Packaç   | ge Description (QFN 32)                             | 87 |

|             | 27.1.    | Package Marking                                     | 88 |

|             | 27.2.    | Recommended PCB Footprint for Package (QFN 32)      | 89 |

|             | 27.3.    | Package Thermal Properties                          | 89 |

|             | 27.4.    | Soldering Information                               | 89 |

|             | 27.5.    | Plastic Tube Specification                          | 90 |

|             | 27.6.    | Carrier Tape and Reel Specification                 | 90 |

| 28.         | Orderi   | ng Information                                      | 90 |

| 29.         | Genera   | al Information                                      | 91 |

| 30.         | Addres   | ss Information                                      | 93 |

### 1. Abbreviations

ACP Adjacent Channel Power

ACR Adjacent Channel Rejection

ADC Analog-to-Digital Converter

AFC Automatic Frequency Control

AGC Automatic Gain Control

AMR Automatic Meter Reading

ASK Amplitude Shift Keying

BER Bit Error Rate

BOM Bill Of Materials

bps bits per second

BT Bandwidth-Time product (for GFSK)

ChBW Receiver Channel Filter Bandwidth

CW Continuous Wave

DAC Digital-to-Analog Converter

DNM Do Not Mount

ESR Equivalent Series Resistance

FHSS Frequency Hopping Spread Spectrum

FM Frequency Modulation FS Frequency Synthesizer FSK Frequency Shift Keying

GFSK Gaussian Frequency Shift Keying

ICIntegrated CircuitIFIntermediate FrequencyIP3Third Order Intercept PointISMIndustrial Scientific Medical

kbps kilo bits per second LNA Low Noise Amplifier

LO Local Oscillator (in receive mode)

MCU Micro Controller Unit

NRZ Non Return to Zero

OOK On-Off Keying

PA Power Amplifier

PD Phase Detector / Power Down

PER Packet Error Rate

PCB Printed Circuit Board

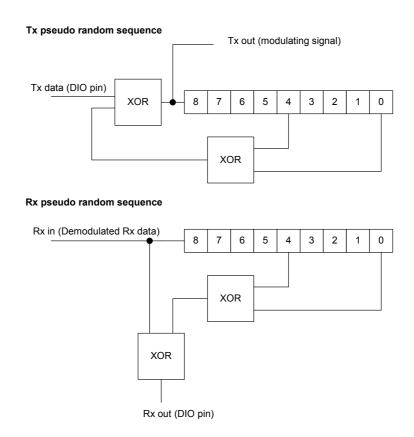

PN9 Pseudo-random Bit Sequence (9-bit)

PLL Phase Locked Loop

PSEL Program Select

RF Radio Frequency

RKE Remote Keyless Entry

RSSI Received Signal Strength Indicator

RX Receive (mode) SBW Signal Bandwidth

SPI Serial Peripheral Interface

SRD Short Range Device

TBD To Be Decided/Defined

TPMS Tire Pressure Monitoring

T/R Transmit/Receive (switch)

TX Transmit (mode)

UHF Ultra High Frequency

VCO Voltage Controlled Oscillator

VGA Variable Gain Amplifier

XOSC Crystal oscillator

XTAL Crystal

### 2. Absolute Maximum Ratings

The absolute maximum ratings given Table 1 should under no circumstances be violated. Stress exceeding one or more of the limiting values may cause permanent damage to the device.

| Parameter                 | Min  | Max              | Unit | Condition                                  |

|---------------------------|------|------------------|------|--------------------------------------------|

| Supply voltage, VDD       | -0.3 | 5.0              | V    | All supply pins must have the same voltage |

| Voltage on any pin        | -0.3 | VDD+0.3, max 5.0 | V    |                                            |

| Input RF level            |      | 10               | dBm  |                                            |

| Storage temperature range | -50  | 150              | °C   |                                            |

| Package body temperature  |      | 250              | °C   | Norm: IPC/JEDEC J-STD-020B 1               |

| Humidity non-condensing   | 5    | 85               | %    |                                            |

| ESD                       |      | ±1               | kV   | All pads except RF                         |

| (Human Body Model)        |      | ±0.4             | kV   | RF Pads                                    |

Table 1. Absolute maximum ratings

<sup>&</sup>lt;sup>1</sup> The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD\_020B "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices".

Caution! ESD sensitive device.

Precaution should be used when handling

the device in order to prevent permanent

damage.

### 3. Operating Conditions

The operating conditions for *CC1021* are listed in Table 2.

| Parameter                           | Min        | Тур | Max        | Unit       | Condition / Note                                                                   |

|-------------------------------------|------------|-----|------------|------------|------------------------------------------------------------------------------------|

| RF Frequency Range                  | 402<br>804 |     | 470<br>940 | MHz<br>MHz | Programmable in <300 Hz steps<br>Programmable in <600 Hz steps                     |

| Operating ambient temperature range | -40        |     | 85         | °C         |                                                                                    |

| Supply voltage                      | 2.3        | 3.0 | 3.6        | V          | The same supply voltage should be used for digital (DVDD) and analog (AVDD) power. |

**Table 2. Operating conditions**

### 4. Electrical Specifications

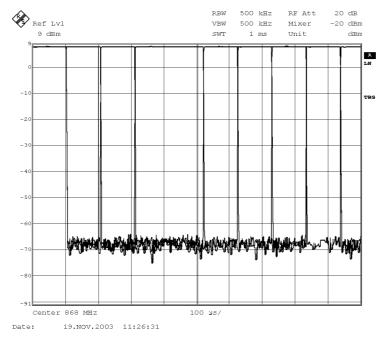

Table 3 to Table 10 gives the *CC1021* electrical specifications. All measurements were performed using the 2 layer PCB CC1020EMX reference design. This is the same test circuit as shown in Figure 3. Temperature =  $25^{\circ}$ C, supply voltage = AVDD = DVDD = 3.0 V if nothing else stated. Crystal frequency = 14.7456 MHz.

The electrical specifications given for 868 MHz are also applicable for the 902 – 928 MHz frequency range.

### 4.1. RF Transmit Section

| Parameter                                                                                                     | Min    | Тур        | Max        | Unit       | Condition / Note                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------|--------|------------|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit data rate                                                                                            | 0.45   |            | 153.6      | kBaud      | The data rate is programmable.<br>See section 10 on page 27 for<br>details.                                                                                                         |

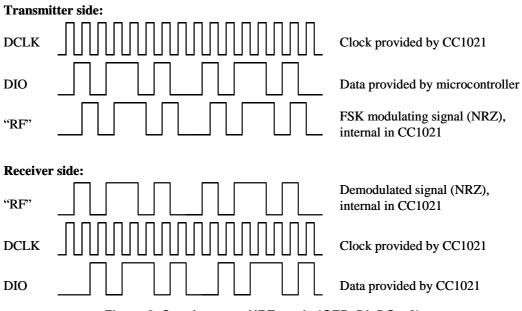

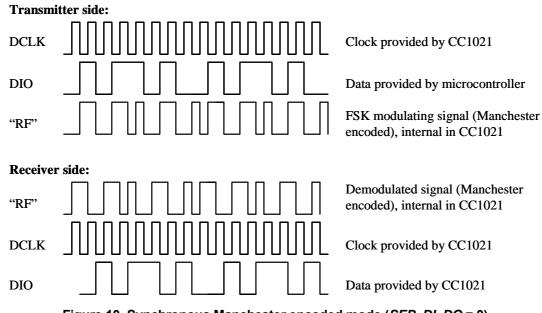

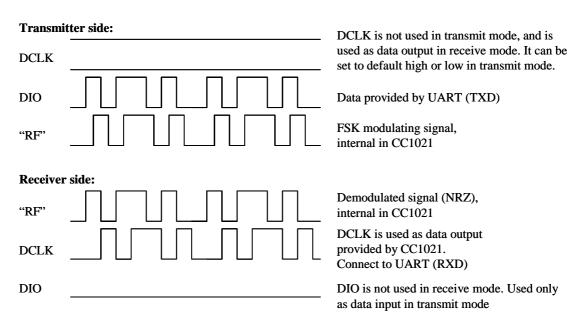

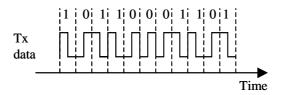

|                                                                                                               |        |            |            |            | NRZ or Manchester encoding can<br>be used. 153.6 kBaud equals<br>153.6 kbps using NRZ coding<br>and 76.8 kbps using Manchester<br>coding. See section 9.2 on page<br>25 for details |

|                                                                                                               |        |            |            |            | Minimum data rate for OOK is 2.4 kBaud                                                                                                                                              |

| Binary FSK frequency separation                                                                               | 0<br>0 |            | 108<br>216 | kHz<br>kHz | in 402 - 470 MHz range<br>in 804 - 940 MHz range                                                                                                                                    |

|                                                                                                               |        |            |            |            | 108/216 kHz is the maximum<br>guaranteed separation at 1.84<br>MHz reference frequency. Larger<br>separations can be achieved at<br>higher reference frequencies.                   |

|                                                                                                               |        |            |            |            | The frequency separation is programmable in 112.5/225 Hz steps when using a 14.7456 MHz crystal and REF_DIV=1. See section 11 on page 28 for details.                               |

| Output power 433 MHz                                                                                          |        | -20 to +10 |            | dBm        | Delivered to 50 $\Omega$ single-ended load. The output power is                                                                                                                     |

| 868 MHz                                                                                                       |        | -20 to +5  |            | dBm        | programmable and should not be<br>programmed to exceed +10/+5<br>dBm at 433/868 MHz under any<br>operating conditions. See section<br>14 on page 46 for details.                    |

| Output power tolerance                                                                                        |        | -4<br>+3   |            | dB<br>dB   | At maximum output power<br>At 2.3 V, +85°C<br>At 3.6 V, -40°C                                                                                                                       |

| Harmonics, radiated CW  2 <sup>nd</sup> harmonic, 433 MHz, +10 dBm 3 <sup>rd</sup> harmonic, 433 MHz, +10 dBm |        | -50<br>-50 |            | dBc<br>dBc | Harmonics are measured as EIRP values according to EN 300 220. The antenna (SMAFF-433 and SMAFF-868 from R.W.                                                                       |

| 2 <sup>nd</sup> harmonic, 868 MHz, +5 dBm<br>3 <sup>rd</sup> harmonic, 868 MHz, +5 dBm                        |        | -50<br>-50 |            | dBc<br>dBc | Badland) plays a part in attenuating the harmonics.                                                                                                                                 |

| Adjacent channel power (GFSK)                                                                                 |        |            |            |            | ACP is measured in a 100 kHz                                                                                                                                                        |

| 433 MHz                                                                                                       |        | -46        |            | dBc        | bandwidth at ±100 kHz offset.  Modulation: 19.2 kBaud NRZ PN9 sequence, ±19.8 kHz                                                                                                   |

| 868 MHz                                                                                                       |        | -42        |            | dBc        | frequency deviation.                                                                                                                                                                |

| Occupied bandwidth (99.5%,GFSK)                                                                               |        | 2-         |            |            | Bandwidth for 99.5% of total average power.                                                                                                                                         |

| 433 MHz                                                                                                       |        | 60         |            | kHz        | Modulation: 19.2 kBaud NRZ                                                                                                                                                          |

| 868 MHz                                                                                                       |        | 60         |            | kHz        | PN9 sequence, ±19.8 kHz frequency deviation.                                                                                                                                        |

| Parameter                                 | Min | Тур      | Max | Unit | Condition / Note                                                                                                                                                           |

|-------------------------------------------|-----|----------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Modulation bandwidth, 868 MHz             |     |          |     |      | Bandwidth where the power                                                                                                                                                  |

| 19.2 kBaud, ±9.9 kHz frequency deviation  |     | 48       |     | kHz  | envelope of modulation equals  -36 dBm. Spectrum analyzer  RBW = 1 kHz.                                                                                                    |

| 38.4 kBaud, ±19.8 kHz frequency deviation |     | 106      |     | kHz  | TAIL.                                                                                                                                                                      |

| Spurious emission, radiated CW            |     |          |     |      | At maximum output power,<br>+10/+5 dBm at 433/868 MHz.                                                                                                                     |

| 47-74, 87.5-118,<br>174-230, 470-862 MHz  |     |          | -54 | dBm  | To comply with EN 300 220,<br>FCC CFR47 part 15 and ARIB                                                                                                                   |

| 9 kHz – 1 GHz                             |     |          | -36 | dBm  | STD T-67 an external (antenna) filter, as implemented in the                                                                                                               |

| 1 – 4 GHz                                 |     |          | -30 | dBm  | application circuit in Figure 25, must be used and tailored to each individual design to reduce out-of-band spurious emission levels.                                      |

|                                           |     |          |     |      | Spurious emissions are measured as EIRP values according to EN 300 220. The antenna (SMAFF-433 and SMAFF-868 from R.W. Badland) plays a part in attenuating the harmonics. |

|                                           |     |          |     |      | If the output power is increased using an external PA, a filter must be used to attenuate spurs below 862 MHz.                                                             |

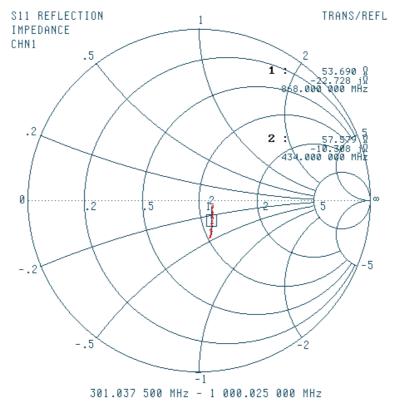

| Optimum load impedance                    |     |          |     |      | Transmit mode. For matching                                                                                                                                                |

| 433 MHz                                   |     | 54 + j44 |     | Ω    | details see section 14 on page 46.                                                                                                                                         |

| 868 MHz                                   |     | 15 + j24 |     | Ω    |                                                                                                                                                                            |

| 915 MHz                                   |     | 20 + j35 |     | Ω    |                                                                                                                                                                            |

Table 3. RF transmit parameters

### 4.2. RF Receive Section

| Parameter                                       | Min | Тур                 | Max | Unit       | Condition / Note                                                                                                                |

|-------------------------------------------------|-----|---------------------|-----|------------|---------------------------------------------------------------------------------------------------------------------------------|

| Receiver Sensitivity, 433 MHz, FSK              |     |                     |     |            | Sensitivity is measured with PN9 sequence at BER = 10 <sup>-3</sup>                                                             |

| 38.4 kHz channel filter BW (1)                  |     | -109                |     | dBm        | (1) 38.4 kHz receiver channel filter bandwidth: 4.8 kBaud, NRZ coded data, ±4.95 kHz frequency deviation.                       |

| 102.4 kHz channel filter BW (2)                 |     | -104                |     | dBm        | (2) 102.4 kHz receiver channel filter bandwidth: 19.2 kBaud, NRZ coded data, ±19.8 kHz frequency deviation.                     |

| 102.4 kHz channel filter BW (3)                 |     | -104                |     | dBm        | (3) 102.4 kHz receiver channel filter bandwidth: 38.4 kBaud, NRZ coded data, ±19.8 kHz frequency deviation.                     |

| 307.2 kHz channel filter BW (4)                 |     | -96                 |     | dBm        | (4) 307.2 kHz receiver channel filter bandwidth: 153.6 kBaud, NRZ coded data, ±72 kHz frequency deviation.                      |

| Receiver Sensitivity, 868 MHz, FSK              |     |                     |     |            | See Table 19 and Table 20 or                                                                                                    |

| 38.4 kHz channel filter BW (1)                  |     | -108                |     | dBm        | typical sensitivity figures at other channel filter bandwidths.                                                                 |

| 102.4 kHz channel filter BW (2)                 |     | -103                |     | dBm        | Chamer mer bandwidths.                                                                                                          |

| 102.4 kHz channel filter BW (3)                 |     | -103                |     | dBm        |                                                                                                                                 |

| 307.2 kHz channel filter BW (4)                 |     | -94                 |     | dBm        |                                                                                                                                 |

| Receiver sensitivity, 433 MHz, OOK              |     |                     |     |            | Sensitivity is measured with PN9 sequence at BER = 10 <sup>-3</sup>                                                             |

| 9.6 kBaud<br>153.6 kBaud                        |     | -103<br>-81         |     | dBm<br>dBm | Manchester coded data.                                                                                                          |

| Receiver sensitivity, 868 MHz, OOK              |     |                     |     |            | See Table 27 for typical                                                                                                        |

| 9.6 kBaud<br>153.6 kBaud                        |     | -104<br>-87         |     | dBm<br>dBm | sensitivity figures at other data rates.                                                                                        |

| Saturation (maximum input level)<br>FSK and OOK |     | 10                  |     | dBm        | FSK: Manchester/NRZ coded data OOK: Manchester coded data BER = 10 <sup>-3</sup>                                                |

| System noise bandwidth                          |     | 38.4<br>to<br>307.2 |     | kHz        | The receiver channel filter 6 dB bandwidth is programmable from 38.4 kHz to 307.2 kHz. See section 12.2 on page 30 for details. |

| Noise figure, cascaded<br>433 and 868 MHz       |     | 7                   |     | dB         | NRZ coded data                                                                                                                  |

| Parameter                                                                                                                                                                                       | Min | Тур                              | Max | Unit                 | Condition / Note                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|-----|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input IP3                                                                                                                                                                                       |     |                                  |     |                      | Two tone test (+10 MHz and +20 MHz)                                                                                                                                                                                          |

| 433 MHz 102.4 kHz channel filter BW                                                                                                                                                             |     | -23<br>-18<br>-16                |     | dBm<br>dBm<br>dBm    | LNA2 maximum gain<br>LNA2 medium gain<br>LNA2 minimum gain                                                                                                                                                                   |

| 868 MHz 102.4 kHz channel filter BW                                                                                                                                                             |     | -18<br>-15<br>-13                |     | dBm<br>dBm<br>dBm    | LNA2 maximum gain<br>LNA2 medium gain<br>LNA2 minimum gain                                                                                                                                                                   |

| Co-channel rejection, FSK and OOK                                                                                                                                                               |     | -11                              |     | dB                   | Wanted signal 3 dB above the                                                                                                                                                                                                 |

| 433 MHz and 868 MHz,<br>102.4 kHz channel filter BW,                                                                                                                                            |     | -11                              |     | ub                   | sensitivity level, CW jammer at operating frequency, BER = 10 <sup>-3</sup>                                                                                                                                                  |

| Adjacent channel rejection (ACR)                                                                                                                                                                |     |                                  |     |                      | Wanted signal 3 dB above the                                                                                                                                                                                                 |

| 433 MHz 102.4 kHz channel filter BW                                                                                                                                                             |     | 32                               |     | dB                   | sensitivity level, CW jammer at adjacent channel, BER = 10 <sup>-3</sup> .                                                                                                                                                   |

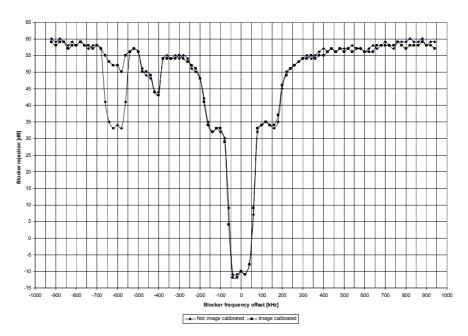

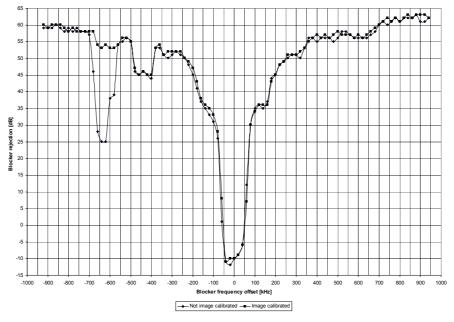

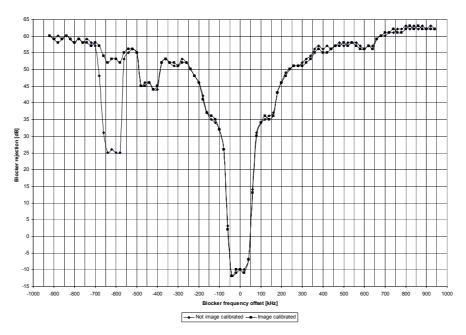

| 868 MHz 102.4 kHz channel filter BW                                                                                                                                                             |     | 30                               |     | dB                   | Measured at ±100 kHz offset.<br>See Figure 16 to Figure 19.                                                                                                                                                                  |

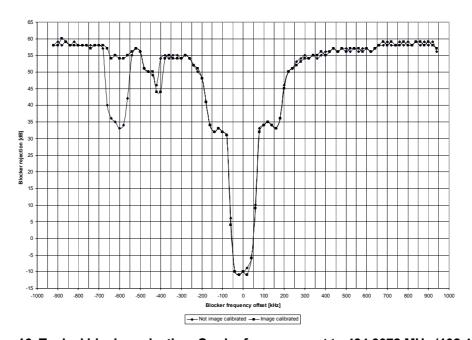

| Image channel rejection<br>433/868 MHz                                                                                                                                                          |     |                                  |     |                      | Wanted signal 3 dB above the sensitivity level, CW jammer at image frequency, BER = 10 <sup>-3</sup> .                                                                                                                       |

| No I/Q gain and phase calibration                                                                                                                                                               |     | 25/25                            |     | dB                   | 102.4 kHz channel filter bandwidth. See Figure 16 to                                                                                                                                                                         |

| I/Q gain and phase calibrated                                                                                                                                                                   |     | 50/50                            |     | dB                   | Figure 19.                                                                                                                                                                                                                   |

|                                                                                                                                                                                                 |     |                                  |     |                      | Image rejection after calibration will depend on temperature and supply voltage. Refer to section 12.6 on page 35.                                                                                                           |

| Selectivity*  433 MHz 102.4 kHz channel filter BW ±200 kHz offset ±300 kHz offset  868 MHz 102.4 kHz channel filter BW ±200 kHz offset ±300 kHz offset  (*Close-in spurious response rejection) |     | 45<br>53<br>45<br>50             |     | dB<br>dB<br>dB       | Wanted signal 3 dB above the sensitivity level. CW jammer is swept in 20 kHz steps within ± 1 MHz from wanted channel. BER = 10 <sup>-3</sup> . Adjacent channel and image channel are excluded. See Figure 16 to Figure 19. |

| Blocking / Desensitization*<br>433/868 MHz                                                                                                                                                      |     |                                  |     |                      | Wanted signal 3 dB above the                                                                                                                                                                                                 |

| ± 1 MHz<br>± 2 MHz<br>± 5 MHz<br>± 10 MHz<br>(*Out-of-band spurious response<br>rejection)                                                                                                      |     | 52/58<br>56/64<br>58/64<br>64/66 |     | dB<br>dB<br>dB<br>dB | sensitivity level, CW jammer at ± 1, 2, 5 and 10 MHz offset, BER = 10 <sup>-3</sup> . 102.4 kHz channel filter bandwidth.  Complying with EN 300 220, class 2 receiver requirements.                                         |

| Image frequency suppression,<br>433/868 MHz                                                                                                                                                     |     |                                  |     |                      | Ratio between sensitivity for a signal at the image frequency to the sensitivity in the wanted                                                                                                                               |

| No I/Q gain and phase calibration                                                                                                                                                               |     | 35/35                            |     | dB                   | channel. Image frequency is RF-<br>2 IF. BER = 10 <sup>-3</sup> . 102.4 kHz                                                                                                                                                  |

| I/Q gain and phase calibrated                                                                                                                                                                   |     | 60/60                            |     | dB                   | channel filter bandwidth.                                                                                                                                                                                                    |

| Parameter                      | Min | Тур      | Max  | Unit | Condition / Note                                                                                                                                                                                                                             |

|--------------------------------|-----|----------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Spurious reception             |     |          | 37   | dB   | Ratio between sensitivity for an unwanted frequency to the sensitivity in the wanted channel. The signal source is swept over all frequencies 100 MHz – 2 GHz. Signal level for BER = 10 <sup>-3</sup> . 102.4 kHz channel filter bandwidth. |

| LO leakage, 433/868 MHz        |     | <-80/-66 |      | dBm  |                                                                                                                                                                                                                                              |

| VCO leakage                    |     | -64      |      | dBm  | VCO frequency resides between<br>1608 – 1880 MHz                                                                                                                                                                                             |

| Spurious emission, radiated CW |     |          |      |      |                                                                                                                                                                                                                                              |

| 9 kHz – 1 GHz                  |     | <-60     |      | dBm  | Complying with EN 300 220,<br>FCC CFR47 part 15 and ARIB<br>STD T-67.                                                                                                                                                                        |

| 1 – 4 GHz                      |     | <-60     |      | dBm  | Spurious emissions are measured as EIRP values according to EN 300 220.                                                                                                                                                                      |

| Input impedance                |     |          |      |      | D : 1 0 " 11                                                                                                                                                                                                                                 |

| 433 MHz                        |     | 58 - j10 |      | Ω    | Receive mode. See section 14 on page 46 for details.                                                                                                                                                                                         |

| 868 MHz                        |     | 54 - j22 |      | Ω    |                                                                                                                                                                                                                                              |

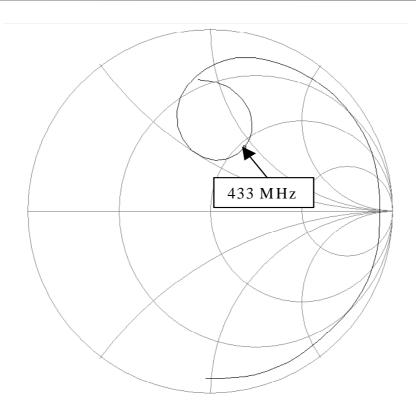

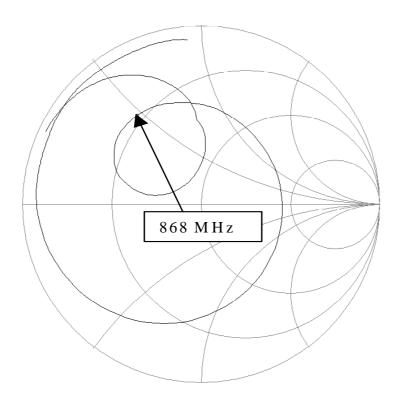

| Matched input impedance, S11   |     |          |      |      |                                                                                                                                                                                                                                              |

| 433 MHz                        |     | -14      |      | dB   | Using application circuit matching network. See section 14 on page 46 for details.                                                                                                                                                           |

| 868 MHz                        |     | -12      |      | dB   | To lot details.                                                                                                                                                                                                                              |

| Matched input impedance        |     |          |      |      | Llaina application aircuit matching                                                                                                                                                                                                          |

| 433 MHz                        |     | 39 - j14 |      | Ω    | Using application circuit matching network. See section 14 on page 46 for details.                                                                                                                                                           |

| 868 MHz                        |     | 32 - j10 |      | Ω    | To for dotaile.                                                                                                                                                                                                                              |

| Bit synchronization offset     |     |          | 8000 | ppm  | The maximum bit rate offset tolerated by the bit synchronization circuit for 6 dB degradation (synchronous modes only)                                                                                                                       |

| Data latency                   |     |          |      |      |                                                                                                                                                                                                                                              |

| NRZ mode                       |     | 4        |      | Baud | Time from clocking the data on<br>the transmitter DIO pin until data<br>is available on receiver DIO pin                                                                                                                                     |

| Manchester mode                |     | 8        |      | Baud | is a raisasis sir receive. Bio pin                                                                                                                                                                                                           |

Table 4. RF receive parameters

### 4.3. RSSI / Carrier Sense Section

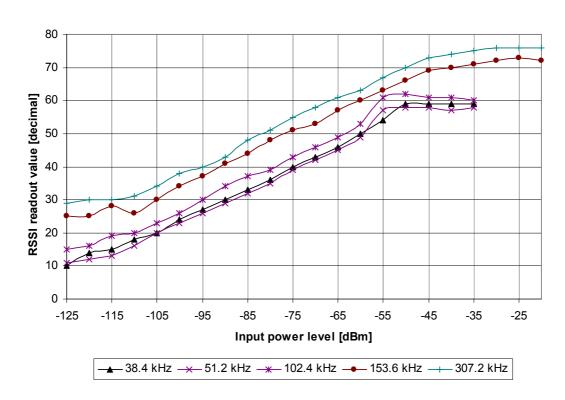

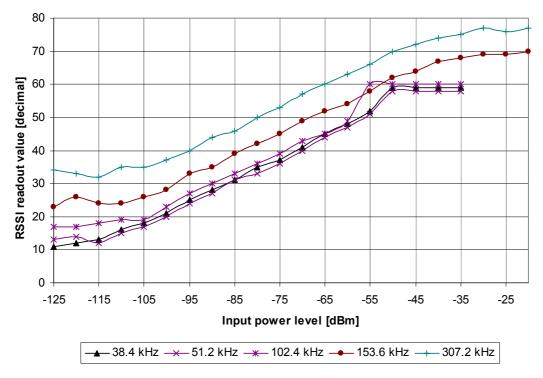

| 63<br>± 3  |                                       | dB                                    | See section 12.5 on page 33 for details.                                                                                                                                                                          |

|------------|---------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ± 3        |                                       |                                       | uetaiis.                                                                                                                                                                                                          |

|            |                                       | dB                                    | See section 12.5 on page 33 for details.                                                                                                                                                                          |

| ± 1        |                                       | dB                                    |                                                                                                                                                                                                                   |

|            |                                       |                                       | Shorter RSSI attach times can be traded for lower RSSI accuracy.                                                                                                                                                  |

| 730        |                                       | μS                                    | See section 12.5 on page 33 for details.                                                                                                                                                                          |

| 380        |                                       | μS                                    | Shorter RSSI attach times can                                                                                                                                                                                     |

| 140        |                                       | μS                                    | also be traded for reduced<br>sensitivity and selectivity by<br>increasing the receiver channel<br>filter bandwidth.                                                                                              |

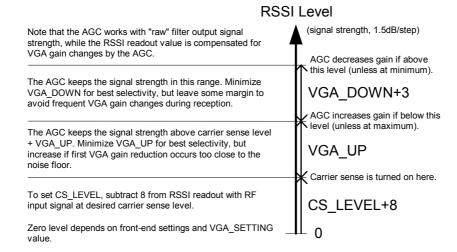

| 40         |                                       | dB                                    | Accuracy is as for RSSI                                                                                                                                                                                           |

| -57<br>-44 |                                       | dBm<br>dBm<br>dBm                     | At carrier sense level -98 dBm, CW jammer at ±100 kHz and ±200 kHz offset.  Carrier sense is measured by applying a signal at ±100 kHz and ±200 kHz offset and observe at which level carrier sense is indicated. |

|            | 730<br>380<br>140<br>40<br>-57<br>-44 | 730<br>380<br>140<br>40<br>-57<br>-44 | 730 μs 380 μs 140 μs 40 dB  -57 dBm dBm -60 dBm                                                                                                                                                                   |

Table 5. RSSI / Carrier sense parameters

### 4.4. IF Section

| Parameter                        | Min | Тур                 | Max | Unit | Condition / Note                                                                                                      |

|----------------------------------|-----|---------------------|-----|------|-----------------------------------------------------------------------------------------------------------------------|

| Intermediate frequency (IF)      |     | 307.2               |     | kHz  | See section 12.1 on page 30 for details.                                                                              |

| Digital channel filter bandwidth |     | 38.4<br>to<br>307.2 |     | kHz  | The channel filter 6 dB bandwidth is programmable from 9.6 kHz to 307.2 kHz. See section 12.2 on page 30 for details. |

| AFC resolution                   |     | 1200                |     | Hz   | At 19.2 kBaud  Given as Baud rate/16. See section 12.13 on page 42 for details.                                       |

Table 6. IF section parameters

### 4.5. Crystal Oscillator Section

| Parameter                                                      | Min            | Тур                                         | Max            | Unit                             | Condition / Note                                                                                                                                                                                    |

|----------------------------------------------------------------|----------------|---------------------------------------------|----------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystal Oscillator Frequency                                   | 4.9152         | 14.7456                                     | 19.6608        | MHz                              | Recommended frequency is<br>14.7456 MHz. See section 19 on<br>page 59 for details.                                                                                                                  |

| Crystal operation                                              |                | Parallel                                    |                |                                  | C4 and C5 are loading capacitors. See section 19 on page 59 for details.                                                                                                                            |

| Crystal load capacitance                                       | 12<br>12<br>12 | 22<br>16<br>16                              | 30<br>30<br>16 | pF<br>pF<br>pF                   | 4.9-6 MHz, 22 pF recommended<br>6-8 MHz, 16 pF recommended<br>8-19.6 MHz, 16 pF recommended                                                                                                         |

| Crystal oscillator start-up time                               |                | 1.55<br>1.0<br>0.90<br>0.95<br>0.60<br>0.63 |                | ms<br>ms<br>ms<br>ms<br>ms<br>ms | 4.9152 MHz, 12 pF load<br>7.3728 MHz, 12 pF load<br>9.8304 MHz, 12 pF load<br>14.7456 MHz, 16 pF load<br>17.2032 MHz, 12 pF load<br>19.6608 MHz, 12 pF load                                         |

| External clock signal drive, sine wave                         |                | 300                                         |                | mVpp                             | The external clock signal must be connected to XOSC_Q1 using a DC block (10 nF). Set XOSC_BYPASS = 0 in the INTERFACE register when using an external clock signal with low amplitude or a crystal. |

| External clock signal drive, full-swing digital external clock |                | 0 - VDD                                     |                | V                                | The external clock signal must be connected to XOSC_Q1. No DC block shall be used. Set XOSC_BYPASS = 1 in the INTERFACE register when using a full-swing digital external clock.                    |

**Table 7. Crystal oscillator parameters**

### 4.6. Frequency Synthesizer Section

| Parameter                                                                                                                                                                   | Min | Тур                               | Max | Unit                                           | Condition / Note                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------|-----|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Phase noise, 402 – 470 MHz                                                                                                                                                  |     | -79<br>-80<br>-87<br>-100<br>-105 |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz | Unmodulated carrier At 12.5 kHz offset from carrier At 25 kHz offset from carrier At 50 kHz offset from carrier At 100 kHz offset from carrier At 1 MHz offset from carrier Measured using loop filter components given in Table 13. The phase noise will be higher for larger PLL loop filter bandwidth. |

| Phase noise, 804 – 940 MHz                                                                                                                                                  |     | -73<br>-74<br>-81<br>-94<br>-111  |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz | Unmodulated carrier At 12.5 kHz offset from carrier At 25 kHz offset from carrier At 50 kHz offset from carrier At 100 kHz offset from carrier At 1 MHz offset from carrier Measured using loop filter components given in Table 13. The phase noise will be higher for larger PLL loop filter bandwidth. |

| PLL loop filter bandwidth  Loop filter 2, up to 19.2 kBaud  Loop filter 3, up to 38.4 kBaud                                                                                 |     | 15<br>30.5                        |     | kHz<br>kHz                                     | After PLL and VCO calibration. The PLL loop bandwidth is programmable. See Table 25 on page 54 for loop filter component values.                                                                                                                                                                          |

| PLL lock time (RX / TX turn time) Loop filter 2, up to 19.2 kBaud Loop filter 3, up to 38.4 kBaud Loop filter 5, up to 153.6 kBaud                                          |     | 140<br>75<br>14                   |     | us<br>us<br>us                                 | 307.2 kHz frequency step to RF frequency within ±10 kHz, ±15 kHz, ±50 kHz settling accuracy for loop filter 2, 3 and 5 respectively. Depends on loop filter component values and <i>PLL_BW</i> register setting. See Table 26 on page 54 for more details.                                                |

| PLL turn-on time. From power down mode with crystal oscillator running.  Loop filter 2, up to 19.2 kBaud  Loop filter 3, up to 38.4 kBaud  Loop filter 5, up to 153.6 kBaud |     | 1300<br>1080<br>700               |     | us<br>us<br>us                                 | Time from writing to registers to RF frequency within ±10 kHz, ±15 kHz, ±50 kHz settling accuracy for loop filter 2, 3 and 5 respectively. Depends on loop filter component values and <i>PLL_BW</i> register setting. See Table 25 on page 54 for more details.                                          |

Table 8. Frequency synthesizer parameters

### 4.7. Digital Inputs / Outputs

| 0<br>0.7*<br>/DD |                                                              | 0.3*<br>VDD                                          | V                                                    |                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /DD              |                                                              |                                                      |                                                      |                                                                                                                                                                                                                                                                                                      |

| _                |                                                              | VDD                                                  | V                                                    |                                                                                                                                                                                                                                                                                                      |

| 0                |                                                              | 0.4                                                  | V                                                    | Output current -2.0 mA, 3.0 V supply voltage                                                                                                                                                                                                                                                         |

| 2.5              |                                                              | VDD                                                  | V                                                    | Output current 2.0 mA,<br>3.0 V supply voltage                                                                                                                                                                                                                                                       |

| NA               |                                                              | -1                                                   | μА                                                   | Input signal equals GND.  PSEL has an internal pull-up resistor and during configuration the current will be -350 μA.                                                                                                                                                                                |

| NA               |                                                              | 1                                                    | μА                                                   | Input signal equals VDD                                                                                                                                                                                                                                                                              |

| 20               |                                                              |                                                      | ns                                                   | TX mode, minimum time DIO must be ready before the positive edge of DCLK. Data should be set up on the negative edge of DCLK.                                                                                                                                                                        |

| 10               |                                                              |                                                      | ns                                                   | TX mode, minimum time DIO must be held after the positive edge of DCLK. Data should be set up on the negative edge of DCLK.                                                                                                                                                                          |

|                  |                                                              |                                                      |                                                      | See Table 14 on page 24 for more details                                                                                                                                                                                                                                                             |

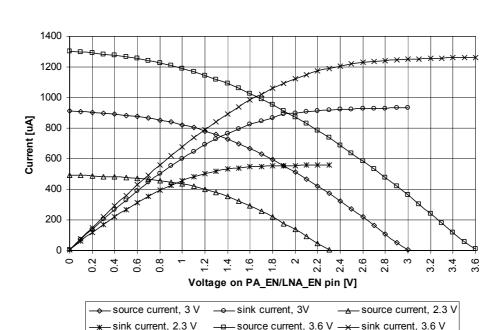

|                  | 0.90<br>0.87<br>0.81<br>0.69<br>0.93<br>0.92<br>0.89<br>0.79 |                                                      | mA<br>mA<br>mA<br>mA<br>mA<br>mA                     | Source current 0 V on LNA_EN, PA_EN pins 0.5 V on LNA_EN, PA_EN pins 1.0 V on LNA_EN, PA_EN pins 1.5 V on LNA_EN, PA_EN pins Sink current 3.0 V on LNA_EN, PA_EN pins 2.5 V on LNA_EN, PA_EN pins 2.0 V on LNA_EN, PA_EN pins 1.5 V on LNA_EN, PA_EN pins See Figure 36 on page 63 for more details. |

|                  | 10                                                           | 0.90<br>0.87<br>0.81<br>0.69<br>0.93<br>0.92<br>0.89 | 0.90<br>0.87<br>0.81<br>0.69<br>0.93<br>0.92<br>0.89 | 0.90 mA<br>0.87 mA<br>0.81 mA<br>0.69 mA<br>0.92 mA<br>0.89 mA                                                                                                                                                                                                                                       |

Table 9. Digital inputs / outputs parameters

### 4.8. Current Consumption

| Parameter                                                     | Min | Тур       | Max | Unit | Condition / Note                                                  |

|---------------------------------------------------------------|-----|-----------|-----|------|-------------------------------------------------------------------|

| Power Down mode                                               |     | 0.2       | 1.8 | μА   | Oscillator core off                                               |

| Current Consumption, receive mode 433 and 868 MHz             |     | 19.9      |     | mA   |                                                                   |

| Current Consumption, transmit mode 433/868 MHz:               |     |           |     |      |                                                                   |

| P = −20 dBm                                                   |     | 12.3/14.5 |     | mA   | The output power is delivered to a 50 $\Omega$ single-ended load. |

| P = −5 dBm                                                    |     | 14.4/17.0 |     | mA   | See section 13.2 on page 44 for                                   |

| P = 0 dBm                                                     |     | 16.2/20.5 |     | mA   | more details.                                                     |

| P = +5 dBm                                                    |     | 20.5/25.1 |     | mA   |                                                                   |

| P = +10 dBm (433 MHz only)                                    |     | 27.1      |     | mA   |                                                                   |

| Current Consumption, crystal oscillator                       |     | 77        |     | μА   | 14.7456 MHz, 16 pF load crystal                                   |

| Current Consumption, crystal oscillator and bias              |     | 500       |     | μА   | 14.7456 MHz, 16 pF load crystal                                   |

| Current Consumption, crystal oscillator, bias and synthesizer |     | 7.5       |     | mA   | 14.7456 MHz, 16 pF load crystal                                   |

**Table 10. Current consumption**

### 5. Pin Assignment

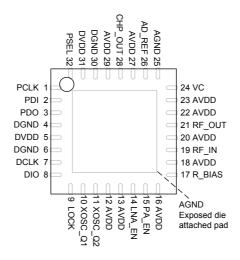

Table 11 provides an overview of the *CC1021* pinout.

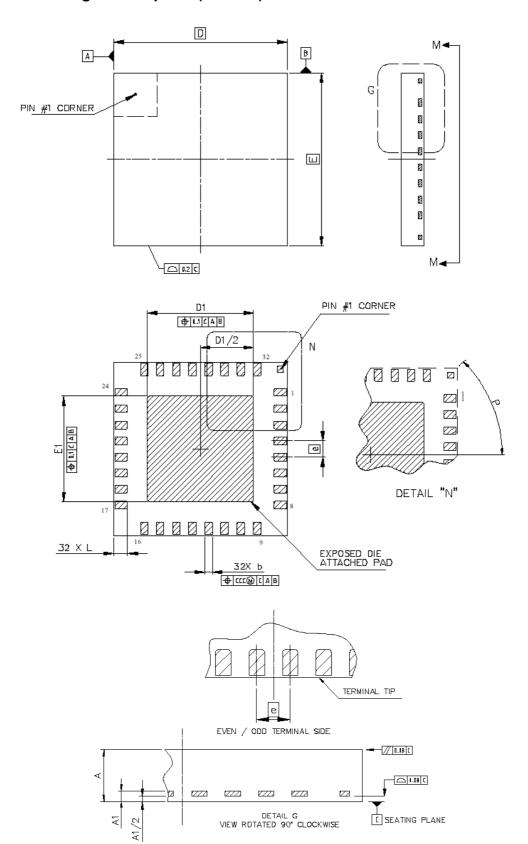

The *CC1021* comes in a QFN32 type package (see page 87 for details).

Figure 1. CC1021 package (top view)

| Pin no.  | Pin name           | Pin type             | Description                                                                                          |

|----------|--------------------|----------------------|------------------------------------------------------------------------------------------------------|

| -        | AGND               | Ground (analog)      | Exposed die attached pad. Must be soldered to a solid ground plane as                                |

|          |                    |                      | this is the ground connection for all analog modules. See page 65 for                                |

|          |                    |                      | more details.                                                                                        |

| 1        | PCLK               | Digital input        | Programming clock for SPI configuration interface                                                    |

| 2        | PDI                | Digital input        | Programming data input for SPI configuration interface                                               |

| 3        | PDO                | Digital output       | Programming data output for SPI configuration interface                                              |

| 4        | DGND               | Ground (digital)     | Ground connection (0 V) for digital modules and digital I/O                                          |

| 5        | DVDD               | Power (digital)      | Power supply (3 V typical) for digital modules and digital I/O                                       |

| 6        | DGND               | Ground (digital)     | Ground connection (0 V) for digital modules (substrate)                                              |

| 7        | DCLK               | Digital output       | Clock for data in both receive and transmit mode.                                                    |

|          |                    |                      | Can be used as receive data output in asynchronous mode                                              |

| 8        | DIO                | Digital input/output | Data input in transmit mode; data output in receive mode                                             |

|          |                    |                      | Can also be used to start power-up sequencing in receive                                             |

| 9        | LOCK               | Digital output       | PLL Lock indicator, active low. Output is asserted (low) when PLL is in                              |

|          |                    |                      | lock. The pin can also be used as a general digital output, or as receive                            |

| 40       | V000 04            | A mala mimmud        | data output in synchronous NRZ/Manchester mode                                                       |

| 10<br>11 | XOSC_Q1<br>XOSC Q2 | Analog input         | Crystal oscillator or external clock input                                                           |

|          |                    | Analog output        | Crystal oscillator                                                                                   |

| 12       | AVDD               | Power (analog)       | Power supply (3 V typical) for crystal oscillator                                                    |

| 13<br>14 | AVDD               | Power (analog)       | Power supply (3 V typical) for the IF VGA                                                            |

| 14       | LNA_EN             | Digital output       | General digital output. Can be used for controlling an external LNA if higher sensitivity is needed. |

| 15       | PA_EN              | Digital output       | General digital output. Can be used for controlling an external PA if                                |

| 15       | FA_EIN             | Digital output       | higher output power is needed.                                                                       |

| 16       | AVDD               | Power (analog)       | Power supply (3 V typical) for global bias generator and IF anti-alias                               |

| 10       | AVDD               | 1 ower (analog)      | filter                                                                                               |

| 17       | R_BIAS             | Analog output        | Connection for external precision bias resistor (82 k $\Omega$ , $\pm$ 1%)                           |

| 18       | AVDD               | Power (analog)       | Power supply (3 V typical) for LNA input stage                                                       |

| 19       | RF IN              | RF Input             | RF signal input from antenna (external AC-coupling)                                                  |

| 20       | AVDD               | Power (analog)       | Power supply (3 V typical) for LNA                                                                   |

| 21       | RF_OUT             | RF output            | RF signal output to antenna                                                                          |

| 22       | AVDD               | Power (analog)       | Power supply (3 V typical) for LO buffers, mixers, prescaler, and first PA                           |

|          |                    | , 0,                 | stage                                                                                                |

| 23       | AVDD               | Power (analog)       | Power supply (3 V typical) for VCO                                                                   |

| 24       | VC                 | Analog input         | VCO control voltage input from external loop filter                                                  |

| 25       | AGND               | Ground (analog)      | Ground connection (0 V) for analog modules (guard)                                                   |

| 26       | AD_REF             | Power (analog)       | 3 V reference input for ADC                                                                          |

| 27       | AVDD               | Power (analog)       | Power supply (3 V typical) for charge pump and phase detector                                        |

| 28       | CHP_OUT            | Analog output        | PLL charge pump output to external loop filter                                                       |

| 29       | AVDD               | Power (analog)       | Power supply (3 V typical) for ADC                                                                   |

| 30       | DGND               | Ground (digital)     | Ground connection (0 V) for digital modules (guard)                                                  |

| 31       | DVDD               | Power (digital)      | Power supply connection (3 V typical) for digital modules                                            |

| 32       | PSEL               | Digital input        | Programming chip select, active low, for configuration interface. Internal pull-up resistor.         |

Table 11. Pin assignment overview

### Note:

DCLK, DIO and LOCK are highimpedance (3-state) in power down (BIAS\_PD = 1 in the MAIN register). The exposed die attached pad **must** be soldered to a solid ground plane as this is the main ground connection for the chip.

### 6. Circuit Description

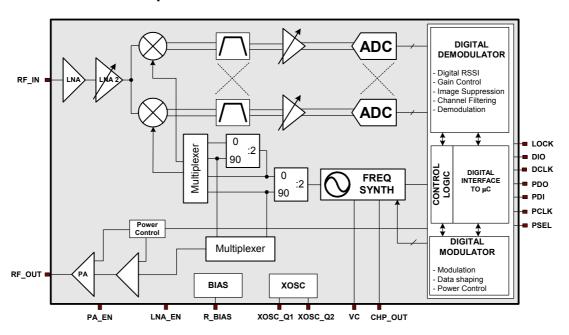

Figure 2. CC1021 simplified block diagram

A simplified block diagram of *CC1021* is shown in Figure 2. Only signal pins are shown.

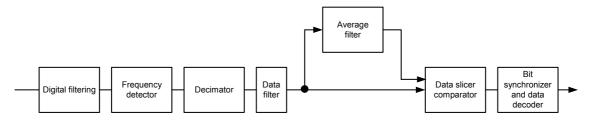

CC1021 features a low-IF receiver. The received RF signal is amplified by the lownoise amplifier (LNA and LNA2) and down-converted in quadrature (I and Q) to the intermediate frequency (IF). At IF, the signal is complex filtered and amplified, and then digitized by the ADCs. Automatic gain control, fine channel filtering, demodulation and synchronization is performed digitally. CC1021 outputs the digital demodulated data on the DIO pin. A synchronized data clock is available at the DCLK pin. RSSI is available in digital format and can be read via the serial interface. The RSSI also features a programmable carrier sense indicator.

In transmit mode, the synthesized RF frequency is fed directly to the power  $\ensuremath{\mathsf{R}}$

amplifier (PA). The RF output is frequency shift keyed (FSK) by the digital bit stream that is fed to the DIO pin. Optionally, a Gaussian filter can be used to obtain Gaussian FSK (GFSK).

The frequency synthesizer includes a completely on-chip LC VCO and a 90 degrees phase splitter for generating the LO\_I and LO\_Q signals to the down-conversion mixers in receive mode. The VCO operates in the frequency range 1.608-1.880 GHz. The CHP\_OUT pin is the charge pump output and VC is the control node of the on-chip VCO. The external loop filter is placed between these pins. A crystal is to be connected between XOSC\_Q1 and XOSC\_Q2. A lock signal is available from the PLL.

The 4-wire SPI serial interface is used for configuration.

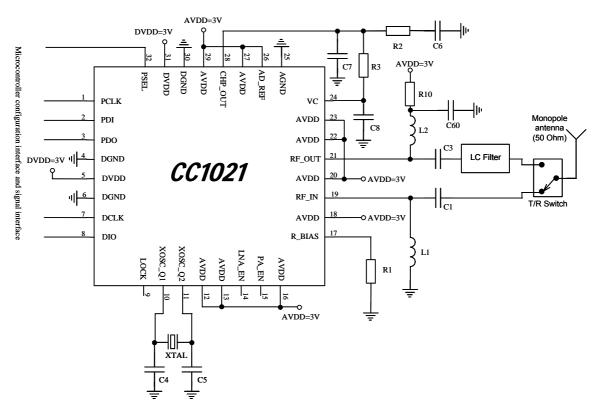

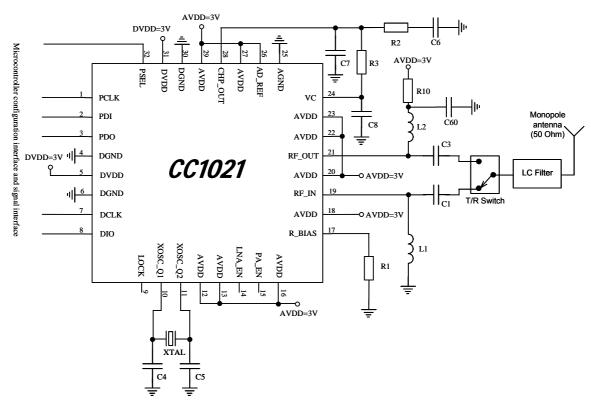

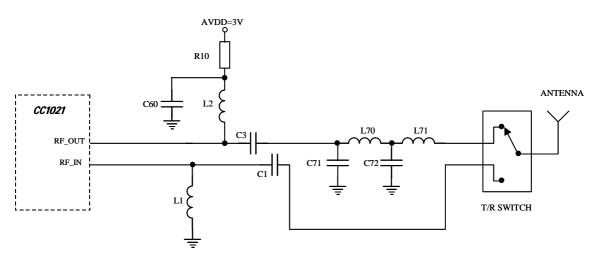

### 7. Application Circuit

Very few external components are required for the operation of *CC1021*. The recommended application circuit is shown in Figure 3. The external components are described in Table 12 and values are given in Table 13.

### Input / output matching