# CONTENT

## 1.0 Objective

This document outlines the trouble shooting for the CT6558.

## 2.0 Scope

1. Used for radio trouble shooting in factory.

2. Used for radio trouble shooting in customer service.

## 3.0 Definition of terms

Nil

## 4.0 Responsibility

Nil

## 5.0 Detail procedure

- 5.1 General description.....

- 5.11 Product Overview.....

- 5.12 Product technical parameters .....

- 5.2 CT6558 Signal Flow Overview.....

- 5.21 Receiver Principle and troubleshooting.....

- 5.22 Transmitter Principle and troubleshooting.....

- 5.23 Logic circuit Principle and troubleshooting.....

- 5.3 Exploded view and figures.....

## 6.0 Reference

- 6.1 CPU (OM6357-7).....

- 6.2 PMU (PCF50603).....

- 6.3 Tranceiver (UAA3537HN).....

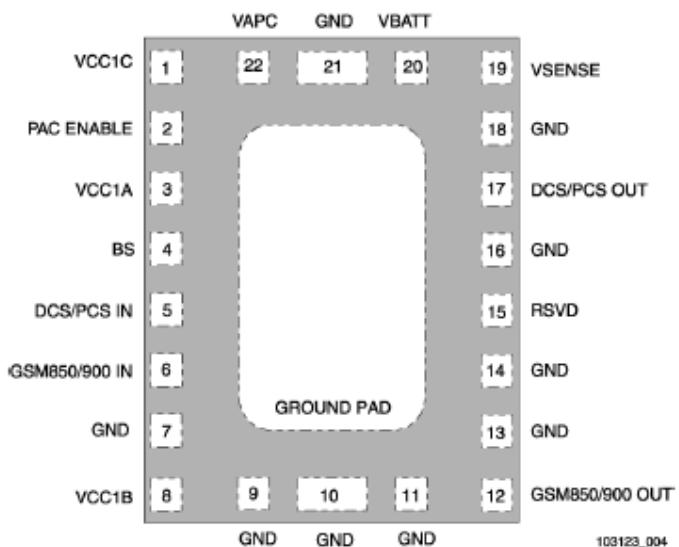

- 6.4 PA&PAC IC (SKY77324).....

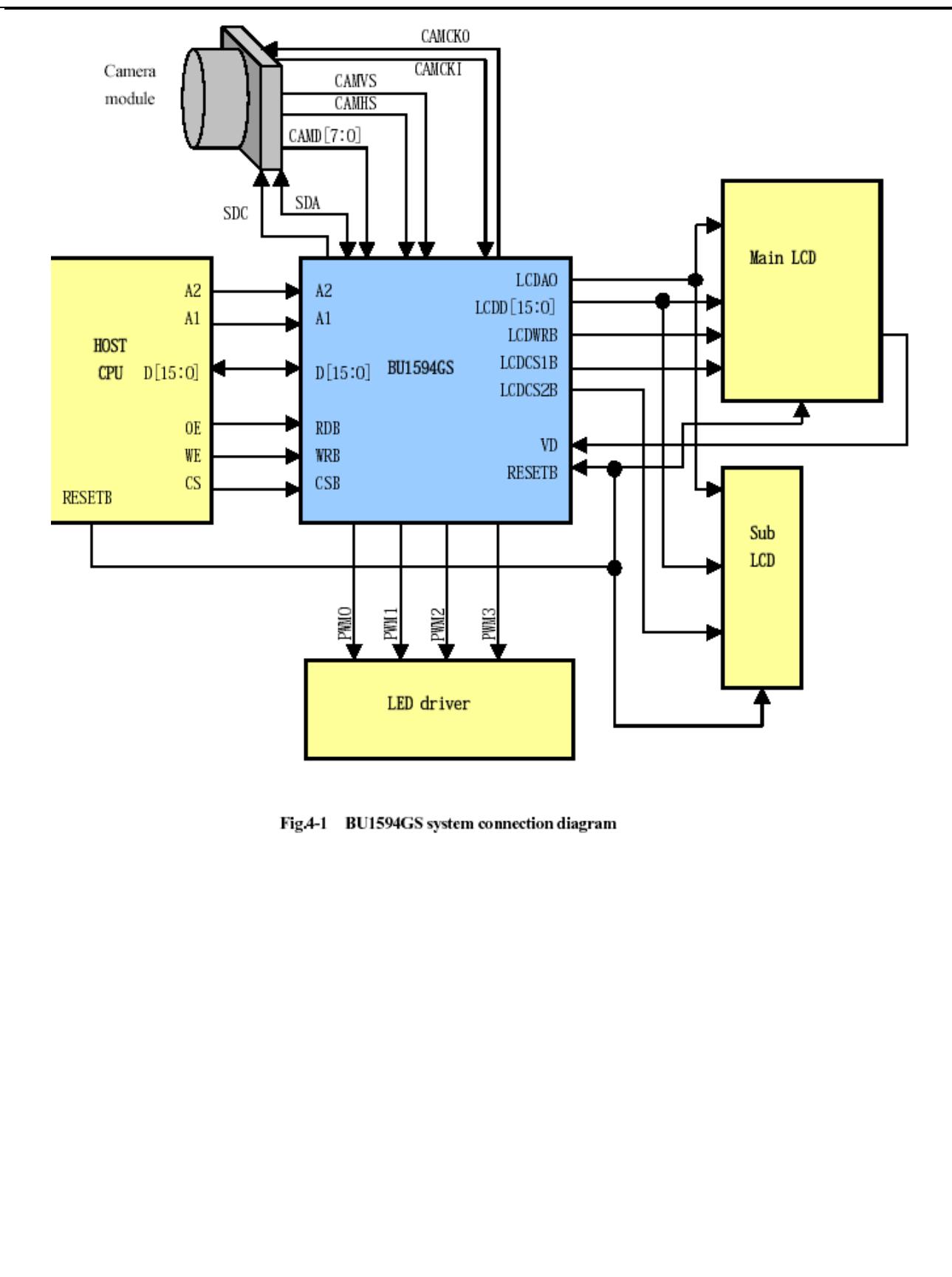

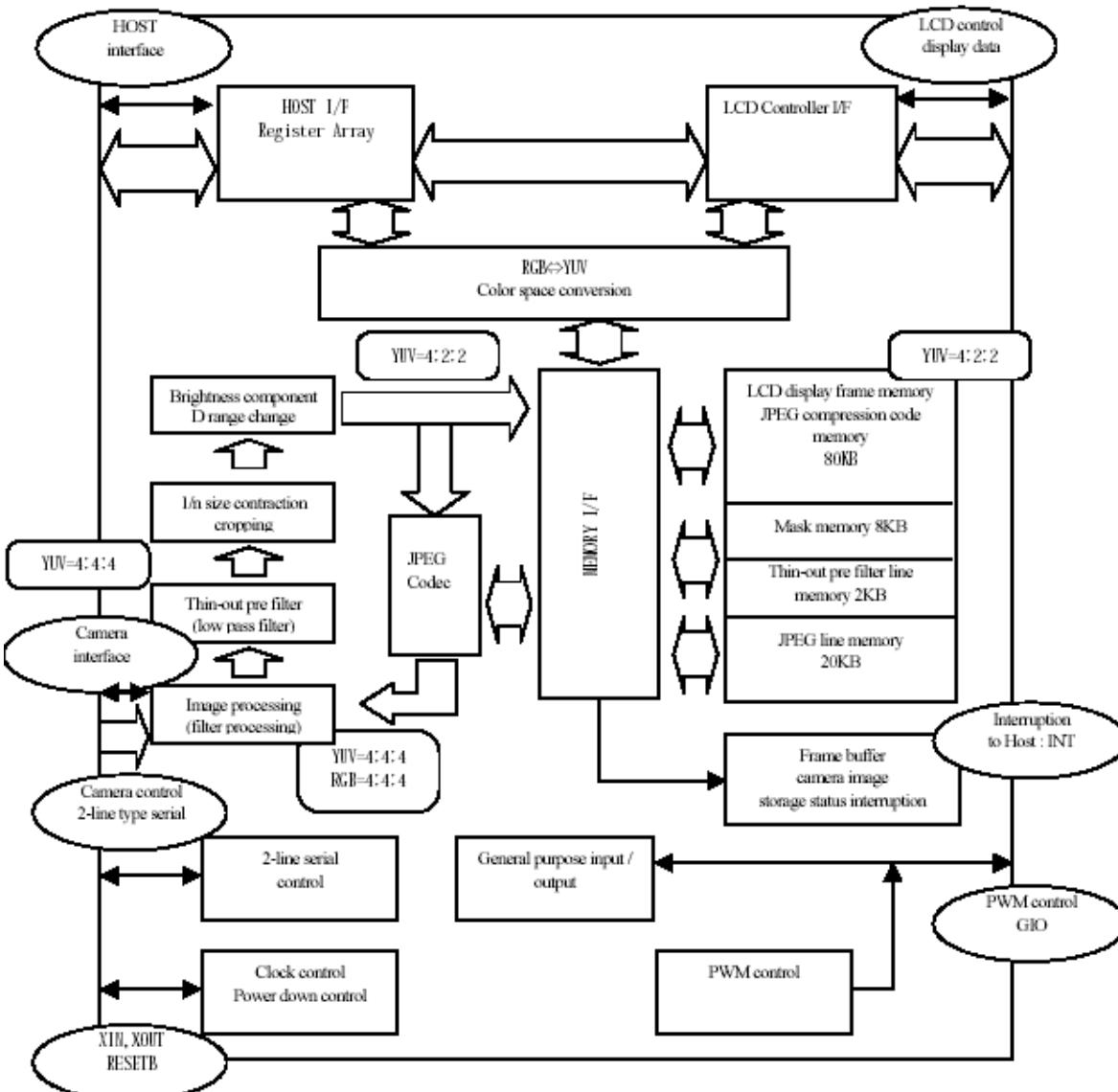

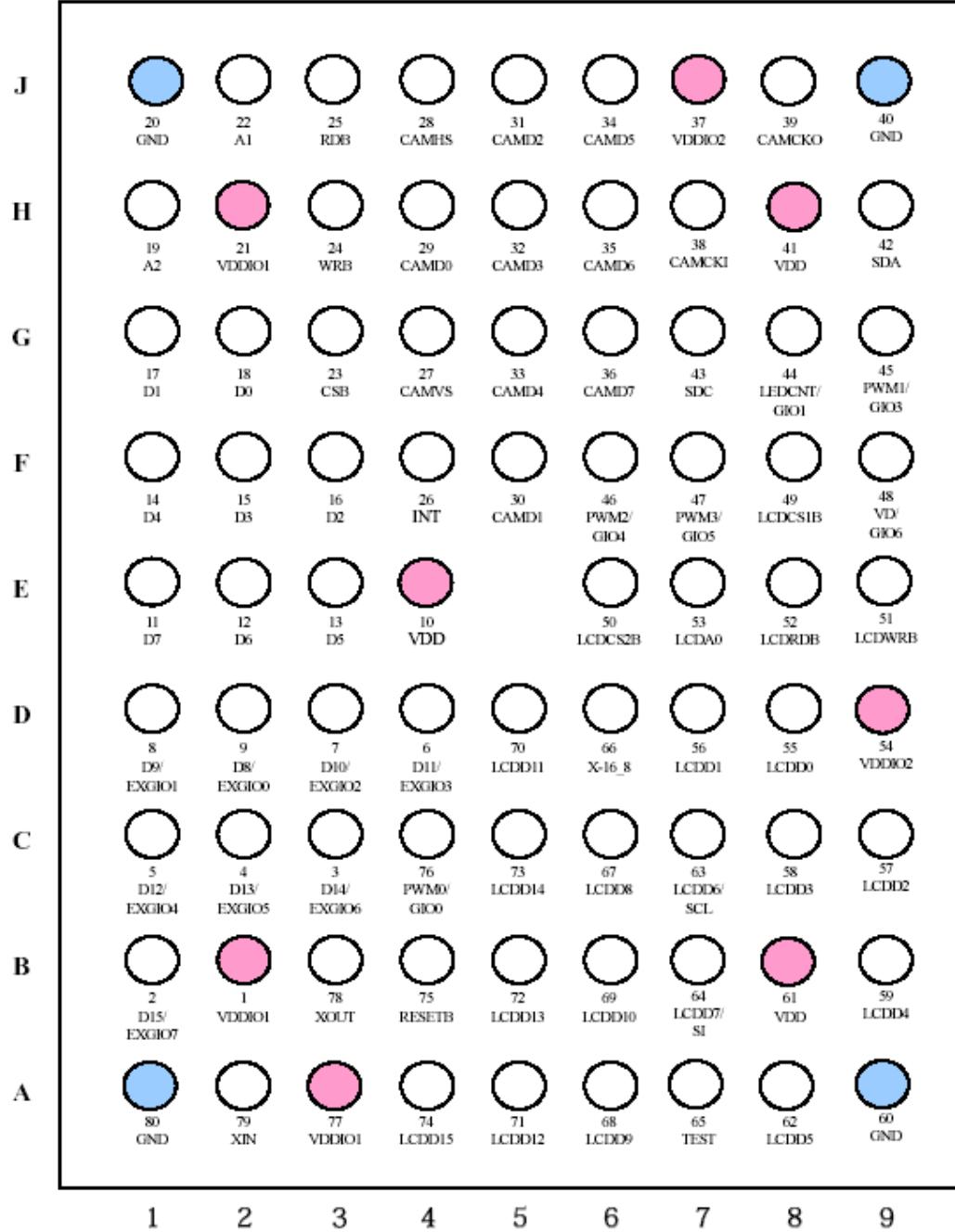

- 6.5 CAMERA IC (BU1594GS).....

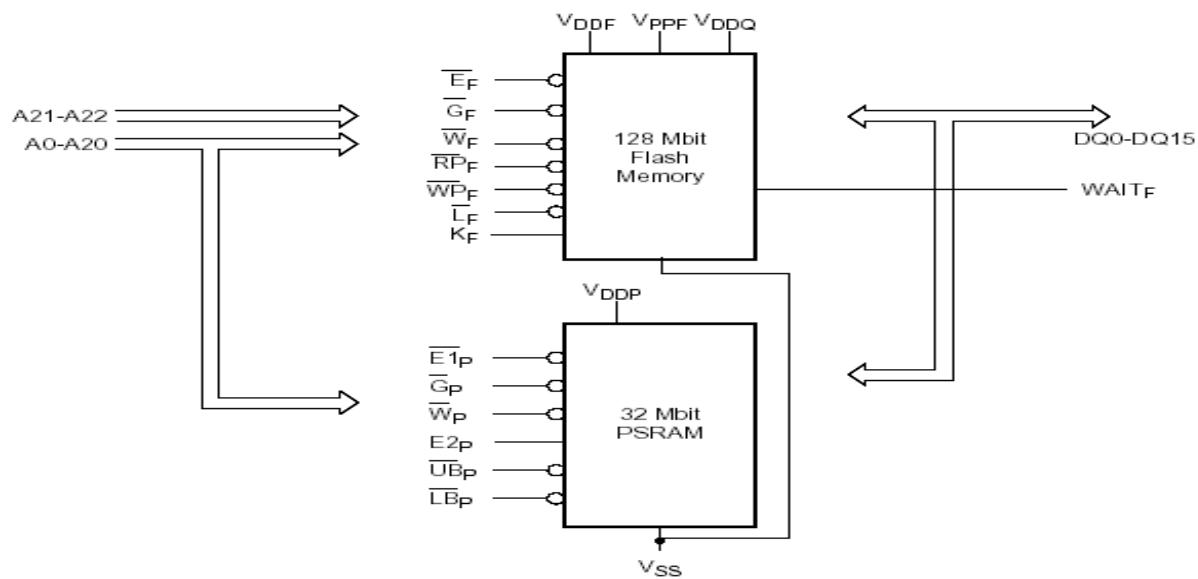

- 6.6 MEMORY (M36L0R7050T0ZAQT/STM).....

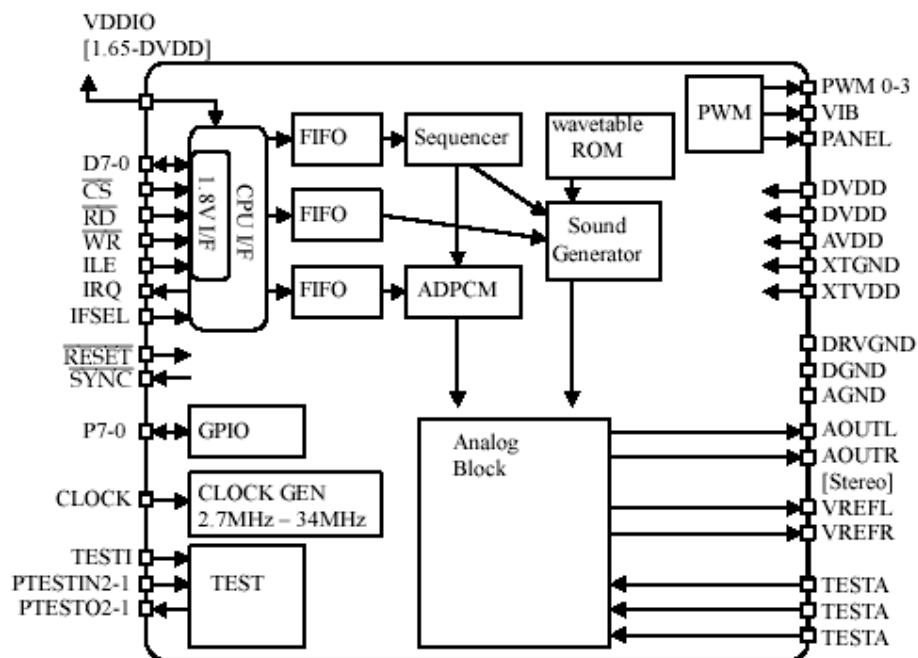

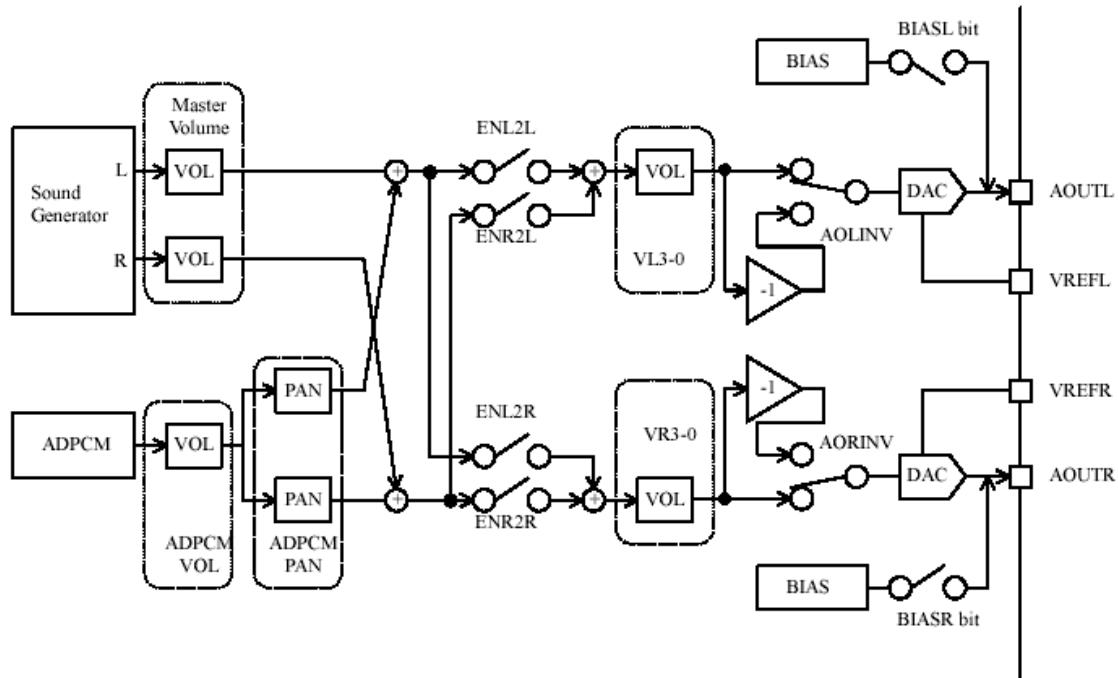

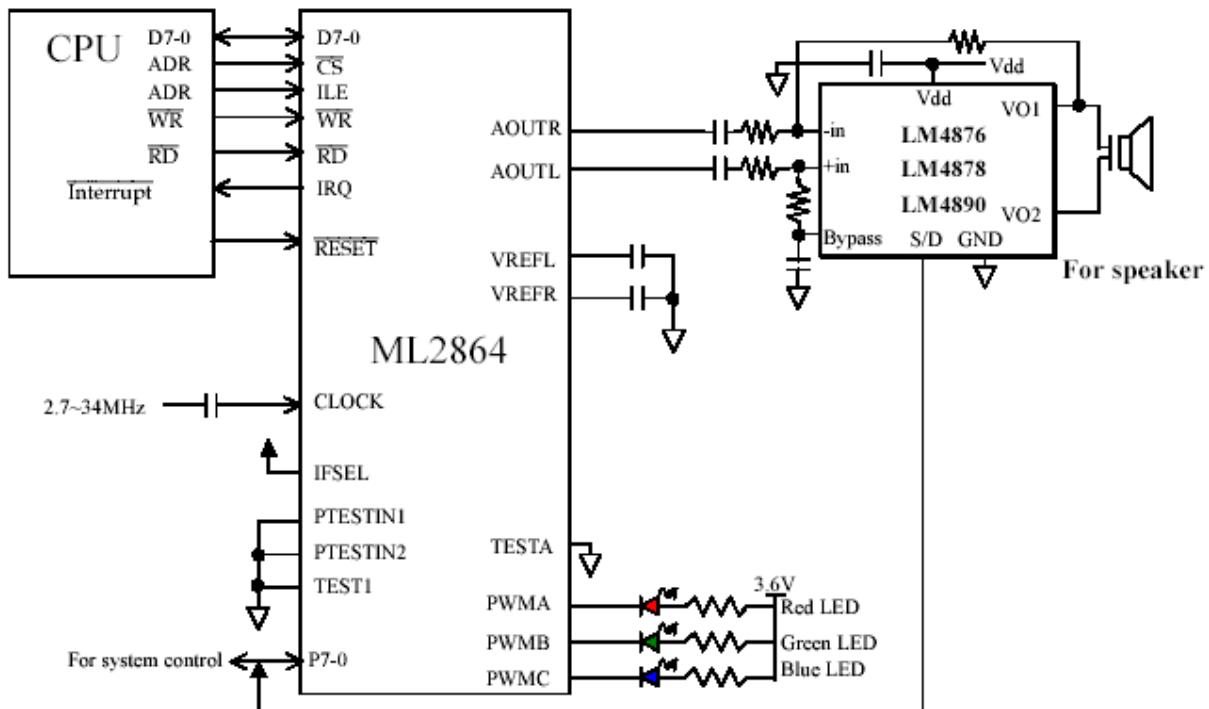

- 6.7 MELODY IC (ML2864).....

- 6.8 CHARGE IC (UBA2008).....

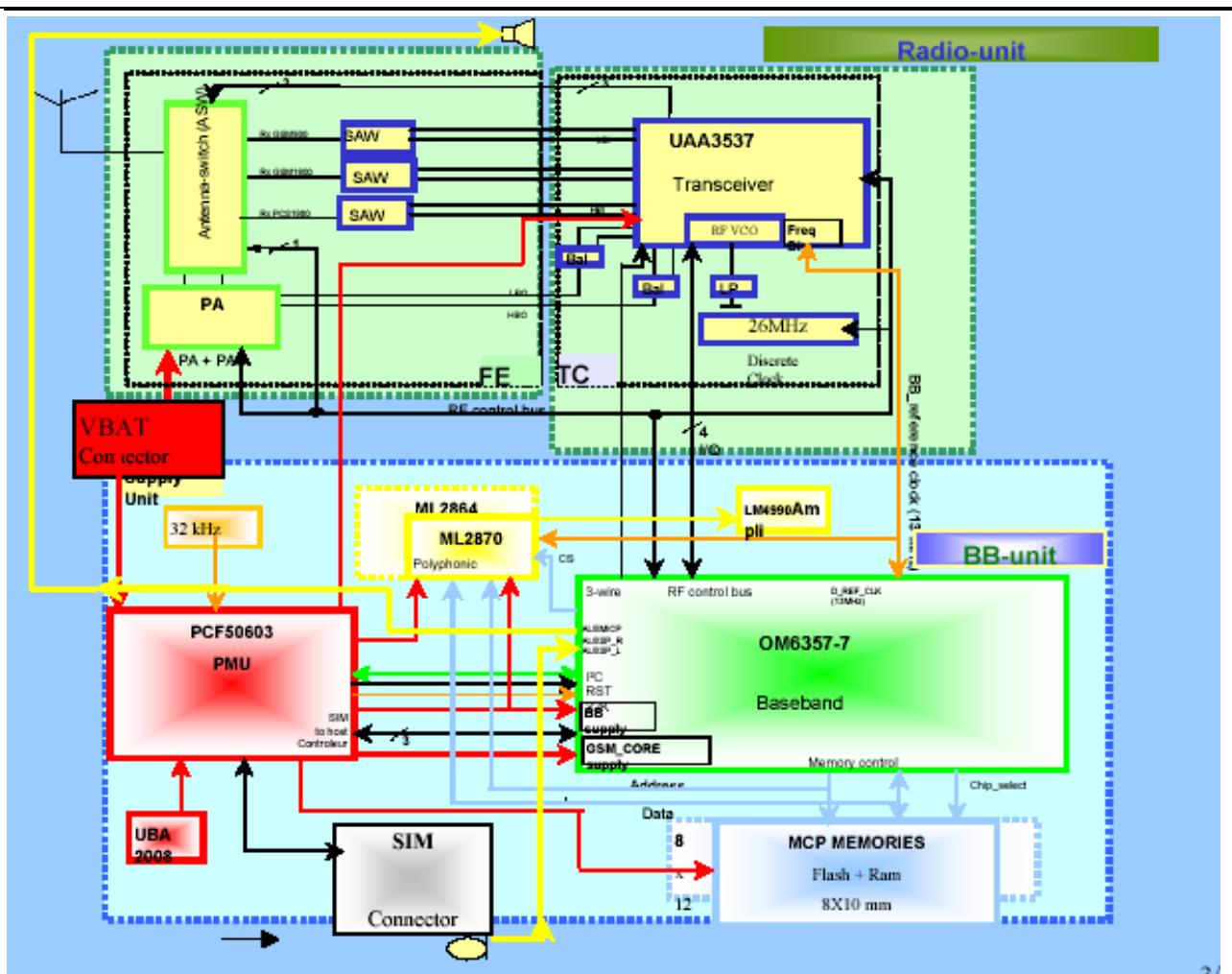

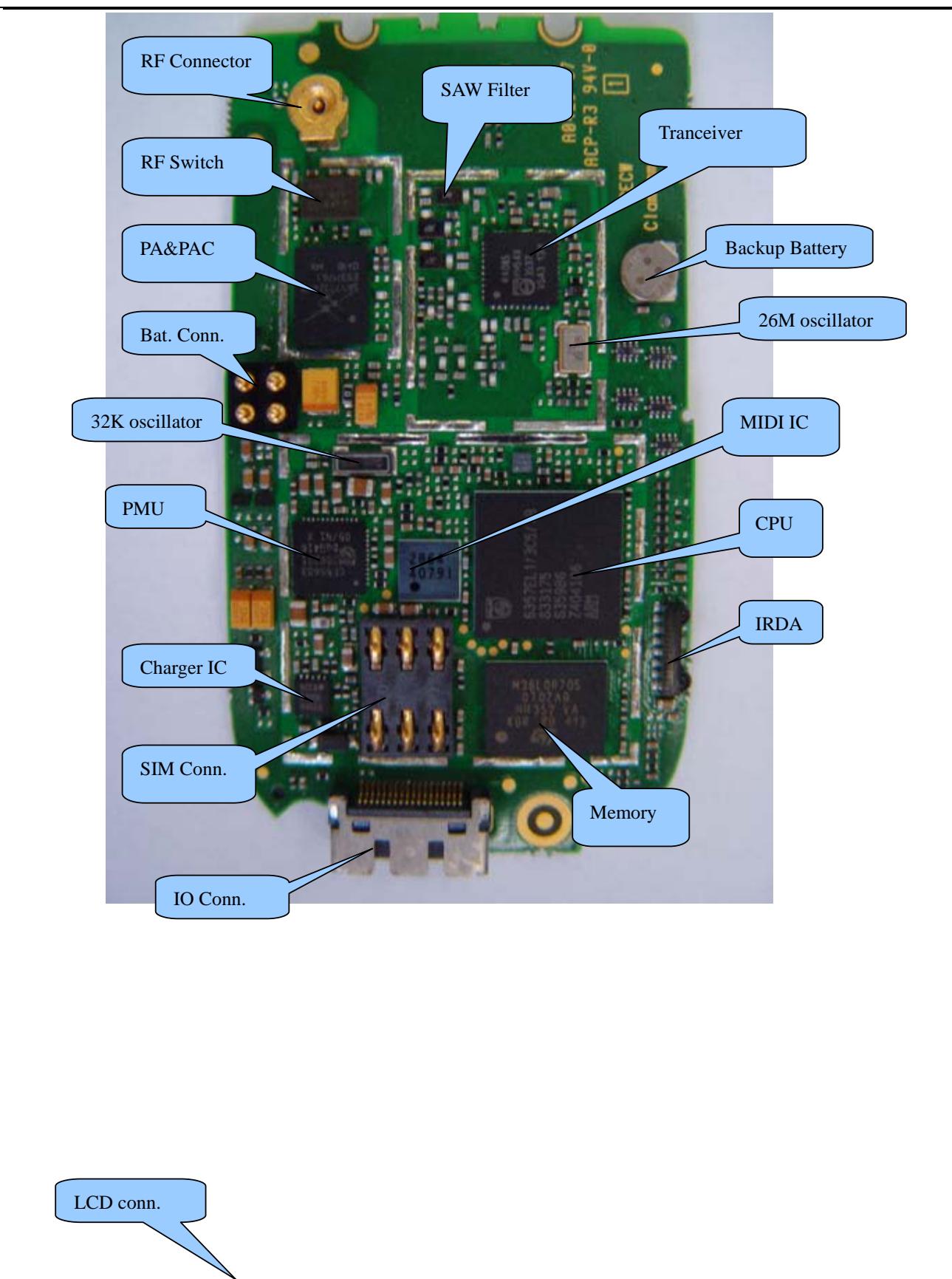

**Tuning Up procedure & Operational Manual****5.1 General description****5.11 Product overview:**

CT6558 product is new model phone designed by CECW, it works at Tri-band, EGSM、DCS and PCS band its weight is only 85g, the size is 85x45x24 CT6558 is a more powerful product, with 300,000 pixels camera sensor inside, 65k colors CSTN main display which pixels is 128\*160,sub-display is STN screen, and has 64 polyphonies, and has hand free function.

CT6558 CPU runs at 13MHz, with 128M Flash Memory and 32M SRAM. The main IC include CPU (OM6357EL/3C5/7)、FLASH(M36L0R7050T0ZAQT /STM)、PMU(PCF50603)、Transceiver(UAA3537HN)、PA(SKY77324), CT6558 can dial 4 hours continuously and can be in idle mode up to 400hours ,using 600Mah LI battery.

**5.1.2 Product technical parameters:**

GENERAL:

| item                          | EGSM(GSM)                                                                                               | DCS                                                                  | PCS                                                                   |

|-------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------|

| Frequency allocation          | TX (Uplink)<br>:880MHZ-915MHZ<br>RX (Downlink)<br>:925MHZ-960MHZ                                        | TX (Uplink)<br>:1710MHZ-1785MHZ<br>RX (Downlink):<br>1805MHZ-1880MHZ | TX (Uplink) :<br>1850MHZ-1910MHZ<br>RX (Downlink):<br>1930MHZ-1990MHZ |

| Channel band width            | 200KHz                                                                                                  | 200KHz                                                               | 200KHz                                                                |

| Channel                       | 975-1023,0-124                                                                                          | 512-885                                                              | 512-810                                                               |

| Modulation                    | GMSK,BT=0.3                                                                                             | GMSK,BT=0.3                                                          | GMSK,BT=0.3                                                           |

| TX/RX channel space           | 45MHz                                                                                                   | 95MHz                                                                | 80MHz                                                                 |

| (Fn)Freq. calculating formula | GSM<br>$F_n = 890.2 + (N-1) * 0.2$<br>EGSM<br>$F_n = 880.2 + (N-975) * 0.2$<br>N: Channel No. Unit: MHz | $F_n = 1710.2 + (N-512) * 0.2$<br>Unit: MHz                          | $F_n = 1850.2 + (N-512) * 0.2$<br>Unit: MHz                           |

## 5.2 CT6558 Signal Flow Overview:

### 5.2.1 Receiver principle and troubleshooting

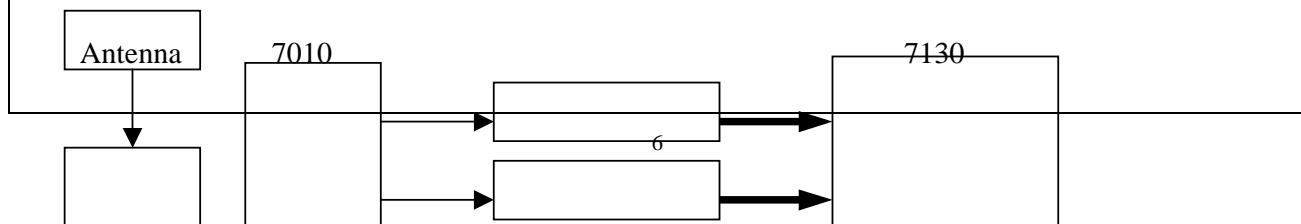

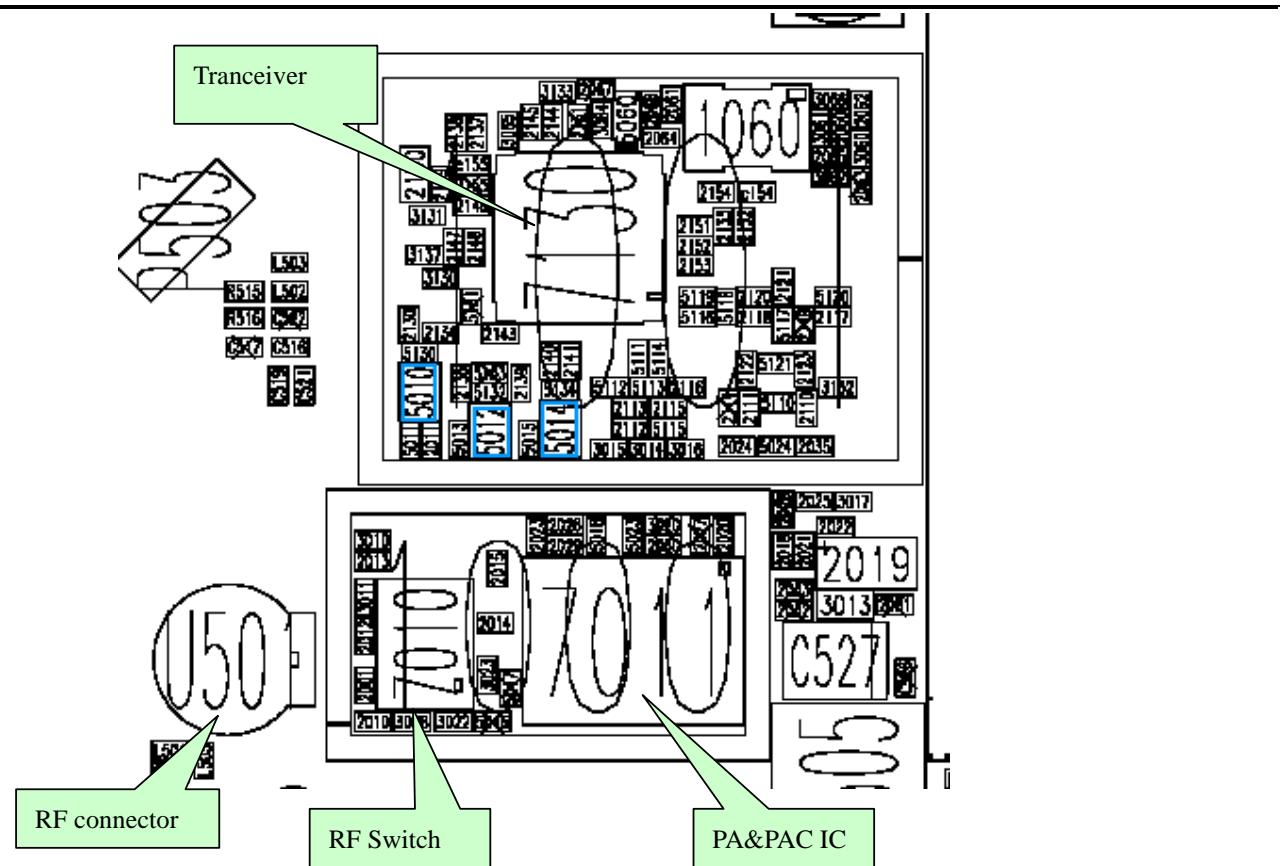

CT6558 RX signal flow chart(Figure 1):

Figure 1

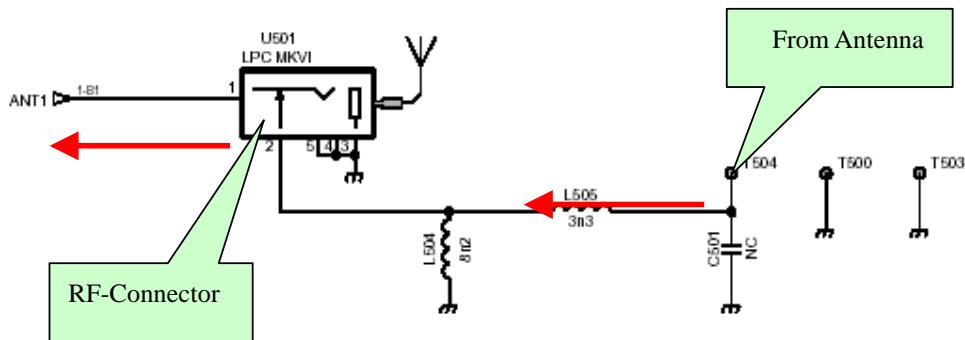

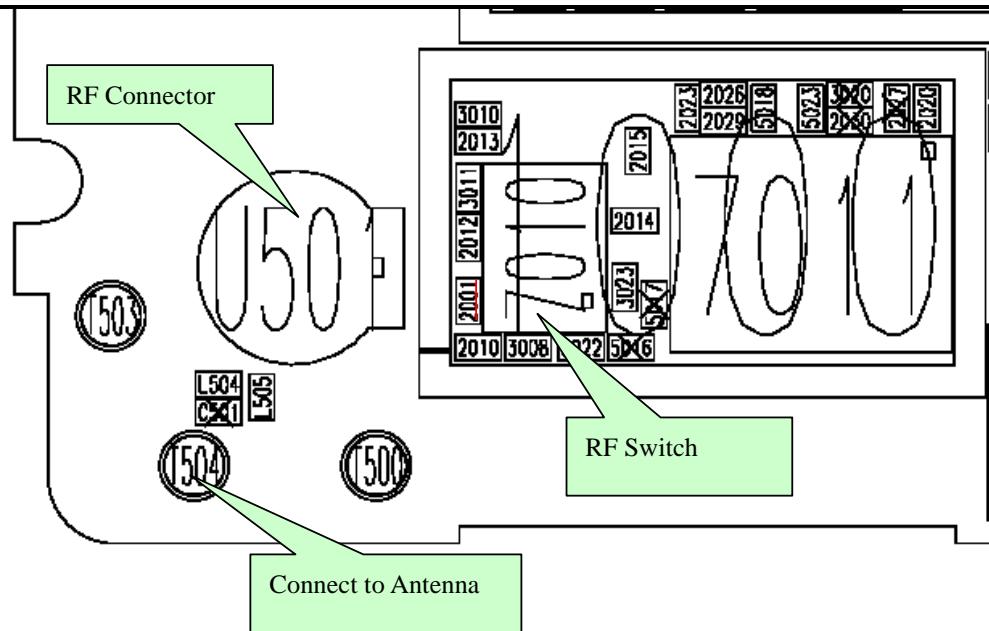

### 1. CT6558 downlink signal flow from Antenna to RF-Connector:

The aerial signal mobile phone received go from antenna to RF Connector. RF Connector, which is a special parts developed for RF test. By connecting U501 and RF cable to spectrum analyzer, you can measure the signal.

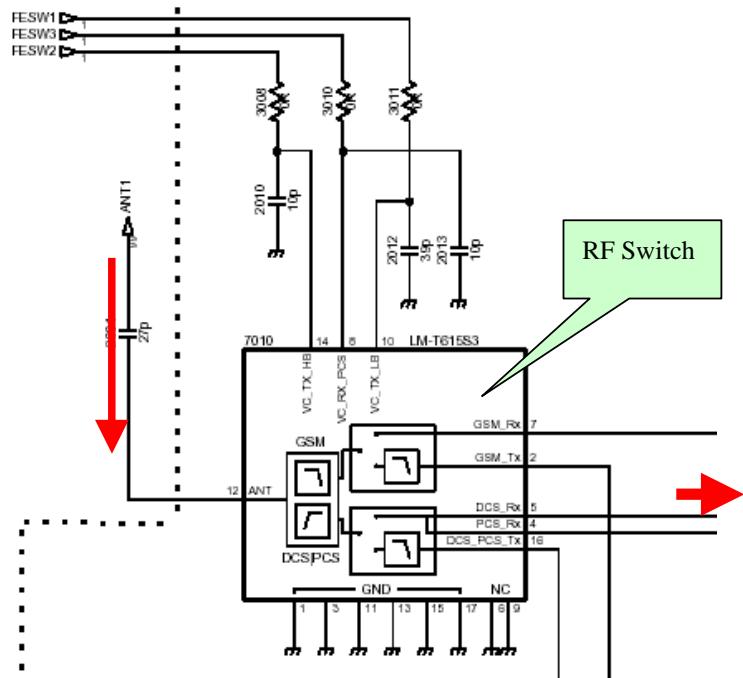

2. Signal output from RF Connector will be input to RF\_SW. Tranceiver control FSW1、FSW2、FSW3 signals, which will be in charge of RF\_SW in relative Band(EGSM、DCS、PCS), and in TX/RX status..

Following is the relative controlling signal status :

### 3. Control Logic

| Operating Mode | VCONT1 | VCONT2 | VCONT3 |

|----------------|--------|--------|--------|

| Tx-GSM850/900  | H      | L      | L      |

| Tx-DCS/PCS     | L      | H      | L      |

| Rx-GSM850/900  | L      | L      | L      |

| Rx-DCS         | L      | L      | L      |

| Rx-PCS         | L      | L      | H      |

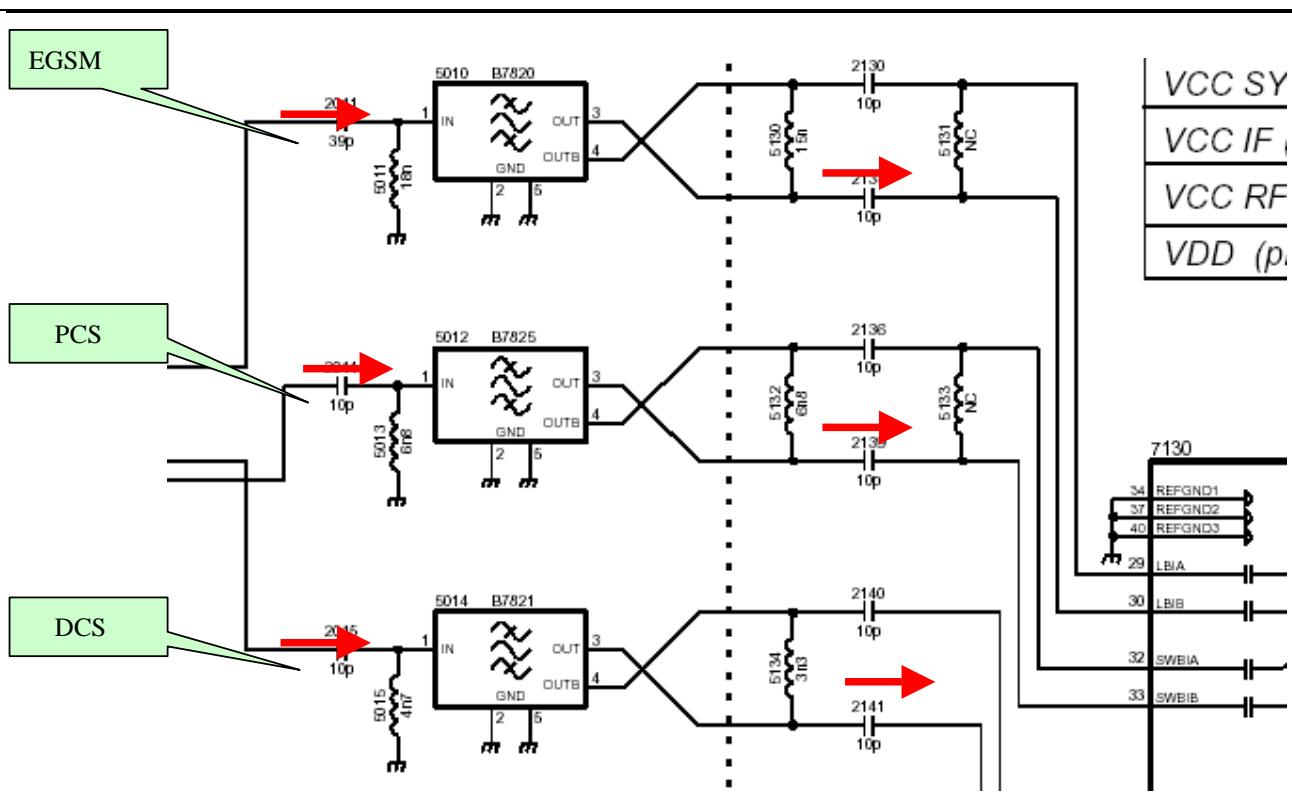

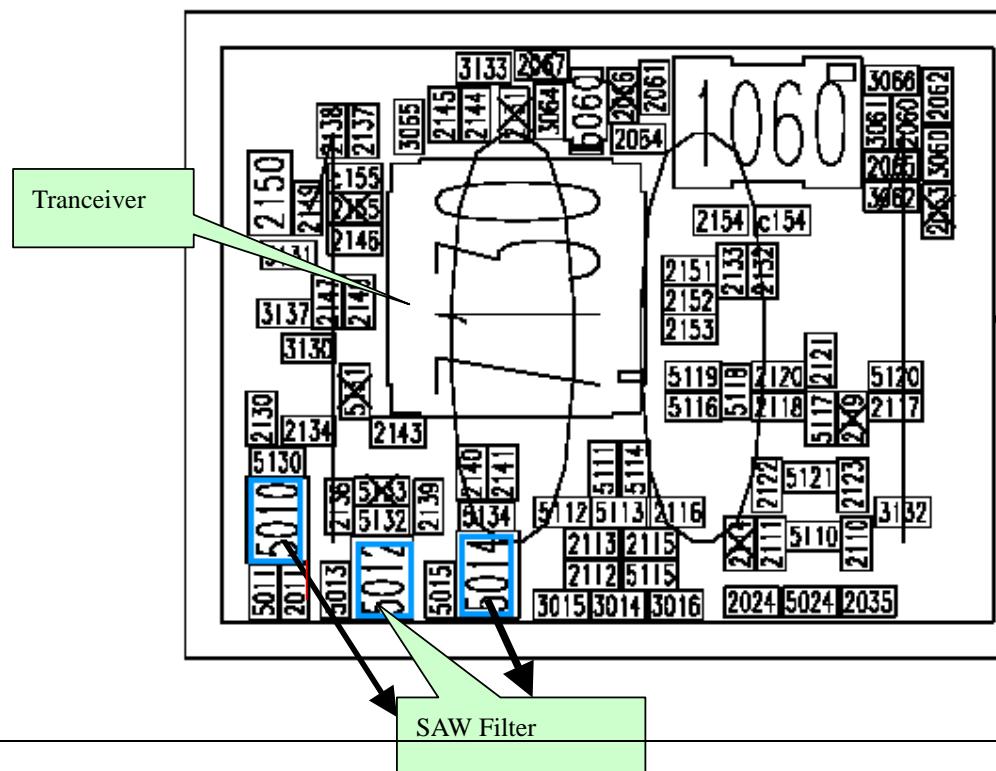

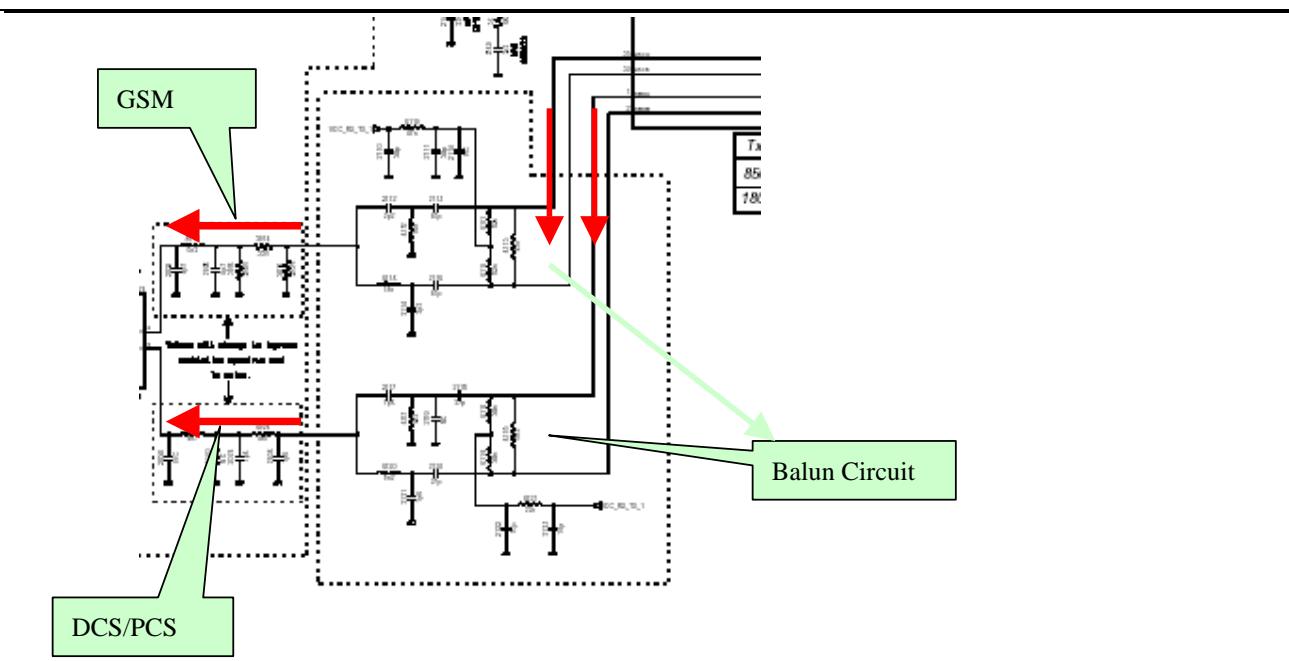

3. The RX signal output from RF\_SW, flowing to relative SAW Filter, then go through Balun circuit , input to tranceiver.

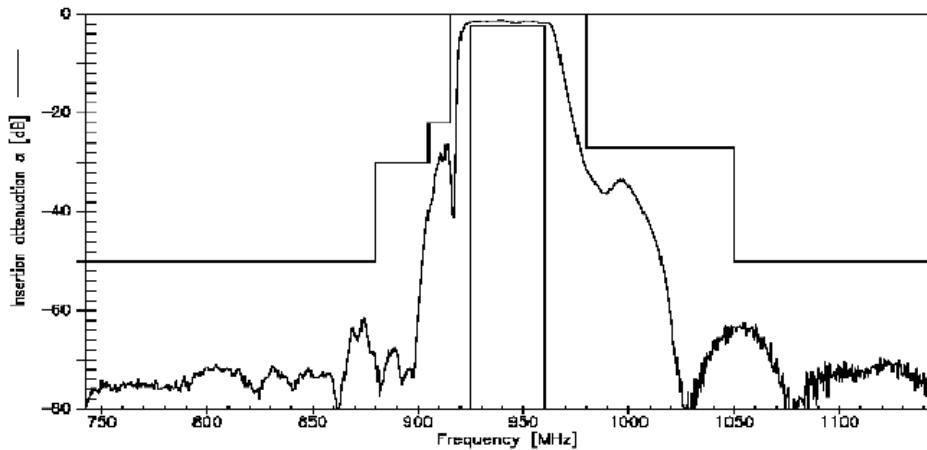

SAW Filter

For example:(EGAM, 925-960Mhz)

SAW Filter (EGSM)

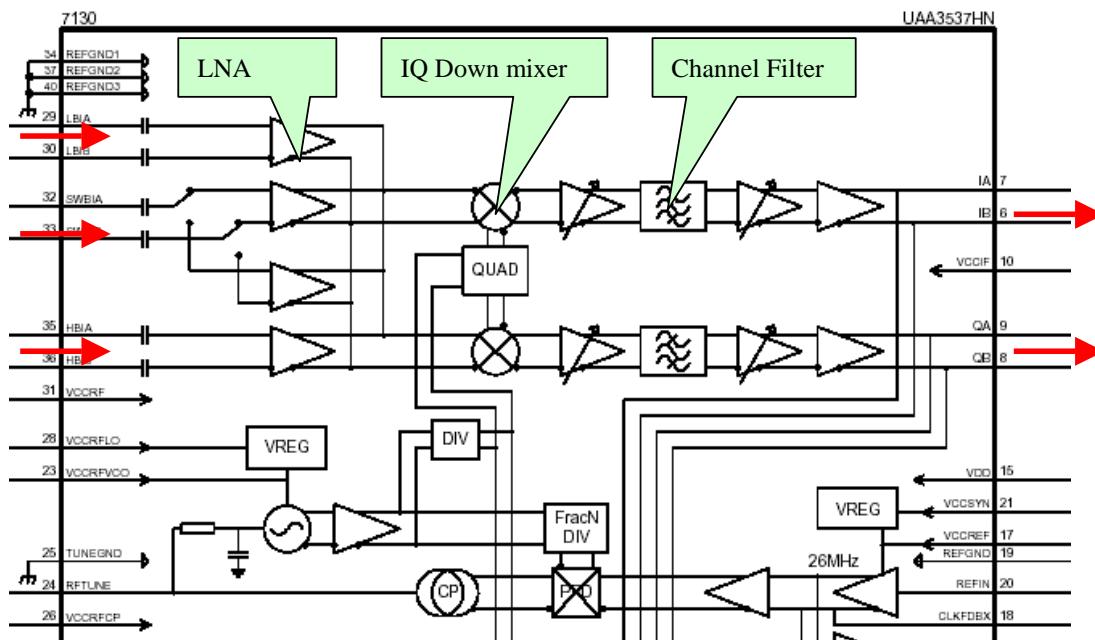

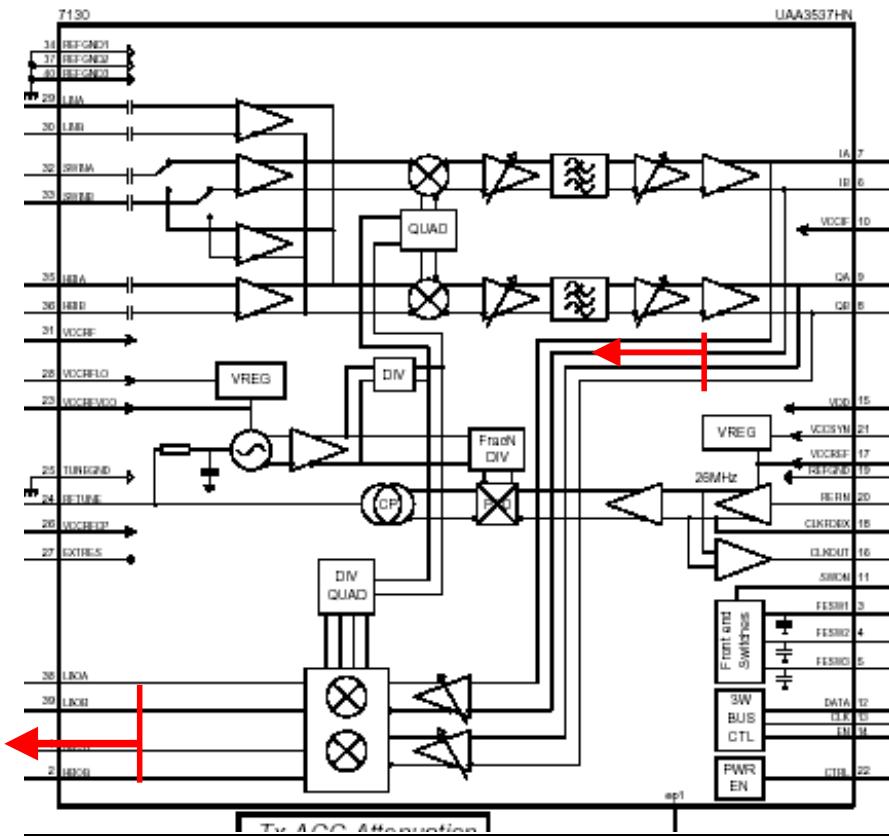

4. 7130 is the main IC in RF circuit, which response for signal modulation and demodulation. Signal input in 7130 after pass BPF, Signal pass LNA, then mix with local signal (RF-VCO) get the -100Khz signal. After pass the filter, output (IA IB QA QB) IQ signal. RF-VCO is fully integrated inside 7130.

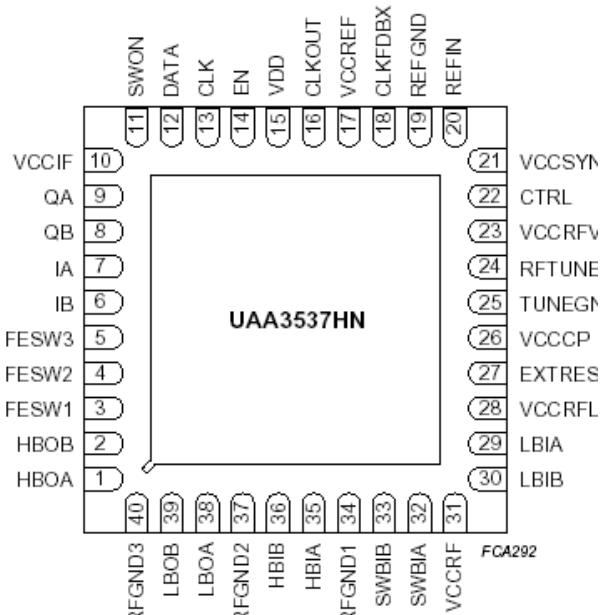

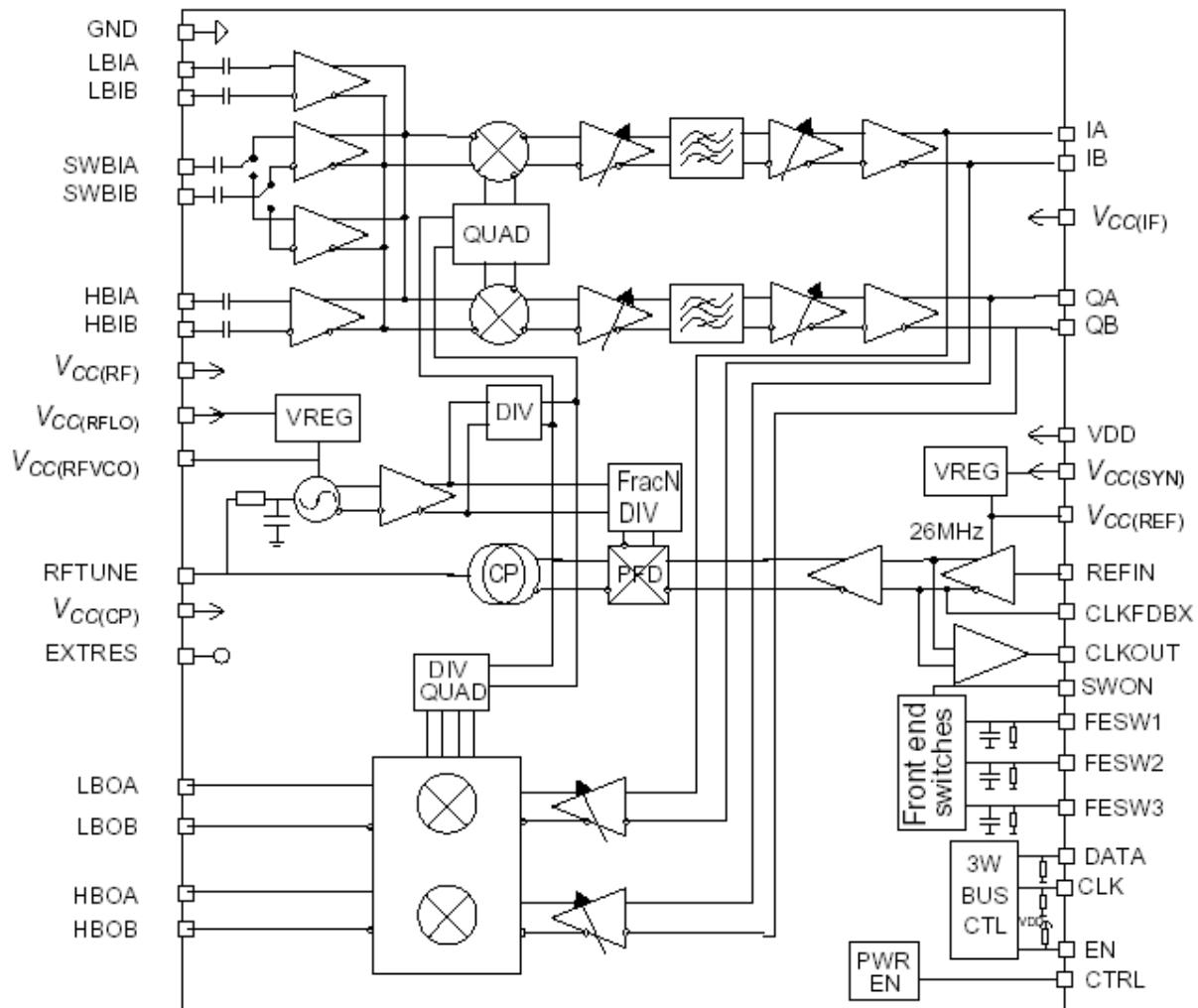

The receiver consists of two distinct parts, the RF receiver front-end and IF section. The RF front-end amplifies the EGSM/DCS/PCS aerial signal, converts the chosen channel down to a low IF of  $-100\text{kHz}$ , and provides in addition more than 35dB image suppression. Four LNAs are available on chip and can be configured to allow 3 bands (low, high and switched). The switched LNA will be used for roaming in different countries. Some selectivity is provided at this stage by an on-chip low-pass filter, channel selectivity is provided by means of a high performance integrated band-pass filter. The IF section further amplifies the wanted channel, performs gain control to tune the output level to the desired value and rejects DC.

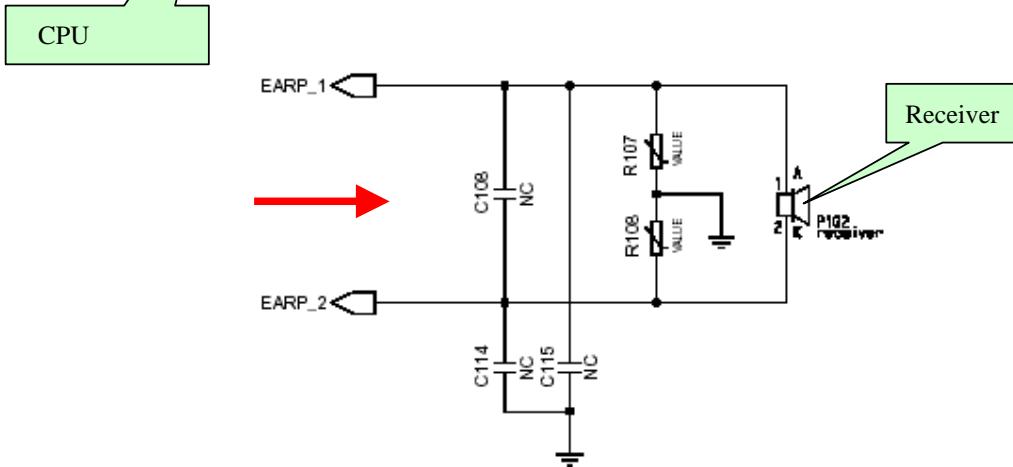

5. Four IQ signals input to CPU, go through A/D, DSP, and D/A section in CPU, then output to receiver.

## Tuning Up procedure & Operational Manual

### Trouble shooting to receiver circuit

1. We separate the failures in 3 parts: Logic failure, receiver failure and transmission failure. First we need define the failure according to the failed item then we begin the analysis in detail.

2. Receiver key parameters include: RX LEVEL, RX QUALITY, MOBILE CALL, FLATNESS, TIME MASK, PHASE ERROR, FREQUENCY ERROR, etc.

- 2.1 Confirm the analyzer station has been set up:

- a .Setup the right work condition of Agilent8960: Band: EGSM; Channel, Altitude of transmitter of the BS.

- b. Power on radio, Connect the RF cable from 8960 to radio, setup right channel no. and RX altitude of debug tool, same as 8960.

- C. then using debug tool in RX mode, press 'measure' button to check whether the received signal is same as input signal.

Test signal on a good radio to get reference signal when you don't know if the signal is right

Step1:Measure the received signal according to signal flowing chart.

Measure the signal with spectrum analyzer on 2001 to check if the input signal is right. If wrong signal was detected it maybe U501 cold sold or part defect.

Measure the signal on pin12 of 7010 to check if the input signal is right. If wrong signal was detected it maybe 2001 cold soldering, tombstone part, part missing or screwed part.

Step2: Measure the output signal from 7010 to check if the signal is right, EGSM signal: measured from pin 7 (Measure at 2011); DCS signal: measured from pin5 (at 2015), and for PCS at 2014. If the signal is not right, should check if 7010 cold soldering, soldering short part, part defect or un-soldering. If no defect was found at 7010, then check if the control signal “FSW1, FSW2, FSW3” is right. If the signal is not right please check 7130 and parts around them. If no clear issue found, change 7010, 7130, one by one

Step3: Measure the input signal and output signal of BPF. If the input signal is wrong, check on 2011: EGSM and 2015: DCS, 2014:PCS. If the output signal is wrong , check the filter 5010: EGSM, 5014: DCS, 5012:PCS: 2014

Step4: Measure I/Q signal output from 7130. If the signal is not good, check if there are defects on 7130. Also need check the working voltage of 7130.

Step5: Measure I/Q Signal input to CPU, Otherwise change 7300.

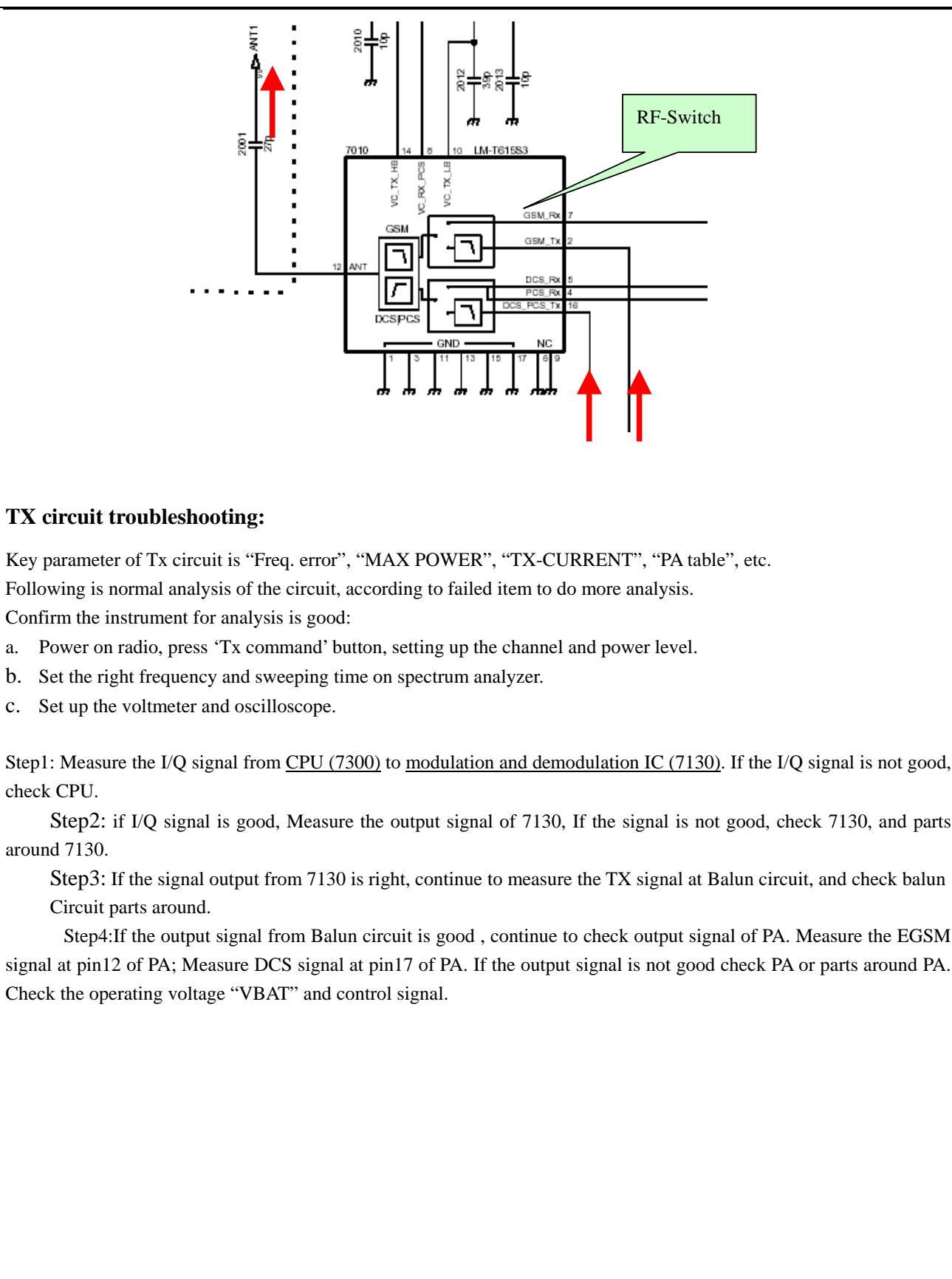

### 5.2.2 Transmitter principle and troubleshooting:

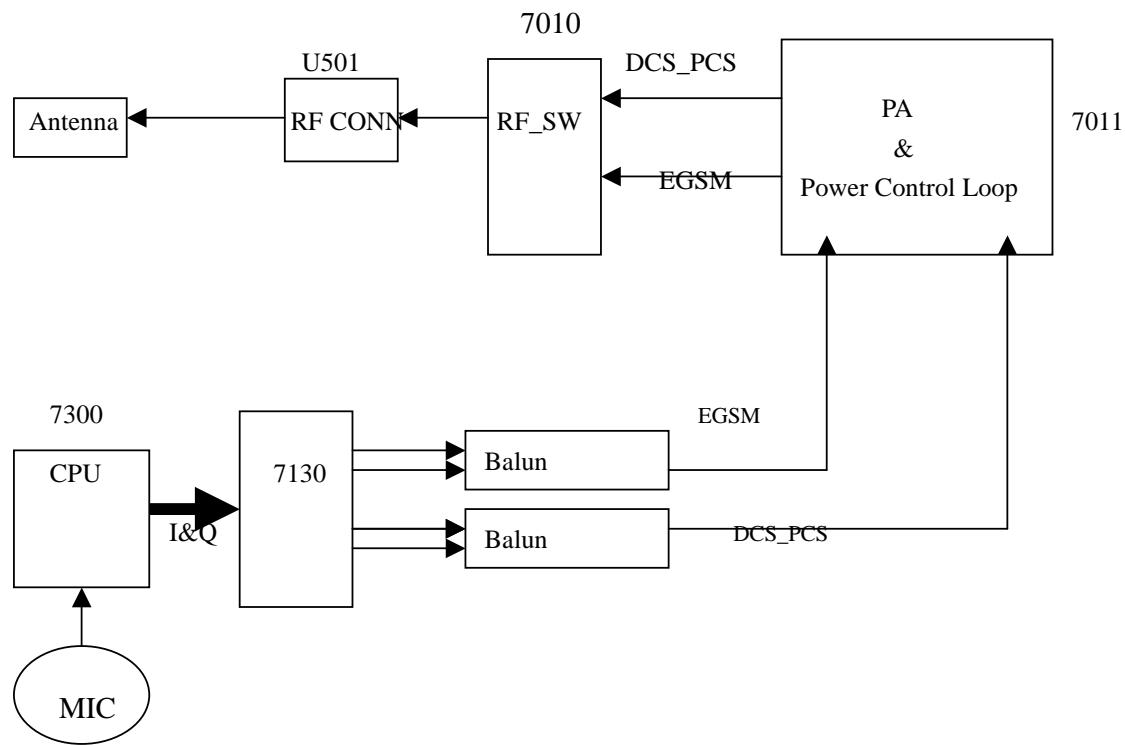

Transmitter circuit signal flowing chart:

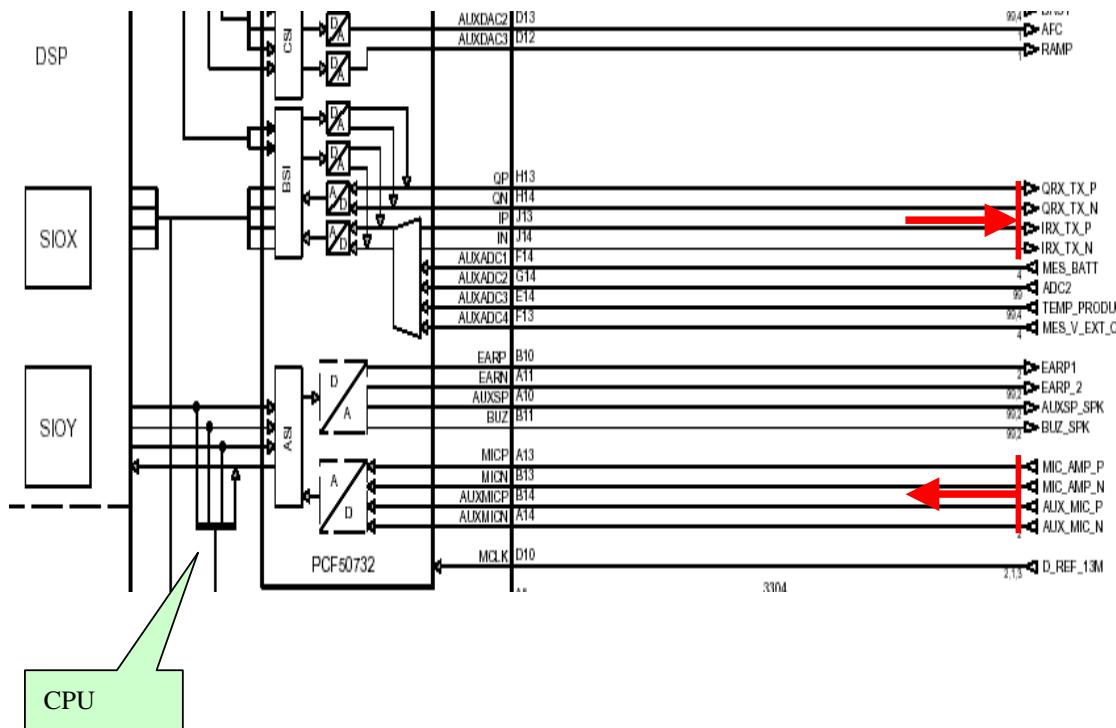

## 1. Microphone to CPU (7300):

Audio signal input from Microphone , Microphone convert the voice signal to analog signal and input to CPU (7300).

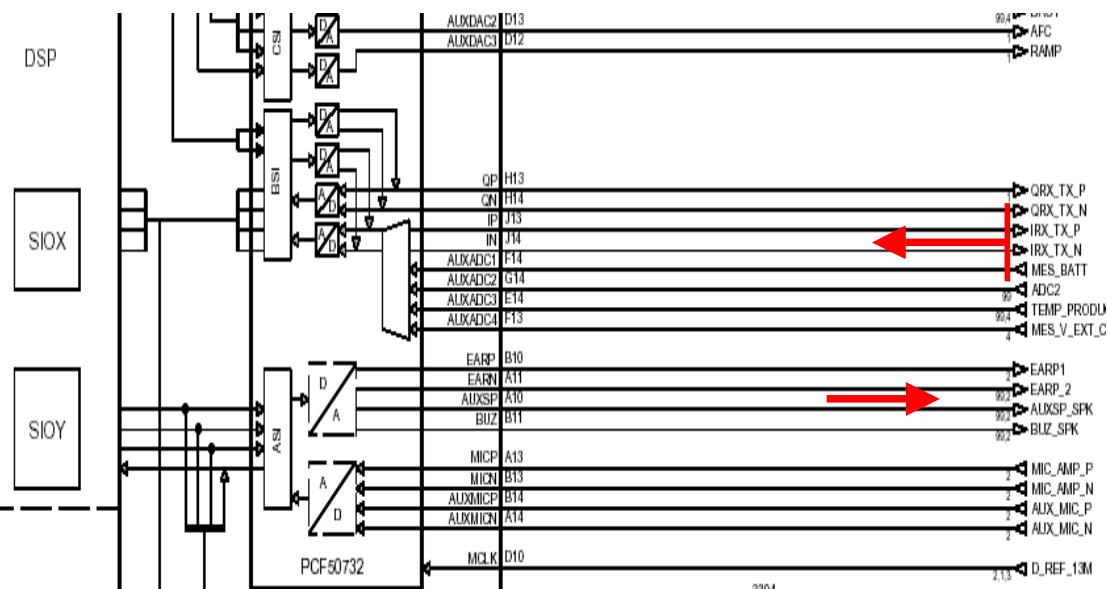

2. After A/D, convert analog signal to logic signal in CPU. Then send the logic signal to DSP pass ASI. Then processed logic signal pass D/A converter divided into four signals (IQ), output from CPU (7300) to 7130, QRX-TX-P, QRX-TX-N, IRX-TX-P, IRX-TX-N .

2. Then the I/Q signal modulate in 7130. The transmitter is fully differential using a direct-up conversion architecture. It consists of a single side band power up mixer. The fully-integrated VCO and the power mixer are designed to achieve LO suppression, quadrature phase error, quadrature amplitude balance and low noise floor specifications.

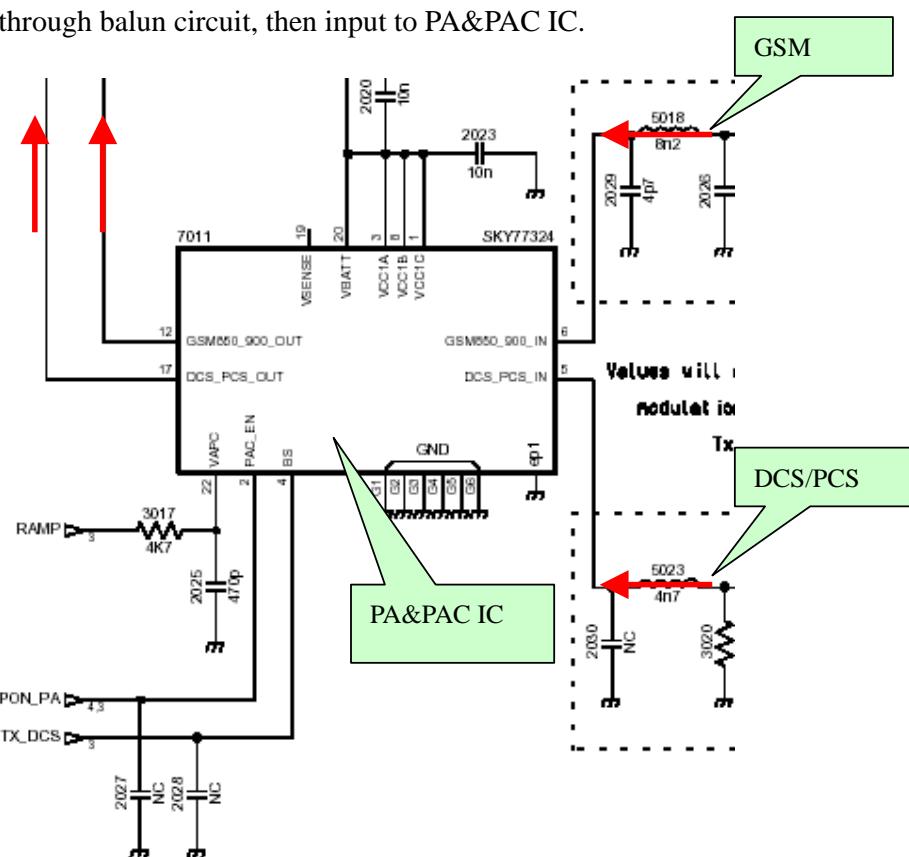

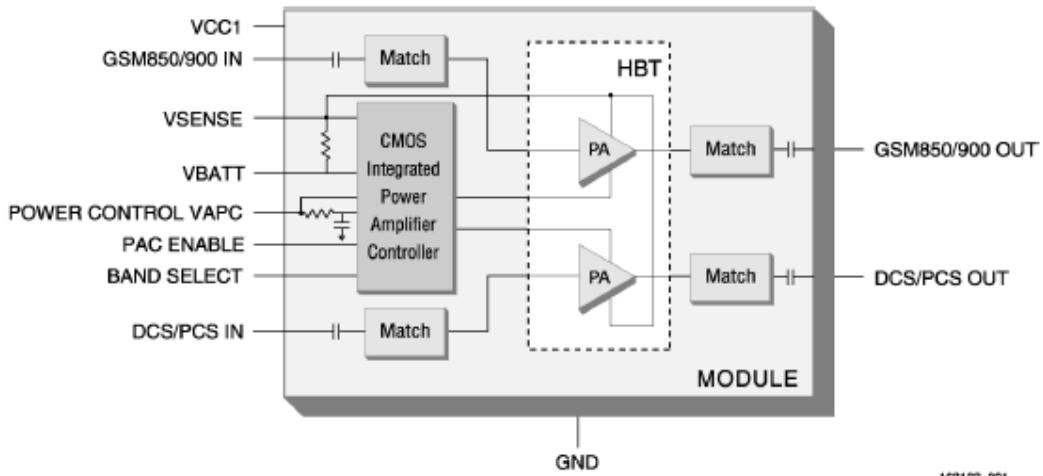

3. Output Signal from tranceiver will pass by Balun circuit, then flow to PA&PAC IC.

4. TX signal flow through balun circuit, then input to PA&PAC IC.

5. Tx signals output from PA, flow through RF-SW, RF-Connector to antenna.

Step5: Measure the input signal and output signal of RF-SWITCH (7010). Also need check and control signal of 7010 .

Measure antenna at last. Check U501, Antenna, if the signal is not good.

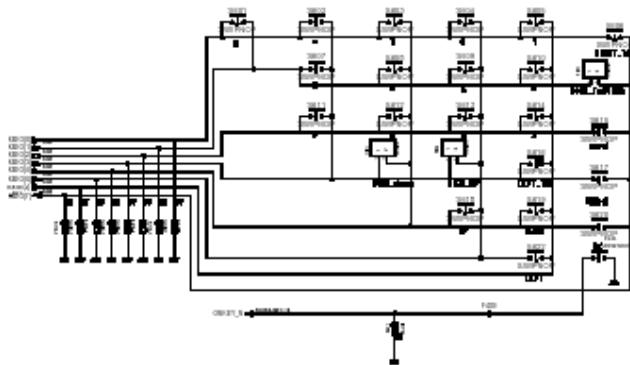

### 5.2.3 Logic circuit principle and troubleshooting:

#### radio can't turn on

##### 1. the turning on process introduction :

- A. First power on radio, then after getting V\_BAT, PMU will generate V\_ISUP(2.7V), 7400 32.768K oscillator begin to run. ONKEY\_N output 2.3V.

- If radio is connected with I/O CABLE, when DownLoad software into radio, PC Sever will be ready.

- B. Pressing ON\_KEY, about 14ms later, PMU will generate VDD1,VDD2, VDD3,AVDD,VCC\_SYN and VDD1,VDD2 ,AVDD is supplied to CPU, V-MEM is supplied to Memory, VCC\_SYN is supplied to 7130.

7130 will generate VCCREF which will be used for 1060(oscillator). After 9 CLK32 period(one CLK32 period is about 30uS),1060 will generate stable 26M clock signal, which will be divided by 2 inside 7130 ,and output REF\_13M supplied to CPU.

- C. After 32 CLK32 period when already generated stable 26M clock, the ON/OFF CONTROL module in PMU will generate RESTO\_N signal, which will flow to CPU ,and reset CPU.

D. After resetting CPU, the basic turning on information read from ROM inside will be sent out by TXD0 pin, these codes will be sent to connector, if connector is connected with PC Sever by I/O CABLE, PC Sever will send back a reply code by RXD0 pin to CPU, Radio hand in PC successfully. Then begin to download ‘.fdl’ file into Flash.

E. If connector is not connected with PC by I/O CABLE, no reply code feedback, CPU will run , open Bus, send out Chip-select signal, then run ‘.fdl’ file in Flash, open backlight, display etc, enter normal mode.

**2. Trouble shooting :Radio cannot power on:**

A.

- a. Power the radio measure “VBAT”. If the voltage is not correct check battery or power supply.

- b. Check the battery connector or interface connector.

- c. Check the base band power supply and RF power supply provide by 7400. if not correct change 7400.

- d. Check if 32Khz oscillator work. If not work change oscillator.

- e. Check if 26M oscillator work. If it doesn’t work, change 26M oscillator. Also need check the parts around it;

- f. Check PMU, Memory, CPU, tranceiver, otherwise change them.

**Vibration issue:**

Check if the vibrator is good.

Check if there are assembly issues.

Check if the motor connector, has problem.

Check relative parts.

**No key function:**

Check metal dome, otherwise change it.

Check side key, whether there is soldering issue.

Check whether it’s PCB issue.

Check CPU IC whether CS,US, otherwise change it.

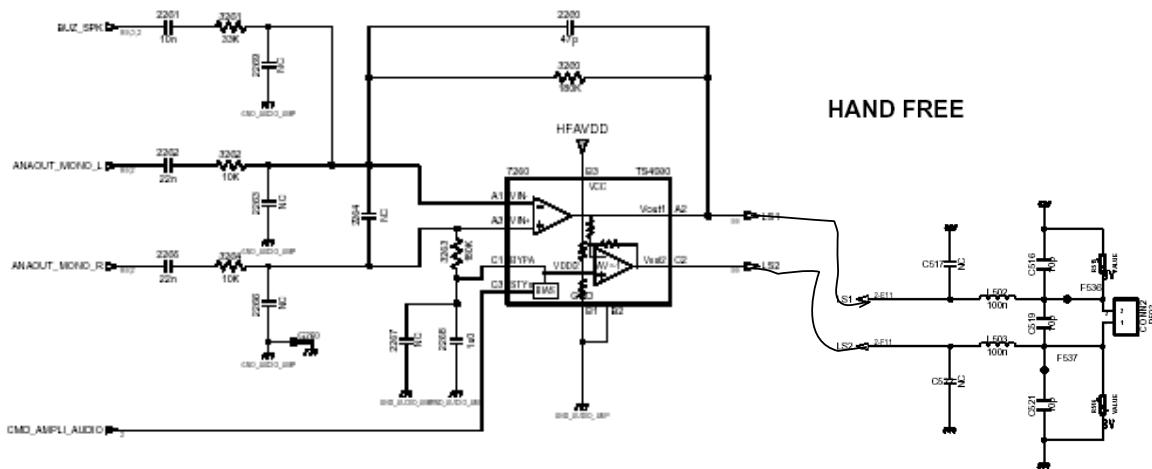

## Tuning Up procedure & Operational Manual

### No hand free function:

Check the soldering issue of component.

Check Audio PA 7200, whether CS, US, CD.

Check Speaker, LCD FPC, otherwise change them.

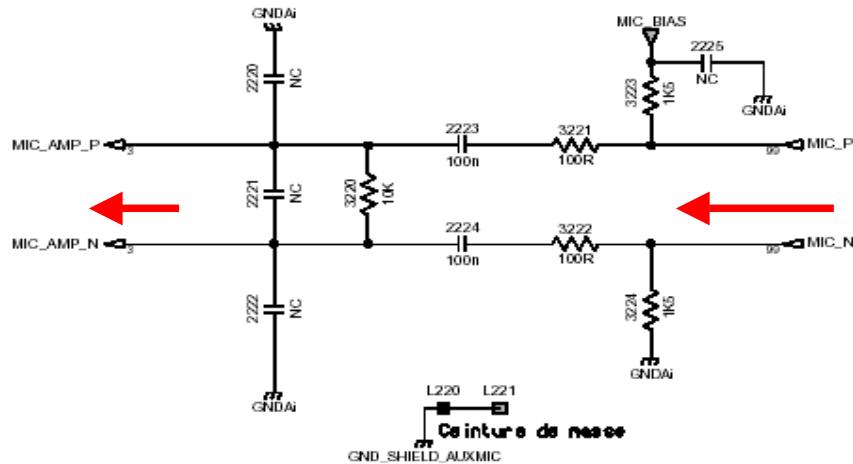

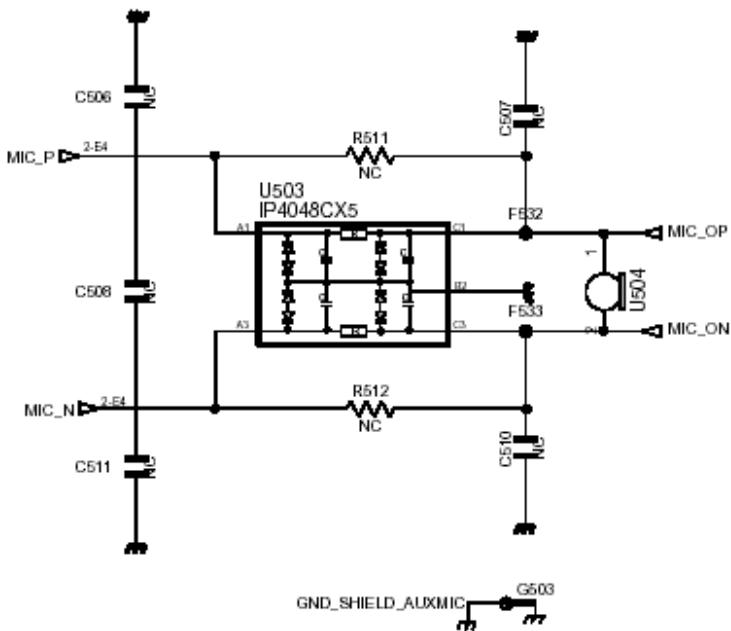

### Mic has no function:

Check the assembly of Mic. Avoid assembly issue.

Check the signal at contact point to the Mic.

If the signal is not correct check the part in the circuit.

Check the signal "MIC-BIAS". If it's not correct, change 7400.

Otherwise change MIC, U503 in turns.

## MICROPHONE

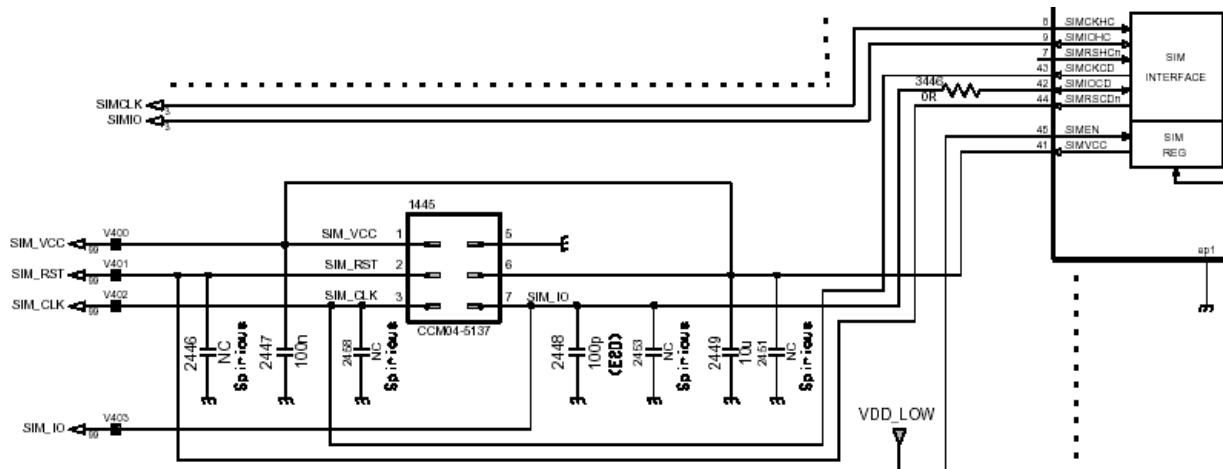

### **Check SIM card issue:**

Check whether the SIM card can work

Check no soldering issue to SIM connector.

Check the good contact between SIM card and the connector

Check if the power signal is correct.

Check if the clock signal is correct.

Check if I/O signal is correct.

Otherwise change SIM connector, PMU, CPU in turns.

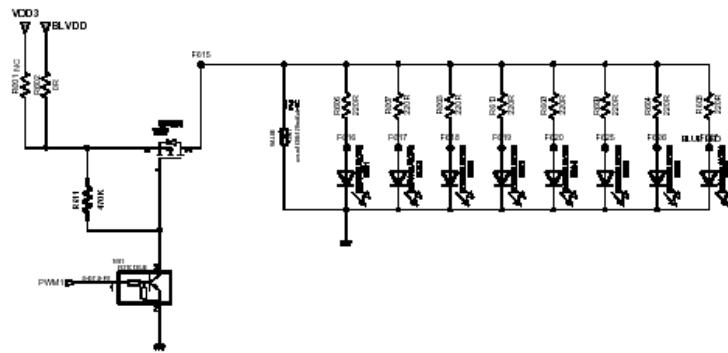

No back light:

1. Check back light and Resistance.

2. Check voltage of BLVDD, if it is abnormal, change 7400.

3. Check T602,T601 and relative parts, otherwise change it.

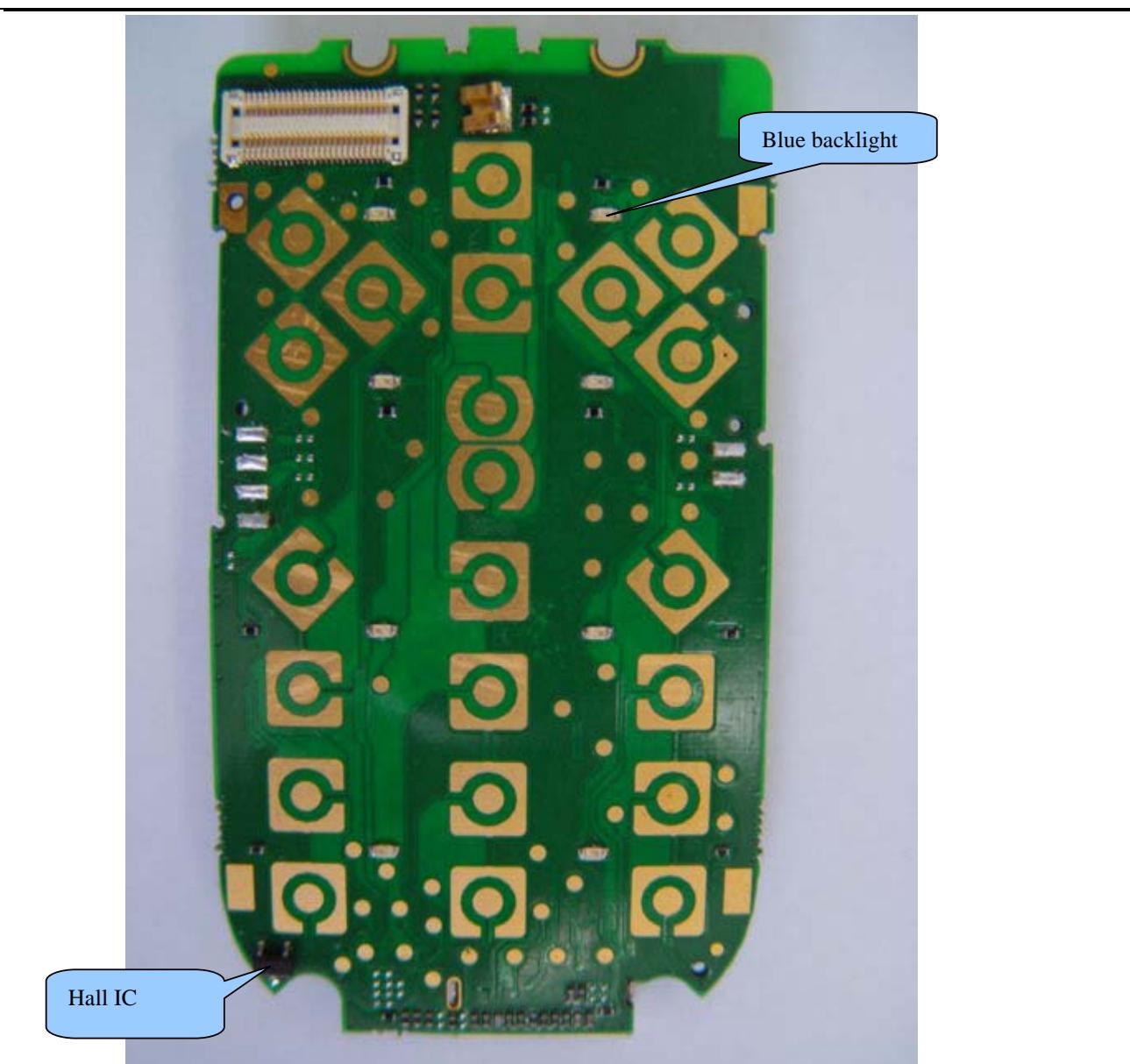

#### BACKLIGHT FOR KEYPAD

No display:

1. Check LCD FPC ,re-assemble the phone.

2. Check Connector on PCBA,, Pin on LCD PCB, whether CS,US,SS,CD.

3. Check LCD MODULE whether it's defective.

4. Otherwise change CPU,MEMORY, PMU in turn.

No camera function:

1. Check LCD FPC ,if it's defective, change it .

2. Check LCD MODULE(Sensor inside), if it's defect, change it .

3. Check LCD Connector on PCBA, whether it's CS,US SS.

4. Otherwise change CPU, MEMORY IC in turn.

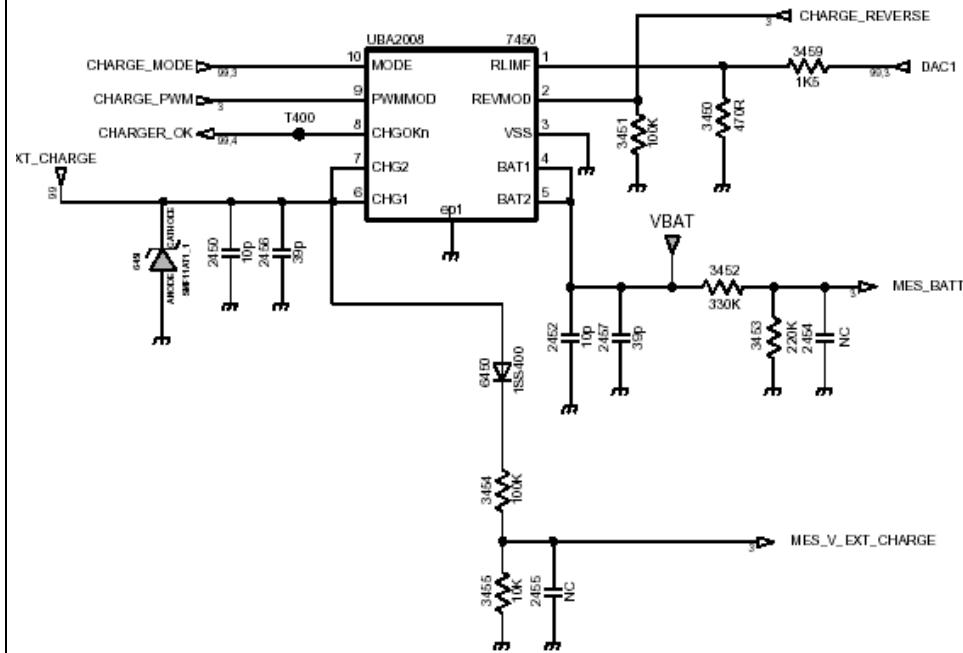

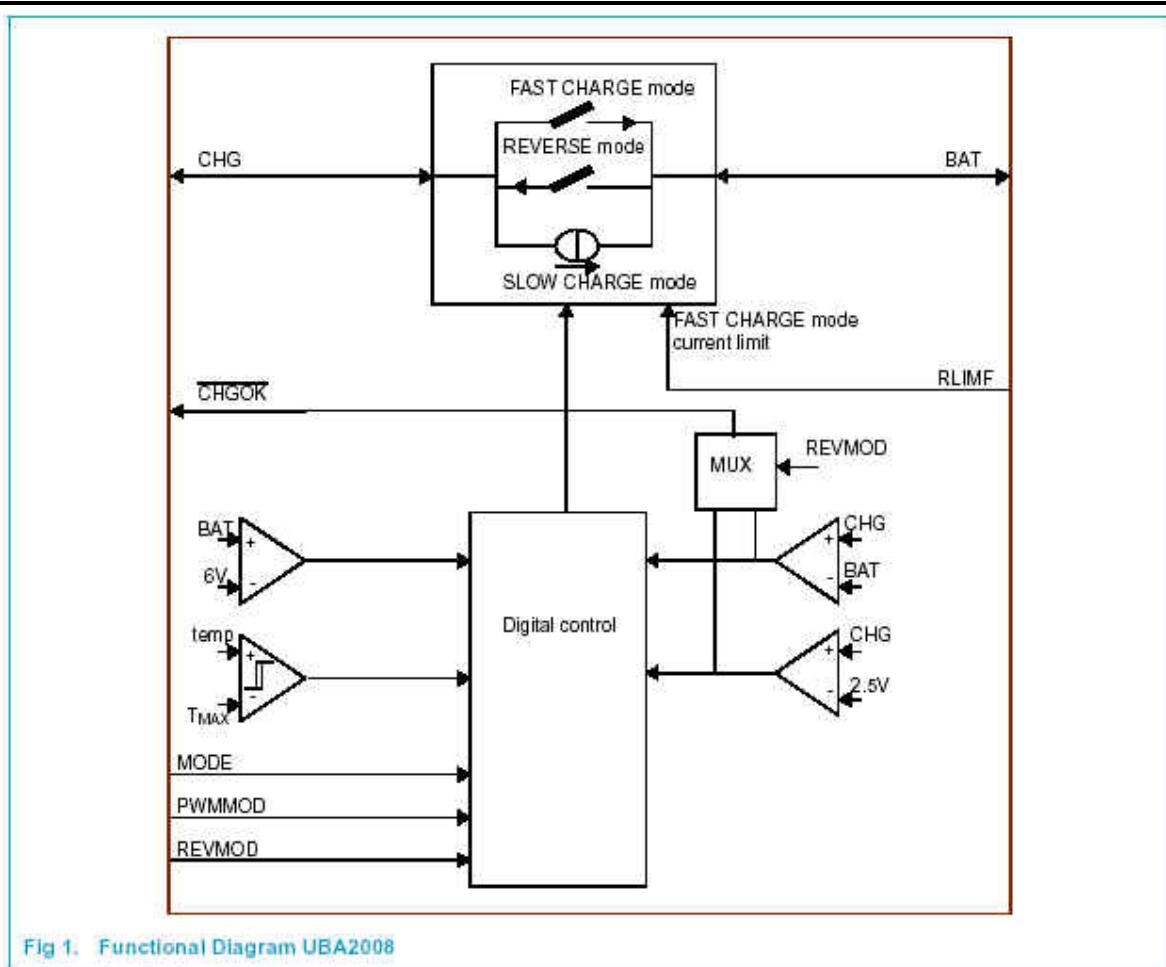

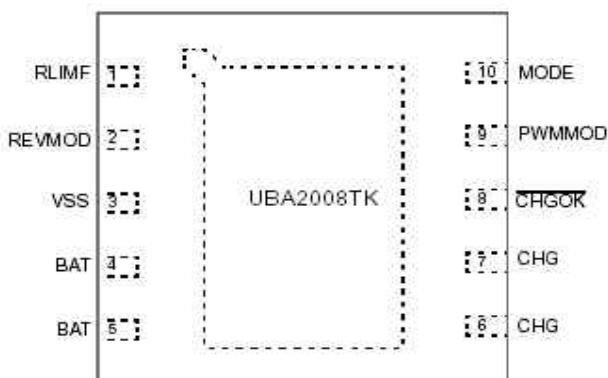

**No charging function:**

Check if the battery connector is good.

Check whether the charging IC is good.

Check other relative parts around charging circuit

Check all the relative signals.

Change 7450,7400, 7300 one by one at last.

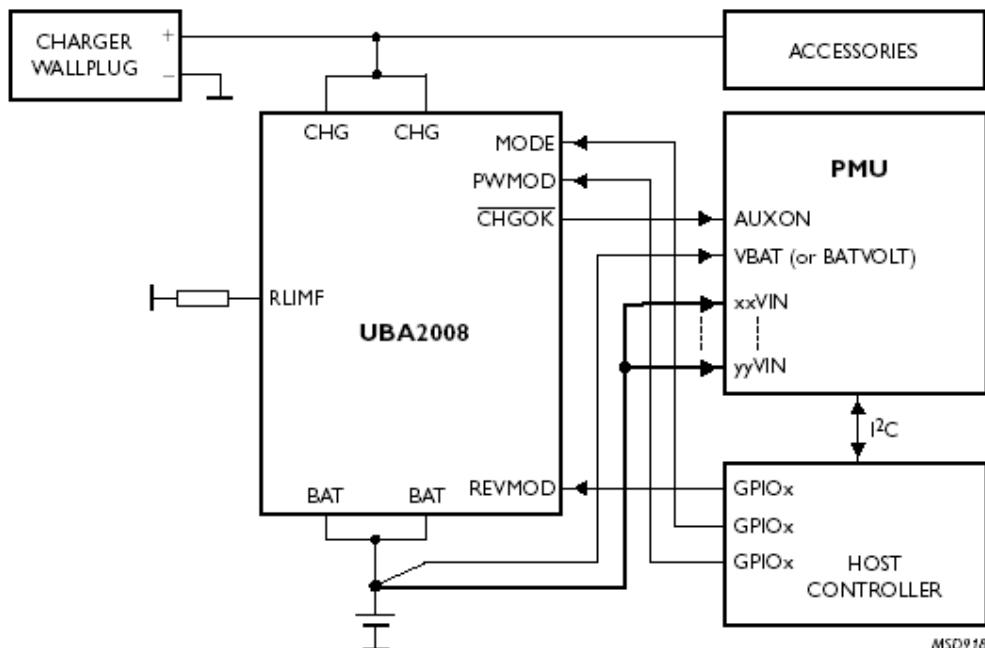

### Charge of Battery

REF = 450-499 Function code = 2B7

charging function figure:

MSD918

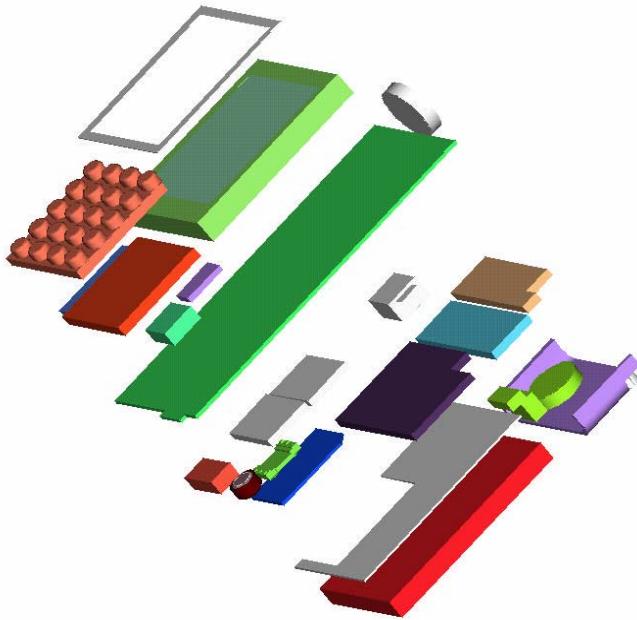

**Tuning Up procedure & Operational Manual****5.3 Figure:****5.3.1 Product exploded view:****5.3.2 Defect description abbreviation:**

|    |                      |      |                          |      |                       |

|----|----------------------|------|--------------------------|------|-----------------------|

| 冷焊 | CS (Cold Solder)     | 多余焊锡 | ES (Excess Solder)       | 元件歪斜 | SP (Skewed Part)      |

| 连焊 | SS (Solder Short)    | 元件翘起 | TP (Tombstone Part)      | 元件移动 | MP (Misaligned Part)  |

| 开路 | OT (Open Trace)      | 元件放反 | RP (Reversed Part)       | 元件丢失 | PM (Part Missing)     |

| 短路 | DS (Direct Short)    | 多余元件 | EP (Extra Part)          | 元件损坏 | DP (Damaged Part)     |

| 错件 | WP (Wrong Part)      | 管脚弯曲 | BP (Bent Pin)            | 元件缺陷 | CD (Component Defect) |

| 虚焊 | PS (Pretense Solder) | 焊锡不足 | IS (Insufficient Solder) |      |                       |

## 6 Reference

### CT6558 main IC introduction:

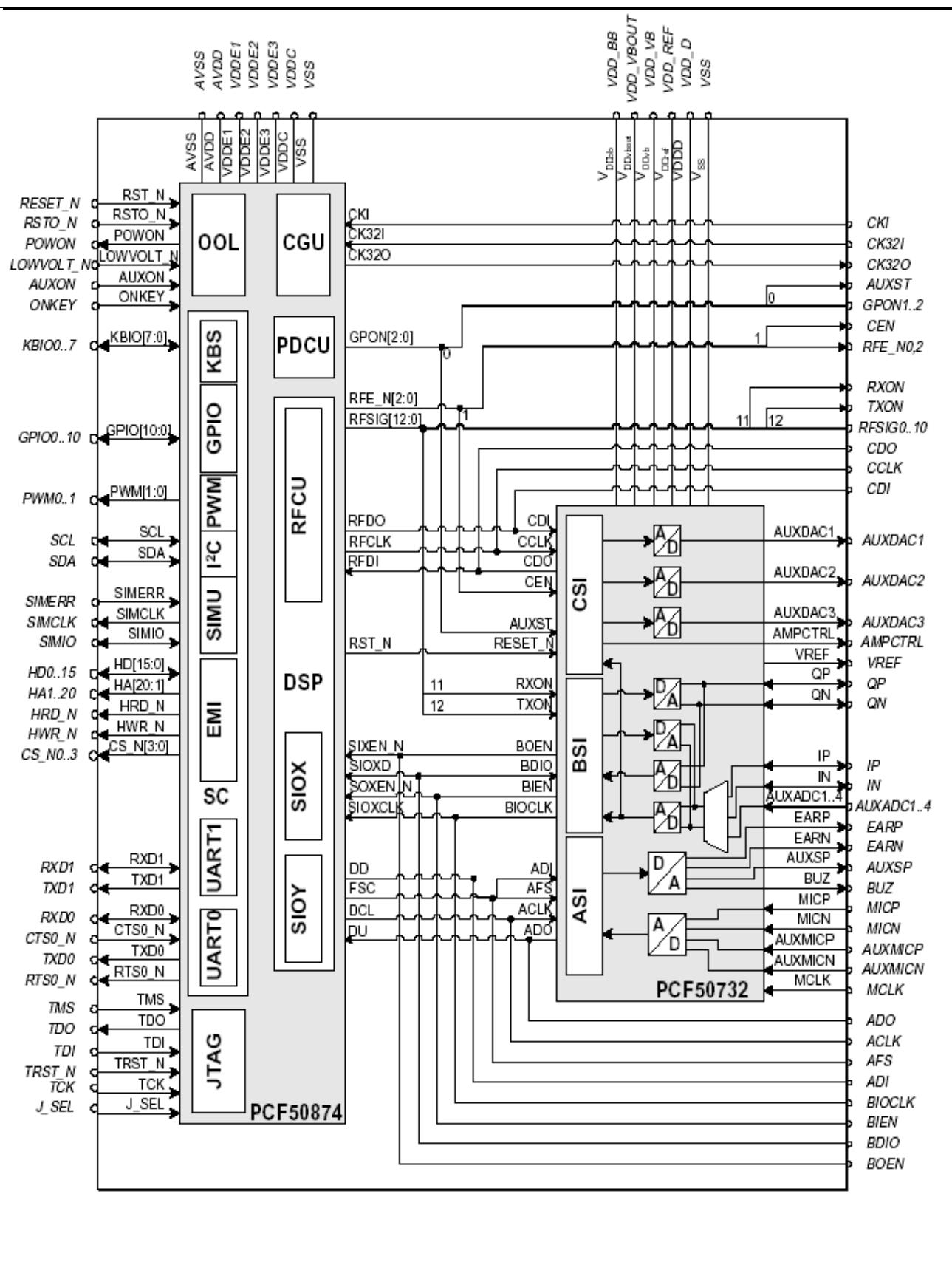

#### 6.1 CPU (OM6357-7)

##### 7300:

###### 1 GENERAL REMARKS

The OM6357-7 is a multichip package (MCP) containing two integrated circuits. It is designed to provide the baseband processing for GSM handsets. The components are:

- PCF50874-6, an integrated baseband processor with an ARM micro controller, R.E.A.L. DSP, timer and interface hardware.

- PCF50732, an analogue baseband and audio interface with voiceband processor (VSP), baseband and auxiliary CODECs.

Table 4 Pin Description

| OM6357-7                              |                                                |                                                                    | CONNECTED TO DEVICE SIGNALS |        |       |          |        |          |

|---------------------------------------|------------------------------------------------|--------------------------------------------------------------------|-----------------------------|--------|-------|----------|--------|----------|

| NAME                                  | DESCRIPTION                                    | BALL                                                               | PCF50874-6                  |        |       | PCF50732 |        |          |

|                                       |                                                |                                                                    | TYP<br>E                    | SUPPLY | NAME  | TYP<br>E | SUPPLY | NAME     |

| Power and Ground <sup>(5)(6)(7)</sup> |                                                |                                                                    |                             |        |       |          |        |          |

| VSS                                   | Groundconnections<br>PCF50874-6                | C3, E8, G1,<br>G13, J1, K1,<br>K7, M7, N5,<br>N10, N11,<br>N14, P1 | G                           |        | VSS   |          |        |          |

| AVSS                                  | Analog ground<br>PCF50874-6                    | P10                                                                | G                           |        | AVSS  |          |        |          |

| VSS_BB                                | PCF50732<br>Baseband analog<br>ground          | E13                                                                |                             |        |       | G        |        | Vss      |

| VSS_REF                               | PCF50732<br>Bandgap Reference<br>ground        | C13                                                                |                             |        |       | G        |        | Vss      |

| VSS_VB                                | PCF50732<br>Voiceband ground                   | A12                                                                |                             |        |       | G        |        | Vss      |

| VSS_VBOUT                             | PCF50732<br>Voiceband output<br>drivers ground | C11                                                                |                             |        |       | G        |        | Vss      |

| VSSD                                  | PCF50732 Digital<br>ground                     | D11                                                                |                             |        |       | G        |        | Vss      |

| VDD_BB                                | Analog supplies                                | F12                                                                |                             |        |       | P        |        | VDDbb    |

| VDD_REF                               | PCF50732                                       | D14                                                                |                             |        |       | P        |        | VDDref   |

| VDD_VB                                |                                                | B12                                                                |                             |        |       | P        |        | VDDvb    |

| VDD_VBOUT                             |                                                | C12                                                                |                             |        |       | P        |        | VDDvbout |

| VDD_D                                 | Digital supply<br>PCF50732                     | C9                                                                 | P                           |        |       | P        |        | VDDD     |

| AVDD                                  | Analog supply<br>PCF50874-6                    | P12                                                                | P                           |        | AVDD  |          |        |          |

| VDDE1                                 | Digital supplies for<br>PCF50874-6             | C8, H11, N12,<br>P9                                                | P                           |        | VDDE1 |          |        |          |

| VDDE2                                 |                                                | P8, C1                                                             | P                           |        | VDDE2 |          |        |          |

| VDDE3                                 |                                                | P4, M6, G2,<br>L3                                                  | P                           |        | VDDE3 |          |        |          |

| VDDC                                  | Digital supply for<br>core of<br>PCF50874-6    | F5, N13, M8,<br>K6                                                 | P                           |        | VDDC  |          |        |          |

| Reference Voltage                     |                                                |                                                                    |                             |        |       |          |        |          |

| OM6357-7                               |                                                 |      | CONNECTED TO DEVICE SIGNALS |        |                         |                                                                                      |        |         |

|----------------------------------------|-------------------------------------------------|------|-----------------------------|--------|-------------------------|--------------------------------------------------------------------------------------|--------|---------|

| NAME                                   | DESCRIPTION                                     | BALL | PCF50874-6                  |        |                         | PCF50732                                                                             |        |         |

|                                        |                                                 |      | TYP<br>E                    | SUPPLY | NAME                    | TYP<br>E                                                                             | SUPPLY | NAME    |

| VREF                                   | bandgap reference for external noise decoupling | C14  |                             |        |                         | IO                                                                                   | VDD_RF | VREF    |

| On/Off Logic                           |                                                 |      |                             |        |                         |                                                                                      |        |         |

| RST_N <sup>(5)</sup>                   | PCF50874-6 reset output                         | H10  | IO                          | VDDE1  | RST_N                   |                                                                                      |        |         |

| RESET_N <sup>(5)</sup>                 | PCF50732 reset input                            | C10  |                             |        |                         | I                                                                                    | VDDD   | RESET_N |

| RSTO_N                                 | PCF50874-6 reset input                          | M10  | I                           | VDDE1  | RSTO_N                  |                                                                                      |        |         |

| AUXON_N                                | auxiliary power-on signal                       | K14  | I                           | VDDE1  | AUXON_N                 |                                                                                      |        |         |

| Clocks                                 |                                                 |      |                             |        |                         |                                                                                      |        |         |

| CKI                                    | 13MHz clock input                               | P11  | I                           | AVDD   | CKI                     |                                                                                      |        |         |

| CKI32I                                 | 32kHz clock input                               | P13  | I                           | VDDE1  | CLK32I                  |                                                                                      |        |         |

| CK32O_TES<br>T/TRCCLK <sup>(2)</sup>   | CLK32k test output/Trace Clock                  | P14  | O                           | VDDE1  | CLK32O_TE<br>ST/TRCCLK  |                                                                                      |        |         |

| MCLK                                   | 13MHz clock input                               | D10  |                             |        |                         | I                                                                                    | VDD_BB | MCLK    |

| RF Control Interface                   |                                                 |      |                             |        |                         |                                                                                      |        |         |

| CCLK                                   | RF interface clock                              | E10  | O                           | VDDE1  | RFCLK                   | I                                                                                    | VDDD   | CCLK    |

| CDO                                    | control serial data                             | E9   | I                           | VDDE1  | RFDI                    | O                                                                                    | VDDD   | CDO     |

| CDI                                    | control serial data                             | D8   | O                           | VDDE1  | RFDO                    | I                                                                                    | VDDD   | CDI     |

| CEN                                    | enable ctrl. serial                             | D9   | O                           | VDDE1  | RFE_N1                  | I                                                                                    | VDDD   | CEN     |

| RFE_N2                                 | additional RF interface enables                 | K12  | O                           | VDDE1  | RFE_N2                  |                                                                                      |        |         |

| RFE_N0/<br>TRCPKT[0] <sup>(2)</sup>    | RF interface group enable 0/Trace Packet Port   | J12  | O                           | VDDE1  | RFE_N0/<br>TRCPKT[0]    |                                                                                      |        |         |

| RFSIG12/<br>PIPESTAT[2] <sup>(2)</sup> | baseband transmit active/Pipeline Status        | G12  | IO                          | VDDE1  | RFSIG12/<br>PIPESTAT[2] | RFIG12/RFSIG11 is indirectly showing the package internal connection to the PCF50732 |        |         |

| RFSIG11/<br>PIPESTAT[1] <sup>(2)</sup> | baseband receive active/Pipeline Status         | H12  | IO                          | VDDE1  | RFSIG11/<br>PIPESTAT[1] |                                                                                      |        |         |

| RFSIG10                                | signal generator output                         | D7   | O                           | VDDE1  | RFSIG10                 |                                                                                      |        |         |

| RFSIG9/PIPE<br>STAT[0] <sup>(2)</sup>  | signal generator output/Pipeline Status         | K10  | O                           | VDDE1  | RFSIG9/<br>PIPESTAT[0]  |                                                                                      |        |         |

| OM6357-7                             |                                                   |      | CONNECTED TO DEVICE SIGNALS |        |                       |                                                                                                   |        |      |

|--------------------------------------|---------------------------------------------------|------|-----------------------------|--------|-----------------------|---------------------------------------------------------------------------------------------------|--------|------|

| NAME                                 | DESCRIPTION                                       | BALL | PCF50874-6                  |        |                       | PCF50732                                                                                          |        |      |

|                                      |                                                   |      | TYP<br>E                    | SUPPLY | NAME                  | TYP<br>E                                                                                          | SUPPLY | NAME |

| RFSIG8                               | signal generator output                           | E7   | O                           | VDDE1  | RFSIG8                |                                                                                                   |        |      |

| RFSIG7                               | signal generator output                           | O6   | O                           | VDDE2  | RFSIG7                |                                                                                                   |        |      |

| RFSIG6                               | signal generator output                           | B7   | O                           | VDDE2  | RFSIG6                |                                                                                                   |        |      |

| RFSIG5/<br>TRCSYNC <sup>[2]</sup>    | signal generator output/Trace Synchronisation     | C7   | O                           | VDDE2  | RFSIG5/<br>TRCSYNC    |                                                                                                   |        |      |

| RFSIG4                               | signal generator output                           | A7   | O                           | VDDE2  | RFSIG4                |                                                                                                   |        |      |

| RFSIG3                               | signal generator output                           | B6   | O                           | VDDE2  | RFSIG3                |                                                                                                   |        |      |

| RFSIG2                               | signal generator output                           | D6   | O                           | VDDE2  | RFSIG2                |                                                                                                   |        |      |

| RFSIG1                               | signal generator output                           | A6   | O                           | VDDE2  | RFSIG1                |                                                                                                   |        |      |

| RFSIG0                               | signal generator output                           | D5   | O                           | VDDE2  | RFSIG0                |                                                                                                   |        |      |

| Baseband Interface                   |                                                   |      |                             |        |                       |                                                                                                   |        |      |

| SIOXCLK/<br>TRCPKT[7] <sup>[2]</sup> | interface clock/Trace Packet Port                 | F11  | I/O                         | VDDE1  | SIOXCLK/<br>TRCPKT[7] | SIOXCLK/SIXEN_N/<br>SOXEN_N is indirectly showing the package internal connection to the PCF50732 |        |      |

| SIXEN_N/<br>TRCPKT[5] <sup>[2]</sup> | baseband serial data enable RX/ Trace Packet Port | G11  | I/O                         | VDDE1  | SIXEN_N/<br>TRCPKT[5] |                                                                                                   |        |      |

| SOXEN_N/<br>TRCPKT[6] <sup>[2]</sup> | baseband serial data enable TX/ Trace Packet Port | F10  | I/O                         | VDDE1  | SOXEN_N/<br>TRCPKT[6] |                                                                                                   |        |      |

| BDIO                                 | baseband serial data                              | E11  | I/O                         | VDDE1  | SIOXD                 | I/O                                                                                               | VDDD   | BDIO |

| Audio Interface                      |                                                   |      |                             |        |                       |                                                                                                   |        |      |

| DCL/<br>TRCPKT[2] <sup>[2]</sup>     | audio serial interface clock/ Trace Packet Port   | B8   | I/O                         | VDDE1  | DCL/<br>TRCPKT[2]     | DCL/FSC/ DU/DD is indirectly showing the package internal connection to the PCF50732              |        |      |

| FSC/<br>TRCPKT[1] <sup>[2]</sup>     | audio serial frame/ Trace Packet Port             | B9   | I/O                         | VDDE1  | FSC/<br>TRCPKT[1]     |                                                                                                   |        |      |

| DU/<br>TRCPKT[3] <sup>[2]</sup>      | TX audio serial / Trace Packet Port               | A9   | I/O                         | VDDE1  | DU/<br>TRCPKT[3]      |                                                                                                   |        |      |

| DD/<br>TRCPKT[4] <sup>[2]</sup>      | RX audio serial/ Trace Packet Port                | A8   | I/O                         | VDDE1  | DD/<br>TRCPKT[4]      |                                                                                                   |        |      |

| OM6357-7                           |                               |      | CONNECTED TO DEVICE SIGNALS |        |       |          |        |      |

|------------------------------------|-------------------------------|------|-----------------------------|--------|-------|----------|--------|------|

| NAME                               | DESCRIPTION                   | BALL | PCF50874-6                  |        |       | PCF50732 |        |      |

|                                    |                               |      | TYPE                        | SUPPLY | NAME  | TYPE     | SUPPLY | NAME |

| <b>I<sup>2</sup>C Bus</b>          |                               |      |                             |        |       |          |        |      |

| SCL                                | interface clock               | C2   | VO                          | VDDE2  | SCL   |          |        |      |

| SDA                                | data transfer                 | B3   | VO                          | VDDE2  | SDA   |          |        |      |

| <b>Memory Interface</b>            |                               |      |                             |        |       |          |        |      |

| HWR_N                              | memory control signals        | L5   | O                           | VDDE3  | HWR_N |          |        |      |

| HRD_N                              |                               | H5   | O                           | VDDE3  | HRD_N |          |        |      |

| CS_N0                              |                               | N4   | O                           | VDDE3  | CS0_N |          |        |      |

| CS_N1                              |                               | G5   | O                           | VDDE3  | CS1_N |          |        |      |

| CS_N2                              |                               | M5   | O                           | VDDE3  | CS2_N |          |        |      |

| CS_N3                              |                               | G3   | O                           | VDDE3  | CS3_N |          |        |      |

| HA1                                | memory address bus            | M4   | O                           | VDDE3  | HA1   |          |        |      |

| HA2                                |                               | P3   | O                           | VDDE3  | HA2   |          |        |      |

| HA3                                |                               | L4   | O                           | VDDE3  | HA3   |          |        |      |

| HA4                                |                               | N3   | O                           | VDDE3  | HA4   |          |        |      |

| HA5                                |                               | K5   | O                           | VDDE3  | HA5   |          |        |      |

| HA6                                |                               | M3   | O                           | VDDE3  | HA6   |          |        |      |

| HA7                                |                               | P2   | O                           | VDDE3  | HA7   |          |        |      |

| HA8                                |                               | N2   | O                           | VDDE3  | HA8   |          |        |      |

| HA9                                |                               | M1   | O                           | VDDE3  | HA9   |          |        |      |

| HA10                               |                               | N1   | O                           | VDDE3  | HA10  |          |        |      |

| HA11                               |                               | L2   | O                           | VDDE3  | HA11  |          |        |      |

| HA12                               |                               | L1   | O                           | VDDE3  | HA12  |          |        |      |

| HA13                               |                               | M2   | O                           | VDDE3  | HA13  |          |        |      |

| HA14                               |                               | J2   | O                           | VDDE3  | HA14  |          |        |      |

| HA15                               |                               | J5   | O                           | VDDE3  | HA15  |          |        |      |

| HA16                               |                               | K3   | O                           | VDDE3  | HA16  |          |        |      |

| HA17                               |                               | J4   | O                           | VDDE3  | HA17  |          |        |      |

| HA18                               |                               | K4   | O                           | VDDE3  | HA18  |          |        |      |

| HA19 <sup>(1)</sup>                |                               | K2   | O                           | VDDE3  | HA19  |          |        |      |

| HA20 <sup>(1)</sup>                |                               | G4   | O                           | VDDE3  | HA20  |          |        |      |

| HA21                               |                               | P5   | O                           | VDDE3  | HA21  |          |        |      |

| HA22 <sup>(1)</sup>                |                               | N6   | O                           | VDDE3  | HA22  |          |        |      |

| HA23 <sup>(1)</sup>                |                               | L6   | O                           | VDDE3  | HA23  |          |        |      |

| HA24                               |                               | J7   | O                           | VDDE3  | HA24  |          |        |      |

| HA25 <sup>(1)</sup><br>multiplexed | SC address HA25 / LDS_N / LDS | J6   | O                           | VDDE3  | HA25  |          |        |      |

| OM6357-7                           |                                     |      | CONNECTED TO DEVICE SIGNALS |        |        |          |        |      |

|------------------------------------|-------------------------------------|------|-----------------------------|--------|--------|----------|--------|------|

| NAME                               | DESCRIPTION                         | BALL | PCF50874-6                  |        |        | PCF50732 |        |      |

|                                    |                                     |      | TYPE                        | SUPPLY | NAME   | TYPE     | SUPPLY | NAME |

| HA26 <sup>(1)</sup><br>multiplexed | SC address HA0 / HA26 / UDS_N / UDS | H6   | O                           | VDDE3  | HA26   |          |        |      |

| HD0                                | memory data bus                     | H4   | IO                          | VDDE3  | HD0    |          |        |      |

| HD1                                |                                     | H3   | IO                          | VDDE3  | HD1    |          |        |      |

| HD2                                |                                     | H2   | IO                          | VDDE3  | HD2    |          |        |      |

| HD3                                |                                     | J3   | IO                          | VDDE3  | HD3    |          |        |      |

| HD4                                |                                     | E5   | IO                          | VDDE3  | HD4    |          |        |      |

| HD5                                |                                     | H1   | IO                          | VDDE3  | HD5    |          |        |      |

| HD6                                |                                     | B1   | IO                          | VDDE3  | HD6    |          |        |      |

| HD7                                |                                     | E4   | IO                          | VDDE3  | HD7    |          |        |      |

| HD8                                |                                     | F3   | IO                          | VDDE3  | HD8    |          |        |      |

| HD9                                |                                     | F2   | IO                          | VDDE3  | HD9    |          |        |      |

| HD10                               |                                     | F1   | IO                          | VDDE3  | HD10   |          |        |      |

| HD11                               |                                     | E1   | IO                          | VDDE3  | HD11   |          |        |      |

| HD12                               |                                     | D1   | IO                          | VDDE3  | HD12   |          |        |      |

| HD13                               |                                     | E3   | IO                          | VDDE3  | HD13   |          |        |      |

| HD14                               |                                     | E2   | IO                          | VDDE3  | HD14   |          |        |      |

| HD15                               |                                     | B2   | IO                          | VDDE3  | HD15   |          |        |      |

| Keyboard scanner                   |                                     |      |                             |        |        |          |        |      |

| KBIO7                              | keyboard matrix                     | L14  | IO                          | VDDE1  | KBIO7  |          |        |      |

| KBIO6                              |                                     | L12  | IO                          | VDDE1  | KBIO6  |          |        |      |

| KBIO5                              |                                     | L13  | IO                          | VDDE1  | KBIO5  |          |        |      |

| KBIO4                              |                                     | L11  | IO                          | VDDE1  | KBIO4  |          |        |      |

| KBIO3                              |                                     | J11  | IO                          | VDDE1  | KBIO3  |          |        |      |

| KBIO2                              |                                     | K13  | IO                          | VDDE1  | KBIO2  |          |        |      |

| KBIO1                              |                                     | J10  | IO                          | VDDE1  | KBIO1  |          |        |      |

| KBIO0                              |                                     | K11  | O                           | VDDE1  | KBIO0  |          |        |      |

| UART0                              |                                     |      |                             |        |        |          |        |      |

| CTS0_N                             | clear to send                       | B5   | I                           | VDDE2  | CTS0_N |          |        |      |

| RTS0_N                             | request to send                     | A5   | O                           | VDDE2  | RTS0_N |          |        |      |

| TXD0                               | transmit data                       | C5   | O                           | VDDE2  | TXD0   |          |        |      |

| RXD0                               | receive data                        | C4   | IO                          | VDDE2  | RXD0   |          |        |      |

| UART1                              |                                     |      |                             |        |        |          |        |      |

| TXD1                               | transmit data                       | A4   | O                           | VDDE2  | TXD1   |          |        |      |

| RXD1                               | receive data                        | D4   | IO                          | VDDE2  | RXD1   |          |        |      |

| SIM Interface                      |                                     |      |                             |        |        |          |        |      |

| OM6357-7                  |                                     |      | CONNECTED TO DEVICE SIGNALS |        |               |          |        |       |

|---------------------------|-------------------------------------|------|-----------------------------|--------|---------------|----------|--------|-------|

| NAME                      | DESCRIPTION                         | BALL | PCF50874-6                  |        |               | PCF50732 |        |       |

|                           |                                     |      | TYPE                        | SUPPLY | NAME          | TYPE     | SUPPLY | NAME  |

| SIMCLK                    | interface clock                     | M14  | O                           | VDDE1  | SIMCLK        |          |        |       |

| SIMIO                     | data transfer                       | M13  | IO                          | VDDE1  | SIMIO         |          |        |       |

| SIMERR                    | error removal                       | M11  | I                           | VDDE1  | SIMERR        |          |        |       |

| General Purpose I/O Port  |                                     |      |                             |        |               |          |        |       |

| GPIO10/EXT2               | general purpose signal              | K8   | IO                          | VDDE2  | GPIO10/EXT2   |          |        |       |

| GPIO9/EXT1                |                                     | N8   | IO                          | VDDE2  | GPIO9/EXT1    |          |        |       |

| GPIO8/PWM01               |                                     | P6   | IO                          | VDDE2  | GPIO8/PWM01   |          |        |       |

| GPIO7/EXT3                |                                     | N7   | IO                          | VDDE2  | GPIO7/EXT3    |          |        |       |

| GPIO6/DSP_REQ             |                                     | L9   | IO                          | VDDE2  | GPIO6/DSP_REQ |          |        |       |

| GPIO5                     |                                     | L7   | IO                          | VDDE2  | GPIO5         |          |        |       |

| GPIO4                     |                                     | P7   | IO                          | VDDE2  | GPIO4         |          |        |       |

| GPIO3/FRAME               |                                     | M9   | IO                          | VDDE2  | GPIO3/FRAME   |          |        |       |

| GPIO2                     |                                     | L8   | IO                          | VDDE2  | GPIO2         |          |        |       |

| GPIO1                     |                                     | K9   | IO                          | VDDE2  | GPIO1         |          |        |       |

| GPIO0                     |                                     | M12  | IO                          | VDDE2  | GPIO0         |          |        |       |

| Pulse Width Modulator     |                                     |      |                             |        |               |          |        |       |

| PWM1                      | pulse width modulator signal        | E6   | O                           | VDDE2  | PWM1          |          |        |       |

| PWM0                      |                                     | F4   | O                           | VDDE2  | PWM0          |          |        |       |

| JTAG and Test Access Port |                                     |      |                             |        |               |          |        |       |

| TCK                       | interface clock                     | A3   | I                           | VDDE2  | TCK           |          |        |       |

| TMS                       | test mode select                    | A2   | I                           | VDDE2  | TMS           |          |        |       |

| TDI                       | test data input                     | D2   | I                           | VDDE2  | TDI           |          |        |       |

| TDO                       | test data output                    | D3   | O                           | VDDE2  | TDO           |          |        |       |

| TRST_N                    | reset                               | A1   | I                           | VDDE2  | TRST_N        |          |        |       |

| J_SEL                     | controller select BBP DSP or BBP SC | B4   | I                           | VDDE2  | J_SEL         |          |        |       |

| Power-Down Control        |                                     |      |                             |        |               |          |        |       |

| GPON2                     | general purpose power down signal   | N9   | O                           | VDDE2  | GPON2         |          |        |       |

| GPON1                     |                                     | L10  | O                           | VDDE2  | GPON1         |          |        |       |

| AUXST                     |                                     | G10  | O                           | VDDE1  | GPON0         | I        | VDDD   | AUXST |

| IF Signals                |                                     |      |                             |        |               |          |        |       |

| OM6357-7            |                                         |      | CONNECTED TO DEVICE SIGNALS |        |      |          |            |         |

|---------------------|-----------------------------------------|------|-----------------------------|--------|------|----------|------------|---------|

| NAME                | DESCRIPTION                             | BALL | PCF50874-6                  |        |      | PCF50732 |            |         |

|                     |                                         |      | TYP<br>E                    | SUPPLY | NAME | TYP<br>E | SUPPLY     | NAME    |

| IP                  | baseband differential I signal          | J13  |                             |        |      | IO       | VDD_BB     | IP      |

| IN                  |                                         | J14  |                             |        |      | IO       | VDD_BB     | IN      |

| QP                  | baseband differential Q signal          | H13  |                             |        |      | IO       | VDD_BB     | QP      |

| QN                  |                                         | H14  |                             |        |      | IO       | VDD_BB     | QN      |

| Auxiliary Functions |                                         |      |                             |        |      |          |            |         |

| AUXADC1             | auxiliary ADC input                     | F14  |                             |        |      | I        | VDD_BB     | AUXADC1 |

| AUXADC2             |                                         | G14  |                             |        |      | I        | VDD_BB     | AUXADC2 |

| AUXADC3             |                                         | E14  |                             |        |      | I        | VDD_BB     | AUXADC3 |

| AUXADC4             |                                         | F13  |                             |        |      | I        | VDD_BB     | AUXADC4 |

| AUXDAC1             | auxiliary DAC outputs                   | E12  |                             |        |      | O        | VDD_BB     | AUXDAC1 |

| AUXDAC2             |                                         | D13  |                             |        |      | O        | VDD_BB     | AUXDAC2 |

| AUXDAC3             |                                         | D12  |                             |        |      | O        | VDD_BB     | AUXDAC3 |

| Voiceband Codec     |                                         |      |                             |        |      |          |            |         |

| MICP                | microphone differential input           | A13  |                             |        |      | I        | VDD_VB     | MICP    |

| MICN                |                                         | B13  |                             |        |      | I        | VDD_VB     | MICN    |

| AUXMICP             | auxiliary microphone differential input | B14  |                             |        |      | I        | VDD_VB     | AUXMICP |

| AUXMICN             |                                         | A14  |                             |        |      | I        | VDD_VB     | AUXMICN |

| EARN                | earphone differential output            | A11  |                             |        |      | O        | VDD_VB OUT | EARN    |

| EARP                |                                         | B10  |                             |        |      | O        | VDD_VB OUT | EARP    |

| AUXSP               | auxiliary speaker output                | A10  |                             |        |      | O        | VDD_VB OUT | AUXSP   |

| BUZ                 | buzzer output                           | B11  |                             |        |      | O        | VDD_VB OUT | BUZ     |

Table 3 LBGA183 Top view of MCP

|          | 1      | 2    | 3     | 4     | 5      | 6      | 7                      | 8                 | 9                 | 10                         | 11                         | 12                         | 13                          | 14                          |             |    |

|----------|--------|------|-------|-------|--------|--------|------------------------|-------------------|-------------------|----------------------------|----------------------------|----------------------------|-----------------------------|-----------------------------|-------------|----|

| <b>A</b> | TRST_N | TMS  | TCK   | TXD1  | RTS0_N | RFSIG1 | RFSIG4                 | DD/TRC<br>PKT[4]  | DU/TRC<br>PKT[3]  | AUXSP                      | EARN                       | VSS_VB                     | MICP                        | AUX<br>MICN                 |             |    |

| <b>B</b> | HD6    | HD15 | SDA   | J_SEL | CTS0_N | RFSIG3 | RFSIG6                 | DCL/TRC<br>PKT[2] | FSC/TRC<br>PKT[1] | EARP                       | BLZ                        | VDD_VB                     | MICN                        | AUX<br>MICP                 |             |    |

| <b>C</b> | VDD2   | SCL  | VSS   | RXDO  | TXD0   | RFSIG7 | RFSIG5/<br>TRCSYN<br>C | VDD1              | VDD_D             | RESETN                     | VSS_VBOUT                  | VDD_VBOUT                  | VSS_REF                     | VREF                        |             |    |

| <b>D</b> | HD12   | TDI  | TDO   | RXD1  | RFSIG0 | RFSIG2 | RFSIG10                | CDI               | CEN               | MCLK                       | VSSD                       | AUX<br>DAC3                | AUX<br>DAC2                 | VDD_REF                     |             |    |

| <b>E</b> | HD11   | HD14 | HD13  | HD7   | HD4    | PWM1   | RFSIG8                 | VSS               | CDO               | CCLK                       | BDIO                       | AUX<br>DAC1                | VSS_BB                      | AUX<br>ADC3                 |             |    |

| <b>F</b> | HD10   | HD9  | HD8   | PWM0  | VDDC   |        |                        |                   |                   |                            | SIOEN_N/<br>TRCPKT<br>T[6] | SIOXCLK/<br>TRCPKT<br>T[7] | VDD_BB                      | AUX<br>ADC4                 | AUX<br>ADC1 |    |

| <b>G</b> | VSS    | VDD3 | CS3_N | HA20  | CS1_N  |        |                        |                   |                   |                            | AUXST                      | SIXEN_N/<br>TRCPKT<br>[5]  | RFSIG12/<br>PIPESTA<br>T[2] | VSS                         | AUX<br>ADC2 |    |

| <b>H</b> | HD5    | HD2  | HD1   | HD0   | HRD_N  | HA26   |                        |                   |                   |                            |                            | RST_N                      | VDD1                        | RFSIG11/<br>PIPESTA<br>T[1] | QP          | QN |

| <b>J</b> | VSS    | HA14 | HD3   | HA17  | HA15   | HA25   | HA24                   | KBIO1             | KBIO3             | RFE_N0/<br>TRCPKT<br>[0]   | IP                         | IN                         |                             |                             |             |    |

| <b>K</b> | VSS    | HA19 | HA16  | HA18  | HA5    | VDDC   | VSS                    | GPIO10            | GPIO1             | RFSIG9/<br>PIPESTA<br>T[0] | KBIO0                      | RFE_N2                     | KBIO2                       | AUXON_N                     |             |    |

| <b>L</b> | HA12   | HA11 | VDD3  | HA3   | HWR_N  | HA23   | GPIO5                  | GPIO2             | GPIO6             | GPON1                      | KBIO4                      | KBIO6                      | KBIO5                       | KBIO7                       |             |    |

| <b>M</b> | HA9    | HA13 | HA6   | HA1   | CS2_N  | VDD3   | VSS                    | VDDC              | GPIO3             | RST0_N                     | SIMERR                     | GPIO0                      | SIMIO                       | SIMCLK                      |             |    |

| <b>N</b> | HA10   | HA8  | HA4   | CS0_N | VSS    | HA22   | GPIO7                  | GPIO9             | GPON2             | VSS                        | VSS                        | VDD1                       | VDDC                        | VSS                         |             |    |

| <b>P</b> | VSS    | HA7  | HA2   | VDD3  | HA21   | GPIO8  | GPIO4                  | VDD2              | VDD1              | AVSS                       | CKI                        | AVDD                       | CK1321                      | CK320_TEST/TR<br>CCLK       |             |    |

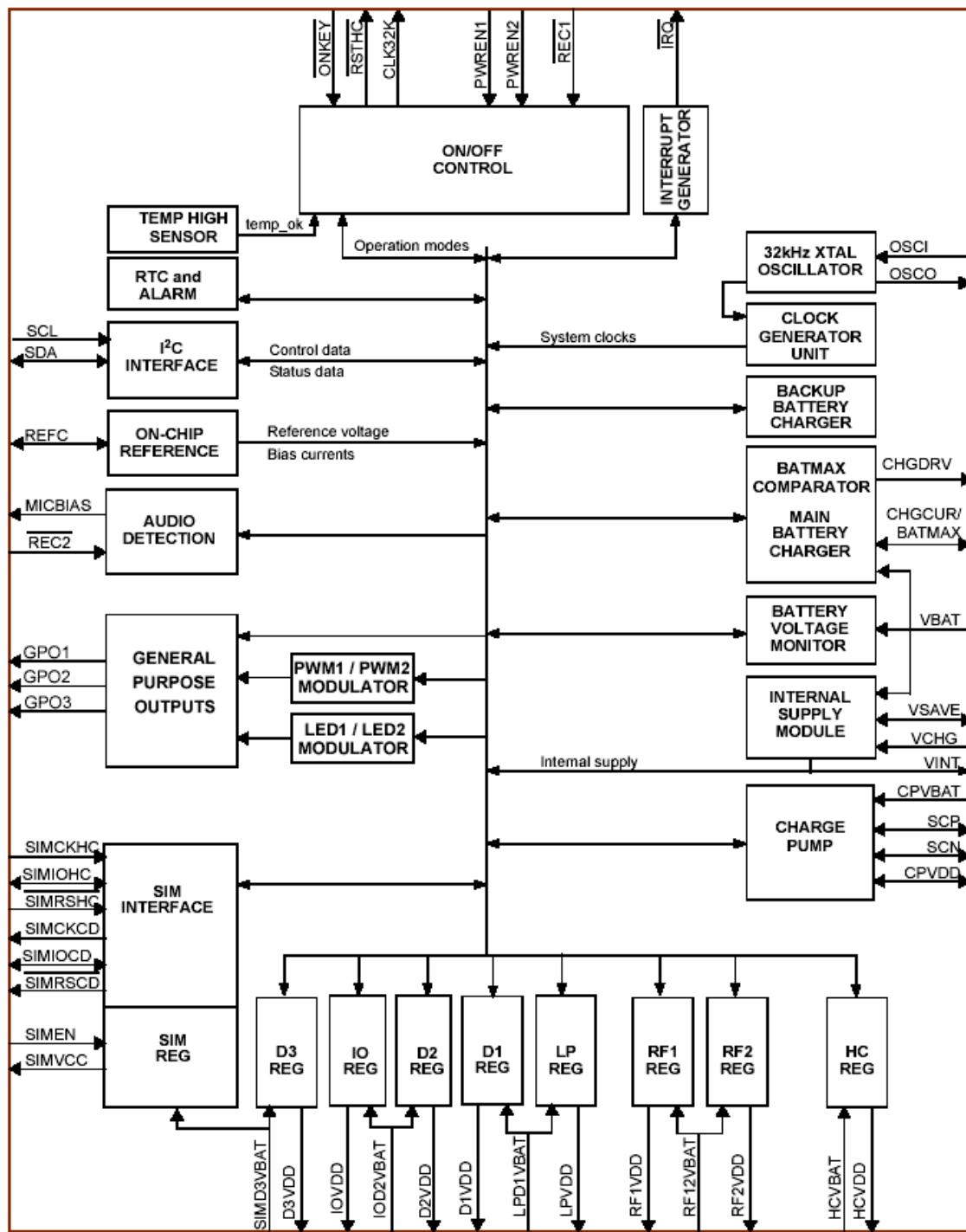

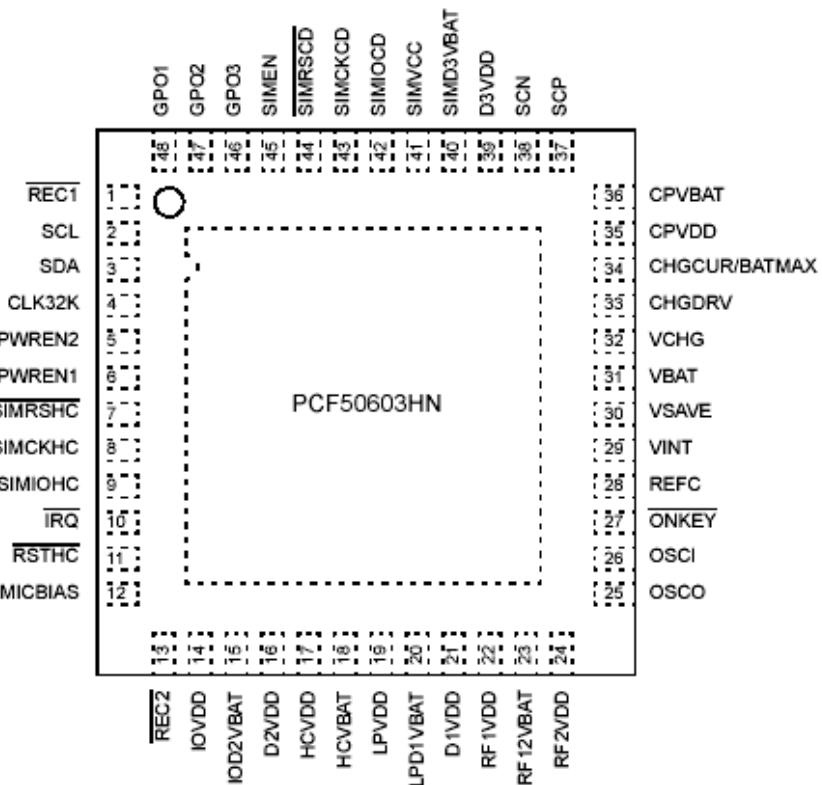

## 6.2 PMU (PCF50603)

**7400: POWE-SIM-MANAGEMENT**

The PCF50603 is a highly integrated solution for power supply generation, battery management including charging and a Subscriber Identity Module (SIM) card interface including supply generation. The device is controlled by a host controller via a 400 kHz I<sup>2</sup>C serial interface.

**2.1 System control**

- Serial 400 kHz I<sup>2</sup>C interface to transfer the control data between the PCF50603 and the host controller.

- On/Off Control module (hereafter OOC) to control the power ramp-up and ramp-down sequences for the handset. Furthermore it determines the supported system operating states: NOPOWER, SAVE, STANDBY, ACTIVE to realize minimum power consumption in all states.

- Internal current controlled oscillator (hereafter CCO) generates the internal high clock frequency. The generated frequency is typically 3.6 MHz.

- An accurate 32.768 kHz oscillator (hereafter OSC32). This oscillator can be used to supply the 32 kHz clock domains in the system, to improve the accuracy of the internal clock, and to reduce the power consumption of the PCF50603.

- Interrupt controller (hereafter INT) that generates the interrupt request for the host controller. All interrupt sources can be masked.

- The Real Time Clock module (hereafter RTC) uses the 32 kHz clock to provide time reference and alarm functions with wake up control for the handset.

- One accessory recognition pin with debounce filters and capability to start up the system (hereafter REC1).

- One accessory detection comparator input with programmable threshold levels that issues an interrupt when an accessory is connected (hereafter REC2).

- Two pulse-width modulators (hereafter PWM1 and PWM2): generating an output voltage with programmable duty cycle and frequency.

- Two LED modulators (hereafter LED1 and LED2) capable of generating 8 different blinking patterns with 8 different repetition periods.

- Three General Purpose Outputs (hereafter GPO), programmable through the serial interface. The GPO are open drain NMOS outputs, capable of handling the full battery voltage range and high sink currents.

**Tuning Up procedure & Operational Manual**

The GPO's can be programmed to be continuously active low or tristate. In addition the GPO outputs can be controlled by the LED or PWM modulators.

- Watchdog timer that can be activated by software.

## 2.2 Supply voltage generation

- The power supplies have programmable activity modes (OFF, ECO, ON). In the ACTIVE state, the operation modes can be selected by the two external pins PWREN1 and PWREN2.

- One charge pump with programmable output voltage for the supply of white or blue LED's (hereafter CP).

- Two 100 mA LDO voltage regulators with fixed output voltage (mask programmable) for RF supplies. Regulators are optimized for low noise, high power supply rejection, and excellent load regulation (hereafter RF1REG, RF2REG).

- Two 150 mA LDO voltage regulators that are optimized for small external capacitors (hereafter D1REG, D2REG). D1REG provides a programmable output voltage, D2REG provides a fixed output voltage (mask programmable).

- One 150 mA LDO voltage regulator dedicated for the supply of the IO pads. This regulator has a fixed output voltage (mask programmable) and is optimized for a small external capacitor (hereafter IOREG).

- One 100 mA LDO voltage regulator with fixed output voltage (mask programmable). In its ECO mode (low power operation mode), it can be used to permanently supply parts in the system in all activity states (hereafter LPREG).

- One 100 mA LDO voltage regulator with programmable output voltage. This regulator is optimized for a small external capacitor (hereafter D3REG).

- One 250 mA LDO voltage regulator with programmable output voltage. This high current regulator is optimized for applications like hands-free audio (hereafter HCREG).

- D1REG, D2REG, D3REG, IOREG, and LPREG support a low power operation mode (hereafter ECO mode). In this mode, the output power is limited to 1 mA and the internal power consumption is reduced significantly.

- Microphone bias voltage generator with low noise, and high power supply rejection (MBGEN).

- The temperature high sensor (hereafter TS) provides thermal protection for the whole chip.

- Enhanced ESD protection on all pins that connect to the main battery pack.

## 2.3 Battery management

- The PCF50603 operates from a 3 cell NiCd/NiMH or a 1 cell Lilon battery pack.

- Battery voltage monitor (hereafter BVM) to detect a too low main battery voltage with programmable threshold levels. A low battery condition is reported via the interrupt mechanism.

- Charger control: option between two different charger control functions, depending on the configuration:

- ◆ Configuration CCCV: Constant Current Constant Voltage (hereafter CCCV) linear charger control supporting Lilon as well as NiCd/NiMH battery types for a wide range of battery capacities.

- ◆ Configuration BATMAX: comparator that compares the battery voltage against a programmable threshold voltage. This function can be activated by software and is used to detect the end-of-charge.

- The PCF50603 supports the use of a backup battery that powers the PCF50603 at empty main battery situations. The backup battery is used to supply the real-time clock, the internal state, and the LPVDD supply in its ECO mode. Goldcaps, Li and Lilon cells are supported.

- Includes a backup battery charger (hereafter BBC). A rechargeable backup battery or backup capacitor can be charged from the main battery. For charging, a programmable constant voltage mode is supported.

## 2.4 Subscriber Identity Module card interface

- The Subscriber Identity Module card interface (hereafter SIMI) supports two different modes that can be selected:

- ◆ Transparent interface including an arbiter and signal level translators.

- ◆ SIM card interface with integrated sequencer, arbiter and signal level translators. The sequencer supports and controls card activation and de-activation, warm reset, and controlled clock stop for power down modes.

- Dedicated SIM supply (hereafter SIMREG) that supports 3.0 V and 1.8 V cards. Including a power saving ECO mode for the power down mode of the SIM card.

- Enhanced ESD protection on all pins that connect to the SIM card contact pins.

Fig 1. Functional Diagram PCF50603

## Tuning Up procedure & Operational Manual

**Table 6: Pin description ...continued**

| Symbol                                                 | HVQFN48<br>Pin no | Supply  | Description/Remarks                                                                                                                                         |

|--------------------------------------------------------|-------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK32K                                                 | 4                 | IOVDD   | 32.768 kHz digital clock output; note that this output is only available when the system is in ACTIVE state and IOVDD is on. <sup>[1]</sup>                 |

| PWREN1                                                 | 6                 | IOVDD   | Control signal selects in combination with PWREN2 the ON, OFF or ECO mode of the linear regulators. <sup>[1]</sup>                                          |

| PWREN2                                                 | 5                 | IOVDD   | Control signal selects in combination with PWREN1 the ON, OFF or ECO mode of the linear regulators. <sup>[1]</sup>                                          |

| IRQ                                                    | 10                | IOVDD   | Interrupt request to host controller; this low active signal is realized as an open drain output with an internal pull-up resistor to IOVDD. <sup>[1]</sup> |

| REC1                                                   | 1                 | VINT    | Accessory recognition input with debounce filter. Input with internal pull-up resistor to VINT. <sup>[1]</sup>                                              |

| REC2                                                   | 13                | MICBIAS | Accessory recognition input with debounce filter and programmable threshold. <sup>[1]</sup>                                                                 |

| <b>Charge Pump</b>                                     |                   |         |                                                                                                                                                             |

| CPVBAT                                                 | 36                | n.a.    | Input for charge pump <sup>[1]</sup>                                                                                                                        |

| SCP                                                    | 37                | n.a.    | Switching capacitor positive side <sup>[1]</sup>                                                                                                            |

| SCN                                                    | 38                | n.a.    | Switching capacitor negative side <sup>[1]</sup>                                                                                                            |

| CPVDD                                                  | 35                | n.a.    | Charge pump output voltage <sup>[1]</sup>                                                                                                                   |

| <b>Linear regulators</b>                               |                   |         |                                                                                                                                                             |

| RF12VBAT                                               | 23                | n.a.    | Shared input for RF1 and RF2 linear regulators <sup>[1]</sup>                                                                                               |

| RF1VDD                                                 | 22                | n.a.    | RF1 linear regulator output voltage <sup>[1]</sup>                                                                                                          |

| RF2VDD                                                 | 24                | n.a.    | RF2 linear regulator output voltage <sup>[1]</sup>                                                                                                          |

| IOD2VBAT                                               | 15                | n.a.    | Shared input for IO and D2 linear regulator <sup>[1]</sup>                                                                                                  |

| IOVDD                                                  | 14                | n.a.    | IO linear regulator output voltage <sup>[1]</sup>                                                                                                           |

| D2VDD                                                  | 16                | n.a.    | Digital 2 linear regulator output voltage <sup>[1]</sup>                                                                                                    |

| SIMD3VBAT                                              | 40                | n.a.    | Shared input for D3 and SIM linear regulators <sup>[1]</sup>                                                                                                |

| D3VDD                                                  | 39                | n.a.    | Digital 3 linear regulator output voltage <sup>[1]</sup>                                                                                                    |

| LPD1VBAT                                               | 20                | n.a.    | Shared input for D1 and LP linear regulators <sup>[1]</sup>                                                                                                 |

| LPVDD                                                  | 19                | n.a.    | Low-power linear regulator output voltage <sup>[1]</sup>                                                                                                    |

| D1VDD                                                  | 21                | n.a.    | Digital 1 linear regulator output voltage <sup>[1]</sup>                                                                                                    |

| HCVBAT                                                 | 18                | n.a.    | Input for high current linear regulator <sup>[1]</sup>                                                                                                      |

| HCVDD                                                  | 17                | n.a.    | High current linear regulator output voltage <sup>[1]</sup>                                                                                                 |

| <b>32.768 kHz oscillator</b>                           |                   |         |                                                                                                                                                             |

| OSCI                                                   | 26                | VINT    | 32.768 kHz oscillator input <sup>[1]</sup>                                                                                                                  |

| OSCO                                                   | 25                | VINT    | 32.768 kHz oscillator output <sup>[1]</sup>                                                                                                                 |

| <b>Internal supply</b>                                 |                   |         |                                                                                                                                                             |

| VBAT                                                   | 31                | n.a.    | Main battery connection <sup>[1]</sup>                                                                                                                      |

| VSAVE                                                  | 30                | n.a.    | Backup battery connection <sup>[1]</sup>                                                                                                                    |

| VCHG                                                   | 32                | n.a.    | Charger connection <sup>[2]</sup>                                                                                                                           |

| VINT                                                   | 29                | n.a.    | Internal supply voltage output <sup>[1]</sup>                                                                                                               |

| <b>On-chip reference and microphone bias generator</b> |                   |         |                                                                                                                                                             |

**Table 6: Pin description ...continued**

| Symbol                                        | HVQFN48<br>Pin no | Supply | Description/Remarks                                                                          |

|-----------------------------------------------|-------------------|--------|----------------------------------------------------------------------------------------------|

| REFC                                          | 28                | n.a.   | Reference voltage bypass capacitor connection <sup>[1]</sup>                                 |

| MICBIAS                                       | 12                | n.a.   | Microphone bias voltage output <sup>[1]</sup>                                                |

| <b>I<sup>2</sup>C interface</b>               |                   |        |                                                                                              |

| SCL                                           | 2                 | IOVDD  | I <sup>2</sup> C clock <sup>[1]</sup>                                                        |

| SDA                                           | 3                 | IOVDD  | I <sup>2</sup> C data <sup>[1]</sup>                                                         |