# 802.11g Wireless LAN SiP Module (WM-BG-MR -01)

# PRODUCT SPECIFICATION of 802.11g WM-BG-MR -01 B2B Wireless Lan +BT Combo Module

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

#### Introduction

The 802.11 Wireless SiP module WMBG-MR-01 which refers as "SiP-g combo module" is a small size module that provides full function of 802.11g/b and Bluetooth class 2 on a tiny module via 60 pins board to board connector.

This multi- functionality and board to board physical interface provides 16 bit PC Card /CF+ bus interface for WiFi and UART for Bluetooth.

The small size & low profile physical design make it easier for system design to enable high performance wireless connectivity without space constrain. The low power consumption (Sleep mode 1 mA) and excellent radio performance make it the best solution for OEM customers who require embedded 802.11g Wi-Fi + Bluetooth featuress, such as, Wireless PDA, Scanner Smart phone, Media player slim type Notebook, barcode ,mini-Printer, VoIP phone etc.

For 802.11g feature, Marvell "Libertas" chipset solution is adopted and CSR BlueCore 03-ROMfor Bluetooth. The Radio architecture & high integration MAC/BB chip provide excellent sensitivity with rich system performance. Two antenna connectors provide antenna connectivity for each function.

WM-BG-AG-01 provides outstanding BT WiFi coexistence solution through internal 2 wires , hardware interface to optimized connection with CSR Bluetooth solution even without good antenna isolation between BT & WiFi module.

In addition to WEP 64/128, WPA and TKIP, AES is supported to provide the latest security requirement on your network.

For the software and driver development, USI provides extensive technical document and reference software code for the system integration under the agreement of Marvell International Ltd.

#### **Features**

- Lead Free design which supporting Green design requirement.

- 2 wires, hardware signaling BT WiFi coexistence supported.

- Small size suitable for low volume system integration.PCM audio interface supported.

- Low power consumption & excellent power management performance, extend battery life.

- 2.412-2.484 GHz two SKUs for worldwide market.

- Easy for integration into mobile and handheld device with flexible system configuration and antenna design.

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

#### 1. EXECUTIVE SUMMARY

The WM-BG-MR-01 module - is one of the product families in USI's product offering, targeting for system integration requiring a smaller form factor. It also provides the standard migration to high data rate to USI's current SIP customers. The WM-BG-MR-01 module providing B to B type connector is provided as option for customers, who want to have Board to board type assembly.

This document outlines the product requirements for a "system in Package" 802.11g/(b) combo module – here after referred as WM-BG-MR-01 Module.

This product is targeted for first shipments by end of **2Q 2005** and is designated for use in embedded applications mainly in the mobile device, which required, small size and high data rate wireless connectivity. The application such as, Wireless PDA, slim type Notebook, Media Adapter, Barcode scanner, mini-Printer, VoIP phone, Data storage device could be the potential application for wireless WM-BG-MR-01.

#### 2. DELIVERABLES

The following products and software will be part of the product.

- WM-BG-MR-01 Module with packaging

- Evaluation kits, including application (CF, PCMCIA Adapter card, RF cable with SMA connector, antenna),

- Software utility which supporting customer for integration, performance test, and homologation. Capable of testing, loading (firmware) and configuring (MAC, CIS) for the WM-BG-MR-01 module.

- Unit Test / Qualification report

- Product Specifications.

- Agency certification pre-test report base on adapter boards

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

#### 3. REFERENCE DOCUMENTS

| C.I.S.P.R.<br>Pub. 22   | "Limits and methods of measurement of radio interference characteristics of information technology equipment." International Special Committee on Radio Interference (C.I.S.P.R.), Third Edition, 1997.                                                                                   |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CB Bulletin<br>No. 96A  | "Adherence to IEC Standards: "Requirements for IEC 950, 2 <sup>nd</sup> Edition and Amendments 1 (1991), 2(1993), 3 (1995) and 4(1996). Product Categories: Meas, Med, Off, Tron." IEC System for Conformity Testing to Standards for Safety of Electrical Equipment (IECEE), April 2000. |

| CFR 47,<br>Part 15-B    | "Unintentional Radiators". Title 47 of the Code of Federal Regulations, Part 15, FCC Rules, Radio Frequency Devices, Subpart B.                                                                                                                                                           |

| CFR 47,<br>Part 15-C    | "Intentional Radiators". Title 47 of the Code of Federal Regulations, Part 15, FCC Rules, Subpart C. URL: <a href="http://www.access.gpo.gov/nara/cfr/waisidx/98/47cfr15/98.html">http://www.access.gpo.gov/nara/cfr/waisidx/98/47cfr15/98.html</a>                                       |

| CSA C22.2<br>No. 950-95 | "Safety of Information Technology Equipment including Electrical Business Equipment, Third Edition." Canadian Standards Association, 1995, including revised pages through July 1997.                                                                                                     |

| EN 60 950               | "Safety of Information Technology Equipment Including Electrical Business Equipment." European Committee for Electrotechnical Standardization (CENELEC), 1996, (IEC 950, Second Edition, including Amendment 1, 2, 3 and 4).                                                              |

| IEC 950                 | "Safety of Information Technology Equipment Including Electrical Business Equipment." European Committee for Electrotechnical Standardization, Intentional Electrotechnical Commission. 1991, Second Edition, including Amendments 1, 2, 3, and 4.                                        |

| IEEE 802.11             | "Wireless LAN Medium Access Control (MAC) And Physical Layer (PHY) Specifications." Institute of Electrical and Electronics Engineers. 1999.                                                                                                                                              |

4. COMPATIBILITY AND INTEROPERABILITY

#### 4.1. WI-FI LOGO

The product needs to be verified with Wi-Fi certification base on CF form factor to prove the hardware compatibility. For the other specific application, Wi-Fi certification is dependent on the capability and application of the host system.

#### 4.2. WHQL COMPLIANCE

Not required for WM-BG-MR-01 module

#### 5. CONFIGURABILITY

No user configuration needed. The CIS and MAC Address will be loaded during production of the WM-BG-MR-01 module.

#### 6. SECURITY

The WM-BG-MR-01 module supports WEP64/128,WPA, AES-CCM which including TKIP (full version TKIP SSN WPA). Refer to Marvell Libertas solution.

#### 7. OPERATING SYSTEM COMPATIBILITY

Drivers are supported for the following OS:

- Windows CE 3.0 /.NET , Win CE 5.0 (2005)

- Linux.

- Pocket PC 2003.2004

#### 8. LEGAL, REGULATORY & OTHER TECHNICAL CONSTRAINTS

The WM-BG-MR-01 module is pre-tested to ensure that all requirements met as set forth in the following sections.

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

Final certification (module certification) requires the antenna of targeted system with a lead-time of 6 weeks. The product deliverable shall be a pre-tested WM-BG-MR-01 module. No module level certification on WM-BG-MR-01 module.

#### 9.1. EMC

The module will be pre-tested to ensure that we can certify the product in the following countries when final certification will be performed on products and or platforms.

- US. FCC CFR47 Part 15-B, Class B

- Canada. CSA C22.2, Class B

- Europe. 89/336/EEC, EMC Directive, including CE Mark

- ETS300 826, EMC standard for 2.4GHz wideband transmission systems

- EN55022, Class B (Emissions)

EN50082-1 (Immunity)

- EN61000-3-2 (Harmonic AC current emissions)

- Japan. VCCI Standard, Class 2 (Emissions)

- Korea (MIC)

#### 9.2. PRODUCT SAFETY SPECIFICATION

The WM-BG-MR-01 module is tested and pass successfully the following criteria; The testing is to assure the quality of safety requirement on module. Final certification will be conducted on system level.

- UL1950 /CSA C22.2.950

- EN60 950 (IEC 950)

- CB scheme certification from National certification body as listed in CB bulletin No. 96A.

#### •

#### 9.3. COMPONENT SPECIFICATION

All components used in this device meet the following component approval requirements.

<u>PRINTED WIRING BOARDS</u>: The printed wiring boards shall be Underwriters Laboratories Inc. "Recognized Component" (ZPMV2) under the category for Printed Wiring Boards, and shall be flammability rated 94V-1 or less flammable. The board material shall be rated 130°C minimum.

<u>CONNECTORS</u>: Any connectors, if used, shall be Underwriters Laboratories, Inc. "Recognized" (ECBT2/RTRT2) in accordance with the requirements in the UL Standard for Safety, UL 498. Any polymeric connector housing shall be molded of plastics rated UL 94V-2 or less flammable when tested to UL 94.

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

<u>WIRING</u>: Any wiring material, if used, shall be UL Recognized Component Appliance Wiring Material (AVLV2). Wire shall be minimum rated 30V, 105°C.

<u>PLASTIC PARTS</u> - Any plastic parts used shall be molded of plastics that are UL "Recognized" (QFMZ2) and rated UL 94V-2 or less flammable when tested to UL 94.

<u>"PB FREE"</u> - The entire component Suppliers has to support Green requirement base on USI's policy. All of the components which including process and materials has to be Lead Free.

#### 9.4. RADIO REQUIREMENTS AND AP PROVALS

The WM-BG-MR-01 module is tested with adapter card to comply with following standard. The testing is to assure the performance of regulatory requirement on module. Final certification will be conducted on system level.

• US/CAN: FCC CFR47 Part 15.247

Japan: TELECKorea: MIC

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

#### 9.5. PRODUCT MARKING

The Module is marked by laser marking which containing the following information:

Description: WM-BG-XX-XX Serial number: yyllwkxxxx

Revision: format to follow USI revision level in PDM System

For the serial number the following format will be followed:

yy =last two digits of current year

II = Assembly Location:

UT = USI Taiwan UM = USI Mexico UC = USI China

wk = current week (week period = starting on Monday)

xxxx = consecutive number, starting at 0000 at beginning of each week.

#### 9.6. ENVIRONMENTALLY SAFE MATERIAL RESTRICTIONS

The use of polychlorinated biphenyls (PCB's) is prohibited (specifically) as dielectric in capacitors or transformers.

Electrolytic capacitors shall not be composed of any quaternary salt ammonium and/or gamma-butyrolactone (i.e. no el caps allowed).

No CFC's (chlorofluorocarbons) shall be used anywhere in the manufacture of this product.

The use of tantalum capacitors should be minimized in any product of the product family [including the power-supply]. Where the use of tantalum caps cannot be avoided, provisions must be made in the manufacturing process to prevent reverse polarization.

The WMBG-MR-01 module hardware design should take the safety of operation into consideration and prevent the potential risk on Labor safety for manufacturing process.

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

#### 10.1. HOST INTERFACE

The host interface will be compatible with CompactFlash (PCMCIA) standard, 16 bit I/O bus. Signals which are not used won't be routed to the physical interface (connector). The host interface of Combo SiP Bluetooth portion is compliant with UART interface, the default baud rate setting is 115.2kbps and the optional range is from 9.6kbps to 921.6kbps.

#### On Board connector

Molex 53794-0608 or 55560-0607

A

Datasheet\_Molex\_53 794-0608.pdf

Datasheet\_Molex\_55 560-0607.pdf

[Socket, 60 pins, with positioning protection, stack height which is able to support 1.5 mm]

#### **Host System:**

#### **Host System Connector**

Molex 54722-0607 [Header, 60 pins, with positioning protection, stack height 1.5mm]

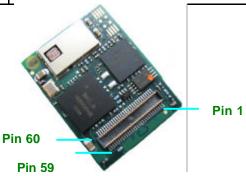

#### Pin definition

[ ...] means optional function of the pin.

${\bf PD}$  : Signal pull down internally in the chip by 50K ohm  $\,$  while initialization.  ${\bf PU}$  : Signal pull up internally in the chip by 100K ohm while initialization.

**5VT**: 5 Volt tolerance pin

xxx\_B : Signal pins end with \_B are "active high"

| Pin             | Definition    | Draft Description Type |                                                                                                | Type            |

|-----------------|---------------|------------------------|------------------------------------------------------------------------------------------------|-----------------|

| Number          |               |                        |                                                                                                |                 |

| WM-BG-<br>MR-01 | CF+ interface |                        |                                                                                                |                 |

| 1               | GND           | GND                    | GND                                                                                            |                 |

| 2               | D03           | HD3                    | Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE | O, PD, 5VT, 4mA |

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

|    |       |          | bus. HD[15:0] are used to access the MODULE                                                      | Databus          |

|----|-------|----------|--------------------------------------------------------------------------------------------------|------------------|

|    |       |          | MAC Host Interface register                                                                      | Databas          |

| 3  | D04   | HD4      | Data Input/Output line constitute a bi-directional                                               | O, PD, 5VT, 4mA  |

|    |       |          | bus. HD[15:0] are used to access the MODULE                                                      | Databus          |

|    |       |          | MAC Host Interface register                                                                      |                  |

| 4  | D05   | HD5      | Data Input/Output line constitute a bi-directional                                               | IO, PD, 5VT, 4mA |

|    |       |          | bus. HD[15:0] are used to access the MODULE                                                      | Databus          |

|    |       |          | MAC Host Interface register                                                                      |                  |

| 5  | D06   | HD6      | Data Input/Output line constitute a bi-directional                                               | IO, PD, 5VT, 4mA |

|    |       |          | bus. HD[15:0] are used to access the MODULE                                                      |                  |

|    |       |          | MAC Host Interface register                                                                      |                  |

| 6  | D07   | HD7      | Data Input/Output line constitute a bi-directional                                               | IO, PD, 5VT, 4mA |

|    |       |          | bus. HD[15:0] are used to access the MODULE                                                      |                  |

|    |       |          | MAC Host Interface register                                                                      |                  |

| 7  | -CE_1 | HCE1_B   | Card Enable1 is driven by the host system and is                                                 | Input, PU, 5VT   |

|    |       |          | used as select strobe in both I/O and memory                                                     |                  |

|    |       |          | mode. Enables even numbered address bytes.                                                       |                  |

| 8  | A10   | A10      | ADDRESS BUS lines driven by the host system                                                      | Input, PD,5VT    |

|    |       |          | which enables addressing of 0.5K address range                                                   |                  |

|    |       |          | within MAC. This address range is mainly used for                                                |                  |

|    |       |          | accessing the CIS in Memory Mode. Signal HA0 is                                                  |                  |

|    |       |          | not used in word access mode. The pin is open in                                                 |                  |

|    |       | LIOE D   | B2B module.                                                                                      | L COLLEGE        |

| 9  | -OE   | HOE_B    | OUTPUT ENABLE is driven by the host during a                                                     | Input, PU,5VT    |

| 40 | 4.00  | 1140     | memory Read Access.                                                                              |                  |

| 10 | A09   | HA9      | ADDRESS BUS lines driven by the host system                                                      | Input, PD,5VT    |

|    |       |          | which enables addressing of 0.5K address range within MAC. This address range is mainly used for |                  |

|    |       |          | accessing the CIS in Memory Mode. Signal HAO is                                                  |                  |

|    |       |          | not used in word access mode.                                                                    |                  |

| 11 | A08   | HA8      | ADDRESS BUS lines driven by the host system                                                      | Input, PD,5VT    |

|    | 7.00  | 1 11 10  | which enables addressing of 0.5K address range                                                   | put, 1 5,0 v 1   |

|    |       |          | within MAC. This address range is mainly used for                                                |                  |

|    |       |          | accessing the CIS in Memory Mode. Signal HA0 is                                                  |                  |

|    |       |          | not used in word access mode.                                                                    |                  |

| 12 | A07   | HA7      | ADDRESS BUS lines driven by the host system                                                      | Input, PD,5VT    |

|    |       |          | which enables addressing of 0.5K address range                                                   | ' ' '            |

|    |       |          | within MAC. This address range is mainly used for                                                |                  |

|    |       |          | accessing the CIS in Memory Mode. Signal HA0 is                                                  |                  |

|    |       |          | not used in word access mode.                                                                    |                  |

| 13 | VCC   | VCC_WLAN | Power, 3.3V_WLAN                                                                                 | Input            |

| 14 | A06   | HA6      | ADDRESS BUS lines driven by the host system                                                      | Input, PD, 5VT   |

|    |       |          | which enables addressing of 0.5K address range                                                   |                  |

|    |       |          | within MAC. This address range is mainly used for                                                |                  |

|    |       |          | accessing the CIS in Memory Mode. Signal HA0 is                                                  |                  |

|    |       |          | not used in word access mode.                                                                    |                  |

| 15 | A05   | HA5      | ADDRESS BUS lines driven by the host system                                                      | Input, PD, 5VT   |

|    |       |          | which enables addressing of 0.5K address range                                                   |                  |

|    |       |          | within MAC. This address range is mainly used for                                                |                  |

|    |       |          | accessing the CIS in Memory Mode. Signal HA0 is                                                  |                  |

|    |       |          | not used in word access mode.                                                                    |                  |

| 16 | A04   | HA4      | ADDRESS BUS lines driven by the host system                                                      | Input, PD, 5VT   |

|    |       |          | which enables addressing of 0.5K address range                                                   |                  |

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

|    |         |          | within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is                                                                                                                          |                  |

|----|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|    |         |          | not used in word access mode.                                                                                                                                                                                              |                  |

| 17 | A03     | HA3      | ADDRESS BUS lines driven by the host system                                                                                                                                                                                | Input, PD, 5VT   |

|    | 7.00    |          | which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode.                                             | mpat, 1 2, 0 1 1 |

| 18 | A02     | HA2      | ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. | Input, PD, 5VT   |

| 19 | A01     | HA1      | ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. | Input, PD, 5VT   |

| 20 | A00     | HA0      | ADDRESS BUS lines driven by the host system which enables addressing of 0.5K address range within MAC. This address range is mainly used for accessing the CIS in Memory Mode. Signal HA0 is not used in word access mode. | Input, PD, 5VT   |

| 21 | D00     | HD0      | Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register                                                                                                 | IO, PD, 5VT, 4mA |

| 22 | D01     | HD1      | Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register                                                                                                 | IO, PD, 5VT, 4mA |

| 23 | D02     | HD2      | Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register                                                                                                 | IO, PD, 5VT, 4mA |

| 24 | -IOIS16 | IOIS16_B | Output signal to indicate 16 bit IO operation. This signal is connected to ground at module side to indicate 16 bit IO                                                                                                     | GND              |

| 25 | -CD2    | CD2      | Normal operation, this pin is functionally for card detection.                                                                                                                                                             | Out, 6mA, 5VT.   |

| 26 | N/A     | TXD_B    | UART CMOS output data line                                                                                                                                                                                                 | Output,WPU, 1µA  |

| 27 | N/A     | RTS_B    | UART CMOS output signal, request to sent                                                                                                                                                                                   | Output ,WPU, 1µA |

| 28 | N/A     | PCM_In   | Reserved for BT portion , keep its open on host side if no use.                                                                                                                                                            |                  |

| 29 | N/A     | VCC_WLAN | Power_WLAN                                                                                                                                                                                                                 | Input            |

| 30 | GND     | GND      |                                                                                                                                                                                                                            |                  |

| 31 | GND     | GND      |                                                                                                                                                                                                                            |                  |

| 32 | D10     | HD10     | Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register                                                                                                 | IO, PD, 5VT, 4mA |

| 33 | D09     | HD9      | Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register                                                                                                 | IO, PD, 5VT, 4mA |

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

| 34 | D08     | HD8                                                                                                                             | Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE                                                                                                                             | IO, PD, 5VT, 4mA |

|----|---------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 35 | -STSCHG | HSTSCHG_B                                                                                                                       | MAC Host Interface register  STATUS CHANGE indication to the host. This signal gets active when one of the bits in the PRR or CSR registers are set                                                                        | Output, 4mA      |

| 36 | -SPKR   | PCM_Sync                                                                                                                        | Reserved for BT portion , keep its open on host side if no use.                                                                                                                                                            |                  |

| 37 | -REG    | HREG_B                                                                                                                          | HREG_B ATTRIBUTE MEMORY SELECT is driven by the host system and is used to access the Attribute Memory                                                                                                                     |                  |

| 38 | -INPACK | HINPACK_B                                                                                                                       | INPUT ACKNOWLEDGE is driven by MAC. Is asserted when the device is selected and the device is responding to an I/O Read command.                                                                                           | Output, 2mA      |

| 39 | -WAIT   | HWAIT_B                                                                                                                         | HWAIT_B is driven by MAC and allows for extending the memory or I/O cycle                                                                                                                                                  | Output, 4mA      |

| 40 | RESET   | HRESET                                                                                                                          | Used to asynchronously reset the complete Module                                                                                                                                                                           | Input, PU,5VT    |

| 41 | -VS2    | VS2_B                                                                                                                           | Voltage sense signal                                                                                                                                                                                                       | Output, 5VT 4mA  |

| 42 | N/A     | WLAN_LED_B                                                                                                                      | WLAN LED control signal, driven the LED indicating the link status of WLAN                                                                                                                                                 | Output, 4mA      |

| 43 | N/A     | PCM_OUT                                                                                                                         | Reserved for BT portion , keep its open on host side if no use.                                                                                                                                                            |                  |

| 44 | IREQ    | IREQ_B                                                                                                                          | INTERRUPT REQUEST to the host. In Memory mode this pin signifies RDY/BSY_typically used during card initialization immediately after reset or power on. Indicates to the host that the device is not able to transfer data | Output, 4mA      |

| 45 | -WE     | HWE_B                                                                                                                           | WRITE ENABLE is driven by the host during a memory Write Access                                                                                                                                                            | Input, PU,5VT    |

| 46 | -IOWR   | HIOWR_B                                                                                                                         | I/O Write Strobe is driven by the host and is asserted when the host wants to write to an on-chip I/O register                                                                                                             | Input, PU,5VT    |

| 47 | -IORD   | HIORD_B                                                                                                                         | I/O Read Strobe is driven by the host and is asserted when the host wants to read from an on-chip I/O register                                                                                                             | Input, PU,5VT    |

| 48 | -VS1    | -VS1                                                                                                                            | Reserved                                                                                                                                                                                                                   | Output, 5VT      |

| 49 | -CE2    | HCE2_B                                                                                                                          | CARD ENABLE2 is driven by the host system and is used as select strobe in both I/O and memory mode. Enables odd numbered address bytes                                                                                     | Input, PU,5VT    |

| 50 | D15     | HD15                                                                                                                            | Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register                                                                                                 | IO, PD, 5VT, 4mA |

| 51 | D14     | HD14 Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register |                                                                                                                                                                                                                            | IO, PD, 5VT, 4mA |

| 52 | D13     | HD13                                                                                                                            | Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register                                                                                                 | IO, PD, 5VT, 4mA |

| 53 | D12     | HD12                                                                                                                            | Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE MAC Host Interface register                                                                                                 | IO, PD, 5VT, 4mA |

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

| 54 | D11 | HD11     | Data Input/Output line constitute a bi-directional bus. HD[15:0] are used to access the MODULE | IO, PD, 5VT, 4mA |

|----|-----|----------|------------------------------------------------------------------------------------------------|------------------|

|    |     |          | MAC Host Interface register                                                                    |                  |

| 55 | N/A | BT_LED_B | BT LED control signal which drive the LED to                                                   | Output 4mA       |

|    |     |          | indicate the activity of Bluetooth                                                             |                  |

| 56 | N/A | RXD_B    | UART data line CMOS input signal                                                               | Input, WPD, 1µA  |

|    |     |          |                                                                                                |                  |

| 57 | N/A | CTS_B    | UART clear to sent COMS input signal                                                           | Input, WPD, 1µA  |

|    |     |          |                                                                                                |                  |

| 58 | N/A | PCM_CLK  | Reserved for BT portion , keep its open on host                                                |                  |

|    |     |          | side if no use.                                                                                |                  |

| 59 | VCC | VCC_BT   | Power 3.3V_BT                                                                                  | Input            |

| 60 | GND | GND      |                                                                                                |                  |

|    |     |          |                                                                                                | I                |

Fig 1: Pin 1 assignment and indication Drawing (To be updated with latest design)

#### 10.2.1. LED INTERFACE

The Wireless Module will provide two control signals to the host and capable to drive an LED to indicate the connectivity and operating status.

The WM-BG-MR-01 have 2 LED's (output) via 60 pins connector for feedback to the user on the current WLAN activity state. The signaling will reflect status / activity as described in the table below. Those two signals are provided via the board to board connector with the following pin assignment.

| Pin No | Pin description | Function description          |

|--------|-----------------|-------------------------------|

| 42     | WLAN_LED        | Link activity of Wireless LAN |

| 55     | BT              | Power status indication       |

#### LED code to be defined!

#### 10.2.2. ANTENNA INTERFACE

No antenna diversity supported on the Wireless Module. The output impedance of the cable is 50 Ohms.

Antenna Connector: *Hirose W-FL-R-SMT(10)*

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

#### 10.2.3. BLUETOOTH INTERFACE

There are interfaces signal to routed between WiFi and Bluetooth to provide coexistence with 802.15 Bluetooth modules.

The BT co-existence interface supported, which is 2 Wire CSR co-existence.

The control signals are provided via the 60 pins B2B connector with the interface defined as below:

| Symbol      | Interface  | "Signal name" & description                                                                                         |

|-------------|------------|---------------------------------------------------------------------------------------------------------------------|

| ВТАСТ       | 2 Wire-CSR | "BT_Priority" This pin indicates to WLAN BCA device that BT module is active or will soon be active to TX/RX stage. |

| WLAN_active | 2 Wire-CSR | "Wlan_Active", This pin indicates to BT module that WLAN is active or will soon be active to TX/RX stage.           |

Note 1: "WLAN BCA" device is a functional block in 88W8385 works as Bluetooth co-existence management .

#### 10.3. SOFTWARE

The following source code will be provided for porting to the embedded system under the SLA with chipset supplier

- Linux source code

- Source code of development utility base on Windows CE

#### 11. DESIGN FOR EXCELLENCE (DFX)

#### 11.1. TESTABILITY

The WM-BG-MR-01 module can be tested on the by using adapter card or similar interface. The adapter card must be such that from the FTS the WM-BG-MR-01 module is seen and recognized as PC Card or Compaq Flash.

No additional test pins are required to support in-circuit testing.

#### 11.2. LOGISTICS

All customer specific requirements – customization – will be implemented at the highest possible level to support build to order and keep the number of modules in SMT to a minimum. Additional module variants might be added base on business potential.

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.

#### 12. HUMAN FACTORS

Due to the nature of this product (embedded module) no human factors required

#### 13. INDUSTRIAL DESIGN

Due to the nature of this product (embedded module) no industrial design requirements are required.

#### 14. RELIABILITY

The WM-BG-MR-01 module guarantee an MTBF of 150,000 hrs based on an ambient temperature and workload of 2,920 hours. The workload is based on a unit working for 8 hours per day, 365 days per year.

The MTBF estimation base on is Bell code standard, Class II.

#### 15. PACKAGE

To be updated.

All rights are reserved by USI. No part of this technical document can be reproduced in any form without permission of USI.