## **Micrtoune USB Dongle : Cable free MT0760-CF30/100**

### **Operational Description**

#### **Hopping sequence is generated (pseudorandomly)**

In total, 10 types of hopping sequences are defined .five for the 79-hop and five for the 23-hop system, respectively. Using the notation of parentheses () for figures related to the 23-hop system, these sequences are:

- A **page hopping sequence** with 32 (16) unique wake-up frequencies distributed equally over the 79 (23) MHz, with a period length of 32 (16);

- A **page response sequence** covering 32 (16) unique response frequencies that all are in an one-to-one correspondence to the current page hopping sequence. The master and slave use different rules to obtain the same sequence;

- An **inquiry sequence** with 32 (16) unique wake-up frequencies distributed equally over the 79 (23) MHz, with a period length of 32 (16);

- A **inquiry response sequence** covering 32 (16) unique response frequencies that all are in an one-to-one correspondence to the current inquiry hopping sequence.

- A **channel hopping sequence** which has a very long period length, which does not show repetitive patterns over a short time interval, but which distributes the hop frequencies equally over the 79 (23) MHz during a short time interval;

For the page hopping sequence, it is important that we can easily shift the phase forward or backward, so we need a 1-1 mapping from a counter to the hop frequencies. For each case, both a hop sequence from master to slave and from slave to master are required.

The inquiry and inquiry response sequences always utilizes the GIAC LAP as lower address part and the DCI as upper address part in deriving the hopping sequence, even if it concerns a DIAC inquiry.

#### **Example of the hopping sequence channels (hopset table)**

The selection scheme consists of two parts:

- selecting a sequence;

- mapping this sequence on the hop frequencies;

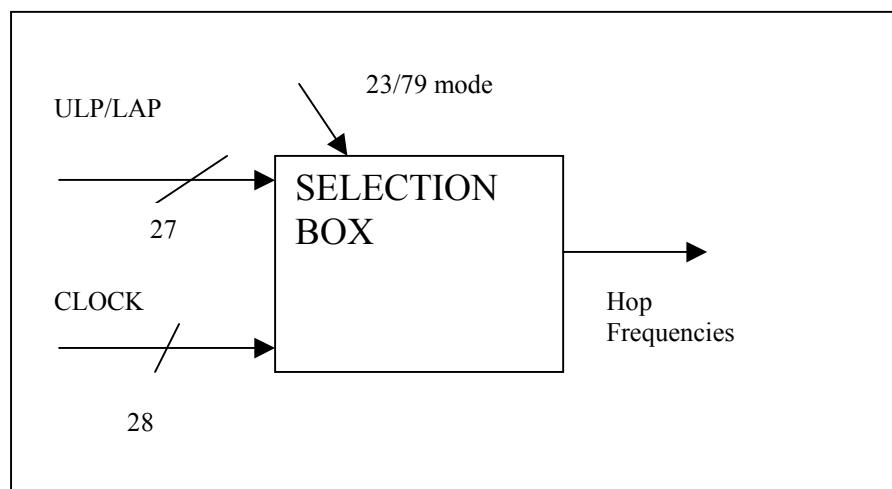

The general block diagram of the hop selection scheme is shown in 1.

The mapping from the input to a particular hop frequency is performed in the selection box. Basically, the input is the native clock and the current address. In **CONNECTION** state, the native clock (CLKN) is modified by an offset to equal the master clock (CLK). Only the 27 MSBs of the clock are used. In the **page** and **inquiry** substates, all 28 bits of the clock are used. However, in **page** substate the native clock will be modified to the master's estimate of the paged unit.

The address input consists of 28 bits, i.e., the entire LAP and the 4 LSBs of the UAP. In **CONNECTION** state, the address of the master is used. In **page** sub-state

the address of the paged unit is used. When in **inquiry** substate, the UAP/LAP corresponding to the GIAC is used. The output constitutes a pseudo-random sequence, either covering 79 hop or 23 hops, depending on the state.

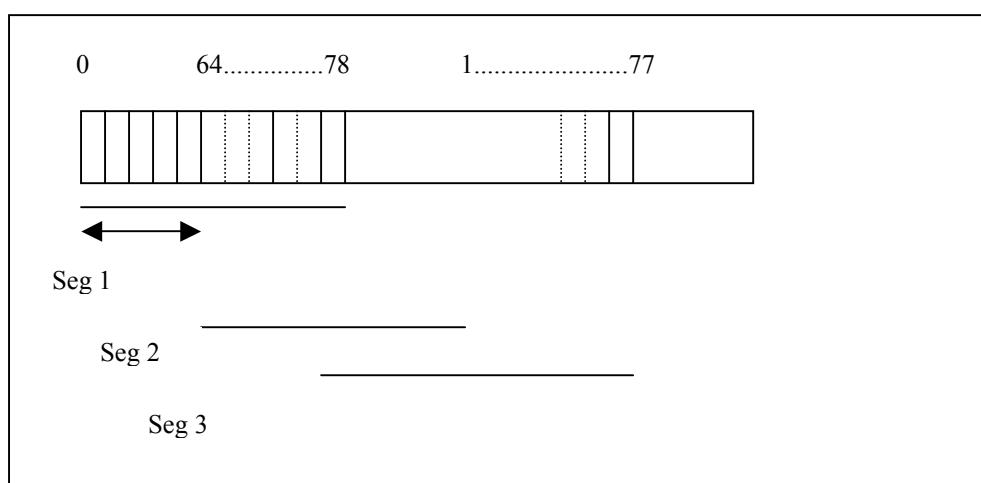

For the 79-hop system, the selection scheme chooses a segment of 32 hop frequencies spanning about 64 MHz and visits these hops once in a random order. Next, a different 32-hop segment is chosen, etc. In case of the **page**, **page scan**, or **page response** substates, the same 32-hop segment is used all the time (the segment is selected by the address; different units will have different paging segments). In connection state, the output constitutes a pseudo-random sequence that slides through the 79 hops or 23 hops, depending on the selected hop system.

Figure 1.

For the 79-hop system, the selection scheme chooses a segment of 32 hop frequencies spanning about 64 MHz and visits these hops once in a random order. Next, a different 32-hop segment is chosen, etc. In case of the **page**, **page scan**, or **page response** substates, the same 32-hop segment is used all the time (the segment is selected by the address; different units will have different paging segments). In connection state, the output constitutes a pseudo-random sequence that slides through the 79 hops or 23 hops, depending on the selected hop system. The principle is depicted in Figure 2.0

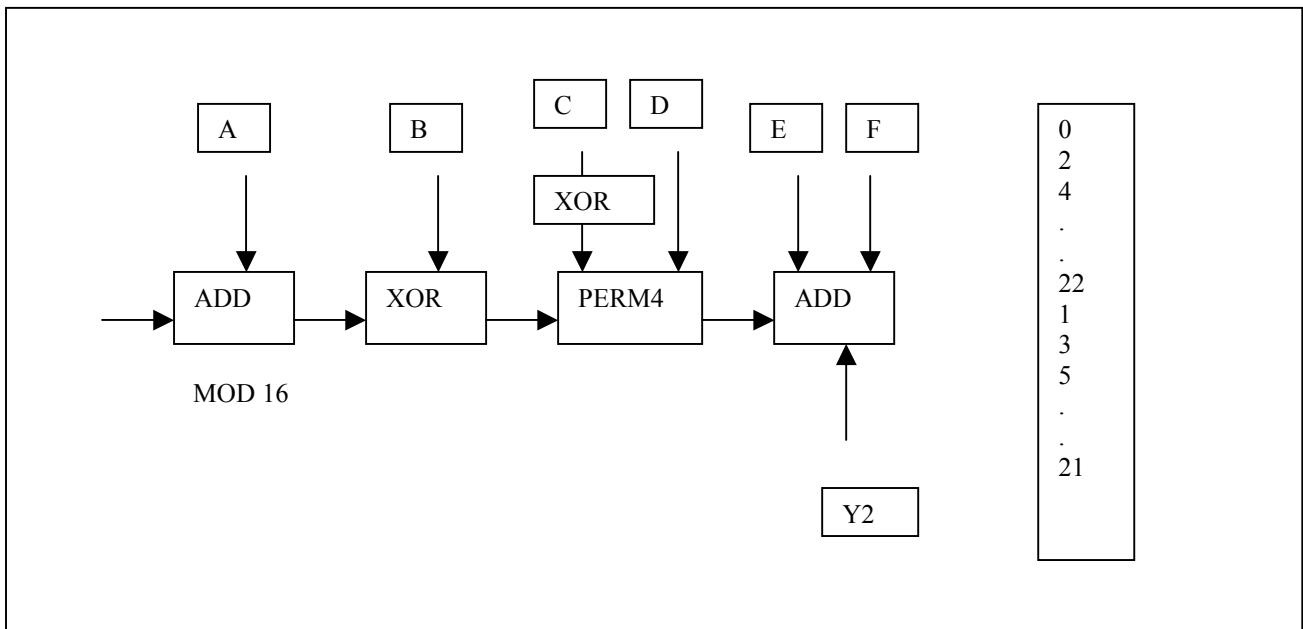

The hop selection kernels for the 79 hop system are shown in Figure 3.0. The X input determines the phase in the 32-hop segment, whereas Y1 and Y2 selects between master-to-slave and slave-to-master transmission. The inputs A to D determine the ordering within the segment, the inputs E and F determine the mapping onto the hop frequencies. The kernel addresses a register containing the hop frequencies. This list should be created such that first all even hop frequencies are listed and then all odd hop frequencies. In this way, a 32-hop segment spans about 64 MHz, whereas a 16-hop segment spans the entire 23-MHz.

Figure 3.0

The selection procedure consists of an addition, an XOR operation, a permutation operation, an addition, and finally a register selection. In the remainder of this chapter, the notation  $A_i$  is used for bit  $i$  of the BD\_ADDR.

### 11.2.1 First addition operation

The first addition operation only adds a constant to the phase and applies a modulo 32 or a modulo 16 operation. For the page hopping sequence, the first addition is redundant since it only changes the phase within the segment. However, when different segments are concatenated (as in the channel hopping sequence), the first addition operation will have an impact on the resulting sequence.

### 11.2.2 XOR operation

Let  $Z'$  denote the output of the first addition. In the XOR operation, the four LSBs of  $Z'$  are modulo-2 added to the address bits A 22-19 .

The permutation operation involves the switching from 5 inputs to 5 outputs for the 79 hop system and from 4 inputs to 4 outputs for 23 hop system, in a manner controlled by the control word. Table 1 shows the control of the butterflies by the control signals P. Note that P 0-8 corresponds to D 0-8 , and, corresponds to for in Figure 3.0

| Control<br>Signal | Butterfly | Control<br>signal | Butterfly |

|-------------------|-----------|-------------------|-----------|

| P 0               | {Z 0,Z 1} | P 8               | {Z1,Z4}   |

| P 1               | {Z 2,Z 3} | P 9               | {Z 0,Z 3} |

| P 2               | {Z 1,Z 2} | P 10              | {Z 2,Z 4} |

| P 3               | {Z 3,Z 4} | P 11              | {Z 1,Z 3} |

| P 4               | {Z 0,Z 4} | P 12              | {Z 0,Z 3} |

| P 5               | {Z 1,Z 3} | P 13              | {Z 1,Z 2} |

| P 6               | {Z 0,Z 2} |                   |           |

| P 7               | {Z 3,Z 4} |                   |           |

Table 11.1: Control of the butterflies for the 79 hop system

### Description how the associated receiver has the ability to shift frequencies in synchronization with the transmitted signals

The Bluetooth transceiver applies a time-division duplex (TDD) scheme. This means that it alternately transmits and receives in a synchronous manner. It depends on the mode of the Bluetooth unit what the exact timing of the TDD scheme is. In the normal connection mode, *the master transmission shall always start at even numbered time slots (master CLK1=0) and the slave transmission shall always start at odd numbered time slots (master CLK1=1)*. Due to packet types that cover more than a single slot, master transmission may continue in odd numbered slots and slave transmission may continue in even numbered slots. All timing diagrams shown in this chapter are based on the signals as present at the antenna. The term “exact” when used to describe timing refers to an ideal transmission or reception and neglects timing jitter and clock frequency imperfections.

The average timing of master packet transmission must not drift faster than 20 ppm relative to the ideal slot timing of 625  $\mu$ s. The instantaneous timing must not deviate more than 1  $\mu$ s from the average timing. Thus, the absolute packet transmission timing of slot boundary must fulfill the equation:

(EQ 1)

where is the nominal slot length (625  $\mu$ s), denotes jitter (  $\mu$ s) at slot boundary , and, , denotes the drift ( ppm) within slot . The jitter and drift may vary arbitrarily within the given limits for every slot, while “offset” is an arbitrary but fixed constant. For hold, park and sniff mode the drift and jit-ter

parameters as described in Link Manager Protocol apply.

## MASTER/SLAVE TIMING SYNCHRONIZATION

The piconet is synchronized by the system clock of the master. The master never adjusts its system clock during the existence of the piconet: it keeps an exact interval of  $M \times 625 \text{ }\mu\text{s}$  (where  $M$  is an even, positive integer larger than 0) between consecutive transmissions. The slaves adapt their native clocks with a timing offset in order to match the master clock. This offset is updated each time a packet is received from the master: by comparing the exact RX timing of the received packet with the estimated RX timing, the slaves correct the offset for any timing misalignments. Note that the slave RX timing can be corrected with any packet sent in the master-to-slave slot, since only the channel access code is required to synchronize the slave. The slave TX timing shall be based on the most recent slave RX timing. The RX timing is based on the latest successful trigger during a master-to-slave slot. For ACL links, this trigger must have occurred in the master-to-slave slot directly preceding the current slave transmission; for SCO links, the trigger may have occurred several master-to-slave slots before since a slave is allowed to send an SCO packet even if no packet was received in the preceding master-to-slave slot.

The slave shall be able to receive the packets and adjust the RX timing as long as the timing mismatch remains within the  $\pm 10 \text{ }\mu\text{s}$  uncertainty window.

The master TX timing is strictly related to the master clock. The master shall keep an exact interval of  $M \times 1250 \text{ }\mu\text{s}$  (where  $M$  is a positive integer larger than 0) between the start of successive transmissions; the RX timing is based on this TX timing with a shift of exactly  $N \times 625 \text{ }\mu\text{s}$  (where  $N$  is an odd, positive integer larger than 0). During the master RX cycle, the master will also use the  $\pm 10 \text{ }\mu\text{s}$  uncertainty window to allow for slave misalignments. The master will adjust the RX processing of the considered packet accordingly, but will **not** adjust its RX/TX timing for the following TX and RX cycles. During periods when an active slave is not able to receive any valid channel access codes from the master, the slave may increase its receive uncertainty window and/or use predicted timing drift to increase the probability of receiving the master's bursts when reception resumes.