**DATA**  **UNWIRED**

**HÖFT & WESSEL**

This document and its contents shall not be reproduced or transferred in any form without express permission.

Compensation will be claimed for any infringement. All rights reserved in the event of patenting or registration of utility models.

© Höft & Wessel AG 2008

Subject to amendment, errors excepted

## Contents

|                                                                |           |

|----------------------------------------------------------------|-----------|

| <b>1. Preface.....</b>                                         | <b>4</b>  |

| 1.1    About this document.....                                | 4         |

| 1.2    Related Documents .....                                 | 4         |

| 1.3    Contact Höft & Wessel AG .....                          | 4         |

| <b>2. Important User information .....</b>                     | <b>5</b>  |

| 2.1    Note for Users in Canada .....                          | 6         |

| 2.2    Note for Users in the USA .....                         | 7         |

| <b>3. Introduction.....</b>                                    | <b>8</b>  |

| 3.1    General description.....                                | 8         |

| 3.2    System diagram.....                                     | 8         |

| <b>4. Conformity .....</b>                                     | <b>9</b>  |

| <b>5. Hardware Description .....</b>                           | <b>10</b> |

| 5.1    Mechanical Characteristics.....                         | 10        |

| 5.1.1    Dimensions .....                                      | 10        |

| 5.1.2    Weight.....                                           | 10        |

| 5.1.3    Image .....                                           | 10        |

| 5.1.4    Mechanical Drawing.....                               | 11        |

| 5.2    Electrical Characteristics .....                        | 12        |

| 5.2.1    Pinout .....                                          | 12        |

| 5.2.2    Absolute Maximum Ratings .....                        | 13        |

| 5.2.3    Electrical Specifications .....                       | 13        |

| 5.2.3.1    Power Supply .....                                  | 13        |

| 5.2.3.2    Digital I/O.....                                    | 14        |

| 5.2.3.3    UART interface.....                                 | 14        |

| 5.2.3.4    SPI interface.....                                  | 14        |

| 5.2.3.5    Radio Frequency Interface .....                     | 15        |

| 5.2.3.6    Voice interface.....                                | 16        |

| 5.2.3.6.1    Microphone bias.....                              | 16        |

| 5.2.3.6.2    Microphone input.....                             | 16        |

| 5.2.3.6.3    Speaker output.....                               | 17        |

| 5.3    Environmental Conditions.....                           | 17        |

| 5.4    Interface Description.....                              | 18        |

| 5.4.1    System connector .....                                | 18        |

| 5.4.2    UART Interface .....                                  | 19        |

| 5.4.2.1    Minimum RS-232 configuration.....                   | 19        |

| 5.4.3    SPI Interface .....                                   | 20        |

| 5.4.4    Voice Interface .....                                 | 20        |

| 5.4.4.1    Connection of microphone and speaker .....          | 20        |

| 5.4.5    ADC/PWM Interface.....                                | 21        |

| 5.4.6    Reset Interface.....                                  | 22        |

| 5.4.6.1    Reset timing (external reset).....                  | 23        |

| 5.4.6.2    Short Reset .....                                   | 24        |

| 5.4.6.3    Activation of Download and Configuration Mode ..... | 24        |

| 5.4.6.4    Precautions to avoid Reset Problems .....           | 25        |

| 5.4.7    I2C Interface .....                                   | 25        |

| 5.4.8    PCM Interface .....                                   | 25        |

| 5.4.9    General Purpose I/O .....                             | 25        |

| 5.4.10    LED interface .....                                  | 26        |

| 5.4.11    Bus Interface .....                                  | 26        |

| 5.4.12    RF Interface .....                                   | 27        |

| <b>6. Specific Integration Topics .....</b>                    | <b>29</b> |

| 6.1    Power Supply.....                                       | 29        |

| 6.2    Range .....                                             | 29        |

## 1. Preface

Dear customer, thank you for choosing the HW 86022 FHSS radio module. You have made a good choice, since HW 86022 is a powerful and very versatile product that easily adds 2.4 GHz FHSS (Frequency Hopping Spread Spectrum) communication to your application.

Höft & Wessel aims for best customer satisfaction. In case of any problems with this manual or with our products please do not hesitate to contact us. Your feedback will enable our specialists to solve your problems and continually improve our products and documentation.

### 1.1 About this document

This manual contains the full technical specification of the HW 86022 as well as all necessary information for a successful hardware integration. It will help you in getting the optimum integration result.

HW 86022 is a future-proof product which offers a number of flexible interfaces and features. It is delivered together with Höft & Wessel FHSS firmware. However, not all of the versatile features described in the hardware section are supported by the standard firmware but some will require a customised firmware.

### 1.2 Related Documents

Refer to HW 86022 Firmware Manual for detailed information on software integration and configuration command reference.

### 1.3 Contact Höft & Wessel AG

For immediate assistance please address yourself to the Höft & Wessel service line:

Phone: +49-1803-232829

Fax: +49-511-6102-411

Email: [info@hoeft-wessel.de](mailto:info@hoeft-wessel.de)

If you have general questions concerning Höft & Wessel Data-Unwired products you may directly contact the Data-Unwired team:

Phone: +49-511-6102-226

Fax: +49-511-6102-437

Email: [tol@hoeft-wessel.de](mailto:tol@hoeft-wessel.de)

Latest revisions of all publicly available documentation and firmware downloads are available from our web-site [www.data-unwired.com](http://www.data-unwired.com). If you are interested in Höft & Wessel Group in general, visit [www.hoeft-wessel.com](http://www.hoeft-wessel.com).

Address:

Höft & Wessel AG

Rotenburger Strasse 20

D-30659 Hannover

Germany

## 2. Important User information

### NOTE:

This equipment makes use of radio spectrum and emits radio frequency energy. Care should be taken when the device is integrated in systems. Make sure that all specification within this document are followed, especially concerning operating temperature and supply voltage range.

Refer to national regulations of the region where the HW 86022 module shall be operated and make sure the national requirements are fulfilled.

Modifications not expressly approved by Höft & Wessel AG could void the user's authority to operate the equipment.

### NOTE:

This equipment is sensitive to electro-static discharge. Use an ESD-safe workstation for handling and use suitable packaging.

## 2.1 Note for Users in Canada

### General Notes:

Operation is subject to the following two conditions:

- (1) this device may not cause harmful interference, and

- (2) this device must accept any interference, including interference that may cause undesired operation of the device.

To reduce potential radio interference to other users, the antenna type and its gain should be chosen so that the equivalent isotropically radiated power (e.i.r.p.) is not more than that permitted for successful communication.

### Integration into a Host System:

This radio module is designed for professional use and must be integrated into a host system by qualified personnel only.

The module is granted a limited modular approval, i.e. it can be integrated in host systems if the following requirements are met:

- The supply voltage specifications in chapter 5.2.3.1 in this document must be met.

- The permanently attached wire antenna must be used.

- The design of the final product section containing the HW 86022 transceiver module must be approved by Höft & Wessel AG.

The use of other than the attached antenna is not covered by the granted modular approval. In a case where a different antenna is necessary contact Höft & Wessel AG for information about applicable authorization procedures.

The outside of the host device into which the module is installed must display a label referring to the enclosed module. This exterior label can use wording such as the following: "Contains Transmitter Module IC 4153A-860221" or "Contains IC 4153A-860221"

## 2.2 Note for Users in the USA

### General Note:

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications.

However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

The rated RF power (conducted) of the device is 0.072 W. The internal antennas used for this mobile transmitter must provide a separation distance of at least 20 cm from all persons and must not be co-located and operated in conjunction with any other antenna or transmitter.

### Integration into a Host System:

This radio module is designed for professional use and must be integrated into a host system by qualified personnel only.

The module is granted a limited modular approval, i.e. it can be integrated in host systems if the following requirements are met:

- The supply voltage specifications in chapter 5.2.3.1 in this document must be met.

- The permanently attached wire antenna must be used.

- The design of the final product section containing the HW 86022 transceiver module must be approved by Höft & Wessel AG.

The use of other than the attached antenna is not covered by the granted modular approval. In a case where a different antenna is necessary contact Höft & Wessel AG for information about applicable authorization procedures.

The outside of the host device into which the module is installed must display a label referring to the enclosed module. This exterior label can use wording such as the following: "Contains Transmitter Module FCC ID: PGM860221" or "Contains FCC ID: PGM860221".

On the host application a label shall show the following wording:

„This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.“

Refer to Part 2 and Part 15C of FCC Rules for details.

### 3. Introduction

The FHSS radio module HW 86022 is a highly versatile and powerful engine for industrial applications. It is based on DECT technology, but operates on the 2.4 GHz ISM band. It provides a complete radio according to 2.4 GHz FHSS standard together with a combined DECT baseband and application processor interfacing the host system.

#### 3.1 General description

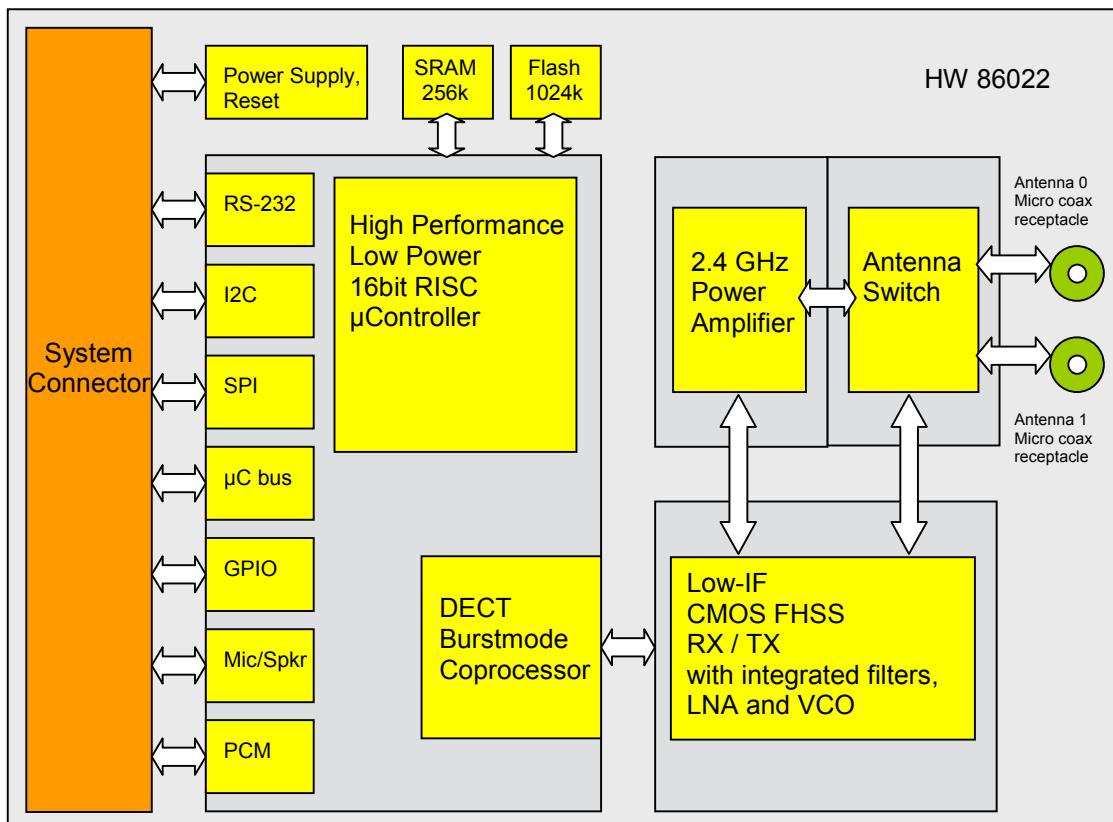

Built around a 16-bit high-speed low-power RISC microcontroller and a highly integrated state-of-the-art 2.4 GHz FHSS radio the architecture of the HW 86022 features a full set of useful interfaces for support of data and voice services in various environments.

These include RS-232 and SPI for data transmission. Additional general purpose I/Os, I2C plus an accessible bus interface make the HW 86022 ideally suited for industrial automation and control applications with specific I/O requirements. A PCM interface allows for connection to digital voice systems and an analogue front-end supports direct connection of voice equipment such as headsets.

The RF section complies with world wide standards for operation on the 2.4 GHz ISM band used throughout the world. Two antenna ports allow for the use of diversity antennas to improve radio performance in difficult environments.

DECT/FHSS protocol stack and application software is integrated in the HW 86022 firmware and can be upgraded in the field.

The single-sided ultra-compact and low-power design make the HW 86022 optimally suited for battery powered and handheld devices.

#### 3.2 System diagram

Figure 1: HW86022 System Diagram

## 4. Conformity

The HW 86022 module complies with the essential requirements of §3 and the other relevant provisions of Article 3 of the R&TTE directive when used for its intended purpose and is labelled with the CE conformity mark. It has obtained a limited modular approval according to FCC (USA) and IC (Canada) regulations.

### Standards for Approval

#### EU

EN 300328

Electromagnetic compatibility and Radio spectrum Matters (ERM); Wideband transmission systems; Data transmission equipment operating in the 2,4 GHz ISM band and using wide band modulation techniques; Harmonized EN covering essential requirements under article 3.2 of the R&TTE Directive

EN 301489-1

Electromagnetic compatibility and Radio spectrum Matters (ERM); ElectroMagnetic Compatibility (EMC) standard for radio equipment and services; Part 1: Common technical requirements

EN 301489-17

Electromagnetic compatibility and Radio spectrum Matters (ERM); ElectroMagnetic Compatibility (EMC) standard for radio equipment and services; Part 17: Specific conditions for 2,4 GHz wideband transmission systems and 5 GHz high performance RLAN equipment

EN 61000-4-3

Electromagnetic compatibility (EMC) - Part 4-3: Testing and measurement techniques - Radiated, radio-frequency, electromagnetic field immunity test

EN 60950-1

Safety of information technology equipment

#### US

FCC regulations §15.247

Radio Frequency Devices - Intentional Radiators - Operation within the bands 902 - 928 MHz, 2400 - 2483.5 MHz, and 5725 - 5850 MHz.

#### Canada

RSS-210, Annex 8

Low-power Licence-exempt Radiocommunication Devices; Annex 8 - Frequency Hopping and Digital Modulation Systems Operating in the Bands 902-928 MHz, 2400-2483.5 MHz, and 5725-5850 MHz

### Additional Standards

ETSI EN 301175

Digital Enhanced Cordless Telecommunications (DECT); Common Interface (CI);

## 5. Hardware Description

### 5.1 Mechanical Characteristics

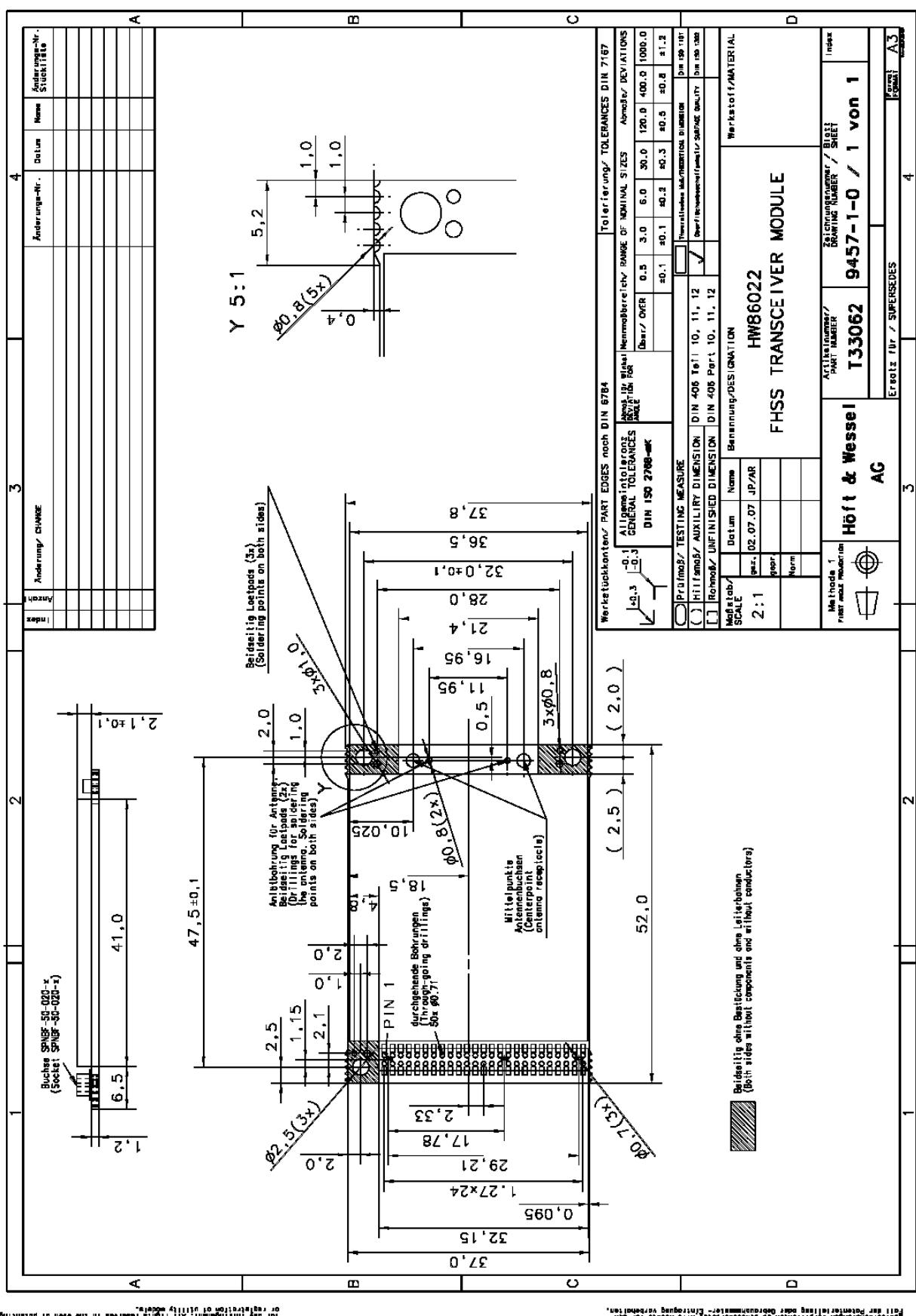

#### 5.1.1 Dimensions

| Parameter | Typ. | unit |

|-----------|------|------|

| Length    | 52.0 | mm   |

| Width     | 37.0 | mm   |

| Height    | 3.2  | mm   |

#### 5.1.2 Weight

| Parameter | Typ. | unit |

|-----------|------|------|

| Weight    | 8.3  | g    |

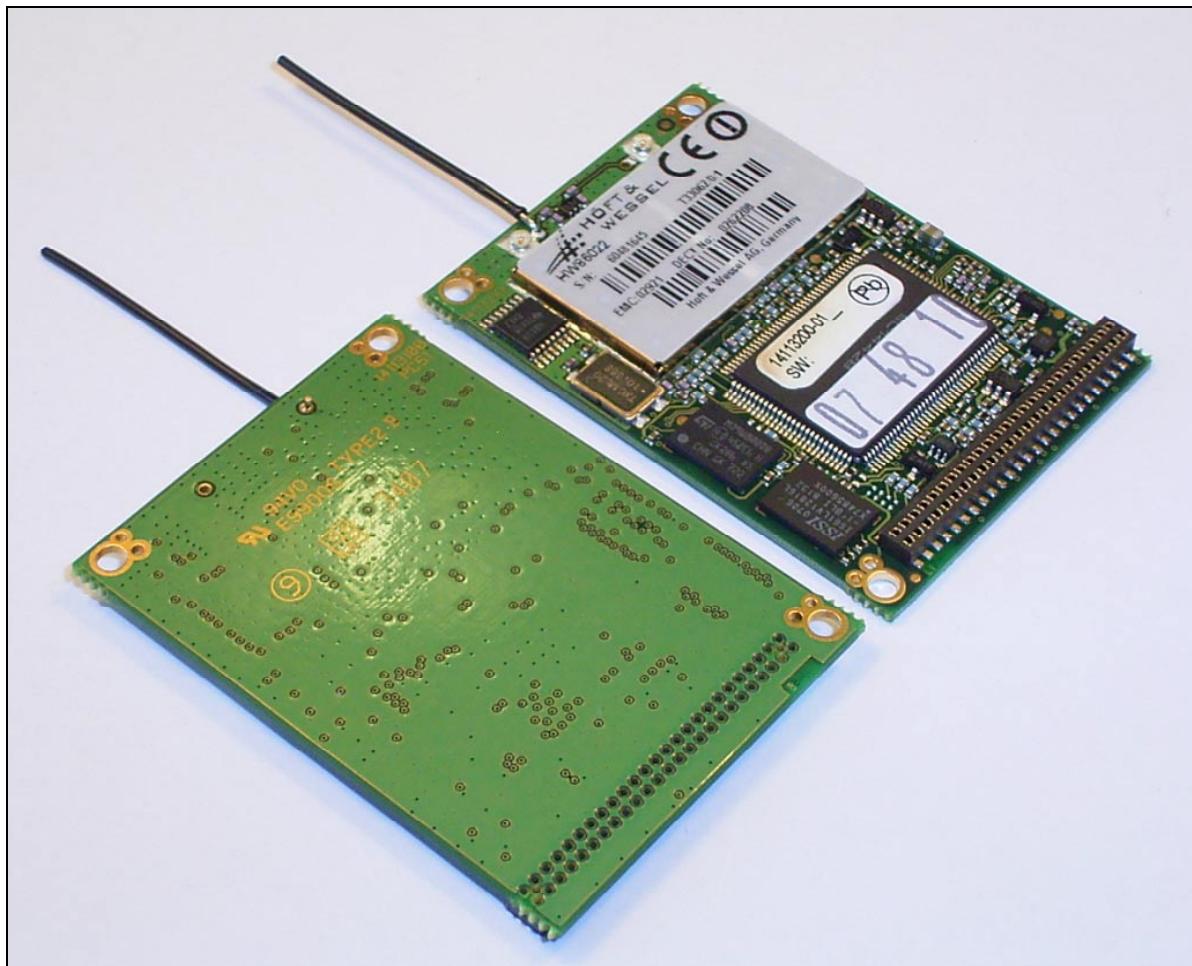

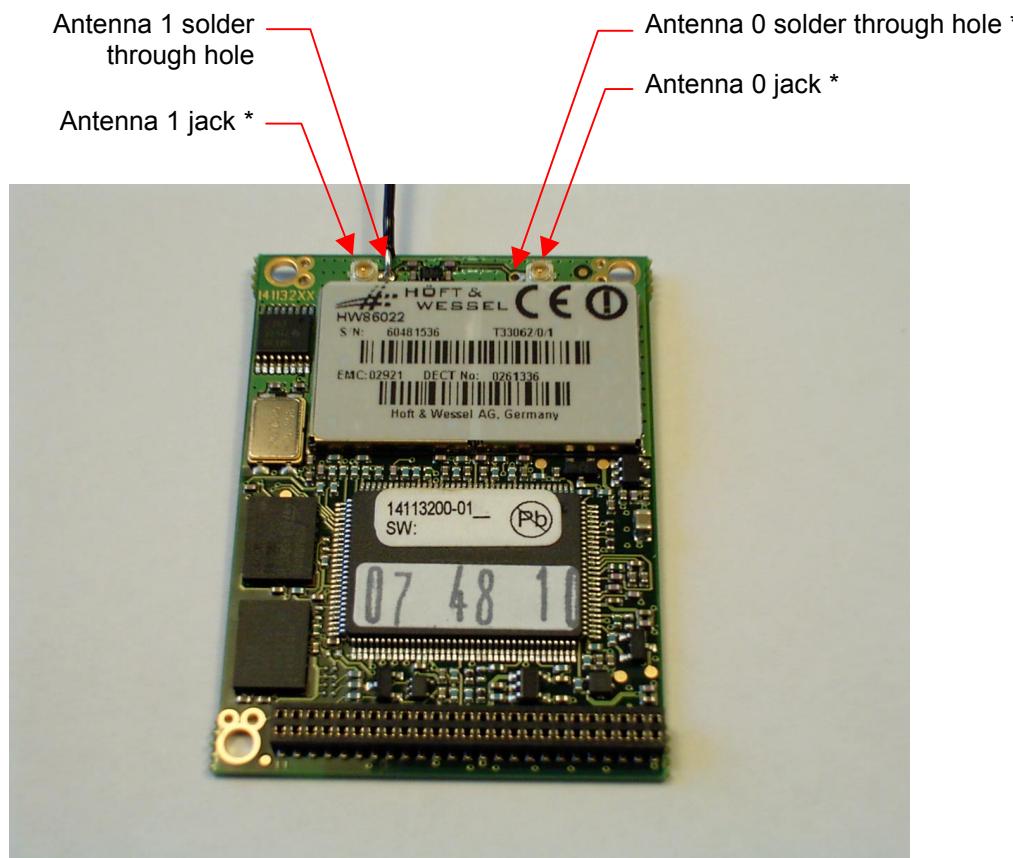

#### 5.1.3 Image

Figure 2: HW 86022 top and bottom view

## 5.1.4 Mechanical Drawing

Figure 3: Mechanical drawing

## 5.2 Electrical Characteristics

### 5.2.1 Pinout

| Pin | Name                | Description                                                                        | Pintype      | reset state |

|-----|---------------------|------------------------------------------------------------------------------------|--------------|-------------|

| 1   | VXN                 | Speaker out negative                                                               | Analogue     | Oa          |

| 2   | VXP                 | Speaker out positive                                                               | Analogue     | Oa          |

| 3   | VXIN                | Microphone in negative                                                             | Analogue     | Ia          |

| 4   | VXIP                | Microphone in positive                                                             | Analogue     | Ia          |

| 5   | MICN                | Microphone bias out reference                                                      | Analogue     | Oa          |

| 6   | MICP                | Microphone bias out positive                                                       | Analogue     | Oa          |

| 7   | RSTNO               | Reset out                                                                          | Digital      | Ipu80k      |

| 8   | RINGP/SPIDI         | Ring out, SPI data in                                                              | Digital      | I           |

| 9   | ADC/GPIO12          | Analogue digital converter in, General purpose I/O                                 | Dig/Analogue | I           |

| 10  | PWM/SPICLK          | PWM out, SPI clock in/out, General purpose I/O                                     | Digital      | I           |

| 11  | SDA/PCMFS1/GPIO11   | I2C Data, PCM frame sync 1, General purpose I/O                                    | Digital      | Ipu         |

| 12  | SCL/GPIO10          | I2C Clock, General purpose I/O                                                     | Digital      | O1          |

| 13  | GPIO1/LED0          | General purpose I/O, LED0 control                                                  | Digital      | O1          |

| 14  | GPIO2/SPIDO/LED1    | General purpose O, SPI data out, LED1 control                                      | Digital      | O0          |

| 15  | GPIO3/PCMFS0        | General purpose I/O, PCM frame sync 0                                              | Digital      | Ipu         |

| 16  | GPIO4/PCMCLK        | General purpose I/O, PCM clock in/out                                              | Digital      | Ipu         |

| 17  | GPIO5/PCMDIN        | General purpose I/O, PCM data in                                                   | Digital      | Ipu         |

| 18  | GPIO6/PCMDO         | General purpose I/O, PCM data out                                                  | Digital      | Ipu         |

| 19  | GPIO7/EXTINT/PIWRDY | General purpose I/O, external interrupt request in, parallel interface write ready | Digital      | Ipu         |

| 20  | GPIO8/EXTCS/PICS    | General purpose I/O, external chip select out, parallel interface select           | Digital      | Ipu         |

| 21  | RSTBI               | Reset in                                                                           | Digital      | Ipu         |

| 22  | GND                 | Ground                                                                             | Ground       |             |

| 23  | RTSI/PIRDREQ/BOOT2  | RS232 RST in, parallel interface read request, mode select in                      | Digital      | Ipu         |

| 24  | DTRI/BOOT3          | RS232 DTR in, mode select in                                                       | Digital      | Ipu         |

| 25  | RXDO                | RS232 RXD out                                                                      | Digital      | Ipu         |

| 26  | TXDI                | RS232 TXD in                                                                       | Digital      | I           |

| 27  | V3P3                | Digital section power supply                                                       | Supply       |             |

| 28  | VBATP               | RF section power supply                                                            | Supply       |             |

| 29  | CTSO/BOOT0          | RS232 CTS out, mode select in                                                      | Digital      | Ipu         |

| 30  | DSRO/BOOT1          | RS232 DSR out, mode select in                                                      | Digital      | Ipu         |

| 31  | DCDIO               | RS232 DCD in/out, General purpose I/O                                              | Digital      | Ohzpu       |

| 32  | RIIO                | RS232 RI in/out, General purpose I/O                                               | Digital      | Ohzpu       |

| 33  | RDn                 | μC bus read                                                                        | Digital      | O1          |

| 34  | WRn                 | μC bus write                                                                       | Digital      | O1          |

| 35  | D0                  | μC bus data                                                                        | Digital      | O1          |

| 36  | D1                  | μC bus data                                                                        | Digital      | O1          |

| 37  | D2                  | μC bus data                                                                        | Digital      | O1          |

| 38  | D3                  | μC bus data                                                                        | Digital      | O1          |

| 39  | D4                  | μC bus data                                                                        | Digital      | O1          |

| 40  | D5                  | μC bus data                                                                        | Digital      | O1          |

| 41  | D6                  | μC bus data                                                                        | Digital      | O1          |

| 42  | D7                  | μC bus data                                                                        | Digital      | O1          |

| 43  | A0                  | μC bus address                                                                     | Digital      | O1          |

| 44  | A1                  | μC bus address                                                                     | Digital      | O1          |

| 45  | A2                  | μC bus address                                                                     | Digital      | O1          |

| 46  | A3                  | μC bus address                                                                     | Digital      | O1          |

| 47  | A4                  | μC bus address                                                                     | Digital      | O1          |

| 48  | A5                  | μC bus address                                                                     | Digital      | O1          |

| 49  | GPIO9               | General purpose I/O                                                                | Digital      | Ohz         |

| 50  | GND                 | Ground                                                                             | Ground       |             |

Legend: Oa - analogue output, Ia - analogue input, Ipu - digital input with internal pull-up, Ipu80k - digital input with 80kOhm pull-up - digital input w/o pull-up, O1 - digital output high state, O0 - digital output low state, Ohz - digital output high impedance state, Ohzpu - digital output high impedance state with pullup.

### 5.2.2 Absolute Maximum Ratings

| Parameter | Remarks                                                 | Conditions              | Min          | Max             | unit |

|-----------|---------------------------------------------------------|-------------------------|--------------|-----------------|------|

| V3P3      | Digital supply voltage                                  |                         | -0.3         | 4.0             | V    |

| VBATP     | RF supply voltage                                       |                         | -0.3         | 4.6             | V    |

| liosum    | Current through all IO pins                             |                         |              | 90              | mA   |

| lio       | Current through IO pin                                  |                         |              | 20              | mA   |

| Vdigin    | Max Voltage on any digital inputs                       | V3P3>=3.3V<br>V3P3<3.3V | -0.3<br>-0.3 | 3.6<br>V3P3+0.3 | V    |

| Vanain    | Max voltage on any analogue inputs                      |                         | -0.3         | 2.0             | V    |

| lioprot   | Max current through any pin's protection diodes to V3P3 |                         |              | 100             | µA   |

| Imicprot  | Max current through MIC input pin's protection diodes   |                         |              | 2.4             | mA   |

NOTE: Absolute maximum ratings may be applied to the module for a short period of time. Applying values greater than those mentioned will damage the module.

### 5.2.3 Electrical Specifications

#### 5.2.3.1 Power Supply

| Parameter    | Remarks                | Conditions                                                                                                                                                                                                                                             | Min | Typ.                                                                                          | Max | unit |

|--------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------|-----|------|

| V3P3         | Digital supply voltage |                                                                                                                                                                                                                                                        | 3.1 | 3.3                                                                                           | 3.5 | V    |

| VBATP        | RF supply voltage      |                                                                                                                                                                                                                                                        | 3.0 |                                                                                               | 4.6 | V    |

| VBATP_ripple | Ripple on VBATP        |                                                                                                                                                                                                                                                        |     |                                                                                               | 100 | mV   |

| I3P3         | Digital supply current | CO<br>Idle<br>1-bearer<br><br>CLDPS<br>Idle<br>115kbps                                                                                                                                                                                                 |     | 8..11<br>13..15                                                                               |     | mA   |

| IBATP        | RF supply current      | CO<br>PT Scan<br>PT Sync'ed<br>PT 1-bearer<br>FT Idle<br>FT 1-bearer<br><br>CLDPS<br>PT Scan<br>PT Sync'ed 0kbps<br>PT RX 115kbps<br>PT TX 115kbps<br>FT Idle 0kbps<br>FT RX 115kbps<br>FT TX 115kbps<br><br>Continuous Receive<br>Continuous Transmit |     | 123<br>9<br>16<br>62<br>71<br><br>123<br>26<br>72<br>59<br>29<br>106<br>101<br><br>123<br>175 |     | mA   |

NOTE: A limited power source acc. to EN 60950-1, section 2.5, shall be used. Maximum IBATP current during transmission may increase in case of antenna impedance mismatch.

### 5.2.3.2 Digital I/O

| Parameter          | Remarks                | Conditions | Min | Typ. | Max                    | unit |

|--------------------|------------------------|------------|-----|------|------------------------|------|

| Vin_dig_high       | Digital in high level  |            | 2.0 |      |                        | V    |

| Vin_dig_low        | Digital in low level   |            |     |      | 1.0<br>(GPIO9:0.<br>6) | V    |

| Vout_dig_low_100µ  | Digital out low level  | 100µA      |     |      | 0.1                    | V    |

| Vout_dig_low_8m    | Digital out low level  | 8mA        |     |      | 0.6                    | V    |

| Vout_dig_high_100µ | Digital out high level | 100µA      | 3.0 |      |                        | V    |

| Vout_dig_high_8m   | Digital out high level | 8mA        | 2.4 |      |                        | V    |

### 5.2.3.3 UART interface

| Parameter       | Remarks                                                                      | Conditions | Min | Typ.                                          | Max | unit |

|-----------------|------------------------------------------------------------------------------|------------|-----|-----------------------------------------------|-----|------|

| UART data rates | Default:<br>115.2 kbps in data mode, 9.6 kbps in hardware configuration mode |            |     | 230.4<br>115.2<br>57.6<br>38.4<br>19.2<br>9.6 |     | kBd  |

| UART framing    |                                                                              |            |     | 8N1                                           |     |      |

| UART buffer     |                                                                              |            |     | DMA,<br>software controlled                   |     |      |

### 5.2.3.4 SPI interface

SPI interface will be operated in Master mode.

| Parameter        | Remarks | Conditions | Min | Typ.                    | Max   | unit |

|------------------|---------|------------|-----|-------------------------|-------|------|

| SPI Clock Master |         |            |     | 1.296<br>2.592<br>5.184 |       | MHz  |

| SPI Clock Slave  |         |            |     |                         | 5.184 | MHz  |

| SPI Mode         |         |            |     | 0, 1, 2, 3              |       |      |

### 5.2.3.5 Radio Frequency Interface

| Parameter                       | Remarks          | Conditions          | Min                                                         | Typ.  | Max    | unit   |

|---------------------------------|------------------|---------------------|-------------------------------------------------------------|-------|--------|--------|

| Frequency range                 |                  |                     | 2400                                                        |       | 2483.5 | MHz    |

| Channel spacing                 |                  |                     |                                                             | 1.728 |        | MHz    |

| Hopping channels                |                  |                     |                                                             | 45    |        |        |

| Frequency offset                |                  |                     | -50                                                         | 0     | +50    | kHz    |

| Frequency drift                 |                  |                     | -16                                                         | -30   | -41    | kHz/ms |

| Transmitter output power        |                  |                     | 18.0                                                        | 19.0  | 20.0   | dBm    |

| Receiver sensitivity            | BER < 10e-3      |                     | -93                                                         | -90   | -87    | dBm    |

| Antenna ports impedance         |                  |                     |                                                             | 50    |        | Ohm    |

| Isolation between antenna ports |                  |                     | 10                                                          | 20    |        | dB     |

| Modulation                      |                  |                     | Gaussian Frequency Shift Keying (GFSK: BxT=0.5 ; m= 288kHz) |       |        |        |

| Deviation                       |                  |                     | 280                                                         |       | 400    | kHz    |

| Multiplexing                    |                  |                     | Time Division Multiple Access (TDMA)                        |       |        |        |

| Bearers                         | blind slot radio | connection oriented | 6 full-slot duplex bearers                                  |       |        |        |

| Air data rate                   |                  |                     | 1.152                                                       |       |        |        |

| User data rate                  | per radio cell   | CLDPS               | up to 230                                                   |       |        |        |

|                                 | per bearer       | connection oriented | 26                                                          |       |        |        |

### 5.2.3.6 Voice interface

#### 5.2.3.6.1 Microphone bias

| Parameter    | Remarks                                         | Conditions                   | Min | Typ. | Max | unit |

|--------------|-------------------------------------------------|------------------------------|-----|------|-----|------|

| Vref         | Differential voltage between MICP and MICN pins |                              |     | 1.5  |     | V    |

| Vrefp_acc    | Accuracy of MICP voltage                        | Trimmed                      | -1  |      | +1  | %    |

| Vrefn_m      | Voltage from MICN to GND                        |                              |     | 0    |     | V    |

| Vrefp_load_c | MICP load capacitance                           |                              |     |      | 20  | pF   |

| Rvrefp       | MICP output resistance                          |                              |     | 10   | 15  | Ohm  |

| Nrefp        | MICP peak noise                                 | CCITT weighted               |     | -100 | -80 | dBV  |

| Srefp        | MICP power supply rejection ratio               |                              | 40  |      |     | dB   |

| Ivrefp       | MICP output current                             | Minimal load must be applied | 100 |      | 600 | µA   |

#### 5.2.3.6.2 Microphone input

| Parameter     | Remarks                                                        | Conditions                                                                            | Min   | Typ. | Max   | unit |

|---------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|------|-------|------|

| Vmic_0dB      | Differential RMS input voltage between VXIP and VXIN for 0dBm0 | 0dBm0 at codec output = -3.14dB of max PCM value, microphone gain at minimum, @1020Hz |       | 130  |       | mV   |

| Vmic_0dB_acc  | Accuracy                                                       | Trimmed                                                                               | -0.5  |      | +0.5  | dB   |

| Vmic_cm       | VXIP/VXIN common mode voltage                                  |                                                                                       |       | 0.9  |       | V    |

| Vmic_gain     | Microphone gain                                                | Software controlled, 16 steps                                                         | 0     |      | 30.1  | dB   |

| Vmic_gain_acc | Microphone gain accuracy                                       |                                                                                       | -0.75 |      | +0.75 | dB   |

| Rmic_diff     | Differential input impedance between VXIN and VXIP             |                                                                                       | 150   |      |       | kOhm |

| Vmic_offset   | Input referred DC-offset                                       | Microphone gain at maximum                                                            | -2.6  |      | +2.6  | mV   |

### 5.2.3.6.3 Speaker output

| Parameter                                           | Remarks | Conditions                                                                                                       | Min   | Typ. | Max       | unit |

|-----------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------|-------|------|-----------|------|

| Differential RMS output voltage between VXP and VXN |         | 0dBm0 at codec input = -3.14dB from max PCM value, speaker gain = 0.0dB, load circuit acc. to section 0, @1020Hz |       | 0.69 |           | V    |

| Differential Output Impedance between VXP and VXN   |         |                                                                                                                  |       | 2    | 5         | Ohm  |

| Load resistance                                     |         |                                                                                                                  | 30    |      |           | Ohm  |

| Load capacitance                                    |         | RL = 00<br>RI < 1kohm                                                                                            |       |      | 100<br>30 | pF   |

| Speaker gain                                        |         | Software controlled                                                                                              | -12   |      | 2.2       | dB   |

| Absolute speaker gain accuracy                      |         |                                                                                                                  | -0.75 |      | +0.75     | dB   |

## 5.3 Environmental Conditions

| Parameter | Remarks                 | Conditions     | Min | Typ. | Max | unit |

|-----------|-------------------------|----------------|-----|------|-----|------|

| Ta_op     | Operational temperature |                | -20 | +25  | +60 | °C   |

| Ta_st     | Storage temperature     |                | -40 |      | +80 | °C   |

| H         | Humidity                | Non condensing | 0   |      | 95  | %    |

## 5.4 Interface Description

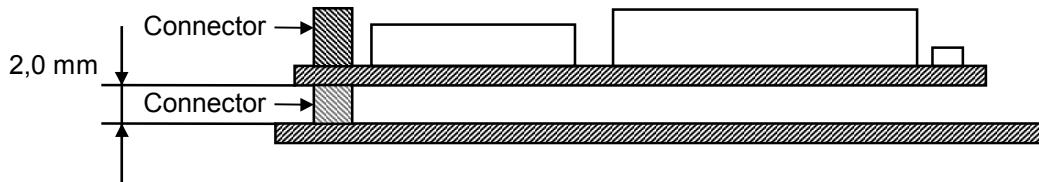

### 5.4.1 System connector

The interface to the host system is implemented as a 50 pin 1.27mm grid female connector. The part used on the HW 86022 module is a Plastron SPNBF-50-B-0, which is compatible to Samtec CLP-125-02-G-D-BE.

It is recommended to connect the module with a pin header by bottom entry method, i.e. through the printed board. This allows for best space saving and the RF connectors are accessible in mounted position.

Suitable pin header connectors are available from different manufacturers, such as Plastron, Samtec or others. The pin length determines the module's height above the host circuit board, depending whether components shall be fitted underneath the module.

Find a list of parts below as a suggestion. See section **Fehler! Verweisquelle konnte nicht gefunden werden.** of this document for accessories.

| Manufacturer | Part No.      |

|--------------|---------------|

| Plastron     | SPNZ-50...    |

|              | SPNB2-50...   |

| Samtech      | FTSH125-01... |

Figure 4: No components fitted on target PCB below HW 86022. Minimum distance between PCBs 2,0 mm

Figure 5: Components fitted on target PCB below HW 86022. Distance between PCBs depend on component heights (here: 4,0 mm)

### 5.4.2 UART Interface

The HW 86022 module provides a fully featured RS-232 serial interface. All interface signals are 3.3V CMOS level and are active at low state. A V.24 line driver must be provided in order to connect to a standard V.24 device, e.g. a PC.

#### NOTE!

**Connecting the module to a V.24 line without external line drivers may damage the module.**

| Signal | I/O | Description                              |

|--------|-----|------------------------------------------|

| TXDI   | I   | serial data from host to HW 86022        |

| RXDO   | O   | serial data from HW 86022 to host        |

| RTSI   | I   | hardware handshake from host to HW 86022 |

| CTSO   | O   | hardware handshake from HW 86022 to host |

| DTRI   | I   | ready signal from host to HW 86022       |

| DSRO   | O   | ready signal from HW 86022 to host       |

| DCDIO  | I/O | carrier detect modem lead signal         |

| RIIO   | I/O | ring indicator modem lead signal         |

Some of the RS-232 signals are used to control mode selection during hardware reset. Refer to section 5.4.6 for details. Most lead signals have enhanced functionality depending on software configuration. Refer to HW 86022 Firmware Manual for a detailed description.

#### NOTE!

**The UART interface does not support the transmission of break signals as these have a special purpose function in Höft & Wessel devices. Do not apply break conditions unless specified by Höft & Wessel. Make sure that a break condition is not applied during power-up transient conditions.**

#### 5.4.2.1 Minimum RS-232 configuration

The RS-232 interface may also be used in reduced configurations.

3-wire (RXDO,TXDI,GND) interface

- no hardware handshake, no call control

- requires to disable hardware handshake (see command „SPCOM“ in HW 86022 Firmware Manual for details) and call control (command „SPCC“).

5-wire interface (RXDO,TXDI,RTSI,CTSO,GND)

- hardware handshake, no call control

- requires to disable call control (see command „SPCC“ in HW 86022 Firmware Manual for details)

### 5.4.3 SPI Interface

The Serial Programming Interface provides a performant serial interface to control the module and for user data transfer. The module will act as SPI master device and therefore control SPI clock.

| Signal | I/O | Description  |

|--------|-----|--------------|

| SPIDO  | O   | SPI data out |

| SPIDI  | I   | SPI data in  |

| SPICLK | I/O | SPI clock    |

This feature is not supported in standard firmware release.

### 5.4.4 Voice Interface

Analogue voice interface is provided by hardware. The interface provides differential input and output as well as microphone bias generation and is suitable for connecting differential mode handsets or headsets.

| Signal | I/O | Description                        |

|--------|-----|------------------------------------|

| VXOP   | O   | analogue speaker output positive   |

| VXON   | O   | analogue speaker output negative   |

| VXIP   | I   | analogue microphone input positive |

| VXIN   | I   | analogue microphone input negative |

| MICBP  | O   | microphone bias voltage positive   |

| MICBN  | O   | microphone bias voltage negative   |

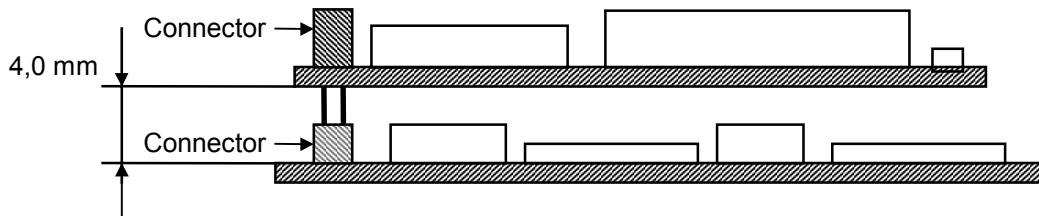

#### 5.4.4.1 Connection of microphone and speaker

Figure 3 shows a typical circuit to connect speaker and electret microphone.

The values of the components must be chosen such that

- Together with the input impedance of the pre-amplifier the AC coupling capacitors C1 and C2 form a transfer function with a zero at a frequency low enough to avoid unacceptable ripples in the considered signal bandwidth.

- A very low frequency pole (below 50 Hz) is formed by the capacitor C4 and the series resistors R1 and R2.

- The microphone biasing current is set such that the required sensitivity target is met. This depends on the microphone characteristics.

- System performance may be further enhanced by an additional capacitor C3 that filters out the peak of the cavity resonance. The value depends on the physical characteristics of the microphone housing.

Component values in Figure 1 are typical for a low impedance microphone (less than 3 k $\Omega$ ).

Note that all signals are dc-coupled to the microcontroller.

Figure 6: Electrical connection of microphone and speaker

#### 5.4.5 ADC/PWM Interface

This interface is used to capture and reproduce analogue signals with low bandwidth.

| Signal | I/O | Description                     |

|--------|-----|---------------------------------|

| ADC    | I   | analogue / digital converter in |

| PWM    | O   | pulse width modulated output    |

This feature is not supported in standard firmware releases.

### 5.4.6 Reset Interface

The reset interface is used to reset the HW 86022 module and its external peripherals.

| Signal | I/O | Description                                               |

|--------|-----|-----------------------------------------------------------|

| RSTBI  | I   | Reset input, ac-coupled, triggers on falling edge         |

| RSTNO  | I/O | Reset output, active low, $Z=3.3\text{k}\Omega\text{m}^1$ |

| BOOT0  | I   | download mode selection                                   |

| BOOT1  | I   | download mode selection                                   |

| BOOT2  | I   | data / configuration mode selection                       |

| BOOT3  | I   | data / configuration mode selection                       |

A reset at the HW 86022 module occurs in the following situations:

- Power on reset

- low voltage detected from internal supervisory circuit

- software reset

- external reset through RSTBI signal

- external reset through RSTNO signal (not recommended)

The HW 86022 module may simply be reset through the reset interface, but additionally certain reset sequences are used to change the module's operational modes:

- Data mode – normal operation with user data transfer

- Configuration mode – allows for configuration commands to be entered in order to change the software settings

- Download mode – a new firmware binary may be downloaded to the module's flash memory.

To support these modes the module must reliably distinguish an external reset from any other reset (collectively referred to as internal resets). This is achieved through appropriate reset timing. The host, which initiates the external reset must pull the RSTBI signal down. This will physically reset the HW 86022 module as can be observed on the RSTNO output.

After termination of its internal reset cycle, the HW 86022 will raise the RSTNO signal and firmware starts execution. In an early stage of program execution the firmware will test the value of the RSTBI signal. An external reset is indicated by a logical low.

At power-up the HW 86022 is automatically reset by the internal supervisory circuit.

A reset by the host processor (using the RSTBI signal) is needed in order to:

- start **configuration mode** (however, a software configuration mode may be entered by applying an escape sequence, see HW 86022 Firmware Manual).

- start **download mode** (however, the download procedure may also be invoked with a special command in configuration mode, see HW 86022 Firmware Manual).

- change from one of the above modes to **data mode** (normal operation), except if the software configuration mode entered by an escape sequence the data mode can be entered with an exit command.

If none of these hardware functions are required by the application, the RSTBI pin may be left open. In any case, taking provisions for potential firmware downloads is a substantial advantage for the future-proofness of your product. Use the configuration mode reset in your application e.g. if you cannot operate at the initial serial speed or want to avoid the escape sequence to be transferred through the data channel. Also, a few commands may not be available during software configuration mode (using the escape sequence).

---

<sup>1</sup> RSTNO pin is driven by a push-pull output through a series resistor of 3.3kΩ. Care must be taken when this pin shall be used to control external circuitry as only high impedance inputs shall be connected to ensure proper operation.

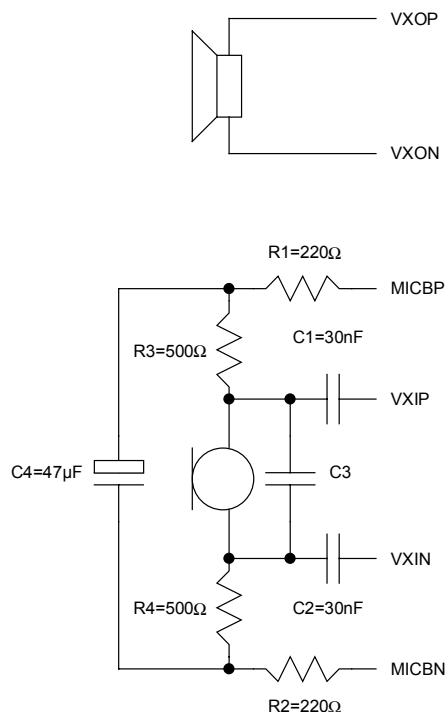

#### 5.4.6.1 Reset timing (external reset)

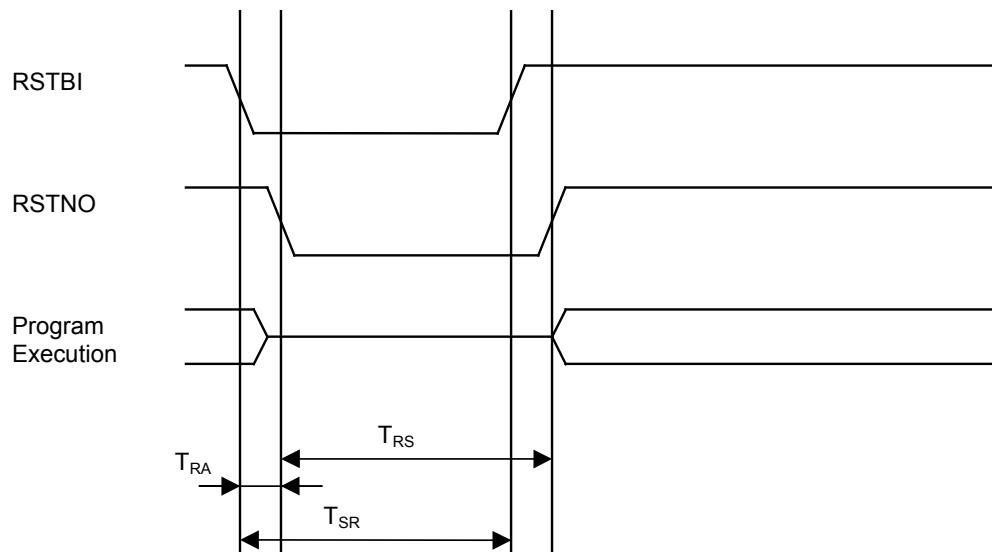

In order to make sure that an external reset is detected correctly by the firmware, the host must pull RSTBI down sufficiently long time. The exact timing requirements are indicated in Figure 7.

Figure 7: Reset Timing

| Parameter | min.        | max.       |

|-----------|-------------|------------|

| $T_{RA}$  |             | 11 $\mu$ s |

| $T_{RS}$  | 100 ms      | 860 ms     |

| $T_{SD}$  | 18 $\mu$ s  | 100 ms     |

| $T_{SH}$  | 100 $\mu$ s |            |

The host hardware can be sure to generate external reset pulses of sufficient length, if

- either it observes the RSTNO signal and keeps the RSTBI signal LOW at least 100ms after the rising edge of RSTNO, or

- it applies a RSTBI pulse of at least 960ms.

The latter method is simpler but also slower.

$T_{RS}$  specifies the duration of the reset pulse. It depends on component tolerances, temperature and operating voltage and therefore may be variable.

$T_{SD}$  specifies the time where the status of BOOTx lines is latched. It depends on the firmware implementation and may vary between different firmware versions.

#### 5.4.6.2 Short Reset

A short reset is a low-active RSTBI pulse that is shorter than the RSTNO pulse.

Figure 8: Short Reset

| Parameter | min. | max. |

|-----------|------|------|

| $T_{SR}$  | 5ms  | 50ms |

Although it is triggered by the RSTBI signal the firmware of the HW 86022 treats a short reset as an internal reset. The host hardware may use this feature to emulate a power-up reset to the HW 86022. A short reset will lead to normal start of firmware unless BOOT0 and BOOT1 pins are pulled low from external circuitry. In this case the download mode is entered.

#### 5.4.6.3 Activation of Download and Configuration Mode

During any reset (internal or external) interface signals BOOT0, BOOT1 overload the normal function of these signals (CTSO, DSRO). They are used to activate download mode if pulled low from external circuitry.

If case of an external reset (RSTBI held low after rising edge of RSTNO) the BOOT2 and BOOT3 signals are evaluated in order to activate configuration mode or normal start of firmware (data mode).

The following table gives an overview on how the modes are selected. Combinations other than specified must not be applied.

| RSTBI | BOOT0 (CTSO) | BOOT1 (DSRO) | BOOT2 (RTSI) | BOOT3 (DTRI) | Function                                  |

|-------|--------------|--------------|--------------|--------------|-------------------------------------------|

| X     | LOW          | LOW          | X            | X            | Enable firmware <b>download mode</b>      |

| LOW   | HIGH         | HIGH         | HIGH         | HIGH         | Enable firmware <b>configuration mode</b> |

| LOW   | HIGH         | HIGH         | LOW          | HIGH         | Enable firmware <b>data mode</b>          |

| HIGH  | HIGH         | HIGH         | X            | X            | (normal operation)                        |

X: don't care

RSTBI, BOOT0, BOOT1, BOOT2 and BOOT3 are latched at the rising edge of RSTNO +  $T_{SD}$ . All signals have internal pull-ups and may be left unconnected if not used. In order to avoid unwanted switches to firmware download mode, the host device shall take care that BOOT0 and BOOT1 are driven low only together with RSTBI driven low. For normal firmware start RSTBI shall not be held low. In case of external reset BOOT2 and BOOT3 shall be used as normal RS 232 signals after RSTBI is released.

The evaluation kit HW 86916 includes adapter boards that support firmware download and configuration mode reset from a standard PC COM port as well as the required software tools.

#### 5.4.6.4 Precautions to avoid Reset Problems

The host hardware must assure an appropriate environment that avoids unwanted resets. The reset behaviour is a main source of integration problems and requires specific attention.

Please make sure that the following conditions are fulfilled during operation:

- V3P3 must not drop below 2.63 V. This will trigger a low voltage reset.

- At power-up the RSTBI signal should be either high impedance (not connected) or logic HIGH if data mode is required. A logic LOW during power-up may be interpreted as external reset and may result in unwanted mode selection.

- If the host hardware is not able to assure the appropriate RSTBI level during power-up, it may use a short reset afterwards to emulate a power-up reset.

- DSRO and CTSO are outputs of the HW 86022. The host hardware must never actively drive these signals for any other purpose than entering the download mode. They shall only be driven from the host during RSTBI = low.

- The external reset is triggered by the falling edge of the RSTBI signal. Make sure that the fall time (90% down to 10% of V3P3) is less than 50ns.

#### 5.4.7 I2C Interface

I2C Interface is provided by the hardware. This feature is not supported in standard firmware releases.

#### 5.4.8 PCM Interface

PCM Interface is provided by the hardware.

| Signal  | I/O | Description                    |

|---------|-----|--------------------------------|

| PCMCLK  | I/O | PCM clock signal in/out        |

| PCMFS0  | I/O | PCM frame sync 0 in/out        |

| PCMFS1  | I/O | PCM frame sync 1 strobe in/out |

| PCMDIN  | I/O | PCM data in/out                |

| PCMDOUT | I/O | PCM data out/out               |

PCMDIN and PCMDOUT are open drain outputs or inputs without internal pull-ups. External pull-up resistors are required for operation.

This feature is not supported in standard firmware release.

#### 5.4.9 General Purpose I/O

HW 86022 provides 12 general purpose I/O pins GPIO1 to GPIO12. They are enabled by firmware. Since most signals are multiplexed with other interface signals, certain restrictions to the usage of GPIO signals apply.

This feature is not supported in standard firmware release.

#### 5.4.10 LED interface

LED0 and LED1 outputs are provided. They may be used to control two LEDs to display connection and configuration mode and data activity.

| Signal | State | Description |

|--------|-------|-------------|

| LED0   | LOW   | LED0 off    |

|        | HIGH  | LED0 on     |

| LED1   | LOW   | LED1 off    |

|        | HIGH  | LED1 on     |

| LED0                                                                                | LED1                                                                              | Meaning                                                                     |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| •                                                                                   | •                                                                                 | Power off condition or firmware download                                    |

|  • | •                                                                                 | Power on, not connected state related to higher protocol level (slow blink) |

|    | •                                                                                 | Connection to base station established, flickers while data is transmitted. |

| •                                                                                   |  | Device has entered configuration mode.                                      |

Note that current capability is limited so that an external LED driver may be required.

This functionality is deactivated by default and must be activated by software (for details see command „SPUI“ in HW 86022 Firmware Manual).

#### 5.4.11 Bus Interface

The bus interface allows for external peripherals to be accessed by the module. The 8-bit data bus and 5-bit address bus, together with control signals, including chip select, DMA and interrupt signals allows for a variety of external peripherals to be accessed by the module.

| Signal   | I/O | Description                          |

|----------|-----|--------------------------------------|

| A0 .. A5 | O   | Address bus                          |

| D0 .. D7 | I/O | Data bus                             |

| RDN      | O   | Read signal, active low              |

| WRN      | O   | Read signal, active low              |

| EXTCS    | O   | Chip select signal, active low       |

| EXTINT   | I   | Interrupt request signal, active low |

| PIWRDY   | I   | Parallel Interface Write Ready       |

| PIRDREQ  | O   | Parallel Interface Read Request      |

This feature is not supported in standard firmware release.

### 5.4.12 RF Interface

RF Interface provides two antenna connections.

The used antenna ports 0 or 1 can be configured by software. In addition the module supports antenna diversity. During reception of data, the module measures the signal strength on both antennas and activates the antenna with highest level for reception of a data packet. This will significantly improve operation for example in multipath environments, utilising the effect that fading is space dependant and one of the two antennas will most probably experience less fading than the other. See HW 86022 Firmware Manual for details on configuration.

The coaxial connector used on the module is a Hirose U.FL series connector, type U.FL-R-SMT, reference no. CL331-0471-0. Refer to [www.hirose.com](http://www.hirose.com) for details.

Adequate cable sets are available with the Hirose connectors already mounted. Contact Höft & Wessel AG for accessories.

On the antenna 0 and 1 solder through holes, a wire antenna may be attached if no external antenna shall be used. The attached antenna can be a quarter wavelength monopole with a length of approx. 38 mm.

Figure 9: Antenna Ports

**NOTE:**

**i** The limited modular approval according to FCC and IC regulations does only cover the use of the attached wire antenna. The antenna terminals marked with \* are for use in Europe only.

**NOTE:**

**Do not use the through hole connection and the coaxial connector of one antenna port at the same time.**

**NOTE:**

**Use ESD safe environments for soldering on antenna ports.**

The HW 86022 module comes with one wire antenna mounted on Antenna 1 solder through hole.

Figure 10: HW 86022 with wire antenna mounted on ANT1 port.

**Wire antenna specification:**

|                    |             |

|--------------------|-------------|

| Length:            | 30 mm max.  |

| Diameter:          | 1.2 mm typ. |

| Projection top:    | 3.0 mm max. |

| Projection bottom: | 2.0 mm max. |

## 6. Specific Integration Topics

### 6.1 Power Supply

A limited power source acc. to EN 60950-1, section 2.5, shall be used to supply the module. In USA a class 2 power source (UL 60950-1, UL 1310) is an adequate solution.

There are two power supply rails: V3P3 supplies digital section including processor, memories and DECT baseband with a medium current draw, while VBATP supplies the RF transceiver and power amplifier with a high peak pulsed current draw.

Especially the VBATP power supply must be chosen so that the maximum current during transmit pulses can be delivered. Keep in mind that an antenna which is not sufficiently matched to the transmitter impedance may significantly increase the transmitter current draw.

### 6.2 Range

The range of a wireless system is on one hand determined by the transmitter power, the receiver sensitivity and the gain of the antennas used. The significant factor is the attenuation of the radio path. This attenuation is a minimum in open space, i.e. a maximum range can be achieved here. In an industrial environment for example the radio path may be determined by huge obstacles which lead to strong attenuation of radio signals. In addition, reflections occur on objects within the radio path which lead to multi-path propagation. I.e. multiple signals that reach the receiver out of phase will lead to an additional attenuation referred to as fading.

Therefore the range that can be covered with Data-Unwired FHSS systems depends on the application. However, typically values are:

- up to 60 m inside buildings

- up to 300 m outside buildings

- up to 1000 m and more under ideal conditions (line of sight, clear Fresnel zone)

Note that for extended range operation the receiver synchronisation window, must be increased by software. See command "SPSYWD" in HW 86022 Firmware Manual for details.