# UAA3537G

Low power GSM/GPRS multi-band transceiver

Rev. 0.09 — 6 January 2005

Preliminary Specification

## 1. General description

The UAA3537 is a fully-integrated GSM hand-held transceiver

## 2. Features

- Multiple band application (850, 900, 1800 and 1900 MHz frequency bands).

- Low noise and wide dynamic range low IF receiver

- GPRS multi slot class 12 capable

- More than 3 dB on chip image rejection in receive

- More than 68 dB gain control range in receive

- Direct-up conversion in transmit

- Fully-integrated fractional-N RF-synthesizer with AFC control possibility

- Fully-integrated RF VCO with integrated supply regulator

- semi-integrated reference oscillator with integrated supply regulator

- Fully differential design to minimize cross-talk and spurs

- Functional down to 2.4 V and up to 3.0 V

- Three output to control RF frontend switches (pin diodes)

- 3-wire serial bus interface

- HVQFN40 package

## 3. Applications

- GSM 850 MHz, GSM 900 MHz, DCS 1800 MHz and PCS 1900 MHz hand-held transceiver.

## 4. Quick reference data

Table 1: Quick reference data

| Symbol           | Parameter                     | Conditions | Min | Typ | Max | Unit |

|------------------|-------------------------------|------------|-----|-----|-----|------|

| V <sub>CC</sub>  | Supply voltage                | note 1     | 2.4 | 3.0 |     | V    |

| T <sub>amb</sub> | operating ambient temperature |            | -30 | 70  |     | °C   |

[1] for V<sub>CC</sub> <2.7 V only functionality is guaranteed, AC characteristics are not guaranteed

**PHILIPS**

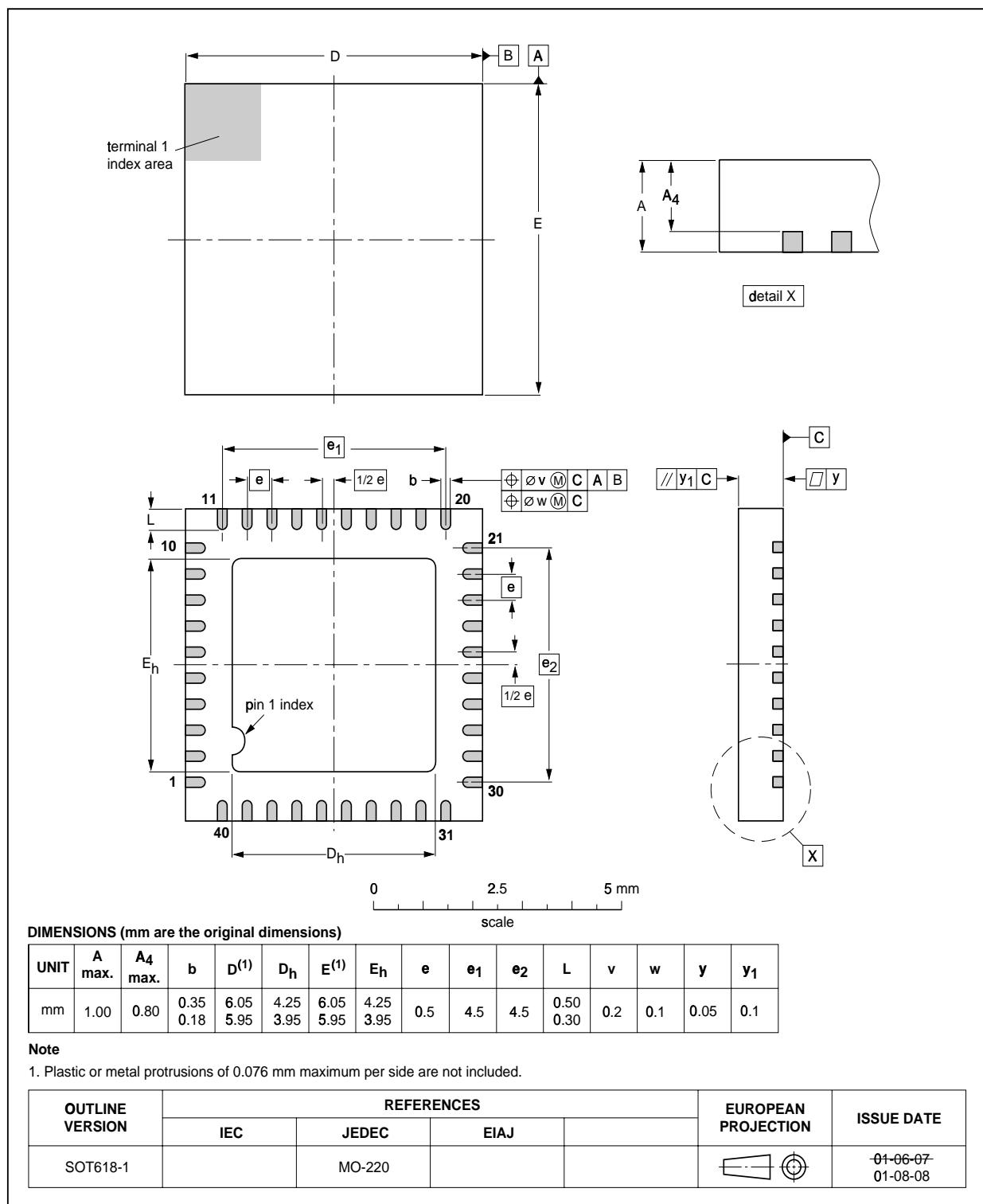

## 5. Ordering information

Table 2: Ordering information

| Type number | Package |                                                       | Version  |

|-------------|---------|-------------------------------------------------------|----------|

|             | Name    | Description                                           |          |

| UAA3537GHN  | HVQFN40 | micro leadframe package; 40 leads; body 6x 6x 0.85 mm | SOT618-1 |

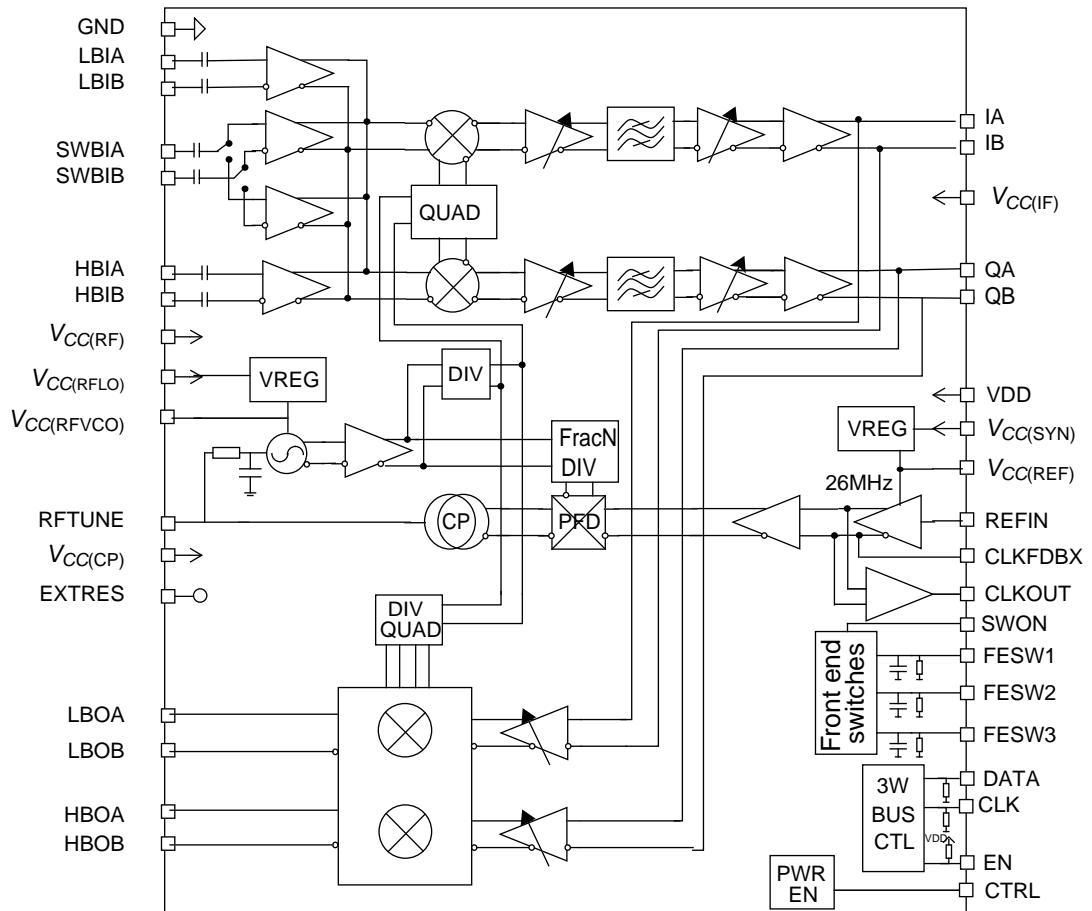

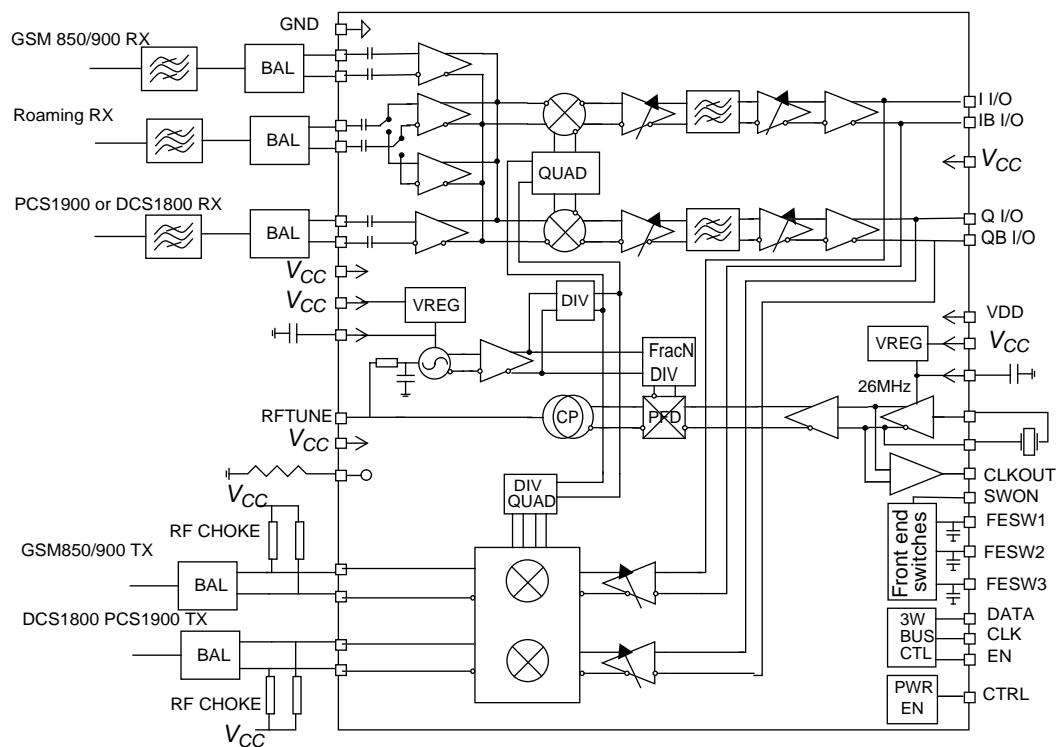

## 6. Block diagram

Fig 1. Block diagram.

## 7. Pinning information

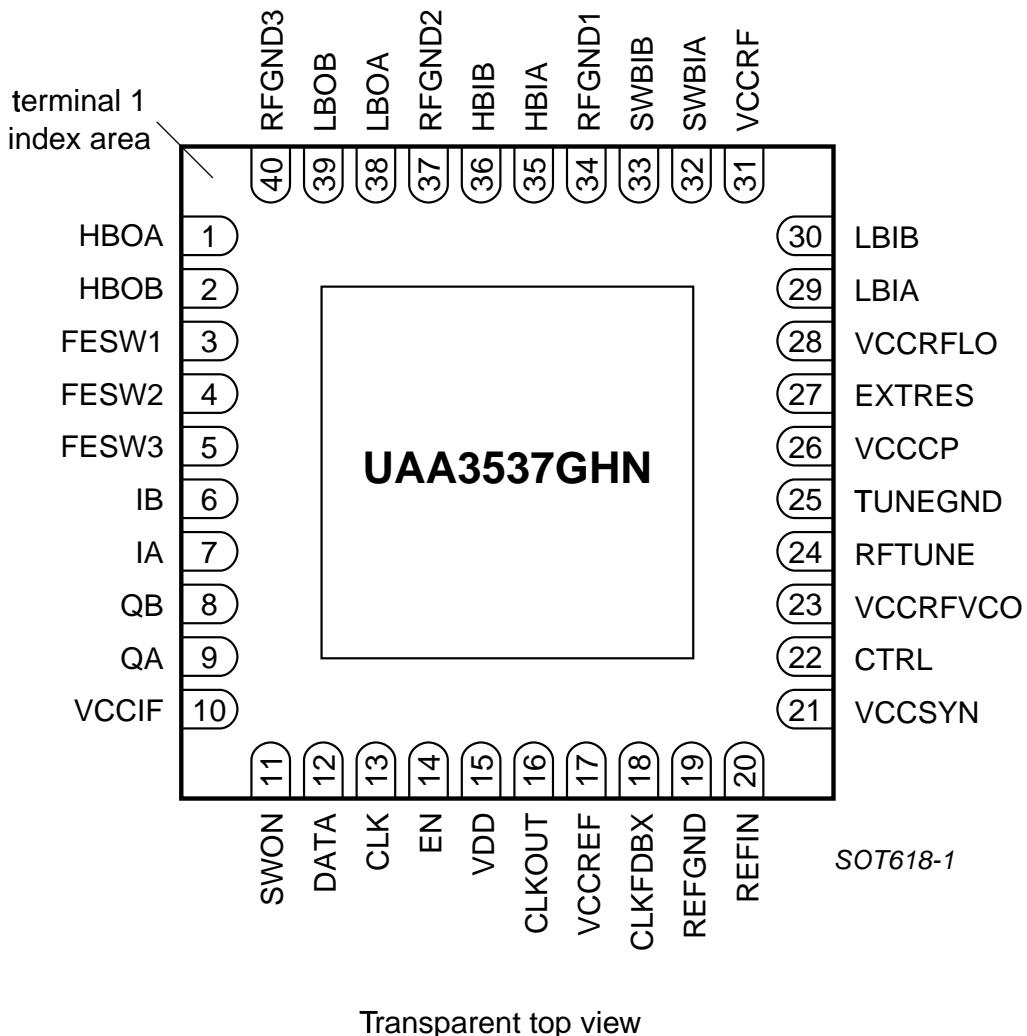

### 7.1 Pinning

Fig 2. Pin configuration (Transparent top view)).

### 7.2 Pin description

Table 3: Pin description

| Symbol | Pin | Description                         |

|--------|-----|-------------------------------------|

| HBOA   | 1   | DCS1800 and PCS1900 bands RF output |

| HBOB   | 2   | DCS1800 and PCS1900 bands RF output |

| FESW1  | 3   | front end switch control output     |

| FESW2  | 4   | front end switch control output     |

| FESW3  | 5   | front end switch control output     |

| IB     | 6   | baseband input-output; I path       |

**Table 3: Pin description...continued**

| Symbol          | Pin | Description                                              |

|-----------------|-----|----------------------------------------------------------|

| IA              | 7   | baseband input-output; I path                            |

| QB              | 8   | baseband input-output; Q path                            |

| QA              | 9   | baseband input-output; Q path                            |

| $V_{CC(IF)}$    | 10  | IF supply                                                |

| SWON            | 11  | front end switch control input                           |

| DATA            | 12  | 3-wire bus; DATA input                                   |

| CLK             | 13  | 3-wire bus; CLK input                                    |

| EN              | 14  | 3-wire bus; ENABLE control pin                           |

| VDD             | 15  | digital supply                                           |

| CLKOUT          | 16  | reference oscillator output                              |

| $V_{CC(REF)}$   | 17  | reference regulator output and reference supply          |

| CLKFDBX         | 18  | reference oscillator feedback                            |

| REFGND          | 19  | GND for reference oscillator                             |

| REFIN           | 20  | reference oscillator input                               |

| $V_{CC(SYN)}$   | 21  | synthesizer and reference regulator supply               |

| CTRL            | 22  | global enable control pin                                |

| $V_{CC(RFVCO)}$ | 23  | RFVCO regulator output and RF VCO supply                 |

| RFTUNE          | 24  | tuning input of RF VCO                                   |

| TUNEGND         | 25  | ground for RF VCO tuning                                 |

| $V_{CC(CP)}$    | 26  | RF charge pump supply                                    |

| EXTRES          | 27  | reference resistor for RF PLL charge pump gains          |

| $V_{CC(RFLO)}$  | 28  | RF LO and RFVCO regulator supply                         |

| LBIA            | 29  | receiver GSM850/900 RF input                             |

| LBIB            | 30  | receiver GSM850/900 RF input                             |

| $V_{CC(RF)}$    | 31  | RF front end and transmit part supply                    |

| SWBIA           | 32  | receiver DCS1800/PCS1900 or GSM850/900 switched RF input |

| SWBIB           | 33  | receiver DCS1800/PCS1900 or GSM850/900 switched RF input |

| RFGND1          | 34  | ground for front end                                     |

| HBIA            | 35  | receiver DCS1800 or PCS1900 bands RF input               |

| HBIB            | 36  | receiver DCS1800 or PCS1900 bands RF input               |

| RFGND2          | 37  | ground for front end                                     |

| LBOA            | 38  | GSM850 and GSM900 RF output                              |

| LBOB            | 39  | GSM850 and GSM900 RF output                              |

| RFGND3          | 40  | ground for front end                                     |

## 8. Functional description

### 8.1 Receiver

The receiver consists of two distinct parts, the RF receiver front-end and the IF section. The RF receiver front-end amplifies the GSM850 (869-894) GSM900 (925-960 MHz), DCS1800 (1805-1880 MHz) or PCS1900 (1930-1990 MHz) aerial signal, converts the chosen channel down to a low IF of -100 kHz, and provides in addition more than 35 dB image suppression. Four LNAs are available on chip and can be configured to allow 3 bands (low, high and switched). The switched LNA will be used for roaming in different countries. Some selectivity is provided at this stage by an on-chip low-pass filter, and channel selectivity is provided by means of a high performance integrated band-pass filter. The IF section further amplifies the wanted channel, performs gain control to tune the output level to the desired value and rejects DC. This DC rejection is realised with an active high pass circuit and operates either continuously or keeps the acquired offset correction during the burst depending on the programming.

### 8.2 Transmitter

The transmitter is fully differential using a direct-up conversion architecture. It consists of a single side band power up mixer. Gain is set over 6 dB via the 3-wire serial programming bus. The fully-integrated VCO and the power mixer are designed to achieve LO suppression, quadrature phase error, quadrature amplitude balance and low noise floor specifications.

### 8.3 Local oscillator

The local oscillator (LO) signals required are provided by an on chip VCO for operation of the receive and transmit sections. The VCO is fully-integrated and self calibrating to reduce manufacturing tolerances. It consists of 64 different frequency ranges that are selected internally depending on frequency programming. The frequencies of the RF VCO are set by an internal fractional-N synthesiser PLL circuit, which are programmable via a 3-wire serial bus. Comparison frequency is 26 MHz (24 Hz step programmability) derived from the 26 MHz reference signal which is generated from the semi-integrated reference oscillator. The quadrature phase RF LO signals required for IQ mixers are generated internally.

### 8.4 Reference Oscillator

An amplifier is integrated to build a crystal oscillator. Externally only a quartz and few passive components are needed. 26 MHz is the reference frequency. It is turned on when the supply voltage  $V_{CC(SYN)}$  is applied. After buffering a reference clock of 26 MHz is supplied to the other parts of the system through the pin CLKOUT. An internal supply voltage regulator using  $V_{CC(SYN)}$  as input supplies the reference oscillator and minimizes parasitic couplings and pushing. AFC can be done by the fractional-N synthesiser programming or via an external varactor. Additionally a coarse AFC control with a resolution of 8 bit is integrated via switchable capacitors. The programming of the coarse AFC capacitors is maintained during sleep mode as the

register memory is supplied via the continuous digital supply VDD. The reference signal (26 MHz) can alternatively be supplied from an external module (to pin REFIN). This module can be supplied through  $V_{CC(REF)}$  pin.

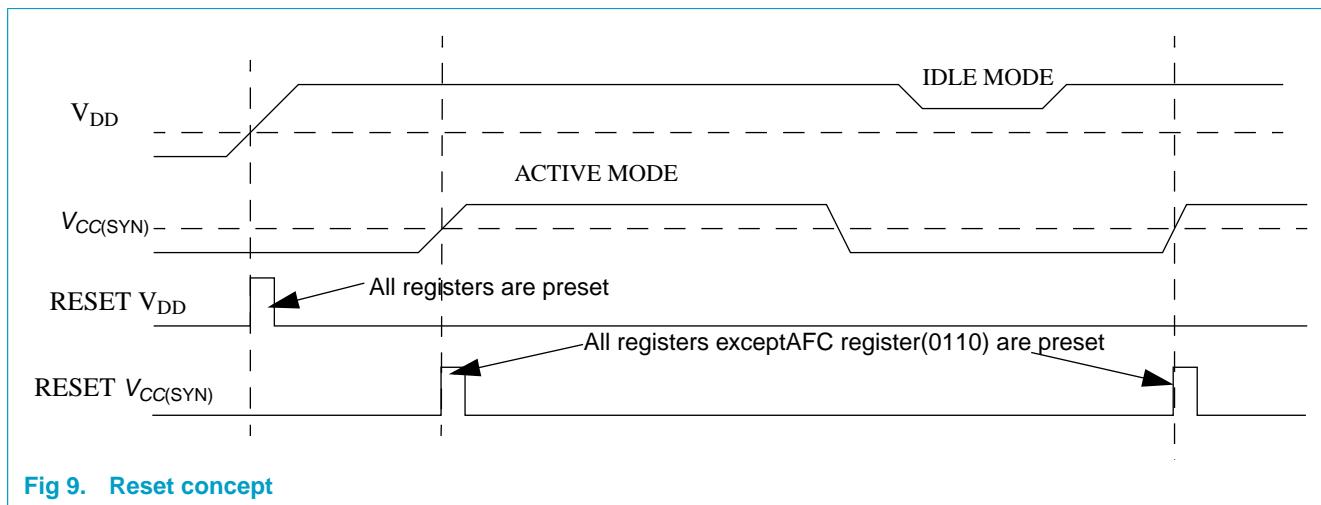

## 8.5 Control

The circuit can be powered-up into four different modes, RX, TX, SYN or REF mode, depending on supply voltages applied, on the logic level at pin CTRL and on the 3-wire bus serial programming. In RX (TX) mode, all sections required for receive (transmit) are turned on. The SYN mode is used to power-up the synthesiser and the RF-VCO prior to the RX or TX mode. In the SYN mode, some internal LO buffers are also powered-up such that VCO pulling is minimized when switching on the receiver or the transmitter. The reference oscillator (REF mode) is turned on by applying the supply voltage. Additionally band selection is done using the 3-wire bus serial programming allowing the proper enabling of the LNAs

## 8.6 Control of front end switches

Three output are provided to drive RF switches of the phone, e.g. for switching between bands.

## 9. Limiting values

**Table 4: Limiting values**

*In accordance with the Absolute Maximum Rating System (IEC 60134).*

| Symbol    | Parameter                     | Conditions                                              | Min  | Max  | Unit |

|-----------|-------------------------------|---------------------------------------------------------|------|------|------|

| $T_{stg}$ | storage temperature           |                                                         | -40  | +150 | °C   |

| $T_{amb}$ | operating ambient temperature |                                                         | -30  | +70  | °C   |

| $P_{tot}$ | total power dissipation       |                                                         |      | 500  | mW   |

| $V_{CC}$  | analog supply voltage         | on all $V_{CC}$ ,<br>LBOA,<br>LBOB,<br>HBOA and<br>HBOB | -0.3 | 3.3  | V    |

| $V_{DD}$  | digital supply voltage        | on $V_{DD}$                                             | -0.3 | 2.75 | V    |

## 10. Thermal characteristics

**Table 5: Thermal characteristics**

| Symbol        | Parameter                                                                               | Conditions  | Value | Unit |

|---------------|-----------------------------------------------------------------------------------------|-------------|-------|------|

| $R_{th(j-a)}$ | thermal resistance from junction to ambient with exposed diepad soldered on 4-layer PCB | in free air | 25    | K/W  |

## 11. Characteristics

**Table 6: DC Characteristics**

$V_{CC} = 2.7V$ ;  $V_{DD} = 1.8V$ ;  $T_{amb} = 25^{\circ}C$ ; unless otherwise stated

| Symbol                                                                                                                                                                                    | Parameter                                             | Conditions                                                                | Min    | Typ                   | Max      | Unit    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------|--------|-----------------------|----------|---------|

| <b>Pin <math>V_{CC(RF)}</math>, <math>V_{CC(IF)}</math>, <math>V_{CC(RFLO)}</math>, <math>V_{CC(SYN)}</math>, <math>V_{CC(CP)}</math>, LBOA, LBOB, HBOA and HBOB, <math>V_{DD}</math></b> |                                                       |                                                                           |        |                       |          |         |

| $V_{CC}$                                                                                                                                                                                  | Analog supply range                                   | note 1                                                                    | 2.4    | 2.8                   | 3.0      | V       |

| $V_{DD}$                                                                                                                                                                                  | Digital supply range                                  | note 2                                                                    | 1.3    | 1.8                   | 2        | V       |

| $I_{CCREF}$                                                                                                                                                                               | supply current REF mode                               | reference oscillator active ( $V_{CC(SYN)} = 2.7V$ )                      | -      | 4.7                   | 6.0      | mA      |

| $I_{CCSYN}$                                                                                                                                                                               | supply current SYN mode                               | SYN mode active, $SYNTX=0$<br>SYN mode active, $SYNTX=1$                  | -<br>- | 31<br>42              | 40<br>52 | mA      |

| $I_{CCRX}$                                                                                                                                                                                | supply current RX mode                                | RX and SYN mode active;<br>FESW off                                       | -      | 65                    | 82       | mA      |

| $I_{CCTX;LB}$                                                                                                                                                                             | Low band supply current TX mode                       | TX and SYN mode active;<br>FESW off; $G1TX1 = 0$ ;<br>$BND2 = 0$ ; note 4 | -      | 120                   | 145      | mA      |

| $I_{CCTX;HB}$                                                                                                                                                                             | High band supply current TX mode                      | TX and SYN mode active;<br>FESW off; $G1TX1 = 1$ ;<br>$BND2 = 1$ ; note 4 | -      | 110                   | 135      | mA      |

| $I_{IN\_TX}$                                                                                                                                                                              | supply current on TX outputs (LBOA, LBOB, HBOA, HBOB) |                                                                           | -      | 34                    | -        | mA      |

| $I_{IDLE}$                                                                                                                                                                                | supply current in idle mode                           | $V_{CC} = 0$ or open, $V_{DD} = 1.8V$                                     | -      | 10                    | 30       | $\mu A$ |

| $I_{DD}$                                                                                                                                                                                  | digital supply current                                | SYN mode active                                                           | -      | 1                     | 2        | mA      |

| <b>Pins IA, IB, QA and QB</b>                                                                                                                                                             |                                                       |                                                                           |        |                       |          |         |

| $V_{CM\_IQ}$                                                                                                                                                                              | common mode IQ voltage range                          | $(V_{IA}+V_{IB})/2$ or $(V_{QA}+V_{QB})/2$ ;<br>note 3                    | 1.15   | 1.25                  | 1.35     | V       |

| <b>Pin <math>V_{CC(REF)}</math></b>                                                                                                                                                       |                                                       |                                                                           |        |                       |          |         |

| $V_{CC(REF)}$                                                                                                                                                                             | internal supply voltage of reference oscillator       | $V_{CC(SYN)} \geq 2.7V$ ,<br>$-30 \leq T_{amb} \leq 70^{\circ}C$          | 2.3    | 2.4                   | 2.5      | V       |

| $I_{OUTREF}$                                                                                                                                                                              | output current                                        |                                                                           | 2      | -                     | -        | mA      |

| <b>Pin <math>V_{CC(RFVCO)}</math></b>                                                                                                                                                     |                                                       |                                                                           |        |                       |          |         |

| $V_{CC(RFVCO)}$                                                                                                                                                                           | internal supply voltage of RF VCO                     |                                                                           | -      | 2.0                   | -        | V       |

| <b>Pin EXTRES</b>                                                                                                                                                                         |                                                       |                                                                           |        |                       |          |         |

| $V_{EXTRES}$                                                                                                                                                                              | reference voltage                                     | $R_{ext} = 3.3 \text{ k}\Omega$ (1%)                                      | -      | 0.35                  | -        | V       |

| <b>Pins REFIN, CLKFDBX, CLKOUT</b>                                                                                                                                                        |                                                       |                                                                           |        |                       |          |         |

| $V_{REFIN}$                                                                                                                                                                               | intern. supplied DC input voltage                     |                                                                           | 1.0    | 1.1                   | 1.2      | V       |

| $V_{CLKFDBX}$                                                                                                                                                                             | DC output voltage                                     |                                                                           | 1.5    | 1.8                   | 2.1      | V       |

| $V_{CLKOUT}$                                                                                                                                                                              | DC output voltage                                     |                                                                           | -      | $V_{CC(SYN)}$<br>-1.6 | -        | V       |

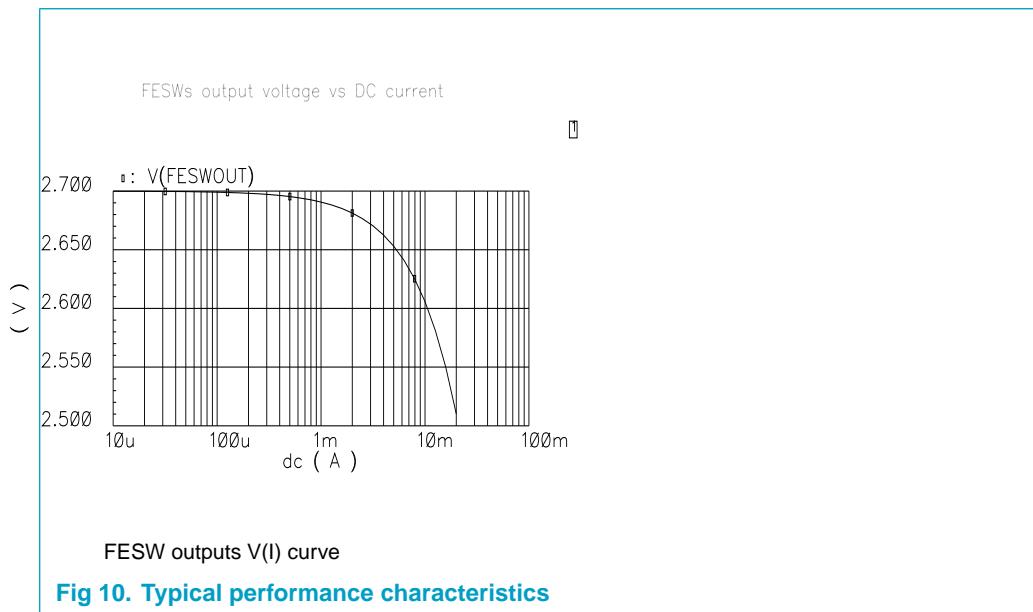

| <b>Pins FESW1, FESW2, FESW3</b>                                                                                                                                                           |                                                       |                                                                           |        |                       |          |         |

| $V_{FESW}$                                                                                                                                                                                | output voltage                                        | $I_{SOURCE} = 10 \text{ mA}$                                              | 2.5    | -                     | -        | V       |

**Table 6: DC Characteristics...continued** $V_{CC} = 2.7V$ ;  $V_{DD} = 1.8V$ ;  $T_{amb} = 25^{\circ}C$ ; unless otherwise stated

| Symbol                                                      | Parameter            | Conditions | Min          | Typ | Max          | Unit       |

|-------------------------------------------------------------|----------------------|------------|--------------|-----|--------------|------------|

| $R_{FESW}$                                                  | Resistor to GND      |            | -            | 10  | -            | k $\Omega$ |

| $C_{FESW}$                                                  | Capacitor to GND     |            | -            | 10  | -            | pF         |

| <b>Digital input levels: pins EN, DATA, CLK, CTRL, SWON</b> |                      |            |              |     |              |            |

| $V_{IH}$                                                    | logic HIGH level     |            | $0.8*V_{DD}$ | -   | $V_{DD}+0.3$ | V          |

| $V_{IL}$                                                    | logic LOW level      |            | -0.3         | -   | $0.2*V_{DD}$ | V          |

| <b>Pull up resistor: pin EN</b>                             |                      |            |              |     |              |            |

| $R_{UP}$                                                    | Resistor to $V_{DD}$ |            | -            | 1   | -            | M $\Omega$ |

| <b>Pull Down resistors: pins DATA, CLK, CTRL, SWON</b>      |                      |            |              |     |              |            |

| $R_{DOWN}$                                                  | Resistor to GND      |            | -            | 1   | -            | M $\Omega$ |

[1] For  $V_{CC} < 2.7$  V only functionnality are guaranteed, AC characteristics are not guaranteed[2] For  $V_{DD} < 1.6$  V only data retention of the internal registers is guaranteed[3] RX mode: DC supplied from the IC

TX mode: DC supplied from external[4] when FESW are on, current drawn from FESW pins will be supplied from  $V_{CC(RF)}$ \*

Table 7: RF Receiver AC Characteristics

$V_{CC} = 2.7V$ ;  $T_{amb} = -30$  to  $+70^{\circ}\text{C}$ ; unless otherwise statedMeasured in a  $50\ \Omega$  impedance system, including external input baluns and matching networks to  $50\ \Omega$ , No DC applied on input pins

| Symbol                      | Parameter                             | Conditions                                              | Min  | Typ         | Max  | Unit     |

|-----------------------------|---------------------------------------|---------------------------------------------------------|------|-------------|------|----------|

| <b>Pins LBIA and LBIB</b>   |                                       |                                                         |      |             |      |          |

| $f_{RF\text{GSM}\ 850}$     | RF input frequency range GSM850 band  |                                                         | 869  | -           | 894  | MHz      |

| $f_{RF\text{GSM}\ 900}$     | RF input frequency range GSM900 band  |                                                         | 925  | -           | 960  | MHz      |

| RIN                         | differential input resistance         | parallel RC input model<br>GSM900 band<br>GSM850 band   | -    | 120<br>120  | -    | $\Omega$ |

| CIN                         | differential input capacitance        | parallel RC input model<br>GSM900 band<br>GSM850 band   | -    | 1.75<br>1.4 | -    | pF       |

| NF                          | noise figure; max AGC gain            | notes 1 and 2                                           | -    | 3.2         | 3.7  | dB       |

| GOFF                        | LNA off-state gain difference         | bit LNA: 1 $\leftrightarrow$ 0; notes 1                 | -    | 45          | -    | dB       |

| POFF                        | LNA off-state power handling          | bit LNA = 0; notes 1 and 4                              | 6    | -           | -    | dBm      |

| <b>Pins HBIA and HBIB</b>   |                                       |                                                         |      |             |      |          |

| $f_{RF\text{DCS1800}}$      | RF input frequency range DCS1800 band |                                                         | 1805 | -           | 1880 | MHz      |

| $f_{RF\text{PCS1900}}$      | RF input frequency range PCS1900 band |                                                         | 1930 | -           | 1990 | MHz      |

| RIN                         | differential input resistance         | parallel RC input model<br>DCS1800 band<br>PCS1900 band | -    | 180<br>200  | -    | $\Omega$ |

| CIN                         | differential input capacitance        | parallel RC input model<br>DCS1800 band<br>PCS1900 band | -    | 1<br>0.5    | -    | pF       |

| NF                          | noise figure; max AGC gain            | notes 1 and 2                                           | -    | 3.2         | 3.7  | dB       |

| GOFF                        | LNA off-state gain difference         | bit LNA: 1 $\leftrightarrow$ 0; notes 1                 | -    | 45          | -    | dB       |

| POFF                        | LNA off-state power handling          | bit LNA = 0; notes 1 and 4                              | 6    | -           | -    | dBm      |

| <b>Pins SWBIA and SWBIB</b> |                                       |                                                         |      |             |      |          |

| $f_{RF\text{GSM850}}$       | RF input frequency range GSM850 band  | LNA1 = 1; LNA2 = 0                                      | 869  | -           | 894  | MHz      |

| $f_{RF\text{GSM900}}$       | RF input frequency range GSM900 band  | LNA1 = 1; LNA2 = 0                                      | 925  | -           | 960  | MHz      |

| $f_{RF\text{DCS1800}}$      | RF input frequency range DCS1800 band | LNA1 = 1; LNA2 = 1                                      | 1805 | -           | 1880 | MHz      |

| $f_{RF\text{PCS1900}}$      | RF input frequency range PCS1900 band | LNA1 = 1; LNA2 = 1                                      | 1930 | -           | 1990 | MHz      |

**Table 7: RF Receiver AC Characteristics...continued** $V_{CC} = 2.7V$ ;  $T_{amb} = -30$  to  $+70^{\circ}C$ ; unless otherwise statedMeasured in a  $50\ \Omega$  impedance system, including external input baluns and matching networks to  $50\ \Omega$ , No DC applied on input pins

| Symbol      | Parameter                                                | Conditions                                                                  | Min | Typ        | Max | Unit     |

|-------------|----------------------------------------------------------|-----------------------------------------------------------------------------|-----|------------|-----|----------|

| $RIN_{LB}$  | differential input resistance for GSM850/GSM900 bands    | parallel RC input model; LNA1 = 1; LNA2 = 0<br>GSM900band<br>GSM850 band    | -   | 110<br>110 | -   | $\Omega$ |

| $RIN_{HB}$  | differential input resistance for DCS1800/PCS1900 bands  | parallel RC input model; LNA1 = 1; LNA2 = 1<br>DCS1800 band<br>PCS1900 band | -   | 100<br>100 | -   | $\Omega$ |

| $CIN_{LB}$  | differential input capacitance for GSM850/GSM900 bands   | parallel RC input model; LNA1 = 1; LNA2 = 0<br>GSM900 band<br>GSM850 band   | -   | 1.6<br>1.5 | -   | pF       |

| $CIN_{HB}$  | differential input capacitance for DCS1800/PCS1900 bands | parallel RC input model; LNA1 = 1; LNA2 = 1<br>DCS1800 band<br>PCS1900 band | -   | 1.9<br>1.9 | -   | pF       |

| $NF_{LB}$   | noise figure; max AGC gain for GSM850/GSM900 bands       | LNA1 = 1; LNA2 = 0; notes 1 and 2                                           | -   | 3.7        | 4.2 | dB       |

| $NF_{HB}$   | noise figure; max AGC gain for DCS1800/PCS1900 bands     | LNA1 = 1; LNA2 = 1; notes 1 and 2                                           | -   | 3.7        | 4.2 | dB       |

| GOFF        | LNA off-state gain difference                            | bit LNA: 1 $\leftrightarrow$ 0; note 1                                      | -   | 45         | -   | dB       |

| $POFF_{LB}$ | LNA off-state power handling                             | LNA1 = 1; LNA2 = 0, bit LNA = 0; notes 1 and 4                              | 6   | -          | -   | dBm      |

| $POFF_{HB}$ | LNA off-state power handling                             | LNA1 = 1; LNA2 = 1, bit LNA = 0; notes 1 and 4                              | 6   | -          | -   | dBm      |

**Pins LBIA, LBIB, SWBIA, SWBIB, HBIA and HBIB**

|             |                                                          |                                     |     |     |     |     |

|-------------|----------------------------------------------------------|-------------------------------------|-----|-----|-----|-----|

| S11         | input power matching                                     | note 2                              | -   | -15 | -10 | dB  |

| $SPUR_{IN}$ | spurious power level at RF input                         | in 800 to 1000 MHz band             | -   | -   | -57 | dBm |

|             |                                                          | in 1800 to 2000 MHz band            | -   | -   | -50 | dBm |

|             |                                                          | out of preceding bands              | -   | -   | -45 | dBm |

| CP1         | 1 dB input compression point; minimum AGC gain           | $T_{amb} = 25^{\circ}C$ ; note 1    | -24 | -   | -   | dBm |

| IP3         | input referred 3rd order intercept; maximum AGC gain     | $T_{amb} = 25^{\circ}C$ ; note 1, 5 | -18 | -   | -   | dBm |

| IP2         | input referred 2nd order intercept; max. AGC gain (AGC1) | $T_{amb} = 25^{\circ}C$ ; note 6    | 40  | 50  | -   | dBm |

**Table 7: RF Receiver AC Characteristics...continued** $V_{CC} = 2.7V$ ;  $T_{amb} = -30$  to  $+70^{\circ}\text{C}$ ; unless otherwise statedMeasured in a  $50\ \Omega$  impedance system, including external input baluns and matching networks to  $50\ \Omega$ , No DC applied on input pins

| Symbol                                  | Parameter                                              | Conditions                                                                                                                                                              | Min                                      | Typ                                    | Max        | Unit                |

|-----------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------|------------|---------------------|

| Blocking <sub>LB</sub>                  | C/N ratio at blocking for GSM850/900 bands             | $T_{amb} = 25^{\circ}\text{C}$ ; $\Delta f = 3\ \text{MHz}$ ;<br>$P_w = -101\text{dBm}$ ;<br>$P_{int} = -25\text{dBm}$ ; note 1                                         | 9                                        | -                                      | -          | dB                  |

| Blocking <sub>HB</sub>                  | C/N ratio at blocking for DCS1800 and PCS1900 bands    | $T_{amb} = 25^{\circ}\text{C}$ ; $\Delta f = 3\ \text{MHz}$ ;<br>$P_w = -101\text{dBm}$ ;<br>$P_{int} = -28\text{dBm}$ ; note 1                                         | 9                                        | -                                      | -          | dB                  |

| IMrej                                   | image rejection                                        | $\Delta f_{IF} = 200\ \text{kHz}$ ; $SBD = 0$ ;<br>$T_{amb} = 25^{\circ}\text{C}$ ; note 1                                                                              | 35                                       | 45                                     | -          | dB                  |

| $\Delta G_{vRF}$                        | gain mismatch between operation of different bands     | notes 1 and 3                                                                                                                                                           | -                                        | -                                      | 2.5        | dB                  |

| <b>Pins IA, IB, QA and QB (RX mode)</b> |                                                        |                                                                                                                                                                         |                                          |                                        |            |                     |

| G <sub>vMIN</sub>                       | voltage conversion gain                                | AGC gain set to minimum; notes 1 and 3                                                                                                                                  | 22                                       | 28                                     | 34         | dB                  |

| G <sub>vMAX</sub>                       | voltage conversion gain                                | AGC gain set to maximum; notes 1 and 3                                                                                                                                  | 92                                       | 96                                     | 100        | dB                  |

| $\Delta G_{vBW}$                        | gain difference between narrow and wide bandwidth mode | RXBW 0<->1                                                                                                                                                              | -0.5                                     | 0                                      | 0.5        | dB                  |

| G <sub>vSTEP</sub>                      | voltage conversion gain step                           | note 3                                                                                                                                                                  | -                                        | 4                                      | -          | dB                  |

| $\Delta G_{vIQ}$                        | gain mismatch I and Q paths                            | note 3                                                                                                                                                                  | -                                        | -                                      | 0.5        | dB                  |

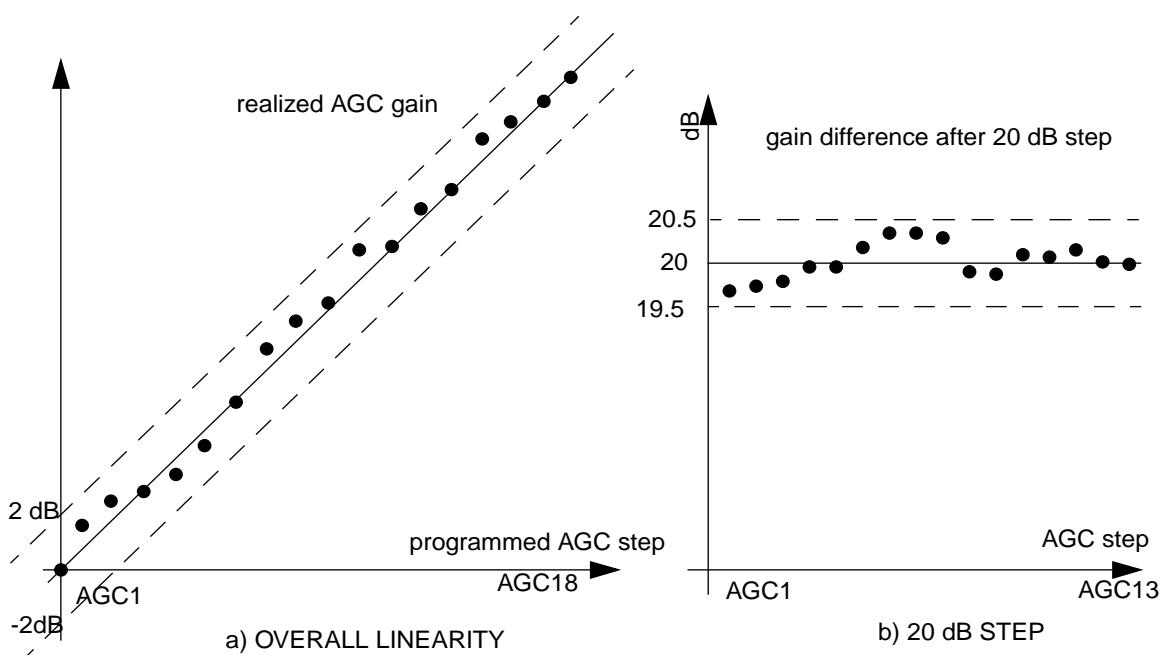

| AGC <sub>lin</sub>                      | gain control linearity                                 | note 2; Fig 3 a)<br>over any 20 dB gain range; Fig 3 b)                                                                                                                 | -2<br>-0.5                               | -<br>-                                 | 2<br>0.5   | dB                  |

| V <sub>OUT</sub>                        | maximum output voltage per pin                         | $RL = 100\ \text{k}\Omega$ differential;<br>$CL = 10\text{pF}$ differential;<br>$P_w < -34\ \text{dBm}$ ; THD < 3%                                                      | 0.75                                     | -                                      | -          | V <sub>pk</sub>     |

| V <sub>ODM_RXIQ</sub>                   | maximum differential output voltage                    | (I-IB) or (Q-QB)<br>$RL = 100\ \text{k}\Omega$ differential;<br>$CL = 10\text{pF}$ differential;<br>$P_w < -34\ \text{dBm}$ ; THD < 3%                                  | 1.5                                      | -                                      | -          | V <sub>pkdiff</sub> |

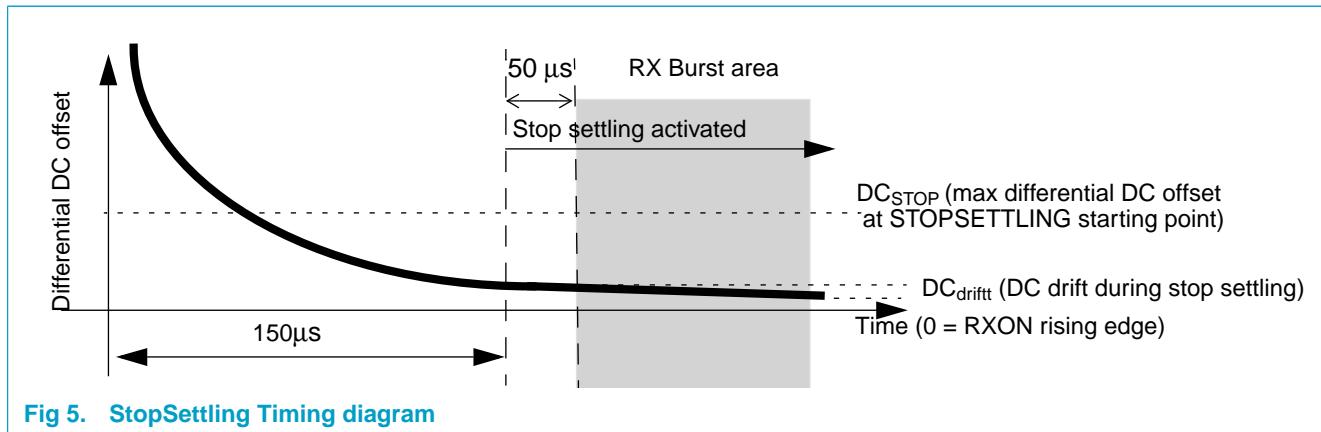

| DC <sub>offset</sub>                    | differential output offset voltage                     | 150 $\mu\text{s}$ after RXON activation                                                                                                                                 | -300                                     | -                                      | 300        | mV                  |

| DC drift                                | differential output offset voltage drift               | STOPSETL = 1; see Fig. 5<br>RX AGC = AGC1 (table 32)<br>RX AGC = AGC2<br>RX AGC = AGC3<br>RX AGC = AGC4<br>RX AGC = AGC5<br>RX AGC = AGC6 or AGC7<br>other RX AGC steps | -<br>7<br>5<br>3<br>2<br>1<br>0.5<br>0.2 | -<br>15<br>11<br>7<br>4<br>3<br>2<br>1 | -<br>mV/ms |                     |

| HP-3dB                                  | -3dB high pass corner frequency (DC notch)             |                                                                                                                                                                         | 4                                        | 6                                      | 8          | kHz                 |

**Table 7: RF Receiver AC Characteristics...continued** $V_{CC} = 2.7V$ ;  $T_{amb} = -30$  to  $+70^{\circ}C$ ; unless otherwise statedMeasured in a  $50\ \Omega$  impedance system, including external input baluns and matching networks to  $50\ \Omega$ , No DC applied on input pins

| Symbol                    | Parameter                                                      | Conditions                                     | Min | Typ | Max | Unit          |

|---------------------------|----------------------------------------------------------------|------------------------------------------------|-----|-----|-----|---------------|

| BW-3dB                    | -3dB LOW IF filter bandwidth for narrow bandwidth mode         | -100 kHz center frequency ; RXBW =0            | 220 | 240 | 260 | kHz           |

| BW-3dB <sub>HI</sub>      | -3dB LOW IF filter bandwidth for wide bandwidth mode           | -100 kHz center frequency ; RXBW =1            | 275 | 305 | 335 | kHz           |

| LP-3dB                    | -3dB low pass corner frequency of mixer output                 |                                                | -   | 470 | -   | kHz           |

| $\Delta\tau_{gd}$         | group delay variation                                          | $-170\text{ kHz} < f_{OUT} < -30\text{ kHz}$   | -   | 1.5 | 2   | $\mu\text{s}$ |

| Att <sub>narrowband</sub> | LOW IF filter attenuation (5th order) in narrow bandwidth mode | $f_{OUT} = -100\text{ kHz} \pm 200\text{ kHz}$ | 17  | 31  | -   | dB            |

|                           |                                                                | $f_{OUT} = -100\text{ kHz} \pm 400\text{ kHz}$ | 54  | 64  | -   | dB            |

|                           |                                                                | $f_{OUT} = -100\text{ kHz} \pm 600\text{ kHz}$ | 73  | 82  | -   | dB            |

| Att <sub>wideband</sub>   | LOW IF filter attenuation (5th order) in wide bandwidth mode   | $f_{OUT} = -100\text{ kHz} \pm 200\text{ kHz}$ | 10  | 19  | -   | dB            |

|                           |                                                                | $f_{OUT} = -100\text{ kHz} \pm 400\text{ kHz}$ | 45  | 54  | -   | dB            |

|                           |                                                                | $f_{OUT} = -100\text{ kHz} \pm 600\text{ kHz}$ | 64  | 73  | -   | dB            |

- [1] measured and guaranteed on evaluation board

- [2] this value includes printed circuit board and balun losses

- [3] Voltage gain defined as the differential base band RMS output voltage (either at pins IA and IB or QA and QB measured in standard load) divided by the RMS input voltage at the RF baluns.

- [4] No degradation of the LNA inputs. See application note (AN 040616/AE) for phase error degradation caused by TX power coupling to RX inputs

- [5] IP3 related to an IM3 measurement with two tones at 800 and 1600 kHz offset.

- [6] IP2 related to an IM2 measurement with two tones at 6 and 6.1 MHz offset.

Fig 3. AGC linearity

Table 8: Transmit section AC Characteristics

$V_{CC} = 2.7V$ ;  $T_{amb} = -30$  to  $+70^{\circ}\text{C}$ ; unless otherwise stated $V_{mod} = 0.5 V_{pk}$ ;  $f_{mod} = 67.7\text{kHz}$ ; I and Q signals matched; unless otherwise stated

| Symbol                                                                                   | Parameter                                                 | Conditions                                           | Min    | Typ  | Max  | Unit             |              |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|--------|------|------|------------------|--------------|

| <b>Pins IA, IB, QA and QB (mode TX)</b>                                                  |                                                           |                                                      |        |      |      |                  |              |

| $f_{mod}$                                                                                | modulation frequency range                                | 3 dB 2 <sup>nd</sup> order low pass cutoff frequency | 0.5    | -    | -    | MHz              |              |

| $\Delta\tau_{gd}$                                                                        | group delay variation                                     | $30\text{ kHz} < f_{mod} < 170\text{ kHz}$           | -      | 1.5  | 2    | $\mu\text{s}$    |              |

| $V_{mod}$                                                                                | modulation level                                          | single ended; peak value                             | -      | 0.5  | 0.55 | $V_{pk}$         |              |

| $V_{I\_TXIQ}$                                                                            | input signal amplitude                                    | differential                                         | -      | 1    | 1.1  | $V_{diff}$       |              |

| $R_{IN}$                                                                                 | dynamic input resistance                                  | single ended                                         | -      | 25   | -    | $\text{k}\Omega$ |              |

| <b>IQ Modulator; <math>f_{mod} = 67.7\text{ kHz}</math>; pins LBOA, LBOB, HBOA, HBOB</b> |                                                           |                                                      |        |      |      |                  |              |

| $P_{out;LB}$                                                                             | Low band output peak power                                | $T_{amb} = 25^{\circ}\text{C}$                       | note 1 | 5.4  | 7    | 8.6              | $\text{dBm}$ |

| $P_{out;HB}$                                                                             | High band output peak power                               | $T_{amb} = 25^{\circ}\text{C}$                       | note 1 | 1.4  | 3    | 4.6              | $\text{dBm}$ |

| $\Delta P_{out}$                                                                         | output peak power variation vs Temp                       |                                                      | note 1 | -0.4 | -    | 0.4              | $\text{dB}$  |

| $\Phi_{NOISE;LB}$                                                                        | phase noise output power density in GSM850/GSM900 bands   | Tamb=25°C; $\Delta f = 400\text{ kHz}$ ; note 1, 2   | -      | -122 | -120 | $\text{dBc/Hz}$  |              |

|                                                                                          |                                                           | Tamb=25°C; $\Delta f = 1.8\text{ MHz}$ ; note 1, 2   | -      | -126 | -124 | $\text{dBc/Hz}$  |              |

|                                                                                          |                                                           | Tamb=25°C; $\Delta f = 20\text{ MHz}$ ; note 1, 2    | -      | -162 | -    | $\text{dBc/Hz}$  |              |

|                                                                                          |                                                           | Tamb=25°C; $\Delta f = 30\text{ MHz}$ ; note 1, 2    | -      | -164 | -163 | $\text{dBc/Hz}$  |              |

| $\Phi_{NOISE;HB}$                                                                        | phase noise output power density in DCS1800/PCS1900 bands | Tamb=25°C; $\Delta f = 400\text{ kHz}$ ; note 1, 2   | -      | -118 | -116 | $\text{dBc/Hz}$  |              |

|                                                                                          |                                                           | Tamb=25°C; $\Delta f = 1.8\text{ MHz}$ ; note 1, 2   | -      | -123 | -121 | $\text{dBc/Hz}$  |              |

|                                                                                          |                                                           | Tamb=25°C; $\Delta f = 20\text{ MHz}$ ; note 1, 2    | -      | -    | -154 | $\text{dBc/Hz}$  |              |

|                                                                                          |                                                           |                                                      | -      | -170 | -    | $\text{dBc/Hz}$  |              |

| $AM_{Noise;LB}$                                                                          | AM noise output power density in GSM850/900 bands         | Tamb=25°C; $\Delta f = 20\text{ MHz}$ ; note 1       | -      | -162 | -    | $\text{dBc/Hz}$  |              |

| $AM_{Noise;HB}$                                                                          | AM noise output power density in DCS1800/PCS1900 bands    | Tamb=25°C; $\Delta f = 20\text{ MHz}$ ; note 1       | -      | -    | -    | $\text{dBc/Hz}$  |              |

| $CREJ;LB$                                                                                | Low band carrier rejection                                | $f = (F_c + f_{mod}) +/- f_{mod}$ ; note 1, 3        | -      | -37  | -30  | $\text{dBc}$     |              |

| $CREJ;HB$                                                                                | High band carrier rejection                               | $f = (F_c + f_{mod}) +/- f_{mod}$ ; note 1, 3        | -      | -35  | -28  | $\text{dBc}$     |              |

| $IM_{OUT;LB}$                                                                            | image level                                               | $f = (F_c + f_{mod}) +/- 2 * f_{mod}$ ; note 1       | -      | -45  | -37  | $\text{dBc}$     |              |

| $IM_{OUT;HB}$                                                                            | image level                                               | $f = (F_c + f_{mod}) +/- 2 * f_{mod}$ ; note 1       | -      | -45  | -37  | $\text{dBc}$     |              |

**Table 8: Transmit section AC Characteristics...continued** $V_{CC} = 2.7V$ ;  $T_{amb} = -30$  to  $+70^{\circ}C$ ; unless otherwise stated $V_{mod} = 0.5 V_{pk}$ ;  $f_{mod} = 67.7\text{kHz}$ ; I and Q signals matched; unless otherwise stated

| Symbol                  | Parameter                                            | Conditions                                                                    | Min | Typ | Max        | Unit     |

|-------------------------|------------------------------------------------------|-------------------------------------------------------------------------------|-----|-----|------------|----------|

| SPUR <sub>3fmLB</sub>   | Low band spurious level at 3*fmod offset from wanted | $f = (F_c + f_{mod}) +/- 3 * f_{mod}$ ; note 1                                | -   | -50 | -45        | dBc      |

| SPUR <sub>3fmHB</sub>   | low band spurious level at 3*fmod offset from wanted | $f = (F_c + f_{mod}) +/- 3 * f_{mod}$ ; note 1                                | -   | -50 | -45        | dBc      |

| SPUR <sub>4fmLB</sub>   | spurious level at 4*fmod offset from wanted          | $f = (F_c + f_{mod}) +/- 4 * f_{mod}$ ; note 1                                | -   | -44 | -42        | dBc      |

| SPUR <sub>4fmHB</sub>   | spurious level at 4*fmod offset from wanted          | $f = (F_c + f_{mod}) +/- 4 * f_{mod}$ ; note 1                                | -   | -44 | -42        | dBc      |

| Spur <sub>otherLB</sub> | Low band spurious level at other frequencies         | $abs(f - (F_c + f_{mod})) \geq 300\text{kHz}$ ; $f < 1.5\text{ GHz}$ ; note 1 | -   | -   | -70        | dBc      |

| Spur <sub>otherHB</sub> | High band spurious level at other frequencies        | $abs(f - (F_c + f_{mod})) \geq 300\text{kHz}$ ; $f < 2.5\text{ GHz}$ ; note 1 | -   | -   | -70        | dBc      |

| Harm <sub>LB</sub>      | Low band harmonics level                             | $G1TX1 = 0$ ; note 1<br>2* $F_c$<br>3* $F_c$                                  | -   | -   | -20<br>-10 | dBc      |

| Harm <sub>HB</sub>      | High band harmonics level                            | $G1TX1 = 1$ ; note 1<br>2* $F_c$<br>3* $F_c$                                  | -   | -   | -20<br>-15 | dBc      |

| $TX_{load, LB}$         | Low band Output load                                 |                                                                               | -   | 160 | -          | $\Omega$ |

| $TX_{load, HB}$         | High Band Output load                                |                                                                               | -   | 200 | -          | $\Omega$ |

[1] Measured at balun output

[2] Measured according to ETSI specification.

[3] lead to phase error rms better than  $3.5^{\circ}$  in HB and  $3^{\circ}$  in LB at antenna output on reference design Sy.Sol 5100.

Table 9: Synthesiser and VCO

$V_{CC} = 2.7V$ ;  $T_{amb} = -30$  to  $+70^{\circ}\text{C}$ ; unless otherwise stated

| Symbol                                                                                                                                   | Parameter                                                      | Conditions                                                     | Min  | Typ        | Max                       | Unit                     |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|------|------------|---------------------------|--------------------------|

| <b>RF-synthesizer</b>                                                                                                                    |                                                                |                                                                |      |            |                           |                          |

| $f_{RFLO}$                                                                                                                               | synthesizer frequency range                                    |                                                                | 3294 | -          | 3982                      | MHz                      |

| $f_{comp}$                                                                                                                               | comparison frequency                                           |                                                                | -    | 26         | -                         | MHz                      |

| $f_{step}$                                                                                                                               | frequency step programmability                                 | $f_{comp} = 26$ MHz at $f_{RFLO}$                              | -    | 24.8       | -                         | Hz                       |

| $\Phi_{noise}$                                                                                                                           | close-in phase noise                                           | $f = f_{RFLO} \pm 2$ kHz; note 1                               | -    | -86        | -78                       | dBc/Hz                   |

| $P_{spur}$                                                                                                                               | spur levels                                                    | $\Delta f > 400$ kHz                                           | -    | -          | -70                       | dBc                      |

| ICP                                                                                                                                      | Charge pump current range                                      | sink or source; $R_{ext}=3.3$ k $\Omega$ (1%); over VCP range; | -    | 200        | -                         | $\mu\text{A}$            |

| $K\Phi$                                                                                                                                  | phase frequency detector gain                                  | for ICP = 0.2 mA                                               | -    | 32         | -                         | $\mu\text{A}/\text{rad}$ |

| VCP                                                                                                                                      | charge pump output voltage                                     | ICP within range specified                                     | 0.4  | -          | $V_{CC(\text{CP})} - 0.4$ | V                        |

| <b>fractional-N synthesizer (<math>f_{LO} = f_{comp} * (N + 2 * K_{frac})</math>; <math>K_{frac} = K/2\exp{21} + 1/2\exp{22}</math>)</b> |                                                                |                                                                |      |            |                           |                          |

| N                                                                                                                                        | integer divider ratio                                          | $f_{comp}=26$ MHz                                              | 126  | -          | 155                       |                          |

| Kfrac                                                                                                                                    | fractional divider ratio                                       | exception see note                                             | 0.25 | -          | 0.75                      |                          |

| <b>Integrated RF oscillator pin RFTUNE</b>                                                                                               |                                                                |                                                                |      |            |                           |                          |

| Gvco                                                                                                                                     | VCO gain                                                       | $V_{tune} = 1.4$ V                                             | -    | 32         | -                         | MHz/V                    |

| $\Delta G_{(VCO * K\Phi)}$                                                                                                               | VCO gain times Chpump gain variation                           | after VCO calibration                                          | 3200 | 6400       | 9600                      | A/Vs                     |

| Rtune                                                                                                                                    | RFTUNE series resistor inside the IC                           |                                                                | -    | 15         | -                         | k $\Omega$               |

| Ctune                                                                                                                                    | parallel capacitor at VCO tuning input to ground inside the IC |                                                                | -    | 46         | -                         | pF                       |

| Vtune                                                                                                                                    | tuning voltage range                                           |                                                                | 0.4  | -          | $V_{CC} - 0.4$            | V                        |

| $\Delta f_{VCC}$                                                                                                                         | pushing                                                        | TX mode, SYNTX = 1<br>RX mode, SYNTX = 0                       | -    | -          | 5<br>10                   | MHz/V                    |

| $T_{VCO\ cal}$                                                                                                                           | VCO calibration time                                           | after synthesizer activation                                   | -    | 32         | -                         | $\mu\text{s}$            |

| <b>Low noise crystal oscillator; pins REFIN, CLKFDBX</b>                                                                                 |                                                                |                                                                |      |            |                           |                          |

| $f_{REF}$                                                                                                                                | reference frequency                                            |                                                                | -    | 26         | -                         | MHz                      |

| $R_{REFIN}$                                                                                                                              | input resistance                                               | $f_{REF} = 26$ MHz                                             | -    | 2.7        | -                         | k $\Omega$               |

| $C_{REFIN}$                                                                                                                              | input capacitance                                              | $f_{REF} = 26$ MHz                                             | -    | 0.8        | -                         | pF                       |

| $R_{CLKFDBX}$                                                                                                                            | output resistance                                              | $f = 26$ MHz; CAFC0/.../7 = 0<br>$f = 26$ MHz; CAFC0/.../7 = 1 | -    | 900<br>600 | -                         | $\Omega$                 |

| $G_v$                                                                                                                                    | small signal voltage gain (REFIN, CLKFDBX)                     | $f=2.6$ MHz; CAFC 0/.../7 = 1;<br>Pin < -42 dBm; note 2        | -    | 26         | -                         | dB                       |

| $V_{IN(REFIN)}$                                                                                                                          | input voltage level                                            | note 1                                                         | 300  | -          | -                         | mVpp                     |

| $V_{CLKFDBX}$                                                                                                                            | limiting output voltage swing                                  | note 1                                                         | -    | 1500       | -                         | mVpp                     |

Table 9: Synthesiser and VCO...continued

$V_{CC} = 2.7V$ ;  $T_{amb} = -30$  to  $+70^{\circ}C$ ; unless otherwise stated

| Symbol                                                             | Parameter                                        | Conditions                                                                                              | Min  | Typ  | Max  | Unit            |

|--------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|-----------------|

| SPUR <sub>OUT</sub>                                                | Spurious emission                                | $f = 2*f_{ref}$ , note 1                                                                                | -    | -    | -20  | dBc             |

|                                                                    | Spurious emission                                | non harmonics, note 1                                                                                   | -    | -    | -70  | dBc             |

| <b>Coarse AFC</b>                                                  |                                                  |                                                                                                         |      |      |      |                 |

| C <sub>CAFC,LO</sub>                                               | CLKFDBX output capacitance LO                    | CAFC 0/.../7 = 0                                                                                        | 13.5 | 15.5 | 17.5 | pF              |

| C <sub>CAFC,HI</sub>                                               | CLKFDBX output capacitance HI                    | CAFC 0/.../7 = 1                                                                                        | 30   | 36   | 42   | pF              |

| C <sub>CAFC,LSB</sub>                                              | LSB of coarse AFC capacitor                      | CAFC 1/.../7 = 0<br>CAFC0 0 <-> 1                                                                       | 61   | 80   | 96   | fF              |

| f <sub>step,XO</sub>                                               | CAFC monotonicity                                | CAFC -> CAFC-1, note 1                                                                                  | 0.1  | 7    | 26   | Hz              |

| <b>Low noise crystal oscillator amplifier output signal CLKOUT</b> |                                                  |                                                                                                         |      |      |      |                 |

| f <sub>CLKOUT</sub>                                                | output frequency                                 |                                                                                                         | -    | 26   | -    | MHz             |

| R <sub>CLKOUT</sub>                                                | output resistance                                |                                                                                                         | -    | 200  | -    | $\Omega$        |

| V <sub>CLKOUT</sub>                                                | limiting output voltage swing                    | note 1, note 3                                                                                          | 0.75 | 1    | 1.5  | V <sub>pp</sub> |

| D <sub>CLKOUT</sub>                                                | duty cycle                                       | note 1                                                                                                  | 40   | -    | 60   | %               |

| $\Phi_{noise-BB}$                                                  | CLKOUT phase noise                               | $\Delta f = 2$ kHz, note 1, 3                                                                           | -    | -    | -118 | dBc/Hz          |

| Jitter <sub>XO</sub>                                               | time jitter at CLKOUT                            | notes 1, 3, 4; RMS value                                                                                | -    | -    | 60   | ps rms          |

| Greverse                                                           | reverse isolation                                | to pin CLKFDBX;<br>BW<100MHz; note 1                                                                    | 20   | 50   | -    | dB              |

| S <sub>CLKOUT, pos</sub>                                           | positive slew rate                               | between V <sub>DC</sub> - 50mV and V <sub>DC</sub> + 50mV; notes 1, 3                                   | 60   | -    | -    | mV/ns           |

| $\Delta f_{ref, CAFC}$                                             | residual frequency error                         | after coarse AFC alignment,<br>$T_{amb} = 25^{\circ}C$ , quartz specified with max $\pm 10$ ppm, note 1 | -0.5 | -    | 0.5  | ppm             |

| $\Delta f/f (T)$                                                   | frequency stability as a function of temperature | over full temperature range, quartz specified with max. +/- 20ppm, note 1                               | -24  | -    | 24   | ppm             |

| $\Delta f/f (t)$                                                   | frequency stability as a function of time        | Cumulative contribution related to the IC over 10 years, $T=25^{\circ}C$ note 1                         | -2   | -    | 2    | ppm             |

[1] These performance are measured and guaranteed on evaluation board. The 26 MHz quartz is outside the IC.  $C_{load\_quartz} = 10$  pF

[2] Gain value is also valid for 26MHz not taking into account loading by C<sub>CAFC</sub> and external capacitor

[3]  $C_{load, CLKOUT} = 20$  pF

[4] based on phase noise measurement

[5] 4 extra value are allowed for K : 80659, 209715, 1887436, 2016492

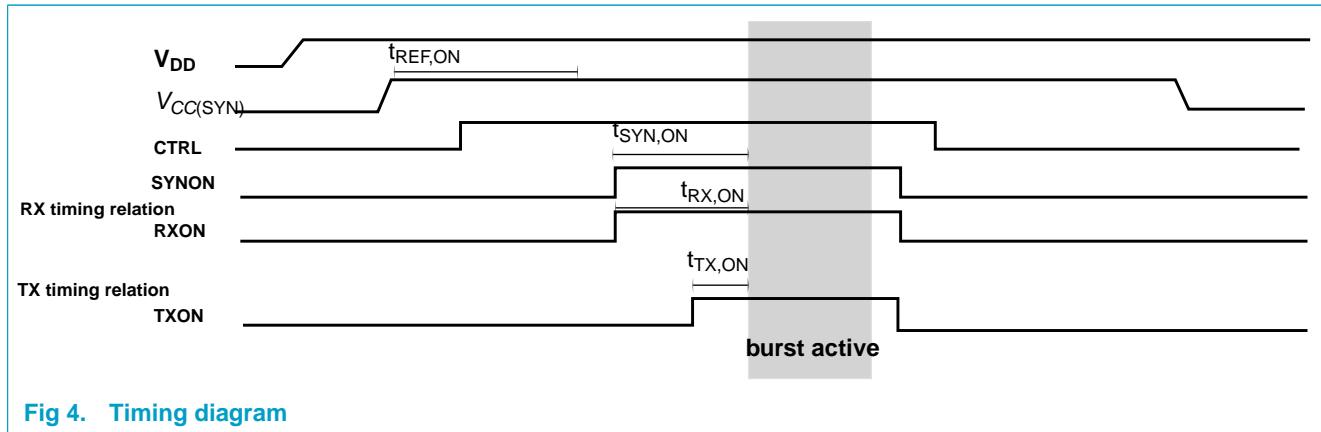

Table 10: Timing specifications

$V_{CC} = 2.7V$ ;  $T_{amb} = -30$  to  $+70^{\circ}\text{C}$ ; unless otherwise stated

| Symbol       | Parameter                            | Conditions                                                                          | Min | Typ | Max | Unit          |

|--------------|--------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| $t_{REF,ON}$ | Turn on time of Reference oscillator | to 0.1ppm of final frequency; notes 1                                               | -   | -   | 4.6 | ms            |

| $t_{SYN,ON}$ | Turn on time of RF synthesiser       | to 0.1ppm of final value of $f_{RX,out}$ ; notes 1, 2, 3                            | -   | -   | 200 | $\mu\text{s}$ |

| $t_{RX,ON}$  | RX DC settling time                  | $V_{(IA-IB)}$ to 50mV from final DC value; notes 1, 4;<br>STOPSETL=0;<br>FASTSETL=0 | -   | -   | 200 | $\mu\text{s}$ |

| $t_{TX,ON}$  | TX settling time                     |                                                                                     | -   | -   | 73  | $\mu\text{s}$ |

[1] These performances are measured and guaranteed on evaluation board.

[2] Only valid after crystal oscillator has locked

[3] Measured acc. GSM specification.

[4] A new RXDC settling is provoked when changing AGC bits G2, G3, G4 or G5. No change of RXDC settling will occur after changing AGC bits G0 and G1.

Fig 4. Timing diagram

Fig 5. StopSettling Timing diagram

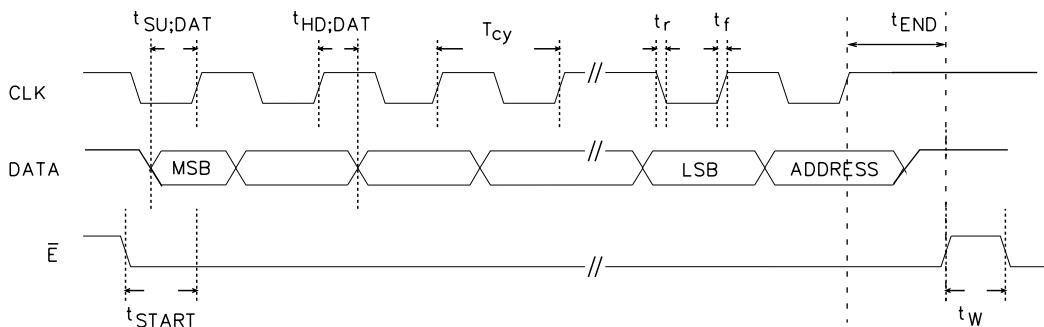

**Table 11: Serial bus timing Characteristics** $V_{DD} = 1.6$  to  $2V$ ;  $T_{amb} = -30$  to  $+70^{\circ}\text{C}$ ; unless otherwise specified.

| Symbol                                      | Parameter                          | Conditions | Min | Typ | Max | Unit |

|---------------------------------------------|------------------------------------|------------|-----|-----|-----|------|

| <b>Serial programming clock; pin CLK</b>    |                                    |            |     |     |     |      |

| tr, tf                                      | input rise and fall times          |            | -   | -   | 8   | ns   |

| t <sub>cy</sub>                             | clock period                       |            | 67  | -   | -   | ns   |

| t <sub>wclk</sub>                           | clock pulse width                  |            | 20  | -   | -   | ns   |

| <b>Enable programming; pin EN</b>           |                                    |            |     |     |     |      |

| t <sub>START</sub>                          | delay to rising clock edge         |            | 15  | -   | -   | ns   |

| t <sub>END</sub>                            | delay from last falling clock edge |            | 15  | -   | -   | ns   |

| t <sub>w</sub>                              | minimum inactive pulse width       |            | 60  | -   | -   | ns   |

| <b>Register serial input data; pin DATA</b> |                                    |            |     |     |     |      |

| t <sub>SU;DATA</sub>                        | input data to clock set-up time    |            | 15  | -   | -   | ns   |

| t <sub>HD;DATA</sub>                        | input data to clock hold time      |            | 22  | -   | -   | ns   |

**Fig 6. Serial bus timing diagram.**

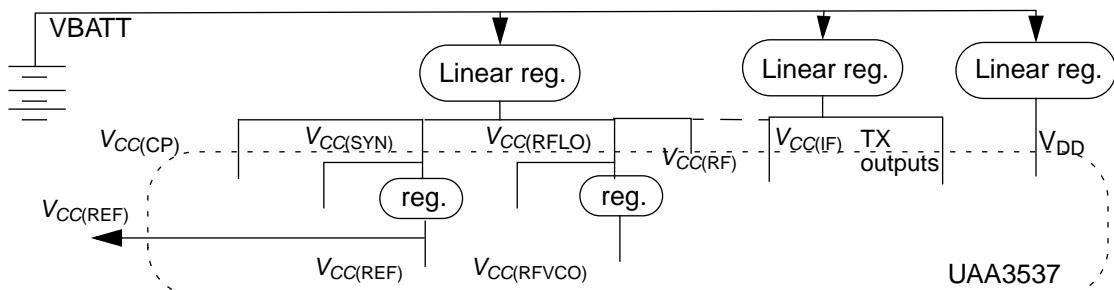

## 12. Power supply concept

Four different voltage supplies are needed

1. Digital supply ( $V_{DD}$ ) for digital inputs, for digital parts. In order to save AFC programming this supply must be kept turned on during sleep mode.

2. for the charge pump block ( $V_{CC(CP)}$ ): supply can be turned off in sleep mode

3. for TX and RX path ( $V_{CC(RFLO)}$ ): supply can be turned off in sleep mode

4. for the reference oscillator ( $V_{CC(SYN)}$ ): supply has to be turned off in sleep mode to turn off the reference oscillator

the following power supply concept is proposed:

Fig 7. Power supply concept

note:  $V_{CC(RF)}$  can be connected either to one or the other regulator (depending on the power regulator capability).

## 13. Operating Mode

### 13.1 Basic operating modes

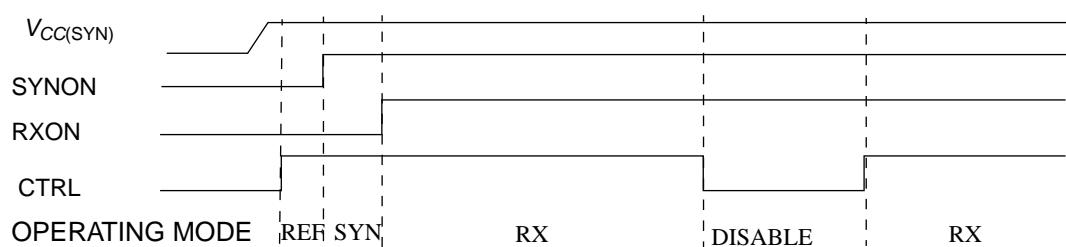

The circuit can be powered up into different modes depending on the logic level applied at pin CTRL, on supply voltage applied and on the control bits SYNON, RXON, TXON of the 3-wire bus. This defines six main modes called IDLE, REF, DISABLE, SYN, RX and TX mode.

**Table 12: Operation mode**

| MODE    | PIN CTRL | BIT SYNON | BIT RXON | BIT TXON | $V_{CC(SYN)}$ |

|---------|----------|-----------|----------|----------|---------------|

| IDLE    | X        | 0         | 0        | 0        | OFF           |

| REF     | X        | 0         | 0        | 0        | ON            |

| DISABLE | 0        | X         | X        | X        | ON            |

| SYN     | 1        | 1         | 0        | 0        | ON            |

| RX      | 1        | 1         | 1        | 0        | ON            |

| TX      | 1        | 1         | 0        | 1        | ON            |

**Table 13: Mode description**

| MODE    | DESCRIPTION                                                    |

|---------|----------------------------------------------------------------|

| IDLE    | Reference, synthesiser, receiver and transmitter are OFF       |

| REF     | Only Reference oscillator is ON                                |

| DISABLE | Transceiver is disabled reference is ON if $V_{CC(SYN)}$ is ON |

| SYN     | Synthesiser is ON; note 1                                      |

| RX      | Receiver is ON; note 2                                         |

| TX      | Transmitter is ON                                              |

[1] The synthesizer includes the LO buffers common also to the receive and transmit sections.

[2] When the receiver is on, it is possible to switch off the low noise amplifier. Refer to receiver control described below.

TX, RX or SYN mode can be disabled by means of the CTRL bit. In fact, internally CTRL bit is combined by logic AND to 3-wire bus TXON, RXON and SYNON bits and so override the operating mode. The goal of the CTRL pin is to handle the DTX and DRX GSM operation. When CTRL pin goes low, only the current mode (TX or RX) is disabled (DISABLE mode) and no internal register are reseted.

**Fig 8. CTRL bit usage, example for RX mode**

### 13.2 Transmit I/Q polarity control

The polarity of the I/Q signal for TX clock can be changed. The selection of these two modes is accomplished by means of the bit IQPOL.

**Table 14: TX I/Q polarity**

| IQPOL BIT STATUS | MODE OF OPERATION           |

|------------------|-----------------------------|

| 0                | Q signal 90 degree before I |

| 1                | I signal 90 degree before Q |

### 13.3 Front end switch control

There are three output pins FESW1, FESW2 and FESW3 that can supply current. They are controlled by means of the bit FESW1H, FESW2H, FESW3H, FESW1L, FESW2L and FESW3L combined with the control pin SWON. This allows to program a changed state to the control register and activate it later on by changing the logic state at the control pin SWON.

The switch status depends on the control bits FESWxx according to the table below

**Table 15: Front end switch status**

| FESWxH BIT STATUS | FESWxL BIT STATUS | SWON PIN STATUS | STATUS AT FESWx PIN     |

|-------------------|-------------------|-----------------|-------------------------|

| X                 | 0                 | 0               | pull down to GND        |

| X                 | 1                 | 0               | source current supplied |

| 0                 | X                 | 1               | pull down to GND        |

| 1                 | X                 | 1               | source current supplied |

### 13.4 Receiver LNAs control

The receiver includes 4 LNAs. One LNA (LBLNA) is connected to LBIA and LBIB inputs, one LNA (HBLNA) is connected to HBIA and HBIB inputs and two LNAs (SW1LNA and SW2LNA) are connected to the same inputs (SWBIA & SWBIB). LBLNA can cover GSM 850 & 900 MHz bands, HBLNA can cover DCS1800 & PCS1900 bands, SW1LNA can cover GSM 850 and 900 bands and SW2LNA can cover DCS1800 and PCS1900 bands. Only one out of those four LNA will operate at one time depending on the LNA1 and LNA2 bits status according to the table below.

**Table 16: switched LNA status**

| LNA1 BIT STATUS | LNA 2 BIT STATUS | OPERATING LNA (covered bands) |

|-----------------|------------------|-------------------------------|

| 0               | 0                | LBLNA (GSM 850 or 900)        |

| 1               | 0                | SW1LNA (GSM 850 or 900)       |

| 1               | 1                | SW2LNA (DCS1800 or PCS1900)   |