## **OPTO 3000**

Author : Felix Meier

Version : 1.0

Created : August 1, 1998 3:40 PM

Modified : May 25, 2001 9:43 AM

Ascom proprietary information. Not to be disclosed without prior written

permission from Ascom Systec Ltd.

Technical data subject to change.

## Table of Contents

|       |                                  |   |

|-------|----------------------------------|---|

| 1.    | <b>Introduction</b>              | 3 |

| 2.    | <b>Batteries</b>                 | 3 |

| 3.    | <b>Antenna System</b>            | 3 |

| 3.1   | Receiving                        | 3 |

| 3.2   | Transmitting                     | 3 |

| 4.    | <b>Preamplifier</b>              | 4 |

| 5.    | <b>Mixer</b>                     | 4 |

| 6.    | <b>Filter / Buffer</b>           | 4 |

| 7.    | <b>Speaker / Earphone Driver</b> | 4 |

| 8.    | <b>Microprocessor</b>            | 4 |

| 8.1   | XTAL / Clock                     | 4 |

| 8.2   | LO Signal Generation             | 4 |

| 8.3   | Tone Generation                  | 5 |

| 8.4   | Operating System Clock           | 5 |

| 8.5   | Watchdog                         | 5 |

| 8.6   | UART                             | 5 |

| 8.7   | EEPROM                           | 5 |

| 8.7.1 | Device Data                      | 5 |

| 8.7.2 | Identity Data                    | 5 |

| 8.8   | Operating System                 | 6 |

| 8.9   | Battery Management               | 6 |

| 8.10  | Transmitter Control              | 6 |

| 9.    | <b>User Interface</b>            | 6 |

| 9.1   | Interface Components             | 6 |

## Abbreviations

xxx a placeholder

## References

xxx a placeholder

## 1. Introduction

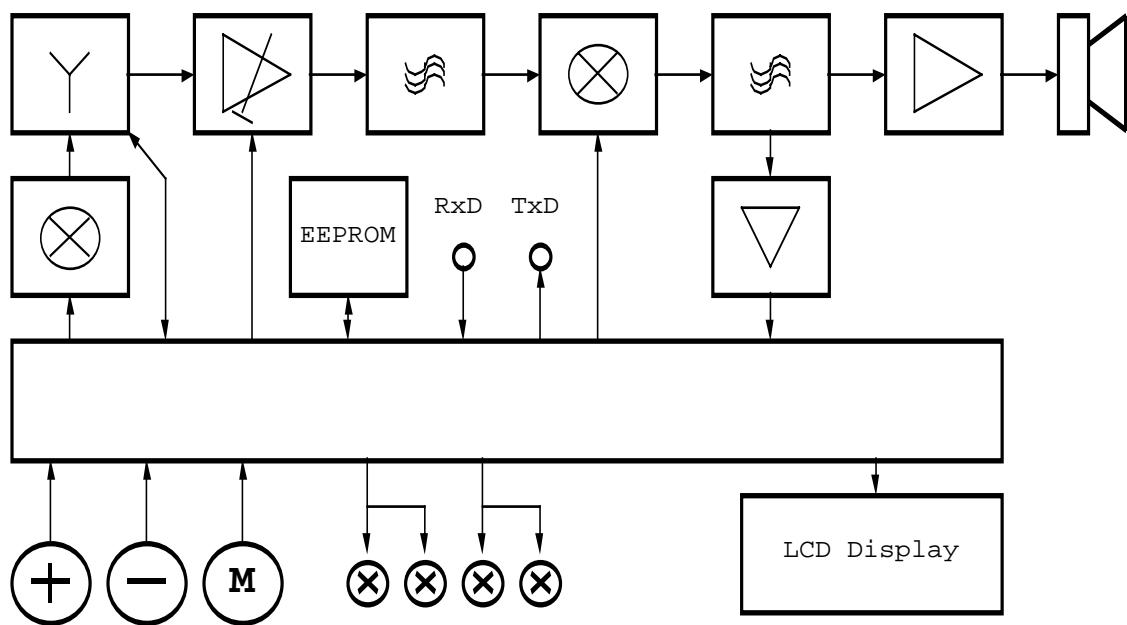

This document outlines the basic concepts for the OPTO 3000 avalanche beacon.

## 2. Batteries

The device will be powered by 3 AAA batteries connected in series. The nominal supply voltage is 3 \* 1.5 V = 4.5 V. Circuits will be designed for operation down to about 3.5 V to ensure adequate lifetime.

## 3. Antenna System

### 3.1 Receiving

The antenna system is made of two orthogonal antennas. One of the antennas is more sensitive than the other since it has a longer ferrite rod. This antenna will also be used for transmission. The Q of the tank is about 70 - 80.

The antennas are switched on and off by the uP. While receiving, a single antenna is active ( tuned to resonance ) at the time. The other one is de-tuned to avoid mutual interference. Individual control signals are provided for the two receive antennas.

### 3.2 Transmitting

The TX antenna power is checked by measuring the peak voltage on the tank via a Schottky diode and a RC filter. The voltage across the capacitor is measured by means of a Schmidt-Trigger. The transmit oscillator is separate from the microprocessor. A pre-scaler is required so a quartz on a multiple of 457 kHz can be used. This pre-scaler has an enable input. The uP provides separate

control signals for oscillator turn-on and for tx signal keying ( counter enable ). The tx signal duty cycle is 25 %. This is sufficient for achieving about 650 mA of resonance current in the antenna tank and saves power.

## 4. Preamplifier

The preamplifier gain ranges from - 24 dB to + 60 dB. The gain can be switched in increments of 12 dB. For large signals, the preamplifier is actually an attenuator. In any case, the signal is passed through a quartz filter for selectivity.

## 5. Mixer

We use a conventional analog mixer. The LO frequency is 455 kHz. It is generated inside the uP by dividing the uP clock frequency by 8. Note that the signal line feeding the mixer is very critical. The currents on this line must be kept at an absolute minimum in order to minimize coupling into the antennas. The mixer gain is about 22 dB.

## 6. Filter / Buffer

The filter / buffer serves several purposes :

- It removes the remaining harmonics from the mixer output.

- It provides a low impedance source ( < 1 k Ohms ) to the uP AD - converter.

- It provides another 40 dB of gain.

## 7. Speaker / Earphone Driver

These amplifiers provide the signal to the local speaker / earphone. They also take care of additional filtering for removing harmonics. Either of them can be used to mute the received analog signal. The inputs also serve as a summing point for the buzzer and receiver signals.

## 8. Microprocessor

The microprocessor is a NEC uPD 78034 or similar ( 78024 ). The 7802x family does not offer OTP / EEPROM / FLASH versions and has an 8 bit ADC. The only other difference to the 7803x family is that the latter has a 10 bit ADC in place of 8 bit. The -Y versions are not of interest, they provide a hardware IIC interface which we do not need.

### 8.1 XTAL / Clock

The XTAL frequency is  $455 \text{ kHz} * 8 = 3.640 \text{ MHz}$  ( 3.639584 MHz ). Since this is an integer multiple of the LO frequency, interference will be minimized.

The PCC register is set to 0x44 ( MCS bit = 1 ). This makes  $f_{\text{CPU}}$  equal to  $f_x = 3.640 \text{ MHz}$ . The internal feedback resistor is switched off to reduce power consumption.

The CPU instruction cycle time is  $2 \times 275 \text{ ns} = 550 \text{ ns}$ .

When the CPU is not busy, it is put in HALT mode to reduce current consumption ( down to 700 – 800  $\mu\text{A}$  from 3 mA ).

### 8.2 LO Signal Generation

The mixer LO signal is generated by using the programmable processor clock output. The CKU control register CKS is set to 0bxxx10011 ( LO on ) or 0bxxx00011 ( LO off ) which provides continuous output of a 455 kHz clock on port pin P74. The P74 output latch must be set to 0, and the PM7 ( port mode register 3 ) bit 4 must also be set to 0 to make the pin an output pin.

### 8.3 Tone Generation

User tones are generated by using the buzzer output. The CKU control register CKS is set to 0b101xxxxx ( tone on ) or 0b001xxxxx ( tone off ) which provides continuous output of a 1777 kHz clock on port pin P75. The P75 output latch must be set to 0, and the PM7 ( port mode register 7 ) bit 5 must also be set to 0 to make the pin an output pin. The output is a 50 % duty cycle square wave and may need some shaping before application to the speaker.

### 8.4 Operating System Clock

For the operating system clock interrupt, we use the watch timer feature. The WTM register is set to 0b01000000 which provides a INTWT1 interrupt every 9.002 ms.

### 8.5 Watchdog

The watchdog timer clock select register TDSC is set to 0b00000111, providing a watchdog overflow every 288 ms. The watchdog timer mode register is set to 0b10011000 for a reset on expiration. Re-trigger the watchdog by writing 0b10000000 to this same register. ( note that the mode bits cannot be re-written to 0 once they have been set to 1 ).

### 8.6 UART

The UART serial interface is used for communication with a PC for manufacturing, testing and maintenance purposes. We use a simple infrared interface driven by 'HC14 inverters.

The UART uses two pins for RxD and TxD ( P23 and P24 ). For UART operation, set ASIM0 to 0b11001000 ( UART0 mode, no parity, 8 bits, 1 stop bit, rx interrupt on error, no infrared mode ).

The BRGC0 ( Baud Rate Generator Control Register ) is set to 0x38. This provides a baud rate of 3.640 MHz / 16 / 24 = 9479 which is -1.3% of the nominal 9600 bit/s.

### 8.7 EEPROM

A 1024 bit ( 128 bytes ) serial EEPROM is used for storing alignment data and production / sales / servicing information.

The EEPROM is partitioned into two domains with separate virgin initialization handling :

#### 8.7.1 Device Data

The device data consists of

- software version

- transmitter parameters

- receiver parameters

- device parameters

- user interface parameters

- software parameters

The device data structure may change when the software version is upgraded. Device data is always initialized to default when the software version is changed. This implies that the device must be re-aligned after a software upgrade. The software version can only be modified by specially authorized entities.

#### 8.7.2 Identity Data

The identity data consists of

- identity version

- serial number

- manufacturing record

- service records ( currently 7 )

The identity data is independent of the software version. It is not re-initialized when a new software version is loaded. The data is safe against any Y2K problems. The identity version and the serial number can only be modified by specially authorized entities.

## 8.8 Operating System

A simple state-event operating system is used. The system provides a single event queue and a timer system with 9 ms resolution. The maximum timer duration is 2.295 sec.

## 8.9 Battery Management

The battery is checked by comparing the full ADC range (  $AV_{REF} = 0xff$  ) to the reference voltage at startup. The percentage of remaining battery capacity is displayed for four seconds after the self-test has completed. While transmitting, the signal strength is checked during every pulse. Transmission, however, is continued until the battery is completely exhausted.

## 8.10 Transmitter Control

The uP consumes about 1 mA or less in idle mode. It is therefore also used for controlling the transmit cycle. This activity includes :

- on / off timing

- transmit signal generation and keying

- checking the transmitter signal level by means of the Schmidt-Trigger

- short blinking of the transmit control LED

# 9. User Interface

## 9.1 Interface Components

The following devices are available for user interfacing :

1. keys :

- one key for mode switching while in receive mode.

- two keys ( + and - ) for modifying parameters ( attenuation, speaker on / off etc. ).

2. LCD Display :

- 5 arrows for direction indication

- symbols

- two digits with a decimal point

3. the loudspeaker. A 1.777 kHz square wave can be generated locally for user tones. The speaker can be turned off for the receiver signal, but not for the user interface tones.

4. LEDs

- Two LEDs for transmitter check display

- Two LEDs for illuminating the LCD display when the ambient light falls below a certain level.

- A phototransistor provides sensing information.