## Technical Description

The brief circuit description is listed as below:

- 1) U5 acts as 2.4GHz RF Module (KNRF51822-A24-AAH) with 16MHz oscillator.

- 2) U1\_7A acts as Voice player (GPC11512C).

a. Q4 acts as audio amplifiers(8050C)

- 3) U1 and U9 acts as a DC to DC regulator(LC3030-50).

- 4) U3 acts as MCU (NM05716DN(64K) with 12MHz crystal(Y1)

**Antenna Type: Internal antenna**

**Antenna Gain: 0dBi**

**Nominal rated field strength: 88.3 dB $\mu$ V/m at 3m**

**Maximum allowed field strength of production tolerance: +/- 5dB**

# nRF51822

Multiprotocol *Bluetooth*® low energy/2.4 GHz RF System on Chip

## Product Specification v3.1

### Key Features

- 2.4 GHz transceiver

- -93 dBm sensitivity in *Bluetooth*® low energy mode

- 250 kbps, 1 Mbps, 2 Mbps supported data rates

- TX Power -20 to +4 dBm in 4 dB steps

- TX Power -30 dBm Whisper mode

- 13 mA peak RX, 10.5 mA peak TX (0 dBm)

- 9.7 mA peak RX, 8 mA peak TX (0 dBm) with DC/DC

- RSSI (1 dB resolution)

- ARM® Cortex™-M0 32 bit processor

- 275  $\mu$ A/MHz running from flash memory

- 150  $\mu$ A/MHz running from RAM

- Serial Wire Debug (SWD)

- S100 series SoftDevice ready

- Memory

- 256 kB or 128 kB embedded flash program memory

- 16 kB or 32 kB RAM

- On-air compatibility with nRF24L series

- Flexible Power Management

- Supply voltage range 1.8 V to 3.6 V

- 4.2  $\mu$ s wake-up using 16 MHz RCOSC

- 0.6  $\mu$ A at 3 V OFF mode

- 1.2  $\mu$ A at 3 V in OFF mode + 1 region RAM retention

- 2.6  $\mu$ A at 3 V ON mode, all blocks IDLE

- 8/9/10 bit ADC - 8 configurable channels

- 31 General Purpose I/O Pins

- One 32 bit and two 16 bit timers with counter mode

- SPI Master/Slave

- Low power comparator

- Temperature sensor

- Two-wire Master (I2C compatible)

- UART (CTS/RTS)

- CPU independent Programmable Peripheral Interconnect (PPI)

- Quadrature Decoder (QDEC)

- AES HW encryption

- Real Timer Counter (RTC)

- Package variants

- QFN48 package, 6 x 6 mm

- WLCSP package, 3.50 x 3.83 mm

- WLCSP package, 3.83 x 3.83 mm

- WLCSP package, 3.50 x 3.33 mm

### Applications

- Computer peripherals and I/O devices

- Mouse

- Keyboard

- Multi-touch trackpad

- Interactive entertainment devices

- Remote control

- Gaming controller

- Beacons

- Personal Area Networks

- Health/fitness sensor and monitor devices

- Medical devices

- Key-fobs + wrist watches

- Remote control toys

## Liability disclaimer

Nordic Semiconductor ASA reserves the right to make changes without further notice to the product to improve reliability, function or design. Nordic Semiconductor ASA does not assume any liability arising out of the application or use of any product or circuits described herein.

## Life support applications

Nordic Semiconductor's products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Nordic Semiconductor ASA customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nordic Semiconductor ASA for any damages resulting from such improper use or sale.

## Contact details

For your nearest distributor, please visit [www.nordicsemi.com](http://www.nordicsemi.com).

Information regarding product updates, downloads, and technical support can be accessed through your My Page account on our home page.

**Main office:** Otto Nielsens veg 12

7052 Trondheim

Norway

Phone: +47 72 89 89 00

Fax: +47 72 89 89 89

**Mailing address:** Nordic Semiconductor

P.O. Box 2336

7004 Trondheim

Norway

## RoHS and REACH statement

Nordic Semiconductor's products meet the requirements of Directive 2002/95/EC of the European Parliament and of the Council on the Restriction of Hazardous Substances (RoHS) and the requirements of the REACH regulation (EC 1907/2006) on Registration, Evaluation, Authorization and Restriction of Chemicals. The SVHC (Substances of Very High Concern) candidate list is continually being updated. Complete hazardous substance reports, material composition reports and latest version of Nordic's REACH statement can be found on our website [www.nordicsemi.com](http://www.nordicsemi.com).

## Datasheet Status

| Status                                  | Description                                                                                                                                                                                                               |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective Product Specification (OPS)   | This product specification contains target specifications for product development.                                                                                                                                        |

| Preliminary Product Specification (PPS) | This product specification contains preliminary data; supplementary data may be published from Nordic Semiconductor ASA later.                                                                                            |

| Product Specification (PS)              | This product specification contains final product specifications. Nordic Semiconductor ASA reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

## Revision History

| Date         | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| October 2014 | 3.1     | <p>Added documentation for the following versions of the chip:</p> <ul style="list-style-type: none"> <li>• nRF51822-QFAC AA0</li> <li>• nRF51822-QFAC Ax0</li> <li>• nRF51822-CDAB AA0</li> <li>• nRF51822-CDAB Ax0</li> <li>• nRF51822-CFAC AA0</li> <li>• nRF51822-CFAC Ax0</li> </ul> <p>(The x in the build codes can be any number between 0 and 9.)</p> <p><b>Added content:</b></p> <ul style="list-style-type: none"> <li>• <i>Section 2.2.2 “CDAB WLCSP ball assignment and functions”</i> on page 13</li> <li>• <i>Section 9.2 “CDAB WLCSP package”</i> on page 67</li> <li>• <i>Section 9.4 “CFAC WLCSP package”</i> on page 69</li> </ul> <p><b>Updated content:</b></p> <ul style="list-style-type: none"> <li>• Feature list on the front page.</li> <li>• <i>Section 2.2.3 “CEAA and CFAC WLCSP ball assignment and functions”</i> on page 16</li> <li>• <i>Section 3.2.1 “Code organization”</i> on page 21</li> <li>• <i>Section 3.2.2 “RAM organization”</i> on page 21</li> <li>• <i>Section 3.3 “Memory Protection Unit (MPU)”</i> on page 22</li> <li>• <i>Section 8.2 “Power management”</i> on page 44</li> <li>• <i>Section 8.3 “Block resource requirements”</i> on page 48</li> <li>• <i>Section 8.12 “Analog to Digital Converter (ADC) specifications”</i> on page 60</li> <li>• <i>Section 10.6 “Code ranges and values”</i> on page 73</li> <li>• <i>Section 10.7 “Product options”</i> on page 75</li> </ul> |

| Date        | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 2014 | 3.0     | <p>Update to reflect the changes in build code:</p> <ul style="list-style-type: none"> <li>• nRF51822-QFAA Hx0</li> <li>• nRF51822-CEAA Ex0</li> <li>• nRF51822-QFAB Cx0</li> </ul> <p>(The x in the build codes can be any number between 0 and 9.)<br/> If you are working with a previous revision of the chip, read version 2.x of the document.</p> <p><b>Added content:</b></p> <ul style="list-style-type: none"> <li>• <i>Section 8.5.3 "Radio current consumption with DC/DC enabled"</i> on page 50</li> <li>• <i>Section 11.1.1 "PCB layout example"</i> on page 77</li> </ul> <p><b>Updated content:</b></p> <ul style="list-style-type: none"> <li>• Feature list on the front page.</li> <li>• <i>Section 2.1 "Block diagram"</i> on page 10</li> <li>• <i>Section 3.2.1 "Code organization"</i> on page 21</li> <li>• <i>Section 3.2.2 "RAM organization"</i> on page 21</li> <li>• <i>Section 3.3 "Memory Protection Unit (MPU)"</i> on page 22</li> <li>• <i>Section 3.4 "Power management (POWER)"</i> on page 23</li> <li>• <i>Section 3.6 "Clock management (CLOCK)"</i> on page 27</li> <li>• <i>Section 3.8 "Debugger support"</i> on page 30</li> <li>• <i>Section 4.2 "Timer/counters (TIMER)"</i> on page 32</li> <li>• <i>Chapter 5 "Instance table"</i> on page 36</li> <li>• <i>Chapter 7 "Operating conditions"</i> on page 38</li> <li>• <i>Section 8.1.2 "16 MHz crystal oscillator (16M XOSC)"</i> on page 40</li> <li>• <i>Section 8.1.3 "32 MHz crystal oscillator (32M XOSC)"</i> on page 41</li> <li>• <i>Section 8.1.4 "16 MHz RC oscillator (16M RCOSC)"</i> on page 42</li> <li>• <i>Section 8.1.6 "32.768 kHz RC oscillator (32k RCOSC)"</i> on page 43</li> <li>• <i>Section 8.1.7 "32.768 kHz Synthesized oscillator (32k SYNT)"</i> on page 43</li> <li>• <i>Section 8.2 "Power management"</i> on page 44</li> <li>• <i>Section 8.3 "Block resource requirements"</i> on page 48</li> <li>• <i>Section 8.4 "CPU"</i> on page 48</li> <li>• <i>Section 8.5.6 "Radio timing parameters"</i> on page 54</li> <li>• <i>Section 8.5.7 "Antenna matching network requirements"</i> on page 54</li> <li>• <i>Section 8.7 "Universal Asynchronous Receiver/Transmitter (UART) specifications"</i> on page 55</li> <li>• <i>Section 8.8 "Serial Peripheral Interface Slave (SPIS) specifications"</i> on page 56</li> <li>• <i>Section 8.12 "Analog to Digital Converter (ADC) specifications"</i> on page 60</li> <li>• <i>Section 8.13 "Timer (TIMER) specifications"</i> on page 61</li> <li>• <i>Section 8.15 "Temperature sensor (TEMP)"</i> on page 61</li> <li>• <i>Section 8.22 "Non-Volatile Memory Controller (NVMC) specifications"</i> on page 64</li> <li>• <i>Section 8.24 "Low Power Comparator (LPCOMP) specifications"</i> on page 65</li> <li>• <i>Section 9.2 "CDAB WL CSP package"</i> on page 67</li> <li>• <i>Section 10.7.2 "Development tools"</i> on page 75</li> <li>• <i>Chapter 11 "Reference circuitry"</i> on page 76</li> </ul> |

| Date         | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| October 2013 | 2.0     | <p>This version of the document will target the nRF51822 QFAA G0 revision of the chip. If you are working with a previous revision of the chip, read version 1.3 or earlier of the document.</p> <p><b>Updated</b> the following sections:</p> <p>Key Feature list on the front page,<br/> <i>Chapter 1 "Introduction"</i> on page 9,<br/> <i>Section 2.1 "Block diagram"</i> on page 10,<br/> <i>Section 2.2 "Pin assignments and functions"</i> on page 11,<br/> <i>Section 3.2 "Memory"</i> on page 20,<br/> <i>Section 3.5 "Programmable Peripheral Interconnect (PPI)"</i> on page 26,<br/> <i>Section 3.7 "GPIO"</i> on page 30,<br/> <i>Section 4.1 "2.4 GHz radio (RADIO)"</i> on page 31,<br/> <i>Section 4.2 "Timer/counters (TIMER)"</i> on page 32,<br/> <i>Section 4.3 "Real Time Counter (RTC)"</i> on page 32,<br/> <i>Section 4.10 "Serial Peripheral Interface (SPI/SPIS)"</i> on page 34,<br/> <i>Section 4.12 "Universal Asynchronous Receiver/Transmitter (UART)"</i> on page 35,<br/> <i>Section 4.14 "Analog to Digital Converter (ADC)"</i> on page 35,<br/> <i>Section 4.15 "GPIO Task Event blocks (GPIOTE)"</i> on page 35,<br/> <i>Chapter 5 "Instance table"</i> on page 36,<br/> <i>Chapter 6 "Absolute maximum ratings"</i> on page 37,<br/> <i>Chapter 8 "Electrical specifications"</i> on page 39,<br/> <i>Section 8.1 "Clock sources"</i> on page 39,<br/> <i>Section 8.1.2 "16 MHz crystal oscillator (16M XOSC)"</i> on page 40,<br/> <i>Section 8.1.3 "32 MHz crystal oscillator (32M XOSC)"</i> on page 41,<br/> <i>Section 8.2 "Power management"</i> on page 44,<br/> <i>Section 8.3 "Block resource requirements"</i> on page 48,<br/> <i>Section 8.7 "Universal Asynchronous Receiver/Transmitter (UART) specifications"</i> on page 55,<br/> <i>Section 8.9 "Serial Peripheral Interface (SPI) Master specifications"</i> on page 57,<br/> <i>Section 8.11 "GPIO Tasks and Events (GPIOTE) specifications"</i> on page 59,<br/> <i>Section 8.13 "Timer (TIMER) specifications"</i> on page 61,<br/> <i>Section 8.16 "Random Number Generator (RNG) specifications"</i> on page 62,<br/> <i>Section 8.17 "AES Electronic Codebook Mode Encryption (ECB) specifications"</i> on page 62,<br/> <i>Section 8.18 "AES CCM Mode Encryption (CCM) specifications"</i> on page 62,<br/> <i>Section 8.19 "Accelerated Address Resolver (AAR) specifications"</i> on page 62,<br/> <i>Section 8.21 "Quadrature Decoder (QDEC) specifications"</i> on page 63,<br/> <i>Section 11.1 "PCB guidelines"</i> on page 76,<br/> <i>Section 11.3 "QFAA QFN48 package"</i> on page 79, and<br/> <i>Section 11.7 "CEAA WLCSP package"</i> on page 103.</p> <p><b>Added</b> the following sections:</p> <p><i>Section 3.3 "Memory Protection Unit (MPU)"</i> on page 22,<br/> <i>Section 4.5 "AES CCM Mode Encryption (CCM)"</i> on page 33,<br/> <i>Section 4.6 "Accelerated Address Resolver (AAR)"</i> on page 33,<br/> <i>Section 4.16 "Low Power Comparator (LPCOMP)"</i> on page 35,<br/> <i>Section 8.5.7 "Antenna matching network requirements"</i> on page 54,<br/> <i>Section 8.8 "Serial Peripheral Interface Slave (SPIS) specifications"</i> on page 56,<br/> <i>Section 8.18 "AES CCM Mode Encryption (CCM) specifications"</i> on page 62,<br/> <i>Section 8.19 "Accelerated Address Resolver (AAR) specifications"</i> on page 62, and<br/> <i>Section 8.24 "Low Power Comparator (LPCOMP) specifications"</i> on page 65.</p> |

| May 2013     | 1.3     | Updated schematics and BOMs in section 11.3 on page 61.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Date          | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| April 2013    | 1.2     | <p>Added chip variant nRF51822-CEAA. Updated feature list on front page.</p> <p><b>Updated</b></p> <p>Section 3.2.1 on page 15, Section 3.2.2 on page 15, Chapter 6 on page 28, Section 10.4 on page 52, and Section 10.5.1 on page 53.</p> <p><b>Added</b></p> <p>Section 2.2.2 on page 10, Section 7.1 on page 29, Section 9.2 on page 50, and Section 11.3 on page 61.</p> <p><b>Removed</b> PCB layouts in Chapter 11 on page 54.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| March 2013    | 1.1     | <p>Added chip variant nRF51822-QFAB. Added 32 MHz crystal oscillator feature. Updated feature list on front page. Moved subsection 'Calculating current when the DC/DC converter is enabled' from chapter 8 to the <i>nRF51 Series Reference Manual</i>.</p> <p><b>Updated</b></p> <p>Chapter 1 on page 6, Section 2.2 on page 8, Section 3.2 on page 12, Section 3.5 on page 16, Section 3.5.1 on page 17, Section 4.2 on page 21, Chapter 5 on page 24, Section 8.1 on page 27, Section 8.1.2 on page 28, Section 8.1.5 on page 30, Section 8.2 on page 32, Section 8.3 on page 34, Section 8.5.3 on page 36, Section 8.8 on page 40, Section 8.9 on page 41, Section 8.10 on page 42, Section 8.14 on page 43, Chapter 10 on page 47, Section 11.2 on page 51, Section 11.3 on page 54, and Section 11.4 on page 57.</p> <p><b>Added</b></p> <p>Section 3.5.4 on page 19, Section 8.1.3 on page 29, and Section 11.1 on page 50.</p> |

| November 2012 | 1.0     | <p>Changed from PPS to PS. Updated the feature list on the front page.</p> <p><b>Updated</b></p> <p>Table 11 on page 25, Table 12 on page 26, Table 14 on page 28, Table 15 on page 28, Table 16 on page 29, Table 17 on page 29, Table 18 on page 30, Table 19 on page 31, Table 21 on page 32, Table 22 on page 32, Table 23 on page 33, Table 27 on page 36, Table 28 on page 37, Table 29 on page 37, Table 31 on page 38, Table 32 on page 38, Table 35 on page 39, Table 38 on page 40, Table 39 on page 40, Table 55 on page 47, Figure 9 on page 48, and Table 57 on page 50.</p>                                                                                                                                                                                                                                                                                                                                               |

## Table of contents

|          |                                                                   |           |

|----------|-------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                               | <b>9</b>  |

| 1.1      | Required reading                                                  | 9         |

| 1.2      | Writing conventions                                               | 9         |

| <b>2</b> | <b>Product overview</b>                                           | <b>10</b> |

| 2.1      | Block diagram                                                     | 10        |

| 2.2      | Pin assignments and functions                                     | 11        |

| <b>3</b> | <b>System blocks</b>                                              | <b>19</b> |

| 3.1      | CPU                                                               | 19        |

| 3.2      | Memory                                                            | 20        |

| 3.3      | Memory Protection Unit (MPU)                                      | 22        |

| 3.4      | Power management (POWER)                                          | 23        |

| 3.5      | Programmable Peripheral Interconnect (PPI)                        | 26        |

| 3.6      | Clock management (CLOCK)                                          | 27        |

| 3.7      | GPIO                                                              | 30        |

| 3.8      | Debugger support                                                  | 30        |

| <b>4</b> | <b>Peripheral blocks</b>                                          | <b>31</b> |

| 4.1      | 2.4 GHz radio (RADIO)                                             | 31        |

| 4.2      | Timer/counters (TIMER)                                            | 32        |

| 4.3      | Real Time Counter (RTC)                                           | 32        |

| 4.4      | AES Electronic Codebook Mode Encryption (ECB)                     | 32        |

| 4.5      | AES CCM Mode Encryption (CCM)                                     | 33        |

| 4.6      | Accelerated Address Resolver (AAR)                                | 33        |

| 4.7      | Random Number Generator (RNG)                                     | 33        |

| 4.8      | Watchdog Timer (WDT)                                              | 33        |

| 4.9      | Temperature sensor (TEMP)                                         | 34        |

| 4.10     | Serial Peripheral Interface (SPI/SPIS)                            | 34        |

| 4.11     | Two-wire interface (TWI)                                          | 34        |

| 4.12     | Universal Asynchronous Receiver/Transmitter (UART)                | 35        |

| 4.13     | Quadrature Decoder (QDEC)                                         | 35        |

| 4.14     | Analog to Digital Converter (ADC)                                 | 35        |

| 4.15     | GPIO Task Event blocks (GPIOTE)                                   | 35        |

| 4.16     | Low Power Comparator (LPCOMP)                                     | 35        |

| <b>5</b> | <b>Instance table</b>                                             | <b>36</b> |

| <b>6</b> | <b>Absolute maximum ratings</b>                                   | <b>37</b> |

| <b>7</b> | <b>Operating conditions</b>                                       | <b>38</b> |

| 7.1      | WLCSP light sensitivity                                           | 38        |

| <b>8</b> | <b>Electrical specifications</b>                                  | <b>39</b> |

| 8.1      | Clock sources                                                     | 39        |

| 8.2      | Power management                                                  | 44        |

| 8.3      | Block resource requirements                                       | 48        |

| 8.4      | CPU                                                               | 48        |

| 8.5      | Radio transceiver                                                 | 49        |

| 8.6      | Received Signal Strength Indicator (RSSI) specifications          | 54        |

| 8.7      | Universal Asynchronous Receiver/Transmitter (UART) specifications | 55        |

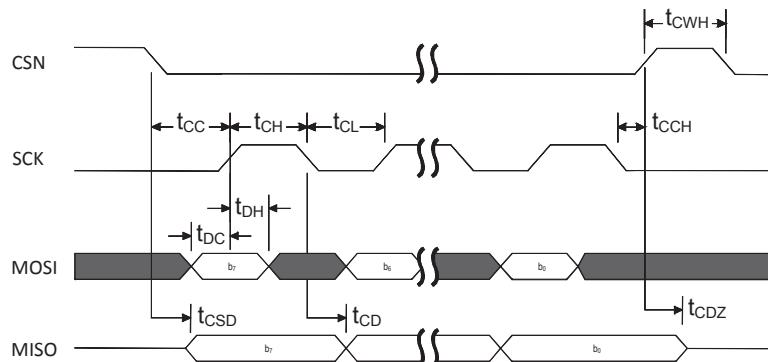

| 8.8      | Serial Peripheral Interface Slave (SPIS) specifications           | 56        |

---

|           |                                                                   |            |

|-----------|-------------------------------------------------------------------|------------|

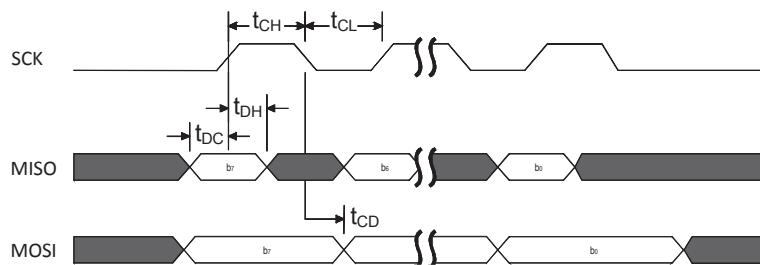

| 8.9       | Serial Peripheral Interface (SPI) Master specifications .....     | 57         |

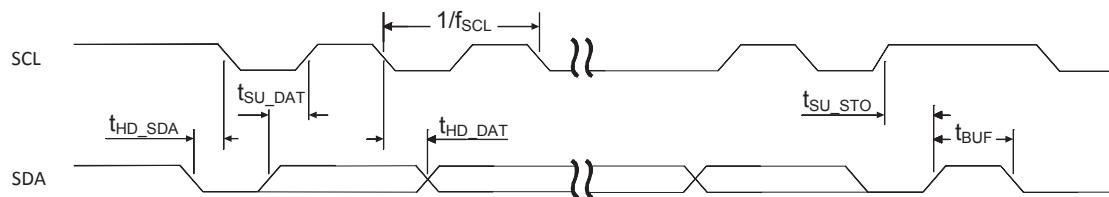

| 8.10      | I2C compatible Two Wire Interface (TWI) specifications.....       | 58         |

| 8.11      | GPIO Tasks and Events (GPIOTE) specifications.....                | 59         |

| 8.12      | Analog to Digital Converter (ADC) specifications.....             | 60         |

| 8.13      | Timer (TIMER) specifications.....                                 | 61         |

| 8.14      | Real Time Counter (RTC) .....                                     | 61         |

| 8.15      | Temperature sensor (TEMP) .....                                   | 61         |

| 8.16      | Random Number Generator (RNG) specifications.....                 | 62         |

| 8.17      | AES Electronic Codebook Mode Encryption (ECB) specifications..... | 62         |

| 8.18      | AES CCM Mode Encryption (CCM) specifications .....                | 62         |

| 8.19      | Accelerated Address Resolver (AAR) specifications .....           | 62         |

| 8.20      | Watchdog Timer (WDT) specifications .....                         | 63         |

| 8.21      | Quadrature Decoder (QDEC) specifications .....                    | 63         |

| 8.22      | Non-Volatile Memory Controller (NVMC) specifications.....         | 64         |

| 8.23      | General Purpose I/O (GPIO) specifications .....                   | 65         |

| 8.24      | Low Power Comparator (LPCOMP) specifications.....                 | 65         |

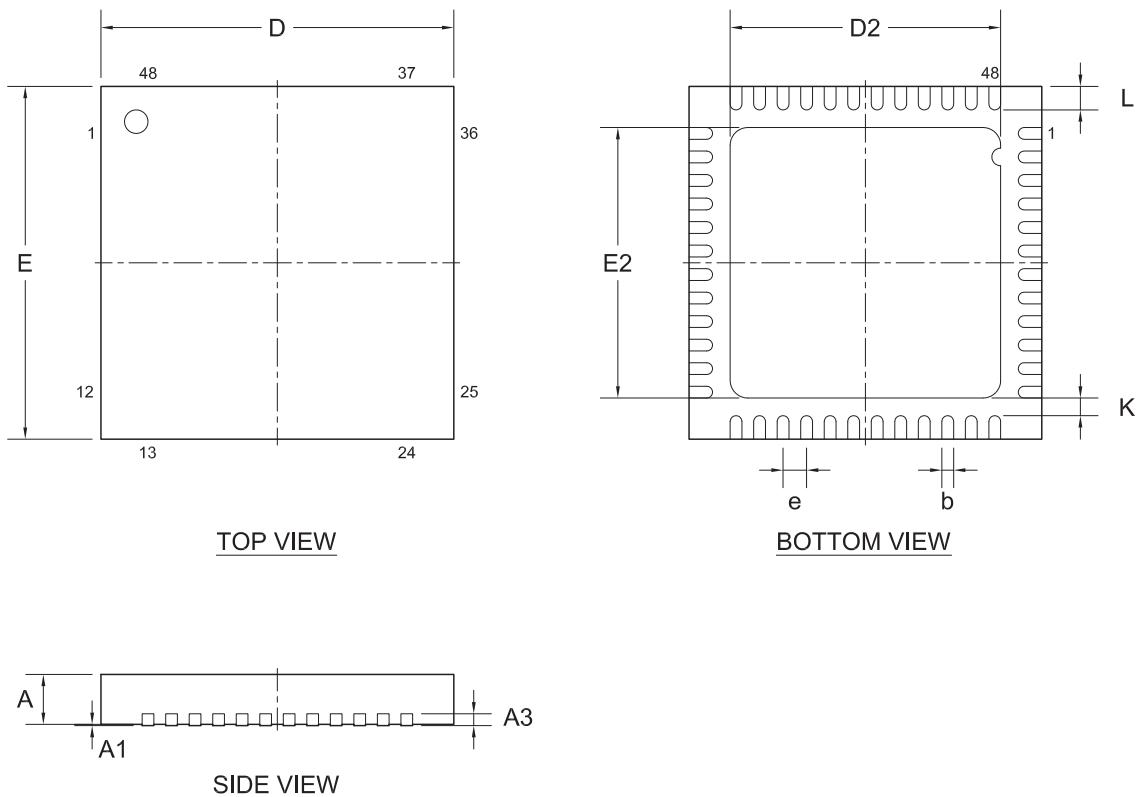

| <b>9</b>  | <b>Mechanical specifications .....</b>                            | <b>66</b>  |

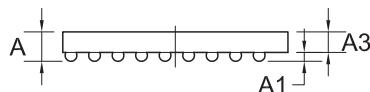

| 9.1       | QFN48 package .....                                               | 66         |

| 9.2       | CDAB WLCSP package .....                                          | 67         |

| 9.3       | CEAA WLCSP package.....                                           | 68         |

| 9.4       | CFAC WLCSP package.....                                           | 69         |

| <b>10</b> | <b>Ordering information .....</b>                                 | <b>70</b>  |

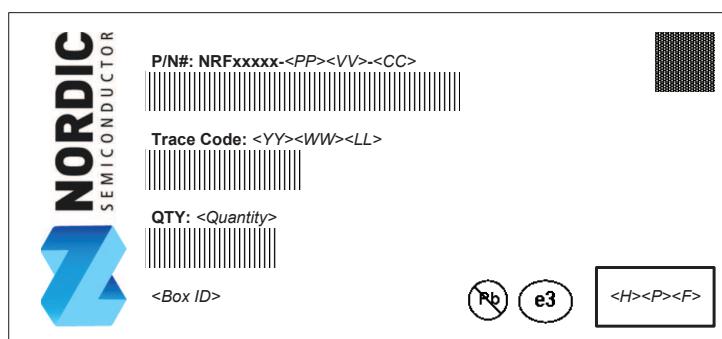

| 10.1      | Chip marking.....                                                 | 70         |

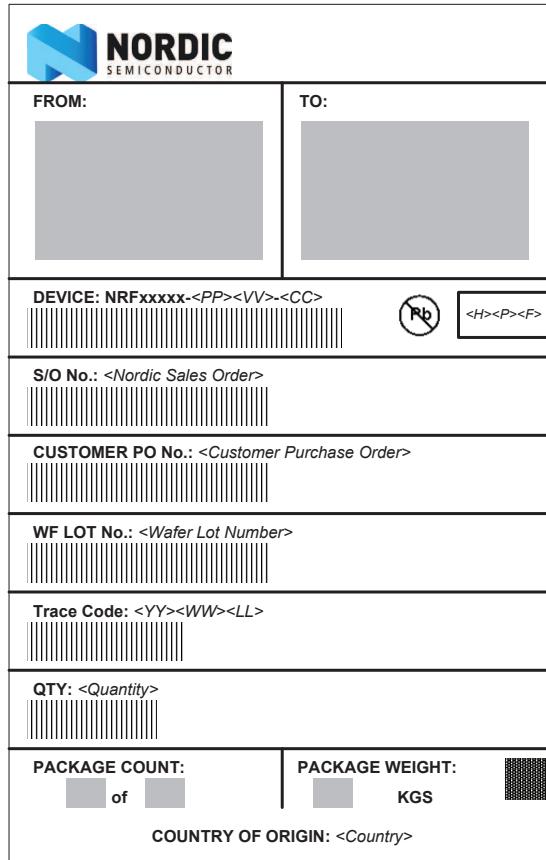

| 10.2      | Inner box label.....                                              | 70         |

| 10.3      | Outer box label.....                                              | 71         |

| 10.4      | Order code .....                                                  | 71         |

| 10.5      | Abbreviations.....                                                | 72         |

| 10.6      | Code ranges and values .....                                      | 73         |

| 10.7      | Product options .....                                             | 75         |

| <b>11</b> | <b>Reference circuitry.....</b>                                   | <b>76</b>  |

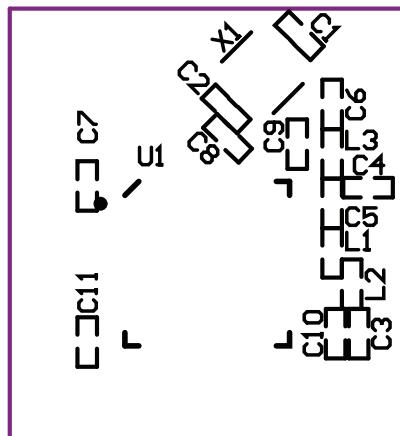

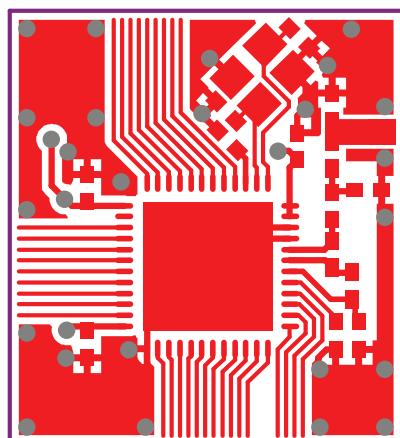

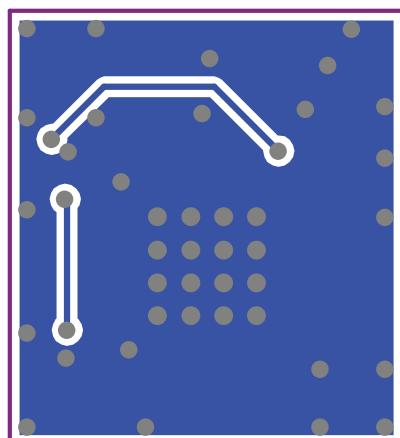

| 11.1      | PCB guidelines.....                                               | 76         |

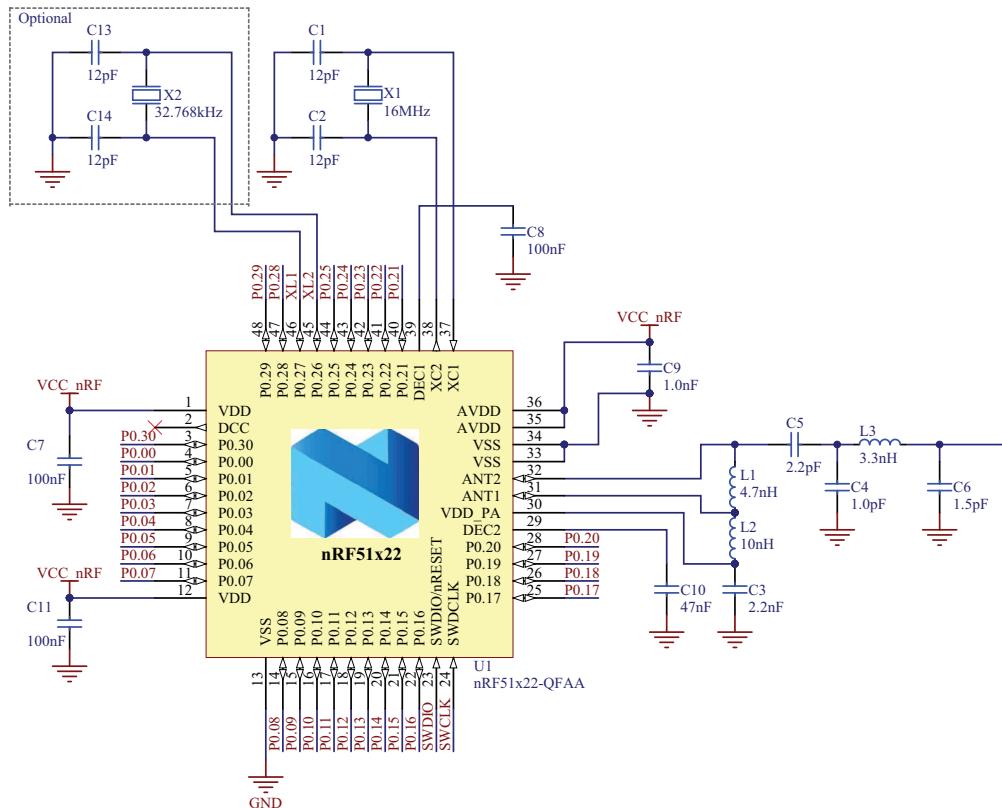

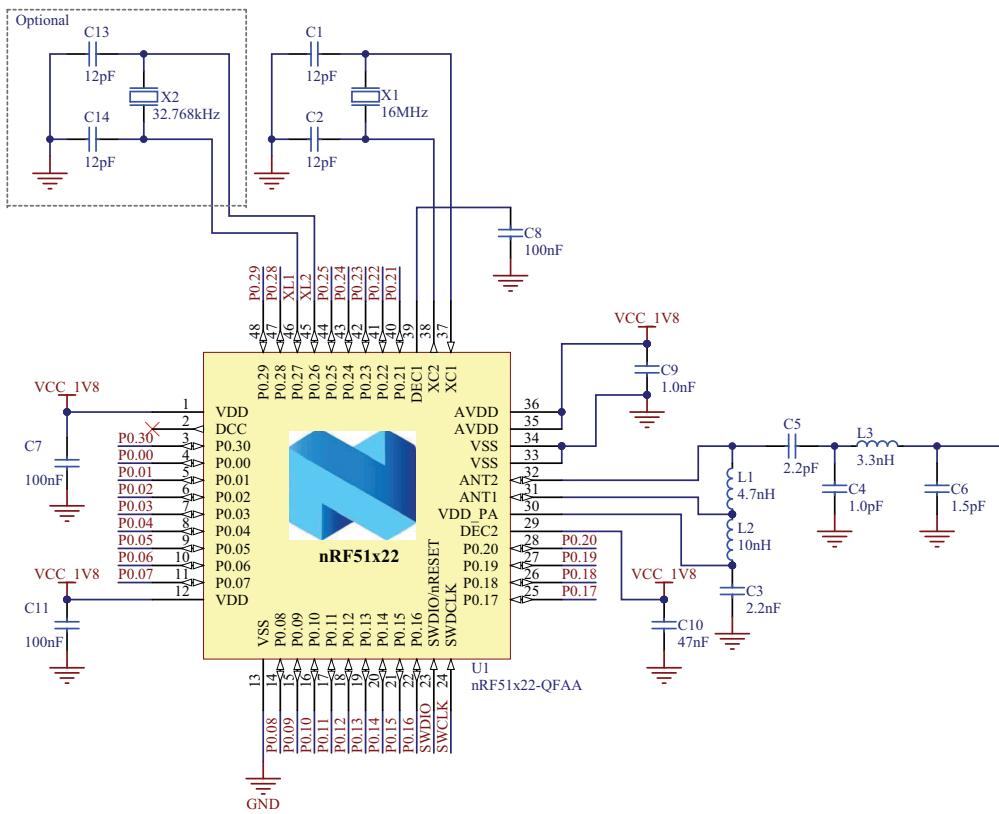

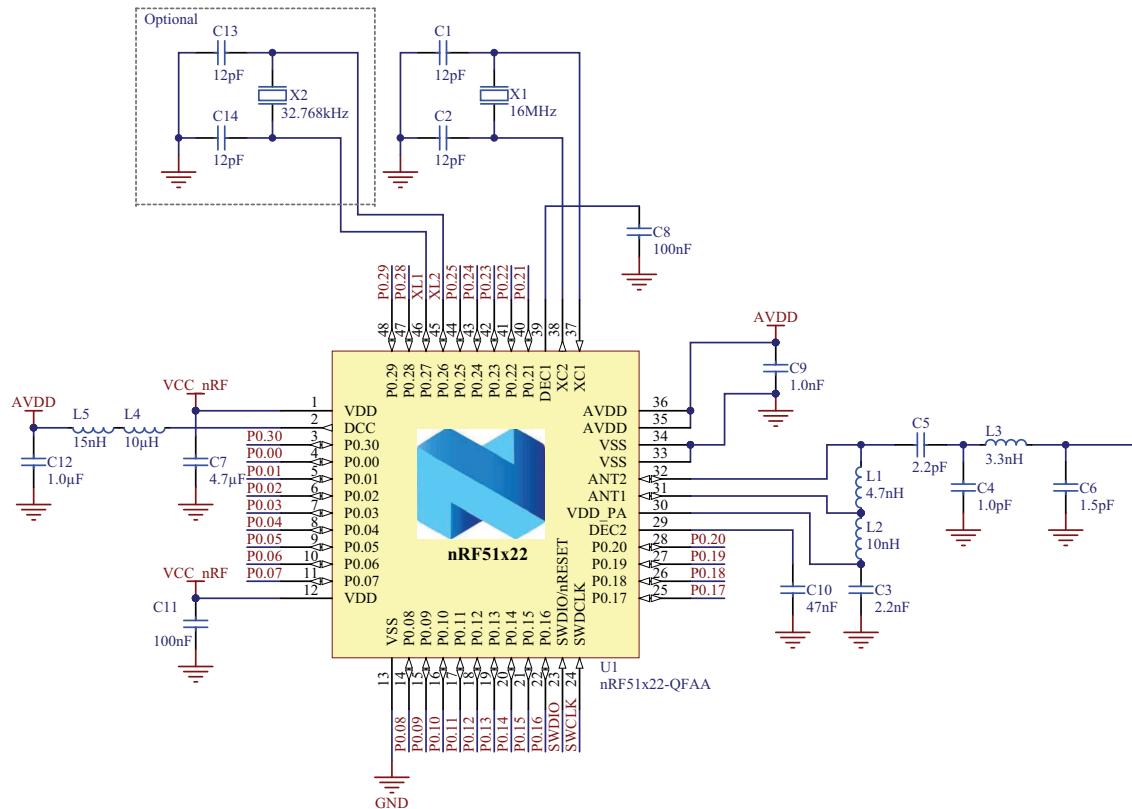

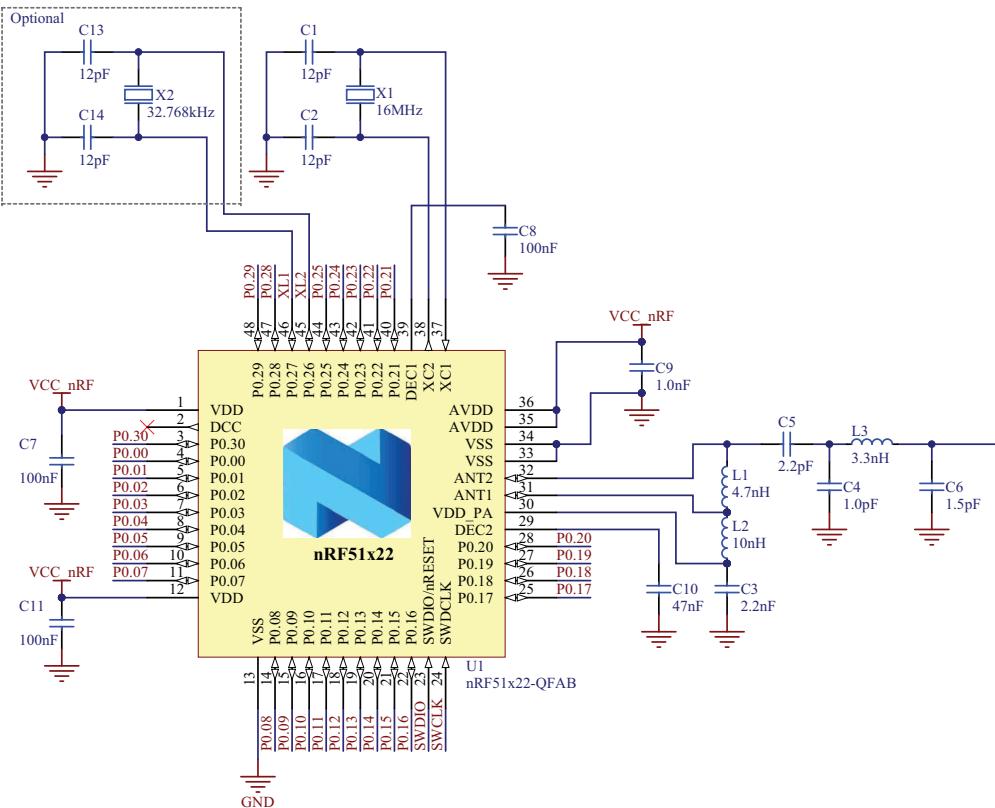

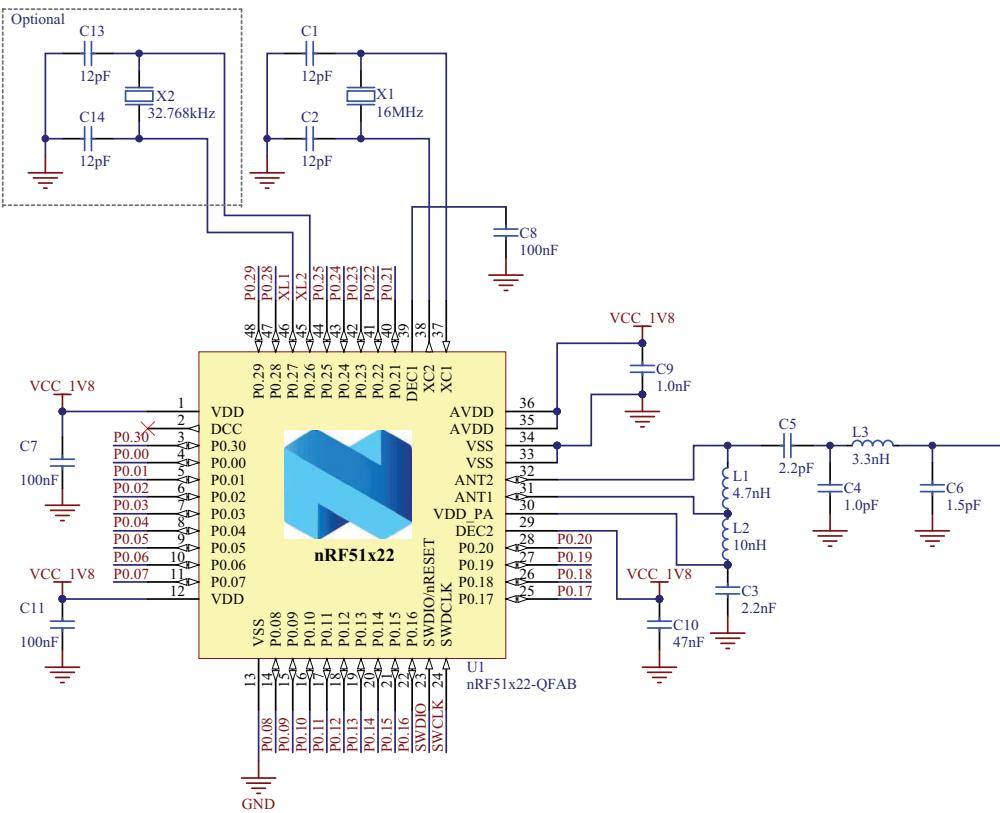

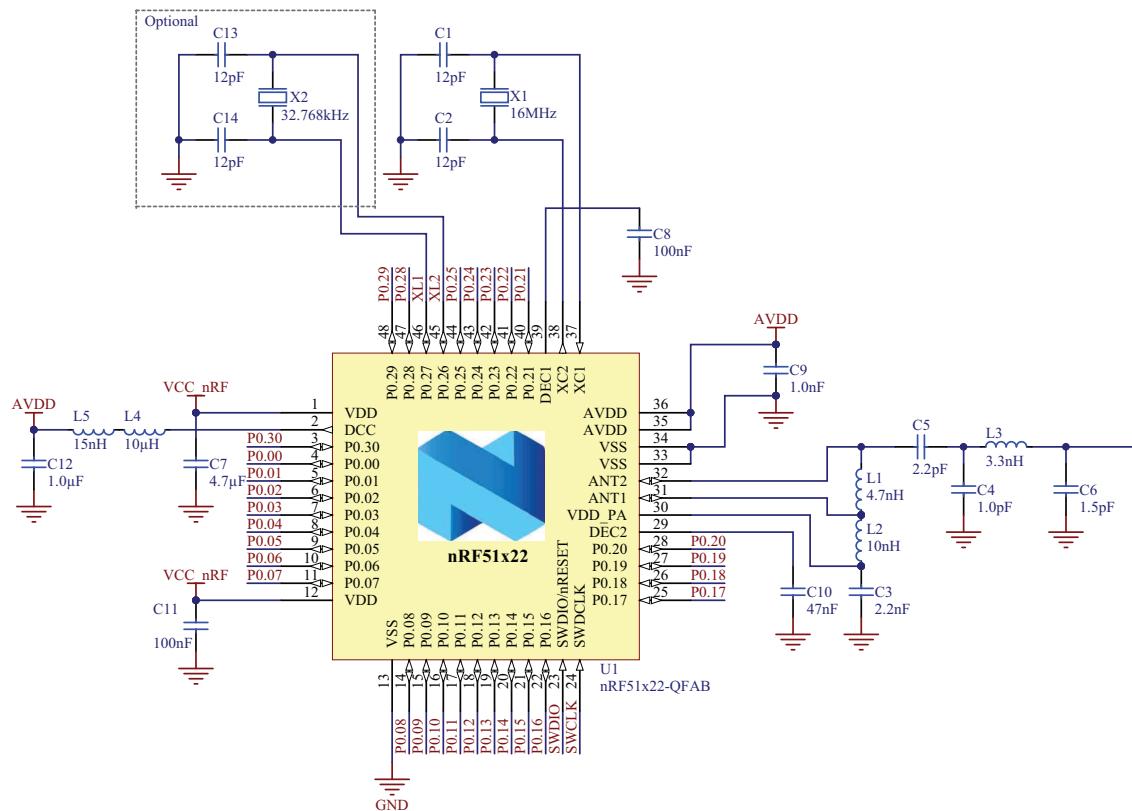

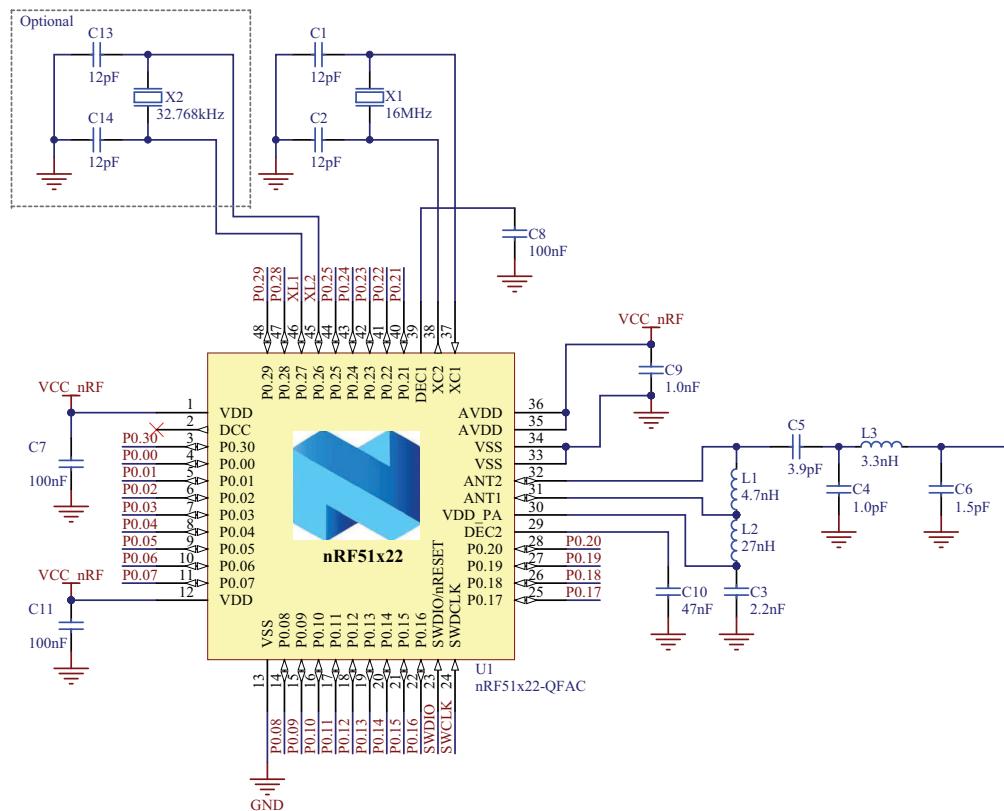

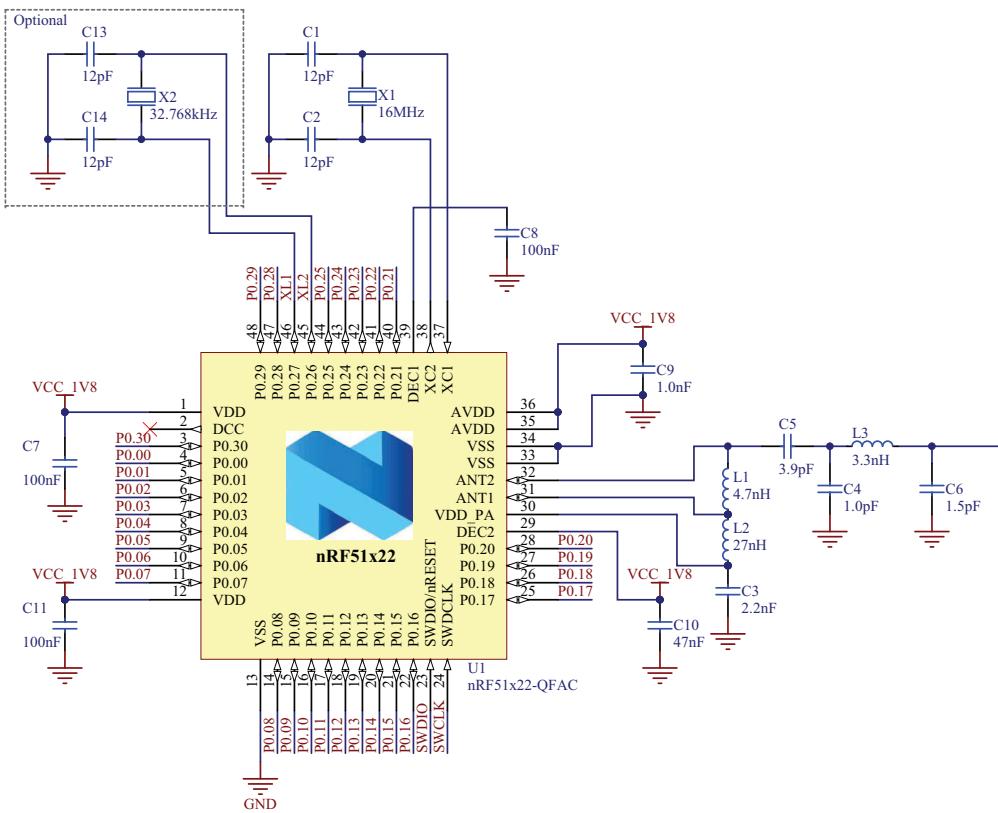

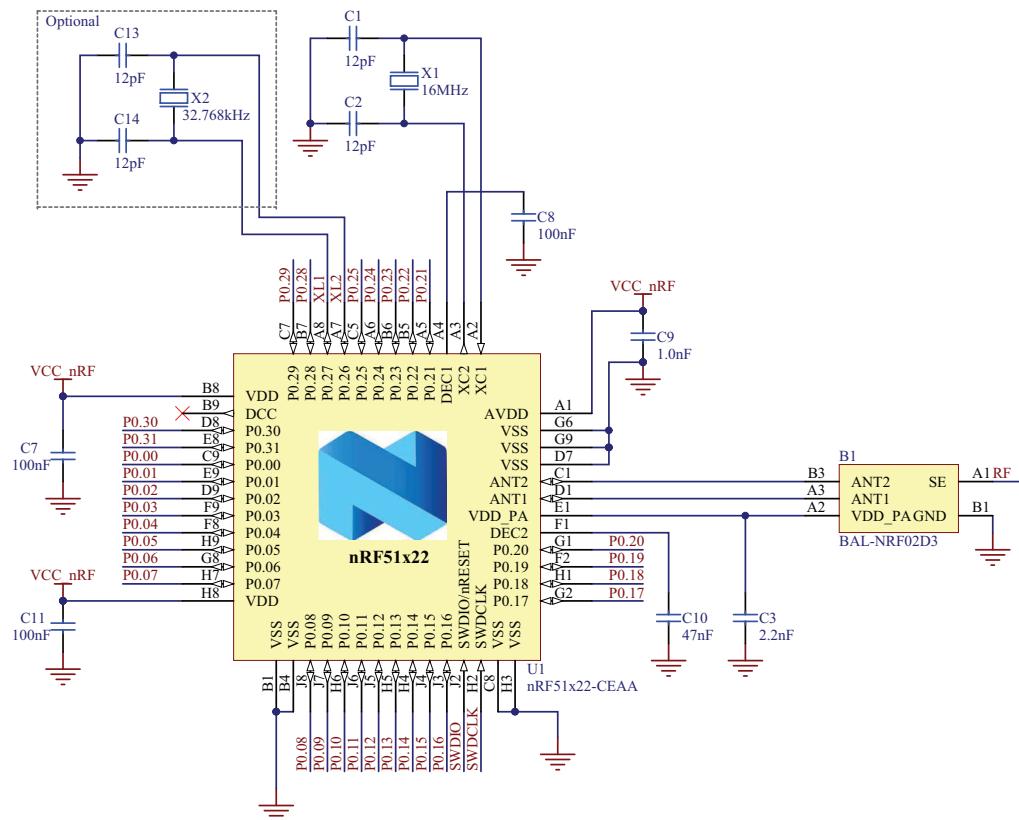

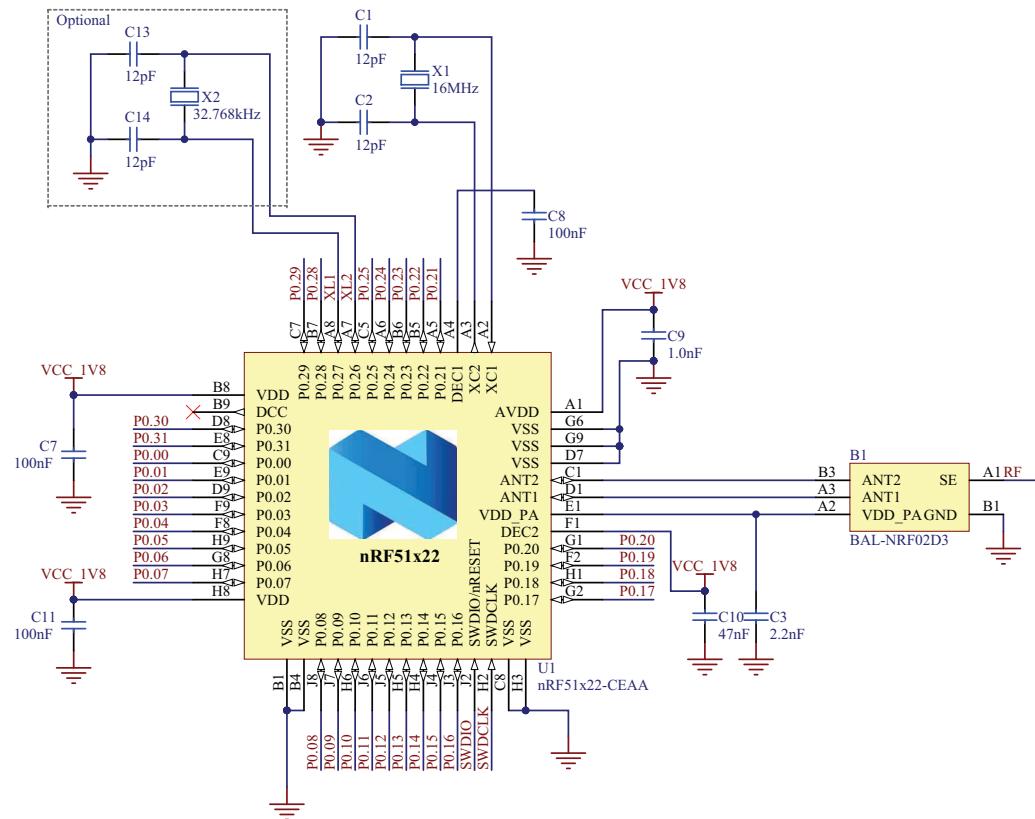

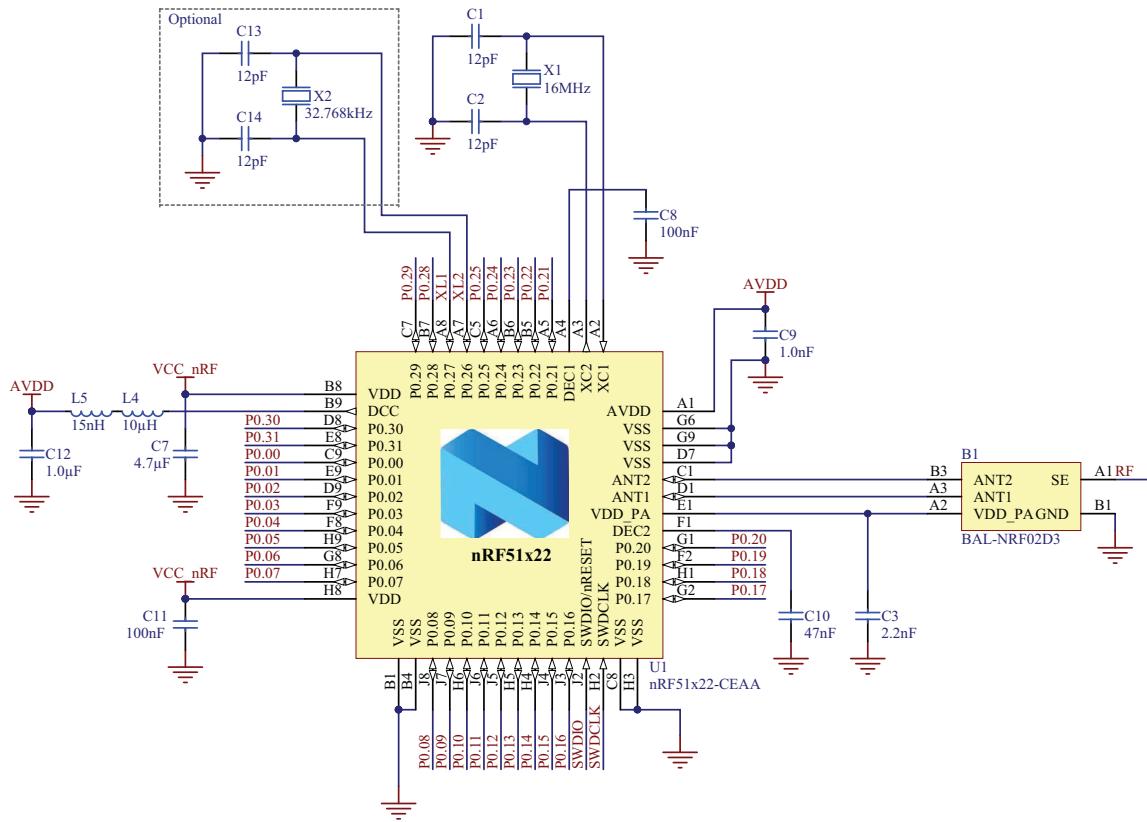

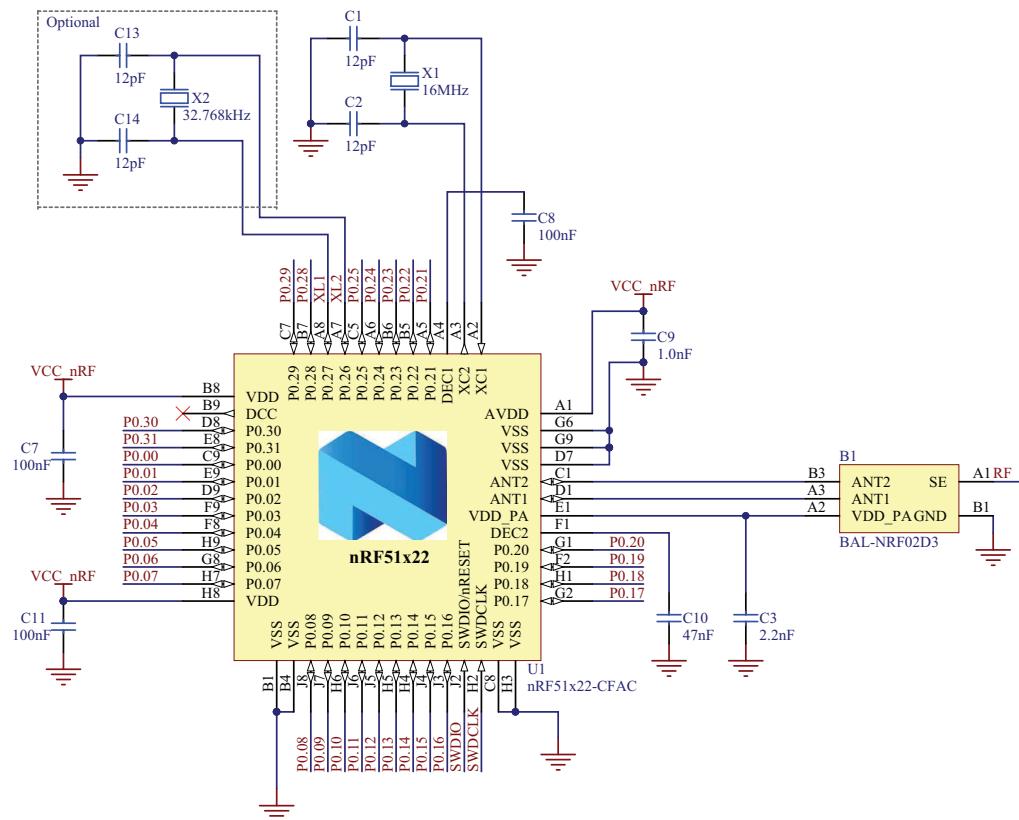

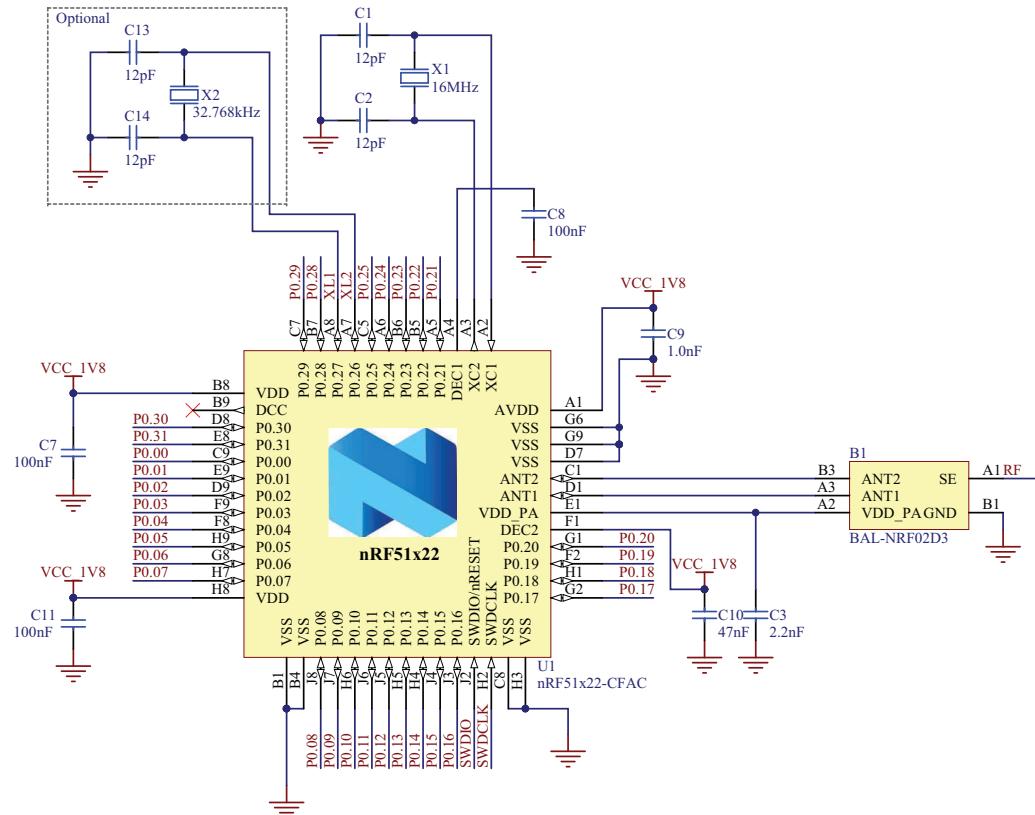

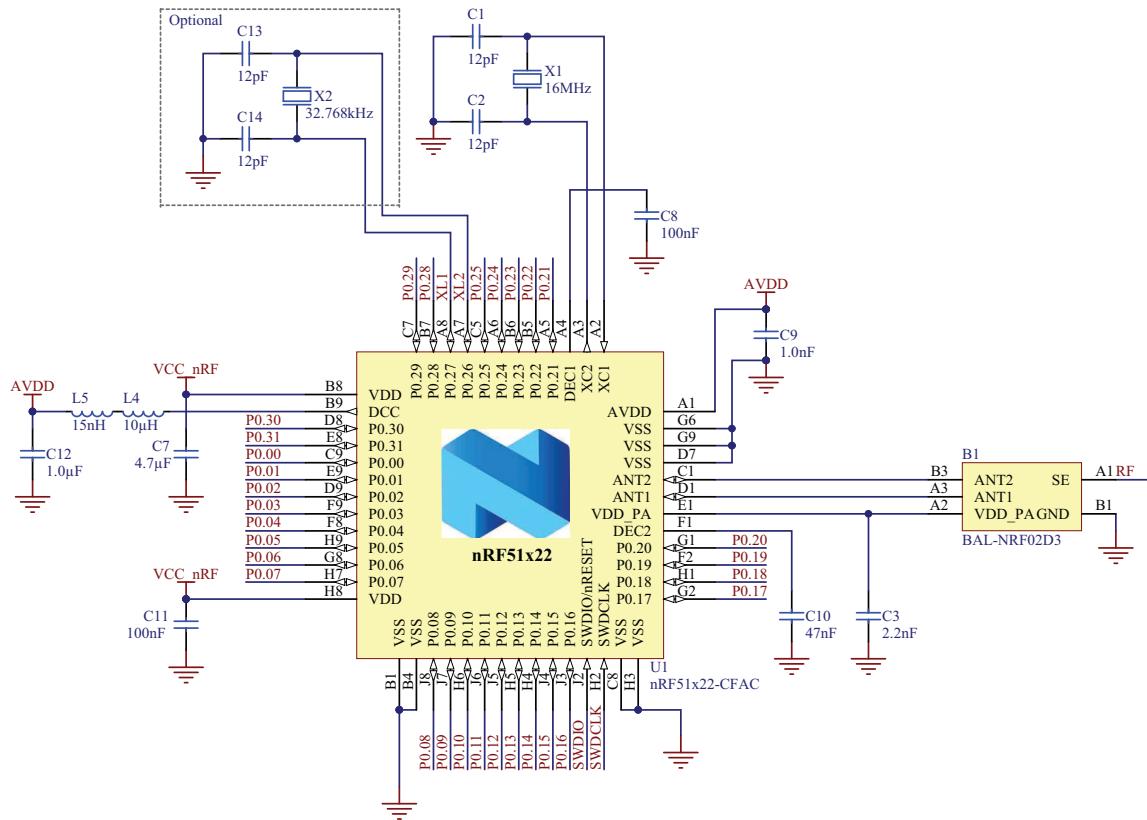

| 11.2      | Reference design schematics.....                                  | 78         |

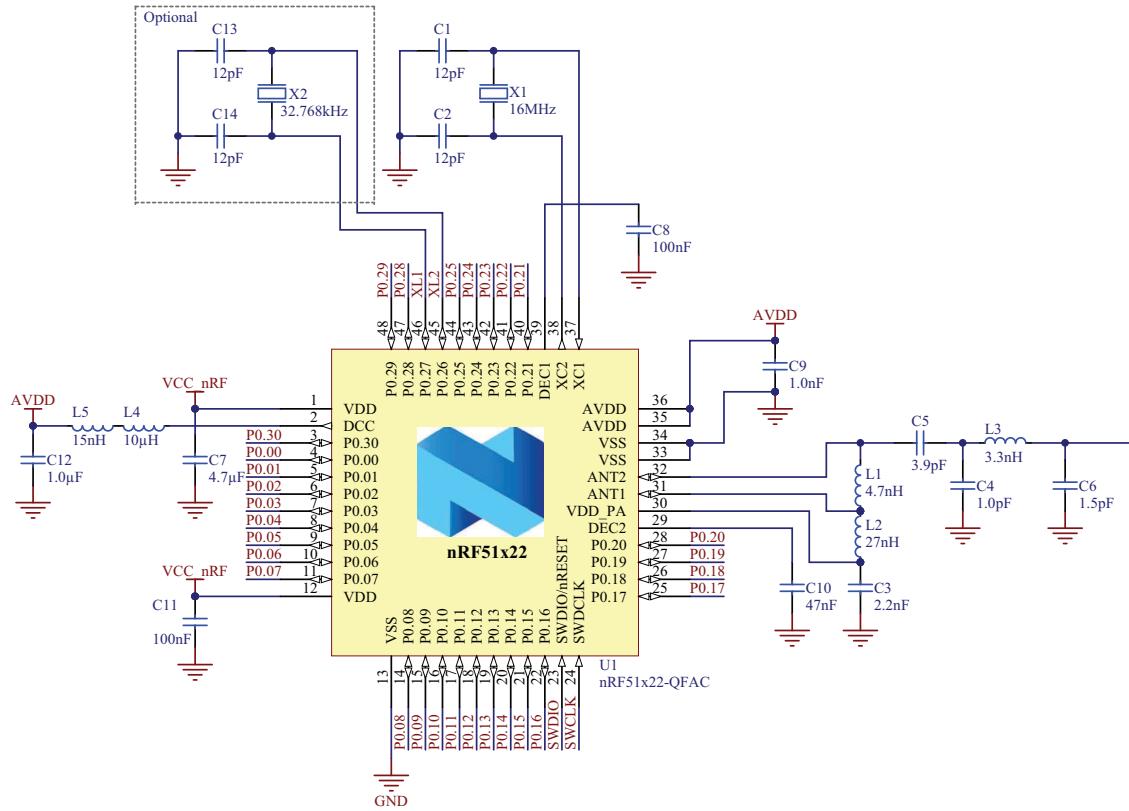

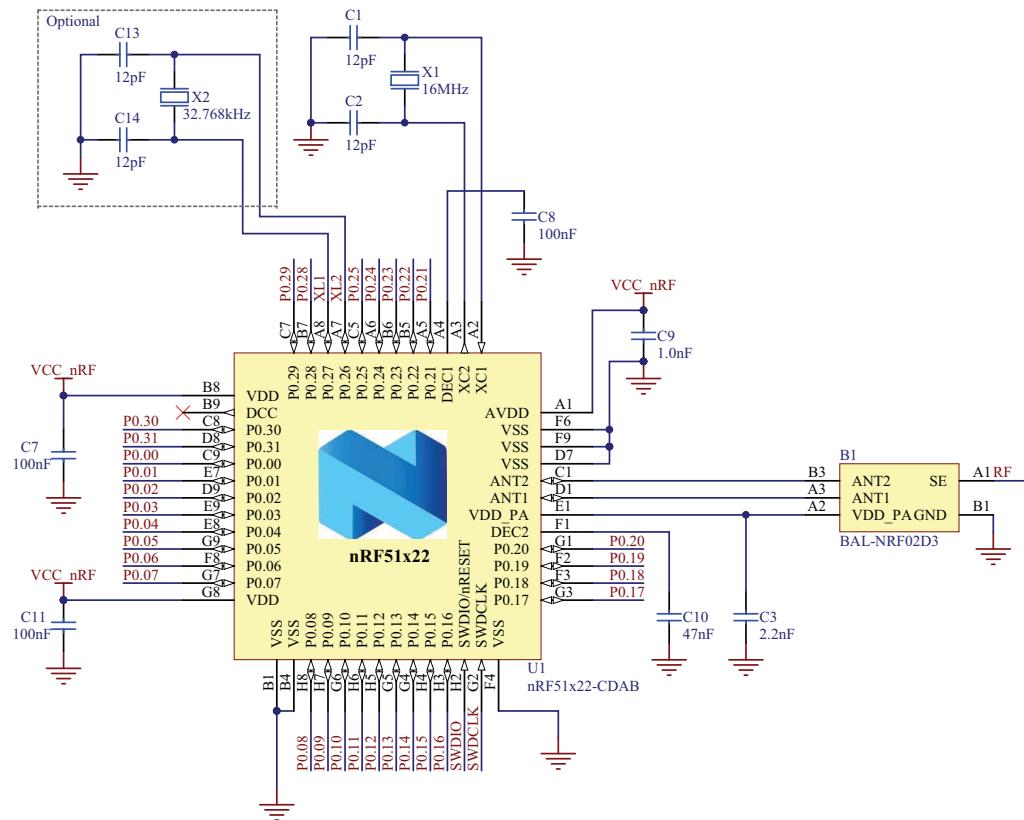

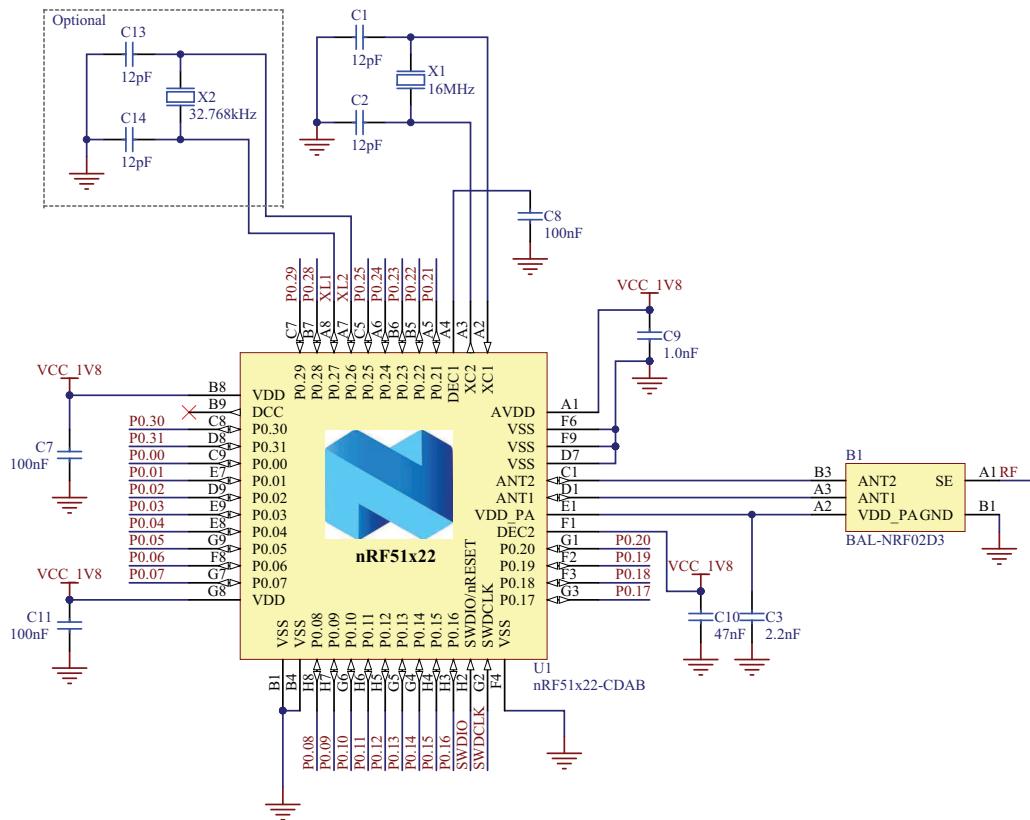

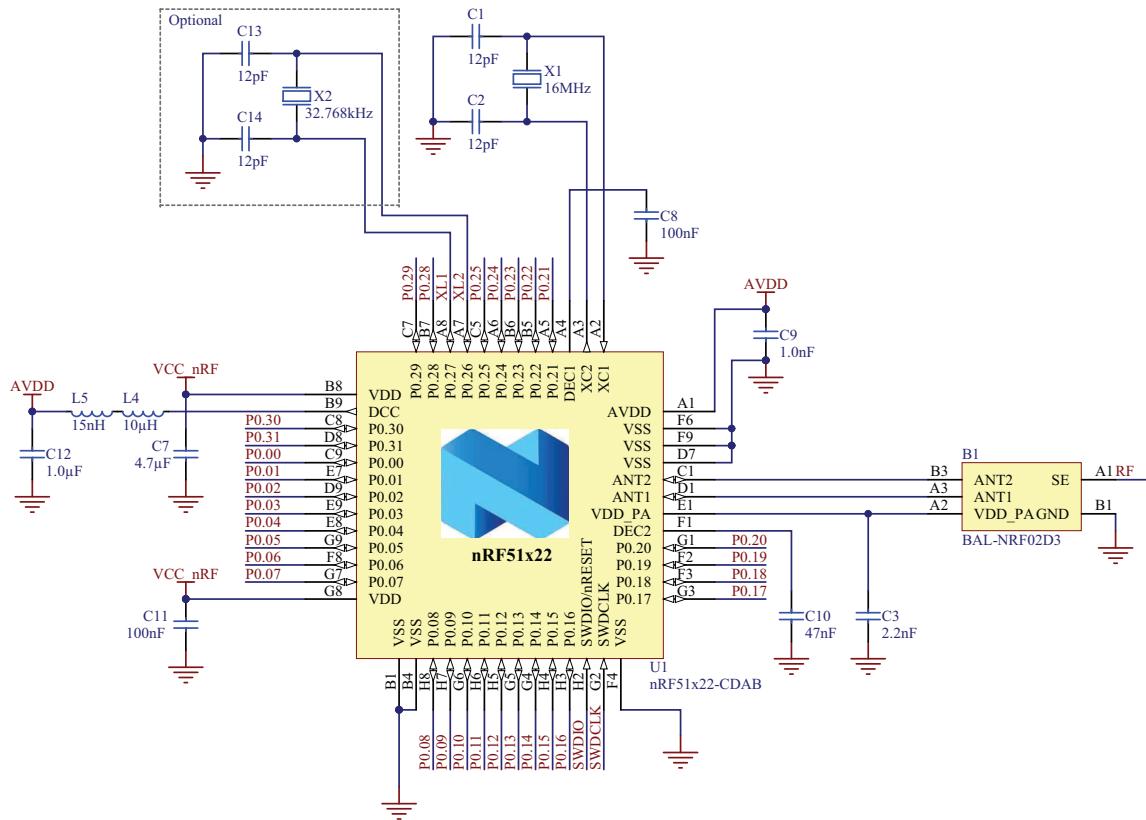

| 11.3      | QFAA QFN48 package .....                                          | 79         |

| 11.4      | QFAB QFN48 package.....                                           | 85         |

| 11.5      | QFAC QFN48 package.....                                           | 91         |

| 11.6      | CDAB WLCSP package .....                                          | 97         |

| 11.7      | CEAA WLCSP package.....                                           | 103        |

| 11.8      | CFAC WLCSP package.....                                           | 109        |

| <b>12</b> | <b>Glossary .....</b>                                             | <b>115</b> |

## 1 Introduction

The nRF51822 is an ultra-low power 2.4 GHz wireless System on Chip (SoC) integrating the nRF51 series 2.4 GHz transceiver, a 32 bit ARM® Cortex™-M0 CPU, flash memory, and analog and digital peripherals. nRF51822 can support *Bluetooth*® low energy and a range of proprietary 2.4 GHz protocols, such as Gazell from Nordic Semiconductor.

Fully qualified *Bluetooth* low energy stacks for nRF51822 are implemented in the S100 series of SoftDevices. The S100 series of SoftDevices are available for free and can be downloaded and installed on nRF51822 independent of your own application code.

### 1.1 Required reading

The following documentation is available for download from [www.nordicsemi.com](http://www.nordicsemi.com):

- *nRF51 Series Reference Manual*

- *nRF51822-PAN (Product Anomaly Notification)*

- *PCN-092 (nRF51822 Product Change Notification)*

### 1.2 Writing conventions

This product specification follows a set of typographic rules to ensure that the document is consistent and easy to read. The following writing conventions are used:

- Command, event names, and bit state conditions, are written in **Lucida Console**.

- Pin names and pin signal conditions are written in **Consolas**.

- File names and User Interface components are written in **bold**.

- Internal cross references are italicized and written in ***semi-bold***.

- Placeholders for parameters are written in italic regular text font. For example, a syntax description of Connect will be written as:

Connect(*TimeOut*, *AdvInterval*).

- Fixed parameters are written in regular text font. For example, a syntax description of Connect will be written as:

Connect(0x00F0, Interval).

## 2 Product overview

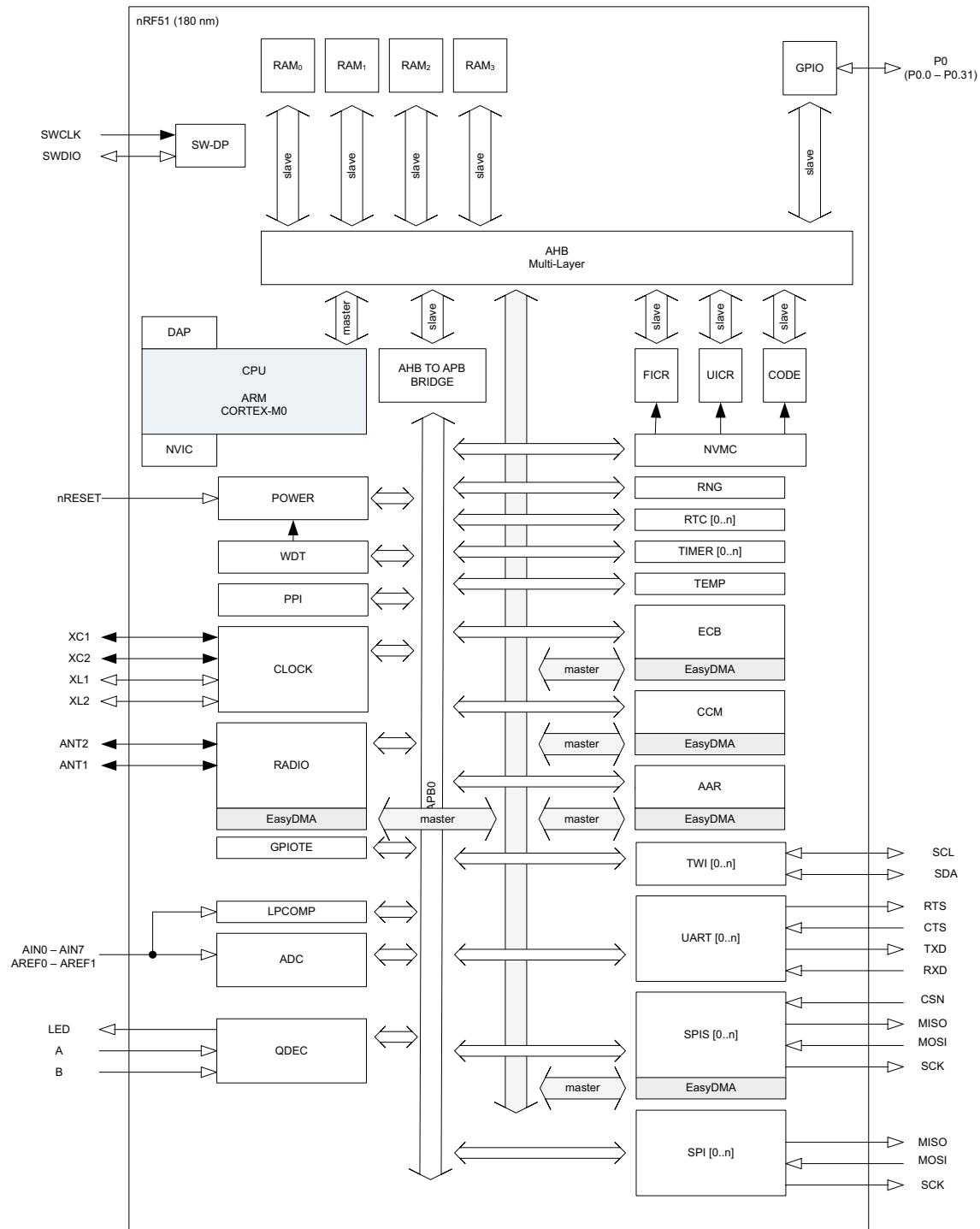

### 2.1 Block diagram

**Figure 1** Block diagram

## 2.2 Pin assignments and functions

This section describes the pin assignment and the pin functions.

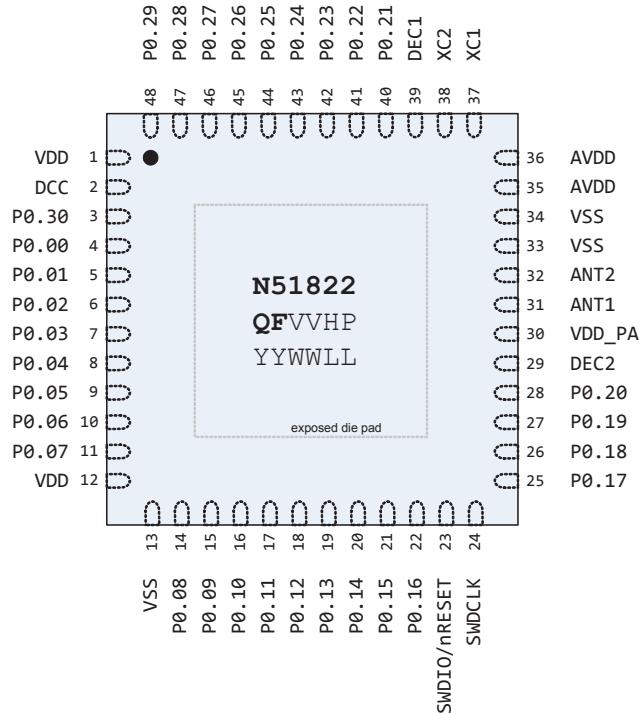

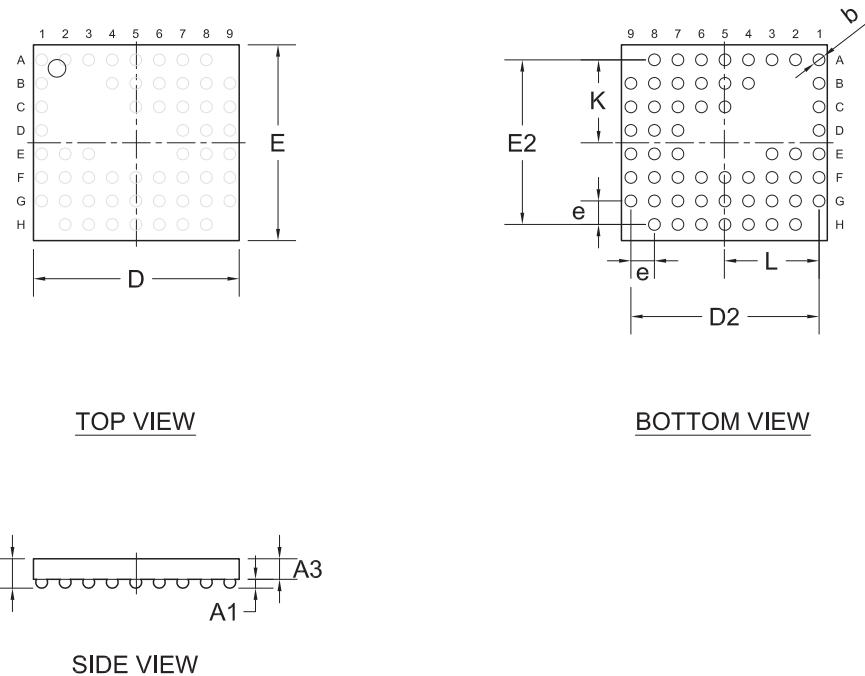

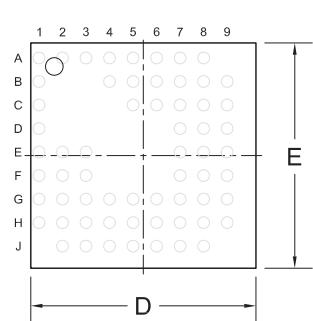

### 2.2.1 Pin assignment QFN48

**Figure 2** Pin assignment - QFN48 packet

**Note:** VV = Variant code, HP = Build code, YYWWLL = Tracking code.

For more information, see [Section 10.6 “Code ranges and values”](#) on page 73.

## 2.2.1.1 Pin functions QFN48

| Pin      | Pin name               | Pin function                                | Description                                                                      |

|----------|------------------------|---------------------------------------------|----------------------------------------------------------------------------------|

| 1        | VDD                    | Power                                       | Power supply.                                                                    |

| 2        | DCC                    | Power                                       | DC/DC output voltage to external LC filter.                                      |

| 3        | P0.30                  | Digital I/O                                 | General purpose I/O pin.                                                         |

| 4        | P0.00<br>AREF0         | Digital I/O<br>Analog input                 | General purpose I/O pin.<br>ADC/LPCOMP reference input 0.                        |

| 5        | P0.01<br>AIN2          | Digital I/O<br>Analog input                 | General purpose I/O pin.<br>ADC/LPCOMP input 2.                                  |

| 6        | P0.02<br>AIN3          | Digital I/O<br>Analog input                 | General purpose I/O pin.<br>ADC/LPCOMP input 3.                                  |

| 7        | P0.03<br>AIN4          | Digital I/O<br>Analog input                 | General purpose I/O pin.<br>ADC/LPCOMP input 4.                                  |

| 8        | P0.04<br>AIN5          | Digital I/O<br>Analog input                 | General purpose I/O pin.<br>ADC/LPCOMP input 5.                                  |

| 9        | P0.05<br>AIN6          | Digital I/O<br>Analog input                 | General purpose I/O pin.<br>ADC/LPCOMP input 6.                                  |

| 10       | P0.06<br>AIN7<br>AREF1 | Digital I/O<br>Analog input<br>Analog input | General purpose I/O pin.<br>ADC/LPCOMP input 7.<br>ADC/LPCOMP reference input 1. |

| 11       | P0.07                  | Digital I/O                                 | General purpose I/O pin.                                                         |

| 12       | VDD                    | Power                                       | Power supply.                                                                    |

| 13       | VSS                    | Power                                       | Ground (0 V) <sup>1</sup> .                                                      |

| 14 to 22 | P0.08 to P0.16         | Digital I/O                                 | General purpose I/O pin.                                                         |

| 23       | SWDIO/nRESET           | Digital I/O                                 | System reset (active low). Also hardware debug and flash programming I/O.        |

| 24       | SWDCLK                 | Digital input                               | Hardware debug and flash programming I/O.                                        |

| 25 to 28 | P0.17 to P0.20         | Digital I/O                                 | General purpose I/O pin.                                                         |

| 29       | DEC2                   | Power                                       | Power supply decoupling.                                                         |

| 30       | VDD_PA                 | Power output                                | Power supply output (+1.6 V) for on-chip RF power amp.                           |

| 31       | ANT1                   | RF                                          | Differential antenna connection (TX and RX).                                     |

| 32       | ANT2                   | RF                                          | Differential antenna connection (TX and RX).                                     |

| 33, 34   | VSS                    | Power                                       | Ground (0 V).                                                                    |

| 35, 36   | AVDD                   | Power                                       | Analog power supply (Radio).                                                     |

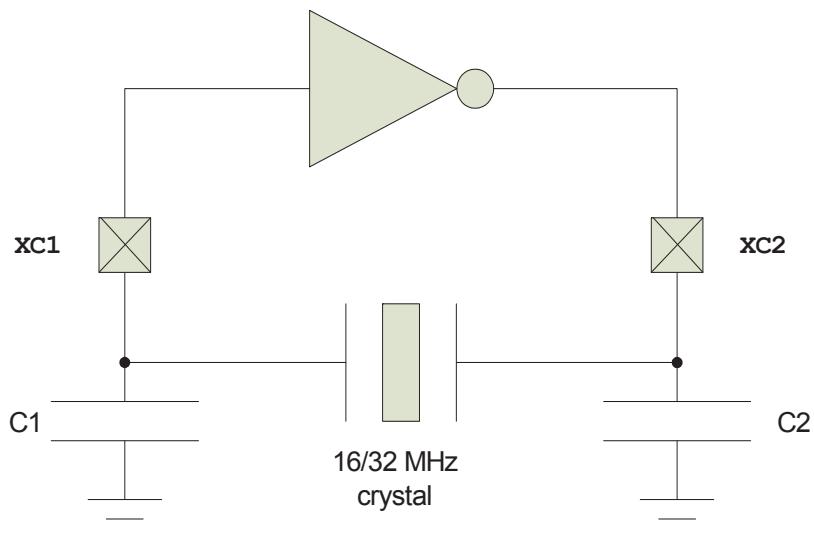

| 37       | XC1                    | Analog input                                | Connection for 16/32 MHz crystal or external 16 MHz clock reference.             |

| 38       | XC2                    | Analog output                               | Connection for 16/32 MHz crystal.                                                |

| 39       | DEC1                   | Power                                       | Power supply decoupling.                                                         |

| Pin      | Pin name             | Pin function                                 | Description                                                                                                                  |

|----------|----------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 40 to 44 | P0.21 to P0.25       | Digital I/O                                  | General purpose I/O pin.                                                                                                     |

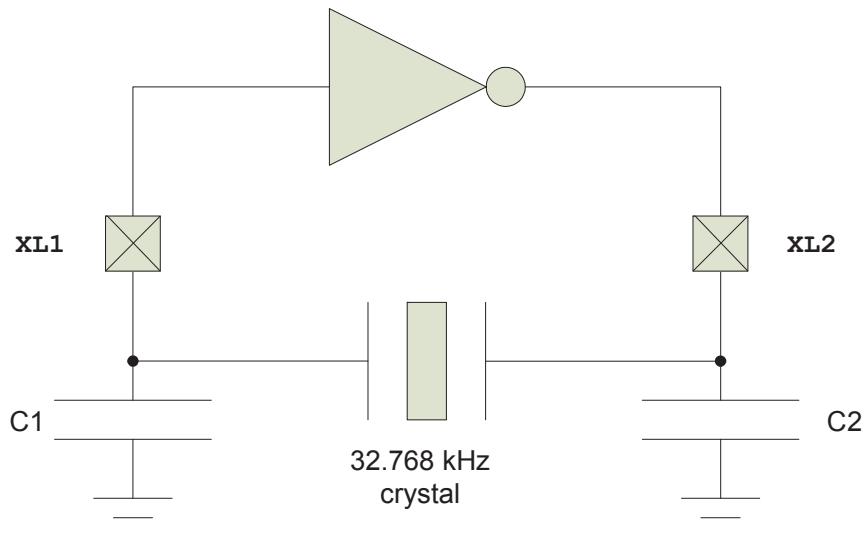

| 45       | P0.26<br>AIN0<br>XL2 | Digital I/O<br>Analog input<br>Analog output | General purpose I/O pin.<br>ADC/LPCOMP input 0.<br>Connection for 32.768 kHz crystal.                                        |

| 46       | P0.27<br>AIN1<br>XL1 | Digital I/O<br>Analog input<br>Analog input  | General purpose I/O pin.<br>ADC/LPCOMP input 1.<br>Connection for 32.768 kHz crystal or external 32.768 kHz clock reference. |

| 47, 48   | P0.28 and P0.29      | Digital I/O                                  | General purpose I/O pin.                                                                                                     |

1. The exposed center pad of the QFN48 package must be connected to ground for proper device operation.

*Table 1 Pin functions QFN48 packet*

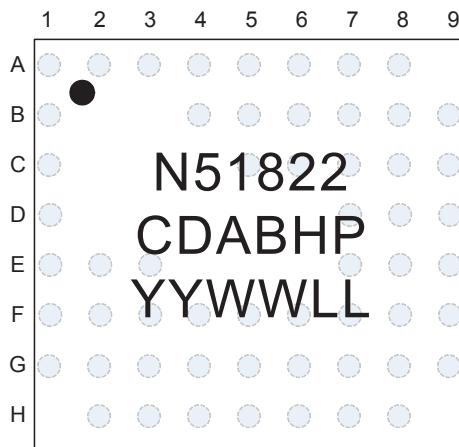

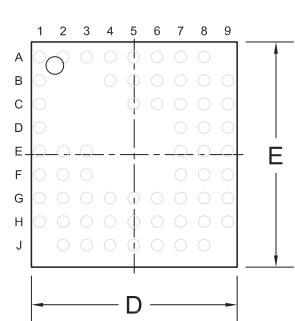

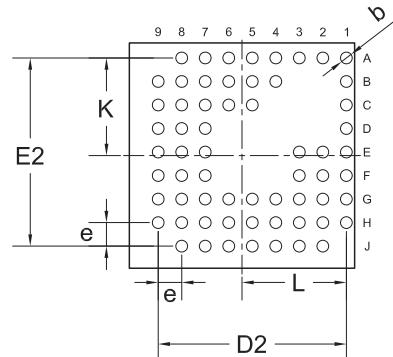

## 2.2.2 CDAB WLCSP ball assignment and functions

*Figure 3 Ball assignment CDAB packet (top side view)*

## 2.2.2.1 Ball functions CDAB

| Ball | Name   | Function      | Description                                                                                    |

|------|--------|---------------|------------------------------------------------------------------------------------------------|

| A1   | AVDD   | Power         | Analog power supply (Radio).                                                                   |

| A2   | XC1    | Analog input  | Crystal connection for 16/32 MHz crystal oscillator or external 16/32 MHz crystal reference.   |

| A3   | XC2    | Analog output | Crystal connection for 16/32 MHz crystal.                                                      |

| A4   | DEC1   | Power         | Power supply decoupling.                                                                       |

| A5   | P0.21  | Digital I/O   | General purpose I/O.                                                                           |

| A6   | P0.24  | Digital I/O   | General purpose I/O.                                                                           |

|      | P0.26  | Digital I/O   | General purpose I/O.                                                                           |

| A7   | AIN0   | Analog input  | ADC input 0.                                                                                   |

|      | XL2    | Analog output | Crystal connection for 32.768 kHz crystal oscillator.                                          |

| A8   | P0.27  | Digital I/O   | General purpose I/O.                                                                           |

|      | AIN1   | Analog input  | ADC input 1.                                                                                   |

|      | XL1    | Analog input  | Crystal connection for 32.768 kHz crystal oscillator or external 32.768 kHz crystal reference. |

| B1   | VSS    | Power         | Ground (0 V).                                                                                  |

| B4   | VSS    | Power         | Ground (0 V).                                                                                  |

| B5   | P0.22  | Digital I/O   | General purpose I/O.                                                                           |

| B6   | P0.23  | Digital I/O   | General purpose I/O.                                                                           |

| B7   | P0.28  | Digital I/O   | General purpose I/O.                                                                           |

| B8   | VDD    | Power         | Power supply.                                                                                  |

| B9   | DCC    | Power         | DC/DC output voltage to external LC filter.                                                    |

| C1   | ANT2   | RF            | Differential antenna connection (TX and RX).                                                   |

| C5   | P0.25  | Digital I/O   | General purpose I/O.                                                                           |

| C6   | N.C.   | No Connection | Must be soldered to PCB.                                                                       |

| C7   | P0.29  | Digital I/O   | General purpose I/O.                                                                           |

| C8   | P0.30  | Digital I/O   | General purpose I/O.                                                                           |

| C9   | P0.00  | Digital I/O   | General purpose I/O.                                                                           |

|      | AREF0  | Analog input  | ADC Reference voltage.                                                                         |

| D1   | ANT1   | RF            | Differential antenna connection (TX and RX).                                                   |

| D7   | VSS    | Power         | Ground (0 V).                                                                                  |

| D8   | P0.31  | Digital I/O   | General purpose I/O.                                                                           |

| D9   | P0.02  | Digital I/O   | General purpose I/O.                                                                           |

|      | AIN3   | Analog input  | ADC input 3.                                                                                   |

| E1   | VDD_PA | Power output  | Power supply output (+1.6 V) for on-chip RF power amp.                                         |

| E2   | N.C.   | No Connection | Must be soldered to PCB.                                                                       |

| E3   | N.C.   | No Connection | Must be soldered to PCB.                                                                       |

| E7   | P0.01  | Digital I/O   | General purpose I/O.                                                                           |

|      | AIN2   | Analog input  | ADC input 2.                                                                                   |

| E8   | P0.04  | Digital I/O   | General purpose I/O.                                                                           |

|      | AIN5   | Analog input  | ADC input 5.                                                                                   |

| Ball | Name                   | Function                                    | Description                                                             |

|------|------------------------|---------------------------------------------|-------------------------------------------------------------------------|

| E9   | P0.03<br>AIN4          | Digital I/O<br>Analog input                 | General purpose I/O.<br>ADC input 4.                                    |

| F1   | DEC2                   | Power                                       | Power supply decoupling.                                                |

| F2   | P0.19                  | Digital I/O                                 | General purpose I/O.                                                    |

| F3   | P0.18                  | Digital I/O                                 | General purpose I/O.                                                    |

| F4   | VSS                    | Power                                       | Ground (0 V).                                                           |

| F5   | N.C.                   | No Connection                               | Must be soldered to PCB.                                                |

| F6   | VSS                    | Power                                       | Ground (0 V).                                                           |

| F7   | N.C.                   | No Connection                               | Must be soldered to PCB.                                                |

| F8   | P0.06<br>AIN7<br>AREF1 | Digital I/O<br>Analog input<br>Analog input | General purpose I/O.<br>ADC input 7.<br>ADC Reference voltage.          |

| F9   | VSS                    | Power                                       | Ground (0 V).                                                           |

| G1   | P0.20                  | Digital I/O                                 | General purpose I/O.                                                    |

| G2   | SWDCLK                 | Digital input                               | Hardware debug and flash programming I/O.                               |

| G3   | P0.17                  | Digital I/O                                 | General purpose I/O.                                                    |

| G4   | P0.14                  | Digital I/O                                 | General purpose I/O.                                                    |

| G5   | P0.13                  | Digital I/O                                 | General purpose I/O.                                                    |

| G6   | P0.10                  | Digital I/O                                 | General purpose I/O.                                                    |

| G7   | P0.07                  | Digital I/O                                 | General purpose I/O.                                                    |

| G8   | VDD                    | Power                                       | Power supply.                                                           |

| G9   | P0.05<br>AIN6          | Digital I/O<br>Analog input                 | General purpose I/O.<br>ADC input 6.                                    |

| H2   | nRESET<br>SWDIO        | Digital I/O                                 | System reset (active low).<br>Hardware debug and flash programming I/O. |

| H3   | P0.16                  | Digital I/O                                 | General purpose I/O.                                                    |

| H4   | P0.15                  | Digital I/O                                 | General purpose I/O.                                                    |

| H5   | P0.12                  | Digital I/O                                 | General purpose I/O.                                                    |

| H6   | P0.11                  | Digital I/O                                 | General purpose I/O.                                                    |

| H7   | P0.09                  | Digital I/O                                 | General purpose I/O.                                                    |

| H8   | P0.08                  | Digital I/O                                 | General purpose I/O.                                                    |

*Table 2 Ball functions CDAB packet*

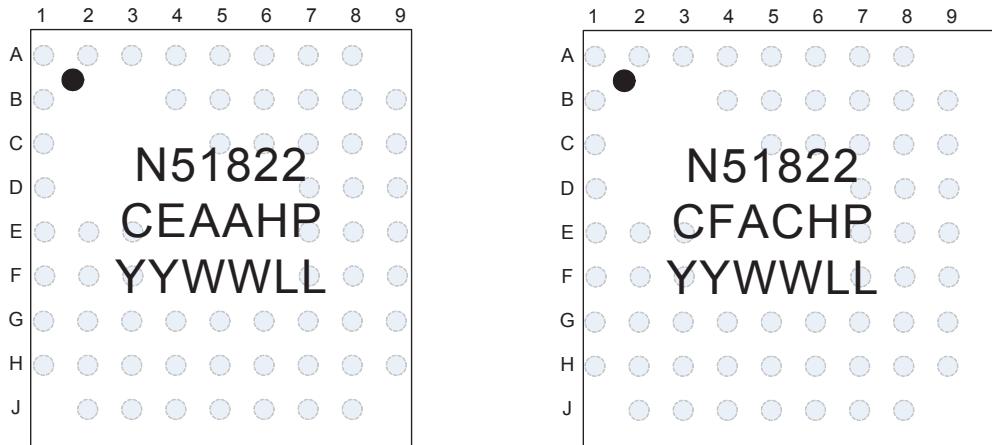

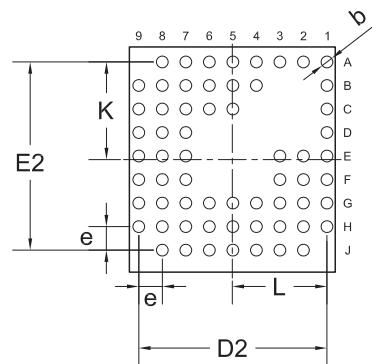

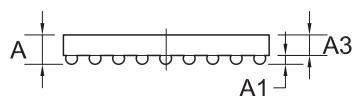

## 2.2.3 CEEA and CFAC WLCSP ball assignment and functions

**Figure 4** Ball assignment CEEA and CFAC packet (top side view)

**Note:** HP = Buildcode, YYWWLL = Tracking code

Solder balls not visible on the top side. Dot denotes A1 corner.

## 2.2.3.1 Ball functions CEAA and CFAC

| Ball | Name   | Function      | Description                                                                                    |

|------|--------|---------------|------------------------------------------------------------------------------------------------|

| A1   | AVDD   | Power         | Analog power supply (Radio).                                                                   |

| A2   | XC1    | Analog input  | Crystal connection for 16/32 MHz crystal oscillator or external 16/32 MHz crystal reference.   |

| A3   | XC2    | Analog output | Crystal connection for 16/32 MHz crystal.                                                      |

| A4   | DEC1   | Power         | Power supply decoupling.                                                                       |

| A5   | P0.21  | Digital I/O   | General purpose I/O.                                                                           |

| A6   | P0.24  | Digital I/O   | General purpose I/O.                                                                           |

|      | P0.26  | Digital I/O   | General purpose I/O.                                                                           |

| A7   | AIN0   | Analog input  | ADC input 0.                                                                                   |

|      | XL2    | Analog output | Crystal connection for 32.768 kHz crystal oscillator.                                          |

| A8   | P0.27  | Digital I/O   | General purpose I/O.                                                                           |

|      | AIN1   | Analog input  | ADC input 1.                                                                                   |

|      | XL1    | Analog input  | Crystal connection for 32.768 kHz crystal oscillator or external 32.768 kHz crystal reference. |

| B1   | VSS    | Power         | Ground (0 V).                                                                                  |

| B4   | VSS    | Power         | Ground (0 V).                                                                                  |

| B5   | P0.22  | Digital I/O   | General purpose I/O.                                                                           |

| B6   | P0.23  | Digital I/O   | General purpose I/O.                                                                           |

| B7   | P0.28  | Digital I/O   | General purpose I/O.                                                                           |

| B8   | VDD    | Power         | Power supply.                                                                                  |

| B9   | DCC    | Power         | DC/DC output voltage to external LC filter.                                                    |

| C1   | ANT2   | RF            | Differential antenna connection (TX and RX).                                                   |

| C5   | P0.25  | Digital I/O   | General purpose I/O.                                                                           |

| C6   | N.C.   | No Connection | Must be soldered to PCB.                                                                       |

| C7   | P0.29  | Digital I/O   | General purpose I/O.                                                                           |

| C8   | VSS    | Power         | Ground (0 V).                                                                                  |

| C9   | P0.00  | Digital I/O   | General purpose I/O.                                                                           |

|      | AREF0  | Analog input  | ADC Reference voltage.                                                                         |

| D1   | ANT1   | RF            | Differential antenna connection (TX and RX).                                                   |

| D7   | VSS    | Power         | Ground (0 V).                                                                                  |

| D8   | P0.30  | Digital I/O   | General purpose I/O.                                                                           |

| D9   | P0.02  | Digital I/O   | General purpose I/O.                                                                           |

|      | AIN3   | Analog input  | ADC input 3.                                                                                   |

| E1   | VDD_PA | Power output  | Power supply output (+1.6 V) for on-chip RF power amp.                                         |

| E2   | N.C.   | No Connection | Must be soldered to PCB.                                                                       |

| E3   | N.C.   | No Connection | Must be soldered to PCB.                                                                       |

| E7   | N.C.   | No Connection | Must be soldered to PCB.                                                                       |

| E8   | P0.31  | Digital I/O   | General purpose I/O.                                                                           |

| E9   | P0.01  | Digital I/O   | General purpose I/O.                                                                           |

|      | AIN2   | Analog input  | ADC input 2.                                                                                   |

| Ball | Name                   | Function                                    | Description                                                               |

|------|------------------------|---------------------------------------------|---------------------------------------------------------------------------|

| F1   | DEC2                   | Power                                       | Power supply decoupling.                                                  |

| F2   | P0.19                  | Digital I/O                                 | General purpose I/O.                                                      |

| F3   | N.C.                   | No Connection                               | Must be soldered to PCB.                                                  |

| F7   | N.C.                   | No Connection                               | Must be soldered to PCB.                                                  |

| F8   | P0.04<br>AIN5          | Digital I/O<br>Analog input                 | General purpose I/O.<br>ADC input 5.                                      |

| F9   | P0.03<br>AIN4          | Digital I/O<br>Analog input                 | General purpose I/O.<br>ADC input 4.                                      |

| G1   | P0.20                  | Digital I/O                                 | General purpose I/O.                                                      |

| G2   | P0.17                  | Digital I/O                                 | General purpose I/O.                                                      |

| G3   | N.C.                   | No Connection                               | Must be soldered to PCB.                                                  |

| G4   | N.C.                   | No Connection                               | Must be soldered to PCB.                                                  |

| G5   | N.C.                   | No Connection                               | Must be soldered to PCB.                                                  |

| G6   | VSS                    | Power                                       | Ground (0 V).                                                             |

| G7   | N.C.                   | No Connection                               | Must be soldered to PCB.                                                  |

| G8   | P0.06<br>AIN7<br>AREF1 | Digital I/O<br>Analog input<br>Analog input | General purpose I/O.<br>ADC input 7.<br>ADC Reference voltage.            |

| G9   | VSS                    | Power                                       | Ground (0 V).                                                             |

| H1   | P0.18                  | Digital I/O                                 | General purpose I/O.                                                      |

| H2   | SWDCLK                 | Digital input                               | Hardware debug and flash programming I/O.                                 |

| H3   | VSS                    | Power                                       | Ground (0 V).                                                             |

| H4   | P0.14                  | Digital I/O                                 | General purpose I/O.                                                      |

| H5   | P0.13                  | Digital I/O                                 | General purpose I/O.                                                      |

| H6   | P0.10                  | Digital I/O                                 | General purpose I/O.                                                      |

| H7   | P0.07                  | Digital I/O                                 | General purpose I/O.                                                      |

| H8   | VDD                    | Power                                       | Power supply.                                                             |

| H9   | P0.05<br>AIN6          | Digital I/O<br>Analog input                 | General purpose I/O.<br>ADC input 6.                                      |

| J2   | SWDIO/<br>nRESET       | Digital I/O                                 | System reset (active low). Also Hardware debug and flash programming I/O. |

| J3   | P0.16                  | Digital I/O                                 | General purpose I/O.                                                      |

| J4   | P0.15                  | Digital I/O                                 | General purpose I/O.                                                      |

| J5   | P0.12                  | Digital I/O                                 | General purpose I/O.                                                      |

| J6   | P0.11                  | Digital I/O                                 | General purpose I/O.                                                      |

| J7   | P0.09                  | Digital I/O                                 | General purpose I/O.                                                      |

| J8   | P0.08                  | Digital I/O                                 | General purpose I/O.                                                      |

Table 3 Ball functions for CEAA and CFAC

## 3 System blocks

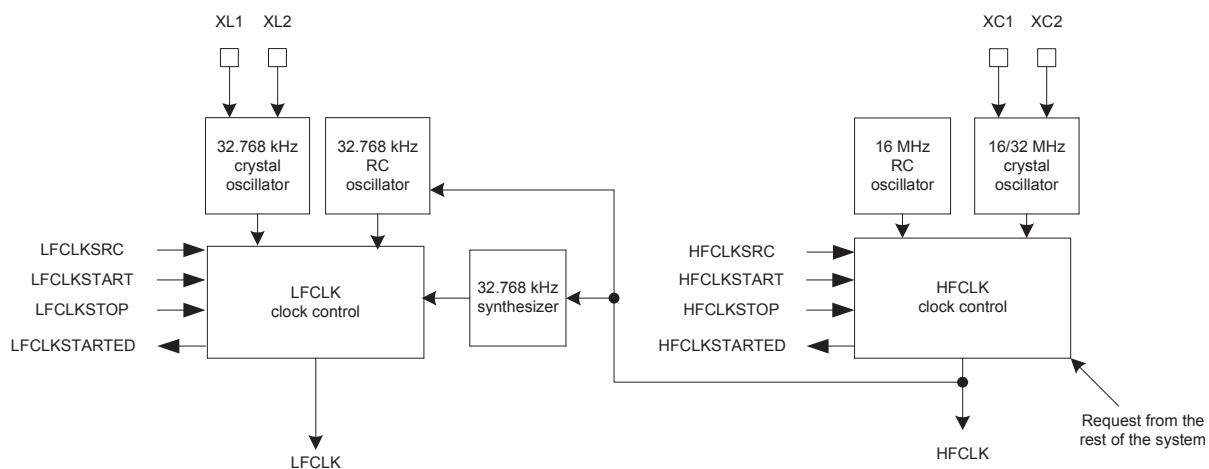

The chip contains system-level features common to all nRF51 series devices including clock control, power and reset, interrupt system, Programmable Peripheral Interconnect (PPI), watchdog, and GPIO.

System blocks which have a register interface and/or interrupt vector assigned are instantiated in the device address space. The instances of system blocks, their associated ID (for those with interrupt vectors), and base addresses are found in *Table 18* on page 36. Detailed functional descriptions, configuration options, and register interfaces can be found in the *nRF51 Series Reference Manual*.

### 3.1 CPU

The ARM® Cortex™-M0 CPU has a 16 bit instruction set with 32 bit extensions ([Thumb-2® technology](#)) that delivers high-density code with a small-memory-footprint. By using a single-cycle 32 bit multiplier, a 3-stage pipeline, and a Nested Vector Interrupt Controller (NVIC), the ARM Cortex-M0 CPU makes program execution simple and highly efficient.

The ARM Cortex Microcontroller Software Interface Standard (CMSIS) hardware abstraction layer for the ARM Cortex-M processor series is implemented and available for M0 CPU. Code is forward compatible with ARM Cortex M3 based devices.

## 3.2 Memory

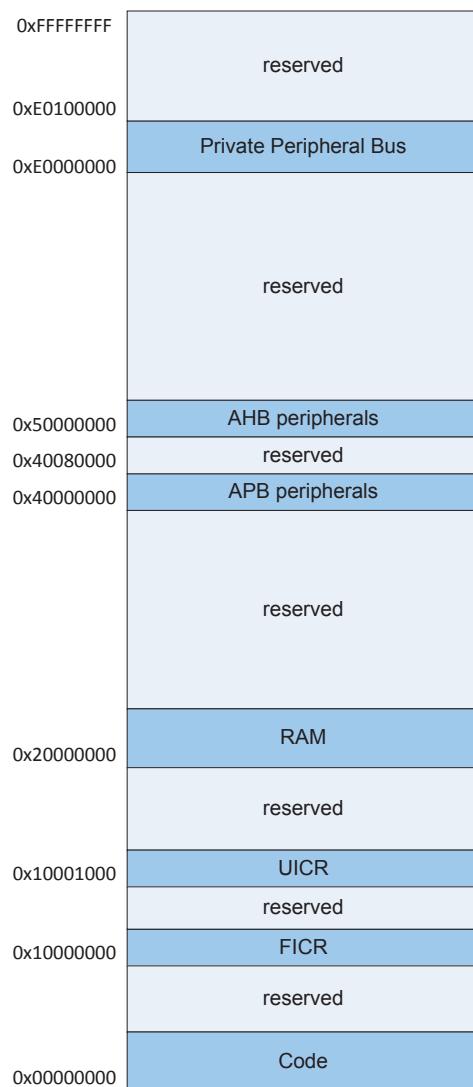

All memory and registers are found in the same address space as shown in the Device Memory Map, see *Figure 5*. Devices in the nRF51 series use flash based memory in the code, FICR, and UICR regions. The RAM region is SRAM.

**Figure 5** Memory Map

The embedded flash memory for program and static data can be programmed using In Application Programming (IAP) routines from RAM through the SWD interface, or in-system from a program executing from code area. The Non-Volatile Memory Controller (NVMC) is used for program/erase operations. Regions of flash memory can be protected from read, write, and erase by the Memory Protection Unit (MPU). A User Information Configuration Register (UICR) contains the lock byte for enabling readback protection to secure the IP, while individual block protection is controlled using registers which can only be cleared on chip reset.

### 3.2.1 Code organization

| Chip variant  | Code size | Page size | No of pages |

|---------------|-----------|-----------|-------------|

| nRF51822-QFAA | 256 kB    | 1024 byte | 256         |

| nRF51822-CEAA |           |           |             |

| nRF51822-QFAB | 128 kB    | 1024 byte | 128         |

| nRF51822-CDAB |           |           |             |

| nRF51822-QFAC | 256 kB    | 1024 byte | 256         |

| nRF51822-CFAC |           |           |             |

*Table 4 Code organization*

### 3.2.2 RAM organization

RAM is divided into blocks for separate power management which is controlled by the POWER System Block. Each block is divided into two 4 kByte RAM sections with separate RAM AHB slaves. Please see the *nRF51 Series Reference Manual* for more information.

| Chip variant  | RAM size | Block  | Size |

|---------------|----------|--------|------|

| nRF51822-QFAA | 16 kB    | Block0 | 8 kB |

| nRF51822-CEAA |          | Block1 | 8 kB |

| nRF51822-QFAB | 16 kB    | Block0 | 8 kB |

| nRF51822-CDAB |          | Block1 | 8 kB |

| nRF51822-QFAC | 32 kB    | Block0 | 8 kB |

| nRF51822-CFAC |          | Block1 | 8 kB |

|               |          | Block2 | 8 kB |

|               |          | Block3 | 8 kB |

*Table 5 RAM organization*

#### How to organize the use of the RAM

For the best performance we recommend the following use of the RAM AHB slaves (Note that the Crypto consists of CCM, ECB, and AAR modules):

- If the Radio and Crypto buffers together are larger in size than one RAM section, the buffers should be separated so the memory used by the Radio is in one RAM section while the memory used by the Crypto is in another RAM section.

- The sections used by CODE should not be combined with sections used by the Radio, Crypto, or SPI.