**Theoretical processing gain and Jammer to Signal ratios (11 Mbps DSSS radio).**

| Data rate (Mbps) | Modulation type | Symbol rate (SyR)      |                     | Processing gain<br>$Gp=10\log(SpR/SyR)$ | (S/N) <sub>o</sub> + Lsys (dB) | Calculated J/S (dB) | Allowed J/S for 10 dB PG, 10dB - (S/N) <sub>o</sub> + Lsys (dB) |

|------------------|-----------------|------------------------|---------------------|-----------------------------------------|--------------------------------|---------------------|-----------------------------------------------------------------|

|                  |                 | Symbols/second (Msp/s) | Chips/symbol (Mcps) |                                         |                                |                     |                                                                 |

| 2                | DBPSK           | 1                      | 11                  | 10.4                                    | 21.3                           | -10.9               | -11.3                                                           |

| 11               | CCK             | 1.375                  | 8                   | 7.6                                     | 19.0                           | -11.4               | -9.0                                                            |

All data as stated above has been provided by Intersil and the datasheet of the HFA3861A DSSS baseband processor.

**HFA3861A**

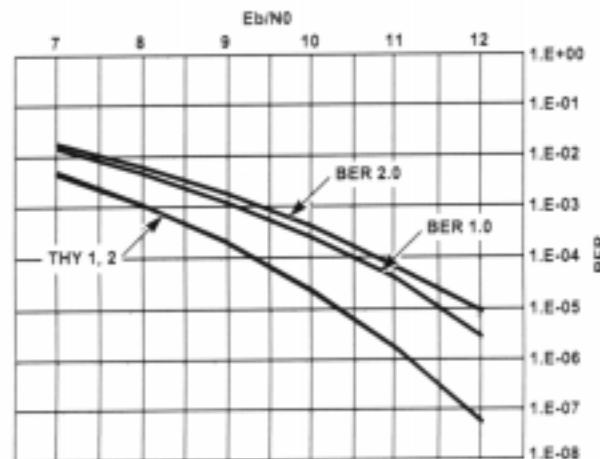

FIGURE 14. BER vs Eb/N0 PERFORMANCE FOR PSK MODES

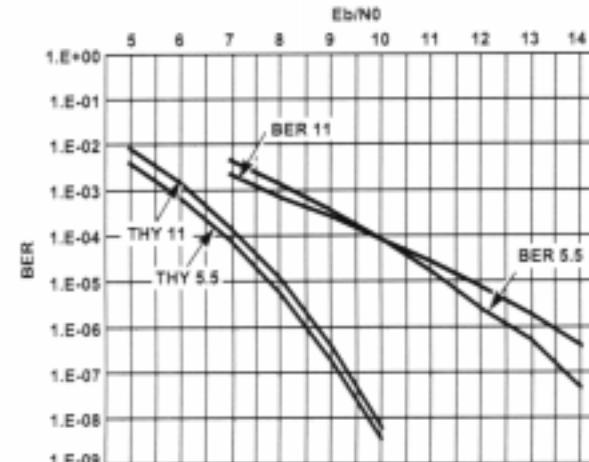

FIGURE 15. BER vs Eb/N0 PERFORMANCE FOR CCK MODES

Figure 1 - Copy of datasheet

Explanation of theoretical processing gain calculations.

**BER = 1.E-5, Data rate = 2 Mbps**

$$G_p = 10\log(S_{pr}/S_{yr}) = 10\log(11/1) = 10.4$$

$$E_b/N_0 = 10.3 \text{ dB} \text{ (from figure 1, copy of datasheet of DSSS baseband processor)}$$

$$(S/N)_o = E_s/N_0 = E_b/N_0 + \text{correction factor for 8 bits/symbol} = 10.3 \text{ dB} + 10\log(8) \text{ dB} = 10.3 \text{ dB} + 9 \text{ dB} = 19.3 \text{ dB}$$

$$L_{sys} = 2 \text{ dB max.}$$

$$G_p = (S/N)_o + M_j + L_{sys}$$

$$\text{Calculated } M_j = J/S = G_p - (S/N)_o - L_{sys} = 10.4 \text{ dB} - 19.3 \text{ dB} - 2 \text{ dB} = -10.9 \text{ dB}$$

$$\text{Allowed } J/S \text{ for 10 dB PG} = G_p - (S/N)_o - L_{sys} = 10 \text{ dB} - (S/N)_o - L_{sys} = 10 \text{ dB} - 19.3 \text{ dB} - 2 \text{ dB} = -11.3 \text{ dB}$$

**BER = 1.E-5, Data rate = 11 Mbps**

$$G_p = 10\log(S_{pr}/S_{yr}) = 10\log(8/1.375) = 7.6$$

$$E_b/N_0 = 8 \text{ dB} \text{ (from figure 1, copy of datasheet of DSSS baseband processor)}$$

$$(S/N)_o = E_s/N_0 = E_b/N_0 + \text{correction factor for 8 bits/symbol} = 8 \text{ dB} + 10\log(8) \text{ dB} = 8 \text{ dB} + 9 \text{ dB} = 17 \text{ dB}$$

$$L_{sys} = 2 \text{ dB max.}$$

$$G_p = (S/N)_o + M_j + L_{sys}$$

$$\text{Calculated } M_j = J/S = G_p - (S/N)_o - L_{sys} = 7.6 \text{ dB} - 17 \text{ dB} - 2 \text{ dB} = -11.4 \text{ dB}$$

$$\text{Allowed } J/S \text{ for 10 dB PG} = G_p - (S/N)_o - L_{sys} = 10 \text{ dB} - (S/N)_o - L_{sys} = 10 \text{ dB} - 17 \text{ dB} - 2 \text{ dB} = -9 \text{ dB}$$