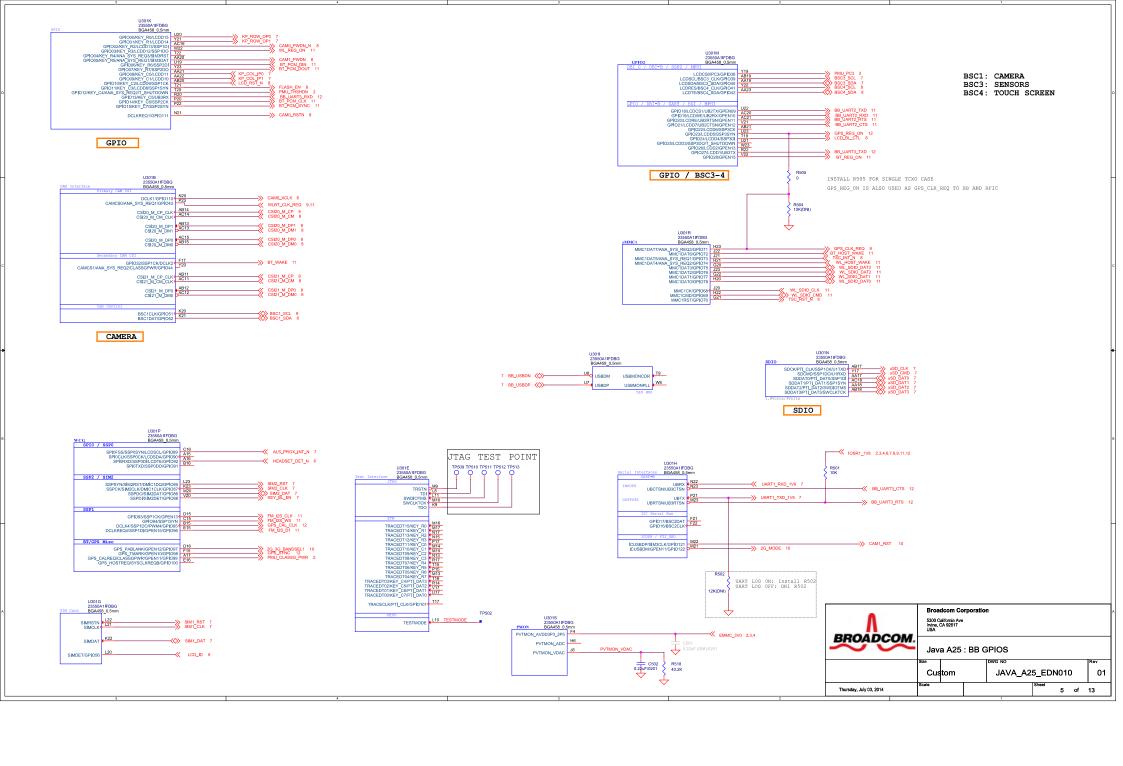

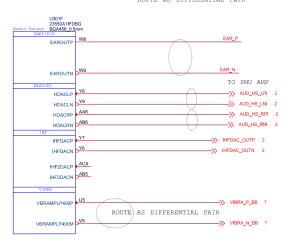

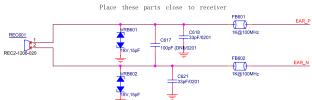

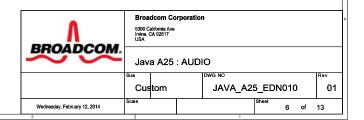

## EARPIECE

ROUTE AS DIFFERENTIAL PAIR

Stereo PA: DNI by default

## WLAN/BT/FM **Dual-Band, Single Antenna** L1102 3.9nH (DNI) GA0000110-1207-B 早 L1101 3.9nH (DNI) C1101 10pF WL\_2G\_RXIN C1102 10pF WRF RFOUT 2G WRF RFOUT 5G ANT1301 GA0000110-1207-B R1315 \_ 0 FM\_TX 早 FL3 LTB-2012-2G4H6-B14-RU 2.4GHz NC = 2 C1103 10pF WRF\_GPIO\_OUT E4\_\_ C1105 | 10pF GND 3.6nH(NC) C1107 C1108 C1109 G3 WRF\_TCXO\_IN 10pF Place shunt caps close to SP3T switch SW\_CTRLS were arranged this way for routability BGA133\_0.4mm OUT1 (RX) => VCONT1 = low; VCONT2 = high OUT2 (TX) => VCONT1 = high; VCONT2 = low VMBAT\_4330 2,7,8,10,12 VMBAT>> Use 2 vias to tie the GND pads to a GND C1111 4.7uF M10 Place these LDO's caps close to chip VOUT\_3P1 FM\_AOUT1 B12 FM\_AOUT2 C1114 4.7uF VOUT\_CLDO VDDIO\_RF C1115 4.7uF VOUT\_LNLDO1 WL\_VDDC\_E7 WL\_VDDC\_K7 WL\_VDDC\_K1 BT\_VDDC\_E8 F5 JTAG\_SEL pin E9 = CLK\_REQ mode NC\_E9 NC\_D7 BT\_CLK\_REQ\_OUT WRF\_VCOLDO\_OUT\_1P2 FB1102 EXT\_SMPS\_REQ EXT\_PWM\_REQ PMU\_AVSS WRF\_GND SDIO DATA : WLBT CLK REQ 5,9 VDDIO assumes 1.8V: max 0.22uF SDIO DATA 3 SDIO DATA 1 SDIO DATA 1 SDIO DATA 0 SDIO CMD BT I2S\_WS BT\_I2S\_CLK BT\_GPIO\_5 BT\_GPIO\_4 BT\_GPIO\_3 BT\_GPIO\_2 BT\_GPIO\_1 BT\_GPIO\_0 2,3,4,5,6,7,8,9,12 IOSR1\_1V8 120@100N FB1104 C1117 0.1uF WRF GND 25 WRF GND IM 25 WRF GND IM 25 RF\_LÖGEN, A, GND F1 WRF\_VCO\_GND H2 WRF\_PA\_GND\_86 WRF\_PA\_GND\_84 WRF\_PA\_GND\_84 WRF\_PA\_GND\_84 WRF\_PA\_GND\_84 WRF\_PA\_GND\_84 WRF\_PA\_GND\_84 WRF\_PA\_GND\_84 WRF\_PA\_GND\_85 L5 WL\_VSS\_1 WL\_VSS\_1 F8 WL VDDIO Place C1119 close to pin M3 BT\_I2S\_DI BT\_I2S\_DO 120@100N FB1105 C1118 0.1uF Route pin A4 directly to C1120; route pin C3 directly to C1121. Use two vias to tie GND pad of capacitors to GND plane. BT\_VDDIO 0.1uF C1120 4.7uF WL\_GPIO\_6 WL\_GPIO\_5 WL\_GPIO\_3 WL\_GPIO\_2 WL\_GPIO\_1 WL\_GPIO\_0 C1122 0.1uF VOUT\_3P3 VDD\_WRF power pins (chip) VDD\_LNLDQ1 BT\_VSSC HSIC\_DATA HSIC\_STROBE HSIC\_RREF HSIC\_AVSS G11 BT\_TM0 WRF XTAL VDD1P2 F3 600@100MHz C1126 WRF\_TCXO\_VDD BCM4330XKUBG BGA133\_0.4mm Ideally, tie each GND pin to a GND plane to reduce GND bounce. If no room, tie GND balls together only if they have the same netname. Otherwise, connect each pin to a GND plane 0.22uF WRF\_VDD\_VCOLDO\_IN\_1P8 VDD\_BT BT\_VCOVDD1P2 BT\_PLLVDD1P2 BT\_RFVDD1P2 BT\_IFVDD1P2 FM\_PLLVSS C9 0.22uF BCM4330XKUBO **Broadcom Corporation** 5300 California Ave Irvine, CA 92617 **BROADCOM** Java A25: WLAN/BT/FM - BCM4330 Custom JAVA\_A25\_EDN010 01 11 of 13

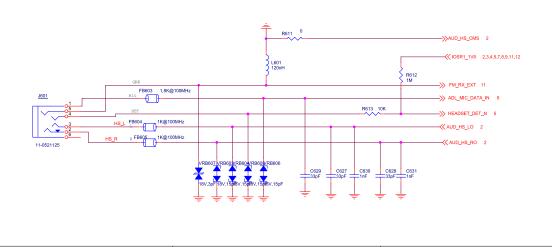

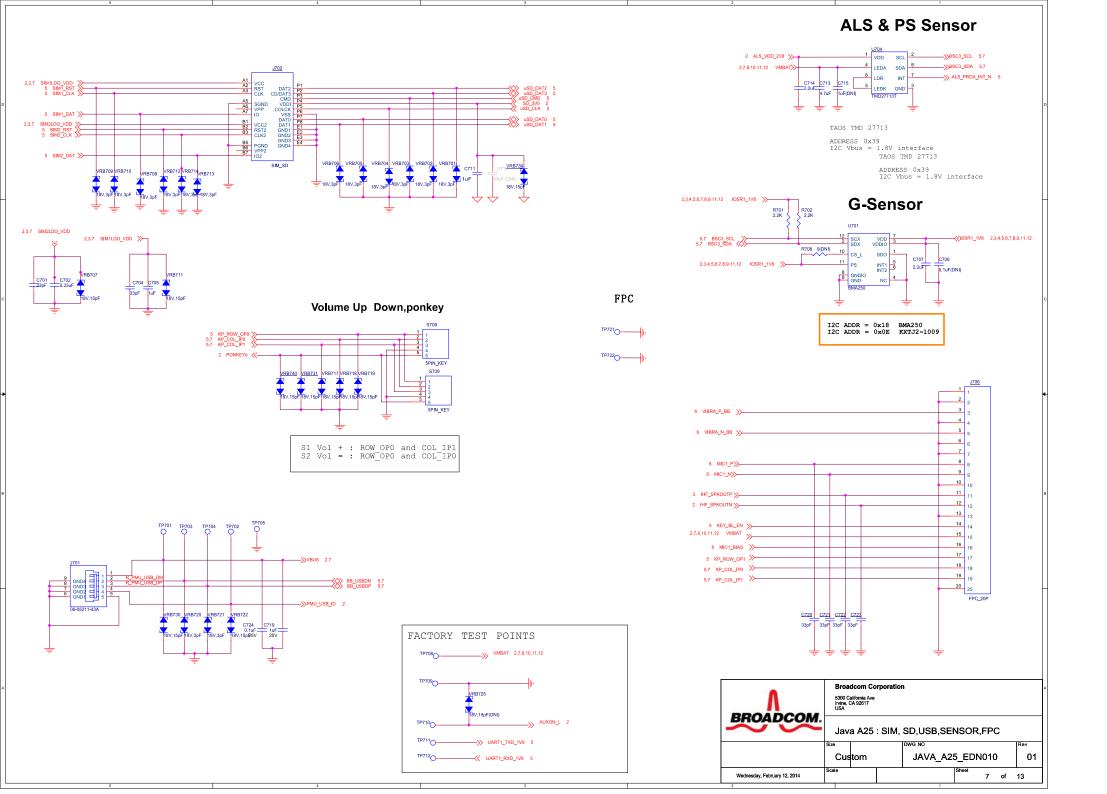

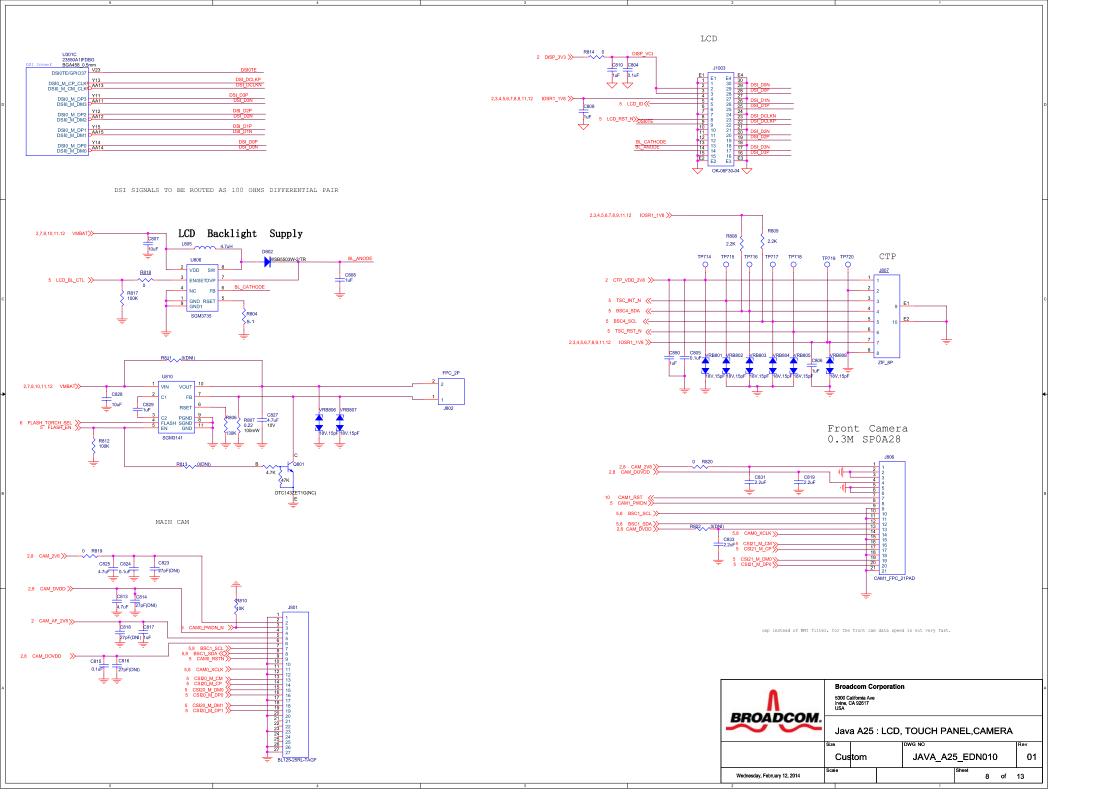

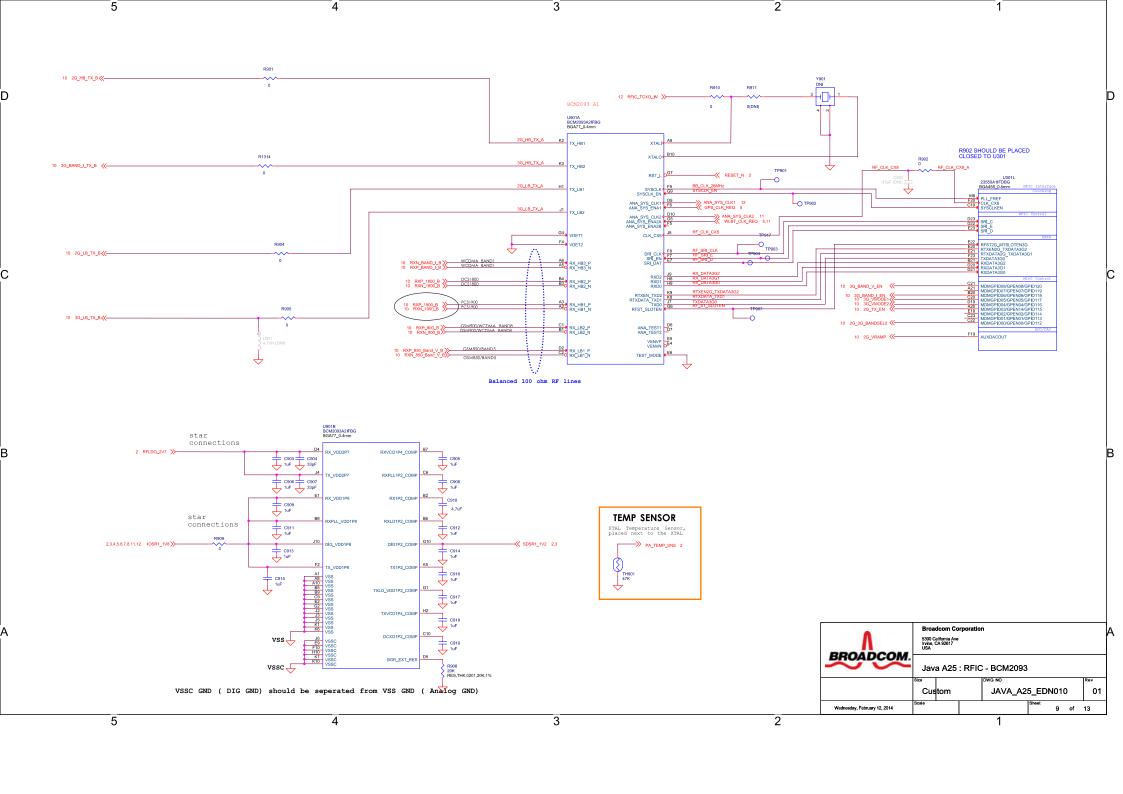

ALL PASSIVE COMPONENTS ARE 0402 SIZE UNLESS OTHERWISE NOTED