## **Direct Sequence Spread Spectrum Baseband Processor**

October 1996

#### Features

- Complete DSSS Baseband Processor

- High Data Rate.....up to 4 MBPS

- Processing Gain . . . . . . . . . . . up to 12dB

- Programmable PN Code ..... up to 16 Bits

- Ultra Small Package ..... 7 x 7 x 1mm

- Single Supply Operation (33MHz Max) . . 2.7V to 5.5V

- Single Supply Operation (44MHz Max) . . 3.3V to 5.0V

- Modulation Method . . . . . . . . . DBPSK or DQPSK

- . Supports Full or Half Duplex Operations

- On-Chip A/D Converters for I/Q Data (3-Bit, 44 MSPS) and RSSI (6-Bit, 2 MSPS)

## **Applications**

- Systems Targeting IEEE802.11 Standard

- DSSS PCMCIA Wireless Transceiver

- Spread Spectrum WLAN RF Modems

- TDMA Packet Protocol Radios

- Part 15 Compliant Radio Links

- Portable Bar Code Scanners/POS Terminal

- Portable PDA/Notebook Computer

- **Wireless Digital Audio**

- · Wireless Digital Video

- PCN/Wireless PBX

## ™ Description

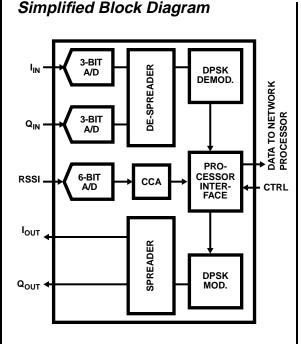

The Harris HSP3824 Direct Sequence (DSSS) baseband processor is part of the PRISM™ 2.4GHz radio chipset, and contains

all the functions necessary for a full or half duplex packet baseband transceiver.

The HSP3824 has on-board ADC's for analog I and Q inputs, for which the HFA3724 IF QMODEM is recommended. Differential phase shift keying modulation schemes DBPSK and DQPSK, with optional data scrambling capability, are combined with a programmable PN sequence of up to 16 bits. Built-in flexibility allows the HSP3824 to be configured through a general purpose control bus, for a wide range of applications. A Receive Signal Strength Indicator (RSSI) monitoring function with on-board 6-bit 2 MSPS ADC provides Clear Channel Assessment (CCA) to avoid data collisions and optimize network throughput. The HSP3824 is housed in a thin plastic quad flat package (TQFP) suitable for PCMCIA board applications.

## Ordering Information

| PART NO.  | TEMP.<br>RANGE (°C) | PKG. TYPE    | PKG. NO. |

|-----------|---------------------|--------------|----------|

| HSP3824VI | -40 to 85           | 48 Lead TQFP | Q48.7x7  |

| List of Contents                                                  |   |

|-------------------------------------------------------------------|---|

| Typical Application Diagram                                       | 3 |

| Pin Description                                                   | 4 |

| External Interfaces                                               | 7 |

| Control Port                                                      | 7 |

| TX Port                                                           | 0 |

| RX Port                                                           | 1 |

| I/Q ADC Interface                                                 | 1 |

| ADC Calibration Circuit and Registers                             | 2 |

| RSSI ADC Interface                                                |   |

| Test Port                                                         | 2 |

| Definitions                                                       |   |

| External AGC Control                                              | 3 |

| Power Down Modes                                                  |   |

| Reset                                                             | 4 |

| Transmitter Description                                           |   |

| Header/Packet Description                                         |   |

| PN Generator Description                                          |   |

| Scrambler and Data Encoder Description                            |   |

| Modulator Description                                             |   |

| Clear Channel Assessment (CCA) and Energy Detect (ED) Description |   |

| Receiver Description                                              |   |

| Acquisition Description                                           |   |

| Two Antenna Acquisition                                           |   |

| One Antenna Acquisition                                           |   |

| Acquisition Signal Quality Parameters2                            |   |

| Procedure to Set Acq. Signal Quality Parameters (Example)         |   |

| PN Correlator Description                                         |   |

| Data Demodulation and Tracking Description                        |   |

| Procedure to Set Signal Quality Registers                         |   |

| Data Decoder and Descrambler Description                          |   |

| Demodulator Performance                                           |   |

| Overall Eb/N0 Versus BER Performance                              |   |

| Clock Offset Tracking Performance                                 |   |

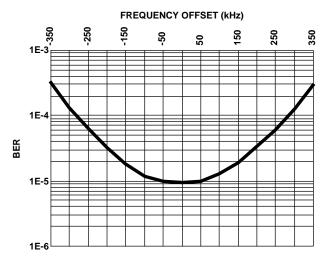

| Carrier Offset Frequency Performance                              |   |

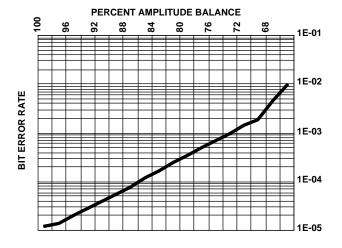

| I/Q Amplitude Imbalance                                           |   |

| A Default Register Configuration                                  |   |

| Control Registers                                                 |   |

| HSP3824 33MHz                                                     |   |

| HSP3824                                                           |   |

| HSP3824 44MHz                                                     |   |

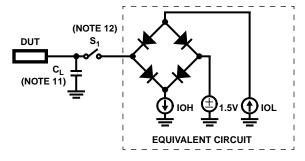

| Test Circuit                                                      |   |

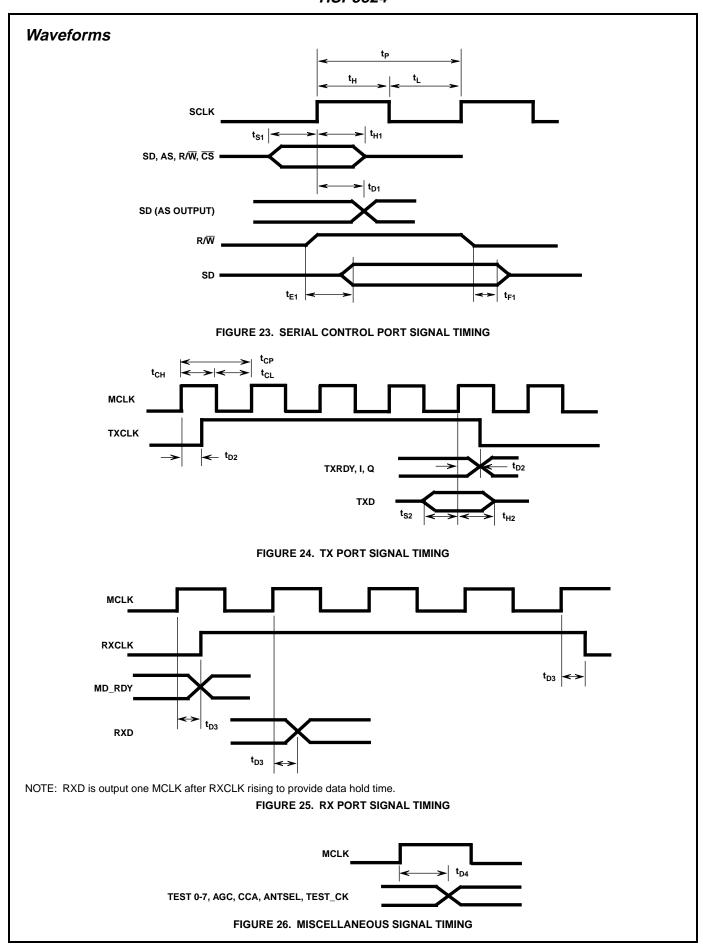

| Waveforms                                                         |   |

| Thin Plastic Quad Flatpack Packages (TQFP)4                       |   |

|                                                                   | • |

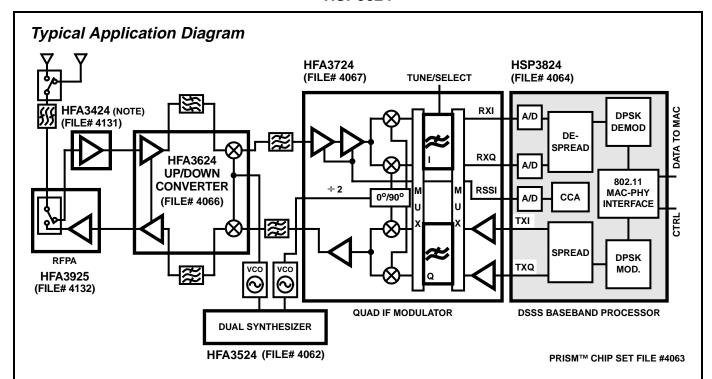

TYPICAL TRANSCEIVER APPLICATION CIRCUIT USING THE HSP3824

NOTE: Required for systems targeting 802.11 specifications.

For additional information on the PRISM<sup>TM</sup> chip set, call (407) 724-7800 to access Harris' AnswerFAX system. When prompted, key in the four-digit document number (File #) of the datasheets you wish to receive.

The four-digit file numbers are shown in Typical Application Diagram, and correspond to the appropriate circuit.

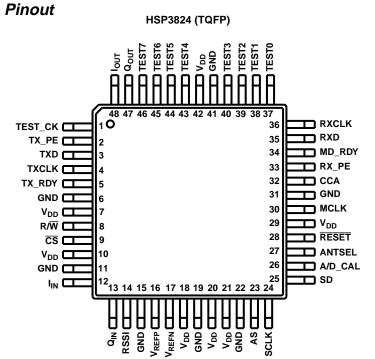

## Pin Description

| NAME                      | PIN           | TYPE I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> (Analog)  | 10, 18, 20    | Power    | DC power supply 2.7V - 5.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>DD</sub> (Digital) | 7, 21, 29, 42 | Power    | DC power supply 2.7V - 5.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GND (Analog)              | 11, 15, 19    | Ground   | DC power supply 2.7V - 5.5V, ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND (Digital)             | 6, 22, 31, 41 | Ground   | DC power supply 2.7V - 5.5V, ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>REFN</sub>         | 17            | I        | "Negative" voltage reference for ADC's (I and Q) [Relative to V <sub>REFP</sub> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>REFP</sub>         | 16            | ı        | "Positive" voltage reference for ADC's (I, Q and RSSI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| I <sub>IN</sub>           | 12            | I        | Analog input to the internal 3-bit A/D of the In-phase received data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Q <sub>IN</sub>           | 13            | I        | Analog input to the internal 3-bit A/D of the Quadrature received data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RSSI                      | 14            | ı        | Receive Signal Strength Indicator Analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A/D_CAL                   | 26            | 0        | This signal is used internally as part of the I and Q ADC calibration circuit. When the ADC calibration circuit is active, the voltage references of the ADCs are adjusted to maintain the outputs of the ADCs in their optimum range. A logic 1 on this pin indicates that one or both of the ADC outputs are at their full scale value. This signal can be integrated externally as a control voltage for an external AGC.                                                                                                                                     |

| TX_PE                     | 2             | I        | When active, the transmitter is configured to be operational, otherwise the transmitter is in standby mode. TX_PE is an input from the external Media Access Controller (MAC) or network processor to the HSP3824. The rising edge of TX_PE will start the internal transmit state machine and the falling edge will inhibit the state machine. TX_PE envelopes the transmit data.                                                                                                                                                                               |

| TXD                       | 3             | I        | TXD is an input, used to transfer serial Data or Preamble/Header information bits from the MAC or network processor to the HSP3824. The data is received serially with the LSB first. The data is clocked in the HSP3824 at the falling edge of TXCLK.                                                                                                                                                                                                                                                                                                           |

| TXCLK                     | 4             | 0        | TXCLK is a clock output used to receive the data on the TXD from the MAC or network processor to the HSP3824, synchronously. Transmit data on the TXD bus is clocked into the HSP3824 on the falling edge. The clocking edge is also programmable to be on either phase of the clock. The rate of the clock will be depending upon the modulation type and data rate that is programmed in the signalling field of the header.                                                                                                                                   |

| TX_RDY                    | 5             | 0        | When the HSP3824 is configured to generate the preamble and Header information internally, TX_RDY is an output to the external network processor indicating that Preamble and Header information has been generated and that the HSP3824 is ready to receive the data packet from the network processor over the TXD serial bus. The TX_RDY returns to the inactive state when the TX_PE goes inactive indicating the end of the data transmission. TX_RDY is an active high signal. This signal is meaningful only when the HSP3824 generates its own preamble. |

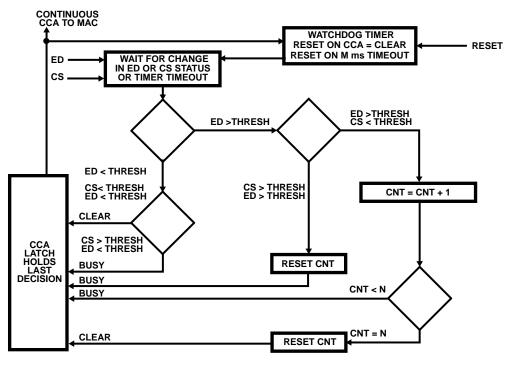

| CCA                       | 32            | 0        | Clear Channel Assessment (CCA) is an output used to signal that the channel is clear to transmit. The CCA algorithm is user programmable and makes its decision as a function of RSSI, Energy detect (ED), Carrier Sense (CRS) and the CCA watch dog timer. The CCA algorithm and its programmable features are described in the data sheet.  Logic 0 = Channel is clear to transmit.  Logic 1 = Channel is NOT clear to transmit (busy).  NOTE: This polarity is programmable and can be inverted.                                                              |

| RXD                       | 35            | 0        | RXD is an output to the external network processor transferring demodulated Header information and data in a serial format. The data is sent serially with the LSB first. The data is frame aligned with MD_RDY.                                                                                                                                                                                                                                                                                                                                                 |

| RXCLK                     | 36            | 0        | RXCLK is the clock output bit clock. This clock is used to transfer Header information and data through the RXD serial bus to the network processor. This clock reflects the bit rate in use.RXCLK will be held to a logic "0" state during the acquisition process. RXCLK becomes active when the HSP3824 enters in the data mode. This occurs once bit sync is declared and a valid signal quality estimate is made, when comparing the programmed signal quality thresholds.                                                                                  |

# Pin Description (Continued)

| NAME             | PIN                                  | TYPE I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD_RDY           | 34                                   | 0        | MD_RDY is an output signal to the network processor, indicating a data packet is ready to be transferred to the processor. MD_RDY is an active high signal and it envelopes the data transfer over the RXD serial bus. MD_RDY returns to its inactive state when there is no more receiver data, when the programmable data length counter reaches its value or when the link has been interrupted. MD_RDY remains inactive during preamble synchronization.                                                                                                                                                                                                                     |

| RX_PE            | 33                                   | I        | When active, receiver is configured to be operational, otherwise receiver is in standby mode. This is an active high input signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ANTSEL           | 27                                   | 0        | The antenna select signal changes state as the receiver switches from antenna to antenna during the acquisition process in the antenna diversity mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SD               | 25                                   | I/O      | SD is a serial bi-directional data bus which is used to transfer address and data to/from the internal registers. The bit ordering of an 8-bit word is MSB first. The first 8 bits during transfers indicate the register address immediately followed by 8 more bits representing the data that needs to be written or read at that register.                                                                                                                                                                                                                                                                                                                                   |

| SCLK             | 24                                   | I        | SCLK is the clock for the SD serial bus. The data on SD is clocked at the rising edge. SCLK is an input clock and it is asynchronous to the internal master clock (MCLK) The maximum rate of this clock is 10MHz or the master clock frequency, whichever is lower.                                                                                                                                                                                                                                                                                                                                                                                                              |

| AS               | 23                                   | I        | AS is an address strobe used to envelope the Address or the data on SD.  Logic 1 = envelopes the address bits.  Logic 0 = envelopes the data bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| R/W              | 8                                    | I        | $R\overline{W}$ is an input to the HSP3824 used to change the direction of the SD bus when reading or writing data on the SD bus. $R\overline{W}$ must be set up prior to the rising edge of SCLK. A high level indicates read while a low level is a write.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ĊS               | 9                                    | I        | $\overline{\text{CS}}$ is a Chip select for the device to activate the serial control port.The $\overline{\text{CS}}$ doesn't impact any of the other interface ports and signals, i.e. the TX or RX ports and interface signals. This is an active low signal. When inactive SD, SCLK, AS and $\overline{\text{R/W}}$ become "don't care" signals.                                                                                                                                                                                                                                                                                                                              |

| TEST 0-7         | 37, 38, 39,<br>40, 43, 44,<br>45, 46 | 0        | This is a data port that can be programmed to bring out internal signals or data for monitoring. This data includes: Correlator phase and magnitude, NCO frequency offset estimate, and signal quality estimates. Some of the discrete signals available include: Carrier Sense (CRS), which becomes active when initial PN acquisition has been declared. Energy Detect (ED) which becomes active when the integrated RSSI value exceeds the programmable threshold. Both ED and CRS are active high signals. These bits are primarily reserved by the manufacturer for testing. A further description of the test port is given at the appropriate section of this data sheet. |

| TEST_CK          | 1                                    | 0        | This is the clock that is used in conjunction with the data that is being output from the test bus (TEST 0-7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RESET            | 28                                   | l        | Master reset for device. When active TX and RX functions are disabled. If RESET is kept low the HSP3824 goes into the power standby mode. RESET does not alter any of the configuration register values nor it presets any of the registers into default values. Device requires programming upon power-up. RESET must be inactive during programming of the device.                                                                                                                                                                                                                                                                                                             |

| MCLK             | 30                                   | I        | Master Clock for device. The maximum frequency of this clock is 44MHz. This is used internally to generate all other internal necessary clocks and is divided by 1, 2, 4, or 8 for the transceiver clocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I <sub>OUT</sub> | 48                                   | 0        | TX Spread baseband I digital output data. Data is output at the programmed chip rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Q <sub>OUT</sub> | 47                                   | 0        | TX Spread baseband Q digital output data. Data is output at the programmed chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

NOTE: Total of 48 pins; ALL pins are used.

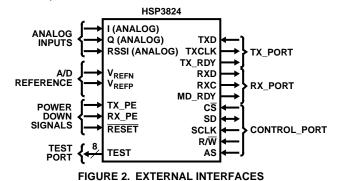

#### External Interfaces

There are three primary digital interface ports for the HSP3824 that are used for configuration and during normal operation of the device. These ports are:

- The TX Port, which is used to accept the data that needs to be transmitted from the network processor.

- The RX Port, which is used to output the received demodulated data to the network processor.

- The Control Port, which is used to configure, write and/or read the status of the internal HSP3824 registers.

In addition to these primary digital interfaces the device includes a byte wide parallel **Test Port** which can be configured to output various internal signals and/or data (i.e. PN acquisition indicator, Correlator magnitude output etc.). The device can also be set into various power consumption modes by external control. The HSP3824 contains three Analog to Digital (A/D) converters. The analog interfaces to the HSP3824 include, the In phase (I) and quadrature (Q) data component inputs, and the RF signal strength indicator input. A reference voltage divider is also required external to the device.

### **Control Port**

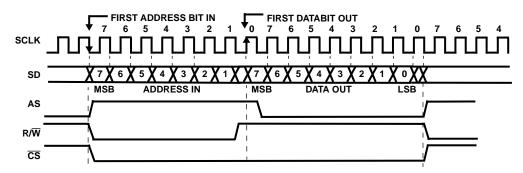

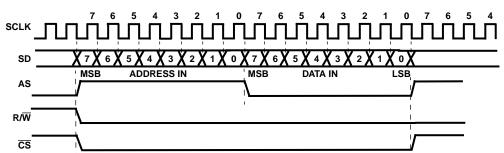

The serial control port is used to serially write and read data to/ from the device. This serial port can operate up to a 10MHz rate or the maximum master clock rate of the device, MCLK (whichever is lower). MCLK must be running and RESET inactive during programming. This port is used to program and to read all internal registers. The first 8 bits always represent the address followed immediately by the 8 data bits for that register. The two LSBs of address are don't care. The serial transfers are accomplished through the serial data pin (SD). SD is a bidirectional serial data bus. An Address Strobe (AS), Chip Select ( $\overline{CS}$ ), and Read/ $\overline{Write}$  (R/ $\overline{W}$ ) are also required as handshake signals for this port. The clock used in conjunction with the address and data on SD is SCLK. This clock is provided by the external source and it is an input to the HSP3824. The timing relationships of these signals are illustrated on Figure 3 and 4. AS is active high during the clocking of the address bits.  $R/\overline{W}$  is high when data is to be read. and low when it is to be written. CS must be active (low) during the entire data transfer cycle. Selects the device. The serial control port operates asynchronously from the TX and RX ports and it can accomplish data transfers independent of the activity at the other digital or analog ports. CS does not effect the TX or RX operation of the device; impacting only the operation of the Control port. The HSP3824 has 57 internal registers that can be configured through the control port. These registers are listed in the Configuration and Control Internal Register table. Table 1 lists the configuration register number, a brief name describing the register, and the HEX address to access each of the registers. The type indicates whether the corresponding register is Read only (R) or Read/Write (R/W). Some registers are two bytes wide as indicated on the table (high and low bytes).

#### NOTES:

- 1. Using falling edge SCLK to generate address/control and capture read data.

- 2. The  $\overline{\text{CS}}$  is a synchronous interface in reference to SCLK. There is at least one clock required before  $\overline{\text{CS}}$  transitions to its active state.

NOTE: Using falling edge SCLK to generate address/control and data.

FIGURE 4. CONTROL PORT WRITE TIMING

TABLE 1. CONFIGURATION AND CONTROL INTERNAL REGISTER LIST

| CONFIGURATION<br>REGISTER | NAME                             | TYPE | REGISTER<br>ADDRESS HEX |  |

|---------------------------|----------------------------------|------|-------------------------|--|

| CR0                       | Modern Config. Register A        | R/W  | 00                      |  |

| CR1                       | Modern Config. Register B        | R/W  | 04                      |  |

| CR2                       | Modem Config. Register C         | R/W  | 08                      |  |

| CR3                       | Modem Config. Register D         | R/W  | 0C                      |  |

| CR4                       | Internal Test Register A         | R/W  | 10                      |  |

| CR5                       | Internal Test Register B         | R/W  | 14                      |  |

| CR6                       | Internal Test Register C         | R    | 18                      |  |

| CR7                       | Modem Status Register A          | R    | 1C                      |  |

| CR8                       | Modem Status Register B          | R    | 20                      |  |

| CR9                       | I/O Definition Register          | R/W  | 24                      |  |

| CR10                      | RSSI Value Register              | R    | 28                      |  |

| CR11                      | ADC_CAL_POS Register             | R/W  | 2C                      |  |

| CR12                      | ADC_CAL_NEG Register             | R/W  | 30                      |  |

| CR13                      | TX_Spread Sequence (High)        | R/W  | 34                      |  |

| CR14                      | TX_Spread Sequence (Low)         | R/W  | 38                      |  |

| CR15                      | Scramble_Seed                    | R/W  | 3C                      |  |

| CR16                      | Scramble_Tap (RX and TX)         | R/W  | 40                      |  |

| CR17                      | CCA_Timer_TH                     | R/W  | 44                      |  |

| CR18                      | CCA_Cycle_TH                     | R/W  | 48                      |  |

| CR19                      | RSSI_TH                          | R/W  | 4C                      |  |

| CR20                      | RX_Spread Sequence (High)        | R/W  | 50                      |  |

| CR21                      | RX_Spread Sequence (Low)         | R/W  | 54                      |  |

| CR22                      | RX_SQ1_ ACQ (High) Threshold     | R/W  | 58                      |  |

| CR23                      | RX-SQ1_ ACQ (Low) Threshold      | R/W  | 5C                      |  |

| CR24                      | RX-SQ1_ ACQ (High) Read          | R    | 60                      |  |

| CR25                      | RX-SQ1_ ACQ (Low) Read           | R    | 64                      |  |

| CR26                      | RX-SQ1_ Data (High) Threshold    | R/W  | 68                      |  |

| CR27                      | RX-SQ1-SQ1_ Data (Low) Threshold | R/W  | 6C                      |  |

| CR28                      | RX-SQ1_ Data (High) Read         | R    | 70                      |  |

| CR29                      | RX-SQ1_ Data (Low) Read          | R    | 74                      |  |

| CR30                      | RX-SQ2_ ACQ (High) Threshold     | R/W  | 78                      |  |

| CR31                      | RX-SQ2- ACQ (Low) Threshold      | R/W  | 7C                      |  |

| CR32                      | RX-SQ2_ ACQ (High) Read          | R    | 80                      |  |

TABLE 1. CONFIGURATION AND CONTROL INTERNAL REGISTER LIST (Continued)

| CONFIGURATION<br>REGISTER | NAME                         | ТҮРЕ | REGISTER<br>ADDRESS HEX |

|---------------------------|------------------------------|------|-------------------------|

| CR33                      | RX-SQ2_ ACQ (Low) Read       | R    | 84                      |

| CR34                      | RX-SQ2_Data (High) Threshold | R/W  | 88                      |

| CR35                      | RX-SQ2_Data (Low) Threshold  | R/W  | 8C                      |

| CR36                      | RX-SQ2_Data (High) Read      | R    | 90                      |

| CR37                      | RX-SQ2_Data (Low) Read       | R    | 94                      |

| CR38                      | RX_SQ_Read; Full Protocol    | R    | 98                      |

| CR39                      | Reserved (must load 00h)     | W    | 9C                      |

| CR40                      | Reserved (must load 00h)     | W    | A0                      |

| CR41                      | UW_Time Out_Length           | R/W  | A4                      |

| CR42                      | SIG_DBPSK Field              | R/W  | A8                      |

| CR43                      | SIG_DQPSK Field              | R/W  | AC                      |

| CR44                      | RX_SER_Field                 | R    | B0                      |

| CR45                      | RX_LEN Field (High)          | R    | B4                      |

| CR46                      | RX_LEN Field (Low)           | R    | B8                      |

| CR47                      | RX_CRC16 (High)              | R    | BC                      |

| CR48                      | RX_CRC16 (Low)               | R    | C0                      |

| CR49                      | UW (High)                    | R/W  | C4                      |

| CR50                      | UW (Low)                     | R/W  | C8                      |

| CR51                      | TX_SER_F                     | R/W  | СС                      |

| CR52                      | TX_LEN (High)                | R/W  | D0                      |

| CR53                      | TX_LEN (LOW)                 | R/W  | D4                      |

| CR54                      | TX_CRC16 (HIGH)              | R    | D8                      |

| CR55                      | TX_CRC16 (LOW)               | R    | DC                      |

| CR56                      | TX_PREM_LEN                  | R/W  | E0                      |

#### TX Port

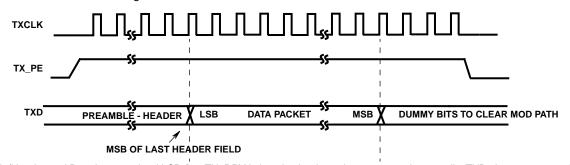

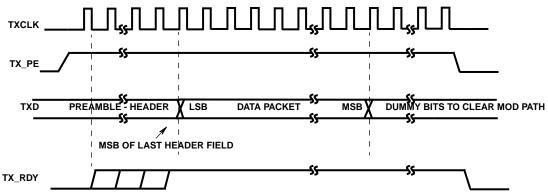

The transmit data port accepts the data that needs to be transmitted serially from an external data source. The data is modulated and transmitted as soon as it is received from the external data source. The serial data is input to the HSP3824 through TXD using the falling edge of TXCLK to clock it in the HSP3824. TXCLK is an output from the HSP3824. A timing scenario of the transmit signal handshakes and sequence is shown on timing diagram Figures 5 and 6.

The external processor initiates the transmit sequence by asserting TX\_PE. TX\_PE envelopes the transmit data packet on TXD. The HSP3824 responds by generating TXCLK to input the serial data on TXD. TXCLK will run until TX\_PE goes back to its inactive state indicating the end of the data packet. There are two possible transmit scenarios.

One scenario is when the HSP3824 internally generates the preamble and header information. During this mode the external source needs to provide only the data portion of the packet. The timing diagram of this mode is illustrated on Figure 6. When the HSP3824 generates the preamble internally, assertion of TX\_PE will initialize the generation of the preamble and header. TX\_RDY, which is an output from the HSP3824, is used to indicate to the external processor that the preamble has been generated and the device is ready to receive the data packet to be transmitted from the external processor. The TX\_RDY timing is programmable in case the external processor needs several clocks of advanced notice before actual data transmission is to begin.

The second transmit scenario supported by the HSP3824 is when the preamble and header information are provided by the external data source. During this mode TX\_RDY is not required as part of the TX handshake. The HSP3824 will immediately start transmitting the data available on TXD upon assertion of TX\_PE. The timing diagram of this TX scenario, where the preamble and header are generated external to the HSP3824, is illustrated on Figure 5.

One other signal that can be used for certain applications as part of the TX interface is the Clear Channel Assessment (CCA) signal which is an output from the HSP3824. The CCA is programmable and it is described with more detail in the Transmitter section of this document, CCA provides the indication that the channel is clear of energy and the transmission will not be subject to collisions. CCA can be monitored by the external processor to assist in deciding when to initiate transmissions. The CCA indication can bypassed or ignored by the external processor. The state of the CCA does not effect the transmit operation of the HSP3824. TX PE alone will always initiate the transmit state independent of the state of CCA. Signals TX\_RDY, TX\_PE and TXCLK can be set individually, by programming Configuration Register (CR) 9, as either active high or active low signals.

The transmit port is completely independent from the operation of the other interface ports including the RX port, therefore supporting a full duplex mode.

NOTE: Preamble/Header and Data is transmitted LSB first TX\_RDY is inactive Logic 0 when generated externally. TXD shown generated from rising edge TXCLK.

FIGURE 5. TX PORT TIMING (EXTERNAL PREAMBLE)

NOTE: Preamble/Header and Data is transmitted LSB first. TXD shown generated from rising edge TXCLK. TX\_RDY generated from falling edge.

FIGURE 6. TX PORT TIMING (INTERNAL PREAMBLE)

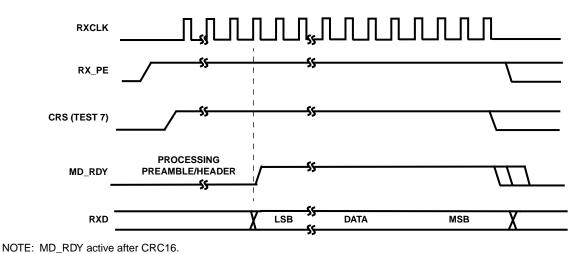

#### RX Port

The timing diagram Figure 7 illustrates the relationships between the various signals of the RX port. The receive data port serially outputs the demodulated data from RXD. The data is output as soon as it is demodulated by the HSP3824. RX\_PE must be at its active state throughout the receive operation. When RX\_PE is inactive the device's receive functions, including acquisition, will be in a stand by mode.

RXCLK is an output from the HSP3824 and is the clock for the serial demodulated data on RXD. MD\_RDY is an output from the HSP3824 and it envelopes the valid data on RXD. The HSP3824 can be also programmed to ignore error detections during the CCITT - CRC 16 check of the header fields. If programmed to ignore errors the device continues to output the demodulated data in its entirety regardless of the CCITT - CRC 16 check result. This option is programmed through CR 2, bit 5.

Note that RXCLK becomes active after acquisition, well before valid data begins to appear on RXD and MD\_RDY is asserted. MD\_RDY returns to its inactive state under the following conditions:

- The number of data symbols, as defined by the length field in the protocol, has been received and output through RXD in its entirety (normal condition).

- PN tracking is lost during demodulation.

- RX\_PE is deactivated by the external controller.

MD\_RDY can be configured through CR 9, bit 6 to be active low, or active high. Energy Detect (ED) pin 45 (Test port), and Carrier Sense (CRS) pin 46 (Test port), are available outputs from the HSP3824 and can be useful signals for an effective RX interface design. Use of these signals is optional. CRS and ED are further described within this document. The receive port is completely independent from the operation of the other interface ports including the TX port, supporting therefore a full duplex mode.

#### I/Q ADC Interface

The PRISM baseband processor chip (HSP3824) includes two 3-bit Analog to Digital converters (ADCs) that sample the analog input from the IF down converter. The I/Q ADC clock, MCLK, samples at twice the chip rate. The maximum sampling rate is 44MHz (power supply: 3.3V to 5.0V) or 33MHz (power supply 2.7V to 5.5V).

The interface specifications for the I and Q ADCs are listed on Table 2 below.

**TABLE 2. I, Q, ADC SPECIFICATIONS**

| PARAMETER                                    | MIN  | TYP   | MAX   |

|----------------------------------------------|------|-------|-------|

| Full Scale Input Voltage (V <sub>P-P</sub> ) | 0.25 | 0.50  | 1.0   |

| Input Bandwidth (-0.5dB)                     | -    | 20MHz | -     |

| Input Capacitance (pF)                       | -    | 5     | -     |

| Input Impedance (DC)                         | 5kΩ  | -     | -     |

| FS (Sampling Frequency)                      | -    | -     | 44MHz |

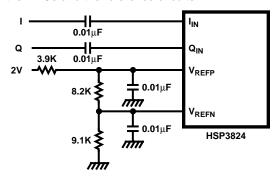

The voltages applied to pin 16,V<sub>REFP</sub> and pin 17, V<sub>REFN</sub> set the references for the internal I and Q ADC converters. In addition, V<sub>REFP</sub> is also used to set the RSSI ADC converter reference. For a nominal 500mV<sub>P-P</sub>, the suggested V<sub>REFP</sub> voltage is 1.75V, and the suggested V<sub>REFN</sub> is 0.93V. V<sub>REFN</sub> should never be less than 0.25V. Since these ADCs are intended to sample AC voltages, their inputs are biased internally and they should be capacitively coupled.

The ADC section includes a compensation (calibration) circuit that automatically adjusts for temperature and component variations of the RF and IF strips. The variations in gain of limiters, AGC circuits, filters etc. can be compensated for up to ±4dB. Without the compensation circuit, the ADCs could see a loss of up to 1.5 bits of the 3 bits of quantization. The ADC calibration circuit adjusts the ADC reference voltages to maintain optimum quantization of the IF input over this variation range. It works on the principle of setting the reference to insure that the signal is at full scale (saturation) a certain percentage of the time. Note that this is not an AGC and it will compensate only for slow variations in signal levels (several seconds).

FIGURE 7. RX PORT TIMING

The procedure for setting the ADC references to accommodate various input signal voltage levels is to set the reference voltages so that the ADC calibration circuit is operating at half scale. This leaves the maximum amount of adjustment room for circuit tolerances.

Figure 8 illustrates the suggested interface configuration for the ADCs and the reference circuits.

FIGURE 8. INTERFACES

## ADC Calibration Circuit and Registers

The ADC compensation or calibration circuit is designed to optimize ADC performance for the I and Q inputs by maintaining the full 3-bit resolution of the outputs. There are two registers (CR 11 AD\_CAL\_POS and CR 12 AD\_CAL\_NEG) that set the parameters for the internal I and Q ADC calibration circuit.

Both I and Q ADC outputs are monitored by the ADC calibration circuit and if either has a full scale value, a 24-bit accumulator is incremented as defined by parameter AD\_CAL\_POS. If neither has a full scale value, the accumulator is decremented as defined by parameter AD\_CAL\_NEG.

A loop gain reduction is accomplished by using only the 5 MSBs out of the 24 bits to drive a D/A converter that adjusts the ADCs reference. The compensation adjustment is updated at 2kHz rate for a 2 MBPS operation. The ADC calibration circuit is only intended to remove slow component variations.

The ratio of the values from the two registers CR11 and CR12 set the probability that either the I or Q ADC converter will be at the saturation. The probability is set by (AD\_CAL\_POS)/(AD\_CAL\_NEG).

This also sets the levels so that operation with either NOISE or DPSK is approximately the same. It is assumed that the RF and IF sections of the receiver have enough gain to cause limiting on thermal noise. This will keep the levels at the ADC approximately same regardless of whether signal is present or not.

The ADC calibration voltage is automatically held during transmit in half duplex operation.

The ADC calibration circuit operation can be defined through CR 1, bits 1 and 0. Table 3 illustrates the possible configurations.

**TABLE 3. ADC CALIBRATION**

| CR 1<br>BIT 0 | CR 1<br>BIT 1 | ADC CALIBRATION CIRCUIT<br>CONFIGURATION     |

|---------------|---------------|----------------------------------------------|

| 0             | 0             | Automatic real time adjustment of reference. |

| 0             | 1             | Reference set at mid scale.                  |

| 1             | 0             | Reference held at most recent value.         |

| 1             | 1             | Reference set at mid scale.                  |

## RSSI ADC Interface

The Receive Signal Strength Indication (RSSI) analog signal is input to a 6-bit ADC, indicating 64 discrete levels of received signal strength. This ADC measures a DC voltage, so its input must be DC coupled. Pin 16 ( $V_{REFP}$ ) sets the reference for the RSSI ADC converter.  $V_{REFP}$  is common for the I and Q and RSSI ADCs. The RSSI signal is used as an input to the programmable Clear Channel Assessment algorithm of the HSP3824. The RSSI ADC output is stored in an 8-bit register (CR10) and it is updated at the symbol rate for access by the external processor to assist in network management.

The interface specifications for the RSSI ADC are listed on Table 4 below ( $V_{REFP} = 1.75V$ ).

**TABLE 4. RSSI ADC SPECIFICATIONS**

| PARAMETER                | MIN  | TYP | MAX  |

|--------------------------|------|-----|------|

| Full Scale Input Voltage | -    | -   | 1.15 |

| Input Bandwidth (0.5dB)  | 1MHz | -   | -    |

| Input Capacitance        | -    | 7pF | -    |

| Input Impedance (DC)     | 1M   | -   | -    |

## **Test Port**

The HSP3824 provides the capability to access a number of internal signals and/or data through the Test port, pins TEST 0-7. In addition pin 1 (TEST\_CK) is an output clock that can be used in conjunction with the data coming from the test port outputs. The test port is programmable through configuration register (CR5).

There are 9 test modes assigned to the PRISM test port listed in the Test Modes Table 5.

**TABLE 5. TEST MODES**

| MODE | DESCRIPTION             | TEST_CLK | TEST (7:0)                                        |

|------|-------------------------|----------|---------------------------------------------------|

| 0    | Normal<br>Operation     | TXCLK    | CRS, ED, "000", Initial<br>Detect, Reserved (1:0) |

| 1    | Correlator Test<br>Mode | TXCLK    | Mag (7:0)                                         |

| 2    | Frequency Test<br>Mode  | DCLK     | Frq Reg (7:0)                                     |

| 3    | Phase Test<br>Mode      | DCLK     | Phase (7:0)                                       |

| 4    | NCO Test Mode           | DCLK     | NCO Phase Accum Reg                               |

| 5    | SQ Test Mode            | LoadSQ   | SQ2 (15:8) Phase<br>Variance                      |

| 6    | Bit Sync Test<br>Mode 1 | RXCLK    | Bit Sync Accum (7:0)                              |

| 7    | Bit Sync Test<br>Mode 2 | LoadSQ   | SQ (14:7) Bit Sync Ref-<br>Data                   |

**TABLE 5. TEST MODES (Continued)**

| MODE        | DESCRIPTION          | TEST_CLK      | TEST (7:0)                |

|-------------|----------------------|---------------|---------------------------|

| 8           | A/D Cal Test<br>Mode | A/D<br>CAL_CK | CRS, ED, "0", ADCal (4:0) |

| 9           | Reserved             |               |                           |

| 10<br>(0Ah) | Reserved             |               |                           |

| 11          | Reserved             |               |                           |

| 12          | Reserved             |               |                           |

| 13          | Reserved             |               |                           |

| 14          | Reserved             |               |                           |

| 15          | Reserved             |               |                           |

## **Definitions**

Normal - Device in the full protocol mode (Mode 3).

TXCLK - Transmit clock (PN rate).

**Initial Detect -** Indicates that Signal Quality 1 and 2 (SQ1 and SQ2) exceed their programmed thresholds. Signal qualities are a function of phase error and correlator magnitude outputs.

**ED** - energy detect indicates that the RSSI value exceeds its programmed threshold.

**CRS** - indicates that a signal has been acquired (PN acquisition).

Mag - Magnitude output from the correlator.

DCLK - Data symbol clock.

FrqReg - Contents of the NCO frequency register.

Phase - phase of signal after carrier loop correction.

**NCO PhaseAccumReg -** Contents of the NCO phase accumulation register.

**LoadSQ** - Strobe that samples and updates Signal Quality, SQ1 and SQ2 values.

**SQ2 -** Signal Quality measure #2. Signal phase variance after removal of data, 8 MSBs of most recent 16-bit stored value.

**RXCLK** - Receive clock (RX sample clock). Nominally 22MHz. **BitSyncAccum** - Real time monitor of the bit synchronization accumulator contents, mantissa only. **SQ1 -** Signal Quality measure #1. Contents of the bit sync accumulator 8 MSBs of most recent 16-bit stored value.

A/D\_Cal\_ck - Clock for applying A/D calibration corrections.

**ADCal -** 5-bit value that drives the D/A adjusting the A/D reference.

#### External AGC Control

The ADC cal output (pin 26) is a binary signal that fluctuates between logic levels as the signals in the I and Q channels are either at full scale or not. If the input level is too high, this output will have a higher duty cycle, and visa versa. Thus, this signal could be integrated with an R-C filter to develop an AGC control voltage. The AGC feedback should be designed to drive it to 50% duty cycle. In the case that an external AGC is in use then the ADC calibration circuit must not be programmed for automatic level adjustment.

#### Power Down Modes

The power consumption modes of the HSP3824 are controlled by the following control signals.

Receiver Power Enable (RX\_PE,pin 33), which disables the receiver when inactive.

Transmitter Power Enable (TX\_PE, pin 2), which disables the transmitter when inactive.

Reset ( $\overline{\text{RESET}}$ , pin 28), which puts the receiver in a sleep mode when it is asserted at least 2 MCLKs after RX\_PE is set at its inactive state. The power down mode where, both RESET and RX\_PE are used is the lowest possible power consumption mode for the receiver. Exiting this mode requires a maximum of 10 $\mu$ s before the device is back at its operational mode.

The contents of the Configuration Registers is not effected by any of the power down modes. The external processor does not have access and cannot modify any of the CRs during the power down modes. No reconfiguration is required when returning to operational modes.

Table 6 describes the power down modes available for the HSP3824 ( $V_{CC}=3.5V$ ). The table values assume that all other inputs to the part (MCLK, SCLK, etc.) continue to run except as noted.

**TABLE 6. POWER DOWN MODES**

| RX_PE    | TX_PE                   | RESET    | 22MHz | 44MHz       | DEVICE STATE                                                                                                                                                                                     |

|----------|-------------------------|----------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inactive | Inactive                | Active   | 3.5mA | 7mA         | Both transmit and receive functions disabled. Device in sleep mode. Control Interface is still active. Register values are maintained. Device will return to its active state within $10\mu s$ . |

| Inactive | Inactive                | Inactive | 37mA  | 50mA        | Both transmit and receive operations disabled. Device will become in its active state within $1\mu s. \\$                                                                                        |

| Inactive | Active                  | Inactive | 37mA  | 50mA        | Receiver operations disabled. Receiver will return in its active state within $1\mu s. \label{eq:multiple}$                                                                                      |

| Active   | Inactive                | Inactive | 42mA  | 62mA        | Transmitter operations disabled. Transmitter will return to its active state within 2 MCLKs.                                                                                                     |

|          | I <sub>CC</sub> Standby |          | 300   | )μ <b>A</b> | All inputs at V <sub>CC</sub> or GND.                                                                                                                                                            |

#### Reset

The RESET signal is used during the power down mode as described in the Power Down Mode section. The RESET does not impact any of the internal configuration registers when asserted. Reset does not set the device in a default configuration, the HSP3824 must always be programmed on power up. The HSP3824 must be programmed with RESET inactive.

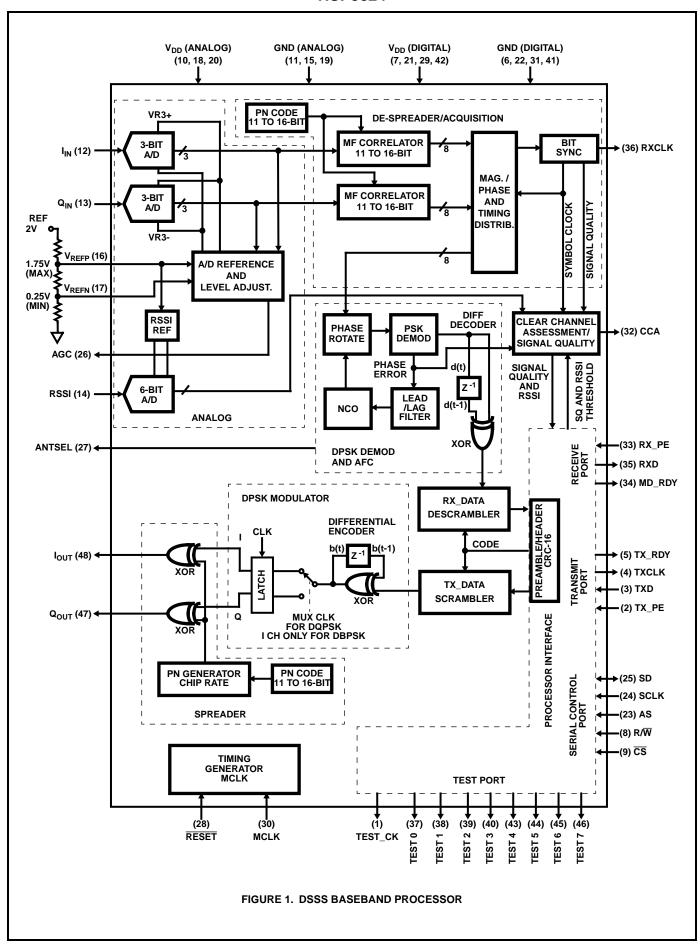

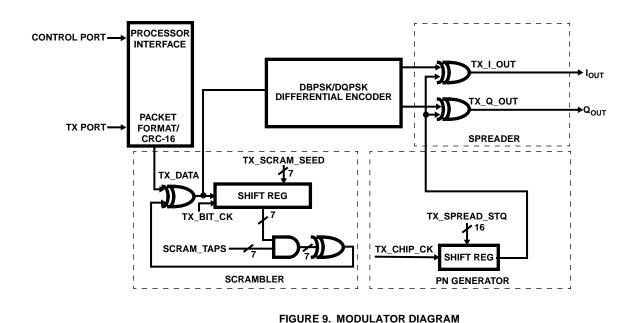

## Transmitter Description

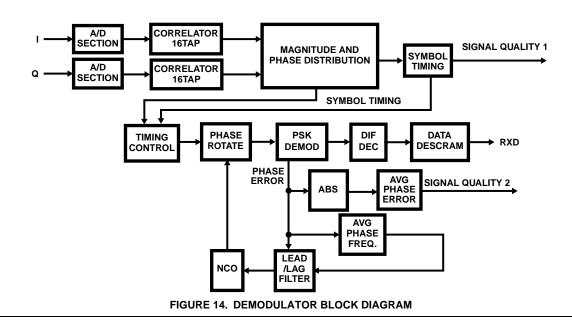

The HSP3824 transmitter is designed as a Direct Sequence Spread Spectrum DBPSK/DQPSK modulator. It can handle data rates of up to 4 MBPS (refer to AC and DC specifications). The major functional blocks of the transmitter include a network processor interface, DBPSK/DQPSK modulator, a data scrambler and a PN generator, as shown on Figure 9.

The transmitter has the capability to either generate its own synchronization preamble and header or accept the preamble and header information from an external source. In the first case, the transmitter knows when to make the DBPSK to DQPSK switchover, as required.

The preamble and header are always transmitted as DBPSK waveforms while the data packets can be configured to be either DBPSK or DQPSK. The preamble is used by the receiver to achieve initial PN synchronization while the header includes the necessary data fields of the communications protocol to establish the physical layer link. There is a choice of four potential preamble/header formats that the HSP3824 can generate internally. These formats are referred to as mode 0, 1, 2 and 3. Mode 0 uses the minimum number of available header fields while mode 3 is a full protocol mode utilizing all available header fields. The number of the synchronization preamble bits is programmable.

The transmitter accepts data from the external source, scrambles it, differentially encodes it as either DBPSK or DQPSK, and mixes it with the BPSK PN spreading. The baseband digital signals are then output to the external IF modulator.

The transmitter includes a programmable PN generator that can provide 11, 13, 15 or 16 chip sequences. The transmitter also contains a programmable clock divider circuit that allows for various data rates. The master clock (MCLK) can be a maximum of 44MHz.

The chip rates are programmed through CR3 for TX and CR2 for RX. In addition the data rate is a function of the sample clock rate (MCLK) and the number of PN bits per symbol.

The following equations show the Symbol rate for both TX and RX as a function of MCLK, Chips per symbol and N.

N is a programmable parameter through configuration registers CR 2and CR 3. The value of N is 2, 4, 8 or 16. N is used internally to divide the MCLK to generate other required clocks for proper operation of the device.

Symbol Rate = MCLK/(N x Chips per Symbol).

The bit rate Table 7 shows examples of the relationships expressed on the symbol rate equation.

The modulator is capable of switching rate automatically in the case where the preamble and header information are DBPSK modulated, and the data is DQPSK modulated.

The modulator is completely independent from the demodulator, allowing the PRISM baseband processor to be used in full duplex operation.

TABLE 7. BIT RATE TABLE EXAMPLES FOR MCLK = 44MHz

| DATA<br>MODULATION | ADC SAMPLE<br>CLOCK<br>(MHz) | TX SETUP CR 3<br>BITS 4, 3 | RX SET UP<br>CR 2 BITS 4, 3 | DATA RATE<br>FOR 11<br>CHIPS/BIT<br>(MBPS) | DATA RATE<br>FOR 13<br>CHIPS/BIT<br>(MBPS) | DATA RATE<br>FOR 15<br>CHIPS/BIT<br>(MBPS) | DATA RATE<br>FOR 16<br>CHIPS/BIT<br>(MBPS) |

|--------------------|------------------------------|----------------------------|-----------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|

| DQPSK              | 44                           | 00 (N = 2)                 | 00                          | 4                                          | 3.385                                      | 2.933                                      | 2.75                                       |

| DQPSK              | 22                           | 01 (N = 4)                 | 01                          | 2                                          | 1.692                                      | 1.467                                      | 1.375                                      |

| DQPSK              | 11                           | 10 (N = 8)                 | 10                          | 1                                          | 0.846                                      | 0.733                                      | 0.688                                      |

| DQPSK              | 5.5                          | 11 (N = 16)                | 11                          | 0. 5                                       | 0.423                                      | 0.367                                      | 0.344                                      |

| DBPSK              | 44                           | 00 (N = 2)                 | 00                          | 2                                          | 1.692                                      | 1.467                                      | 1.375                                      |

| DBPSK              | 22                           | 01 (N = 4)                 | 01                          | 1                                          | 0.846                                      | 0.733                                      | 0.688                                      |

| DBPSK              | 11                           | 10 (N = 8)                 | 10                          | 0.5                                        | 0.423                                      | 0.367                                      | 0.344                                      |

| DBPSK              | 5.5                          | 11 (N = 16)                | 11                          | 0.25                                       | 0.212                                      | 0.183                                      | 0.171                                      |

## Header/Packet Description

The HSP3824 is designed to handle continuous or packetized Direct Sequence Spread Spectrum (DSSS) data transmissions. The HSP3824 can generate its own preamble and header information or it can accept them from an external source.

When preamble and header are internally generated the device supports a synchronization preamble up to 256 symbols, and a header that can include up to five fields. The preamble size and all of the fields are programmable. When internally generated the preamble is all 1's (before entering the scrambler). The actual transmitted pattern of the preamble will be randomized by the scrambler if the user chooses to utilize the data scrambling option.

When the preamble is externally generated the user can choose any desirable bit pattern. Note though, that if the preamble bits will be processed by the scrambler which will alter the original pattern unless it is disabled.

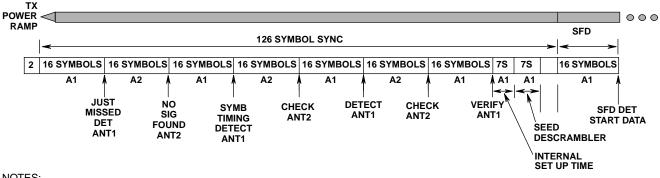

The preamble is always transmitted as a DBPSK waveform with a programmable length of up to 256 symbols long. The HSP3824 requires at least 126 preamble symbols to acquire in a dual antenna configuration (diversity), or a minimum of 78 preamble symbols to acquire under a single antenna configuration. The exact number of necessary preamble symbols should be determined by the system designer, taking

into consideration the noise and interference requirements in conjunction with the desired probability of detection vs probability of false alarm for signal acquisition.

The five available fields for the header are:

SFD Field (16 Bits) - This field carries the ID to establish the link. This is a mandatory field for the HSP3824 to establish communications. The HSP3824 will not declare a valid data packet, even if it PN acquires, unless it detects the specific SFD. The SFD field is required for both Internal preamble/header generation and External preamble/header generation. The HSP3824 receiver can be programmed to time out searching for the SFD. The timer starts counting the moment that initial PN synchronization has been established from the preamble.

**Signal Field (8 Bits) -** This field indicates whether the data packet that follows the header is modulated as DBPSK or DQPSK. In mode 3 the HSP3824 receiver looks at the signal field to determine whether it needs to switch from DBPSK demodulation into DQPSK demodulation at the end of the always DBPSK preamble and header fields.

**Service Field (8 Bits) -** This field can be utilized as required by the user.

**Length Field (16 Bits) -** This field indicates the number of data symbols contained in the data packet. The receiver can be programmed to check the length field in determining

| HEADER                             | CR #0 | BITS  |                                      |                |                         |                         |                         |                  |          |

|------------------------------------|-------|-------|--------------------------------------|----------------|-------------------------|-------------------------|-------------------------|------------------|----------|

| COUNT                              | BIT 4 | BIT 3 |                                      |                |                         |                         |                         |                  |          |

| N (Preamble) +<br>16 (Header) Bits | 0     | 0     | Preamble (SYNC)<br>N Bits Up to 256) | SFD<br>16 Bits | ]                       |                         |                         |                  |          |

| N (Preamble) +<br>32 (Header) Bits | 0     | 1     | Preamble (SYNC)<br>N Bits Up to 256) | SFD<br>16 Bits | CRC16<br>16 Bits        |                         |                         |                  |          |

| N (Preamble) +<br>48 (Header) Bits | 1     | 0     | Preamble (SYNC)<br>N Bits Up to 256) | SFD<br>16 Bits | Length Field<br>16 Bits | CRC16<br>16 Bits        |                         |                  |          |

| N (Preamble) +<br>64 (Header) Bits | 1     | 1     | Preamble (SYNC)<br>N Bits Up to 256) | SFD<br>16 Bits | Signal Field<br>8 Bits  | Service Field<br>8 Bits | Length Field<br>16 Bits | CRC16<br>16 Bits |          |

|                                    |       |       | ← PREAMBLE →                         | -              | -                       | — HEADER —              | -                       |                  | <u> </u> |

|                                    |       |       | FIGURE                               | 10. PREAMBLE   | E/HEADEAR M             | ODES                    |                         |                  |          |

when it needs to de-assert the MD\_RDY interface signal. MD\_RDY envelopes the received data packet as it is being output to the external processor.

CCITT - CRC 16 Field (16 Bits) - This field includes the 16-bit CCITT - CRC 16 calculation of the five header fields. This value is compared with the CCITT - CRC 16 code calculated at the receiver. The HSP3824 receiver can be programmed to drop the link upon a CCITT - CRC 16 error or it can be programmed to ignore the error and to continue with data demodulation.

The CRC or cyclic Redundancy Check is a CCITT CRC-16 FCS (frame check sequence). It is the ones compliment of the remainder generated by the modulo 2 division of the protected bits by the polynominal:

$$X^{16} + x^{12} + x^5 + 1$$

The protected bits are processed in transmit order. All CRC calculations are made prior to data scrambling. A shift register with two taps is used for the calculation. It is preset to all ones and then the protected fields are shifted through the register. The output is then complimented and the residual shifted out MSB first.

When the HSP3824 generates the preamble and header internally it can be configured into one of four link protocol modes.

**Mode 0 -** In this mode the preamble is programmable up to 256 bits (all 1's) and the SFD field is the only field utilized for the header. This mode only supports DBPSK transmissions for the entire packet (preamble/header and data).

**Mode 1 -** In this mode the preamble is programmable up to 256 bits (all 1's) and the SFD and CCITT - CRC 16 fields are used for the header. The data that follows the header can be either DBPSK or DQPSK. The receiver and transmitter must be programmed to the proper modulation type.

**Mode 2 -** In this mode the preamble is programmable up to 256 bits (all 1's) and the SFD, Length Field, and CCITT - CRC 16 fields are used for the header. The data that follows the header can be either DBPSK or DQPSK. The receiver and transmitter must be programmed to the proper modulation type.

Mode 3 - In this mode the preamble is programmable up to 256 bits (all 1's). The header in this mode is using all available fields. In mode 3 the signal field defines the modulation type of the data packet (DBPSK or DQPSK) so the receiver does not need to be preprogrammed to anticipate one or the other. In this mode the device checks the Signal field for the data packet modulation and it switches to DQPSK if it is defined as such in the signal field. Note that the preamble and header are always DBPSK the modulation definition applies only for the data packet. This mode is called the full protocol mode in this document.

Figure 10 summarizes the four preamble/head or modes. In the case that the device is configured to accept the preamble and header from an external source it still needs to be configured in one of the four modes (0:3). Even though the HSP3824 transmitter does not generate the preamble and header information the receiver needs to know the mode in use so it can proceed with the proper protocol and demodulation decisions.

The following Configuration Registers (CR) are used to program the preamble/header functions, more programming details about these registers can be found in the Control Registers section of this document:

**CR 0** - Defines one of the four modes (bits 4, 3) for the TX. Defines whether the SFD timer is active (bit 2). Defines whether the receiver should stop demodulating after the number of symbols indicated in the Length field has been met.

**CR 2 -** Defines to the receiver one of the four protocol modes (bits 1, 0). Indicates whether any detected CCITT - CRC 16 errors need to reset the receiver (return to acquisition) or to ignore them and continue with demodulation (bit 5). Specifies a 128-bit preamble or an 80-bit preamble (bit 2).

**CR 3 -** Defines internal or external preamble generation (bit 2). Indicates to the receiver the data packet modulation (bit 0), note that in mode 3 the contents of this register are overwritten by the information in the received signal field of the header. CR 3 specifies the data modulation type used to the transmitter (bit 1). Bit 1 defines the contents of the signaling field in the header to indicate either DBPSK or DQPSK modulation.

**CR 41 -** Defines the length of time that the demodulator searches for the SFD before returning to acquisition.

**CR 42 -** The contents of this register indicate that the transmitted data is DBPSK. If CR 4-bit 1 is set to indicate DBPSK modulation then the contents of this register are transmitted in the signal field of the header.

**CR 43 -** The contents of this register indicates that the transmitted data is DQPSK. If CR 4-bit 1 is set to indicate DQPSK modulation then the contents of this register are transmitted in the signal field of the header.

**CR 44, 45, 46, 47, 48 -** Status, read only, registers that indicate the service field, data length field and CCITT - CRC 16 field values of the received header.

**CR 49, 50 -** Defines the transmit SFD field value of the header. The receiver will always search to detect this value before it declares a valid data packet.

CR 51 - Defines the contents of the transmit service field.

**CR 52, 53 -** Defines the value of the transmit data length field. This value includes all symbols following the last header field symbol.

**CR 54,55** - Status, read only, registers indicating the calculated CCITT - CRC 16 value of the most recently transmitted header.

**CR 56** - Defines the number of preamble synchronization bits that need to be transmitted when the preamble is internally generated. These symbols are used by the receiver for initial PN acquisition and they are followed by the header fields.

The full protocol requires a setting of 128d = 80h. For other applications, in general increasing the preamble length will improve low signal to noise acquisition performance at the cost of greater link overhead. For dual receive antenna operation, the minimum suggested value is 128d = 80h. For single receive antenna operation, the minimum suggested value is 80d = 50h. These suggested values include a 2 symbol TX power amplifier ramp up. If an AGC is used, its worst case settling time in symbols should be added to these values.

## PN Generator Description

The spread function for this radio uses short sequences. The same sequence is applied to every bit. All transmitted symbols, preamble/header and data are always spread by the PN sequence at the chip rate. The PN sequence sets the Processing Gain (PG) of the Direct Sequence receiver. The HSP3824 can be programmed to utilize 11,13,15 and 16 bit sequences. Given the length of these programmable sequences the PG range of the HSP3824 is:

From 10.41dB (10 LOG(11)) to 12.04dB (10 LOG(16))

The transmitter and receiver PN sequences can are programmed independently. This provides additional flexibility to the network designer.

The TX sequence is set through CR 13 and CR 14 while the RX PN sequence is set through CR 20 and CR 21. A maximum of 16 bits can be programmed between the pairs of these configuration registers. For TX Registers CR13 and CR14 contain the high and low bytes of the sequence for the transmitter. In addition Bits 5 and 6 of CR 4 define the sequence length in chips per bit. CR 13, CR 14 and CR 4 must all be programmed for proper functionality of the PN generator. The sequence is transmitted MSB first. When fewer than 16 bits are in the sequence, the MSBs are truncated.

## Scrambler and Data Encoder Description

The data coder the implements the desired DQPSK coding as shown in the DQPSK Data Encoder table. This coding scheme results from differential coding of the dibits. When used in the DBPSK modes, only the 00 and 11 dibits are used. Vector rotation is counterclockwise.

**TABLE 8. DQPSK DATA ENCODER**

| PHASE SHIFT | DIBITS |

|-------------|--------|

| 0           | 00     |

| +90         | 01     |

| +180        | 11     |

| -90         | 10     |

The data scrambler is a self synchronizing circuit. It consist of a 7-bit shift register with feedback from specified taps of the register, as programmed through CR 16. Both transmitter and receiver use the same scrambling algorithm. All of the bits transmitted are scrambled, including data header and preamble. The scrambler can be disabled.

Scrambling provides additional spreading to each of the spectral lines of the spread DS signal. The additional spreading due to the scrambling will have the same null to null bandwidth, but it will further smear the discrete spectral lines from the PN code sequence. Scrambling might be necessary for certain allocated frequencies to meet transmission waveform requirements as defined by various regulatory agencies.

In the absence of scrambling, the data patterns could contain long strings of ones or zeros. This is definitely the case with the a DS preamble which has a stream of up to 256 continuous ones. The continuous ones would cause the

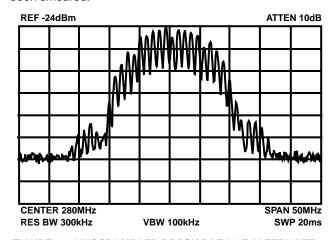

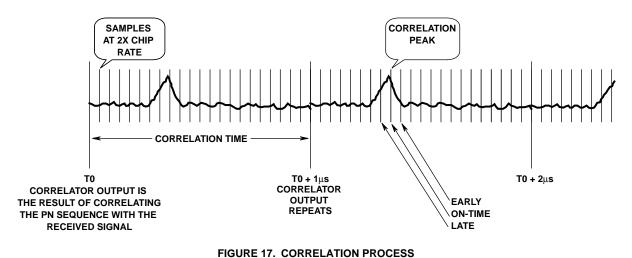

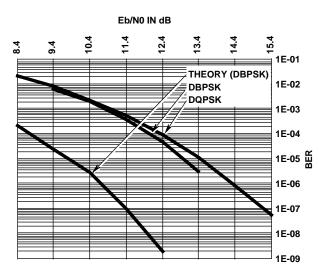

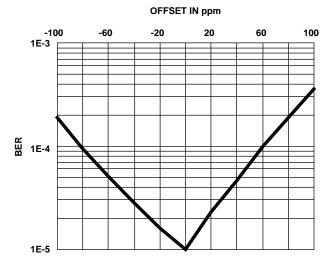

spectrum to be concentrated at the discrete lines defined by the spreading code and potentially cause interference with other narrow band users at these frequencies. Additionally, the DS system itself would be moderately more susceptible to interference at these frequencies. With scrambling, the spectrum is more uniform and these negative effects are reduced, in proportion with the scrambling code length.