# TIME DOMAIN

---

THE NEW WIRELESS MEDIUM

This application seeks approval for an ultra-wideband device that is the subject of a waiver request that was filed by Time Domain with the Commission on February 2, 1998. The waiver request submitted by Time Domain asked that section 15.205 be waived permitting emissions into the restricted bands, and that pulse desensitization not be applied because it is inappropriate for time-modulated ultra-wideband signals.

Ultra-wideband technology developed by Time Domain has been evaluated under a joint FCC-NTIA measurement program conducted in June and July of 1998. Because the intentional emissions from this device appear "noise-like" and, therefore, as if they were the emissions from an unintentional radiator, the test report in Exhibit 5 was prepared by DLS Electronic Systems at the request of Time Domain Corporation as if the equipment under test were subject to regulation as an unintentional radiator. This is consistent with the terms of the waiver request. The intentionally radiated signal is ultra-wideband in nature, having a bandwidth from 1 GHz to 3 GHz with a nominal center of 2 GHz.

See the product description located in this Exhibit for further details. Further, this application complies with the transition provision of section 15.37 of the FCC Rules.

## Product Description

### **Overview**

Description: The RadarVision radar system, designed and developed by Time Domain Corporation, is intended to be used to determine the presence of moving objects in situations where visual line-of-sight is obscured. For example, a law enforcement agency may wish to determine if people are in a room prior to attempting entry.

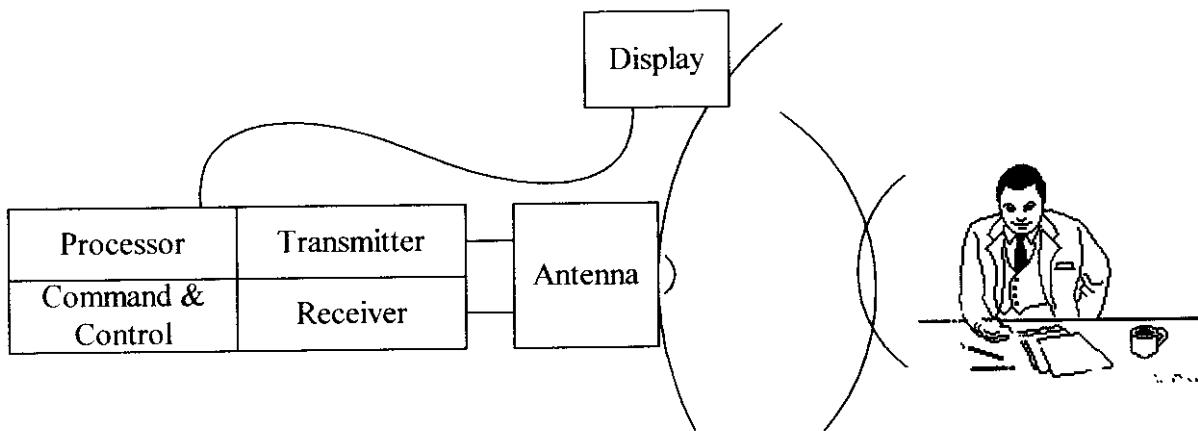

**Figure 1. Representation of RadarVision application,

backpack not shown in picture**

The system consists of a self-contained, battery-powered, man-portable electronics package, containing an ultra-wideband (UWB) transmitter, a compatible UWB receiver and associated antennas, displays, cables and batteries.

**How it works:** The RadarVision radar system works by transmitting a radio frequency (rf) electromagnetic wave, and receiving echoes created when this wave strikes an object and is reflected back to the receiver. By measuring the time between when the wave is transmitted and when the reflection is received, the distance to the reflecting object can be determined. The RadarVision system transmitted wave is a unique ultra-wideband (UWB) pulse. This UWB pulse is transmitted from the antenna toward a reflecting object at a rate very near 1 foot per nano-second (f/ns). The receiver monitors four time windows spaced

**Figure 2. Representation of the RadarVision system in operation.**

10 ns apart. This allows for reception of reflections at 5 foot increments. The current implementation of the RadarVision system is capable of receiving reflected waves from human sized objects at a range of 5, 10, 15 and 20 feet. The radar can be represented by Figure 2. The command control block represents the subsystems that synchronize the radar. Two important aspects of this are:

1) the random dither, and 2) the delay control between XMT (transmit) and REC (receive). This delay control defines the range being monitored. The transmitter consists of a pulser that generates a short duration pulse at a nominal PRF (pulse repetition frequency) of 5 MHz. These pulses have pseudo-randomly varying time spacing between them to make them noise-like. This randomization minimizes the potential for harmful interference. These pulses excite a UWB antenna.

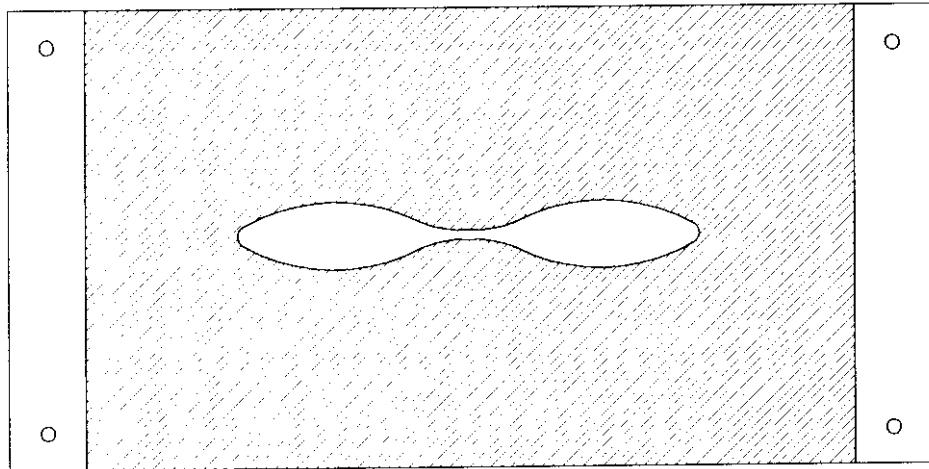

**The RadarVision Antenna:****Figure 3: A diagram of the Time Domain Corporation RadarVision Antenna**

The RadarVision antenna is a magnetic field antenna, in this case an antenna formed by making an aperture in a conductive ground plane. The conductive sheet is used so that current loops of varying sizes circulate, enabling the antenna to radiate over a bandwidth of from 1 GHz to 3 GHz. The antenna uses a reflector to direct the signal toward the desired direction. The transmit antenna radiates the UWB pulse that is reflected by the target, and in turn, received by a similar antenna. The received signals, at ranges determined by the command and control, are sampled by a UWB correlator receiver. This receiver is a coherent matched filter that is designed specifically to receive the desired signals. The data collected is processed, using various techniques to improve the signal-to-noise ratio and to determine if an alarm should be activated. The results of this processing are then displayed.

## Description of the Detailed Block Diagram

A detailed block diagram illustrating the functional interconnects of the main radar components is presented. The radar is a completely self-contained apparatus.

The radar is powered from a nominal 12Vdc sealed lead-acid rechargeable battery pack. This battery pack is attached to the main radar enclosure by two captive screws. The power is routed from the battery pack to the main radar enclosure via a cable and screw on connector. This same cable provides the means for connecting the battery pack to a separate battery charger. The power is routed into the main radar enclosure and through an on-off switch before being connected to the power supply.

The main radar enclosure contains a power supply that is powered from the battery pack. This power supply consists of conventional switching dc-to-dc conversion circuits that are used to convert and regulate the battery pack power to various voltages required by the radar functional blocks.

The control processor is a COTS processor using a '486 level microprocessor associated with conventional support systems. Data, address and control buses are distributed to the radar subsystems by routing them through the standard PC/104 bus. Because this design required other digital and slow-speed, low-level linear board-to-board interconnects a second bus structure was defined which uses the same connectors as the PC/104 bus but has a non-standard pin assignment. This processor is clocked from a signal generated by a 33 MHz crystal oscillator.

The timing board generates precisely timed trigger pulses required by other functional blocks to route or generate signals that perform the radar motion detection. The nominal pulse repetition frequency (PRF) is 5 MHz.

One timer board trigger output is used to control the timing of a pulse generated by the pulser. Each trigger pulse results in the generation of a pulse approximately 1 nano-second long, with a power spectrum center frequency of nominally 2GHz. This pulse is routed through a fixed attenuator to the transmit antenna. The antenna radiates energy in the characteristic Time Domain Corporation ultra-wideband emission.

The emissions impinge on objects and structures in the environment. Portions of these emissions are re-radiated and in turn impinge on the radar receive antenna. The low-noise amplifier (LNA) amplifies the received signals. A low-noise amplifier is used to increase the level of the received signal and environmental noise while contributing negligible noise in the process. The signal is then passed through a correlator. This circuit is analogous to a heterodyne mixer in a conventional radar system. A trigger signal from the timer, that has been delayed a known amount, is used to time a template pulse. This template pulse is multiplied with the received signal, resulting in a base-band signal. Because the trigger to the correlator template generator is synchronous, howbeit

delayed, with the trigger signal to the pulser, all pseudo-random time modulation is removed from this base-band signal.

The base-band processor block uses conventional analog-to-digital processing to generate a record of the amplitude of the sum of the received pulses. This record is stored and repeatedly compared with ensuing records. An indication of movement in the environment is generated when a difference in successive received records differs from stored records.

The control processor is used, at this point, to generate displays on the LCD screen, to generate a tone and direct signals to the DB-9 pin serial connector on the main radar enclosure side panel. This connector is included as part of the user I/O, to provide a link to a laptop computer that serves as an auxiliary display for demonstration and training.

# S-MOS CARDIO™486

## FEATURES

486SL Super Set Core

8XC51SL Keyboard I/F

### Memory:

4- or 8 MB RAM

(12 and 16MB)

256KB ROM

### VGA:

Analog RGB

Mono-STN or color TFT

### SPC2052 FDC

### Power Supply:

3.3V ± 0.3V, 5.0V ± 5%

### IBM PC AT BIOS Compatible

Set-up functions

VGA support

Power management

## DESCRIPTION

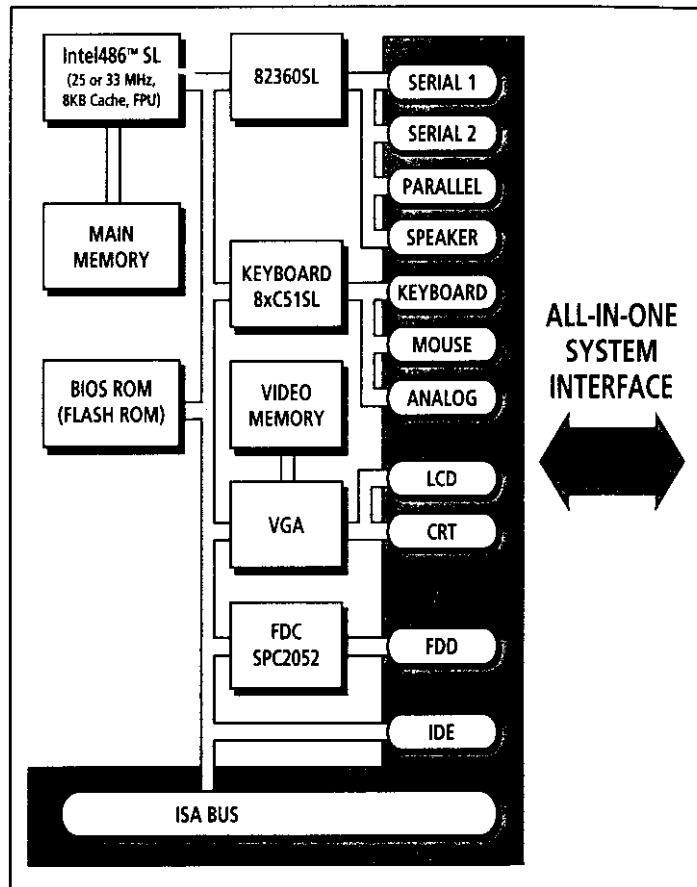

The CARDIO™-486 is compatible with the IBM PC AT and condensed to a PCMCIA-sized card. The CARDIO™-486 consists of Intel486™ SL super set (with 8KB Cache and FPU), VGA, ROM, RAM, FDC and a keyboard controller. The CARDIO™-486 interfaces with peripherals through a standard ISA and the S-MOS ALL-IN-ONE SYSTEM INTERFACE.

The CARDIO™-486 can be tailored to any customer's specific embedded application such as POS, FA and CATV. System upgrading is fast and easy since all cards utilize a standard pin configuration.

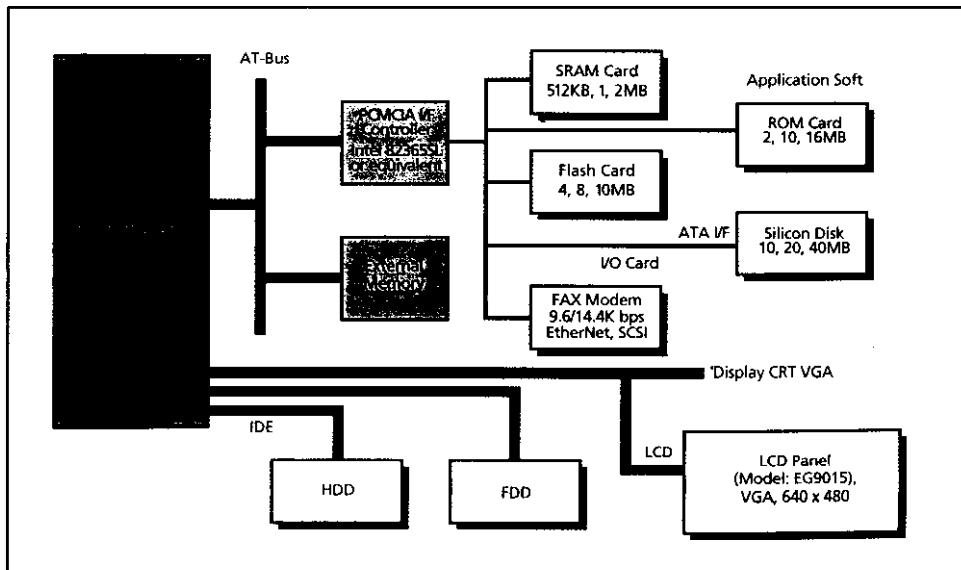

## CARDIO-486 APPLICATION EXAMPLE

# S-MOS CARDIO™-486

## AVAILABLE PRODUCTS

Cardio-86

Cardio-386

Cardio-386L

Cardio-486

Evaluation Board

DIO5300

Evaluation Board Peripherals

DIO5301 (FDD, Power Supply, HDD, LCD)

DIO5301R (FDD, Power Supply, HDD)

DIO5311 (6-inch LCD, 640x480 &amp; Connector)

RAM Cards

IWVB513ES4Y (512KB, w/2nd Battery)

IWVB101ES4Y (1Meg, w/2nd Battery)

IWVB201ES4Y (2Meg, w/2nd Battery)

Flash Cards

IWVB401S8YY (4MB)

IWVB801S8YY (8MB)

IWVB111S8YY (10MB)

Hard Disk Card

HDD170

AX/Modem Cards

FM144

FM96

ATA Flash Cards

ATA202NL11 (2.62MB)

ATA502NL11 (5.24MB)

ATA112NL11 (10.98MB)

LCD Panel Module (640x480, STN Mono)

CG9015 (1/240 Duty)

CG9013 (1/480 Duty)

## SELECTION GUIDE

### BLOCK DIAGRAM

# Liquid Crystal Display Modules

Second Edition

Seiko Instruments is an industry leader in advanced liquid crystal display technology worldwide. Since 1973, Seiko Instruments has been manufacturing a full range of LCDs and LCD modules for medical, industrial, test and measurement, and office automation applications.

Seiko Instruments offers a wide range of LCD modules in both alphanumeric and graphic configurations. These products feature twisted nematic and super twisted nematic technology and are available with electroluminescent and LED backlighting. Seiko Instruments' graphic modules feature advanced cathode fluorescent edge light technology for sharper text and graphics.

Seiko Instruments is a well recognized leader in precision engineering, design and manufacturing of the highest quality industrial high technology and consumer products. The company's Electronic Components Division offers other products to meet your next-generation design needs such as micro thermal printers, quartz crystals and oscillators, fiberoptic components, batteries and application specific standard semiconductors.

Call Seiko Instruments today. We are ready to provide the LCD technology, engineering support and superior quality for your next design.

**New Age Electronics, Inc.**

P.O. Box 1887 • Huntsville, AL 35807

(205) 895-9400 • Fax: (205) 895-0063

4835 University Square Suite #9 • Huntsville, AL 35816

**SII**

Seiko Instruments

Seiko Instruments USA Inc.

Electronic Components Division

2990 West Lomita Blvd.

Torrance, CA 90505 U.S.A.

Phone: (310) 517-7771

Facsimile: (310) 517-7792

SII is a registered trademark of Seiko Instruments USA Inc.

Specifications are subject to change without notice.

Printed in U.S.A.

# LCD TECHNOLOGY

## BASIC TECHNOLOGY

Liquid crystal displays (LCDs) are a passive display technology. This means they do not emit light; instead, they use the ambient light in the environment. By manipulating this light, they display images using very little power. This has made LCDs the preferred technology whenever low power consumption and compact size are critical.

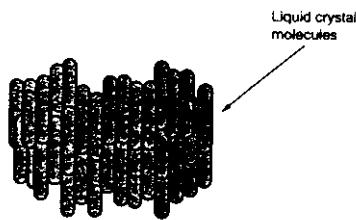

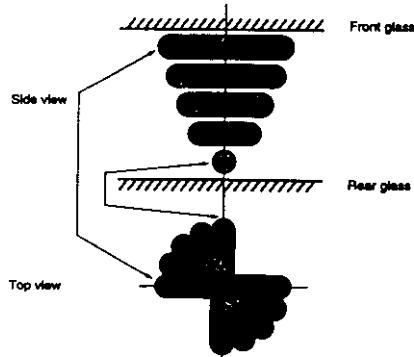

Liquid crystal (LC) is an organic substance that has both a liquid form and a crystal molecular structure. The rod-shaped molecules are normally in a parallel array, and an electric field can be used to control the molecules. Most LCDs today use a type of liquid crystal called twisted nematic (TN) (see Figure 1).

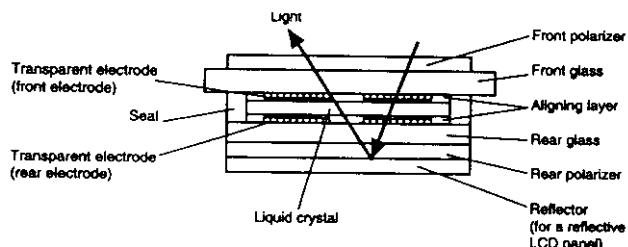

Figure 1 Structure of nematic liquid crystal

LCDs consist of two pieces of glass with electrodes printed on the inside. An alignment layer on each glass surface is used to twist the liquid crystal material in a helical or "twisted" pattern. Polarizers are used on the outside front and rear surfaces (see Figures 2 and 3).

Figure 2 TN LCD panel

Figure 3 Orientation of nematic liquid crystal molecules (twist angle: 90°)

When the LCD is 'off,' no voltage is applied to the electrodes, and light passes through the LCD. When it is 'on,' voltage is applied and the LC molecules align themselves in the direction of the electric field. This causes the LC to be out of phase with the light, creating a dark area on the LCD. By selectively applying voltage to the electrodes, a variety of patterns can be achieved.

Many advances in TN LCDs have been produced. Super twisted nematic (STN) LC material offers a higher twist angle ( $\geq 200^\circ$  vs.  $90^\circ$ ) that provides higher contrast and a better viewing angle. However, one negative feature is the birefringence effect, which shifts the background color to yellow-green and the character color to blue. This background color can be changed to a gray by using a special filter.

The most recent advance has been the introduction of film super twisted nematic (FSTN) displays. This adds a retardation film to the STN display that compensates for the color added by the birefringence effect. This allows a black and white display to be produced.

## BACKLIGHTING

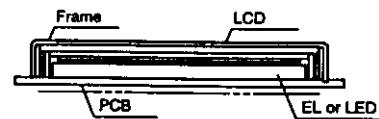

An LCD is basically a reflective part. It needs ambient light to reflect back to the eye. In uses where ambient light is low or nonexistent, a light source must be placed behind the LCD. This is known as backlighting (see Figure 4a). There are several technologies used:

**Electroluminescent (EL):** EL backlights are very thin, lightweight and provide an even light. They are available in a variety of colors, with white being the most popular for use with LCDs. While their power consumption is fairly low, they require voltages of 80 to 100 VAC. This is supplied by an inverter that converts a 5, 12 or 24 VDC input to the AC output. ELs have a limited life of 3,000 to 5,000 hours to half brightness.

**Light Emitting Diode (LED):** LED backlights offer a longer operating life — 50,000 hours minimum — and are brighter than ELs. They do consume more power than ELs. Being a solid state device, they operate directly off +5 VDC, so they do not require an inverter. However, a current limiting resistor is recommended for protection of the LEDs. LEDs are mounted in an array directly behind the display. LEDs come in a variety of colors, with yellow-green being the most common.

Figure 4a EL and LED Backlight

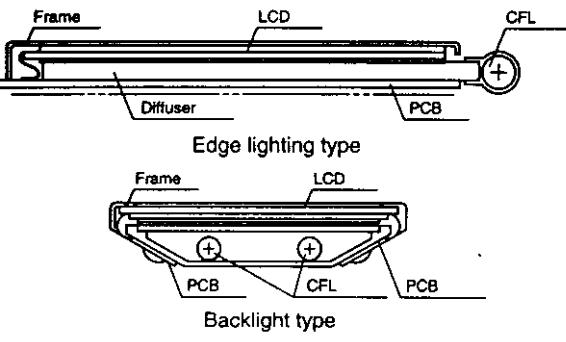

**Cold Cathode Fluorescent Lamp (CFL):** CFL backlight low power consumption and a very bright white light (Figure 4b). Two technologies are used: direct and edge. In both types a cold cathode fluorescent tube is the source. A diffuser distributes the light evenly across the area. Edge lighting offers a thinner package and less CFLs require an inverter to supply the 270 to 300 VAC by the CFL tube. They are used primarily in graphic and have a longer life — 10,000 to 15,000 hours — as do.

Figure 4b

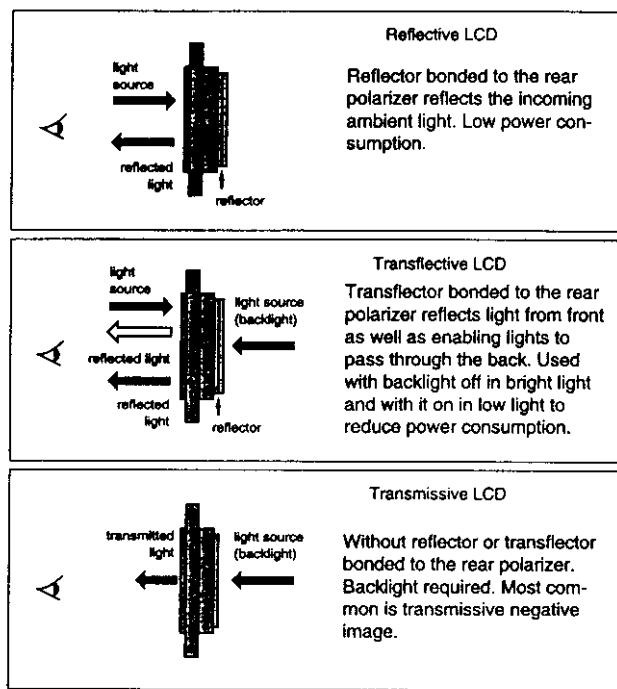

## VING MODES

CDs are offered in three basic light transmission modes: reflective, transreflective and transmissive (see Figure 5). In the reflective mode, ambient light is used to illuminate the display. This is achieved by combining a reflector with the polarizer. It works best in an outdoor or well-lighted environment.

Transreflective LCDs are a mixture of the reflective and transmissive types, with the rear polarizer having partial reflectivity. They are combined with a backlight for use in all lighting conditions. The backlight can be left off when there is sufficient outside lighting, conserving power. In other environments, the backlight is

on to provide a bright display. Reflective LCDs will not "wash out" when viewed in direct sunlight.

Transmissive LCDs have a transparent polarizer and do not reflect ambient light. They require a backlight to be visible. They work best in low light conditions with the backlight on continuously.

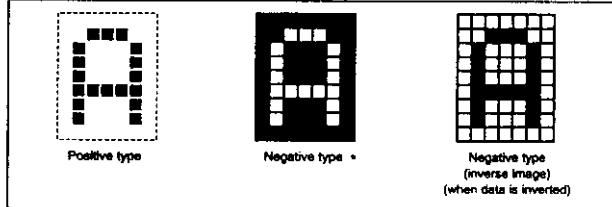

Another feature of the viewing mode is whether the LCD is a positive or negative image (see Figure 6). The standard image is positive, which means a light background with a dark character or dot. This works best in reflective or transreflective mode. A negative image is usually combined with a

transmissive mode. This provides a dark background with a light character. A backlight must be used to provide good illumination. In most graphic applications, the transmissive negative mode is inverted. This combination provides a light background with dark characters.

Figure 5

Figure 6

TABLE 1: LCD Viewing Modes

| Viewing Mode                 | Display Description                    | Application Comments                                                                               | Direct Sunlight          | Office Light        | Subdued Light            | Very Low Light      |

|------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------|---------------------|--------------------------|---------------------|

| Reflective Positive Image    | Dark segments on light background      | Not backlit. Provides best head-on contrast and environmental stability                            | Excellent                | Very Good           | Average                  | Poor                |

| Transflective Positive Image | Dark segments on grey background       | Can be viewed by reflected ambient light or with backlighting                                      | Excellent (No backlight) | Good (No backlight) | Good (Backlit)           | Very Good (Backlit) |

| Transflective Negative Image | Light grey segments on dark background | Needs high ambient light or backlighting. Frequently used with color and multicolor transreflector | Good (No backlight)      | Fair (No backlight) | Good (Backlit)           | Very Good (Backlit) |

| Transmissive Negative Image  | Backlit segments on dark background    | Cannot be read by reflection                                                                       | Poor (Backlit)           | Good (Backlit)      | Very Good (No backlight) | Excellent (Backlit) |

| Transmissive Positive Image  | Dark segments on backlit background    | Designed for very low light conditions, yet able to be read in bright ambient lights               | Good (No backlight)      | Good (Backlit)      | Very Good (Backlit)      | Excellent (Backlit) |

# Graphic LCD Modules

## Features

TN & FSTN technology offers excellent contrast and wide viewing angle

thin, light weight with low power consumption

FL backlight offers high brightness and long life

built-in controller on some models

bit parallel interface except for F1016, G1213 and G1216 (8-bit)

Graphic modules offer the greatest flexibility in putting data on the display. They allow for text, graphics or any combination of the two. Since character size is defined by software, they allow any language or character to be shown. The only limit is the resolution of the display.

Graphic modules are organized in rows (horizontal) and columns (vertical) of pixels. Each pixel is addressed individually, allowing any combination to be "on". This mapping provides the user with the ability to construct text of any size or shape, or true graphics, if that is desired. Seiko Instruments offers resolutions of 100x64 to 640x480.

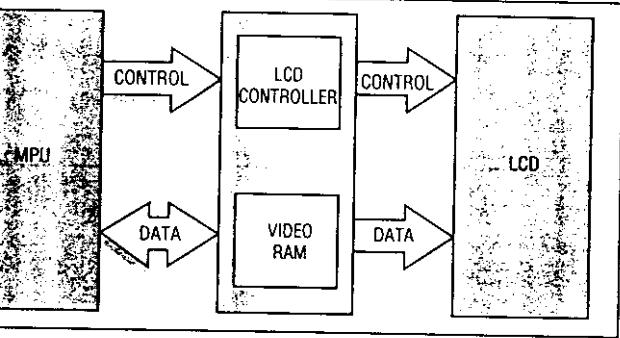

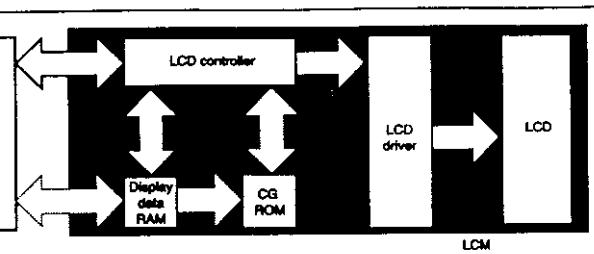

## Circuit Block Diagram

Figure 9

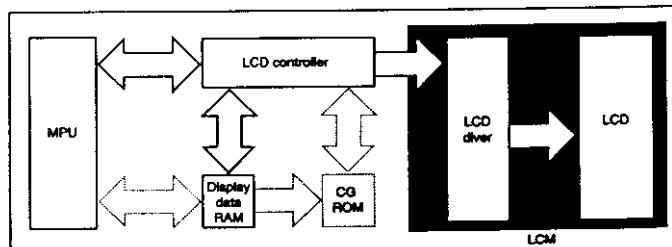

An LCD controller is required to send data to the graphic module (see Fig. 9). This specialized IC receives data from the MPU and sends the proper timing and data signals to the display. Data is sent to the display in 4-bit parallel mode. Each row of data is sent to a data register and then latched. This starts at the top of the display (line 1) and continues until the bottom is reached. For displays with more than 240 rows, the screen is split into upper and lower sections. In this case, 4 bits of data are sent to the upper and lower sections simultaneously.

## CONTROLLER CHIPS

A recommended listing of controller chips for Seiko Instruments graphic modules is shown on page 16. Each controller offers a different mix of features, simplicity and cost. Several modules are offered with an S-MOS SED1330FBA controller and data RAM built in. This allows the display to interface directly with an MPU. The SED1330FBA contains a CG ROM with 160 characters (5x7 format). It also offers a variety of advanced features.

## CONTROLLER BOARDS

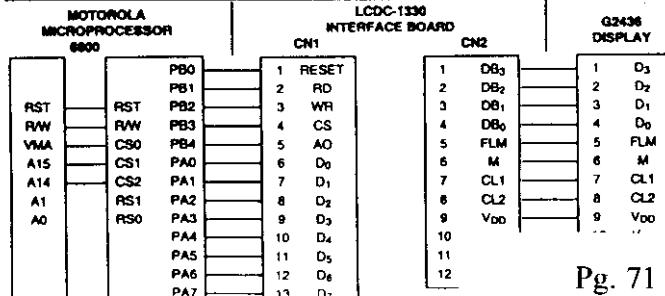

Seiko Instruments offers two controller or interface boards for use with displays that do not have a built-in controller. The first is the LCDC-1330, which contains the SED1330FBA controller chip. This board comes in two versions, the only difference being the amount of RAM included. The LCDC-1330 interfaces directly with the MPU and the display. It can control displays up to 640x200 resolution.

The UV-620 controller board is designed for VGA resolution displays. It contains the Cirrus Logic CL-GD610/620 chip set. This board is designed to be installed directly in a personal computer AT bus. It connects to the display and allows standard PC software to be run.

# Graphic LCD Specifications

## Timing Characteristics

The following Timing diagrams apply to all the graphic modules without a built-in controller.

### Timing characteristics of signal input into common driver

**PRODUCT SELECTION GUIDE (H=HORIZONTAL, V=VERTICAL, T=THICKNESS)****GRAPHIC MODULES****COLOR MODULES**

| Part Number | Dot Format (H x V) | LCD Fluid Type | Module Size (H x V x T,mm) | Viewing Area (H x V,mm) | Dot Size (H x V,mm) | Dot Pitch (H x V,mm) | Duty Cycle, Bias |

|-------------|--------------------|----------------|----------------------------|-------------------------|---------------------|----------------------|------------------|

| G121C0DX000 | 128 x 128          | ECB            | 86 x 95 x 7                | 67 x 67                 | 0.46 x 0.46         | 0.49 x 0.49          | 1/28, 1/10       |

| G121C2EX000 | 128 x 128          | ECB            | 86 x 95 x 7                | 67 x 67                 | 0.46 x 0.46         | 0.49 x 0.49          | 1/28, 1/10       |

**REFLECTIVE MODULES**

|             |           |       |                  |             |             |             |            |

|-------------|-----------|-------|------------------|-------------|-------------|-------------|------------|

| G121300N000 | 128 x 32  | WTSTN | 75 x 42 x 6.8    | 60 x 21     | 0.40 x 0.48 | 0.43 x 0.51 | 1/64,1/9   |

| G121600N000 | 128 x 64  | WTSTN | 75 x 53 x 6.8    | 60 x 33     | 0.40 x 0.40 | 0.43 x 0.43 | 1/64,1/9   |

| G122600N000 | 128 x 64  | STN   | 93 x 70 x 11.4   | 70.7 x 38.8 | 0.52 x 0.52 | 0.43 x 0.43 | 1/64,1/9   |

| G121C00P000 | 128 x 128 | WTSTN | 86 x 95 x 7.0    | 67 x 67     | 0.46 x 0.46 | 0.49 x 0.49 | 1/128,1/10 |

| G121C00P00C | 128 x 128 | WTSTN | 86 x 95 x 7.0    | 67 x 67     | 0.46 x 0.46 | 0.49 x 0.49 | 1/128,1/10 |

| G191C00R0A0 | 192 x 128 | FSTN  | 98 x 86 x 13.4   | 78 x 54     | 0.33 x 0.33 | 0.37 x 0.37 | 1/128,1/12 |

| G191D00P000 | 192 x 192 | WTSTN | 86 x 95 x 7.0    | 67 x 67     | 0.30 x 0.30 | 0.33 x 0.33 | 1/192,1/12 |

| G243600J000 | 240 x 64  | STN   | 180 x 75 x 11.3  | 134 x 41    | 0.49 x 0.49 | 0.53 x 0.53 | 1/64,1/9   |

| G648D00R000 | 640 x 200 | FSTN  | 270 x 150 x 12.0 | 239 x 104   | 0.32 x 0.46 | 0.35 x 0.49 | 1/200,1/15 |

**EL/LED BACKLIGHT MODULES**

|                      |           |       |                  |             |             |             |            |

|----------------------|-----------|-------|------------------|-------------|-------------|-------------|------------|

| G1213B1N000** (LED)  | 128 x 32  | WTSTN | 75 x 42 x 8.9    | 60 x 21     | 0.40 x 0.48 | 0.43 x 0.51 | 1/64,1/9   |

| G1216B1N000** (LED)  | 128 x 64  | WTSTN | 75 x 53 x 8.9    | 60 x 33     | 0.40 x 0.40 | 0.43 x 0.43 | 1/64,1/9   |

| G1226B1J000*** (LED) | 128 x 64  | STN   | 93 x 70 x 11.4   | 70.7 x 38.8 | 0.52 x 0.52 | 0.43 x 0.43 | 1/64,1/9   |

| G121CB1P000** (LED)  | 128 x 128 | WTSTN | 86 x 95 x 9.0    | 67 x 67     | 0.46 x 0.46 | 0.49 x 0.49 | 1/128,1/10 |

| G121CB1P000** (LED)  | 128 x 128 | WTSTN | 86 x 95 x 9.0    | 67 x 67     | 0.46 x 0.46 | 0.49 x 0.49 | 1/128,1/10 |

| G191C21R0A0** (EL)   | 192 x 128 | FSTN  | 98 x 86 x 13.4   | 78 x 54     | 0.33 x 0.33 | 0.37 x 0.37 | 1/128,1/12 |

| G191DB1P000** (LED)  | 192 x 192 | WTSTN | 86 x 95 x 9.0    | 67 x 67     | 0.30 x 0.30 | 0.33 x 0.33 | 1/192,1/12 |

| G243621A000*** (EL)  | 240 x 64  | STN   | 180 x 75 x 11.3  | 134 x 41    | 0.49 x 0.49 | 0.53 x 0.53 | 1/64,1/9   |

| G648D21B000** (EL)   | 640 x 200 | STN   | 270 x 150 x 12.0 | 239 x 104   | 0.32 x 0.46 | 0.35 x 0.49 | 1/200,1/15 |

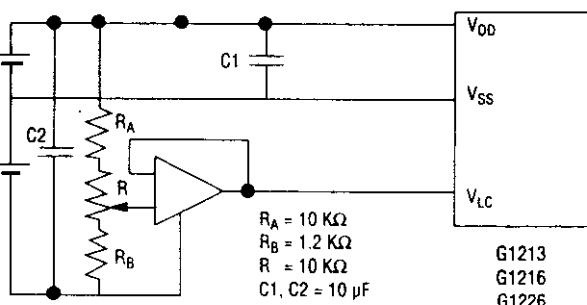

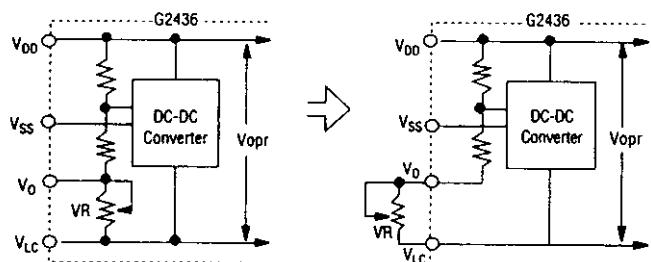

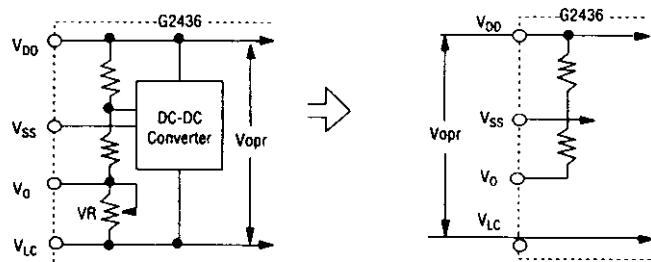

(Unit: mm) A built-in DC/DC converter eliminates the need for  $V_{LC}$ . \*\* These models are transreflective positive viewing mode for direct sunlight applications. All other EL and CFL versions are transmissive negative. WTSTN = Wide temperature super twisted nematic fluid. STN = Super twisted nematic fluid. FSTN = Film super twisted nematic fluid.

**G1213****G1216**

**PRODUCT SELECTION GUIDE (H=HORIZONTAL, V=VERTICAL, T=THICKNESS)****GRAPHIC MODULES****COLOR MODULES**

| Power Requirements            |                                |                                       | Weight<br>(g) | Suitable Controller | Controller Board | Inverter | Part Number |

|-------------------------------|--------------------------------|---------------------------------------|---------------|---------------------|------------------|----------|-------------|

| VDD<br>(V <sub>DD</sub> X mA) | VLC<br>(V <sub>LIC</sub> X mA) | Backlight +<br>(V <sub>BL</sub> X mA) |               |                     |                  |          |             |

| +5V @ 10.0                    | -15V @ 10.0                    | •                                     | 90            | SED-1351*           | •                | •        | G121C0DX000 |

| +5V @ 10.0                    | -15V @ 10.0                    | +5V @ 110                             | 90            | SED-1351*           | •                | INV-50   | G121C2EX000 |

ko Instruments will introduce the S-4581A controller designed for the ECB Color Graphic Modules in mid '96.

**REFLECTIVE MODULES**

|             |              |   |     |                   |                |   |             |

|-------------|--------------|---|-----|-------------------|----------------|---|-------------|

| +5V @ 2.0 - | 8V @ 1.5     | • | 40  | Built-in Data RAM | (Built-in RAM) | • | G121300N000 |

| +5V @ 2.0 - | 8V @ 1.5     | • | 40  | Built-in Data RAM | (Built-in RAM) | • | G121600N000 |

| +5V @ 4.3   | -15V @ 4.1   | • | 75  | MSM6255GS         | LCDC-1330-32A  | • | G121C00P000 |

| +5V @ 6.5   | -15V @ 4.1   | • | 75  | Built-in SED1335  | (Built-in)     | • | G121C00P00C |

| +5V @ 3.1   | -12.4V @ 2.9 | • | 100 | MSM6255GS         | LCDC-1330-32A  | • | G191C00R0AO |

| +5V @ 6.5   | -18V @ 6.0   | • | 75  | MSM6255GS         | LCDC-1330-32A  | • | G191D00P000 |

| +5V @ 8.0   | —            | • | 140 | MSM6255GS         | LCDC-1330-32A  | • | G243600J000 |

| +5V @ 11.0  | -24V @ 9.0   | • | 450 | MSM6255GS         | LCDC-1330-32A  | • | G648D00R000 |

**BLACKLIGHT MODULES**

|            |              |             |     |                   |                |             |                    |

|------------|--------------|-------------|-----|-------------------|----------------|-------------|--------------------|

| +5V @ 2.0  | -BV @ 1.5    | +4.1V @ 50  | 45  | Built-in Data RAM | (Built-in RAM) | •           | G1213B1N000 (LED)  |

| +5V @ 2.0  | -8V @ 1.5    | +4.1V @ 100 | 45  | Built-in Data RAM | (Built-in RAM) | •           | G1216B1N000 (LED)  |

| +5V @ 6.5  | -18V @ 6.0   | +4.1V @ 120 | 100 | MSM625565         | LCDC-1330-32A  | •           | G121C81P000 (LED)  |

| +5V @ 6.5  | -18V @ 6.0   | +4.1V @ 120 | 100 | Built-in SED1335  | (Built-in)     | •           | G121C81P00C (LED)  |

| +5V @ 3.1  | -12.4V @ 2.9 | +5V @ 120   | 100 | MSM6255GS         | LCDC-1330-32A  | SKI-050-05H | G191C21R0AO** (EL) |

| +5V @ 6.5  | -18V @ 6.0   | +4.1V @ 120 | 100 | MSM6255GS         | LCDC-1330-32A  | •           | G191D81P000 (LED)  |

| +5V @ 8.0  | —            | +5V @ 75    | 140 | MSM6255GS         | LCDC-1330-32A  | NEL-D32-49  | G243621A000** (EL) |

| +5V @ 11.0 | -24V @ 9.0   | +12V @ 115  | 450 | MSM6255GS         | LCDC-1330-32A  | NEL-D5-006  | G648D21B000** (EL) |

Power consumption is typical and includes the backlight. For the EL and CFL Versions it includes inverter losses. (Unit: mm)

**G121C**

6130

**G191D**5119

53

G 191 D

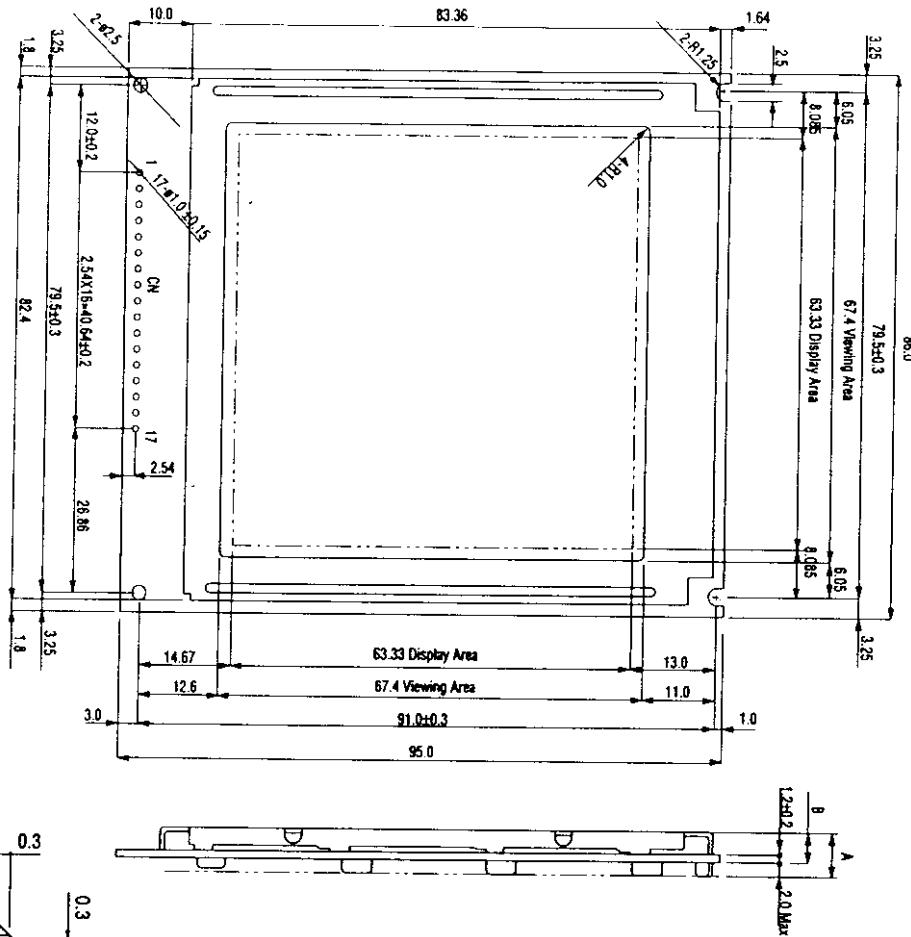

(192 x 192) Unit: mm General Tolerance  $\pm 0.5$

|   |     |    |          |

|---|-----|----|----------|

| 6 | CL2 | 13 | $V_B$    |

| 7 | D1  | 14 | $V_{BS}$ |

| No. | Symbol           | No. | Symbol          |

|-----|------------------|-----|-----------------|

| 1   | V <sub>ce</sub>  | 10  | D1              |

| 2   | F <sub>exp</sub> | 11  | D2              |

| 3   | CL2              | 12  | D3              |

| 4   | INH              | 13  | V <sub>ce</sub> |

| 5   | ELM              | 14  | V <sub>e</sub>  |

| 6   | CL1              | 15  | V <sub>ce</sub> |

| 7   | V <sub>ce</sub>  | 16  | LED (+)         |

| 8   | M                | 17  | LED (-)         |

| 9   | DO               |     |                 |

**No connection to pins 16 & 17 for reflective part (G191D00P000).**

# PRINCIPLES OF OPERATION

Graphic modules offer the greatest flexibility in format-data on the display. They allow for text, graphics or any combination of the two. Since character size is defined byware, they allow any language or character font to beown. The only limit is the resolution of the display.

Graphic modules are organized in rows (horizontal) and columns (vertical) of pixels. Each pixel is addressed individually, allowing any combination to be ON. This bitmapping provides the user with the ability to construct text of any size, shape, or true graphics, if that is desired.

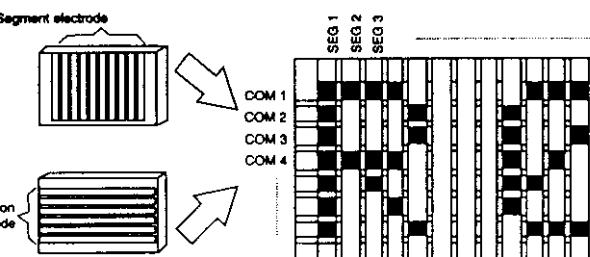

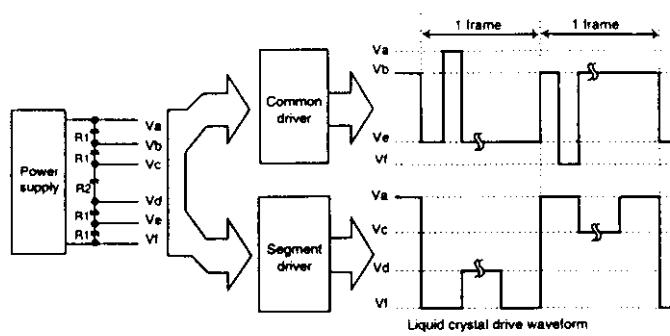

The above figure shows the structure of an LCD. Liquid crystals are placed between two types of glass substrates, one having segment electrodes (SEG1, SEG2, and so on), the other having common electrodes (COM1, COM2, and so on). Each cross point of the segment and common electrodes is a display pixel.

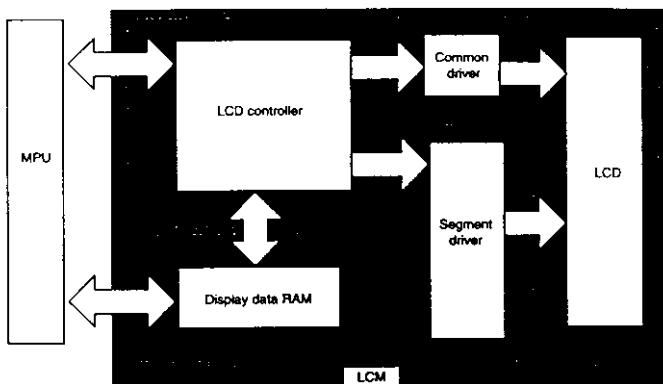

The LCD is driven as follows. The common electrodes are sequentially selected. The display pixels on the selected common electrode are turned on/off according to the select/non-select signals of the corresponding segment electrodes. This is called multiplex drive.

The LCD drivers are classified into two types: the common driver and the segment driver. The common driver drives common electrodes and the segment driver drives segment electrodes. As shown in the figure above, these drivers select a proper voltage level sequentially from the six voltage levels (Va to Vf) to generate liquid crystal drive waveforms. The six voltage levels are generated by resistance division.

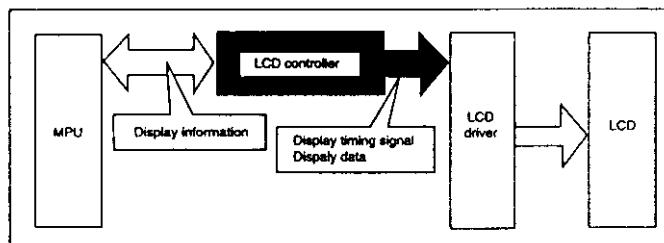

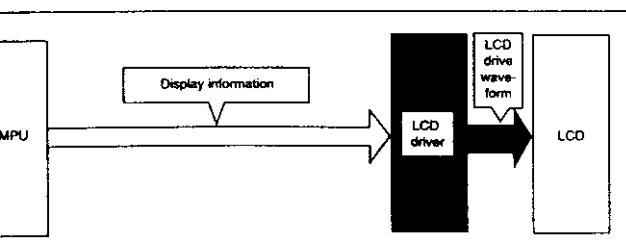

## LCD CONTROLLER

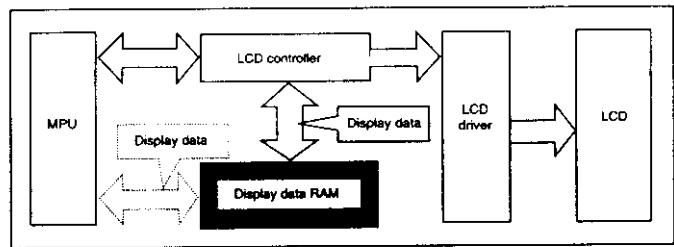

The MPU cannot directly interface the LCD driver. So the LCD controller is placed between the MPU and the LCD drivers to handle the interface between them.

The LCD controller receives display information from the MPU, converts it into the display timing signals and display data required for the LCD drivers, and transfers them to the LCD drivers.

The LCD driver generates liquid crystal drive waveforms according to the display information sent from the MPU, and sends the waveforms to drive the LCD.

# PRINCIPLES OF OPERATION

(CONTINUED)

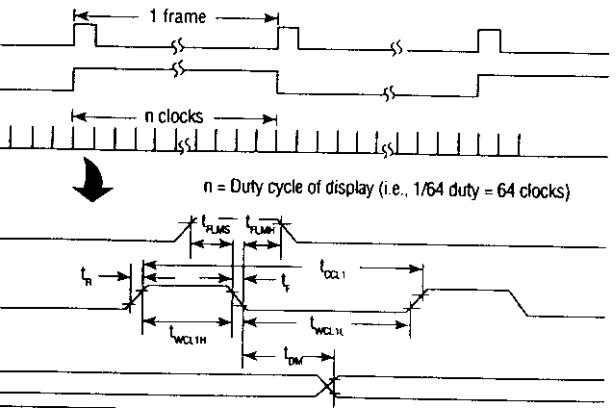

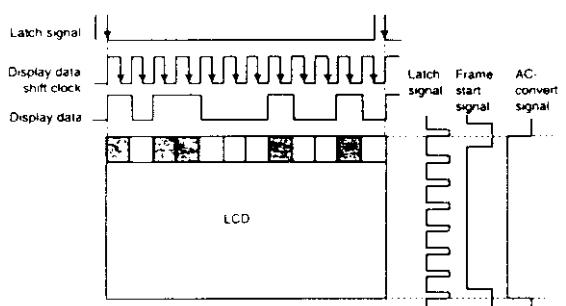

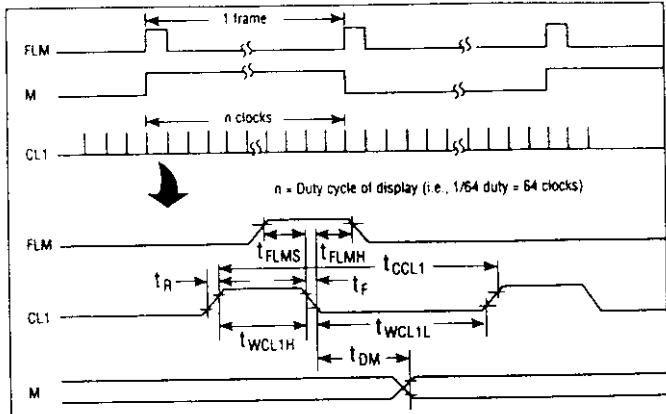

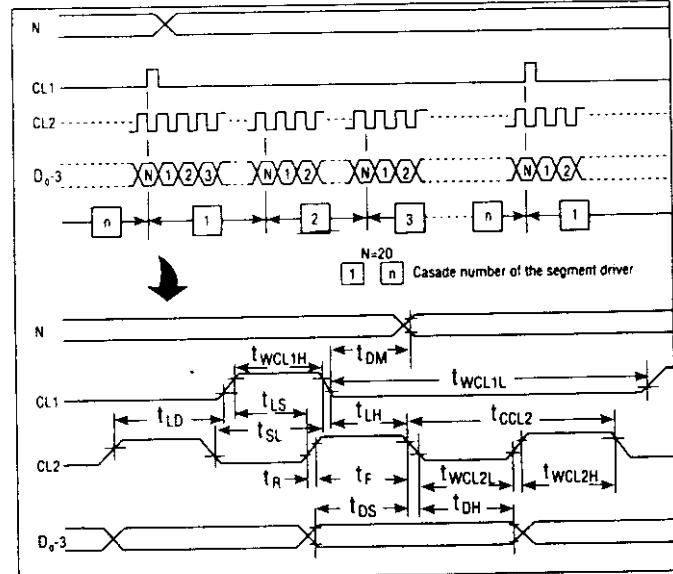

There are four display timing signals: display data shift clock, latch signal, frame start signal, and AC-convert signal.

There are two formats for the display data transfer: serial transfer and parallel transfer. In serial transfer, data is transferred bit by bit as shown in the figure above. In parallel transfer, four or eight bits are transferred at the same time. All **Seiko Instruments** graphic modules use parallel transfer.

## DISPLAY DATA RAM

The display data RAM stores the display information sent from the MPU. The LCD controller reads data from the display data RAM, and transfers the data to the LCD drivers. Some LCD controllers let the MPU directly interface the display data RAM as shown by dotted lines in the figure above.

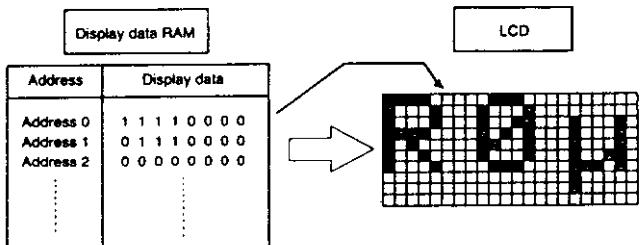

One of the methods to correspond display contents to display data is to assign a display data bit to a display pixel dot. In that case, if the MPU writes and stores data "11110000" at address 0 of the display data RAM, the LCD screen displays a pattern of "■■■■■□□□□□" according to the 0s and 1s in the data. This correspondence method is called the graphic display mode. The graphic display mode allows any pattern to be displayed, because each display pixel dot can be turned on and off independently.

## GRAPHIC LCD MODULE WITH BUILT-IN RAM (G1213, G1216, G1226)

Graphic modules with built-in data RAM have two types of ICs: one integrating the controller and common driver, and one integrating the display data RAM and the segment driver. These modules use direct bitmapping; one bit in RAM corresponds to each pixel on the display. They communicate directly to the microprocessor through an 8-bit parallel interface. All the required controller timing functions are built-in to the module. There is no CG ROM, or any way to store information.

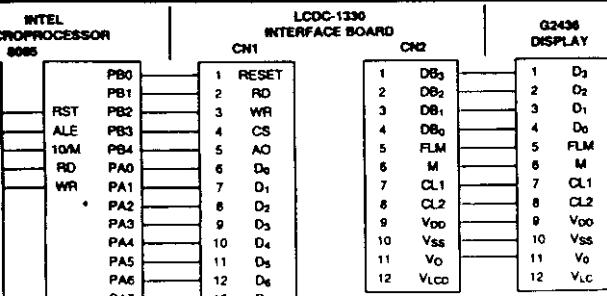

## GRAPHIC LCD MODULES WITH EXTERNAL CONTROLLER (G191C, G191D, G2436, G321E, G648D, G649D)

Most graphic modules feature the segment and common drivers on the LCD module, and use a 4-bit parallel interface to an external controller. The controller can be an external PC board (such as the LCD-1330) or the controller IC can be located on the mother board with the microprocessor. In the larger graphic modules, all the board space is taken up with the driver ICs. Also for small graphic modules with high resolution, there may be no room to locate the controller on the module.

## GRAPHIC MODULES WITH BUILT-IN CONTROLLER (G121C, G2446, G242C, 21D, G324E)

Seiko Instruments offers five graphic modules with the G30 controller built-in.\* These modules interface directly with a microprocessor with an 8-bit parallel interface. The G30 was carefully chosen to offer our customers the most advanced features, including overlayed graphics and text, horizontal and vertical scrolling, built-in character generator, external RAM, etc.

Model G121C features SED1335...see p. 65.

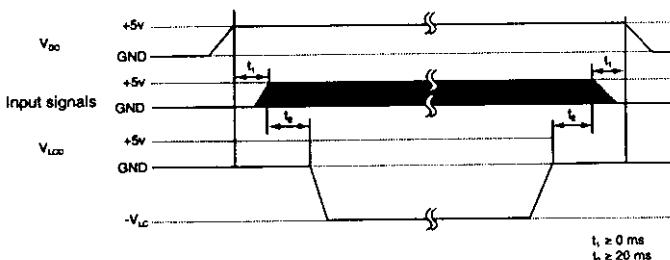

## POWER ON/OFF AND SIGNAL INPUT TIMING

Power ON/OFF and signal input should be performed according to the timing shown below in order not to damage the LCD driving circuit and the LCD panel. See special requirements for G1213, G1216 and G1226 in the next section.

| INTERFACE SIGNAL                 | FUNCTION                                                                                                                      |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| A0                               | Command mode set                                                                                                              |

| CL1                              | Display data latch signal. Signal is used to latch data in each common line                                                   |

| CL2                              | Display data shift signal. Clock signal to shift data in 4-bit increments to the display                                      |

| CS1, CS2                         | Chip select (read/write enable)                                                                                               |

| /CS                              | Chip select                                                                                                                   |

| CS11-CS24                        | Chip select (screen selection)                                                                                                |

| D <sub>0</sub> -D <sub>3</sub>   | Display data signal; D0-D3 for single screen; UD0-UD3 & LD0-LD3 for dual screen display                                       |

| DB <sub>0</sub> -DB <sub>7</sub> | Tri-state bidirectional data bus                                                                                              |

| D/I                              | Display data/display control data instruction                                                                                 |

| E                                | Enable                                                                                                                        |

| FLM                              | Frame start-up signal. Beginning signal that is sent at the start of each screen frame                                        |

| INHX                             | Display on/off signal: H=on, L=off                                                                                            |

| M                                | Liquid crystal AC signal. This signal provides AC polarity in each display frame to prevent damage to the LCD from DC voltage |

| /RD                              | Read                                                                                                                          |

| /RES RST                         | Reset                                                                                                                         |

| RS                               | Register select signal                                                                                                        |

| R/W                              | Read/write select signal                                                                                                      |

| SEL1, SEL2                       | MPU interface configuration; for Intel, SEL 1=0, SEL 2=0; for Motorola, SEL 1=1, SEL 2=0                                      |

| V <sub>dd</sub>                  | Power supply voltage for logic: +5 V                                                                                          |

| V <sub>lc</sub>                  | Power supply for LCD: -5 V to -24 V (see model)                                                                               |

| V <sub>o</sub>                   | LCD contrast adjustment voltage                                                                                               |

| V <sub>ss</sub>                  | Ground                                                                                                                        |

| W/R                              | Write                                                                                                                         |

# PRINCIPLES OF OPERATION

(CONTINUED)

## TIMING CHARACTERISTICS

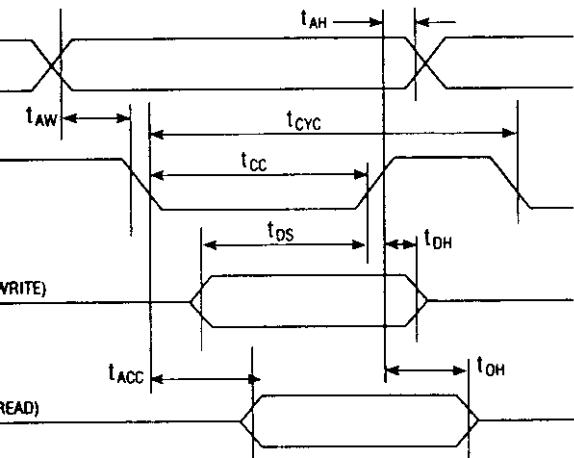

The following timing diagrams apply to all the graphic modules without a built-in controller.

Timing characteristics of signal input into segment driver.

Timing characteristics of signal input into segment driver.

### TIMING CHARACTERISTICS TEMP. = 0 - 50°C, V<sub>DD</sub> = 5.0V ± 5%, V<sub>SS</sub> = 0V

| Item                      | Symbol             | Min. | Max. | Unit |

|---------------------------|--------------------|------|------|------|

| CL1 period                | t <sub>CCL1</sub>  | 1000 |      | ns   |

| CL1 "H" pulse width       | t <sub>WCL1H</sub> | 125  |      | ns   |

| FLM setup time            | t <sub>FLMS</sub>  | 100  |      | ns   |

| FLM hold time             | t <sub>FLMH</sub>  | 100  |      | ns   |

| Input signal rise time    | t <sub>R</sub>     |      | 30   | ns   |

| Input signal fall time    | t <sub>F</sub>     |      | 30   | ns   |

| CL2 period                | t <sub>CCL2</sub>  | 330  |      | ns   |

| CL2 "H" pulse width       | t <sub>WCL2H</sub> | 110  |      | ns   |

| CL2 "L" pulse width       | t <sub>WCL2L</sub> | 110  |      | ns   |

| Data setup time           | t <sub>DS</sub>    | 100  |      | ns   |

| Data hold time            | t <sub>DH</sub>    | 100  |      | ns   |

| CL2 fall to CL1 fall time | t <sub>SL</sub>    | 125  |      | ns   |

| CL1 fall to CL2 fall time | t <sub>LH</sub>    | 80   |      | ns   |

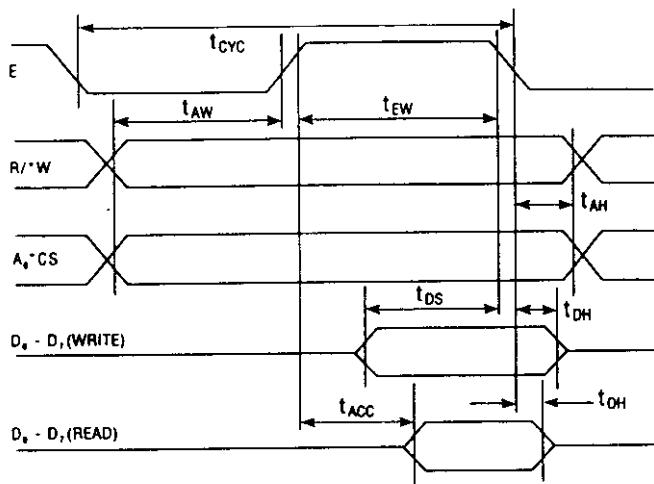

## TIMING CHARACTERISTICS FOR MODULES WITH BUILT-IN 1330 CONTROLLER

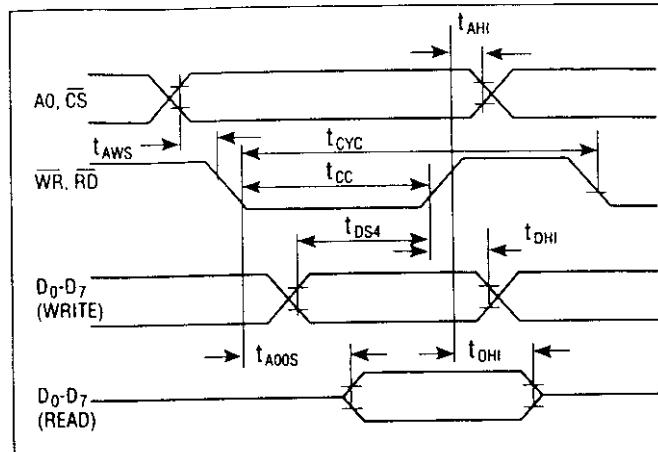

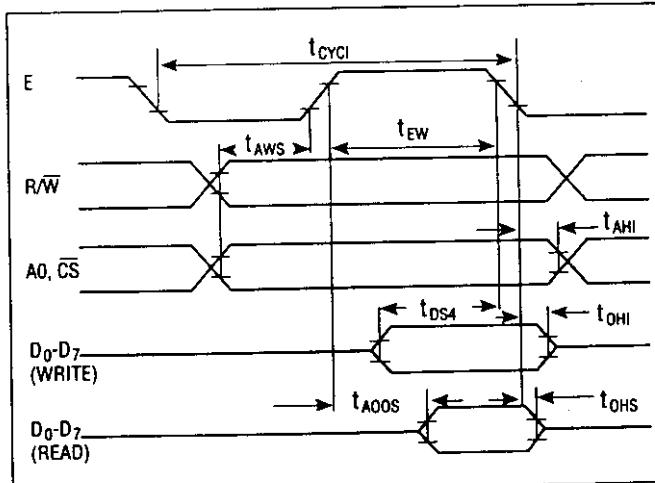

Intel 80 series timing diagram

Motorola 68 series timing diagram

| Signal                  | Symbol         | Item                                                                      | Min.                                                                       | Max.                         | Unit                      |

|-------------------------|----------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------|---------------------------|

| 80 series timing        | WR RD          | t <sub>CYC</sub><br>t <sub>CC</sub>                                       | System cycle time<br>Control pulse width                                   | 1000<br>220                  | -<br>ns                   |

| 68 series timing        | A0, CS, R/W, E | t <sub>CYC</sub><br>t <sub>EW</sub>                                       | System cycle time<br>Enable pulse width                                    | 1000<br>220                  | -<br>ns                   |

|                         | A0, CS         | t <sub>AH</sub><br>t <sub>AW</sub>                                        | Address hold time<br>Address setup time                                    | 10<br>30                     | -<br>ns                   |

| 80 and 68 series timing | D0-D7          | t <sub>DS</sub><br>t <sub>DH</sub><br>t <sub>ACC</sub><br>t <sub>OH</sub> | Data setup time<br>Data hold time<br>RD access time<br>Output disable time | 120<br>10<br>120<br>10<br>50 | -<br>ns<br>ns<br>ns<br>ns |

Note: See page 53 for microprocessor ch

# 330 CONTROLLER FEATURES

## 1330 ADVANCED LCD DISPLAY

### CONTROLLER

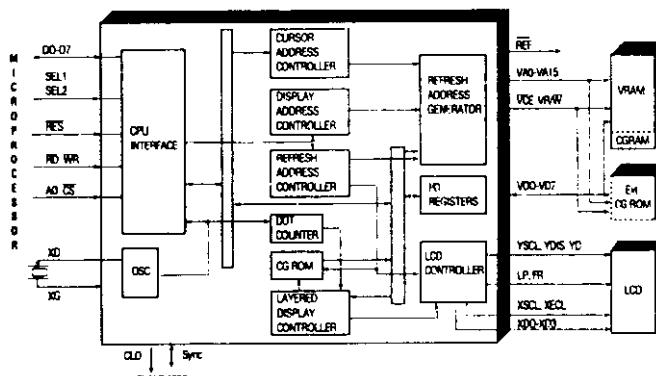

Seiko Instruments has selected the SED1330 to use as a built-in controller in our mid-size graphic modules. This high performance LSI device generates all the signals required by the display memory and LCD drivers, and incorporates a character generator ROM. The command set within the SED1330 allows the user to create a layered display of characters and graphics, scroll the display, and assign display attributes to selected areas of the screen. The controller also functions as a pipeline buffer between the MPU and display memory so a low cost, medium speed SRAM can be used.

This advanced LCD controller IC features:

- 6800 and 8080 family compatibility

- 8-bit parallel buffered MPU interface (bi-directional)

- Control of 64 K bytes of memory

- Horizontal and vertical scrolling

- Reverse video and flashing

- Up to three layers of graphics

- Up to two layers of mixed character & graphics

- User defined characters & internal character generator

- Supports external character ROM & RAM

- Supports 8 x 8 or 8 x 16 pixel characters

The new SED1335 controller, used in model G121C, has the same features as the SED1330. In addition, this new controller accommodates a +3.3 volt input.

The SED1330, shown in the block diagram, is located between the MPU and the display memory. This permits the MPU to send and receive control commands and data for display. The SED1330 can control up to 64 K bytes of display memory.

The on-chip LCD control circuit enables the SED1330 to support all the graphic features of the Seiko Instruments LCD modules, using the on-chip register functions with no external parts.

The SED1330 divides its memory space into four areas:

1. Character data table

2. Graphics data table

3. CG RAM table

4. External CG ROM table

Internal Block Diagram

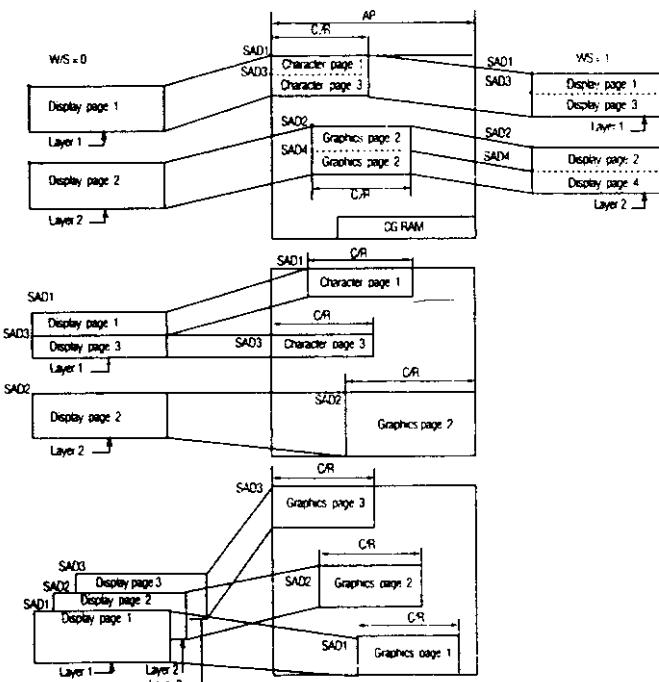

The SED1330 supports virtual screens that are larger than the physical size of the LCD panel address range, C/R. A layer of the SED1330 can be considered as a window in the larger virtual screen held in display memory. This window can be divided into two blocks, with each block able to display a different portion of the virtual screen.

This enables, for example, one block to dynamically scroll through a data area while the other acts as a status message display area.

Display Layers and Memory

# 1330 CONTROLLER FEATURES (CONTINUED)

An SED1330 can provide a superimposed display of up to three layers of screens, but the cursor can be displayed on only one of the three. If more than one layer is used, the cursor home layer is

- The 1st layer (L1) for a two-layer display.

- The 3rd layer (L3) for a three-layer display.

The cursor is not displayed outside its home layer.

Screens can be moved into the cursor's home layer by adjusting the parameters of the SCROLL command.

## SCROLLING

Scrolling of the screens is managed by the MPU, and affected by dynamically modifying the contents of the scroll address registers (SAD1 to SAD4). The MPU determines when scrolling should occur, selection of scroll mode, scroll rate, etc.

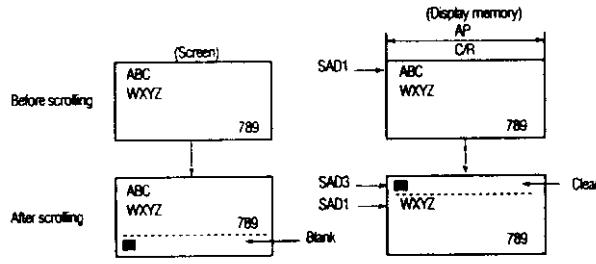

### ON-PAGE SCROLLING

Scrolling is executed in a display memory area the size of one screen. When the cursor is on the bottom line of the display, as shown below, execution of a line feed (LF) or the entry of the last character in the line should cause the whole screen to scroll up by one line width and the bottom line to be cleared. This is achieved by splitting the display between two screens, 1 and 3.

1. Set the start address of screen 3 to the current start address of screen 1 (SAD3 = SAD1).

2. Move screen 1 down one line (SAD1 = SAD1 + AP).

3. Clear the last line of screen 3.

On-page Scrolling

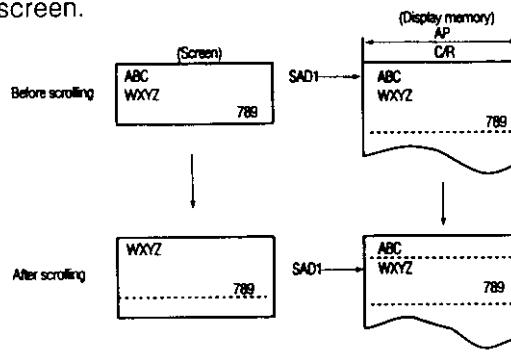

### INTER-PAGE SCROLLING AND PAGE SWITCH-OVER

Inter-page scrolling and page switch-over are available when using display memory with a capacity of more than one screen.

Inter-page Scrolling

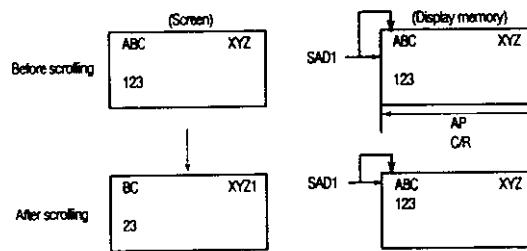

### HORIZONTAL WRAPAROUND SCROLLING

This scrolling style is available when C/R = AP.

Horizontal Wraparound Scrolling

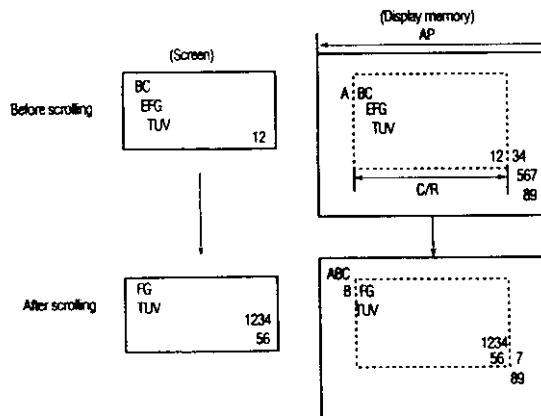

### MULTIDIRECTIONAL SCROLLING

This style of scrolling is available when the size of display memory is larger than the actual screen by at least one character in both the X and Y directions. Multidirectional scrolling is usually made in 1-character units, but by using the HDOT SCR command pixel by pixel, horizontal scrolling is also possible.

Multidirectional Scrolling

## INTERNAL CHARACTER GENERATOR FONT

| Character code bits 0 to 3 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|----------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|                            | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F |

| 2                          | . | . | . | . | . | . | . | . | . | . | . | . | . | . | . | . |

| 3                          | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F |

| 4                          | A | B | C | D | E | F | G | H | I | J | K | L | M | N | O | P |

| 5                          | P | Q | R | S | T | U | V | W | X | Y | Z | ! | ? | ; | , | . |

| 6                          | . | a | b | c | d | e | f | g | h | i | j | k | l | m | n | o |

| 7                          | P | Q | R | S | T | U | V | W | X | Y | Z | ! | ? | , | , | , |

| A                          | 8 | 9 | J | . | 8 | 7 | 2 | 4 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 |

| B                          | 3 | 1 | 2 | 2 | 4 | 0 | 7 | 2 | 7 | 0 | 0 | 2 | 2 | 2 | 2 | 2 |

| C                          | 3 | 1 | 2 | 2 | 1 | 2 | 2 | 2 | 2 | 1 | 2 | 2 | 2 | 2 | 2 | 2 |

| D                          | 3 | 2 | 2 | 2 | 1 | 2 | 2 | 2 | 2 | 1 | 2 | 2 | 2 | 2 | 2 | 2 |

| 1                          | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

# 1330 CONTROLLER FEATURES (CONTINUED)

## EXTERNAL CHARACTER GENERATOR ROM

The external CG ROM can be used when fonts other than those in the internal ROM are needed. Data is stored in the external ROM in the same format used in the internal ROM.

- ▶ Up to 8 x 8-pixel characters ( $M2 = 0$ ) or 8 x 16-pixel characters ( $M2 = 1$ )

- ▶ Up to 256 characters (192 if used together with the internal ROM)

- ▶ Mapped into the display memory address space at FOOOH to F7FFH ( $M2 = 0$ ) or FOOOH to FFFFH ( $M2 = 1$ )

- ▶ Characters can be up to 8 x 16 pixels; however, excess bits must be set to zero.

## CHARACTER GENERATOR RAM

The user can freely use the character generator RAM for storing graphics characters. The character generator RAM can be mapped by the microprocessor anywhere in display memory, allowing effective use of unused address space.

- ▶ Up to 8 x 8-pixel characters ( $M2 = 0$ ) or 8 x 16 characters ( $M2 = 1$ )

- ▶ Up to 256 characters if mapped at FOOOH to FFFFH (64 if used together with character generator ROM)

- ▶ Can be mapped anywhere in display memory address space if used with the character generator ROM

- ▶ Mapped into the display memory address space at FOOOH to F7FFH if not used with the character generator ROM (more than 64 characters are in the CG RAM). Set SAGO to FOOOH and M1 to zero when defining characters number 193 upwards.

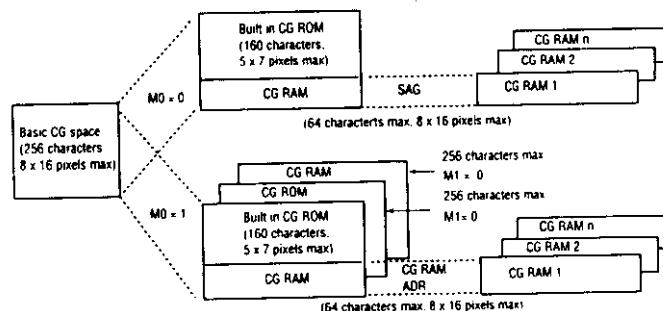

## CG MEMORY ALLOCATION

Since the SED1330 uses 8-bit character codes, it can handle no more than 256 characters at a time. However, if a wider range of characters is required, character generator memory can be bank-switched using the CG RAM ADR command.

Internal and external character mapping

Note that there can be no more than 64 characters per bank.

## CHARACTER MAPPING

| Item                                                     | Parameter                                             | Remarks                                                   |

|----------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------|

| Internal/external character generator selection          |                                                       | M0                                                        |

| Character field height                                   | $M2 = 0$                                              |                                                           |

| 1 to 8 pixels                                            | $M2 = 1$                                              |                                                           |

| 9 to 16 pixels                                           | Graphics mode (8 bits x 1 line)                       |                                                           |

| Internal CG ROM/RAM select<br>External CG ROM/RAM select | Automatic                                             | Determined by the character code                          |

| CG RAM bit 6 correction                                  | M1                                                    |                                                           |

| CG RAM data storage address                              | Specified with CG RAM ADR command                     | Can be moved anywhere in the display memory address space |

| External CG ROM address                                  | Other than the area of figure 49                      |                                                           |

| More than 192 characters                                 | Set SAG to FOOOH and overlay SAG and the CG ROM table |                                                           |

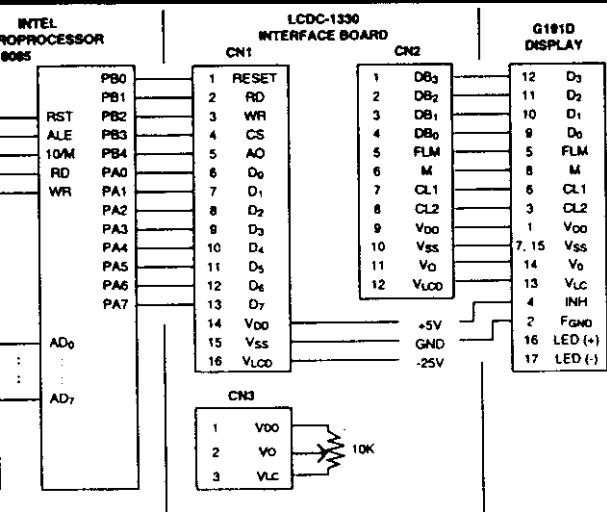

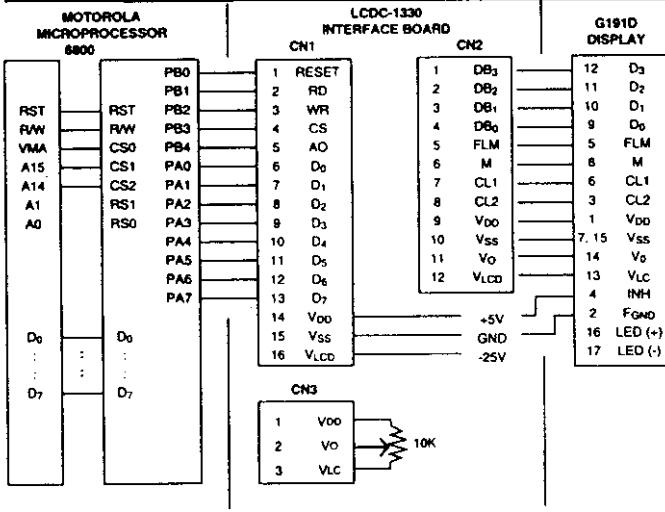

# LCDC-1330 CONTROLLER BOARD

The Seiko Instruments family of LCDC-1330 controller features the advanced SED1330 IC described in the section. These controller boards are designed to the user to quickly interface our graphic modules with 8085 or Motorola 6800 series microprocessors to display text, graphics, and overlaid text and graphics. The boards support 32K bytes of static RAM as display memory that can be defined as text space or graphics. These memory spaces may be overlaid to produce graphics and text, inverse video, area blinking, and masking.

## MORY SIZE SELECTION

| Resolution | Min. memory size for 1 screen | Model number  |

|------------|-------------------------------|---------------|

| LCD        |                               |               |

| X 128      | 2K                            | LCDC-1330-32A |

| X 64       | 2K                            | LCDC-1330-32A |

| X 128      | 3K                            | LCDC-1330-32A |

| X 192      | 5K                            | LCDC-1330-32A |

| X 128      | 4K                            | LCDC-1330-32A |

| X 200      | 8K                            | LCDC-1330-32A |

| X 240      | 8K                            | LCDC-1330-32A |

| X 200      | 16K                           | LCDC-1330-32A |

## LCDC-1330 FEATURES

### CHARACTER DISPLAY MODE

- Programmable or automatic cursor shift function

- Flexible scroll function

- Two or three screen layered function

- Block or underline cursor function

- Area flashing function

- Internal character generator: JIS 160 characters (5x7)

- External character generator: 256 characters (8x8 or 8x16)

### GRAPHIC DISPLAY MODE

- Maximum display size: 640 dots (H) x 256 dots (V)

- 2 or 3 screen overlaid function

- Independent block flashing and on/off control

- Graphic display mode can be mixed with character display mode

## ELECTRICAL CHARACTERISTICS ( $T_{OPR} = 0^\circ\text{C to } 50^\circ\text{C}$ $V_{DD} = 5V \pm 5\%$ ; $V_{SS} = 0V$ )

| Parameter                         | Mln.         | Typ.        | Max.        | Units         | Conditions                                      | Terminals                   |

|-----------------------------------|--------------|-------------|-------------|---------------|-------------------------------------------------|-----------------------------|

| Supply Voltage                    | 4.0          | 5.0         | 6.0         | V             |                                                 | $V_{DD}$                    |

| Power Down Supply Voltage         | 2.0          |             | 6.0         | V             |                                                 |                             |

| Input High Voltage (TTL)          | 2.2          |             |             | V             |                                                 |                             |

| Input Low Voltage (TTL)           | -0.3         |             | 0.8         | V             |                                                 |                             |

| Output High Voltage (TTL)         | 2.4          |             |             | V             |                                                 |                             |

| Output Low Voltage (TTL)          |              |             | 0.4         | V             | $I_{OH}=-0.5\text{mA}$<br>$I_{OL}=5.0\text{mA}$ | $D_0 - D_7, A0$<br>CS RD WR |

| Input High Voltage (CMOS)         | $0.8V_{DD}$  |             |             | V             |                                                 |                             |

| Input Low Voltage (CMOS)          |              |             | $0.2V_{DD}$ | V             |                                                 |                             |

| Output High Voltage (CMOS)        | $V_{DD}-0.4$ |             |             | V             |                                                 |                             |

| Output Low Voltage (CMOS)         | -            |             | 0.4         | V             | $I_{OH}=1.6\text{mA}$<br>$I_{OL}=1.6\text{mA}$  | DB0-DB3, FLM, M<br>CL1 CL2  |

| Positive-going Threshold Voltage  | $0.5V_{DD}$  | $0.7V_{DD}$ | $0.8V_{DD}$ | V             |                                                 | RES                         |

| Negative-going Threshold Voltage  | $0.2V_{DD}$  | $0.3V_{DD}$ | $0.5V_{DD}$ | V             |                                                 | RES                         |

| Input Leakage Current             | -            | 0.05        | 2.0         | $\mu\text{A}$ |                                                 |                             |

| Output Leakage Current            | -            | 0.10        | 5.0         | $\mu\text{A}$ |                                                 |                             |

| Average Dynamic Power Consumption | -            | 8.0         | 12          | mA            |                                                 |                             |

| Average Static Power Consumption  | -            | 0.05        | 20          | $\mu\text{A}$ |                                                 |                             |

**COPROCESSOR INTERFACE TIMING**C to 50°C  $V_{DD} = 5.0V \pm 10\%$

| Symbol                                | Parameter | Min.                | Max. | Units |

|---------------------------------------|-----------|---------------------|------|-------|

| <b>RD SERIES TIMING</b>               |           |                     |      |       |

| RD                                    | $t_{Cyc}$ | System Cycle Time   | 1000 | ns    |

|                                       | $t_{cc}$  | Control Pulse Width | 220  | ns    |

| <b>CS RW SERIES TIMING</b>            |           |                     |      |       |

| CS RW                                 | $t_{Cyc}$ | System Cycle Time   | 1000 | ns    |

|                                       | $t_{EW}$  | Enable Pulse Width  | 220  | ns    |

| <b>FOR 80 MD 68 SERIES PROCESSORS</b> |           |                     |      |       |

| CS                                    | $t_{AH}$  | Address Hold Time   | 10   | ns    |

|                                       | $t_{AW}$  | Address Setup Time  | 30   | ns    |

|                                       | $t_{DS}$  | Data Setup Time     | 120  | ns    |

|                                       | $t_{DH}$  | Data Hold Time      | 10   | ns    |

|                                       | $t_{ACC}$ | RD Access Time      | 120  | ns    |

|                                       | $t_{OH}$  | Output Disable Time | 10   | ns    |

|                                       |           |                     | 50   | ns    |

**SERIES TIMING DIAGRAM****INSTRUCTION SET SUMMARY**

|                   |          |     |

|-------------------|----------|-----|

| System Set        | 01000000 | 40h |

| Display On        | 01011001 | 59h |

| Display Off       | 01011000 | 58h |

| Overlay           | 01011011 | 5Bh |

| CG RAM Address    | 01011100 | 5Ch |

| Scroll            | 01000100 | 44h |

| Horiz. Dot Scroll | 01011010 | 5Ah |

| Cursor Format     | 01011101 | 5Dh |

| Cursor Right      | 01001100 | 4Ch |

| Cursor Left       | 01001101 | 4Dh |

| Cursor Up         | 01001110 | 4Eh |

| Cursor Down       | 01001111 | 4Fh |

| Cursor Write      | 01000110 | 46h |

| Cursor Read       | 01000111 | 47h |

| Memory Write      | 01000010 | 42h |

| Memory Read       | 01000011 | 43h |

| Erase             | 01010010 | 52h |

| Sleep             | 01010011 | 53h |

**68 (SERIES TIMING DIAGRAM)****CONTROL COMMAND DESCRIPTION****SYSTEM SET (C:40H)**

| Symbol | D7                                                                                                                                                                                                         | D6 | D5 | D4 | D3  | D2  | D1  | D0  | Description                                                                                                                                                                                                                                                                                         |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|-----|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1     | 0                                                                                                                                                                                                          | 0  | IV | 1  | 0   | M2  | M1  | M0  | Mode of Operation<br>M0: 0: Internal CG ROM<br>1: External CG ROM or CG RAM<br>M1: 0: 32 RAM based characters<br>1: 64 RAM based characters<br>M2: 0: Character font = 8 rows/character<br>1: Character font = 16 rows/character<br>IV: 0: First layer offset 1 row<br>1: No offset (normally used) |

| P2     | WF                                                                                                                                                                                                         | 0  | 0  | 0  | 0   | FX2 | FX1 | FX0 | Width of a character field<br>WF: 0: Line reverse AC drive<br>1: Frame reverse AC drive (normally used)<br>FXn: 0/1: Define the width of the font (normally 111 is used for 8 pixels wide)                                                                                                          |

| P3     | 0                                                                                                                                                                                                          | 0  | 0  | 0  | FY3 | FY2 | FY1 | FY0 | Height of a character field<br>FYn: 0/1: Define the height of the font (normally 0111 is used for 8 pixels high)                                                                                                                                                                                    |

| P4     | C/R<br>C/R: Total pixels in width divided by FX                                                                                                                                                            |    |    |    |     |     |     |     | Characters per row                                                                                                                                                                                                                                                                                  |

| P5     | T C/R<br>TC/R x UF x FR x 9 = Fosc<br>UF: Lines per frame (vertical pixels/screen)<br>FR: Frame frequency (from 60Hz to 80Hz)<br>Fosc: 10 MHz (107) for LCD-1330<br>6MHz (6 x 106) for built-in controller |    |    |    |     |     |     |     | Timing per character row (Adjust frame frequency)                                                                                                                                                                                                                                                   |

| P6     | L/F<br>L/F: Vertical pixels per screen                                                                                                                                                                     |    |    |    |     |     |     |     | Lines per graphics screen                                                                                                                                                                                                                                                                           |

| P7     | APL<br>APL: Normally CR or C/R+1 is used                                                                                                                                                                   |    |    |    |     |     |     |     | Virtual screen low byte                                                                                                                                                                                                                                                                             |

| P8     | APH<br>APH: Normally 00h is used                                                                                                                                                                           |    |    |    |     |     |     |     | Virtual screen high byte                                                                                                                                                                                                                                                                            |

# LCDC-1330 CONTROLLER BOARD (CONTINUED)

## PIN ASSIGNMENT

### CN1: CONNECTION FOR MICROPROCESSOR INTERFACE

| PIN# | SIGNAL         | PIN# | SIGNAL                |

|------|----------------|------|-----------------------|

| 1    | *RESET         | 9    | D <sub>3</sub>        |

| 2    | *RD (E)        | 10   | D <sub>4</sub>        |

| 3    | *WR (R/*W)     | 11   | D <sub>5</sub>        |

| 4    | *CS            | 12   | D <sub>6</sub>        |

| 5    | A0             | 13   | D <sub>7</sub>        |

| 6    | D <sub>0</sub> | 14   | V <sub>DD</sub> (+5V) |

| 7    | D <sub>1</sub> | 15   | V <sub>SS</sub> (GND) |

| 8    | D <sub>2</sub> | 16   | V <sub>LCD</sub>      |

\*Active low on the control signal

### MOTOROLA 6800 SERIES

| A0 | *RD | R/W | FUNCTION               |

|----|-----|-----|------------------------|

| 0  | 0   | 1   | Status Register Read   |

| 1  | 0   | 1   | Read Data              |

| 0  | 1   | 0   | Write Data             |

| 1  | 1   | 0   | Command Register Write |

\*Active low on the control signal

Except for the Erase command, the LCDC-1330 does not require the CPU to check the ready status between passing commands or parameters. When issuing the Erase command, the CPU must wait for at least two frame times before writing a new command to the LCDC-1330.

### CN2: CONNECTION FOR LCD INTERFACE

| PIN# | SIGNAL          | PIN# | SIGNAL                |

|------|-----------------|------|-----------------------|

| 1    | DB <sub>3</sub> | 7    | CL1 (LP)              |

| 2    | DB <sub>2</sub> | 8    | CL2 (XSCL)            |

| 3    | DB <sub>1</sub> | 9    | V <sub>DD</sub> (+5V) |

| 4    | DB <sub>0</sub> | 10   | V <sub>SS</sub> (GND) |

| 5    | FLM (YD)        | 11   | V <sub>0</sub>        |

| 6    | M (WF)          | 12   | V <sub>LCD</sub>      |

The microprocessor may access the command/status register or read/write data by changing the value of \*RD, \*WR, and A0.

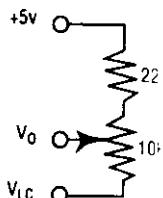

### CN3: CONTRAST ADJUSTMENT

| PIN# | SIGNAL                |

|------|-----------------------|

| 1    | V <sub>DD</sub> (+5V) |

| 2    | V <sub>0</sub>        |

| 3    | V <sub>LCD</sub>      |

### J1: JUMPER SETTINGS FOR CPU

1-2: Select Intel 8085 or Z80 microprocessor

2-3: Select Motorola 6800 microprocessor

## LCDC-1330 CHARACTERISTICS

### ABSOLUTE MAXIMUM RATINGS

| ITEM                                 | SPECIFICATION                  |

|--------------------------------------|--------------------------------|

| Supply Voltage (V <sub>DD</sub> )    | -0.3V to +7.0V                 |

| Voltage on Any Pin Width             |                                |

| Respect to Ground (V <sub>SS</sub> ) | -0.5V to V <sub>DD</sub> + 0.5 |

| Operating Temperature                | 0°C to 50°C                    |

| Storage Temperature                  | -20°C to 60°C                  |

| Power Consumption                    | 60mW                           |

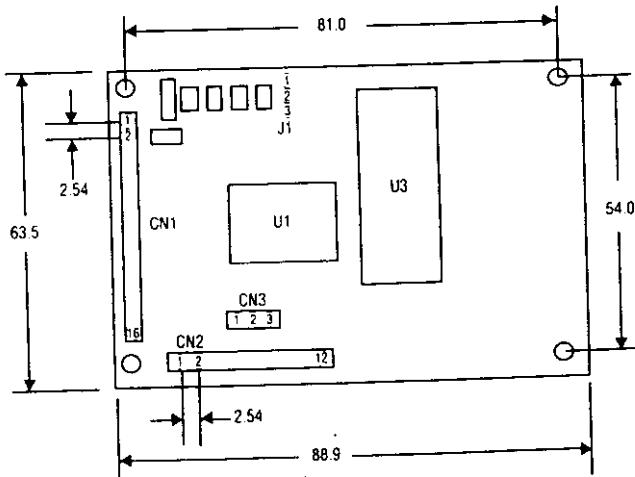

## DIMENSIONS OF LCDC-1330 (MM)

## CONTROL SIGNAL STATUS

### INTEL 8080 SERIES

| A0 | *RD | *WR | FUNCTION               |

|----|-----|-----|------------------------|

| 0  | 0   | 1   | Status Register Read   |

| 1  | 0   | 1   | Read Data              |

| 0  | 1   | 0   | Write Data             |

| 1  | 1   | 0   | Command Register Write |

\*Active low on the control signal

**MORY WRITE (42h)**

This command sets the controller into the write mode. The data that is passed to the parameter will be written to the memory location specified by the current cursor address. After the Memory Write command, the controller automatically advances the cursor to the next sequential location defined by the cursor direction. This allows the users to write many bytes of data to the screen without issuing another write command.

Continuous data writing

**MORY READ (43h)**

This command sets the controller into the read mode. The data that is read from the parameter will be from the memory location specified by the current cursor address. After the Memory Read command, the controller automatically advances the cursor to the next sequential location defined by the cursor direction. This allows the users to

read many bytes of data to the screen without issuing another read command.

P1

P2

-

Pn

} Continuous data reading

**ERASE (C:52h)**

This command clears the screens that are enabled from the current cursor position to the end of the screens. After Erase command is issued, two frame time (min.) delay is needed before issuing the next command. (e.g., 34 ms is needed for 60 Hz frame frequency).

**SLEEP (C:53h)**

This command turns off the display, stops all internal operations, stops the oscillator, and enters the sleep mode. The controller may be brought out of the sleep mode by issuing the System Set command. The contents in the memory remain unchanged.

**ALIZATION SETTING FOR SEIKO INSTRUMENTS LCD MODULES**

| Command          | Symbol | G121C                 | G191C | G191D | G242C | G2436<br>G2446 | G321D | G321E<br>G324E | G648D<br>G649D | Note           |

|------------------|--------|-----------------------|-------|-------|-------|----------------|-------|----------------|----------------|----------------|

| Memory Set       | C      | 40h                   | 40h   | 40h   | 40h   | 40h            | 40h   | 40h            | 40h            |                |

|                  | P1     | 30h                   | 30h   | 30h   | 30h   | 30h            | 30h   | 30h            | 30h            | P5 is based on |

|                  | P2     | 87h                   | 85h   | 85h   | 85h   | 87h            | 87h   | 87h            | 87h            | 70 Hz          |

|                  | P3     | 07h                   | 07h   | 07h   | 07h   | 07h            | 07h   | 07h            | 07h            | frame          |

|                  | P4     | 0Fh                   | 1Fh   | 1Fh   | 27h   | 27h            | 27h   | 27h            | 4Fh            | rate with      |

|                  | P5     | 7Ch                   | 7Ch   | 53h   | 7Ch   | F8h            | 4Fh   | 42h            | 4Fh            | Fosc. =        |

|                  | P6     | 7Fh                   | 7Fh   | BFh   | 7Fh   | 3Fh            | C7h   | EFh            | C7h            | 10 MHz.        |

|                  | P7     | 0Fh                   | 1Fh   | 1Fh   | 27h   | 27h            | 27h   | 27h            | 4Fh            |                |

| Display On       | C      | 59h                   | 59h   | 59h   | 59h   | 59h            | 59h   | 59h            | 59h            |                |

|                  | P1     | 05h                   | 05h   | 05h   | 05h   | 05h            | 05h   | 05h            | 05h            |                |

| Overlay          | C      | 58h                   | 58h   | 58h   | 58h   | 58h            | 58h   | 58h            | 58h            |                |

|                  | P1     | 00h                   | 00h   | 00h   | 00h   | 00h            | 00h   | 00h            | 00h            |                |

| Scroll           | C      | 44h                   | 44h   | 44h   | 44h   | 44h            | 44h   | 44h            | 44h            |                |

|                  | P1     | 00h                   | 00h   | 00h   | 00h   | 00h            | 00h   | 00h            | 00h            |                |

|                  | P2     | 00h                   | 00h   | 00h   | 00h   | 00h            | 00h   | 00h            | 00h            |                |

|                  | P3     | 7Fh                   | 7Fh   | BFh   | 7Fh   | 3Fh            | C7h   | EFh            | C7h            |                |

|                  | P4     | 00h                   | 00h   | 00h   | 00h   | 00h            | 00h   | 00h            | 00h            |                |

|                  | P5     | 04h                   | 04h   | 06h   | 06h   | 04h            | 08h   | 10h            | 10h            |                |

|                  | P6     | 7Fh                   | 7Fh   | BFh   | 7Fh   | 3Fh            | C7h   | EFh            | C7h            |                |

| Cursor Format    | C      | 5Dh                   | 5Dh   | 5Dh   | 5Dh   | 5Dh            | 5Dh   | 5Dh            | 5Dh            |                |

|                  | P1     | 07h                   | 05h   | 05h   | 05h   | 05h            | 07h   | 07h            | 07h            |                |

|                  | P2     | 87h                   | 87h   | 87h   | 87h   | 87h            | 87h   | 87h            | 87h            |                |

| Cursor Write     | C      | 46h                   | 46h   | 46h   | 46h   | 46h            | 46h   | 46h            | 46h            |                |

|                  | P1     | 00h                   | 00h   | 00h   | 00h   | 00h            | 00h   | 00h            | 00h            |                |

| Cursor Direction | P2     | 00h                   | 00h   | 00h   | 00h   | 00h            | 00h   | 00h            | 00h            |                |

|                  | C      | 4Ch                   | 4Ch   | 4Ch   | 4Ch   | 4Ch            | 4Ch   | 4Ch            | 4Ch            |                |

| Memory Write     | C      | 42h                   | 42h   | 42h   | 42h   | 42h            | 42h   | 42h            | 42h            |                |

|                  | P1     | ASCII Code: 20h - 7Fh |       |       |       |                |       |                |                |                |

| Pn               | Pn     | ASCII Code: 20h - 7Fh |       |       |       |                |       |                |                |                |

# LCDC-1330 CONTROLLER BOARD (CONTINUED)

## DISPLAY ON (C:59h)

| Symbol | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Note                     |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|--------------------------|

| P1     | FP5 | FP4 | FP3 | FP2 | FP1 | FPO | FC1 | FC0 |                          |

|        | FC1 | FC0 |     |     |     |     |     |     | Cursor Control           |

|        | 0   | 0   |     |     |     |     |     |     | Cursor off               |

|        | 0   | 1   |     |     |     |     |     |     | Cursor on, no blink      |

|        | 1   | 1   |     |     |     |     |     |     | On with 2 Hz blink rate  |

|        | 1   | 1   |     |     |     |     |     |     | On with 1 Hz blink rate  |

|        | FP1 | FPO |     |     |     |     |     |     | SAD1 (L1)                |

|        | FP3 | FP2 |     |     |     |     |     |     | SAD2 (L2)                |

|        | FP5 | FP4 |     |     |     |     |     |     | SAD3 (L3)                |

|        | 0   | 0   |     |     |     |     |     |     | Layer1                   |

|        | 0   | 1   |     |     |     |     |     |     | Layer 2                  |

|        | 1   | 0   |     |     |     |     |     |     | Layer 3                  |

|        | 1   | 1   |     |     |     |     |     |     |                          |

|        | 0   | 0   |     |     |     |     |     |     | Layer off                |

|        | 0   | 1   |     |     |     |     |     |     | Layer on, no blink       |

|        | 1   | 0   |     |     |     |     |     |     | On with 2 Hz blink rate  |