## Technical Description:

The equipment under test (EUTs) is a Bobbie the Receiver Doll for an interactive hand puppet doll which is operating at 2410 ~ 2470MHz with 1 MHz channel spacing. The EUT is powered by three AAA batteries. After powered ON the EUT and paired up the Master unit (i.e. BoBo the Hand Puppet), the user can listen the voice from the corresponding Master unit by speaker and it can record the voice automatically. The voice can be play-back while the play button is pressed.

Frequency range: 2410 – 2470MHz

Channel spacing: 1MHz Type of modulation: FSK

The functions of main ICs are mentioned as below.

1) U1 acts as Microcontroller.

2) U2 acts as Flash Memory.

For 2.4GHz module;

1) U1 acts as 2.4GHz RF transceiver.

# RF24DT-50DS 2.4GHz Digital RF Module Application Note

Elan Microelectronics Corp.

#### Office:

NO. 12, Innovation 1st. RD., Science-Based Industrial Park, Hsinchu City, Taiwan, R.O.C.

TEL: (03) 563-9977 FAX: (03) 563-0118 http://www.emc.com.tw

## Contents

| 1.Description                                         |   |

|-------------------------------------------------------|---|

| 2.Feature                                             |   |

| 3.Block Diagram                                       |   |

| 4.Pins assignment                                     |   |

| 5.Function Description                                |   |

| 6.Application circuit                                 |   |

| 7.Demo kit                                            |   |

| 8. PCB                                                |   |

| 9.Technical                                           |   |

| 10.BOM                                                |   |

| 11. Description of Operation Mode                     | ) |

| 12. State Machine of Operation Mode                   | 2 |

| 13. System Flowchart                                  | 3 |

| 14. Star Network                                      | ) |

| 15. Frame Structure                                   | 2 |

| 16.Operation Timing Diagram                           | 3 |

| 17.SPI Interface Timing Diagram                       | ) |

| 18.SPI Programmable Function Description              | 2 |

| 19. Serial Register Format of Power ON Initialization | 5 |

| 20.Appendix:                                          | 3 |

| 21.History:                                           | ) |

#### 1. Description

The EM198850H/AW is a CMOS integrated circuit that performs all functions from the antenna to the microcontroller for transmission and reception of a 2.4GHz digital data. This transceiver IC integrates most of the functions required for data transmission into a single integrated circuit. Additionally, the programmability implemented reduces significantly external components count, board space requirements and external adjustments.

#### 2. Feature

- Single-chip FSK transceiver

- Auto ACK & Retransmit

- Star-Network with 6 channels

- Address and CRC computation

- 1/1.6Mbps Data Rate

- 1 ~ 64 bytes Payload Length

- 64 bytes FIFO Size

- 4-wire digital interface (SPI)

- Boost data mode

- Power supply range: 1.8 to 3.6V

- Automatic bypass internal LDO in low supply voltage

- Battery Low Supply Voltage Detector

- Support 4 power modes: Active/Standby/Idle/Power Down

- Operation range: -40 °C to +85 °C

- Standard CMOS process

- On-chip VCO, PLL and PLL Loop Filter

- On chip channel filter

#### **Applications**

- Wireless mouse, keyboard, joystick

- Keyless entry

- Alarm and security system

- Home automation

- Surveillance

- Automotive

- Telemetry

- Industrial sensors

- Wireless data communication

- Toys

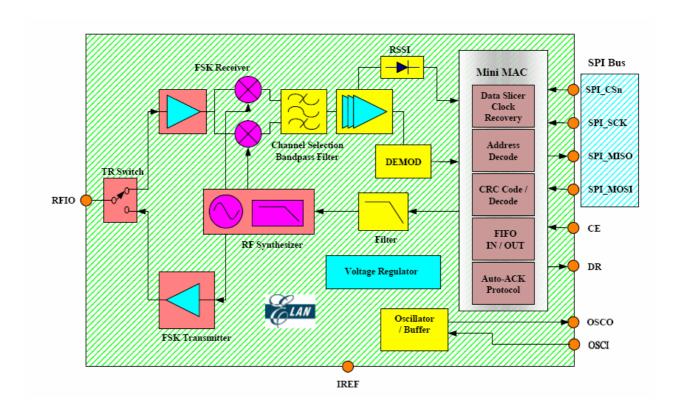

## 3. Block Diagram

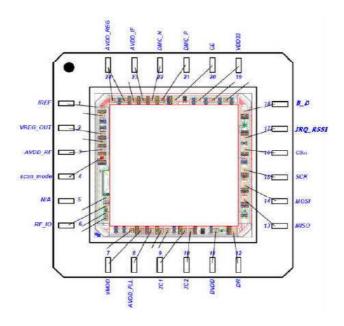

## 4. Pins assignment

# RF24DT-50DS 2.4GHz Digital RF Module Application Note

| Pin     | Symbol      | Туре         | Descriptions                                                   |

|---------|-------------|--------------|----------------------------------------------------------------|

| 19, 24. | DVDD3/AVDD3 | PWR          | Power supply voltage.                                          |

| Exposed | GND         | GND          | Ground connection.                                             |

| Pad     |             |              |                                                                |

| 1       | IREF        | Analog Input | Reference resistor pin, connect to an external resistor        |

| 2       | VREG_OUT    | PWR          | On-chip voltage regulator output                               |

| 3       | AVDD_RF     | PWR          | RF power supply                                                |

| 4, 5.   |             | GND          | Ground connection.                                             |

| 6       | RFIO        | RF 50Ω       | RF input/output                                                |

| 7       | VMOD        | Analog I/O   | Connect to external capacitor for filtering                    |

| 8       | AVDD_PLL    | PWR          | PLL power supply                                               |

| 9       | OSCI        | Analog I/O   | Crystal pin1                                                   |

| 10      | OSCO        | Analog I/O   | Crystal pin2                                                   |

| 11      | DVDD        | PWR          | Digital power supply                                           |

| 12      | DR_IRQ      | Digital I/O  | a. Interrupt signal in buffer mode                             |

|         |             |              | b. Data input/data output in direct mode                       |

| 13      | SPI_MISO    | Digital I/O  | a. Master input/slave output in SPI mode                       |

|         |             |              | b. Data output in buffer mode                                  |

| 14      | SPI_MOSI    | Digital I/O  | a. Master output/slave input in SPI mode                       |

|         | 001.0114    | 51.1/.1.1/6  | b. Data input in buffer mode                                   |

| 15      | SPI_CLK     | Digital I/O  | SPI input clock                                                |

| 16      | CSn         | Digital I/O  | SPI selection/programming enable                               |

| 17      | IRQ_RSSI    | Digital I/O  | IRQ_RSSI output high                                           |

|         |             |              | - to indicate the MCU to read the RSSI, RSSI only valid        |

|         |             |              | during receiving signal - Let MCU know the channel is occupied |

| 18      | B_D         | Digital I/O  | Battery Low Power Detector                                     |

| 20      | CE          | Digital I/O  | Chip enable, enable voltage regulator                          |

|         |             |              | S Demodulator analog output, connect to an external AC         |

| 21      | DMC_P       | Analog I/O   | coupling capacitor                                             |

| 22      | DMC_N       | Analog I/O   | Demodulator analog output, connect to an external AC           |

|         |             | ,            | coupling capacitor                                             |

| 23      | ADD_IF      | PWR          | RX IF power supply, voltage regulator output                   |

## 5. Function Description

The Elan EM198850AW IC is a low-cost, fully integrated CMOS radio frequency (RF) transceiver, combined with dual 64-byte buffered framer block. The RF transceiver is a self-contained, fast-hopping FSK data modem, data rate can be operated up to 1.6Mbps in buffer mode or 2Mbps in direct mode, optimised for use in the widely available 2.4 GHz ISM band. It consists of a fully integrated frequency synthesizer, a power amplifier, a crystal oscillator, a demodulator, modulator, and Auto-ACK protocol engine. A reduced off chip filter is realized by the low IF RX architecture, minimizing the need for external components.

The transceiver utilizes extensive digital processing for excellent overall performance, even in the presence of interference and transmitter impairments. Typical transmit power is 0dBm and digitally controlled, low-IF receiver architecture results in sensitivity to -92dBm or better, with impressive selectivity. User can program transmitter output power, frequency channels, and protocol setup easily through a SPI interface.

In normal application, the on-chip framer processes and stores the RF data in the background, unloading this critical timing function from the MCU. This lowers MCU speed requirements, expedites product development time, and frees the MCU for implementing additional product features.

Many configurations are possible, depending on the user's specific needs. Transmit data is easily sent over-the-air as a complete frame of data, with syncword, SOF, address, payload, and CRC.

Receiving data is just the opposite, using the syncword to train the receiver clock recovery, then the address is checked, then the data is reverse formatted for receive, followed by CRC. All of this is done in hardware to ease the programming and overhead requirements of the baseband MCU.

For longer battery life, power consumption is minimized by automatic enabling of the various transmit, receive, PLL, and PA sections, depending on the instantaneous state of the chip. An idle mode is also provided for ultra low current consumption.

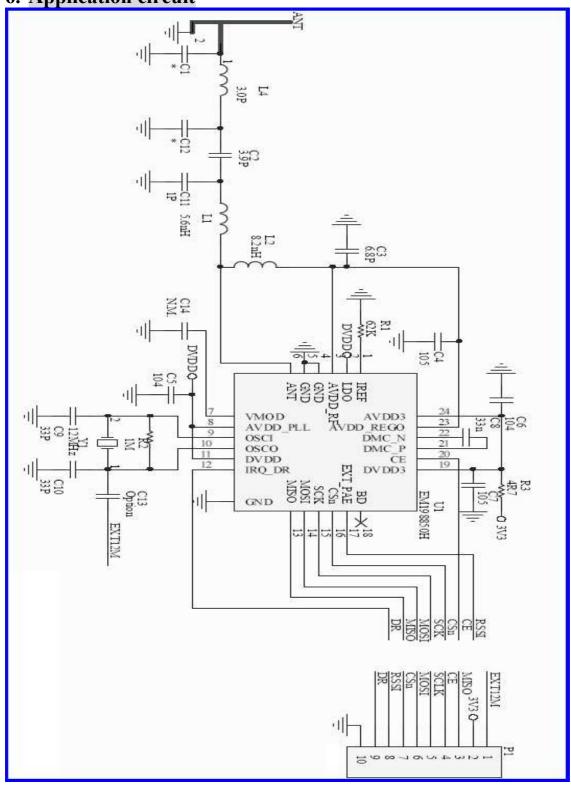

6. Application circuit

<sup>\*</sup> This specification are subject to be changed without notice.

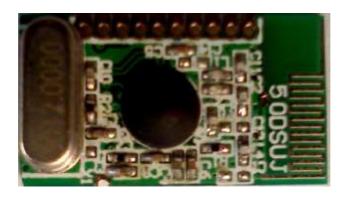

## 7. Demo kit

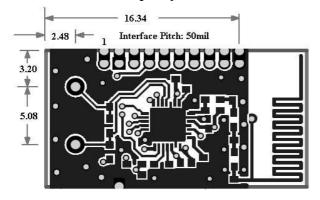

## **8. PCB**

#### **Top Layer**

#### **Bottom Layer**

## Module-P1 interface pins name:

|     |          | •                                                       |

|-----|----------|---------------------------------------------------------|

| Pin | Name     | Description                                             |

| 1   | EXT12M   | Not used.                                               |

| 2   | VDD      | Power supply voltage +3.3V.                             |

| 3   | SPI_MISO | a. Master input/slave output in SPI mode                |

|     |          | b. Data output in buffer mode                           |

| 4   | CE       | Chip enable, enable voltage regulator                   |

| 5   | SPI_CLK  | SPI input clock.                                        |

| 6   | SPI_MOSI | a. Master output/slave input in SPI mode.               |

|     |          | b. Data input in buffer mode.                           |

| 7   | CSn      | SPI selection/programming enable.                       |

| 8   | RSSI     | IRQ_RSSI output high                                    |

|     |          | - to indicate the MCU to read the RSSI, RSSI only valid |

|     |          | during receiving signal.                                |

|     |          | - Let MCU know the channel is occupied.                 |

| 9   | DR_IRQ   | a. Interrupt signal in buffer mode.                     |

|     |          | b. Data input/data output in direct mode.               |

| 10. | GND      | Ground connection.                                      |

<sup>\*</sup> This specification are subject to be changed without notice

## 9. Technical

RFIC/Module DC/AC Bias: DC Voltage input +3.0V Operating mode

| IC<br>Pins | Module<br>Pins | Descriptions                                                                                                                               | AC<br>Characteristic<br>Reference | DC<br>bias |

|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------|

| 1          | X              | Reference resistor pin, connect to an external resistor                                                                                    |                                   | +0.6V      |

| 3, 23.     | X              | Analog Power supply voltage.                                                                                                               |                                   | +1.8V      |

| 2, 8, 11.  | X              | Digital Power supply voltage.                                                                                                              |                                   | +1.8V      |

| 4, 5, E.   | 10             | Ground.                                                                                                                                    |                                   | 0V         |

| 6          | X              | Antenna, RF signal input/output.                                                                                                           | 2.4GHz                            | +1.8V      |

| 7          | X              | NC                                                                                                                                         |                                   |            |

| 9          | X              | Input to the crystal oscillator gain block.                                                                                                | 12MHz 1.0Vpp                      |            |

| 10         | X              | Output of the crystal oscillator gain block.                                                                                               | 12MHz 1.0Vpp                      |            |

| 12         | 9*             | <ul><li>a. Interrupt signal in buffer mode.</li><li>b. Data input/data output in direct mode.</li></ul>                                    | DR_IRQ                            |            |

| 17         | 8*             | IRQ_RSSI output high - to indicate the MCU to read the RSSI, RSSI only valid during receiving signal Let MCU know the channel is occupied. | IRQ_RSSI                          |            |

| 16         | 7              | SPI selection/programming enable.                                                                                                          | SPI enable                        |            |

| 14         | 6*             | <ul><li>a. Master output/slave input in SPI mode.</li><li>b. Data input in buffer mode.</li></ul>                                          | SPI data input                    |            |

| 15         | 5              | SPI input clock.                                                                                                                           | SPI clock                         |            |

| 20         | 4              | Chip enable, enable voltage regulator                                                                                                      | Digital I/O                       |            |

| 13         | 3*             | <ul><li>a. Master input/slave output in SPI mode</li><li>b. Data output in buffer mode</li></ul>                                           | SPI data output                   |            |

| 21         | X              | S Demodulator analog output, connect to an external AC coupling capacitor                                                                  | RX IF                             |            |

| 22         | X              | Demodulator analog output, connect to an external AC coupling capacitor                                                                    | RX IF                             |            |

| 19, 24     | 2              | AVDD & DVDD for the analog & digital I/O pins. Nominally +3.0 VDC, Unregulated input to the on-chip LDO voltage regulator.                 |                                   | +3.0V      |

<sup>\*:</sup> according to firmware setting.

## **10. BOM**

## EM198850 2.4GHz RF Transceiver Module BOM

| Comment     | Description                  | Designator | Quantity |

|-------------|------------------------------|------------|----------|

| 1.0P/10V    | 1005 NPO Ceramic Capacitor   | C11.       | 1        |

| 3.0P/10V    | 1005 NPO Ceramic Capacitor   | L4.        | 1        |

| 3.9P/10V    | 1005 NPO Ceramic Capacitor   | C2.        | 1        |

| 6.8P/10V    | 1005 NPO Ceramic Capacitor   | C3.        | 1        |

| 33P/10V     | 1005 NPO Ceramic Capacitor   | C9, C10*.  | 2        |

| 33n/10V     | 1005 X7R Ceramic Capacitor   | C8.        | 1        |

| 100n/10V    | 1005 X7R Ceramic Capacitor   | C5, C6.    | 2        |

| 1u/6.3V     | 1005 X7R Ceramic Capacitor   | C4, C7.    | 2        |

| 5.6nH       | HI1005 Ceramic Chip Inductor | L1.        | 1        |

| 8.2nH       | HI1005 Ceramic Chip Inductor | L2.        | 1        |

| 4R7         | 1005 Carbon Film Resistor    | R3.        | 1        |

| 62K         | 1005 Carbon Film Resistor    | R1.        | 1        |

| 1M          | 1005 Carbon Film Resistor    | R2.        | 1        |

| EM198850H   | RFIC                         | U1         | 1        |

| 12MHz       | HC-49US±20ppm/CL20P          | Y1         | 1        |

| PCB         | 12X22mmX0.8mm FR-4           | PCB        | 1        |

| 2.4GHz PIFA | PIFA Antenna                 | ANT        |          |

| Total       |                              |            | 19       |

<sup>\*:</sup>depend on Y1 load capacitance.

| 11. Desc      | 11. Description of Operation Mode |       |     |     |     |     |           |    |     |                |         |                |

|---------------|-----------------------------------|-------|-----|-----|-----|-----|-----------|----|-----|----------------|---------|----------------|

| Operation     | 0x40                              | 0x41  |     | 0x  | :00 |     | 0x01      | CE | CSn | MOSI           | MISO    | IRQ            |

| Mode          | [1:0]                             | [7:0] | [7] | [6] | [5] | [0] | [3:1] Pin |    | Pin | Pin            | Pin     | Pin            |

| Power Down    | X                                 | X     | X   | X   | X   | 1   | X         | 0  | X   | SPIin          | SPIout  |                |

| Idle          | X                                 | X     | 0*a | 1   | 0   | 0   | 101       | 0  | X   | SPIin          | SPIout  |                |

| Configuration | X                                 | X     | 1   | 1   | X   | 1   | 010       | 1  | 0   | SPIin          | SPIout  |                |

| Standby I     | 00                                | X     | 0   | 1   | 1   | 1   | 110       | 1  | 1   | <b>FIFO</b> in | SPIout  | <b>IRQ</b> out |

| TX Buffered   | 10                                | 0x80  | 1   | 1   | 1   | 1   | 010       | 1  | 1   | <b>FIFO</b> in | SPIout  | <b>IRQ</b> out |

| Standby II    | 10                                | 0x80  | 1   | 1   | 1   | 1   | 010       | 1  | 1   | <b>FIFO</b> in | SPIout  | <b>IRQ</b> out |

| TX Direct     | 10                                | 0x80  | 1   | 0   | 0   | 1   | 010       | 1  | 1   | SPIin          | SPIout  | Datain         |

| RX Buffered   | 01                                | 0x81  | 1   | 1   | 1   | 1   | 010       | 1  | 1   | SPIin          | FIFOout | <b>IRQ</b> out |

| RX Direct     | 01                                | 0x81  | 1   | 0   | 0   | 1   | 010       | 1  | 1   | SPIin          | SPIout  | Dataout        |

**Table 3: Operation Mode**

For detail register setting, refer to the state machine of operation modes. Please follow the register sequence order showed from up to down when you write the register setting. The symbol "x" means that don't write the registers when you change the operation mode.

#### Configuration

When CSn=0 and CE = 1, the SPI interface may be activated to program the SPI register value. For the detail timing diagram, you can refer to the Figure  $16 \sim$  Figure 18.

#### **Power Down Mode**

When the pin CE sets to 0 and 0x00[0] sets to 1, the EM198850AW is disabled with the minimal current consumption. When entering the power down mode, EM198850AW is not active including voltage regulators and crystal block, and the values of all registers are clear.

#### **Idle**

Idle mode is used to minimize average current consumption while maintaining short start up times. In this mode, the contents of all registers are maintained by internal power supply voltage. It will reduce the register initialization time on the next start up time from idle mode into buffer mode. EM198850AW is not active including voltage regulators and crystal block.

#### Standby I

For RX or TX device, all the RF blocks and mini Mac baseband system clock will be turned off to save average current consumption. In this mode, only voltage regulators, crystal oscillator and clock buffers are active to speed up the start-up time. The configuration word content is maintained during standby I mode.

#### TX Buffered Mode (BUF)

As a transmitter with the function of FIFO and packet handling

#### Standby II

When TX FIFO is empty in TX buffer mode, the TX device would stay in the standby II mode. In

<sup>\*</sup>a: When using external Xtal with internal oscillator, (i.e. R00[2]=1), MCU write 0. When using external clock from MCU, (i.e. R00[2]=0), register R00[7] don't care.

this mode, the regulators, crystal oscillator, clock buffers and mini Mac baseband system clock are activated. No any start-up time is need.

#### TX Direct Mode (DR)

As a transmitter without the function of the FIFO and packet handling

#### **RX Buffered Mode (BUF)**

As a receiver with the function of FIFO and packet handling

#### RX Direct Mode (DR)

As a receiver without the function of the FIFO and packet handling

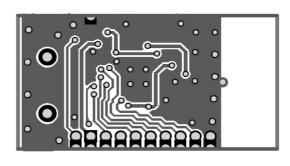

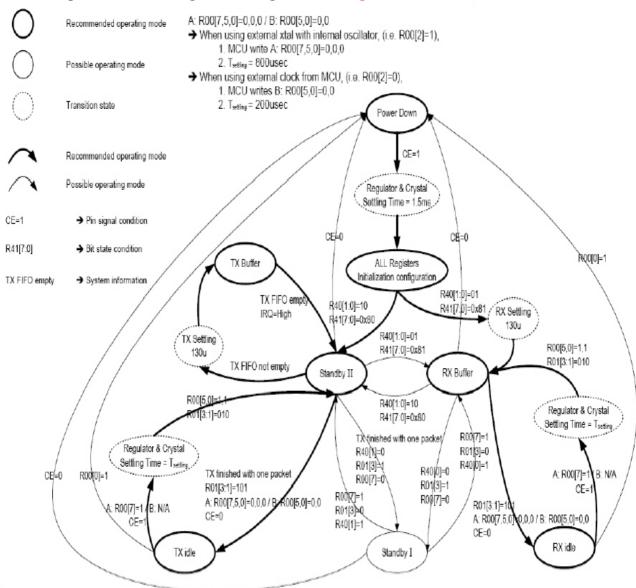

## 12. State Machine of Operation Mode

The Figure is the state machine of operation modes. The MCU can follow the register sequence to write SPI registers into the desired operation mode through digital SPI interface.

Figure 2: State machine diagram

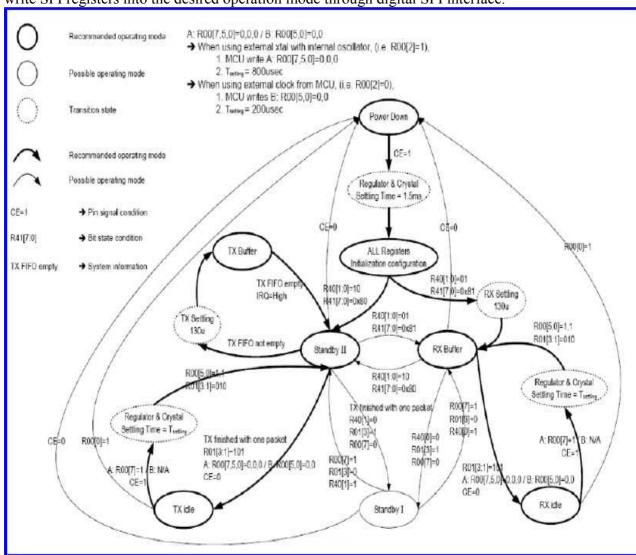

## 13. System Flowchart

#### Tx operation

Figure 3: Operation flowchart of Tx

If there is a packet present in Tx FIFO, the EM198850AW enters Tx Buffer mode and transmits the packet. If Auto ACK is enabled, the EM198850AW enters Rx mode to receive an ACK packet. If the ACK packet is not received before timeout occurs, the EM198850AW returns to Tx standby II mode. It stay in Tx standby II mode until the Backoff Time(0x58[7:0]) has elapsed. If number of retransmits has not reached the ETRYCNT(0x47[7:4]), the EM198850AW start to transmit the last packet once more. When number of retransmits reach the maximum number, the EM198850AW assert DR(IRQ) and automatically add one to packet loss count(0x4F[7:3]) . EM198850AW return to standby II mode wait for next new packet input.

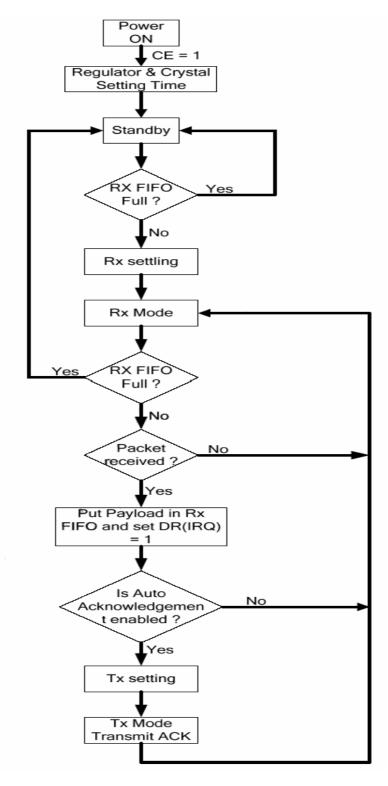

#### Rx operation

Figure 4: Operation flowchart of Rx

If a packet is received from transmitter, the EM198850AW assert DR(IRQ) and put receive packet in Rx FIFO. If Auto ACK is enabled, the EM198850AW enters Tx mode to transmit an ACK packet. After ACK packet is transmitted, the EM198850AW return to Rx mode. When the FIFO is full, number of payload equal to PKTCNT, all the RF circuits will turn off automatically to save power consumption. RF circuits will turn on when the FIFO is not full.

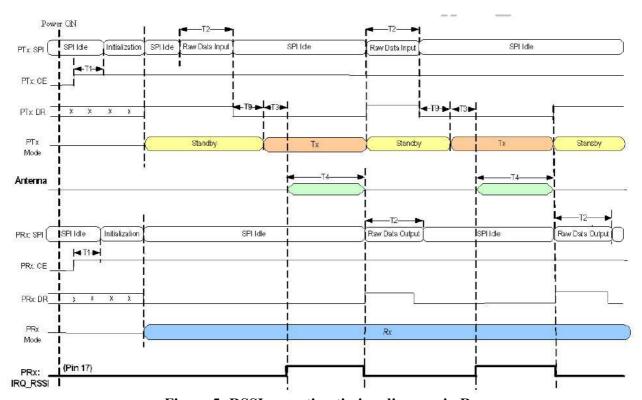

#### RSSI operation in Rx

Figure 5: RSSI operation timing diagram in Rx

In Rx device, pin 17, sets as IRQ\_RSSI, is high to indicate that it is available for the MCU to read the RSSI registers, R0x4B[5:0] through the SPI interface. RSSI values are only valid during receiving signal.

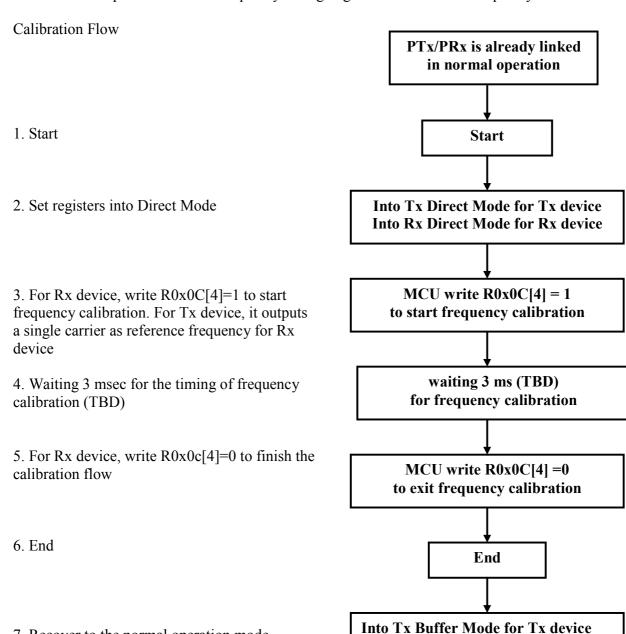

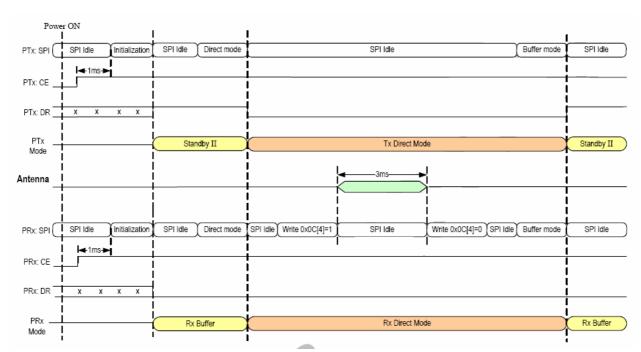

#### Xtal Frequency Offset Calibration

If the EM198850AW uses the external Xtal with internal oscillator to create the system clock, the EM198850AW provide the auto frequency tuning engine to fine the Xtal frequency.

7. Recover to the normal operation mode

Into Rx Buffer Mode for Rx device

<sup>\*</sup> This specification are subject to be changed without notice.

#### **Xtal Frequency Offset Calibration Timing Diagram**

Figure 6: Xtal Frequency Offset Calibration Timing Diagram

Note: When the devices go into POWER DOWN mode, all the calibration result will be refreshed

#### EM198850AW sharing crystal with a MCU

When using a MCU to drive the crystal reference pin OSCO of the EM198850AW transceiver, some rules must be followed. First, the register R0x00[2] is set to Low. When MCU drives the EM198850AW clock input pin, OSCO, the requirement of load capacitance CL is set by the MCU only.

The frequency accuracy of  $\pm$ -60ppm is still required to get a functional radio link. The input signal should not have amplitudes exceeding any rail voltage, but any DC voltage within this is OK. To achieve low current consumption and also good SNR ratio when using an external clock from MCU, it is recommended to use an input signal larger than 0.4 V-peak. When clocked externally, OSCO is the input pin, and OSCI is not used. OSCI must be connected to ground.

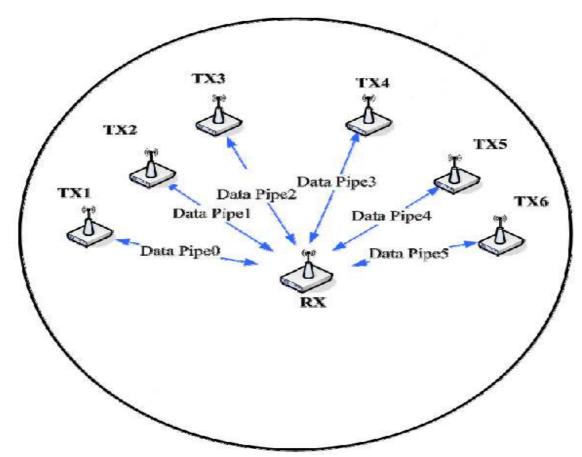

#### 14. Star Network

An EM198850 configured as primary RX will be able to receive data through 6 different data pipes. A data pipe will have a unique address but share the same frequency channel. This means that up to 6 different EM198850 configured as primary TX can communicate with one EM198850 configured as RX, and the EM198850 configured as RX will be able to distinguish between them. Only one data pipe can receive a packet at a time.

Figure 7: in a star network Configuration

The following settings are common to all data pipes:

- Auto ACK enable

- STARTNET enable

- CRC encoding scheme

- Tx / Rx Address width

- Frequency channel

- Air data pipe

- RF data rate

The data pipes are enabled with the bits in the 0x41[5:0] register.

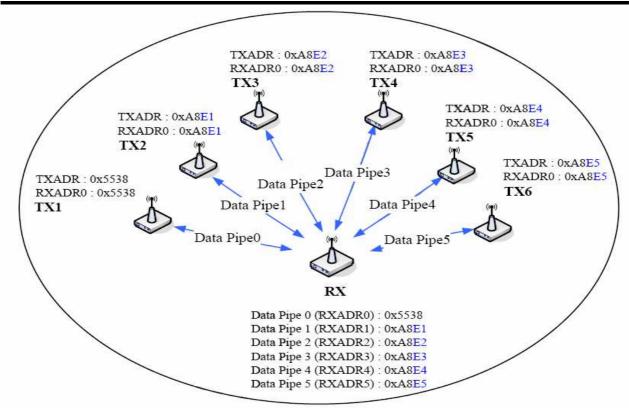

Each data pipe address is configured in the RXADR0 ~ RXADR5. Each data pipe can have up to 2 byte configurable address. Data pipe 0 has a unique 2 byte address. Data pipe 1~5 shares the 8 most

significant address bits. Figure 8. is an example of how data pipes 0~5 are addressed.

|                                                       | Byte 1 | Byte 0 |

|-------------------------------------------------------|--------|--------|

| Data Pipe 0<br>( RXADR0[15:0] = 0x51[7:0],0x50[7:0] ) | 0x55   | 0x38   |

| Data Pipe 1<br>( RXADR1[15:0] = 0x53[7:0],0x52[7:0] ) | 0xA8   | 0xE1   |

| Data Pipe 2<br>( RXADR2[15:0] = 0x53[7:0],0x54[7:0] ) | 0xA8   | 0xE2   |

| Data Pipe 3<br>( RXADR3[15:0] = 0x53[7:0],0x55[7:0] ) | 0xA8   | 0xE3   |

| Data Pipe 4<br>( RXADR4[15:0] = 0x53[7:0],0x56[7:0] ) | 0xA8   | 0xE4   |

| Data Pipe 5 (RXADR5[15:0] = 0x53[7:0],0x57[7:0])      | 0xA8   | 0xE5   |

Figure 8: Addressing Data Pipes 0~5

The Rx receives packet from more than one Tx. To ensure that the ACK packet from the Rx is transmitted to the correct Tx, the Rx takes the data pipe address where it received the packet and use it as the Tx address when transmitting the ACK packet. On the Tx device, the TXADR must be same as the RXADR0. On the Rx device, the RXADR0~RXADR5, defined as the data pipe address, must be unique. Figure 2. is an example of data pipe addressing for the Tx and Rx.

Figure 9: Example of data pipe addressing

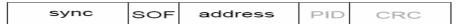

#### 15. Frame Structure

Data Frame-structure

| sync SOF address | PID | payload | CRC |

|------------------|-----|---------|-----|

|------------------|-----|---------|-----|

#### ACK Frame-structure

**Table 4: Frame Structure**

Sync: 4-12 bytes (Default 4 bytes)SOF: Start of Frame (1byte)

- Address: Programmable byte length (1-2 Byte)

- PID: 1 byte

When STARNET 0x40[7] is enabled, PID is adding to frame structure.

When STARNET 0x40[7] is disabled, PID is removing from frame structure.

#### **Example:**

If STARNET 0x40[7] is enabled and set payload length 4 bytes (PKTLEN 0x44[6:0] = 4),

$\rightarrow$  PID= 1 byte, the available payload = 3 bytes

If STARNET 0x40[7] is disabled and set payload length 4 bytes (PKTLEN 0x44[6:0] = 4),

$\rightarrow$  PID= 0 byte, the available payload = 4 bytes

• [7]: Packet type, auto generate by HW

◆ 1'b0 : Data packet (needs ACK or not)

◆ 1'b1: ACK packet

• [6:4]: 000~101 Pipe data number, auto generate by HW

• [3:0]: Packet sequence number, It is used by the Rx device to determine if a packet is new or retransmitted. It defined by user.

- **Payload:** Programmable byte length (1-64 Byte)

- **CRC**: Programmable length(0,1,2,4 Byte)

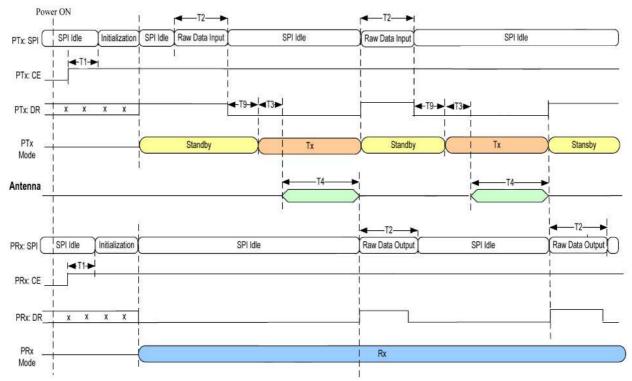

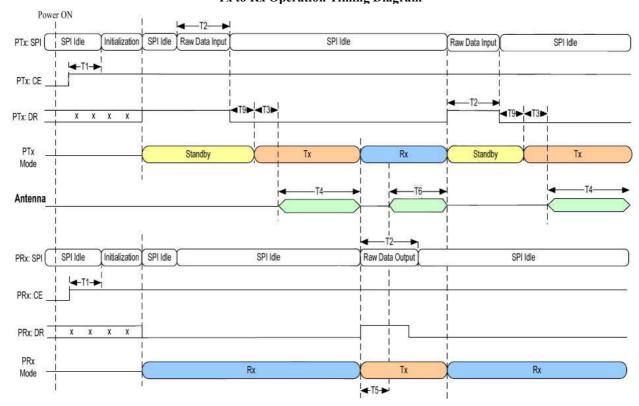

## 16. Operation Timing Diagram

Tx/Rx Link Operation Timing Diagram without Auto-ACK in Buffer Mode

Tx to Rx Operation Timing Diagram

Figure 10: Tx/Rx Link Operation Timing Diagram without Auto-ACK in Buffer Mode

Condition: Disable Auto ACK 0x40[3:2] = 00 PKTCNT 0x45[7:4] = 0001 Enable RXEN0 0x41[5:0] = 000001

The PTx DR is asserted after the packet is transmitted by the PTX. The PRx DR is asserted after the packet is received by the PRX.

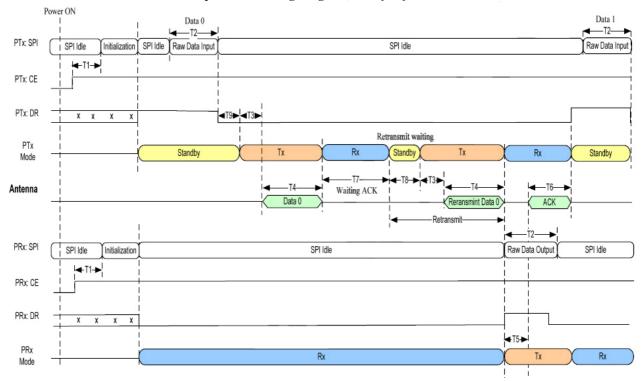

# Tx/Rx Link Operation Timing Diagram with Auto ACK in Buffer Mode Tx to Rx Operation Timing Diagram

Figure 11: Tx/Rx Link Operation Timing Diagram with Auto-ACK in Buffer Mode

Condition: Enable Auto ACK 0x40[3:2] = 11 PKTCNT 0x45[7:4] = 0001 Enable RXEN0 0x41[5:0] = 000001

When the transmission ends the PTX device automatically switches to Rx mode to wait for the ACK packet from the PRX device. After the PTX device receives the ACK packet it responds with an interrupt to MCU. When the PRX device receives the packet it responds with an interrupt to MCU.

Tx/Rx Link Operation Timing Diagram with Auto ACK in Buffer Mode ACK Lost Condition: PTx transmits Data  $\rightarrow$  PTx doesn't receive ACK  $\rightarrow$  Retransmit Data (Retransmit time=1)  $\rightarrow$  PTx receives ACK

Tx to Rx Operation Timing Diagram, 0x47[7:4]RETRYCNT=1

Figure 12: ACK Lost Condition for Tx/Rx Link with Auto-ACK in Buffer Mode

Condition: Enable Auto ACK 0x40[3:2] = 11 PKTCNT 0x45[7:4] = 0001 Enable RXEN0 0x41[5:0] = 000001

Enable RXEN0 0x41[5:0] = 000001 RETRYCNT 0x47[7:4] = 0001

After Data 0 is transmitted, the PTX enters RX mode to receive the ACK packet. After the first transmission, the PTX waits specified time for ACK packet (T7), if it is not in specified time slot, the PTX retransmit the Data 0. When the retransmitted packet is received by the PRX, the PRX DR is asserted and ACK is transmitted back to the PTX. When the ACK is received by the PTX, the PTX DR is asserted.

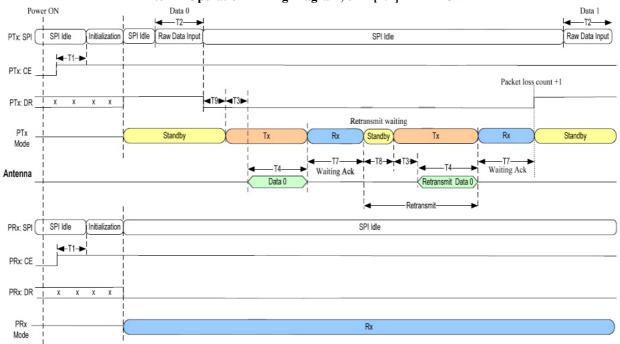

Tx/Rx Link Operation Timing Diagram with Auto ACK in Buffer Mode ACK Lost Condition: PTx transmits Data → PTx doesn't receive ACK → Retransmit Data (Retransmit time=1) → PTx doesn't receive ACK again → Packet Loss Count + 1

Tx to Rx Operation Timing Diagram, 0x47[7:4]RETRYCNT=1

Figure 13: ACK Lost Condition for Tx/Rx Link with Auto-ACK in Buffer Mode

Condition: Enable Auto ACK 0x40[3:2] = 11

PKTCNT 0x45[7:4] = 0001

Enable RXEN0 0x41[5:0] = 000001 RETRYCNT 0x47[7:4] = 0001

If the PTX retransmit counter exceeds the RETRYCNT 0x47[7:4], the PTX DR is asserted and automatically add one to packet loss count (0x4F[7:3]). The payload in PTX FIFO is removed.

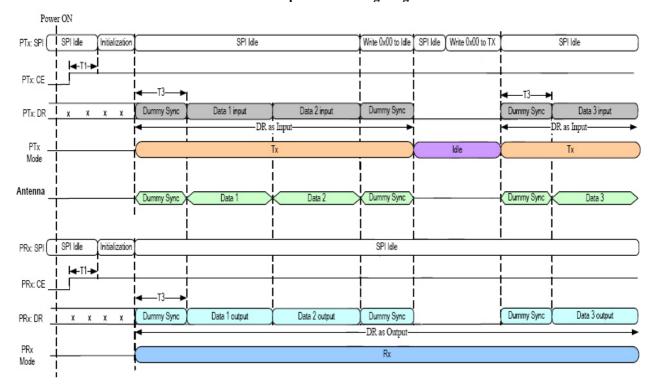

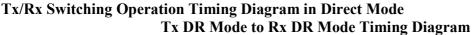

# Tx/Rx Link Operation Timing Diagram in Direct Mode Tx to Rx Operation Timing Diagram

Figure 14: Tx/Rx Link Operation Timing Diagram in Direct Mode

Condition: Set 0x00[6] = 0, 0x00[1] = 1Set 0x00[4:3] = 10 for Rx device Set 0x00[4:3] = 01 for Tx device

When RF blocks are active in Tx device, we need to write dummy sync from pin of DR. It can reduce the Rx receiving settling time. The figure shows the timing diagram from direct mode into idle mode, then into direct mode again.

Figure 15: Tx/Rx Switching Operation Timing Diagram in Direct Mode

Condition: Set 0x00[6] = 0, 0x00[1] = 1Set 0x00[4:3] = 10 for Rx device Set 0x00[4:3] = 01 for Tx device

When RF blocks are active in Tx device, we need to write dummy sync from pin of DR. It can reduce the Rx receiving settling time. The figure shows the timing diagram for Rx/Tx switching operation. If the devices change from Tx(Rx) into Rx(Tx) directly, the devices don't go into standby mode. Besides, the PLL block only takes the time T5 not T3 for PLL settling time.

#### **Time Formula Description:**

Payload Length: n

Data rate: rate

Sync 0x43 [4:0]: s

Address 0x42[7:6]: a

SCK Frequency: SCK

CRC Check 0x43 [6:5]: r

SOF: 1 byte

PID: When STARNET 0x40[7] = 1, PID = 1 byte, else PID=0

Slot time 0x47 [3:0]: **SLT** ACKTOSLOT 0x49 [7:0]: **ATS** BACKOFFWIN 0x58 [7:0]: **BFW**

#### **Formula Description**

T1 must be over 0.8ms for Xtal and regulator settling when using external Xtal with internal oscillator. Only 200us is needed for regulator settling when system reference clock is shared with MCU

Burst Mode : T2 = (n+1) \*8 /SCKNon-Burst Mode : T2 = (2\*n) \*8 /SCK

T3 = 120us

T4 = (s + SOF + a + n + r) \* 8/rate + 15us

T5 = 60us

T6=(s+SOF+PID+a+r)\*8/rate

T7= ATS\*SLT\*10us

T8=BFW\*SLT\*10us

T9= 10us

**Table 5: Delay Times Information**

- T1: Initiation setting time

- T2: TX: Write data to FIFO; RX: Read data from FIFO

- T3: RF delay time for transmit data. (Waiting for PLL settling)

- T4: Packet Input Data Transmission Time

- T5: RF delay for transmit ACK data. (Waiting for PLL settling)

- T6: ACK packet Data Transmission Time

- T7: ACK waiting time, must be larger than T5+T6, programmable from 10us to 32ms.

- T8: Retransmit waiting time, programmable from 0 to 32ms

- T9: Packet Handling Time

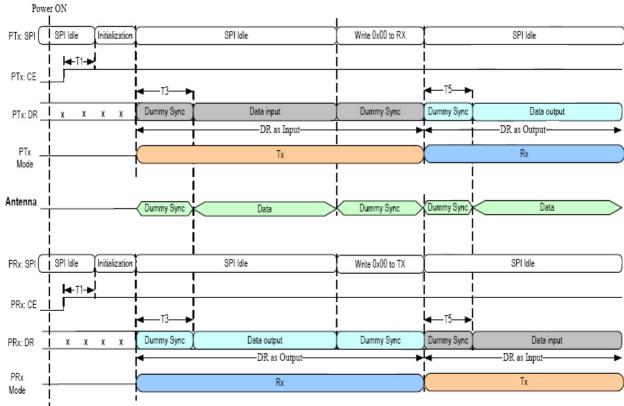

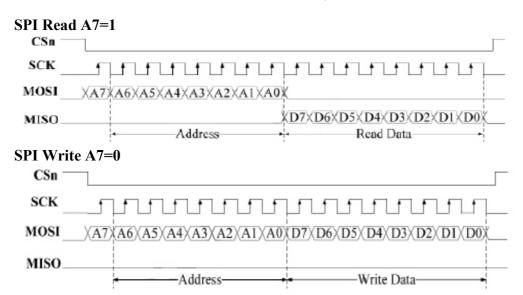

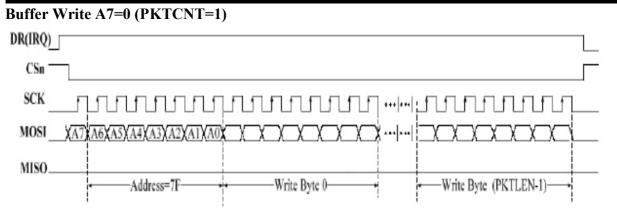

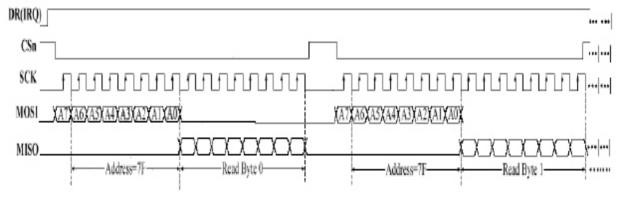

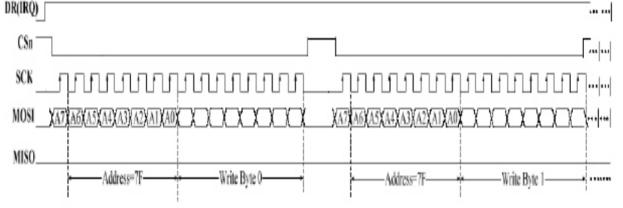

## 17. SPI Interface Timing Diagram

#### A. SPI interface Read / Write for Register

When A7 = 1, MCU read value from EM198850 register. When A7 = 0, MCU write value to EM198850 register.

Figure 16: SPI Read/Write Register Timing Diagram

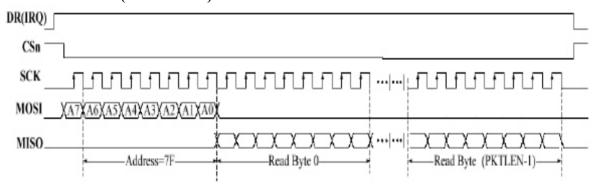

#### B. SPI interface Read / Write for Buffer mode

- ✓ When 0x40[6] = 1, SPI interface switch to Burst mode.

- ✓ Address = 0x7F for FIFO address

#### **Burst Mode:**

#### **Buffer Read A7=1 (PKTCNT=1)**

Figure 17: SPI interface switch to Burst mode when 0x40[6]=1

- ✓ When 0x40[6] = 0, SPI interface switch to Non-Burst mode.

- ✓ Address = 0x7F for FIFO address

#### Non-Burst Mode: Buffer Read A7=1 (PKTCNT=1)

## Buffer Write A7=0 (PKTCNT=1)

Figure 18: SPI interface switch to Non-Burst mode when 0x40[6]=0

## 18. SPI Programmable Function Description

• Data Rate & Crystal Frequency Register Setting

|           |          |     |     |     |   |     |     |   | - |     |       |       |       |       |       |     |     |     | and the same of th |     |       |

|-----------|----------|-----|-----|-----|---|-----|-----|---|---|-----|-------|-------|-------|-------|-------|-----|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| Data Rate | XO Freq. | R00 | R01 | R29 |   | F   | 203 | 3 |   | R0A | R4E   | R42   | R46   | R2D   | R29   | R2E | R2D | R26 | R0C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R28 | R4A   |

| (Mbps)    | (MHz)    | 5   | 0   | 5   | 5 | 4   | 3 2 | 1 | 0 | 5   | [7:0] | [5:0] | [5:3] | [2:0] | [3:2] | 0   | 5   | 3   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3   | [7:0] |

| 1.6       | 12       | 1   | 0   | 1   | 0 | 0 0 | ) 1 | 1 | 0 | 1   | 0x02  | 01111 | 110   | 100   | 10    | 0   | 1   | 0   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1   | 0x27  |

| 1         | 12       | 1   | 0   | 1   | 0 | 0 ( | ) 1 | 1 | 0 | 0   | 0x02  | 11000 | 001   | 010   | 10    | 1   | 0   | 1   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0   | 0x3F  |

| 1.6       | 16       | 1   | 1   | Х   | 0 | 0   | 1 0 | 0 | 0 | 1   | 0x01  | 1010  | 110   | 100   | 10    | 0   | 1   | 0   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1   | 0x27  |

| 1         | 16       | 1   | 1   | Х   | 0 | 0   | 1 0 | 0 | 0 | 0   | 0x01  | 10000 | 001   | 010   | 10    | 1   | 0   | 1   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0   | 0x3F  |

| 1.6       | 24       | 0   | 1   | 1   | 0 | 0   | 1 1 | 0 | 0 | 1   | 0x02  | 01111 | 110   | 100   | 10    | 0   | 1   | 0   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1   | 0x27  |

| 1         | 24       | 0   | 1   | 1   | 0 | 0   | 1 1 | 0 | 0 | 0   | 0x02  | 11000 | 001   | 010   | 10    | 1   | 0   | 1   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0   | 0x3F  |

Table 6: Data Rate & Crystal Frequency Register Setting Table

According to the date rate and crystal frequency, find out the corresponding register values before write registers. When write the initial register values, set the relative register values.

#### • Description of register R0x0E[7]

- ◆ 1: set 1 to forbid to write anyone of RF SPI registers address from 0x20 to 0x33

- 0: set 0 to allow to write anyone of RF SPI registers address from 0x20 to 0x33

- ◆ Example:

If MCU needs to write register R28, because it is one of RF SPI registers from 0x20 to 0x33, MCU writes register sequence from  $R0E[7] = 0 \rightarrow R28 \rightarrow R0E[7] = 1$

#### • Operation Mode Register Setting in Direct Mode

| Operation Mode           | R0C | R28 | R00 | R00 | R01   | R44   | R43   |   |   | R00 |   |   | R | 10 | R41   | R7F   |

|--------------------------|-----|-----|-----|-----|-------|-------|-------|---|---|-----|---|---|---|----|-------|-------|

| Operation Mode           | 5   | 3   | 7   | 5   | [3:1] | [6:0] | [4:0] | 6 | 4 | 3   | 1 | 0 | 1 | 0  | [7:0] | [7:0] |

| Tx Device in Direct Mode | 0   | 1   | 1   | 1*b | 010   | 0x01  | 0x00  | 0 | 0 | 1   | 1 | 1 | 1 | 0  | 0x80  | 0x00  |

| Rx Device in Direct Mode | 0   | 1   | 1   | 1*b | 010   | 0x08  | 0x04  | 0 | 1 | 0   | 1 | 1 | 0 | 1  | 0x81  | Х     |

#### **Table 7: Operation Mode Register Setting Table**

Write Register Sequence from R0C  $\rightarrow$  R0E[7]=0  $\rightarrow$  R28  $\rightarrow$  R0E[7] =1  $\rightarrow$  R00  $\rightarrow$  R00  $\rightarrow$  R01  $\rightarrow$  R44  $\rightarrow$  R43  $\rightarrow$  R00  $\rightarrow$  R40  $\rightarrow$  R41  $\rightarrow$  R7F into direct mode

#### • RF Status Indication

| RF Status indication | R07[6] | R2E[5] |

|----------------------|--------|--------|

| RSSI[5:0]            | 0      | 1      |

| {RSSI[5:1], LD}      | 1      | 1      |

#### **Table 8: RF Status Indication Table**

- $\bullet$  When set R0x07[6] = 0 & R2E[5] =1,

- When PLL turns on, MCU needs to wait 150usec, then MCU reads

<sup>\*</sup>b: the register value of R00[5] is selected by the Table 7. It's determined by Xtal frequency.

R0x4B[5:0] to get the RSSI digital output value, RSSI[5:0].

- Write Register Sequence from  $R07 \rightarrow R0E[7]=0 \rightarrow R2E \rightarrow R0E[7]=1$

- $\bullet$  When set R0x07[6] = 1 & R2E[5] =1,

- When PLL turns on, MCU needs to wait 150usec, then MCU reads R0x4B[5:1] to get the RSSI digital output value, RSSI[5:1].

- When PLL turns on, MCU needs to wait 350usec, then MCU reads R0x4B[0] to get the LD signal (PLL lock detection indication).

- Write Register Sequence from  $R07 \rightarrow R0E[7]=0 \rightarrow R2E \rightarrow R0E[7]=1$

#### Operation Mode Register Setting in Normal Operation Condition

#### Figure 19: Operation Mode Register Setting in Normal Operation Condition

#### • Channel Change in Buffer Mode:

• Write 0x02[6:0] as the table listed below

| ▼ WIIIC 0X02[0.0] | ds the table listed below |

|-------------------|---------------------------|

| CH_NO             | 0x02[6:0]                 |

| 1                 | 0x01                      |

| 2                 | 0x02                      |

| •                 | •                         |

| •                 | •                         |

| •                 | •                         |

| 62                | 0x3E                      |

| 63                | 0x3F                      |

| •                 | •                         |

| •                 | •                         |

| •                 | •                         |

| 80                | 0x50                      |

| 81                | 0x51                      |

| 82                | 0x52                      |

**Table 9: Channel Change Control Table**

#### • Frequency Deviation Control:

| 0x0a[3:0] | Frequency<br>Deviation (kHz) |

|-----------|------------------------------|

| 0011      | 200                          |

| 0 1 1 1   | 400                          |

| 1 1 0 1   | 500                          |

**Table 10: Frequency Deviation Setting**

#### • Battery Detection Level Setting

| Threshold Voltage |           |           |

|-------------------|-----------|-----------|

| 0x29[1:0]         | 0x26[7]=0 | 0x26[7]=1 |

| 00                | 1.9       | 1.7       |

| 01                | 2.0       | 1.8       |

| 10                | 2.1       | 1.9       |

| 11                | 2.2       | 2.0       |

**Table 11: Battery Detection Level Setting**

- ♦ Write Register Sequence from R0E[7]=0 → R29 → R26 → R0E[7]=1 to change the battery detection level.

- ◆ Battery detection function is only active when CE = High.

#### • RX/TX FIFO Reset Function

When MCU writes R0x4D[0] = 1, FIFO will be reset. For RX device, because RX receiver is always active, RF blocks need 120usec settling time after FIFO reset

## 19. Serial Register Format of Power ON Initialization

Follow the serial register addresses showed below to initialize the EM198850 RF transceiver. The register address 0x40[7:0] and 0x41[7:0] are used to set the device into TX or RX mode.

The values showed in table are for the condition listed below:

- Date Rate = 1Mbps

- Xtal Frequency = 12MHz

- TX/RX Buffer Mode

- Package Length = 8 bytes

- Syn. Length = 4 bytes

- Disable Star Network

| Register<br>Address | Initialization Register |     | Description                |

|---------------------|-------------------------|-----|----------------------------|

|                     | TX                      | RX  |                            |

| 0x4E                | 0                       | x02 | Value reference to Table 6 |

| 0x4D                | 0                       | x01 |                            |

| 0x42                | 0                       | x98 | Value reference to Table 6 |

| 0x43                | 0:                      | xC4 |                            |

| 0x44                | 0                       | x08 |                            |

| 0x45                | 0                       | x10 |                            |

| 0x46                | 0                       | x09 | Value reference to Table 6 |

| 0x47                | 0                       | x11 |                            |

| 0x48                | 0                       | x01 |                            |

| 0x49                | 0:                      | x8A |                            |

| 0x4A                | 0x27                    |     | Value reference to Table 6 |

| 0x4B                | 0x00                    |     |                            |

| 0x4C                | 0x06                    |     |                            |

| 0x50                | 0                       | x00 |                            |

| 0x51                | 0                       | x11 |                            |

| 0x52                |                         | x22 |                            |

| 0x53                | 0                       | x33 |                            |

| 0x54                | 0                       | x44 |                            |

| 0x55                |                         | x55 |                            |

| 0x56                | 0x66                    |     |                            |

| 0x57                | 0x77                    |     |                            |

| 0x58                | 0x08                    |     |                            |

| 0x00                | 0xE5                    |     | Value reference to Table 6 |

| 0x01                | 0x84                    |     | Value reference to Table 6 |

| 0x02                | 0x00                    |     |                            |

| 0x03                |                         |     | Value reference to Table 6 |

| 0x04                | 0x00                    |     |                            |

| 0x05                | 05 0x40                 |     |                            |

| 0x06                | 0x5D                    |     |                            |

<sup>\*</sup> This specification are subject to be changed without notice.

| 0x07          | 0x18                           |                                                                            |

|---------------|--------------------------------|----------------------------------------------------------------------------|

| 0x08          | 0x40                           |                                                                            |

| 0x09          | 0x18                           |                                                                            |

| 0x0A          | 0x47                           | Value reference to Table 6                                                 |

| 0x0B          | 0x0B                           |                                                                            |

| 0x0C          | 0xE0                           | Value reference to Table 6                                                 |

| 0x0D          | 0x4F                           |                                                                            |

| 0x0E          | 0x11                           |                                                                            |

| 0x0F          | 0x1C                           |                                                                            |

| 0x20          | 0xAD                           |                                                                            |

| 0x21          | 0x64                           |                                                                            |

| 0x22          | 0x00                           |                                                                            |

| 0x23          | 0xC3                           |                                                                            |

| 0x24          | 0xBD                           |                                                                            |

| 0x25          | 0xA2                           |                                                                            |

| 0x26          | 0x1A                           | Value reference to Table 6                                                 |

| 0x27          | 0x09                           |                                                                            |

| 0x28          | 0x00                           | Value reference to Table 6                                                 |

| 0x29          | 0xB8                           | Value reference to Table 6                                                 |

| 0x2A          | 0x71                           |                                                                            |

| 0x2B          | 0x06                           |                                                                            |

| 0x2C          | 0x80                           |                                                                            |

| 0x2D          | 0x1A                           | Value reference to Table 6                                                 |

| 0x2E          | 0x09                           |                                                                            |

| 0x2F          | 0x64                           |                                                                            |

| 0x30          | 0xC0                           |                                                                            |

| 0x31          | 0x00                           |                                                                            |

| 0x32          | 0x40                           |                                                                            |

| 0x33          | 0x3B                           |                                                                            |

| 0x00          | 0xA7                           |                                                                            |

| 0x32          | 0x4A                           |                                                                            |

| 0x00          | 0xE5                           | Value reference to Table 6                                                 |

| 0x0E          | 0x91                           |                                                                            |

| 0x40          | 0x51                           |                                                                            |

| 0x41          | 0x81                           |                                                                            |

| 0x0C          | 0xC0                           |                                                                            |

| 0x02          | 0x80                           |                                                                            |

| 0x04          | 0x4A                           |                                                                            |

| 0x05          | 0xDA                           |                                                                            |

| 0x06          | 0xFA                           |                                                                            |

| After waiting | g 250uS, MCU continues reading | g 0X4B[5:0] 5times.                                                        |

| 0x4A          | "0x4B (Max)-4                  | Select maximum 0x4B value and minus 4,<br>then write this result into 0x4A |

| 0x05          | 0x40                           |                                                                            |

|               |                                |                                                                            |

# RF24DT-50DS 2.4GHz Digital RF Module Application Note

| 0x02 | 0x00 |  |

|------|------|--|

| 0x0C | 0xE0 |  |

## 20. Appendix:

#### Grounding System

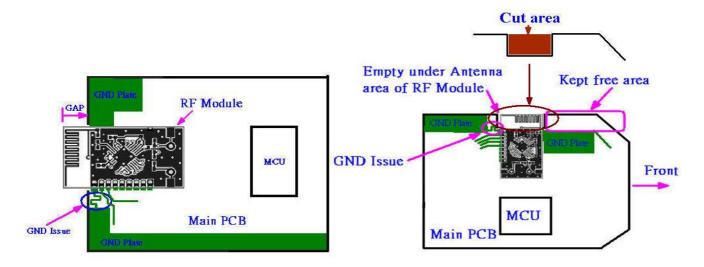

PCB should always be laid out with a ground plane connected to the negative power supply. If this is not done properly, obscure circuit behavior might occur. From a digital designer point of view the reason to this might be difficult to understand, as most digital circuitry functions very well without a ground plane. At RF frequencies even a short line will work as an inductor. All connections to the ground plane must be made as short as possible. A via should be placed close every pad that is to be grounded. Never let two ground pads share one via, this can lead to cross talk between the two pads due to the impedance of the via itself. With surface mounted PCBs all signal routing is done on the same side as where the components are mounted, and the ground plane will be on the opposite side. Preferably the ground plane should cover the complete PCB (except under PCB antennas). If a PCB with more than two layers is used, the ground plane should be placed in the layer that is adjacent to the upper signal layer. It is also a good idea to fill all available space at the signal routing layers with ground plane. These ground planes must then be connected to the main ground plane with multiple vias. Please note that the characteristics of inductors will be changed by the presence of a ground node close by. This must be taken into consideration when selecting value and placing of these.

The ground system will change the antenna impedance when mount the RF module to main PCB, hence, adding an inductor or used the micro-strip to separation the RF & MCU ground system. The solution show as below:

#### Module placement rules

To ensure antenna has proper radiation, module placement on the system board is an important issue for the system design. We summarize the considerations in the following rules of thumb:

- Don't put any ground plane and circuit beneath the antenna pattern area.

- If possible, keep the space around the antenna clear from conducting or dielectric materials, such as electronic components, the casing or the user's body.

• If possible, put the module on the edge of the system.

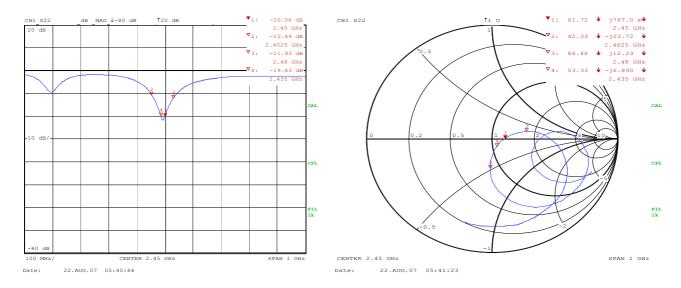

#### Antenna Characteristic

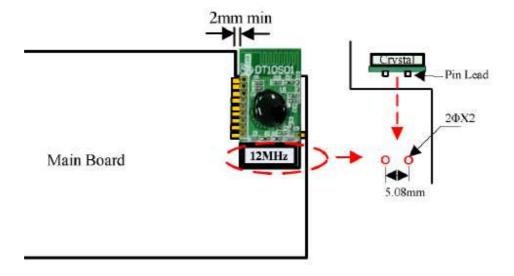

#### RF Module with Main PCB Note

The crystal distributed on the RF module is dip type, it should have via hole underneath the RF module on the main board to make good module contact. Recommendation shows as below:

<sup>\*</sup> This specification are subject to be changed without notice.

21. History:

| Γ | Version | Date          | Description   |

|---|---------|---------------|---------------|

|   | V1.0    | Sep. 09. 2009 | New Creation. |