# MX589 High Speed GMSK Modem

- Data Rates from 4kbps to 64kbps

- Full or Half Duplex Gaussian Minimum Shift Keying (GMSK) Operation

- Selectable BT: (0.3 or 0.5)

- Low Power:

3.0V, 32kbps, 1.5mA typ.

5.0V, 64kbps, 4.0mA typ.

- Low Cost

- Point of Sale Terminals

- Low Power Wireless Data Link for PCs, Laptops, and Printers

- Data for GPS/Differential GPS

- Portable Wireless Data Applications:

Cellular Digital Packet Data (CDPD)

Mobiltex™ Mobile Data System

- Low Current Non-DSP Solution

The MX589 is a single-chip synchronous modem designed for wireless data applications. Employing Gaussian Minimum Shift Keying (GMSK) baseband modulation, the MX589 features a wide range of available data rates: 4kbps to 64kbps. Data rates and choice of BT (0.3 or 0.5) are pin-programmable to provide for different system requirements. The Tx and Rx digital data interfaces are bit serial, synchronized to Tx and Rx data clocks generated by the modem. Separate Tx and Rx Powersave inputs allow full or half-duplex operation. Rx input levels can be set by a suitable AC and DC level adjusting circuit built with external components around an on-chip Rx Input Amplifier. Acquisition, lock and hold of Rx data signals are made easier and faster by the use of Rx Control Inputs to clamp, detect and/or hold input data levels and can be set by the µProcessor as required. The Rx S/N output provides an indication of the quality of the received signal.

All trademarks and service marks are held by their respective companies.

## CONTENTS

| Section.....                               | Page      |

|--------------------------------------------|-----------|

| <b>1. Block Diagram .....</b>              | <b>3</b>  |

| <b>2. Signal List .....</b>                | <b>4</b>  |

| <b>3. External Components .....</b>        | <b>5</b>  |

| <b>4. General Description .....</b>        | <b>6</b>  |

| 4.1 Clock Oscillator Divider .....         | 6         |

| 4.2 Receive .....                          | 7         |

| 4.3 Transmit .....                         | 11        |

| 4.4 Data Formats.....                      | 13        |

| 4.5 Acquisition and Hold Modes.....        | 13        |

| <b>5. Application.....</b>                 | <b>13</b> |

| 5.1 Radio Channel Requirements .....       | 13        |

| 5.2 AC Coupling of Tx and Rx Signals ..... | 15        |

| <b>6. Performance Specification.....</b>   | <b>16</b> |

| 6.1 Electrical Performance .....           | 16        |

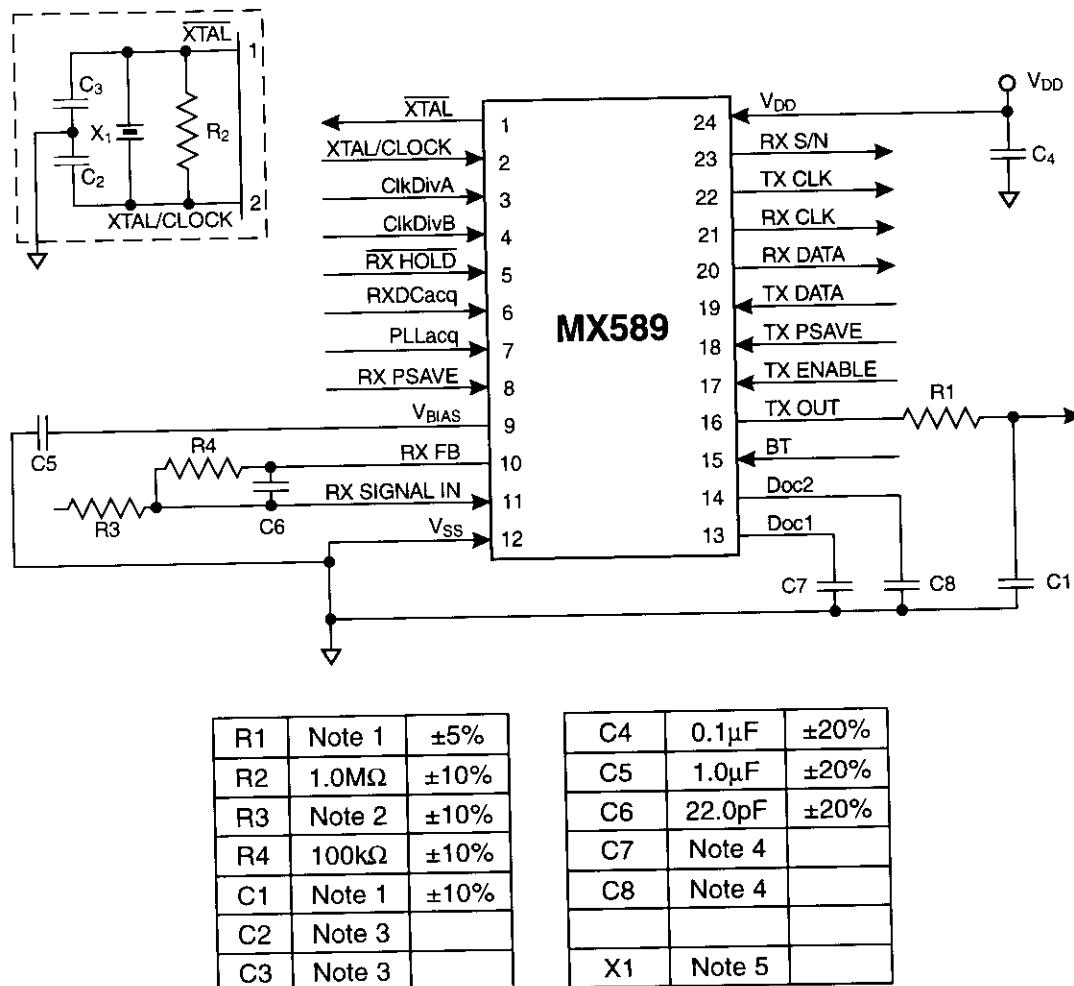

| 6.2 Packaging.....                         | 19        |

MX COM, Inc. reserves the right to change specifications at any time and without notice.

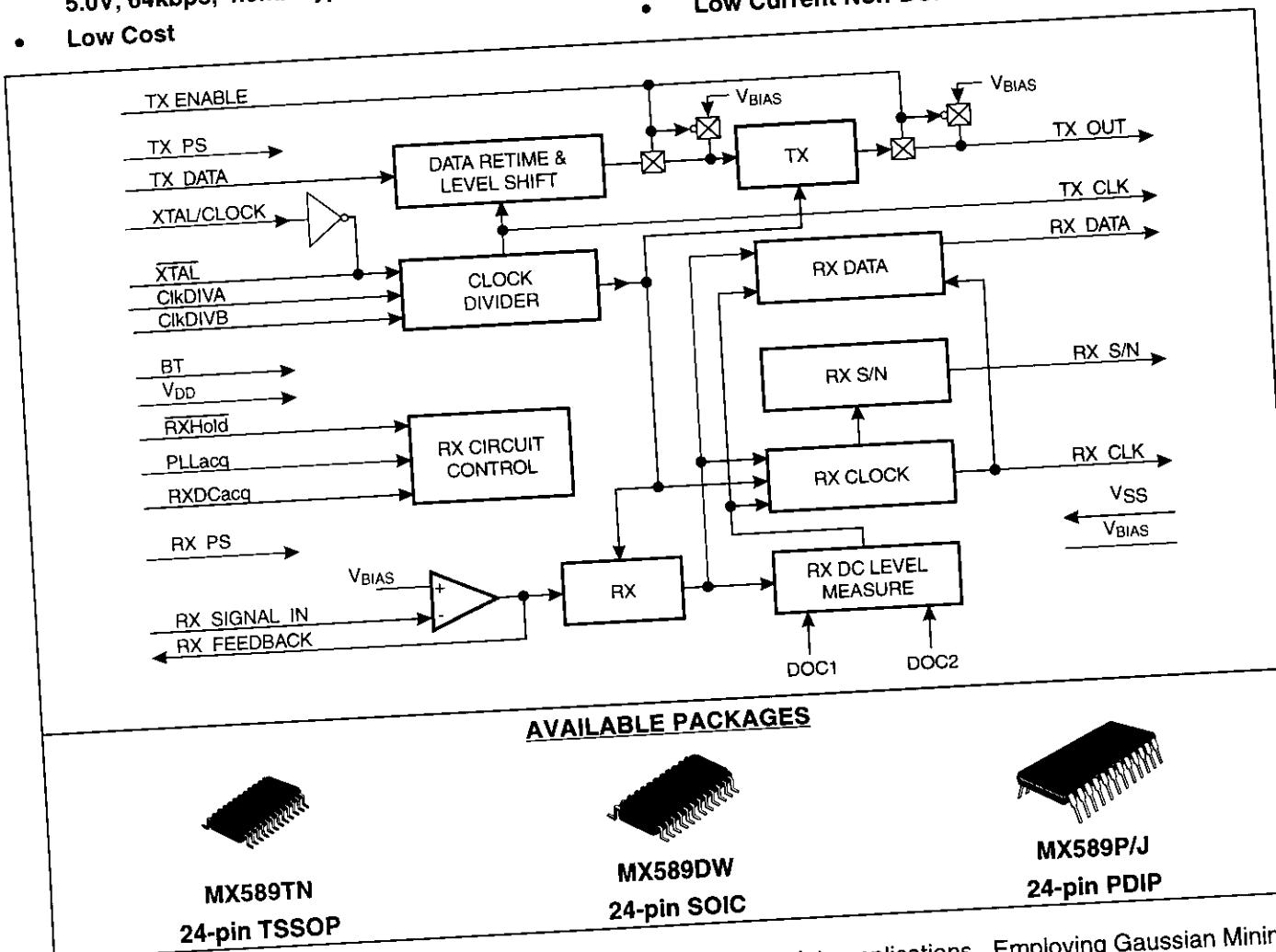

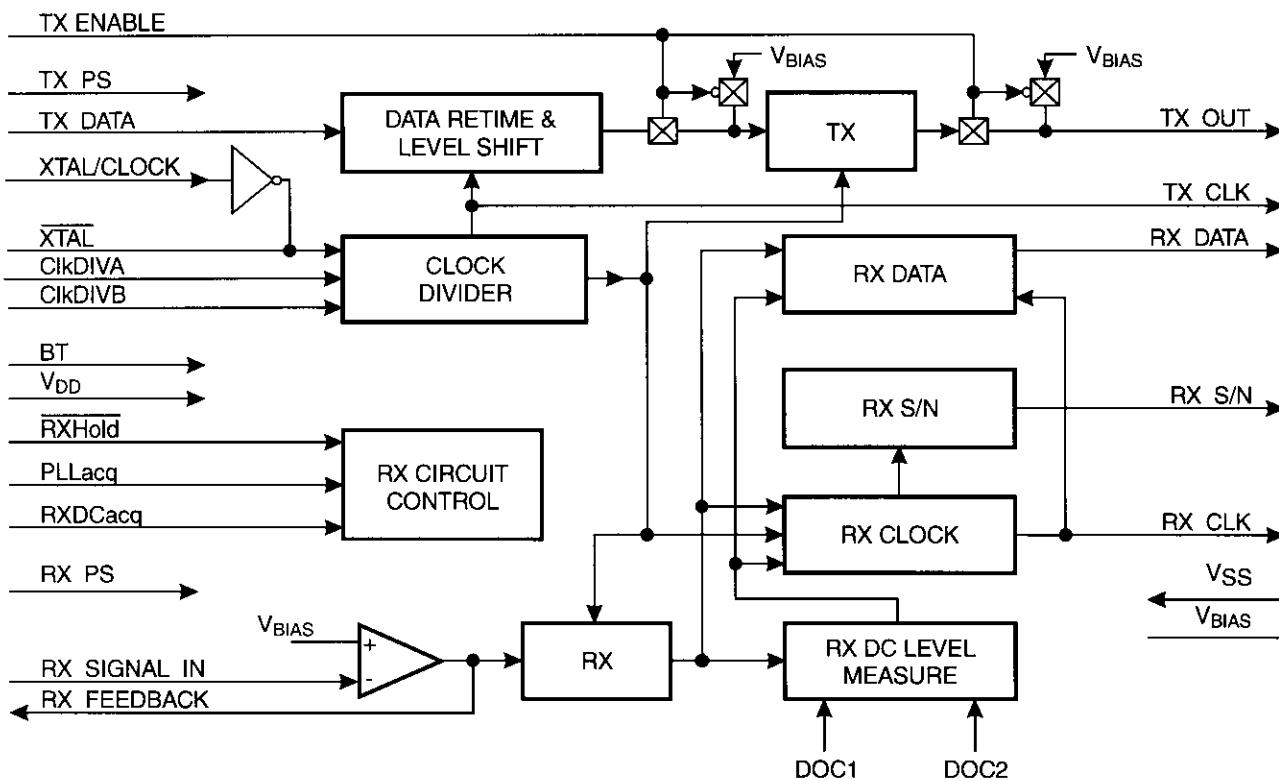

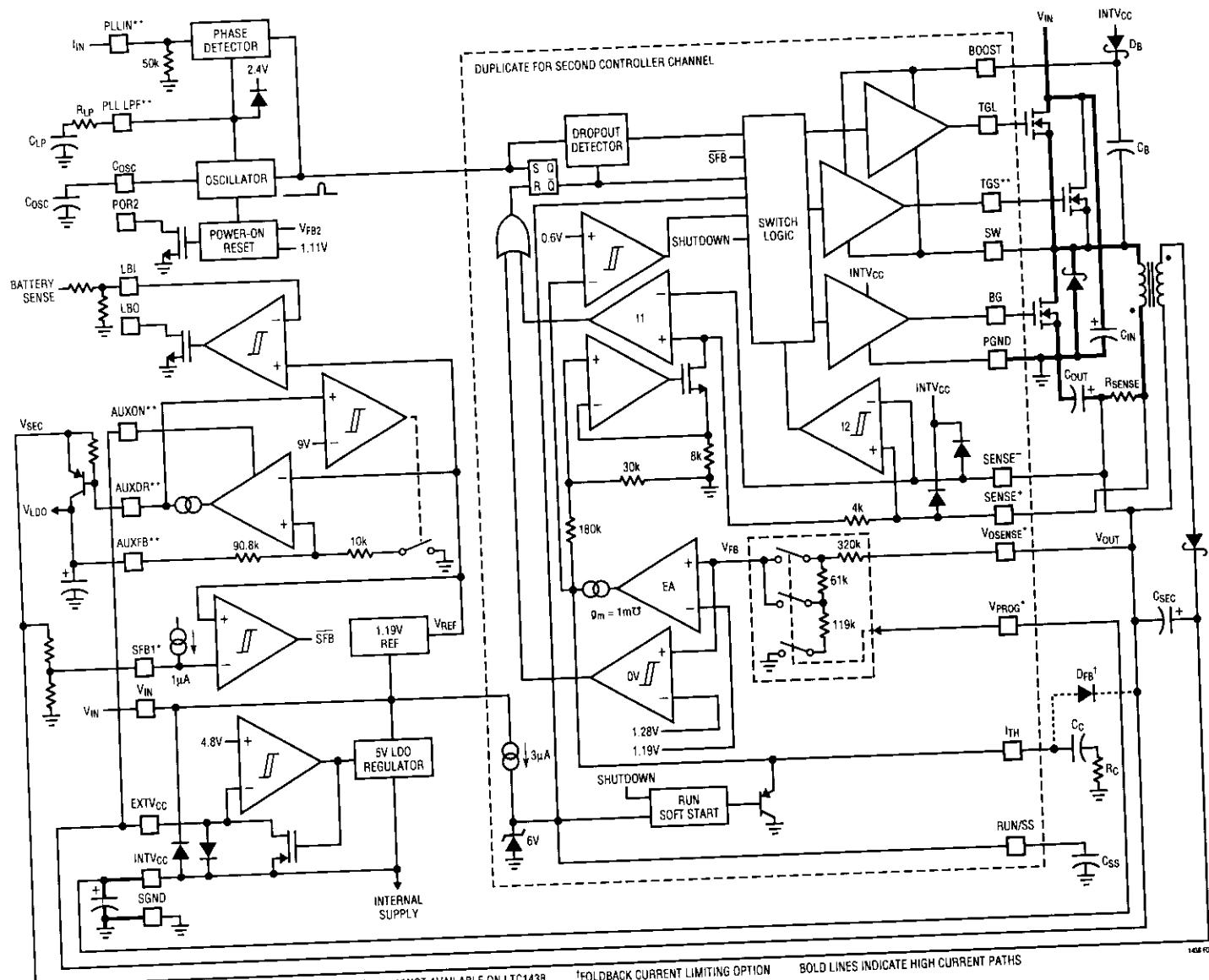

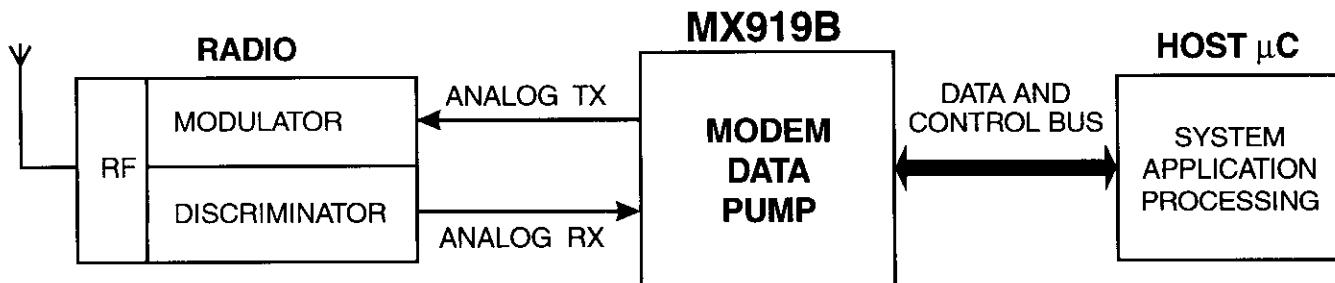

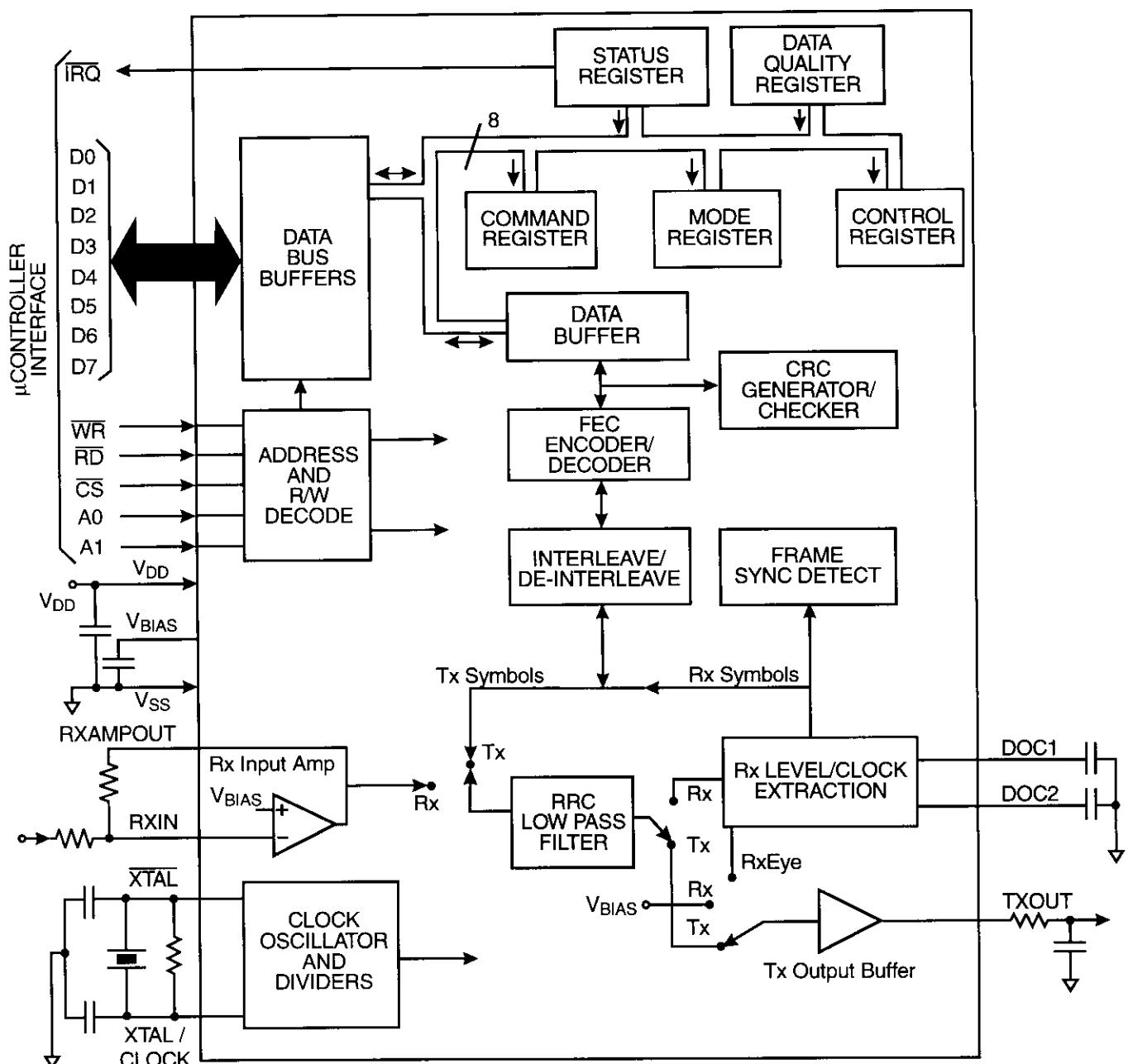

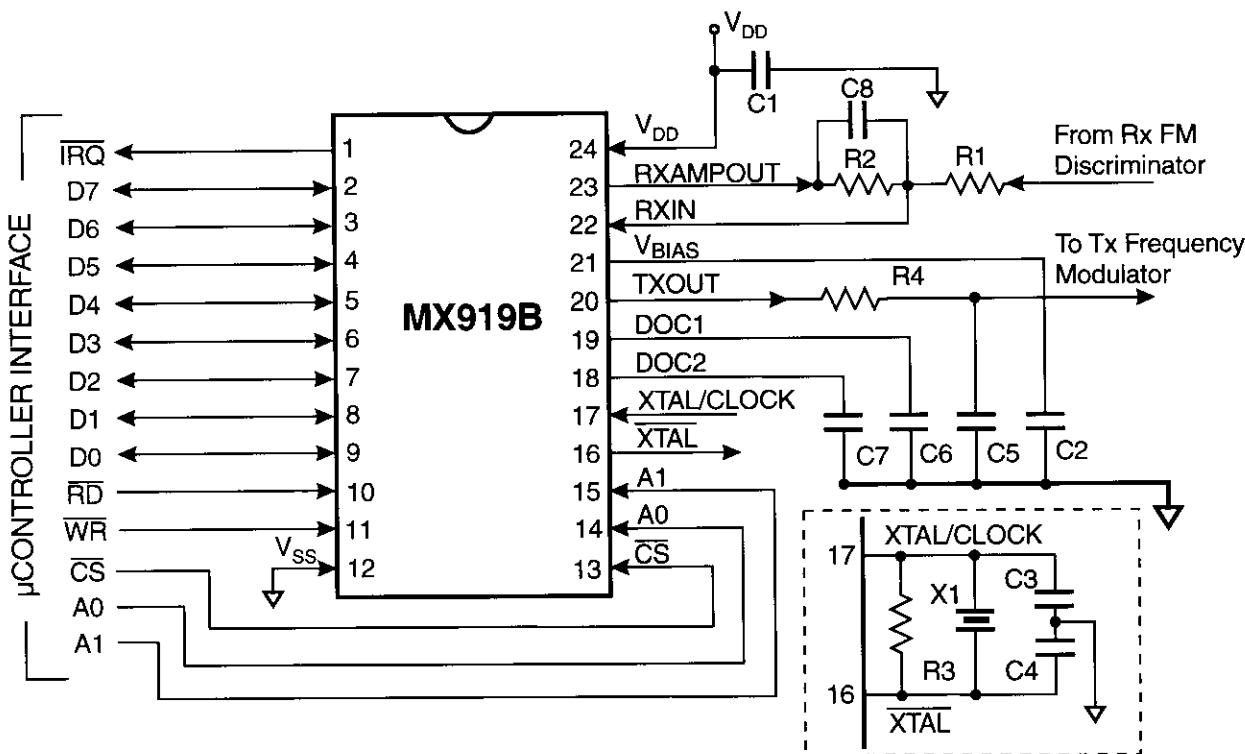

## 1. Block Diagram

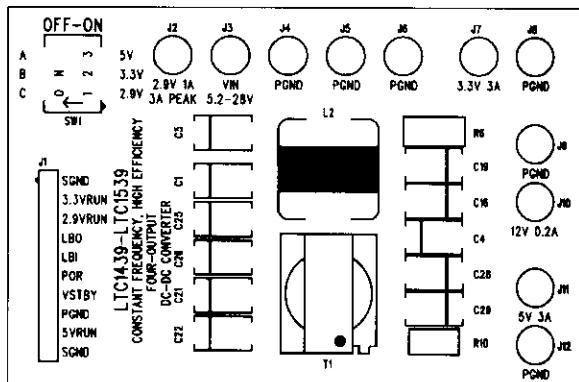

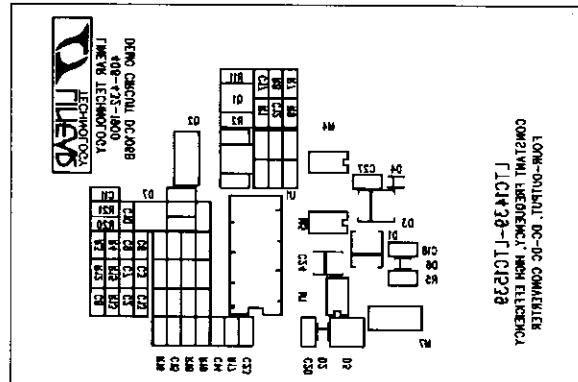

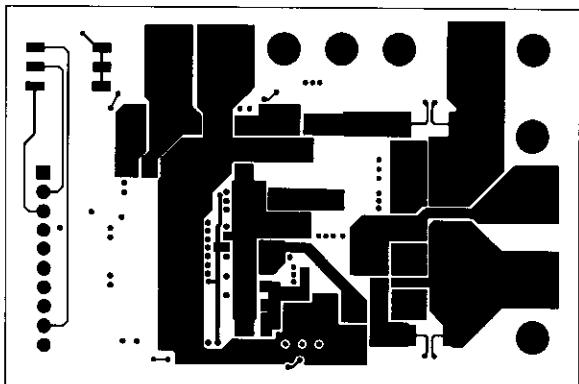

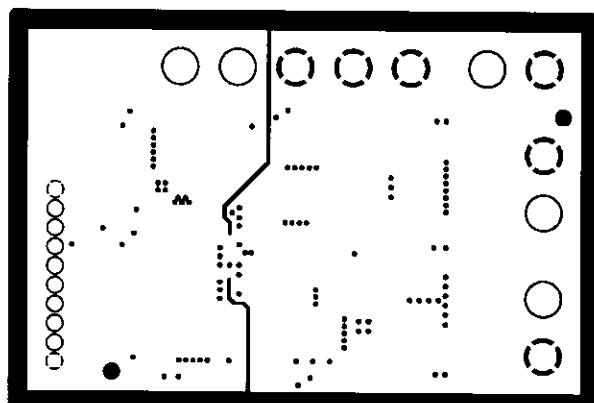

Figure 1: Device Block Diagram

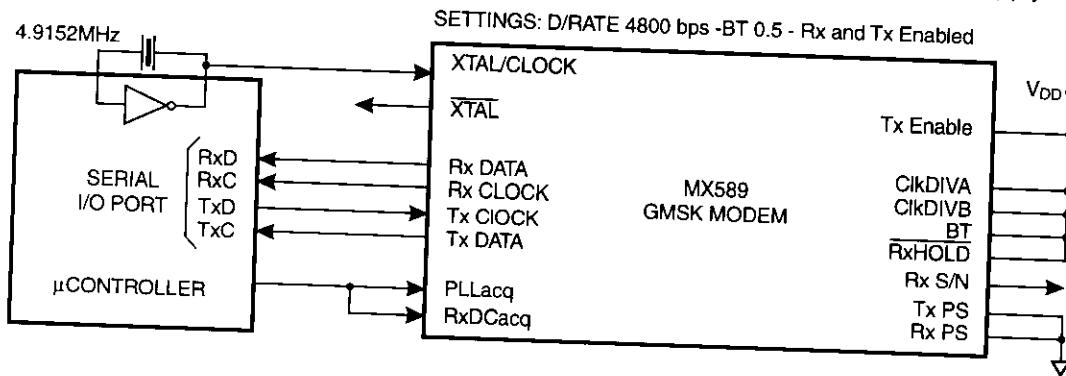

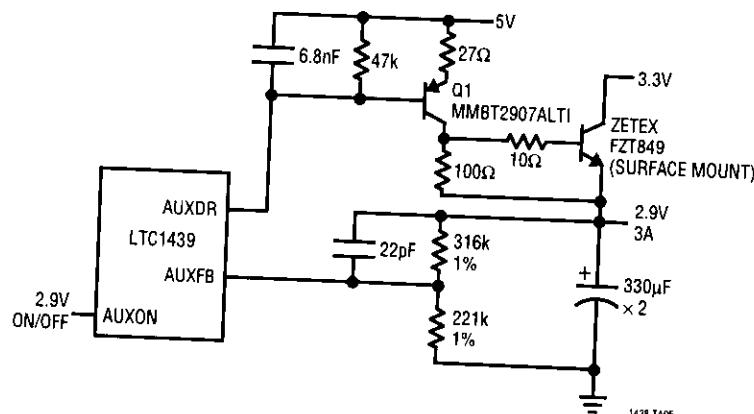

Figure 2: System Block Diagram

## 2. Signal List

| Pin No. | Name              | Type | Description                                                                                                                                                                                                                                                    |

|---------|-------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | XTAL              |      | The output of the on-chip clock oscillator.                                                                                                                                                                                                                    |

| 2       | Xtal/Clock        |      | The input to the on-chip Xtal oscillator. A Xtal, or externally derived clock ( $f_{XTAL}$ ) pulse input should be connected here. If an externally generated clock is to be used, it should be connected to this pin and the <u>XTAL</u> pin left unconnected |

| 3       | ClkDivA           |      | Logic level inputs control the internal clock divider and therefore the transmit and receive data rate. See Table 1                                                                                                                                            |

| 4       | ClkDivB           |      | Logic level inputs control the internal clock divider and therefore the transmit and receive data rate. See Table 1                                                                                                                                            |

| 5       | Rx HOLD           |      | A logic 0 applied to this input will freeze the Clock Extraction and Level Measurement circuits unless they are in Acquire mode.                                                                                                                               |

| 6       | RxDcacq           |      | A logic 1 applied to this input will set the RX Level Measurement circuitry to the Acquire mode.                                                                                                                                                               |

| 7       | PLLacq            |      | A logic 1 applied to this input will set the Rx Clock Extraction circuitry to Acquire mode (see Table 2).                                                                                                                                                      |

| 8       | Rx PSAVE          |      | A logic 1 applied to this input will powersave all receive circuits except for Rx CLK output (which will continue at the set bit-rate) and cause the Rx Data and Rx S/N outputs to go to a logic 0.                                                            |

| 9       | V <sub>BIAS</sub> |      | The internal circuitry bias line, held at $V_{DD}/2$ , this pin must be bypassed to $V_{SS}$ by a capacitor mounted close to the pin.                                                                                                                          |

| 10      | Rx FB             |      | Output of the Rx Input Amplifier.                                                                                                                                                                                                                              |

| 11      | Rx Signal In      |      | Input to Rx Input Amplifier.                                                                                                                                                                                                                                   |

| 12      | V <sub>SS</sub>   |      | Negative supply. Signal ground.                                                                                                                                                                                                                                |

| 13      | Doc1              |      | Connections to the Rx Level Measurement Circuitry. A capacitor should be connected from each pin to $V_{SS}$ . See Figure 3.                                                                                                                                   |

| 14      | Doc2              |      | Connections to the Rx Level Measurement Circuitry. A capacitor should be connected from each pin to $V_{SS}$ . See Figure 3.                                                                                                                                   |

| 15      | BT                |      | A logic level to select the modem BT (the ratio of the Tx Filter's -3dB frequency to the Bit-Rate). A logic 1 = BT of 0.5, a logic 0 = BT of 0.3.                                                                                                              |

| 16      | Tx Out            |      | Tx signal output from the MX589 GMSK Modem.                                                                                                                                                                                                                    |

| 17      | Tx Enable         |      | A logic 1 applied to this input enables the transmit data path through the Tx Filter to the Tx Out pin. A logic 0 will place the Tx Out pin at $V_{BIAS}$ via a high impedance.                                                                                |

| 18      | Tx PSAVE          |      | A logic 1 applied to this input will powersave all transmit circuits except for the Tx Clock.                                                                                                                                                                  |

| 19      | Tx Data           |      | The logic level input for the data to be transmitted. This data should be synchronous with Tx CLK.                                                                                                                                                             |

| 20      | Rx Data           |      | A logic level output carrying the received data, synchronous with Rx CLK.                                                                                                                                                                                      |

| 21      | Rx CLK            |      | A logic level clock output at the received data bit-rate.                                                                                                                                                                                                      |

| 22      | Tx CLK            |      | A logic level clock output at the transmit-data rate.                                                                                                                                                                                                          |

| 23      | Rx S/N            |      | A logic level output which may be used as an indication of the quality of the received signal.                                                                                                                                                                 |

| 24      | V <sub>DD</sub>   |      | Positive supply. A single 5.0V power supply is required. Levels and voltages within this modem are dependent upon this supply. This pin should be bypassed to $V_{SS}$ by a capacitor mounted close to the pin.                                                |

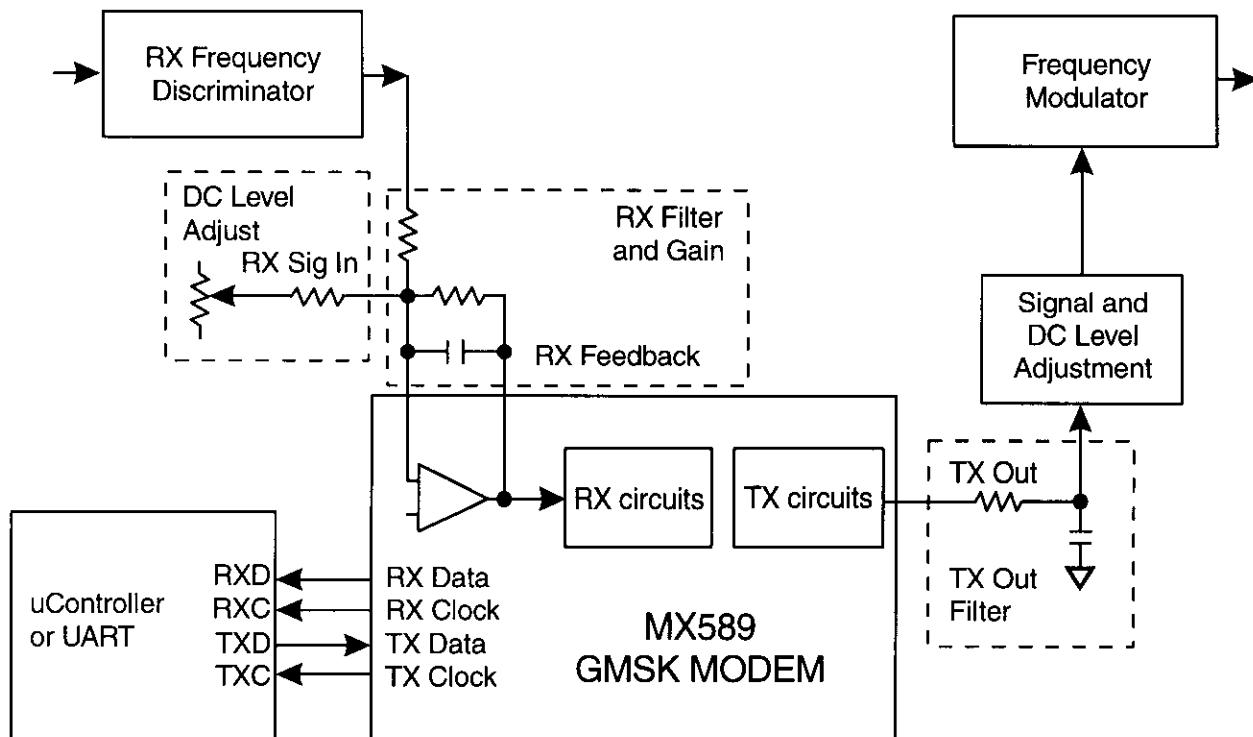

### 3. External Components

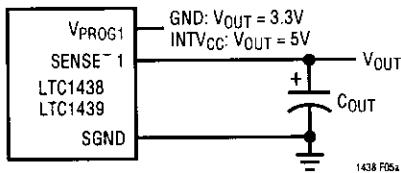

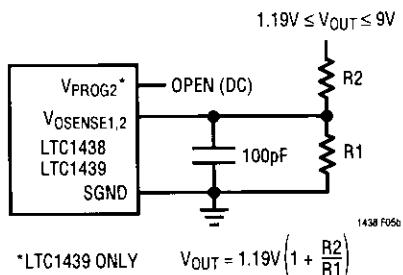

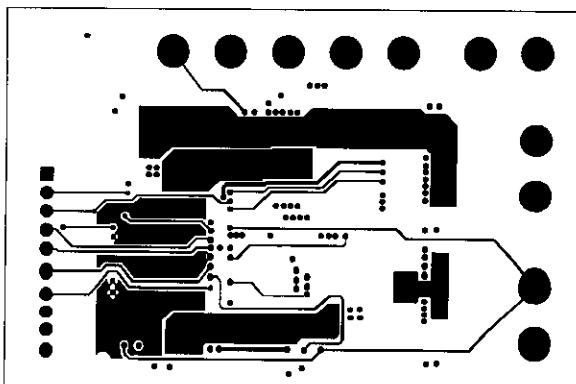

Figure 3: Recommended External Components

#### External Components Notes:

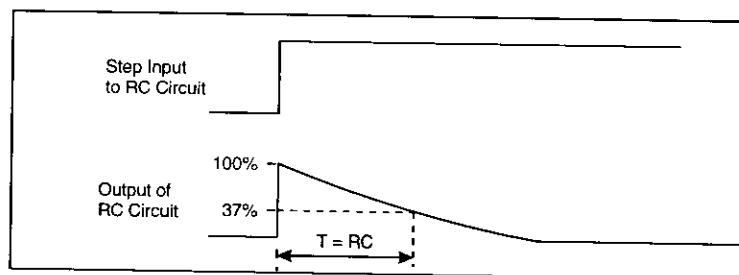

1. The RC network formed by R1 and C1 is required between the Tx Out pin and the input to the modulator. This network, which can form part of any DC level shifting and gain adjustment circuitry, forms an important part of the transmit signal filtering. The ground connection to the capacitor C1 should be positioned to give maximum attenuation of high-frequency noise into the modulator.

The component values should be chosen so that the product of the resistance and the capacitance is:

$$BT \text{ of } 0.3 = 0.34/\text{bit rate (bps)}$$

$$BT \text{ of } 0.5 = 0.22/\text{bit rate (bps)}$$

| Data Rate bps | BT = 0.3 |       | BT = 0.5 |       |

|---------------|----------|-------|----------|-------|

|               | R1       | C1    | R1       | C1    |

| 4000          | 120kΩ    | 680pF | 120kΩ    | 470pF |

| 4800          | 100kΩ    | 680pF | 100kΩ    | 470pF |

| 8000          | 91kΩ     | 470pF | 120kΩ    | 220pF |

| 9600          | 91kΩ     | 390pF | 47kΩ     | 470pF |

| 16000         | 47kΩ     | 470pF | 91kΩ     | 150pF |

| 19200         | 100kΩ    | 180pF | 91kΩ     | 120pF |

| 32000         | 47kΩ     | 220pF | 47kΩ     | 150pF |

| 38400 *       | 47kΩ     | 180pF | 47kΩ     | 120pF |

| 64000 *       | 56kΩ     | 100pF | 51kΩ     | 68pF  |

\*  $V_{DD} \geq 4.5V$

Note: In all cases the value of R1 should not be less than 20.0 kΩ, and the calculated value of C1 includes calculated parasitic capacitance.

2. R3, R4 and C6 form the gain components for the Rx Input signal. R3 should be chosen as required by the signal input level.

3. The values chosen for C2 and C3 (including stray capacitance), should be suitable for the applied  $V_{DD}$  and the frequency of X1.

As a guide : C2 = C3 = 33pF at 1.0MHz falling to 18pF at the maximum frequency.

At 3.0 volts, C2 = C3 = 33pF falling to 18pF at 5.0MHz. The equivalent series resistance of X1 should be less than 2.0kΩ falling to 150Ω at the maximum frequency. Stray capacitance on the Xtal/Clock circuit pins must be minimized.

4. C7 and C8 should both be .015μF for a data rate of 8kbps, and inversely proportional to the data rate for other data rates, e.g. .030μF at 4kbps, .0018μF at 64kbps.

5. The MX589 can operate correctly with Xtal/Clock frequencies between 1.0MHz and 8.2MHz ( $V_{DD} = 5.0V$ ) and 1.0MHz to 5.0MHz ( $V_{DD} = 3.0V$ ) see Table 1 for examples. For best results, a crystal oscillator design should drive the clock inverter input with signal levels of at least 40% of  $V_{DD}$ , peak to peak. Tuning fork crystals generally cannot meet this requirement. To obtain crystal oscillator design assistance, consult your crystal manufacturer. Operation of this device without a Xtal or Clock input may cause device damage.

## 4. General Description

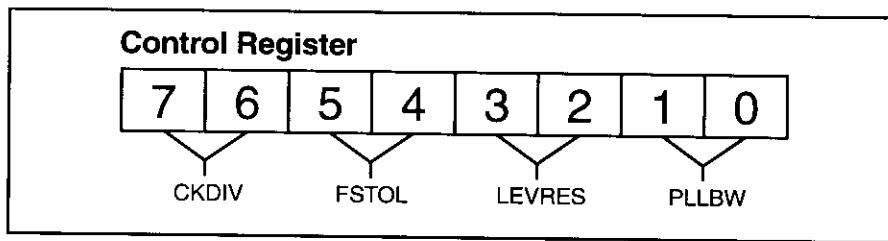

### 4.1 Clock Oscillator Divider

The Tx and (nominal) Rx data rates are determined by division of the frequency present at the Xtal pin, which may be generated by the on-chip Xtal oscillator or derived from an external source. Any Xtal/clock frequency in the range 1.0MHz to 5.0MHz for  $V_{DD} = 3.0V$ , or 1.0 MHz to 8.2MHz for  $V_{DD} = 5.0V$  may be used, depending on the desired data rate.

The division ratio is controlled by the logic level inputs on ClkDivA and ClkDivB pins, as shown in Table 1, together with an indication of how various standard data rates may be derived from common μP Xtal frequencies.

$$\text{Data Rate} = \frac{\text{Xtal/Clock Frequency}}{\text{Division Ratio (Clk Div A/B)}}$$

|           |           | Xtal/Clock Frequency (MHz) |           |            |            |           |

|-----------|-----------|----------------------------|-----------|------------|------------|-----------|

|           |           | 8.192                      | 4.9152    | 4.096      | 2.4576     | 2.048     |

|           |           |                            |           | (12.288/3) | (12.288/5) | (6.144/3) |

| Inputs    |           | Division Ratio             |           |            |            |           |

| ClikDiv A | ClikDiv B | Xtal Freq.                 | Data Rate |            |            |           |

| 0         | 0         | 128                        | 64000*    | 38400*     | 32000      | 19200     |

| 0         | 1         | 256                        | 32000     | 19200      | 16000      | 16000     |

| 1         | 0         | 512                        | 16000     | 9600       | 8000       | 8000      |

| 1         | 1         | 1024                       | 8000      | 4800       | 4000       | 4000      |

\*  $V_{DD} \geq 4.5V$

Table 1: Clock/Data Rates

**Note:** The device operation is not guaranteed above 64kbps or below 4kbps at the relevant supply voltage.

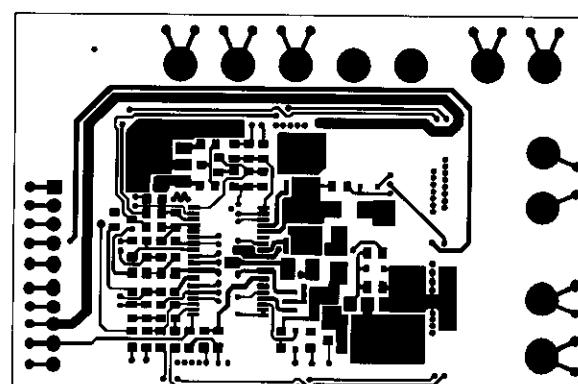

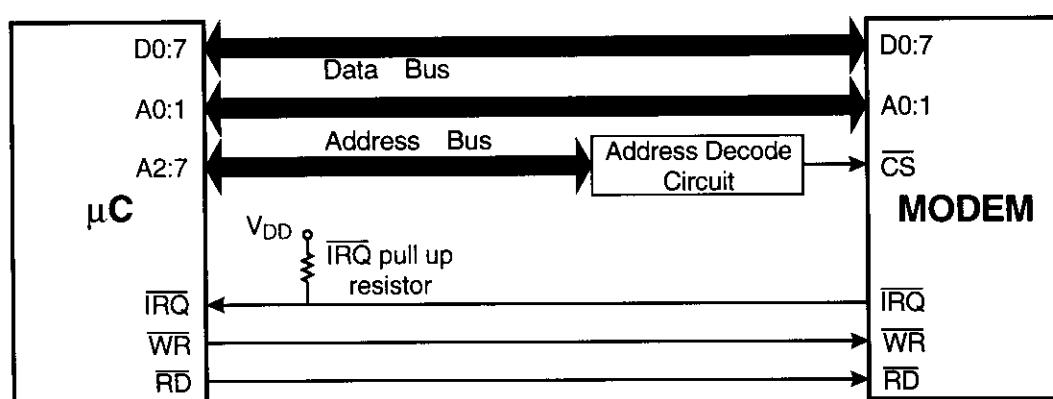

Figure 4: Minimum  $\mu$ Controller System Connections

## 4.2 Receive

### 4.2.1 Rx Signal Path Description

The function of the Rx circuitry is to:

1. Set the incoming signal to a usable level.

2. Clean the signal by filtering.

3. Provide DC level thresholds for clock and data extraction.

4. Provide clock timing information for data extraction and external circuits.

5. Provide Rx data in a binary form.

6. Assess signal quality and provide Signal-to-Noise information.

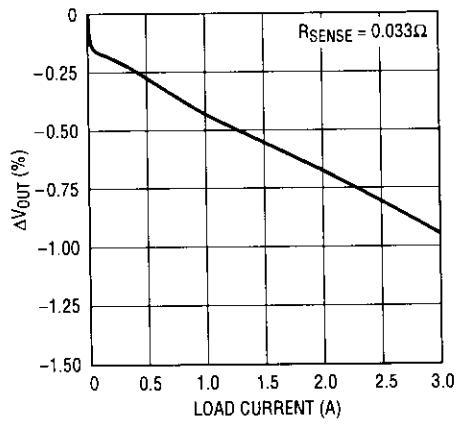

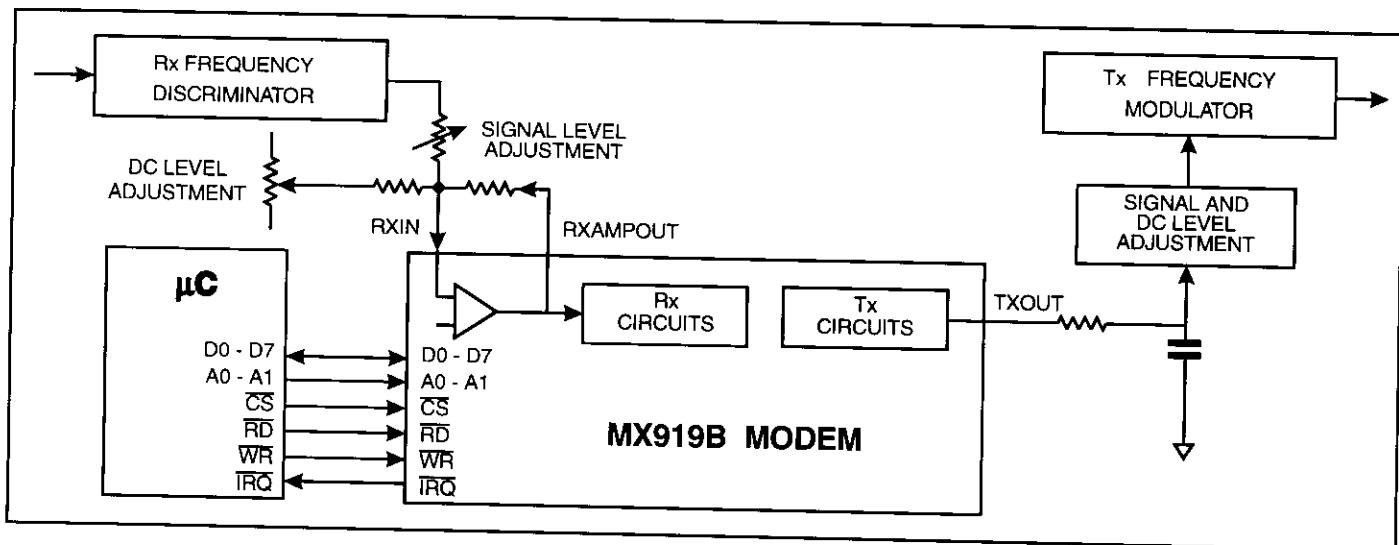

The output of the radio receiver's Frequency Discriminator should be fed to the MX589's Rx Filter by a suitable gain and DC level adjusting circuit. This circuit can be built with external components around the on-chip Rx Input Amplifier. The gain should be set so that the signal level at the Rx Feedback pin is nominally 1V peak to peak (for  $V_{DD} = 5.0V$ ) centered around  $V_{BIAS}$  when receiving a continuous 1111000011110000.. data pattern.

Positive going signal excursions at Rx Feedback pin will produce a logic 0 at the Rx Data Output. Negative going excursions will produce a logic 1.

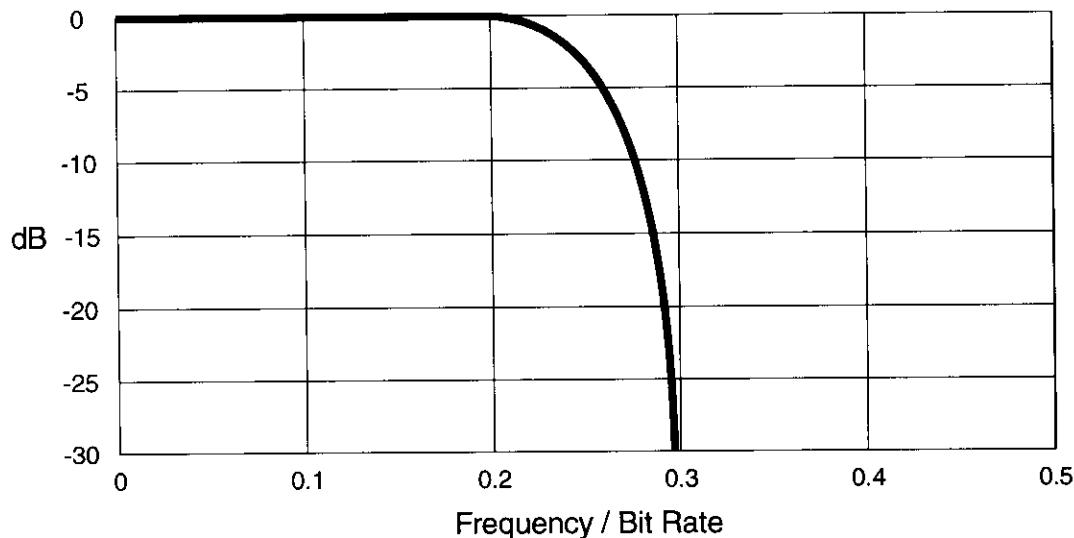

The received signal is fed through the lowpass Rx Filter, which has a -3dB corner frequency of 0.56 times the data bit-rate, before being applied to the Level Measure and Clock and Data extraction blocks.

The Level Measuring block consists of two voltage detectors, one of which measures the amplitude of the positive parts of the received signal. The other measures the amplitude of the negative portions. (Positive refers to signal levels higher than  $V_{DD}/2$ , and negative to levels lower than  $V_{DD}/2$ .) External capacitors are used by these detectors, via the Doc1 &

Doc2 pins, to form voltage hold or integrator circuits. These two levels are then used to establish the optimum DC level decision-thresholds for the Clock and Data extraction, depending upon the Rx signal amplitude and any DC offset.

#### 4.2.2 Rx Circuit Control Modes

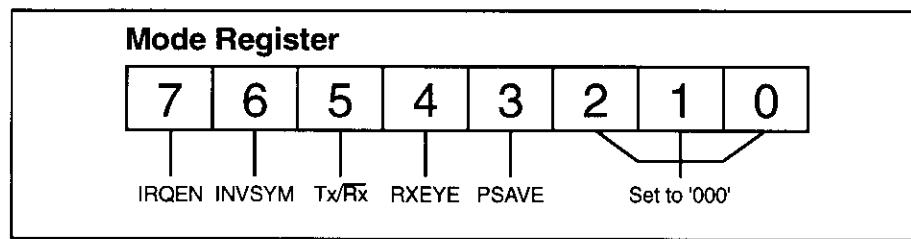

The operating characteristics of the Rx Level Measurement and Clock Extraction circuits are controlled, as shown in Table 2, by logic level inputs applied to the PLLacq, Rx HOLD and RxDCacq pins to suit a particular application, or to cope with changing reception conditions.

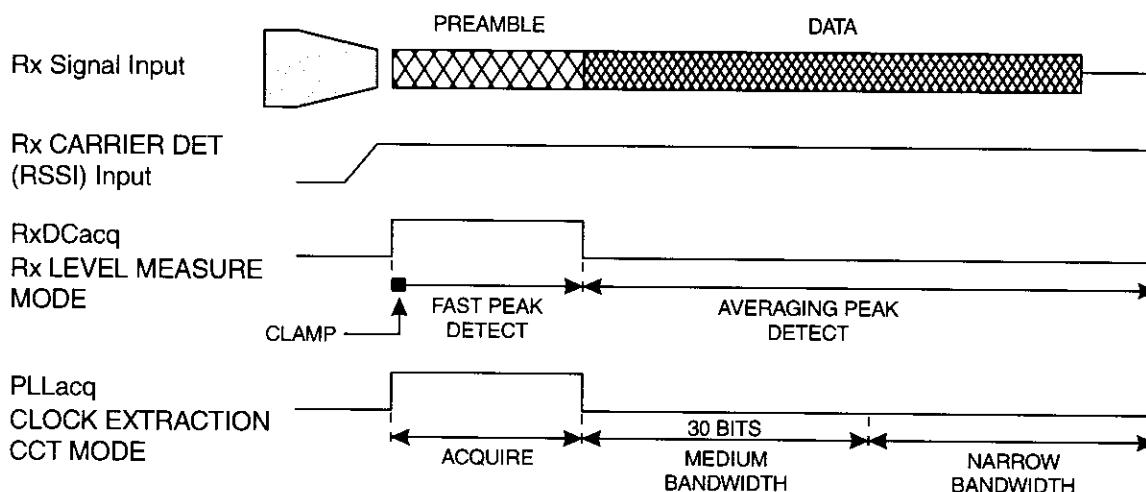

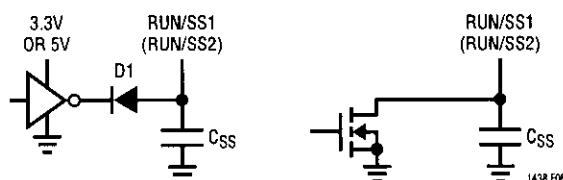

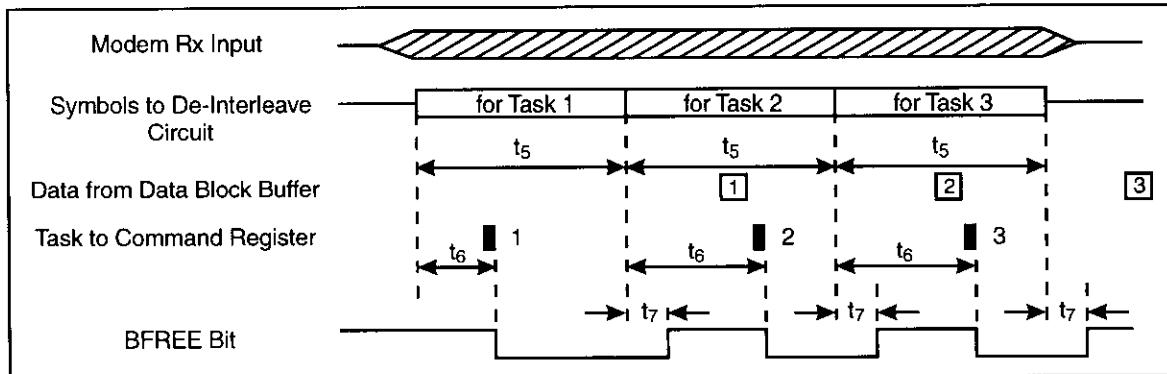

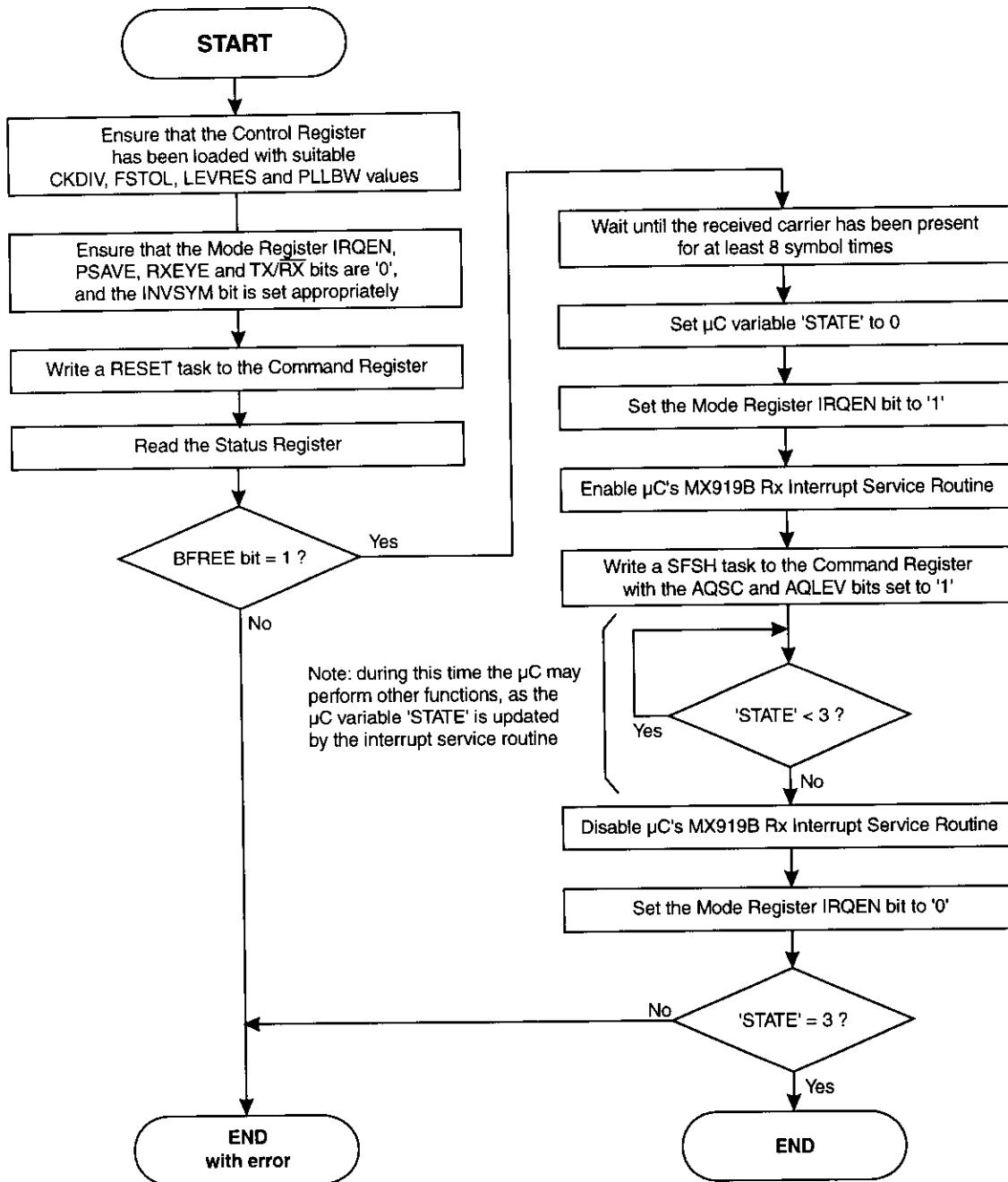

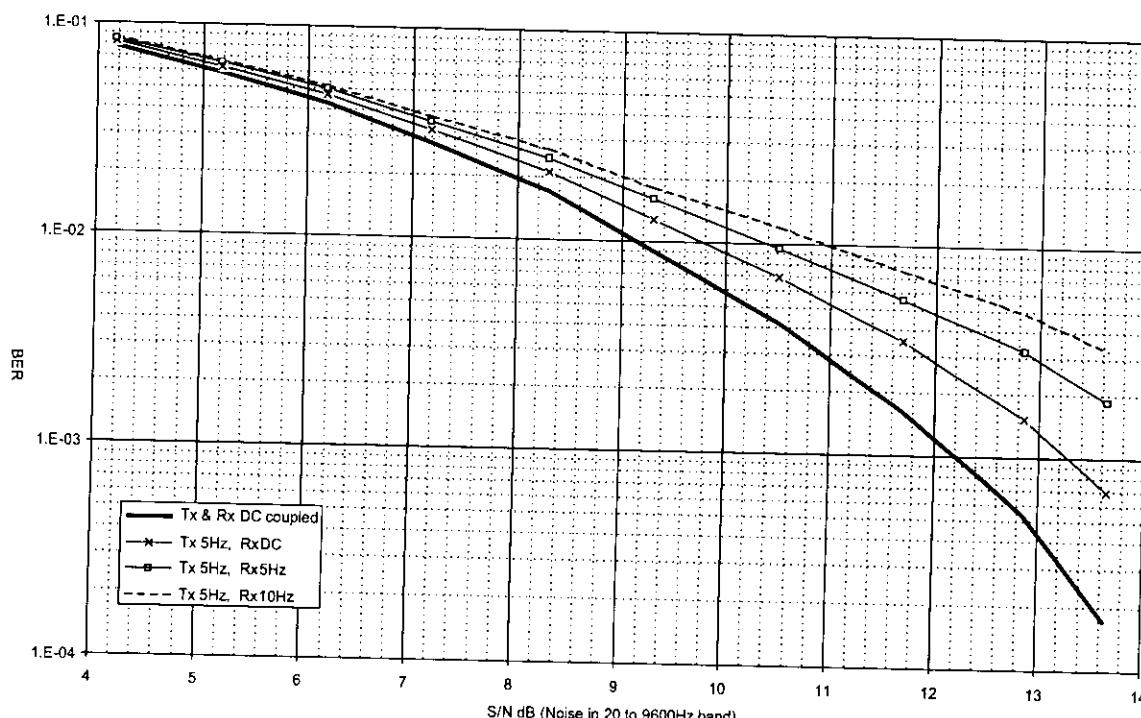

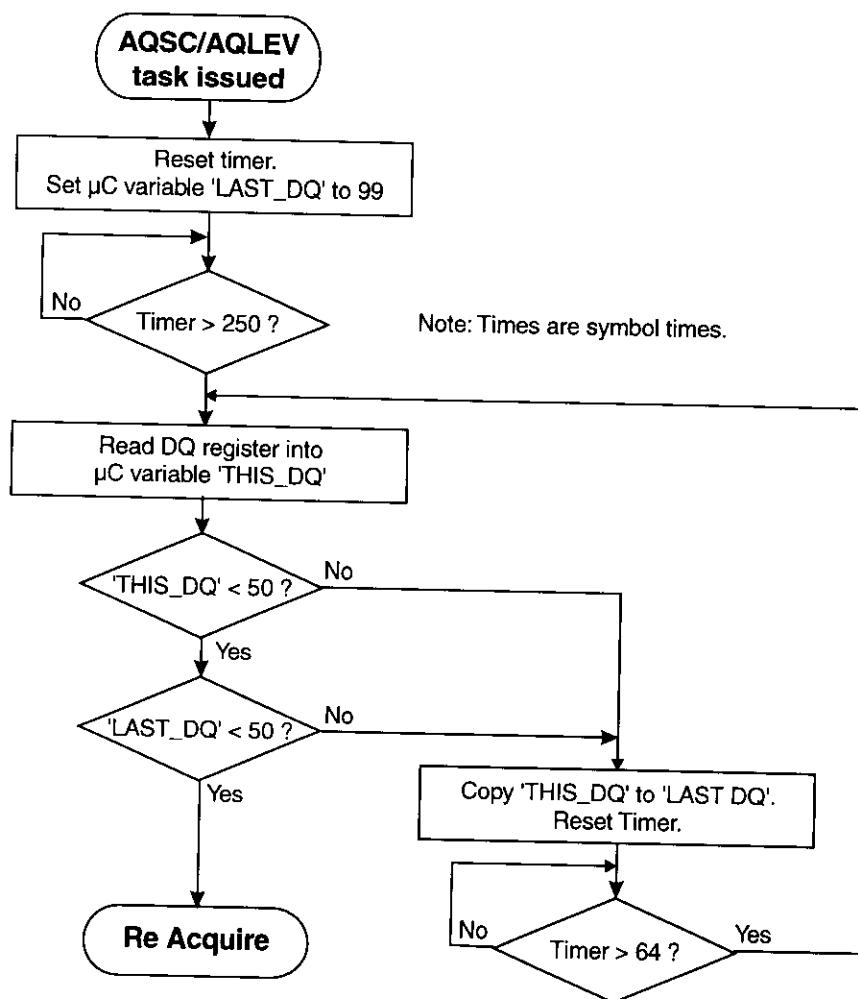

With reference to Figure 5, the Rx Mode Control diagram:

In general, a data transmission will begin with a preamble, for example, 1100110011001100, to allow the receive modem to establish timing and level-lock as quickly as possible. After the Rx carrier has been detected, and during the time that the preamble is expected, the RxDCacq and PLLacq Inputs should be switched from a logic 0 to a logic 1 so that the Level Measuring and Clock Extraction modes are operated and sequenced as shown.

The Rx HOLD input should normally be held at a logic 1 while data is being received, but may be driven to a logic 0 to freeze the Level Measuring Clock Extraction circuits during a fade. If the fade lasts for less than 200 bit periods, normal operation can be resumed by returning the Rx HOLD input to a logic 1 at the end of the fade. For longer fades, it may be better to reset the Level Measuring circuits by placing the RxDCacq to a logic 1 for 10 to 20 bit periods.

Rx HOLD has no effect on the level Measuring circuits while RxDCacq is at a logic 1, and has no effect on the PLL while PLLacq is at a logic 1.

A logic 0 on Rx HOLD does not disable the Rx Clock output, and the Rx Data Extraction and S/N Detector circuits will continue to operate.

Figure 5: Rx Mode Control Diagram

| PLLacq  | Rx HOLD | PLL Action              |                                                                                                                                                                                                                                                                                                                            |

|---------|---------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | 1       | Acquire                 | Sets the PLL bandwidth wide enough to allow a lock to the received signal in less than 8 zero crossings. This mode will operate as long as PLLacq is a logic 1                                                                                                                                                             |

| 1 to 0  | 1       | Medium Bandwidth        | The correction applied to the extracted clock is limited to a maximum of $\pm 1/16$ th bit-period for every two received zero crossings. The PLL operates in this mode for a period of about 30 bits immediately following a 1 to 0 transition of PLLacq input, provided that the Rx HOLD Input is a logic 1.              |

| 0       | 1       | Narrow Bandwidth        | The correction applied to the extracted clock is limited to a maximum of $\pm 1/64$ th bit-period for every two received zero crossings. The PLL operates in this mode whenever the Rx HOLD Input is a logic 1 and PLLacq has been a logic 0 for at least 30 bit periods (after Medium Bandwidth operation for instance)   |

| 0       | 0       | Hold                    | The PLL feedback loop is broken, allowing the Rx Clock to freewheel during signal fade periods.                                                                                                                                                                                                                            |

| RxDcacq | Rx HOLD | Rx Level Measure Action |                                                                                                                                                                                                                                                                                                                            |

| 0 to 1  | X       | Clamp                   | Operates for one bit-time after a 0 to 1 transition of the RxDcacq input. The external capacitors are rapidly charged towards a voltage mid way between the received signal input level and $V_{BIAS}$ with the charge time-constant being of the order of 0.5 bit-time.                                                   |

| 1       | X       | Fast Peak Detect        | The voltage detectors act as peak detectors, one capacitor is used to capture the positive-going signal peaks of the Rx Filter output signal and the other capturing the negative-going peaks. The detectors operate in this mode whenever the RxDcacq input is at a logic 1 except for the initial 1-bit Clamp Mode time. |

| 0       | 1       | Averaging Peak Detect   | Provides a slower but more accurate measurement of the signal peak amplitudes.                                                                                                                                                                                                                                             |

| 0       | 0       | Hold                    | The capacitor charging circuits are disabled so that the outputs of the voltage detectors remain substantially at the last readings (discharging very slowly [time-constant approx. 2,000 bits] towards $V_{BIAS}$ )                                                                                                       |

X = Don't care

**Table 2: PLL and Rx Level Measurement Operational Modes**

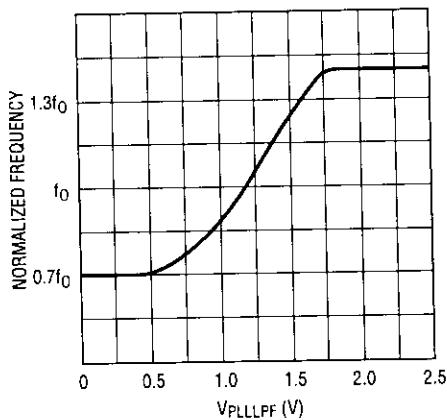

#### 4.2.3 Rx Clock Extraction

Synchronized by a PLL circuit to zero-crossings of the incoming data, the Rx Clock Extraction circuitry controls the Rx Clock output. The Rx Clock is also used internally by the Data Extraction circuitry. The PLL parameters can be varied by the Rx Circuit Control inputs PLLacq and Rx HOLD to operate in one of four PLL modes as described in Table 2

#### 4.2.4 Rx Data Extraction

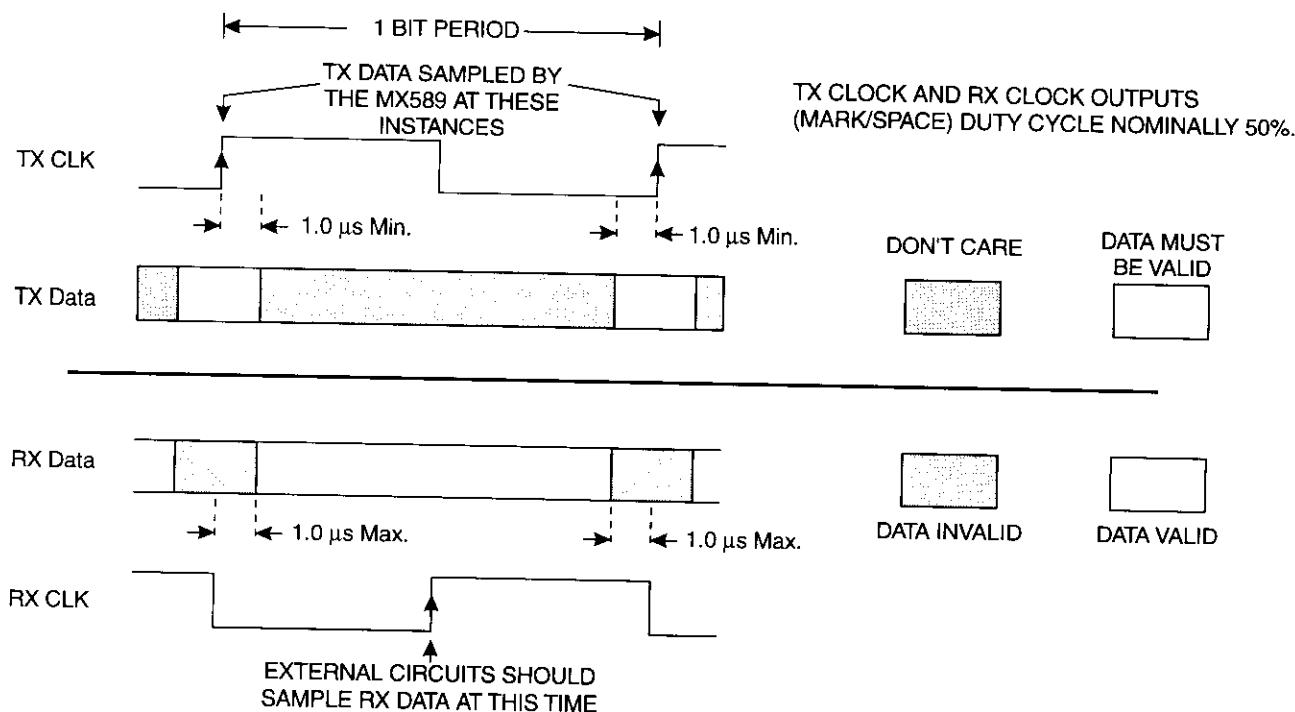

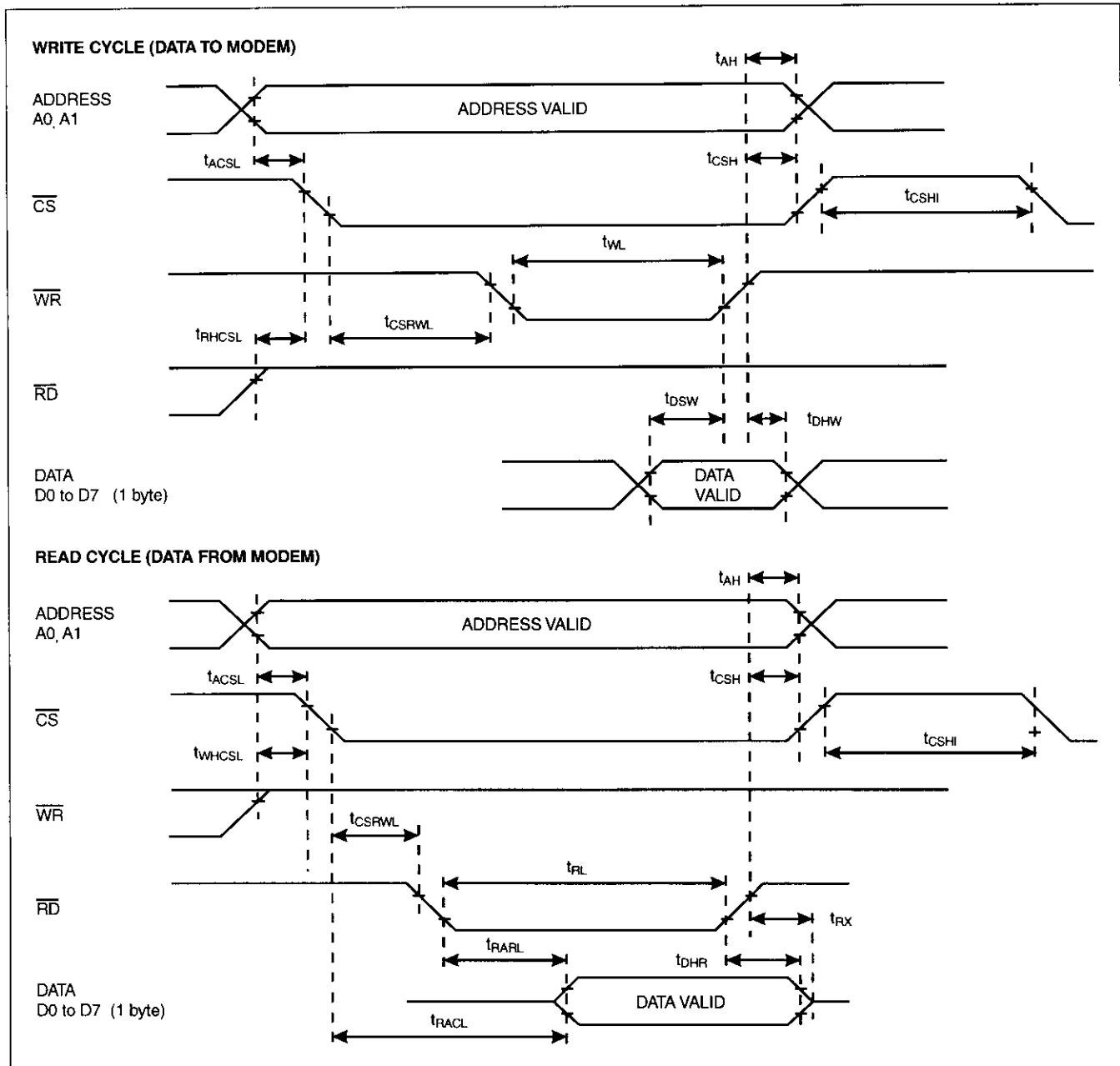

The Rx Data Extraction circuit decides whether each received bit is a 1 or 0 by sampling the received signal, after filtering, and comparing the sample values to an adaptive threshold derived from the Level Measuring circuit. This threshold is adapted from bit to bit to compensate for intersymbol interference caused by the bandlimiting of the overall transmission path and the Gaussian premodulation filter. The extracted data is output from the Rx Data pin, and should be sampled externally on the rising edge of the Rx CLK.

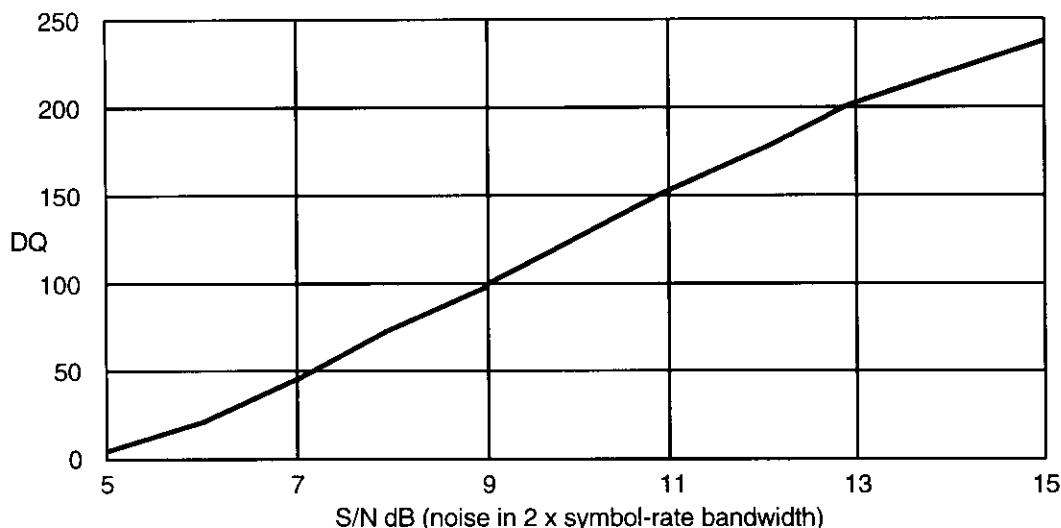

#### 4.2.5 Rx S/N Detection

The Rx S/N Detector system classifies the incoming zero-crossings as GOOD or BAD depending upon the time when each crossing actually occurs with respect to its expected time as determined by the Clock Extraction PLL. This information is then processed to provide a logic level output at the Rx S/N pin. A high level indicates a series of GOOD crossings; a low level indicates a BAD crossing.

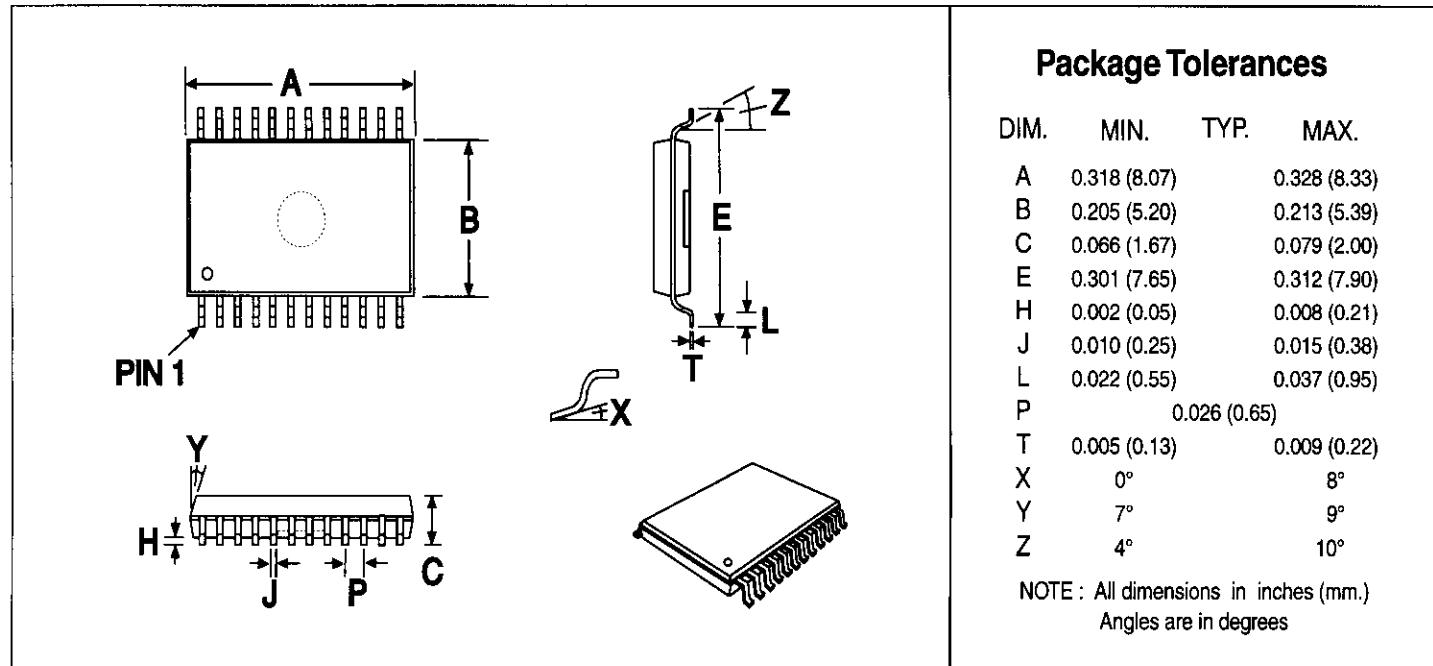

By averaging this output it is possible to derive a measure of the Signal-to-Noise-Ratio and therefore the Bit-Error-Rate of the received signal.

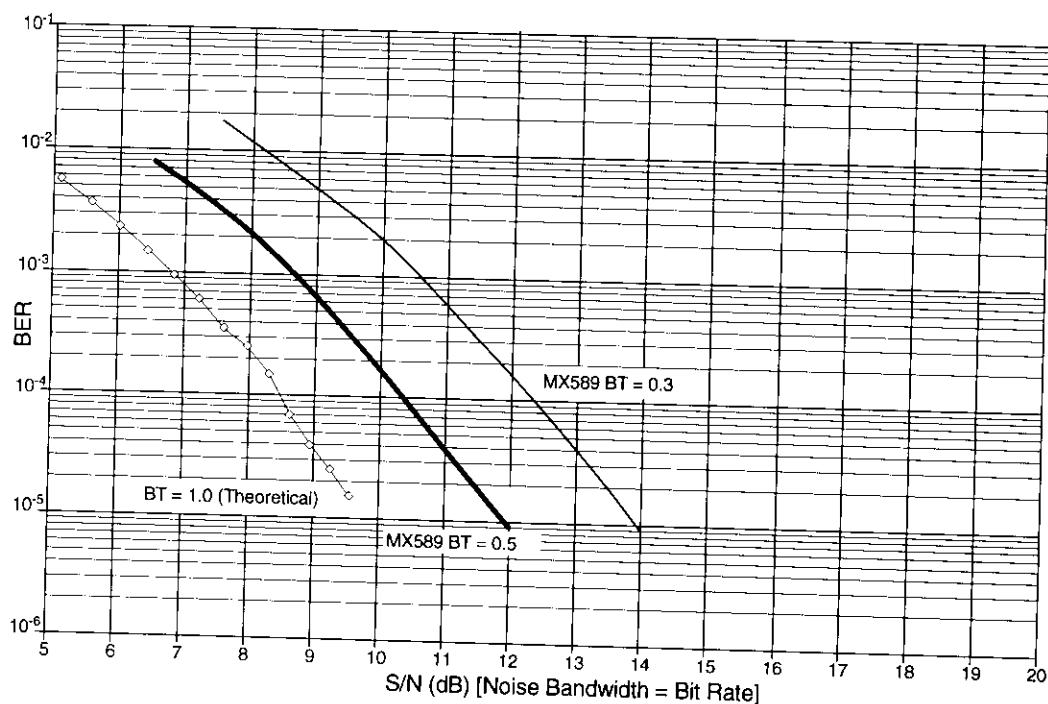

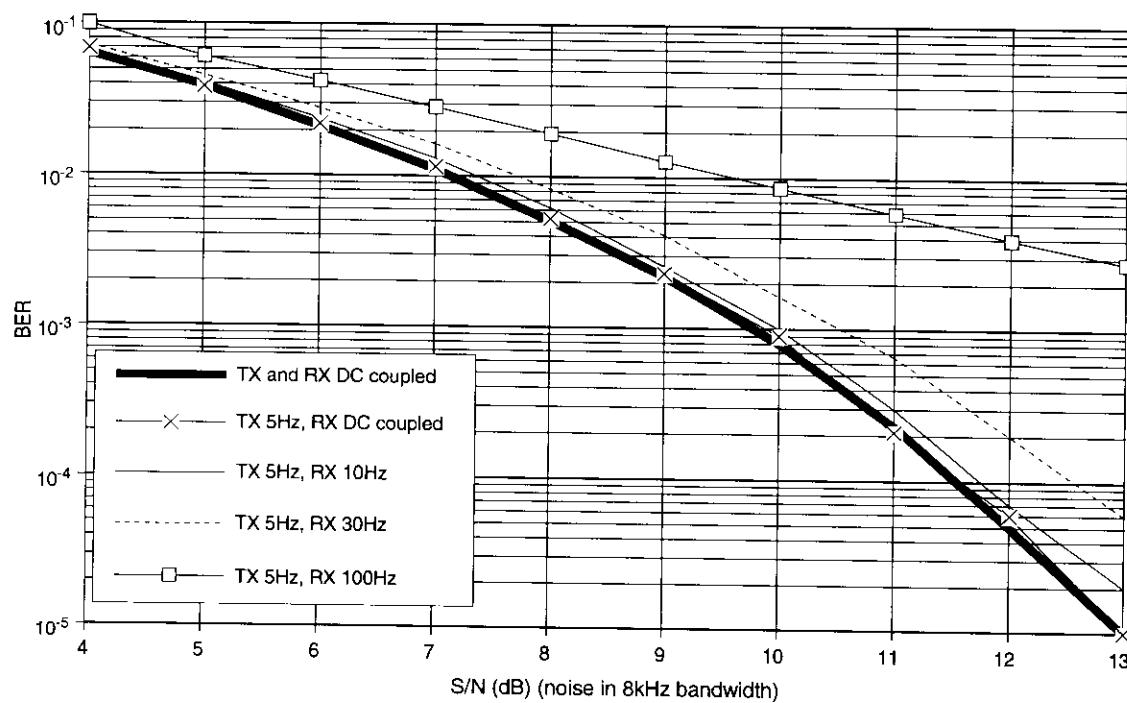

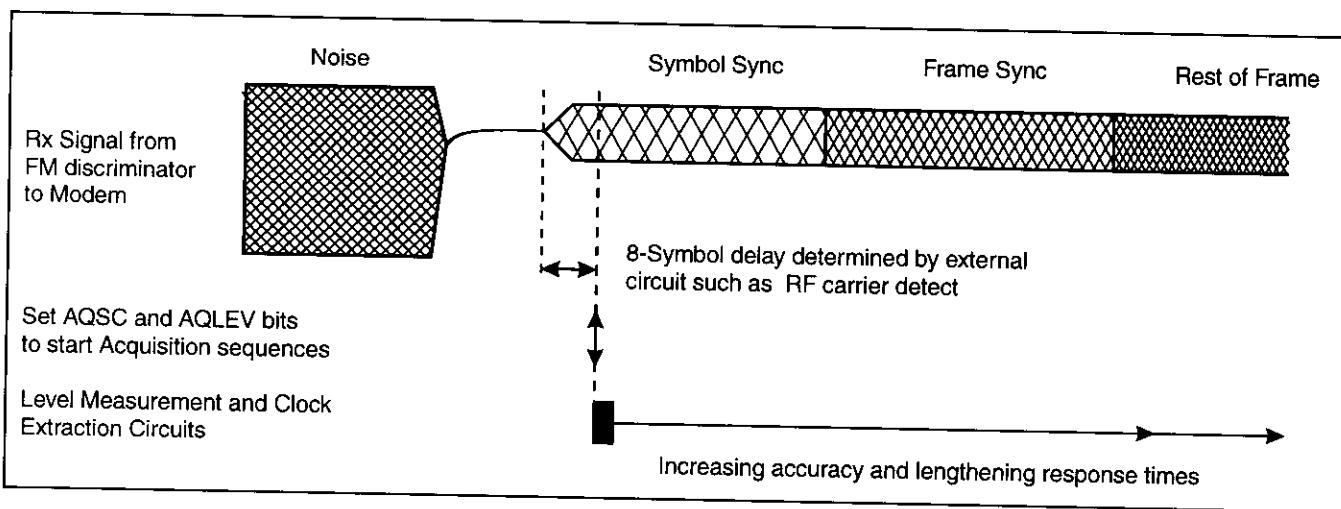

Figure 6: Typical Bit-Error-Rate Performance

#### 4.2.6 Rx Signal Quality

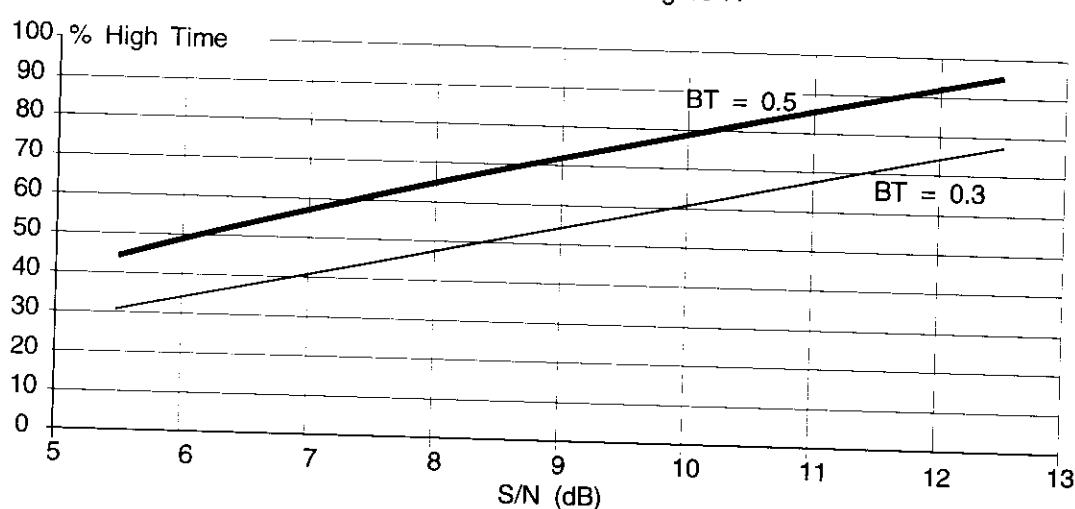

The effect of input Rx signal quality on the Rx S/N output is shown in Figure 7.

Figure 7: Typical Rx S/N Output High time (%) vs Input S/N

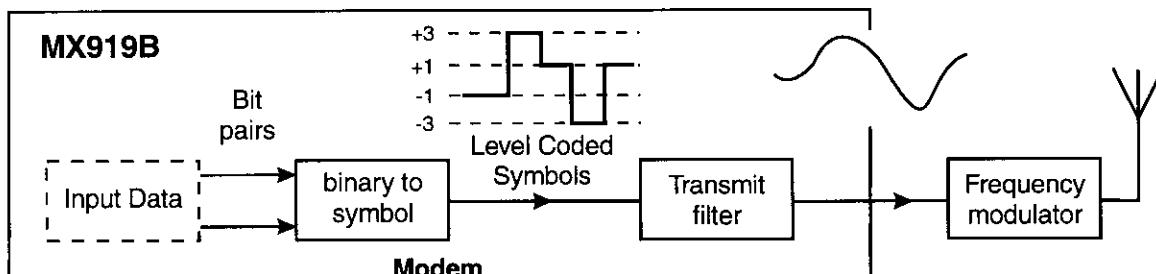

## 4.3 Transmit

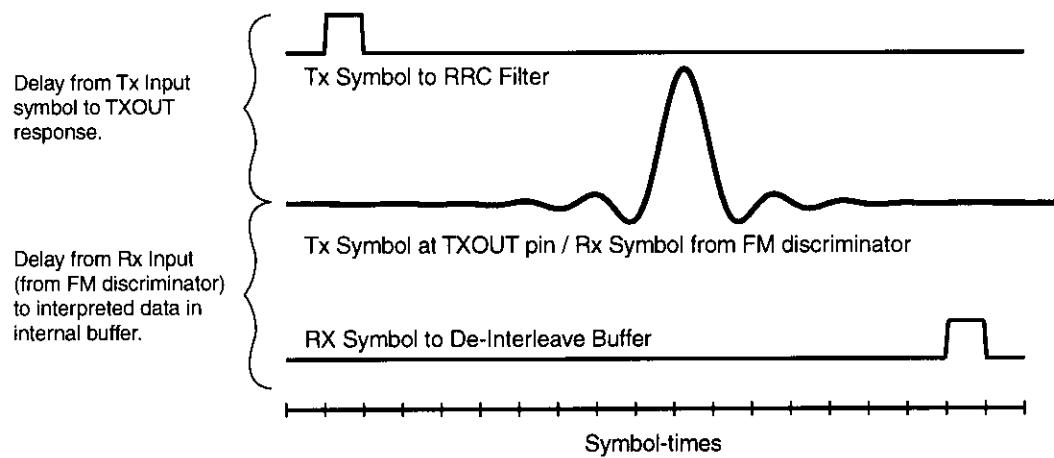

### 4.3.1 Tx Signal Path Description

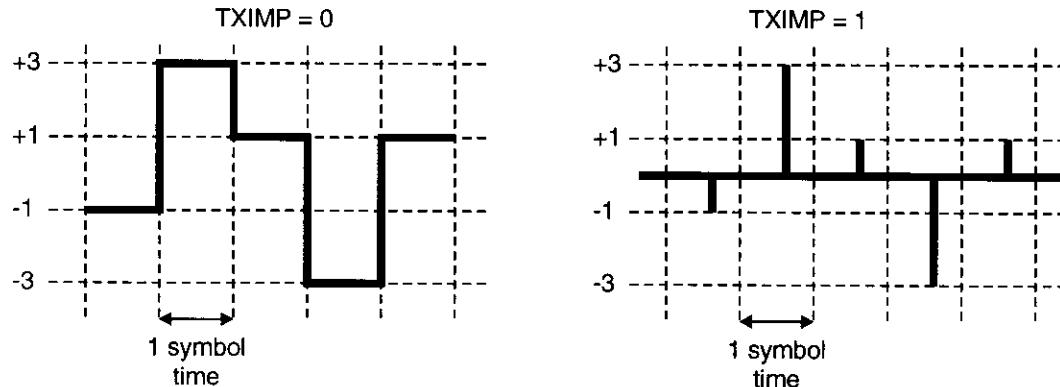

The binary data applied to the Tx Data input is retimed within the chip on each rising edge of the Tx Clock and then converted to a 1-volt peak-to-peak binary signal centered about  $V_{BIAS}$  (for  $V_{DD} = 5.0V$ )

If the Tx Enable input is high, then this internal binary signal will be connected to the input of the lowpass Tx Filter, and the output of the filter connected to the Tx Out pin.

| Tx Enable | Tx Filter Input                  | Tx Out Pin                  |

|-----------|----------------------------------|-----------------------------|

| 1         | $V_{DD}/5$ V <sub>P,P</sub> Data | Filtered Data               |

| 0         | $V_{BIAS}$                       | $V_{BIAS}$ via $500k\Omega$ |

A low input to the Tx Enable will connect the input of the Tx Filter to  $V_{BIAS}$ , and disconnect the Tx Out pin from the filter, connecting it instead to  $V_{BIAS}$  through a high resistance (nominally  $500k\Omega$ ).

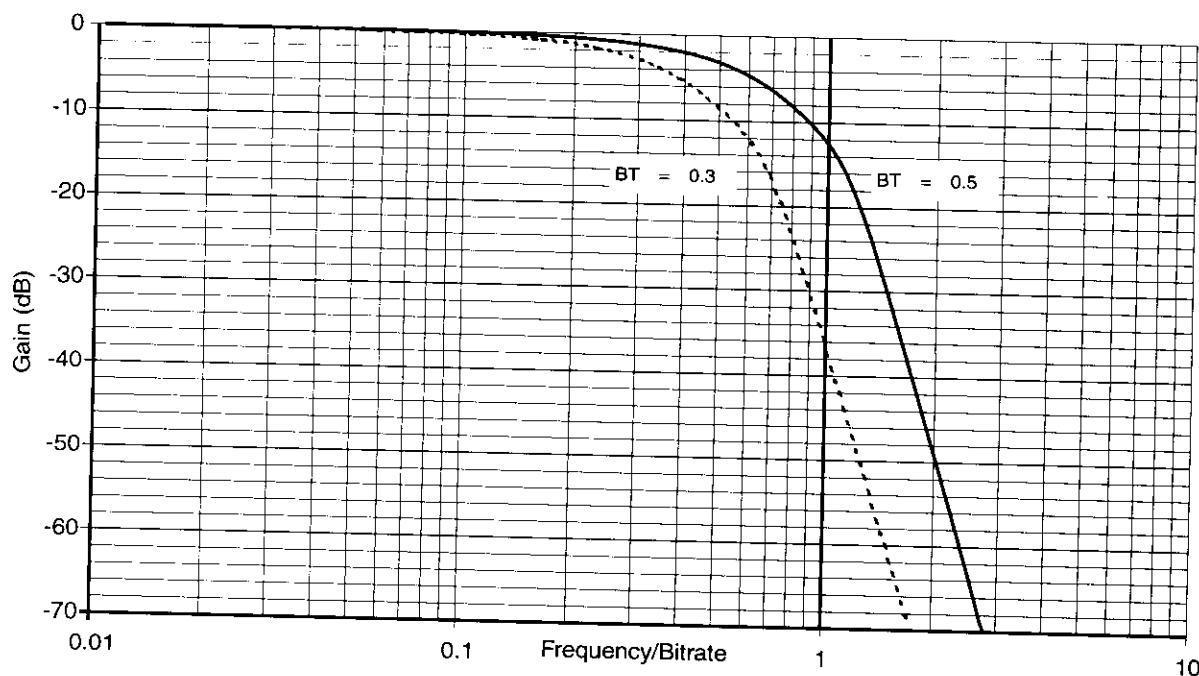

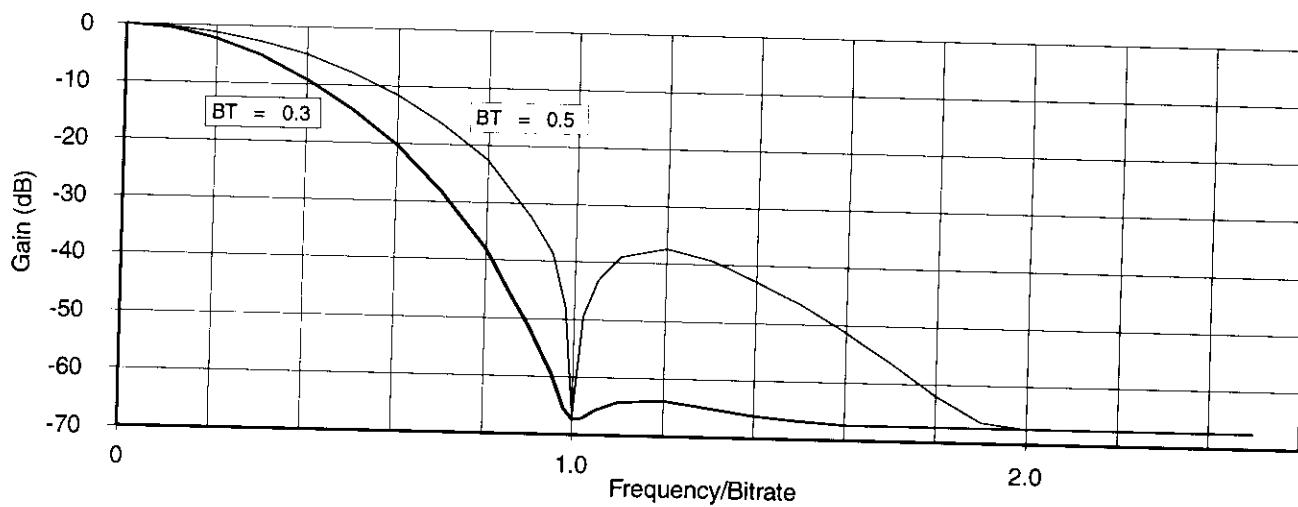

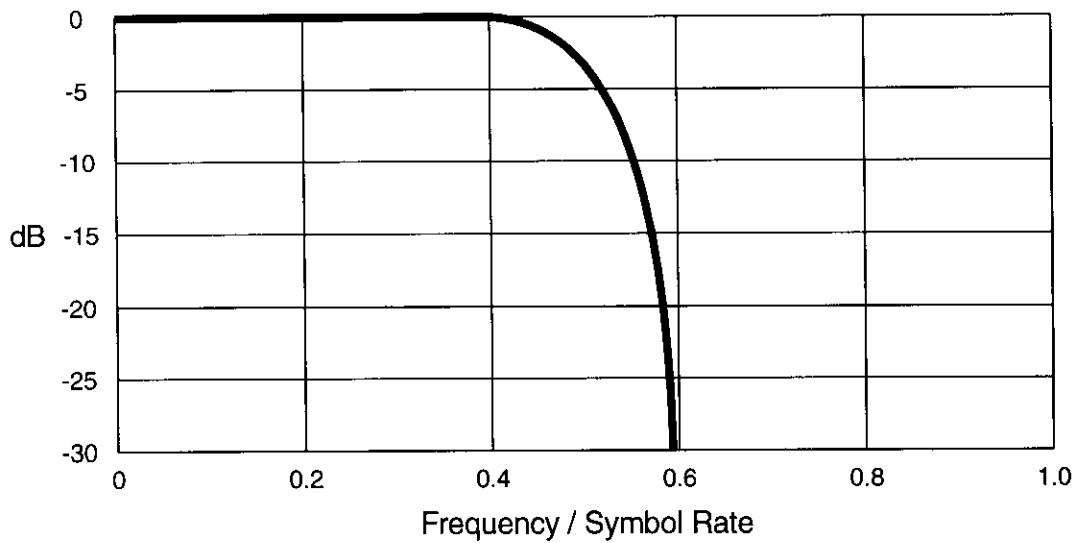

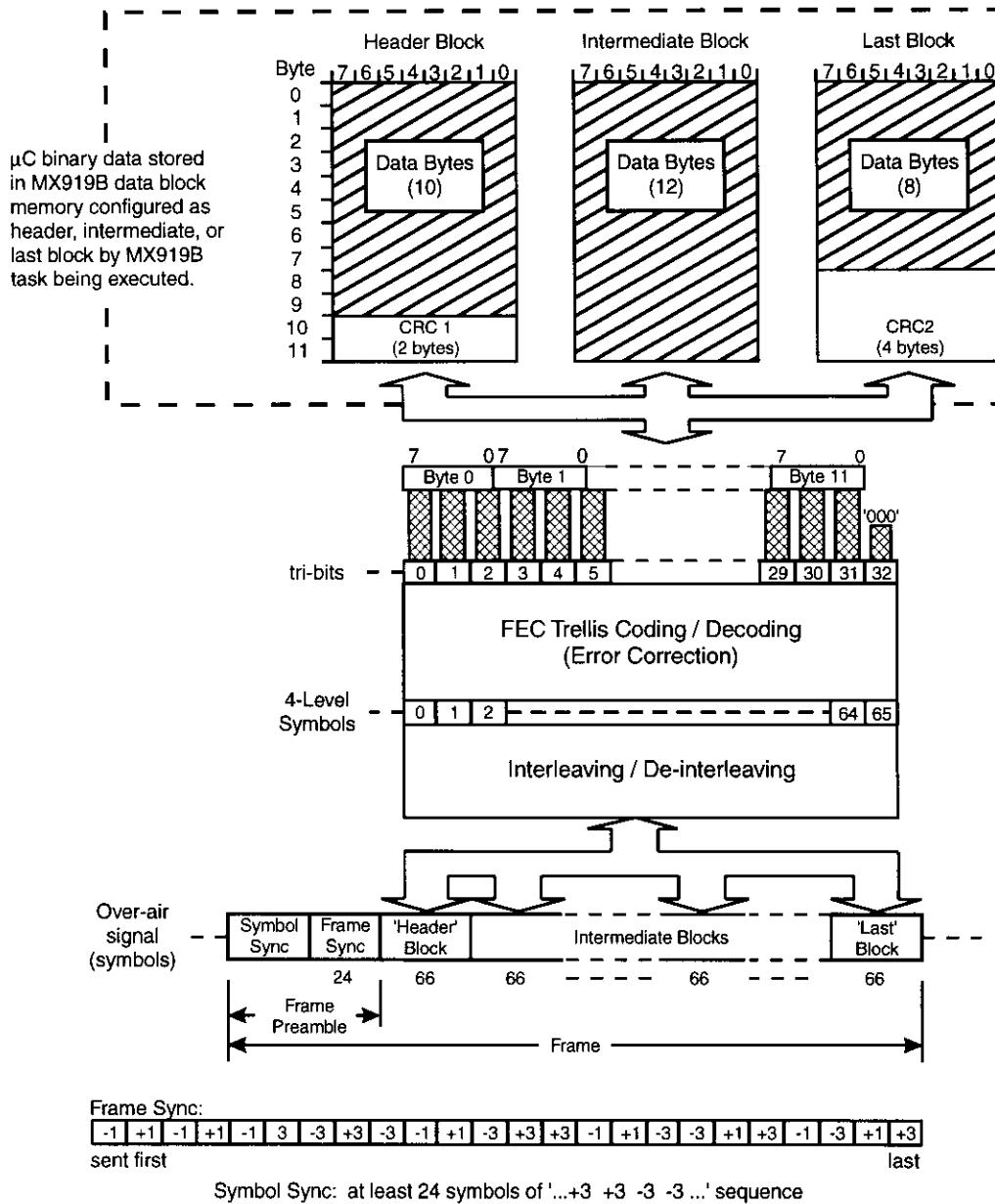

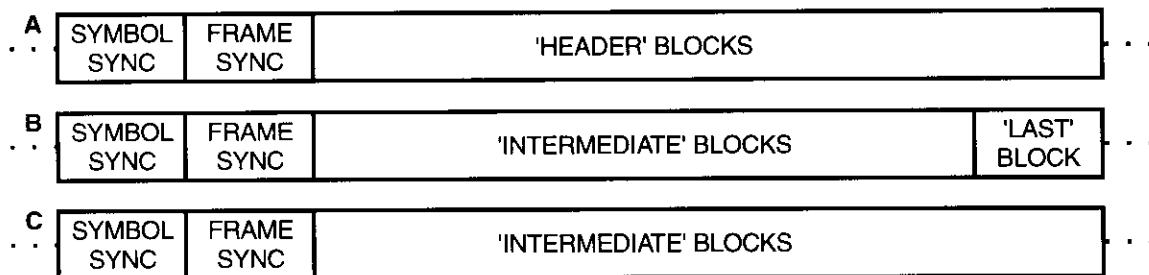

The Tx Filter has a lowpass frequency response, which is approximately gaussian in shape as shown in Figure 9, to minimize amplitude and phase distortion of the binary signal while providing sufficient attenuation of the high frequency components which would otherwise cause interference into adjacent radio channels. The actual filter bandwidth to be used in any particular application will be determined by the overall system requirements. The attenuation-vs-frequency response of the transmit filtering provided by the MX589 have been designed to meet the specifications for most GMSK modem systems, having a -3dB bandwidth switchable between 0.3 and 0.5 times the data bit-rate (BT).

**Note:** An external RC network is required between the Tx Out pin and the input to the Frequency Modulator (see Figure 2 and Figure 3). This network, which can form part of any DC level shifting and gain adjustment circuitry, forms an important part of the transmit signal filtering. The ground connection to capacitor C1 should be positioned to give maximum attenuation of high-frequency noise into the modulator.

The signal at Tx Out is centered around  $V_{BIAS}$ , going positive for logic 1 (high) level inputs to the Tx Data input and negative for logic 0 (low) inputs.

When the transmit circuits are put into a powersave mode (by a logic 1 to the Tx PS pin) the output voltage of the Tx Filter will go to  $V_{SS}$ . When power is subsequently restored to the Tx Filter, its output will take several bit-times to settle. The Tx Enable input can be used to prevent these abnormal voltages from appearing at the Tx Out pin.

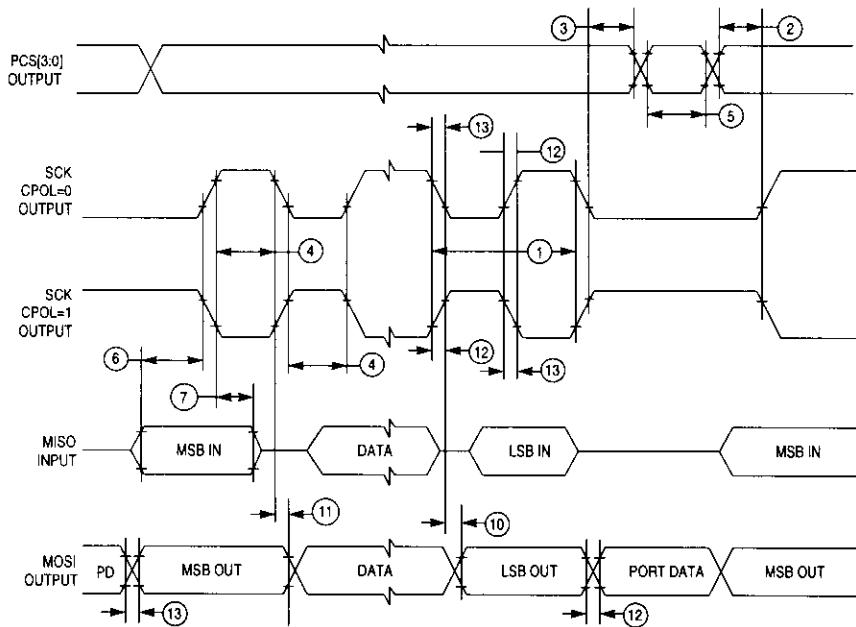

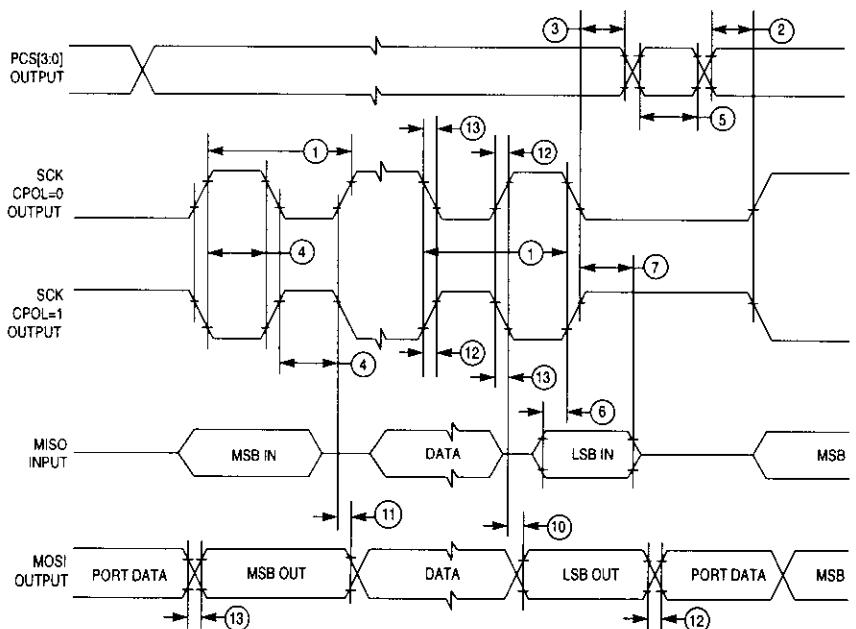

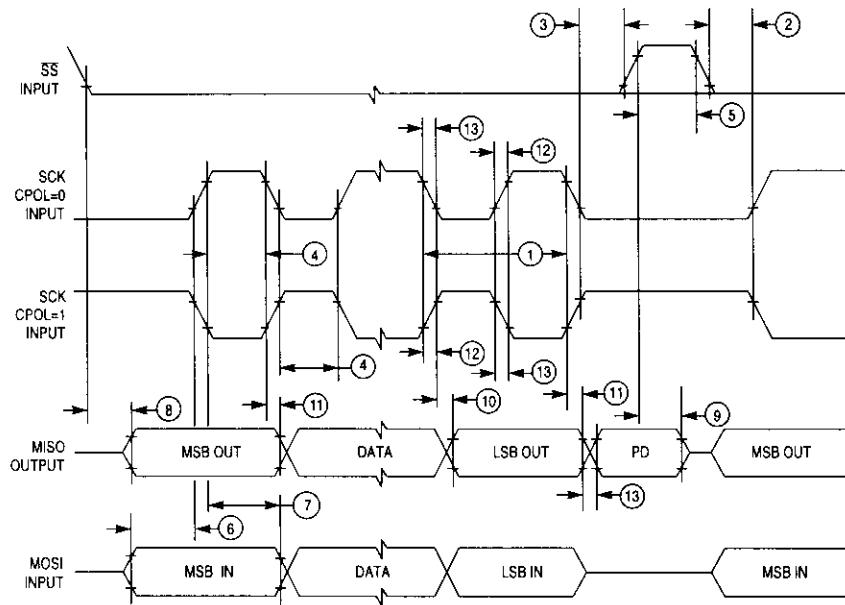

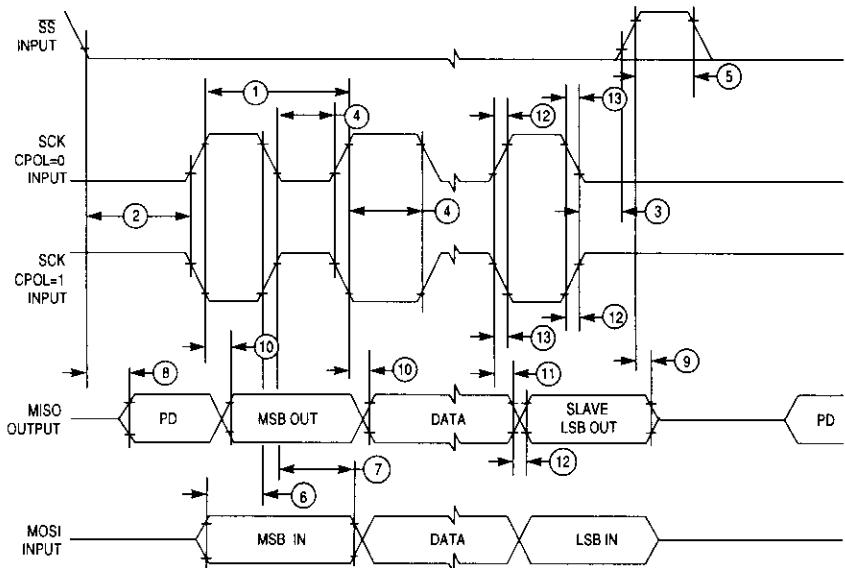

Figure 8: Rx and Tx Clock Data Timings

Figure 9: Tx Filter Response

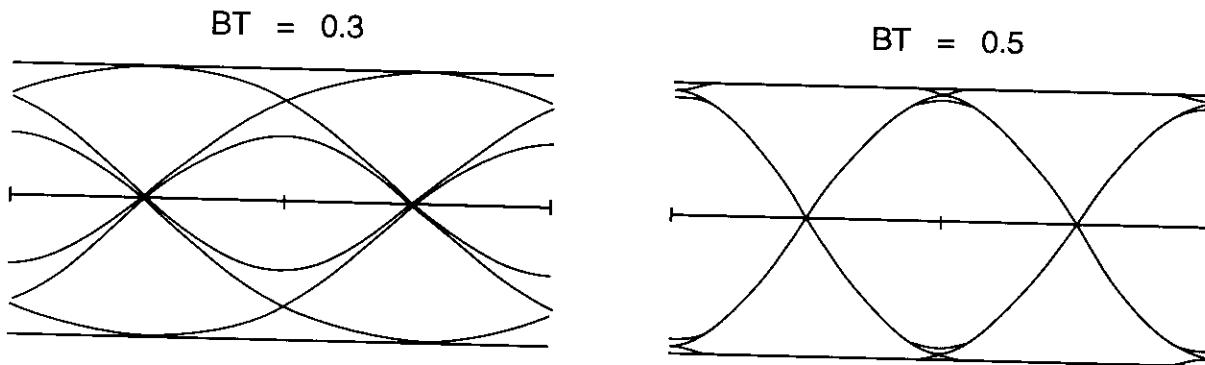

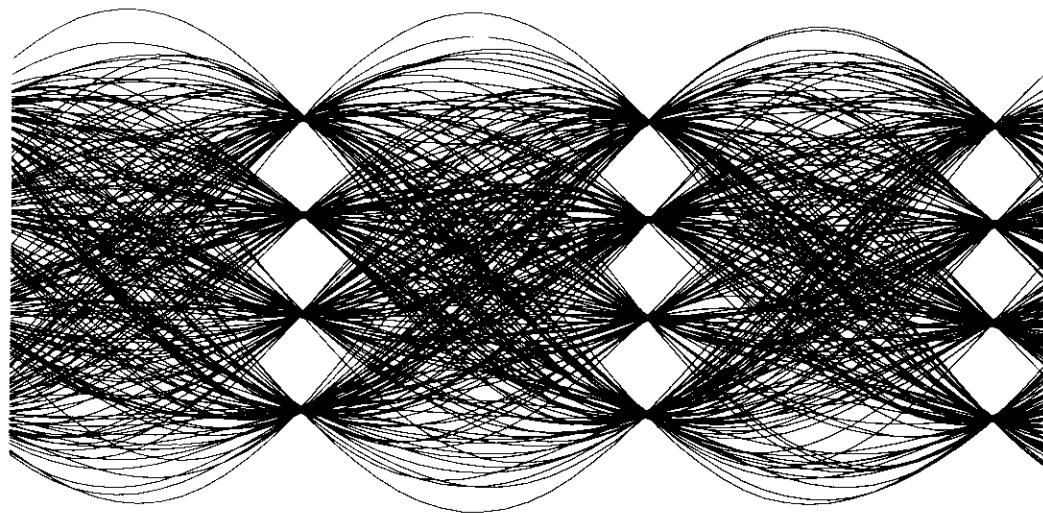

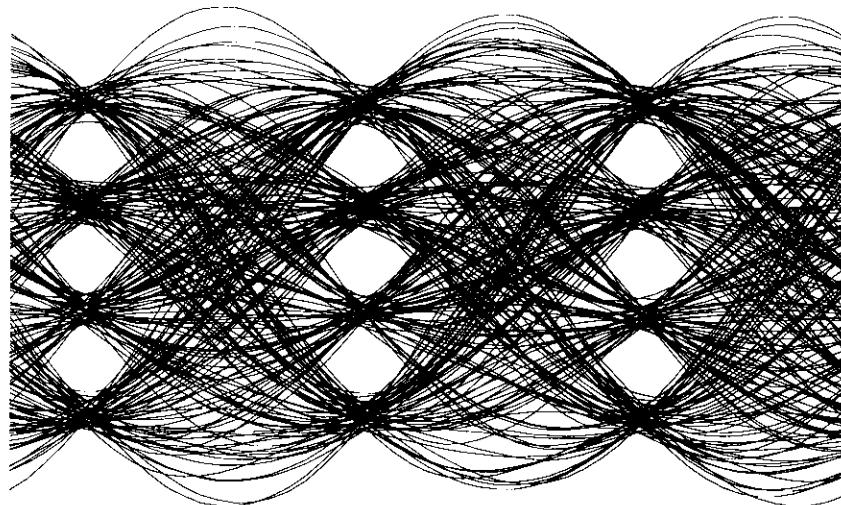

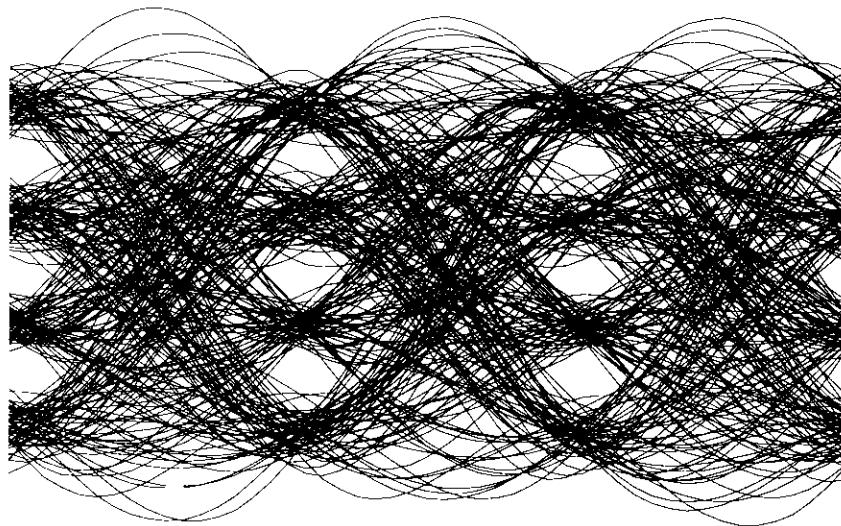

Figure 10: Typical Transmit Eye Patterns

Figure 11: Tx Output spectrum (Random Data)

## 4.4 Data Formats

The receive section of the MX589 works best with data which has a reasonably random structure --the data should contain approximately the same number of ones as zeroes with no long sequences (>100 bits) of consecutive ones or zeroes. Also, long sequences (>100 bits) of 10101010 ... patterns should be avoided.

For this reason, it is recommended that data is made random in some manner before transmission, for example by exclusive-ORing it with the output of a binary pseudo-random pattern generator.

Where data is transmitted in bursts, each burst should be preceded by a preamble designed to allow the receive modem to establish timing and level lock as quickly as possible. This preamble for BT = 0.3 should be at least 16 bits long, and should preferably consist of alternating pairs of ones and zeroes i.e. 110011001100 ....; the eye of pattern 10101010 .... has the most gradual slope and will yield poor peak levels for the Rx circuits. For BT = 0.5 the eye pattern of 10101010... has reduced intersymbol interference and may be used as the preamble (DC Acq pin should be held high during preamble). See Fig. 6.

## 4.5 Acquisition and Hold Modes

The RxDCacq and PLLacq inputs must be pulsed High for about 16 bits at the start of reception to ensure that the DC measurement and timing extraction circuits lock-on to the received signal correctly. Once lock has been achieved, then the above inputs should be taken Low again.

In most applications, there will be a DC step in the output voltage from the receiver FM discriminator due to carrier frequency offsets as channels are changed or when the remote transmitter is turned on.

The MX589 can tolerate DC offsets in the received signal of at least  $\pm 0.5V$  with respect to V<sub>BIAS</sub> (measured at the Rx Feedback pin). However, to ensure that the DC offset compensation circuit operates correctly and with minimum delay, the Low to High transition of the RxDCacq and PLLacq inputs should occur after the mean input voltage to the MX589 has settled to within about 0.1V of its final value.

**Note:** This can place restrictions on the value of any series signal coupling capacitor.

As well as using the Rx Hold input to freeze the Level Measuring and Clock Extraction circuits during a signal fade, it may also be used in systems which use a continuously transmitting control channel to freeze the Rx circuitry during transmission of a data packet, allowing reception to resume afterwards without losing bit synchronization. To achieve this, the MX589 Xtal clock needs to be accurate enough that the derived RxClock output does not drift by more than about 0.1 bit time from the actual received data-rate during the time that the RxHold input is Low.

The RxDCacq input, however, may need to be pulsed high for 2 bit durations to re-establish the level measurements if the RxHold input is low for more than a few hundred bit-times (exact number depends on system crystal tolerances).

The voltages on the Doc1 and Doc2 pins reflect the average peak positive and negative excursions of the (filtered) receive signal, and could therefore be used to derive a measure of the data signal amplitude.

**Note:** These pins are driven from very high-impedance circuits, so that the DC load presented by any external circuitry should exceed 10M $\Omega$  to V<sub>BIAS</sub>.

## 5. Application

### 5.1 Radio Channel Requirements

To achieve legal adjacent channel performance at high bit-rates, a radio with an accurate carrier frequency and an accurate modulation index is required. For optimum channel utilization, (e.g. low BER and high data-rates) attention must be paid to the phase and frequency response of both the IF and baseband circuitry.

#### 5.1.1 Bitrate, BT and Bandwidth

The maximum data rate that can be transmitted over a radio channel depends on the following:

Channel spacing

Allowable adjacent channel interference

Tx filter bandwidth

Peak carrier deviation (Modulation Index)

Tx and Rx carrier frequency accuracies

Modulator and Demodulator linearity

Rx IF filter frequency and phase characteristics

### Use of error correction techniques

#### Acceptable error-rate

As a guide to MOBITEX operation, a raw data-rate of 8kbps at 12.5kHz channel spacing may be achievable -depending on local regulatory requirements- using a  $\pm 2$ kHz maximum deviation, a BT of 0.3, and no more than 1.5kHz discrepancy between Tx & Rx carrier frequencies. Forward error correction (FEC) could then be used with interleaving to reduce the effect of burst errors.

Reducing the data-rate to 4.8kbps would allow the BT to be increased to 0.5, improving the error-rate performance.

### 5.1.2 FM Modulator, Demodulator and IF

For optimum performance, the eye pattern of the received signal (when receiving random data) applied to the MX589 should be as close as possible to the Transmit eye pattern examples shown in Figure 11.

Of particular importance are general symmetry, cleanliness of the zero-crossings, and for a BT of 0.3, the relative amplitude of the inner eye opening.

To achieve this, attention must be paid to -

Linearity and frequency/phase response of the Tx frequency modulator. Unless the transmit data is especially encoded to remove low frequency components, the modulator frequency response should extend down to a few hertz. This is because two-point modulation is necessary for synthesized radios.

Bandwidth & phase response of the Rx IF filters.

Accuracy of the Tx and Rx carrier frequencies -any difference will shift the received signal towards one of the skirts of the IF filter response.

Ideally, the Rx demodulator should be DC coupled to the MX589 Rx Signal In pin (with a DC bias added to center the signal at the Rx Feedback pin around  $V_{DD}/2$  [ $V_{BIAS}$ ]). However AC coupling can be used provided that:

The 3 dB cut-off frequency is 20Hz or below (i.e. a  $0.1\mu F$  capacitor in series with  $100k\Omega$ ).

The data does not contain long sequences of consecutive ones or zeroes.

Sufficient time is allowed after a step change at the discriminator output (resulting from channel changing or the appearance of an RF carrier) for the voltage into the MX589 to settle before the RxDCacq line is strobed.

### 5.1.3 Two Point Modulation

When designing the MX589 into a radio that uses a frequency synthesizer, a two-point modulation technique is recommended. This is both to prevent the radio's PLL circuitry from counteracting the modulation process, and to provide a clean flat modulation response down to DC

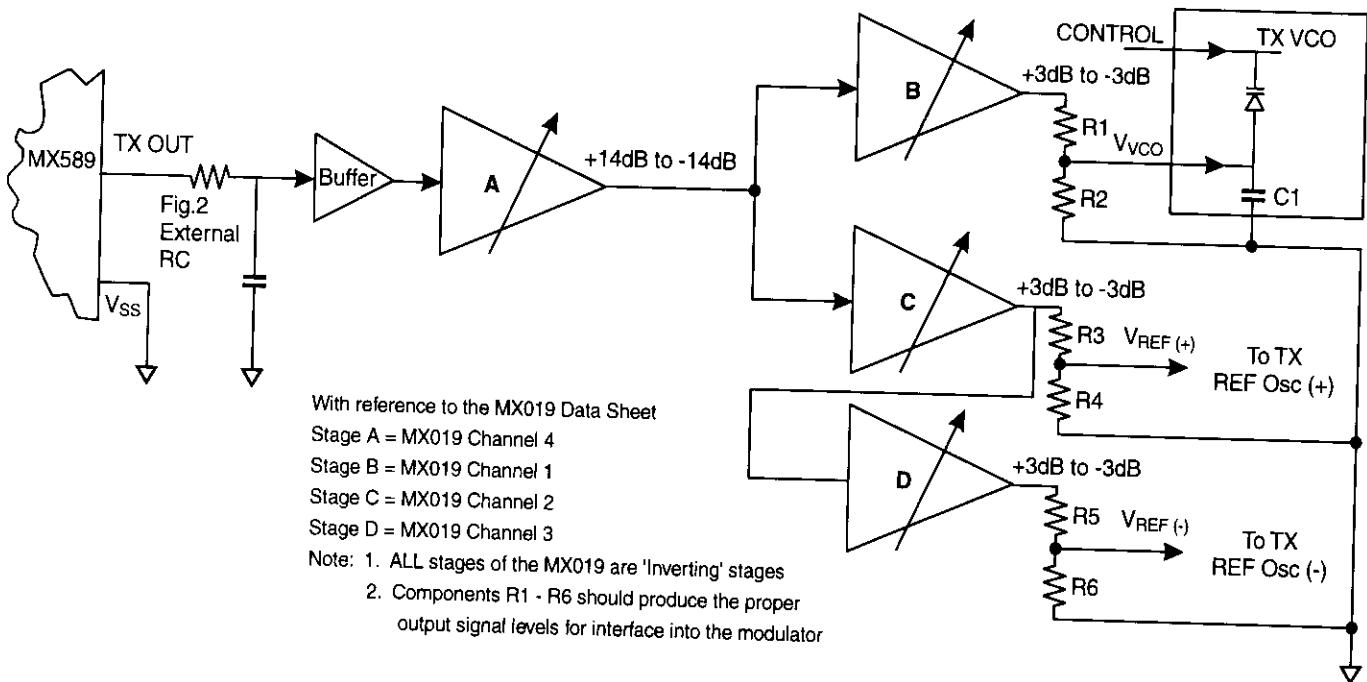

Figure 12 shows a suggested basic configuration to provide a two-point modulation drive from the MX589 Tx Output using MX•COM's MX019 Digitally Controlled Quad Amplifier Array. The MX019 elements provide individual set-up, calibration and dynamic control of modulation levels. Level setting control of the amplifiers/attenuators of the MX019 is via an 8-bit data word.

With reference to Figure 12:

The buffer amplifier is required to prevent loading of the MX589 external RC circuit.

Stage B, with R1/R2, provides suitable signal and DC levels for the VCO varactor; C1 is RF decoupling. The drive level should be adjusted (digitally) to provide the desired deviation.

Stage C, with R3/R4, provides the Reference Oscillator drive (application dependent). This parameter is set by adjusting for minimum AC signal on the PLL control voltage with a low-frequency modulating signal (inside the PLL bandwidth) applied.

Stage D could be used with the components shown if a negative reference drive is required.

Stage A provides buffering and overall level control.

**Figure 12: An Example of Two-Point Modulation Drive with Individual Adjustment Using the MX019**

## 5.2 AC Coupling of Tx and Rx Signals

In practical applications, it will usually be possible to arrange for any AC coupling between the MX589 Tx Output and the frequency modulator to cut-off at a very low frequency such as 5.0Hz, but Ac coupling between the receive discriminator and the input of the MX589 may need to have a shorter time-constant to avoid problems from voltage steps at the output of the discriminator when changing channels or when the distant transmitter turns on.

For these reasons, as well as to maintain reasonable BER, the optimum -3dB cut-off frequencies are around 5.0Hz in the Tx path and 20.Hz in the Rx path.

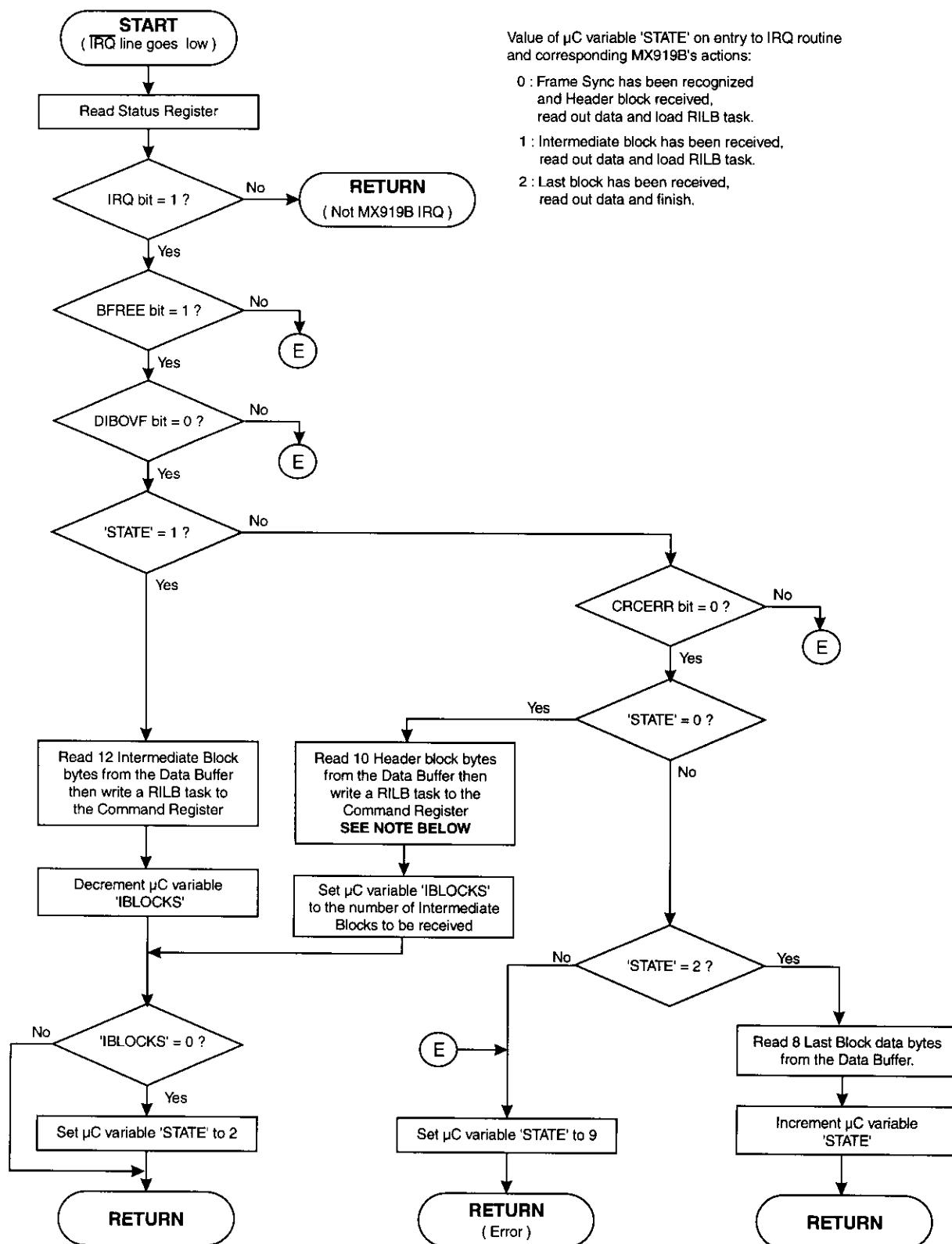

Figure 13 shows the typical static Bit-Error-Rate performance of the MX589 operating under nominal conditions for various degrees of AC coupling at the Rx input and the Tx Output:

Data Rate = 8kbps

V<sub>DD</sub> = 5.0V

T<sub>AMB</sub> = 25°C

Tx BT = 0.3

Figure 13: Effect of AC Coupling on Typical Bit-Error Rate

## 6. Performance Specification

### 6.1 Electrical Performance

#### Absolute Maximum Ratings

Exceeding these maximum ratings can result in damage to the device.

| General                                                     | Min. | Max.           | Units                             |

|-------------------------------------------------------------|------|----------------|-----------------------------------|

| Supply ( $V_{DD}$ - $V_{SS}$ )                              | -0.3 | 7.0            | V                                 |

| Voltage on any pin to $V_{SS}$                              | -0.3 | $V_{DD} + 0.3$ | V                                 |

| Current                                                     |      |                |                                   |

| $V_{DD}$                                                    | -30  | 30             | mA                                |

| $V_{SS}$                                                    | -30  | 30             | mA                                |

| Any other pins                                              | -20  | 20             | mA                                |

| <b>DW / PDIP Package</b>                                    |      |                |                                   |

| Total Allowable Power Dissipation at $T_{AMB} = 25^\circ C$ |      | 800            | mW                                |

| Derating above $25^\circ C$                                 |      | 13             | mW/ $^\circ C$ above $25^\circ C$ |

| Storage Temperature                                         | -55  | 85             | $^\circ C$                        |

| Operating Temperature                                       | -40  | 85             | $^\circ C$                        |

| <b>TN Package</b>                                           |      |                |                                   |

| Total Allowable Power Dissipation at $T_{AMB} = 25^\circ C$ |      | 550            | mW                                |

| Derating above $25^\circ C$                                 |      | 9              | mW/ $^\circ C$ above $25^\circ C$ |

| Storage Temperature                                         | -55  | 85             | $^\circ C$                        |

| Operating Temperature                                       | -40  | 85             | $^\circ C$                        |

**Operating Limits**

Correct operation of the device outside these limits is not implied.

|                              | Notes | Min. | Max. | Units |

|------------------------------|-------|------|------|-------|

| Supply ( $V_{DD} - V_{SS}$ ) |       | 3.0  | 5.5  | V     |

| Temperature                  |       | -40  | 85   | °C    |

| Rx and Tx Data Rate          |       |      |      |       |

| $V_{DD} \geq 3.0V$           |       | 4    | 32   | kbps  |

| $V_{DD} \geq 4.5V$           |       | 4    | 64   | kbps  |

| Xtal/Clock Frequency         |       |      |      |       |

| $V_{DD} \geq 3.0V$           |       | 1.0  | 5.0  | MHz   |

| $V_{DD} \geq 4.5V$           |       | 1.0  | 10.3 | MHz   |

| High Pulse Width             | 1     | 40   |      | ns    |

| Low Pulse Width              | 1     | 40   |      | ns    |

**Operating Limits Notes:**

1. Timing for an external clock input to the Xtal/Clock pin.

**Operating Characteristics**

For the following conditions unless otherwise specified:

$V_{DD} = 5.0V$  @  $T_{AMB} = 25^{\circ}C$

Xtal Frequency = 4.096mhz Data Rate = 8kbps Noise Bandwidth = Bit Rate

|                                               |       |       | Notes | Min. | Typ. | Max | Units       |

|-----------------------------------------------|-------|-------|-------|------|------|-----|-------------|

| <b>Static Values</b>                          |       |       |       |      |      |     |             |

| Supply Current                                | Tx PS | Rx PS | 1     |      |      |     |             |

| $I_{DD}$ ( $V_{DD} = 3.0V$ )                  |       |       |       |      |      |     |             |

|                                               | 1     | 1     |       |      | 0.5  |     | mA          |

|                                               | 0     | 1     |       |      | 1.0  |     | mA          |

|                                               | 1     | 0     |       |      | 1.0  |     | mA          |

|                                               | 0     | 0     |       |      | 1.5  |     | mA          |

| $I_{DD}$                                      |       |       |       |      |      |     |             |

|                                               | 1     | 1     |       |      | 1.0  |     | mA          |

|                                               | 0     | 1     |       |      | 2.0  |     | mA          |

|                                               | 1     | 0     |       |      | 3.0  |     | mA          |

|                                               | 0     | 0     |       |      | 4.0  |     | mA          |

| Input Logic Level                             |       |       |       |      |      |     |             |

| Logic 1 Input Level                           |       |       |       | 3.5  |      |     | V           |

| Logic 0 Input Level                           |       |       |       |      |      | 1.5 | V           |

| Logic Input Current                           |       | 2     |       | -5.0 |      | 5.0 | $\mu A$     |

| Logic 1 Output Level ( $I_{OH} = -120\mu A$ ) |       |       |       | 4.6  |      |     | V           |

| Logic 0 Output Level ( $I_{OL} = -120\mu A$ ) |       |       |       |      |      | 0.4 | V           |

| <b>Transmit Parameters</b>                    |       |       |       |      |      |     |             |

| Tx OUT, Output Impedance                      |       | 3     |       |      | 1.0  |     | $k\Omega$   |

| Tx OUT, Level                                 |       | 4,10  | 0.8   | 1.0  | 1.2  |     | $V_{P-P}$   |

| Tx Data Delay                                 |       |       |       |      |      |     |             |

| BT = 0.3                                      |       | 5     |       |      | 2.0  | 2.5 | bit-periods |

| BT = 0.5                                      |       | 5     |       |      | 1.5  | 2.0 | bit-periods |

| Tx PS to Output-Stable time                   |       | 6     |       |      | 4.0  |     |             |

| <b>Receive Parameters</b>                     |       |       |       |      |      |     |             |

| Rx Amplifier-                                 |       |       |       |      |      |     |             |

| Input Impedance                               |       |       |       | 1.0  |      |     | $M\Omega$   |

| Output Impedance                              |       | 7     |       |      | 10.0 |     | $k\Omega$   |

| Voltage Gain                                  |       |       |       |      | 50.0 |     | dB          |

| Rx Filter Signal Input Level                  |       | 8, 10 | 0.7   | 1.0  | 1.3  |     | $V_{P-P}$   |

| Rx Time Delay                                 |       | 9     |       |      |      | 3.0 | bit-periods |

| <b>On-Chip Xtal Oscillator</b>                |       |       |       |      |      |     |             |

| $R_{IN}$                                      |       |       |       | 10.0 |      |     | $M\Omega$   |

| $R_{OUT}$                                     |       | 11    |       |      | 50.0 |     | $k\Omega$   |

| Voltage Gain                                  |       | 11    |       |      | 25.0 |     | dB          |

**Operating Characteristics Notes:**

1. Not including current drawn from the MX589 pins by external circuitry. See Absolute Maximum Ratings.

2. For  $V_{IN}$  in the range  $V_{SS}$  to  $V_{DD}$ .

3. For a load of 10kW or greater. Tx PS input at logic 0; Tx Enable = 1.

4. Data pattern of 1111000011110000 ..

5. Measured between the rising edge of Tx Clock and the center of the corresponding bit at Tx Out.

6. Time between the falling edge of Tx PS and the Tx Out voltage stabilizing to normal output levels.

7. For a load of 10kW or greater. Rx PS input at logic 0.

8. For optimum performance, Measured at the Rx Feedback pin for a 1111000011110000 ... pattern.

9. Measured between the center of bit at Rx Signal In and corresponding rising edge of the Rx Clock.

10. Levels are proportional to applied  $V_{DD}$ .

11. Small signal measurement at 1.0kHz with no load on Xtal output.

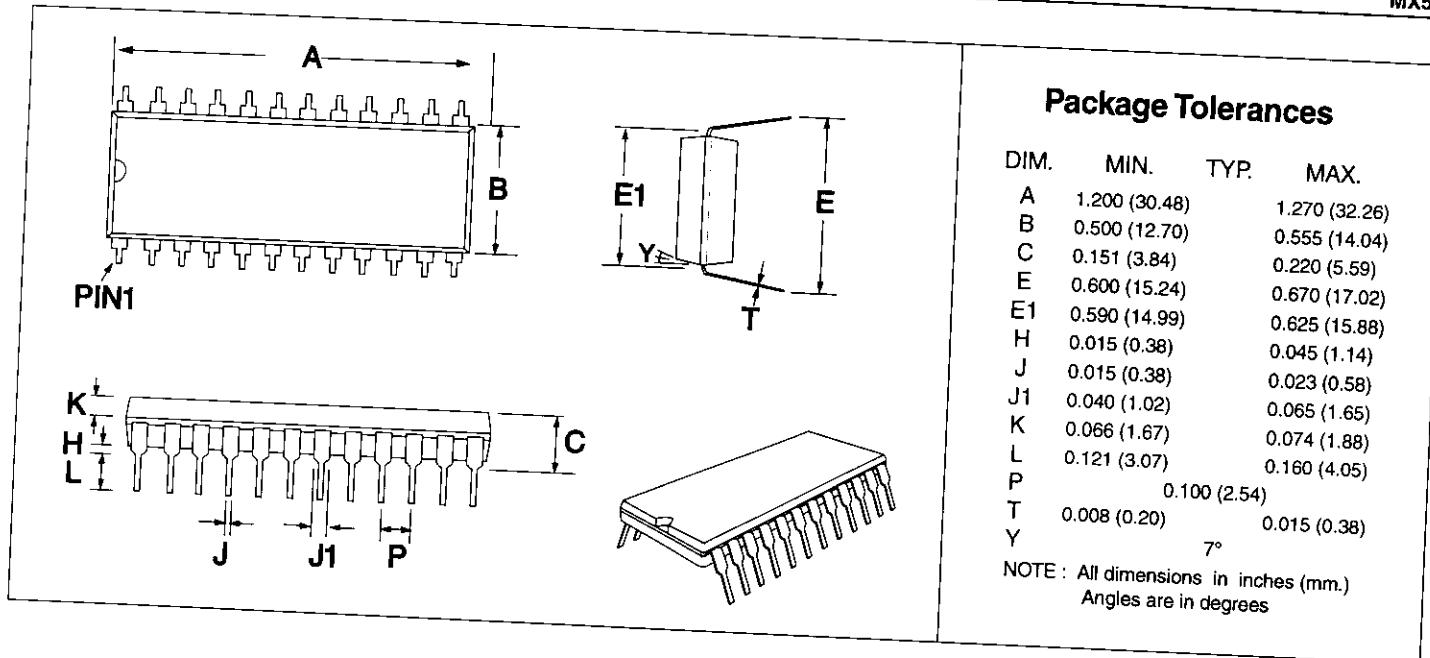

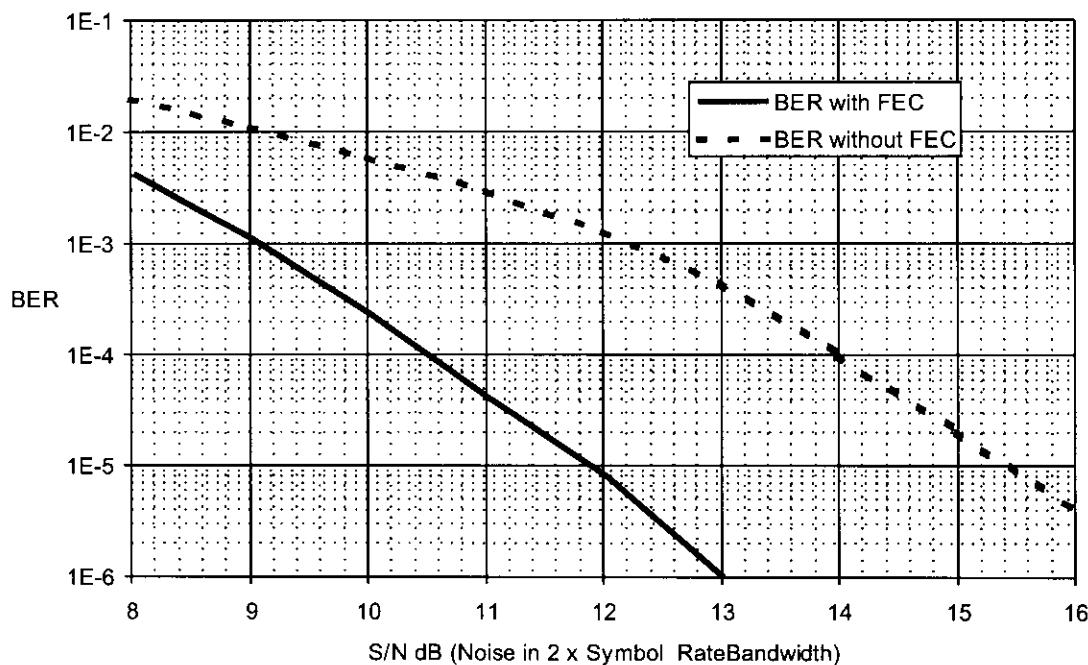

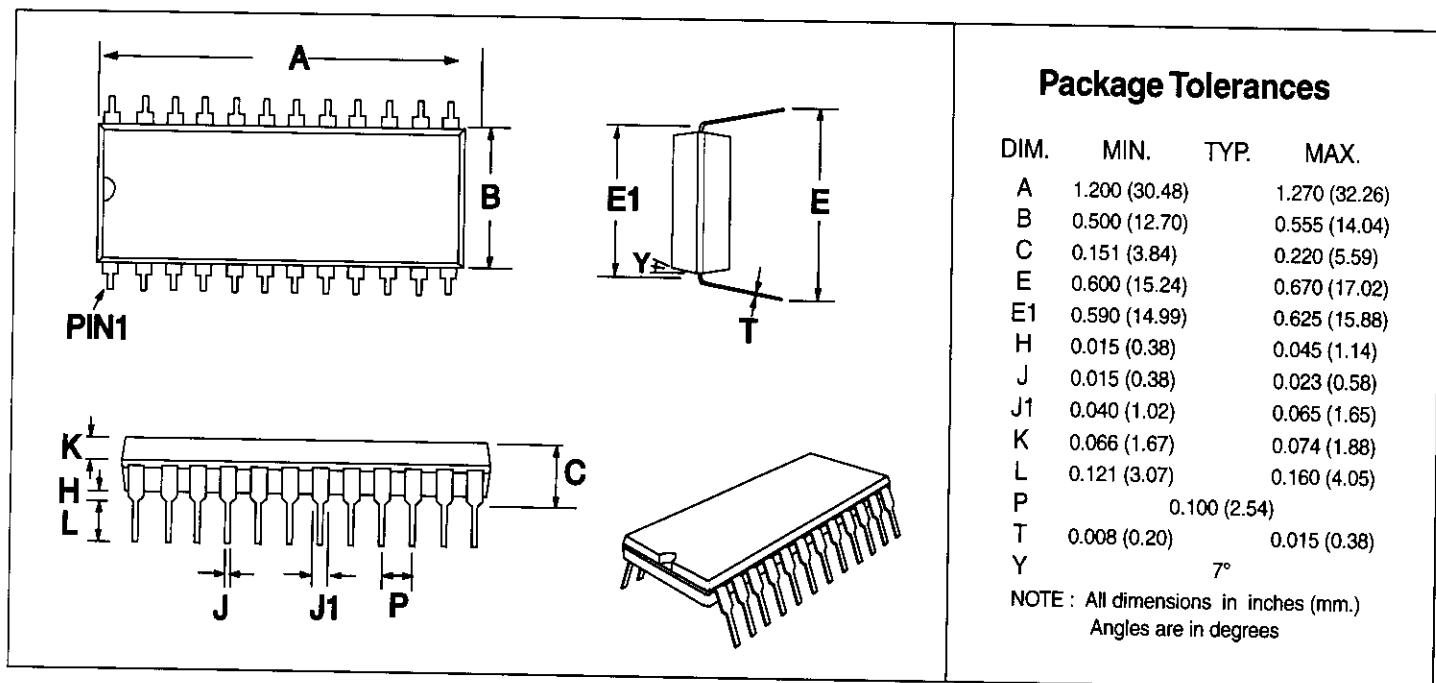

**6.2 Packaging**

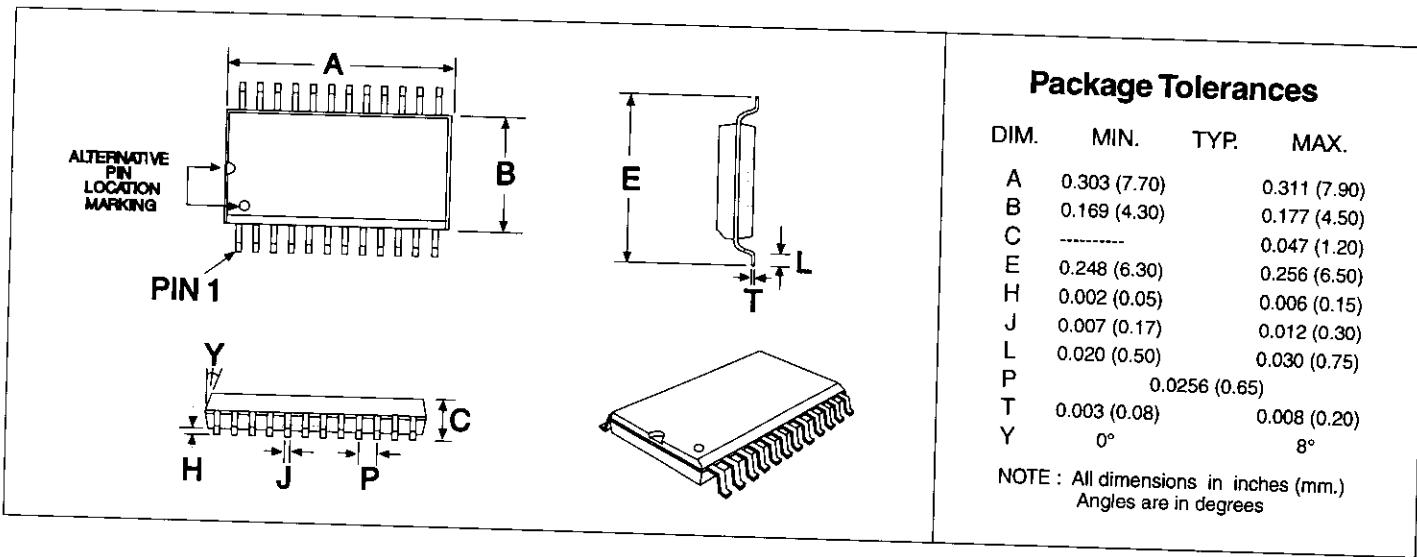

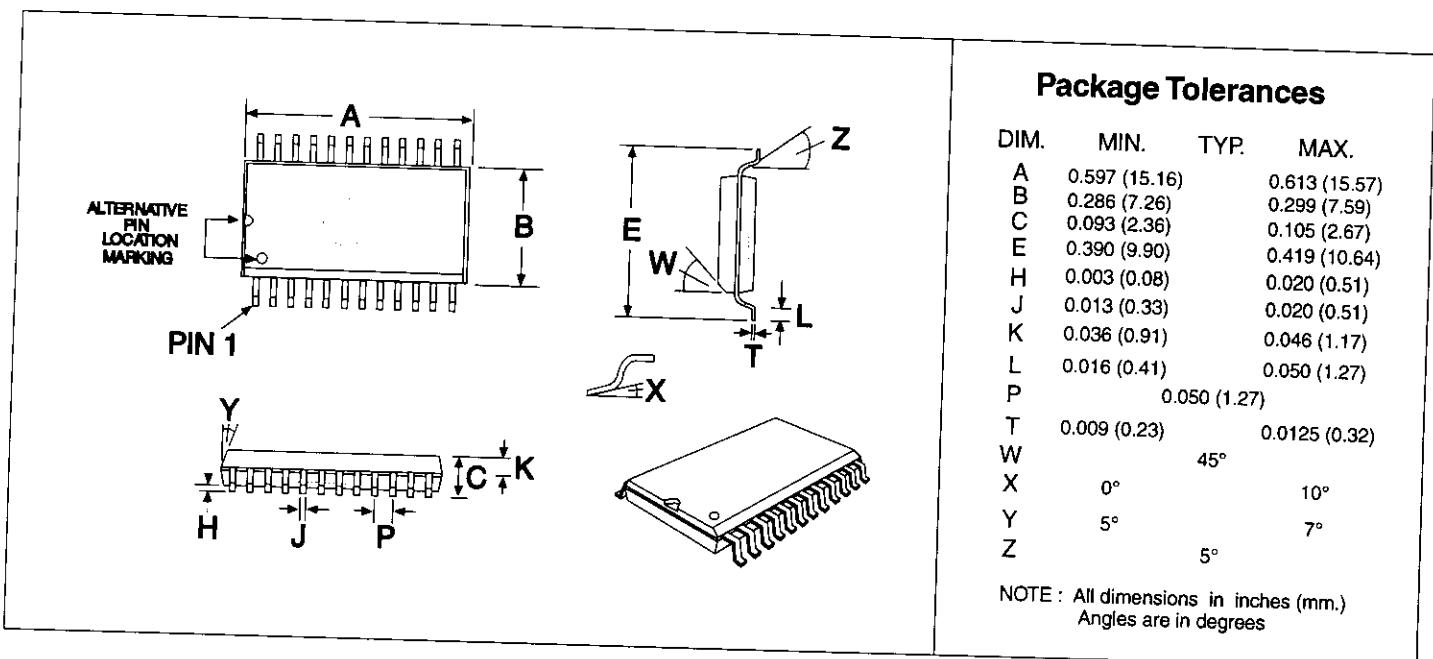

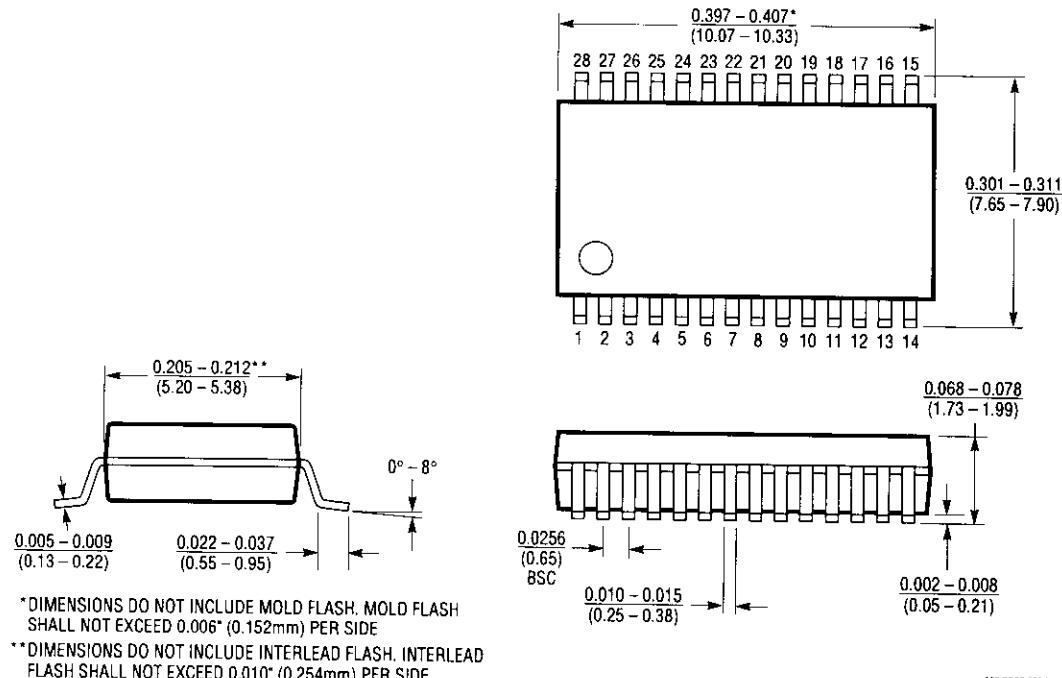

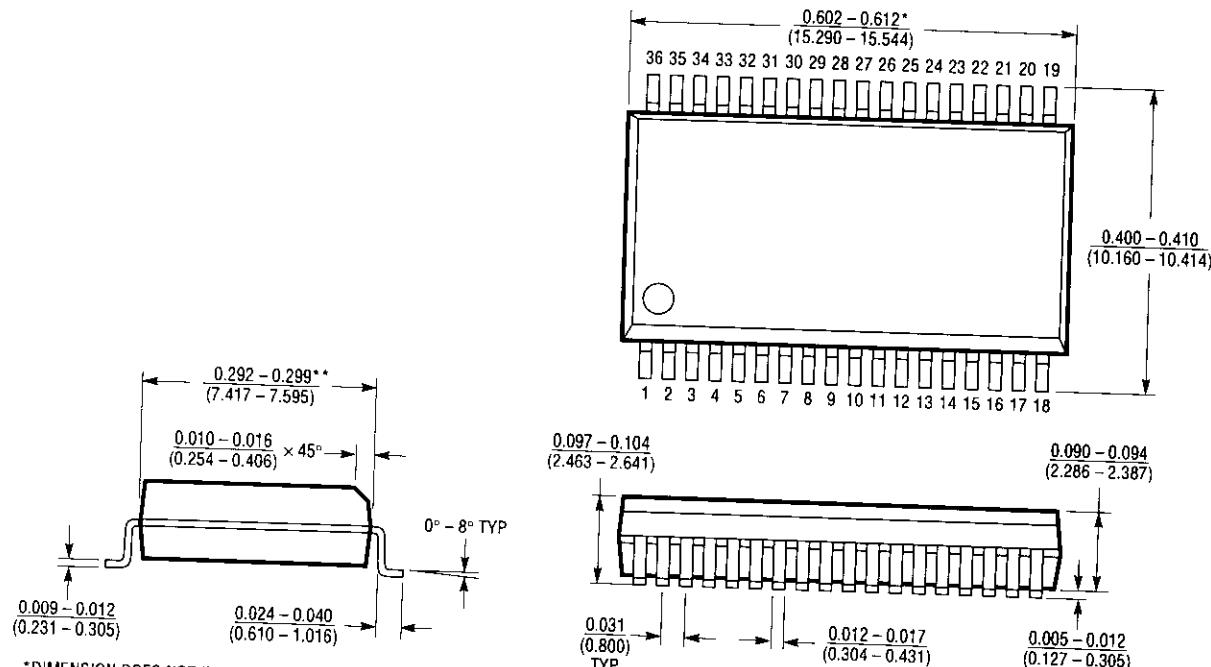

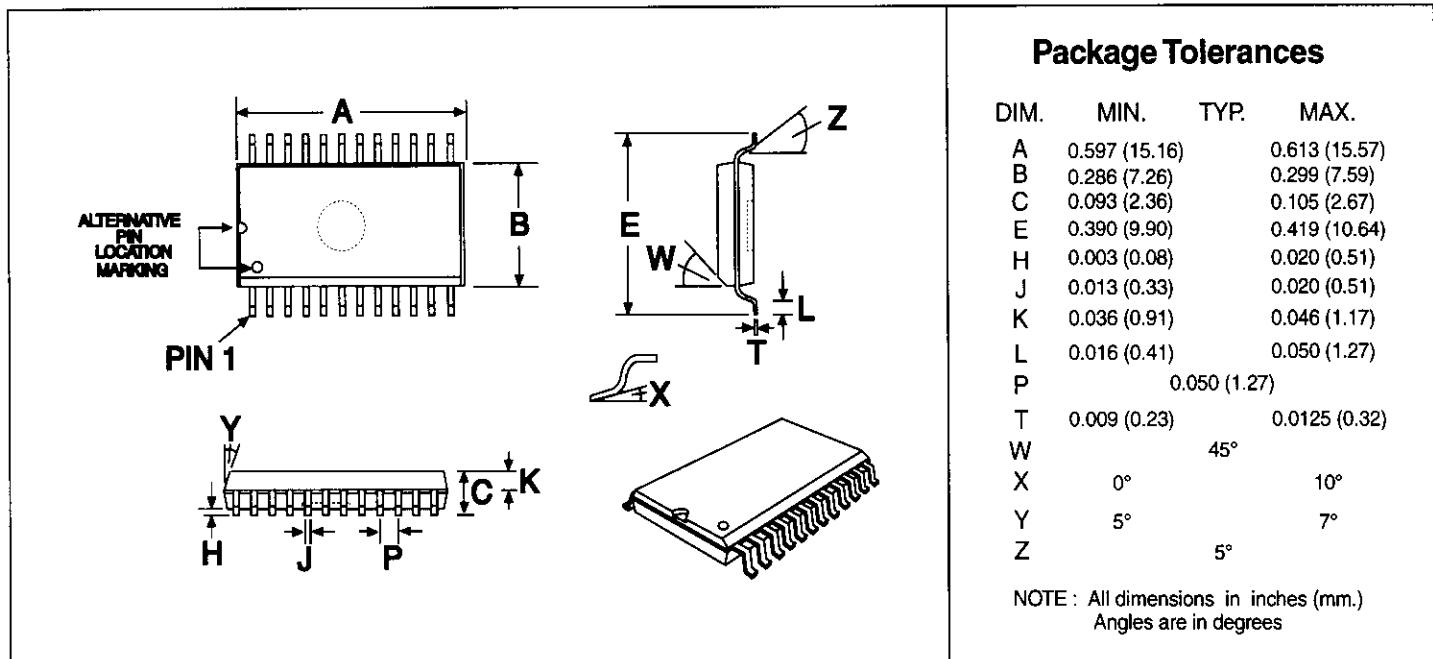

Figure 14: 24-pin TSSOP Mechanical Outline: Order as part no. MX589TN

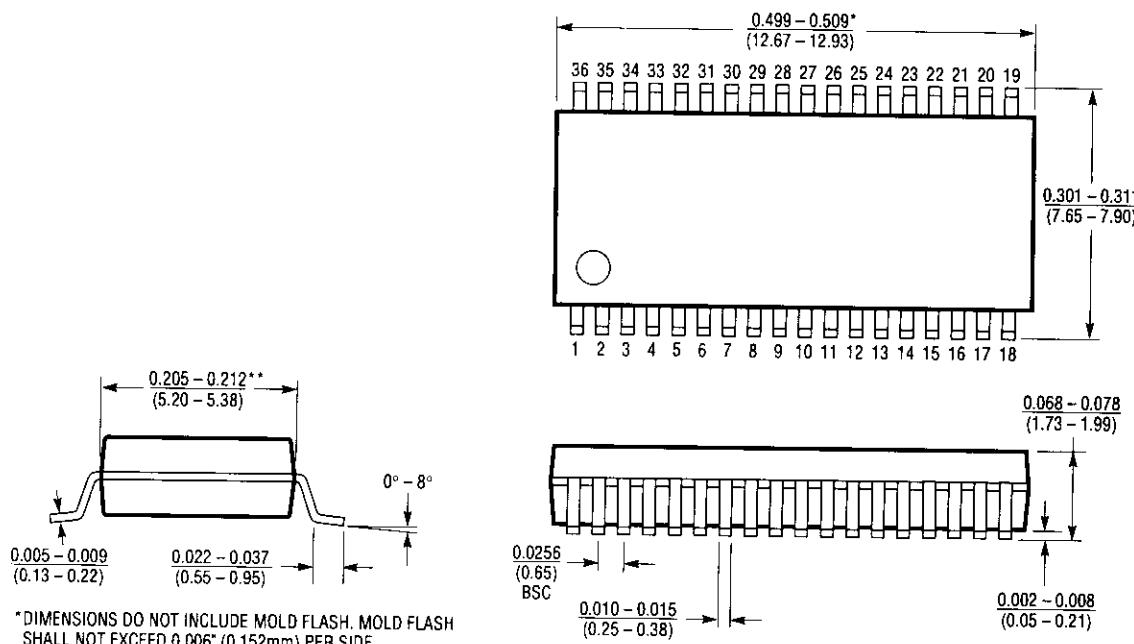

Figure 15: 24-pin SOIC Mechanical Outline: Order as part no. MX589DW

Figure 16: 24-pin PDIP Mechanical Outline: *Order as part no. MX589P*

## **MC68HC16Z1**

### *Technical Supplement*

### **25.17 MHz Electrical Characteristics**

Devices in the M68HC16 Modular Microcontroller Family are built up from a selection of standard functional modules. Published electrical characteristics for MC68HC16Z1 devices are based on a 16.78 MHz system clock. New products that operate at clock frequencies of 25.17 MHz are now available. This supplement consists of a new electrical characteristics appendix (Appendix A) that supplements those published in the *MC68HC16Z1 User's Manual* (MC68HC16Z1UM/AD).

The supplement contains the following updated specifications:

| <b>Table</b>                                        | <b>Page</b> |

|-----------------------------------------------------|-------------|

| Maximum Ratings .....                               | 2           |

| Typical Ratings .....                               | 3           |

| Thermal Characteristics .....                       | 3           |

| Clock Control Timing .....                          | 4           |

| DC Characteristics .....                            | 5           |

| AC Timing .....                                     | 7           |

| Background Debugging Mode Timing .....              | 18          |

| ECLK Bus Timing .....                               | 19          |

| QSPI Timing .....                                   | 20          |

| ADC Maximum Ratings .....                           | 23          |

| ADC DC Electrical Characteristics (Operating) ..... | 24          |

| ADC AC Characteristics (Operating) .....            | 24          |

| ADC Conversion Characteristics (Operating) .....    | 25          |

**Table A-1 Maximum Ratings**

| Num | Rating                                                                                                                                                                     | Symbol           | Value                                                | Unit |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------|------|

| 1   | Supply Voltage <sup>1, 2, 3</sup>                                                                                                                                          | V <sub>DD</sub>  | – 0.3 to + 6.5                                       | V    |

| 2   | Input Voltage <sup>1, 2, 3, 4, 5, 7</sup>                                                                                                                                  | V <sub>IN</sub>  | – 0.3 to + 6.5                                       | V    |

| 3   | Instantaneous Maximum Current<br>Single Pin Limit (all pins) <sup>1, 3, 5, 6</sup>                                                                                         | I <sub>D</sub>   | 25                                                   | mA   |

| 4   | Operating Maximum Current<br>Digital Input Disruptive Current <sup>3, 5, 6, 7, 8</sup><br>V <sub>NEGCLMAP</sub> ≡ – 0.3 V<br>V <sub>POSCLAMP</sub> ≡ V <sub>DD</sub> + 0.3 | I <sub>uD</sub>  | – 500 to 500                                         | μA   |

| 5   | Operating Temperature Range<br>“C” Suffix<br>“V” Suffix<br>“M” Suffix                                                                                                      | T <sub>A</sub>   | TL to TH<br>– 40 to 85<br>– 40 to 105<br>– 40 to 125 | °C   |

| 6   | Storage Temperature Range                                                                                                                                                  | T <sub>stg</sub> | – 55 to 150                                          | °C   |

NOTES:

1. Permanent damage can occur if maximum ratings are exceeded. Exposure to voltages or currents in excess of recommended values affects device reliability. Device modules may not operate normally while being exposed to electrical extremes.

2. Although sections of the device contain circuitry to protect against damage from high static voltages or electrical fields, take normal precautions to avoid exposure to voltages higher than maximum-rated voltages.

3. This parameter is periodically sampled rather than 100% tested.

4. All pins except TSC.

5. Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

6. Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current.

7. All functional non-supply pins are internally clamped to V<sub>SS</sub>. All functional pins except EXTAL and XFC are internally clamped to V<sub>DD</sub>.

8. Total input current for all digital input-only and all digital input/output pins must not exceed 10 mA. Exceeding this limit can cause disruption of normal operation.

**Table A-2 Typical Ratings**

| Num | Rating                                                                                                                                                               | Symbol             | Value                   | Unit                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------|----------------------|

| 1   | Supply Voltage                                                                                                                                                       | V <sub>DD</sub>    | 5.0                     | V                    |

| 2   | Operating Temperature                                                                                                                                                | T <sub>A</sub>     | 25                      | °C                   |

| 3   | V <sub>DD</sub> Supply Current<br>RUN<br>LPSTOP, VCO off<br>LPSTOP, External clock, max f <sub>sys</sub>                                                             | I <sub>DD</sub>    | 113<br>125<br>3.75      | mA<br>μA<br>mA       |

| 4   | Clock Synthesizer Operating Voltage                                                                                                                                  | V <sub>DDSYN</sub> | 5.0                     | V                    |

| 5   | V <sub>DDSYN</sub> Supply Current<br>VCO on, maximum f <sub>sys</sub><br>External Clock, maximum f <sub>sys</sub><br>LPSTOP, VCO off<br>V <sub>DD</sub> powered down | I <sub>DDSYN</sub> | 1.0<br>5.0<br>100<br>50 | mA<br>mA<br>μA<br>μA |

| 6   | RAM Standby Voltage                                                                                                                                                  | V <sub>SB</sub>    | 3.0                     | V                    |

| 7   | RAM Standby Current<br>Normal RAM operation<br>Standby operation                                                                                                     | I <sub>SB</sub>    | 7.0<br>40               | μA<br>μA             |

| 8   | Power Dissipation                                                                                                                                                    | P <sub>D</sub>     | 570                     | mW                   |

**Table A-3 Thermal Characteristics**

| Num | Characteristic                                                                                    | Symbol          | Value    | Unit |

|-----|---------------------------------------------------------------------------------------------------|-----------------|----------|------|

| 1   | Thermal Resistance <sup>1</sup><br>Plastic 132-Pin Surface Mount<br>Plastic 144-Pin Surface Mount | Θ <sub>JA</sub> | 38<br>49 | °C/W |

NOTES:

1. The average chip-junction temperature (T<sub>J</sub>) in C can be obtained from (1):

$$T_J = T_A + (P_D \cdot \Theta_{JA})$$

where:

T<sub>A</sub> = Ambient Temperature, °C

Θ<sub>JA</sub> = Package Thermal Resistance, Junction-to-Ambient, °C/W

P<sub>D</sub> = P<sub>INT</sub> + P<sub>I/O</sub>

P<sub>INT</sub> = I<sub>DD</sub> × V<sub>DD</sub>, Watts — Chip Internal Power

P<sub>I/O</sub> = Power Dissipation on Input and Output Pins — User Determined

For most applications P<sub>I/O</sub> < P<sub>INT</sub> and can be neglected. An approximate relationship between P<sub>D</sub> and T<sub>J</sub> (if P<sub>I/O</sub> is neglected) is (2):

$$P_D = K + (T_J + 273°C)$$

Solving equations (1) and (2) for K gives (3):

$$K = P_D + (T_A + 273°C) + \Theta_{JA} \times P_D^2$$

Where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring P<sub>D</sub> (at equilibrium) for a known T<sub>A</sub>. Using this value of K, the values of P<sub>D</sub> and T<sub>J</sub> can be obtained by solving equations (1) and (2) iteratively for any value of T<sub>A</sub>.

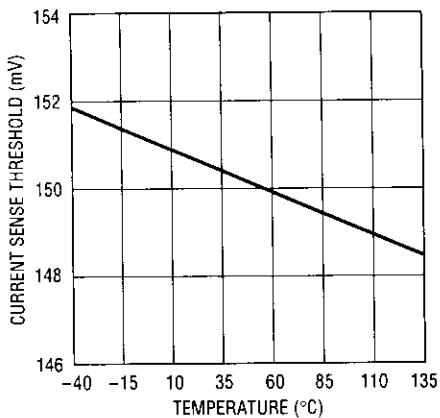

**Table A-4 Clock Control Timing**

( $V_{DD}$  and  $V_{DDSYN} = 5.0$  Vdc  $\pm 5\%$ ,  $V_{SS} = 0$  Vdc,  $T_A = T_L$  to  $T_H$ , Stable External Reference)<sup>1</sup>

| Num | Characteristic                                                                                          | Symbol     | Minimum           | Maximum                           | Unit |

|-----|---------------------------------------------------------------------------------------------------------|------------|-------------------|-----------------------------------|------|

| 1   | PLL Reference Frequency Range                                                                           | $f_{ref}$  | 25                | 50                                | kHz  |

| 2   | System Frequency <sup>2</sup><br>On-Chip PLL System Frequency<br>External Clock Operation               | $f_{sys}$  | dc<br>0.131<br>dc | 25.17<br>25.17<br>25.17           | MHz  |

| 3   | PLL Lock Time <sup>3,5,6,7</sup>                                                                        | $t_{plll}$ | —                 | 20                                | ms   |

| 4   | VCO Frequency <sup>4</sup>                                                                              | $f_{VCO}$  | —                 | 2 ( $f_{sys}$ max)                | MHz  |

| 5   | Limp Mode Clock Frequency<br>SYNCR X bit = 0<br>SYNCR X bit = 1                                         | $f_{limp}$ | —<br>—            | $f_{sys}$ max /2<br>$f_{sys}$ max | MHz  |

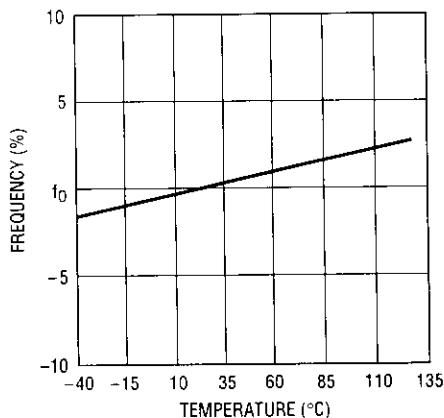

| 6   | CLKOUT Jitter <sup>5,6,7,8</sup><br>Short term (5 $\mu$ s interval)<br>Long term (500 $\mu$ s interval) | $J_{clk}$  | -1.0<br>-0.5      | 1.0<br>0.5                        | %    |

NOTES:

1. Tested with a 32.768 kHz reference.

2. All internal registers retain data at 0 Hz.

3. Assumes that stable  $V_{DDSYN}$  is applied, and that the crystal oscillator is stable. Lock time is measured from the time  $V_{DD}$  and  $V_{DDSYN}$  are valid until ~~RESET~~ is released. This specification also applies to the period required for PLL lock after changing the W and Y frequency control bits in the synthesizer control register (SYNCR) while the PLL is running, and to the period required for the clock to lock after LPSTOP.

4. Internal VCO frequency ( $f_{VCO}$ ) is determined by SYNCR W and Y bit values.

The SYNCR X bit controls a divide-by-two circuit that is not in the synthesizer feedback loop.

When X = 0, the divider is enabled, and  $f_{sys} = f_{VCO} + 4$ .

When X = 1, the divider is disabled, and  $f_{sys} = f_{VCO} + 2$ .

X must equal one when operating at maximum specified  $f_{sys}$ .

5. This parameter is periodically sampled rather than 100% tested.

6. Assumes that a low-leakage external filter network is used to condition clock synthesizer input voltage. Total external resistance from the XFC pin due to external leakage must be greater than 15 M  $\Omega$  to guarantee this specification. Filter network geometry can vary depending upon operating environment.

7. Proper layout procedures must be followed to achieve specifications.

8. Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum  $f_{sys}$ . Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via  $V_{DDSYN}$  and  $V_{SS}$  and variation in crystal oscillator frequency increase the  $J_{clk}$  percentage for a given interval. When jitter is a critical constraint on control system operation, this parameter should be measured during functional testing of the final system.

**Table A-5 DC Characteristics**

( $V_{DD}$  and  $V_{DDSYN} = 5.0$  Vdc  $\pm 5\%$ ,  $V_{SS} = 0$  Vdc,  $T_A = T_L$  to  $T_H$ )

| Num | Characteristic                                                                                                                                                                                                                       | Symbol       | Min                   | Max                  | Unit                     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|----------------------|--------------------------|

| 1   | Input High Voltage                                                                                                                                                                                                                   | $V_{IH}$     | 0.7 ( $V_{DD}$ )      | $V_{DD} + 0.3$       | V                        |

| 2   | Input Low Voltage                                                                                                                                                                                                                    | $V_{IL}$     | $V_{SS} - 0.3$        | 0.2 ( $V_{DD}$ )     | V                        |

| 3   | Input Hysteresis <sup>1, 2</sup>                                                                                                                                                                                                     | $V_{HYS}$    | 0.5                   | —                    | V                        |

| 4   | Input Leakage Current <sup>3, 16</sup><br>$V_{in} = V_{DD}$ or $V_{SS}$                                                                                                                                                              | $I_{in}$     | -2.5                  | 2.5                  | $\mu A$                  |

| 5   | High Impedance (Off-State) Leakage Current <sup>4, 16</sup><br>$V_{in} = V_{DD}$ or $V_{SS}$                                                                                                                                         | $I_{OZ}$     | -2.5                  | 2.5                  | $\mu A$                  |

| 6   | CMOS Output High Voltage <sup>5, 6, 16</sup><br>$I_{OH} = -10.0$ $\mu A$                                                                                                                                                             | $V_{OH}$     | $V_{DD} - 0.2$        | —                    | V                        |

| 7   | CMOS Output Low Voltage <sup>6, 16</sup><br>$I_{OL} = 10.0$ $\mu A$                                                                                                                                                                  | $V_{OL}$     | —                     | 0.2                  | V                        |

| 8   | Output High Voltage <sup>5, 6, 16</sup><br>$I_{OH} = -0.8$ mA                                                                                                                                                                        | $V_{OH}$     | $V_{DD} - 0.8$        | —                    | V                        |

| 9   | Output Low Voltage <sup>7, 16</sup><br>$I_{OL} = 1.6$ mA<br>$I_{OL} = 5.3$ mA<br>$I_{OL} = 12$ mA                                                                                                                                    | $V_{OL}$     | —<br>—<br>—           | 0.4<br>0.4<br>0.4    | V                        |

| 10  | Three State Control Input High Voltage                                                                                                                                                                                               | $V_{IH TSC}$ | 1.6 ( $V_{DD}$ )      | 9.1                  | V                        |

| 11  | Data Bus Mode Select Pull-up Current <sup>8, 9</sup><br>$V_{in} = V_{IL}$<br>$V_{in} = V_{IH}$                                                                                                                                       | $I_{MSP}$    | —<br>-15              | -120<br>—            | $\mu A$                  |

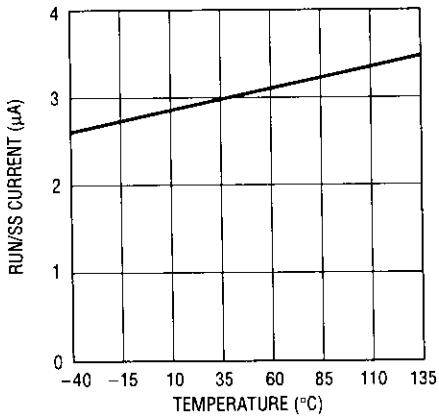

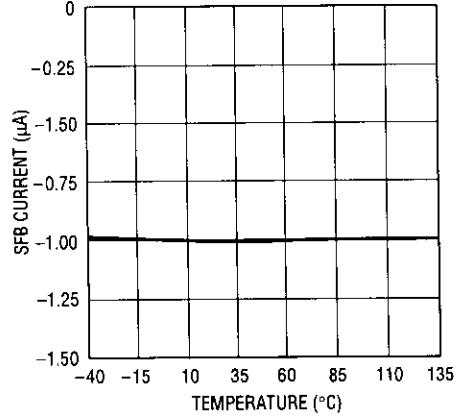

| 12  | $V_{DD}$ Supply Current <sup>10, 11, 12</sup><br>Run<br>LPSTOP, crystal reference, VCO Off (STSIM = 0)<br>LPSTOP, external clock input frequency = maximum $f_{sys}$                                                                 | $I_{DD}$     | —<br>—<br>—           | 140<br>350<br>5      | $\mu A$                  |

| 13  | Clock Synthesizer Operating Voltage                                                                                                                                                                                                  | $V_{DDSYN}$  | 4.75                  | 5.25                 | V                        |

| 14  | $V_{DDSYN}$ Supply Current <sup>6, 12</sup><br>Crystal reference, VCO on, maximum $f_{sys}$<br>External clock input, maximum $f_{sys}$<br>Crystal reference, LPSTOP, VCO off (STSIM = 0)<br>Crystal reference, $V_{DD}$ powered down | $I_{DDSYN}$  | —<br>—<br>—<br>—<br>— | 2<br>7<br>150<br>100 | $\mu A$                  |

| 15  | RAM Standby Voltage <sup>13</sup><br>Specified $V_{DD}$ applied<br>$V_{DD} = V_{SS}$                                                                                                                                                 | $V_{SB}$     | 0.0<br>3.0            | 5.25<br>5.25         | V                        |

| 16  | RAM Standby Current <sup>10</sup><br>Normal RAM operation <sup>14</sup><br>Transient condition<br>Standby operation <sup>13</sup>                                                                                                    | $I_{SB}$     | —<br>—<br>—           | 10<br>3<br>50        | $\mu A$<br>mA<br>$\mu A$ |

| 17  | Power Dissipation <sup>15, 16</sup>                                                                                                                                                                                                  | $P_D$        | —                     | 766                  | mW                       |

| 18  | Input Capacitance <sup>2, 16</sup><br>All input-only pins except ADC pins<br>All input/output pins                                                                                                                                   | $C_{in}$     | —<br>—                | 10<br>20             | pF                       |

**Table A-5 DC Characteristics (Continued)**

( $V_{DD}$  and  $V_{DDSYN} = 5.0$  Vdc  $\pm 5\%$ ,  $V_{SS} = 0$  Vdc,  $T_A = T_L$  to  $T_H$ )

| Num | Characteristic                                                                                                                                                | Symbol | Min              | Max                     | Unit |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|-------------------------|------|

| 19  | Load Capacitance <sup>16</sup><br>Group 1 I/O Pins, CLKOUT, FREEZE/QUOT, IPIPE0<br>Group 2 I/O Pins and CSBOOT, BG/CS<br>Group 3 I/O Pins<br>Group 4 I/O Pins | $C_L$  | —<br>—<br>—<br>— | 90<br>100<br>130<br>200 | pF   |

NOTES:

1. Applies to:

Port ADA[7:0] — AN[7:0]

Port E[7:4] — SIZ[1:0], AS, DS

Port F[7:0] — IRQ[7:1], MODCLK

Port GP[7:0] — IC4/OC5/OC1, IC[3:1], OC[4:1]/OC1

Port QS[7:0] — TXD, PCS[3:1], PCS0/SS, SCK, MOSI, MISO

BKPT/DSCLK, DSI/IPIPE1, PAI, PCLK, RESET, RXD, TSC

EXTAL (when PLL enabled)

2. This parameter is periodically sampled rather than 100% tested.

3. Applies to all input-only pins except ADC pins.

4. Applies to all input/output and output pins

5. Does not apply to HALT and RESET because they are open drain pins. Does not apply to Port QS[7:0] (TXD, PCS[3:1], PCS0/SS, SCK, MOSI, MISO) in wired-OR mode.

6. Applies to Group 1, 2, 4 input/output and all output pins

7. Applies to Group 1, 2, 3, 4 input/output pins, BG/CS, CLKOUT, CSBOOT, FREEZE/QUOT, and IPIPE0

8. Applies to DATA[15:0]

9. Use of an active pulldown device is recommended.

10. Total operating current is the sum of the appropriate  $I_{DD}$ ,  $I_{DDSYN}$ , and  $I_{SB}$  values, plus  $I_{DDA}$ .  $I_{DD}$  values include supply currents for device modules powered by  $V_{DDE}$  and  $V_{DDI}$  pins.

11. Current measured at maximum system clock frequency, all modules active.

12. Tested with a 32.768 kHz crystal reference.

13. The SRAM module will not switch into standby mode as long as  $V_{SB}$  does not exceed  $V_{DD}$  by more than 0.5 volts. The SRAM array cannot be accessed while the module is in standby mode.

14. When  $V_{SB}$  is more than 0.3 V greater than  $V_{DD}$ , current flows between the  $V_{STBY}$  and  $V_{DD}$  pins, which causes standby current to increase toward the maximum transient condition specification. System noise on the  $V_{DD}$  and  $V_{STBY}$  pin can contribute to this condition.

15. Power dissipation measured at specified system clock frequency, all modules active. Power dissipation can be calculated using the expression:

$$P_D = \text{Maximum } V_{DD} (I_{DD} + I_{DDSYN} + I_{SB}) + \text{Maximum } V_{DDA} (I_{DDA})$$

$I_{DD}$  includes supply currents for all device modules powered by  $V_{DDE}$  and  $V_{DDI}$  pins.

16. Input-Only Pins: EXTAL, TSC, BKPT/DSCLK, PAI, PCLK, RXD

Output-Only Pins: CSBOOT, BG/CS1, CLKOUT, FREEZE/QUOT, DS0/IPIPE0, PWMA, PWMB

Input/Output Pins:

Group 1: Port GP[7:0] — IC4/OC5/OC1, IC[3:1], OC[4:1]/OC1

DATA[15:0], DSI/IPIPE1

Group 2: Port C[6:0] — ADDR[22:19]/CS[9:6], FC[2:0]/CS[5:3]

Port E[7:0] — SIZ[1:0], AS, DS, AVEC, DSACK[1:0]

Port F[7:0] — IRQ[7:1], MODCLK

Port QS[7:3] — TXD, PCS[3:1], PCS0/SS, ADDR23/CS10/ECLK

ADDR[18:0], R/W, BERR, BR/CS0, BGACK/CS2

Group 3: HALT, RESET

Group 4: MISO, MOSI, SCK

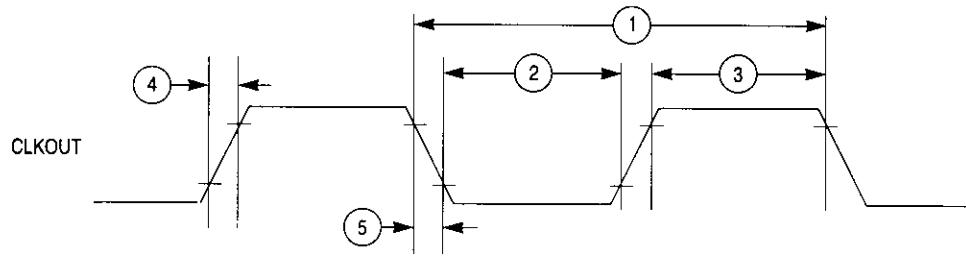

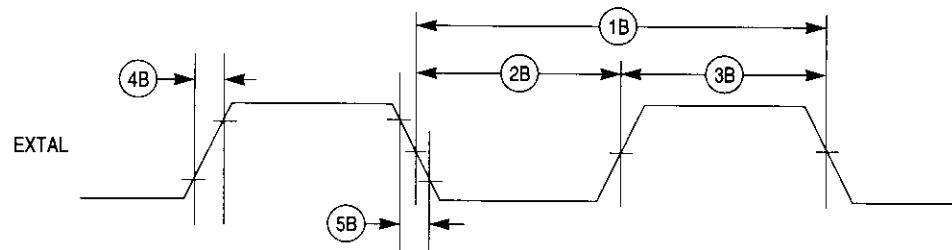

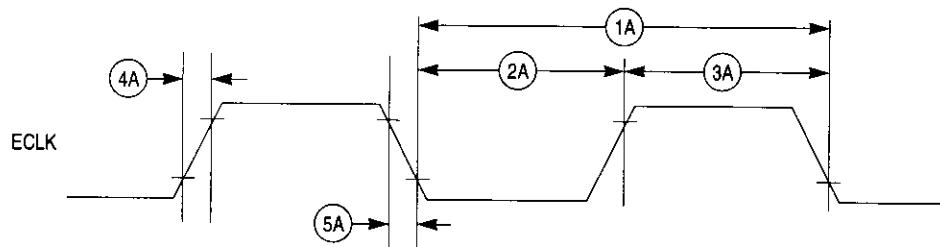

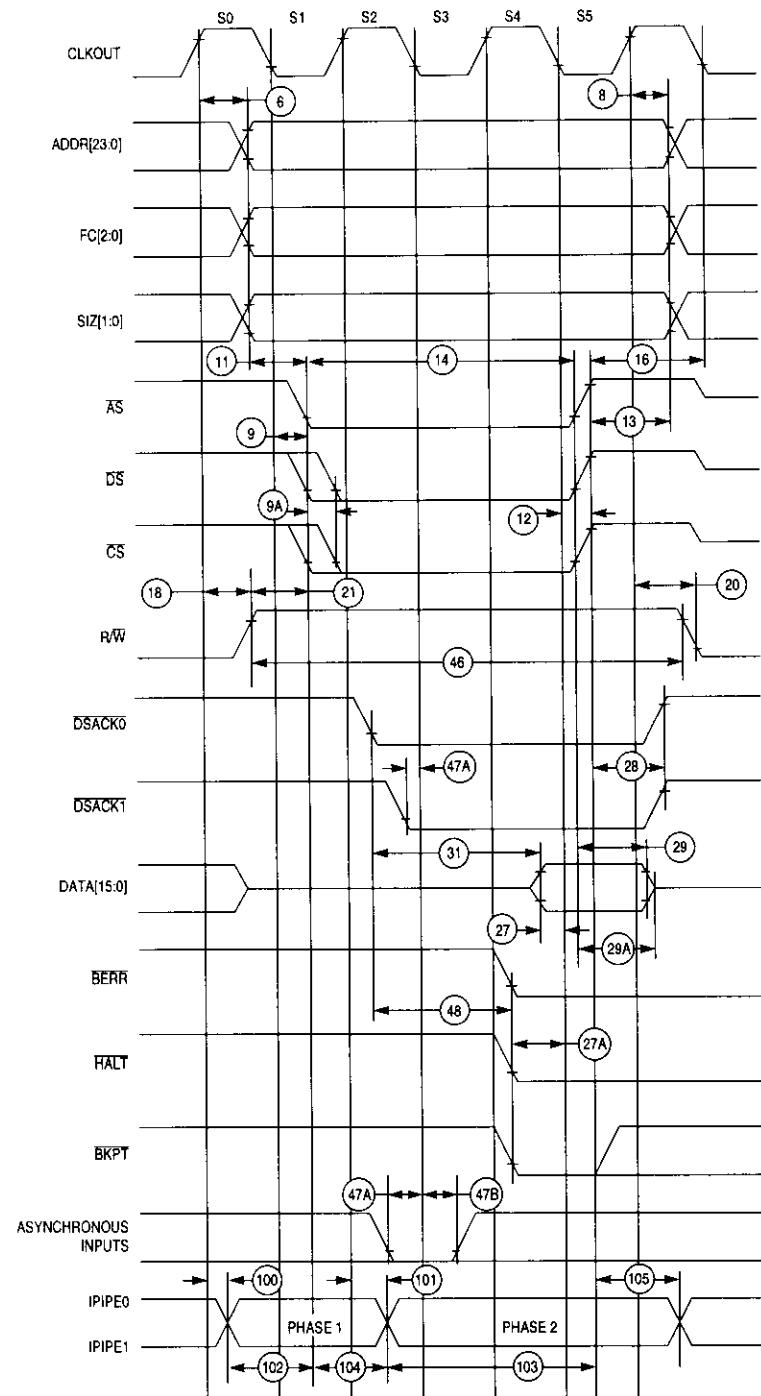

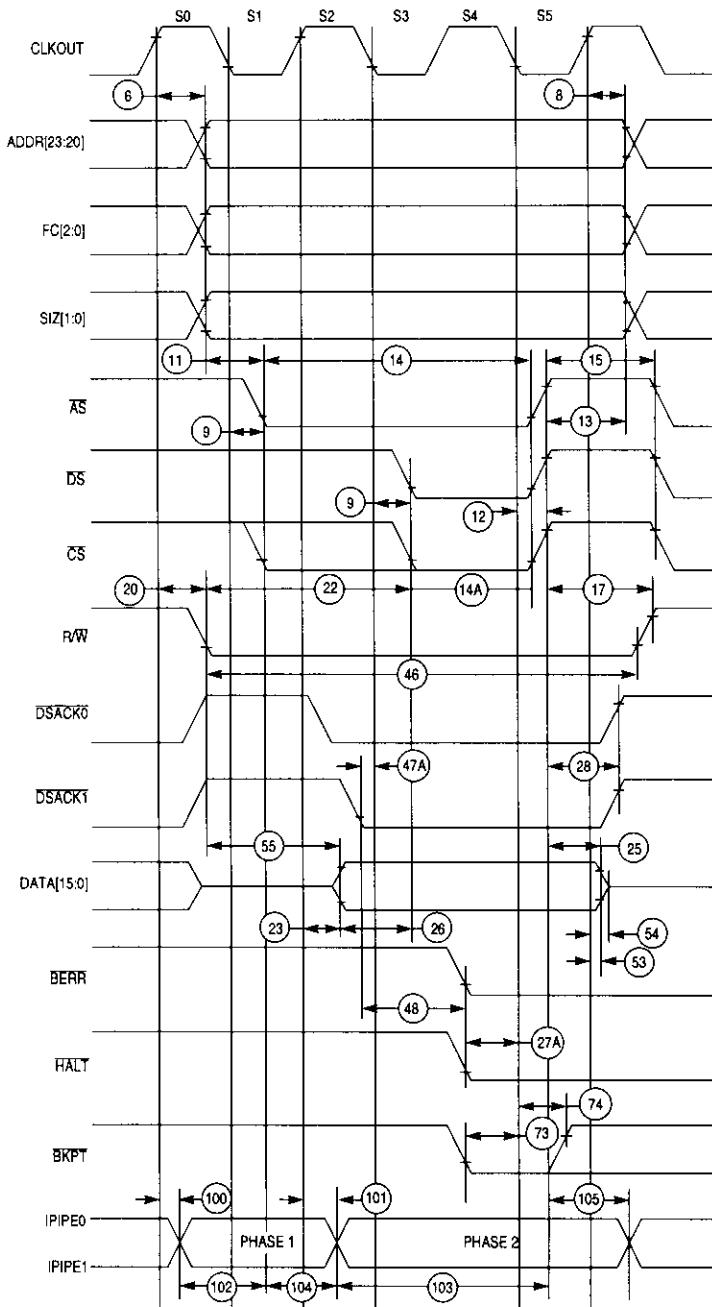

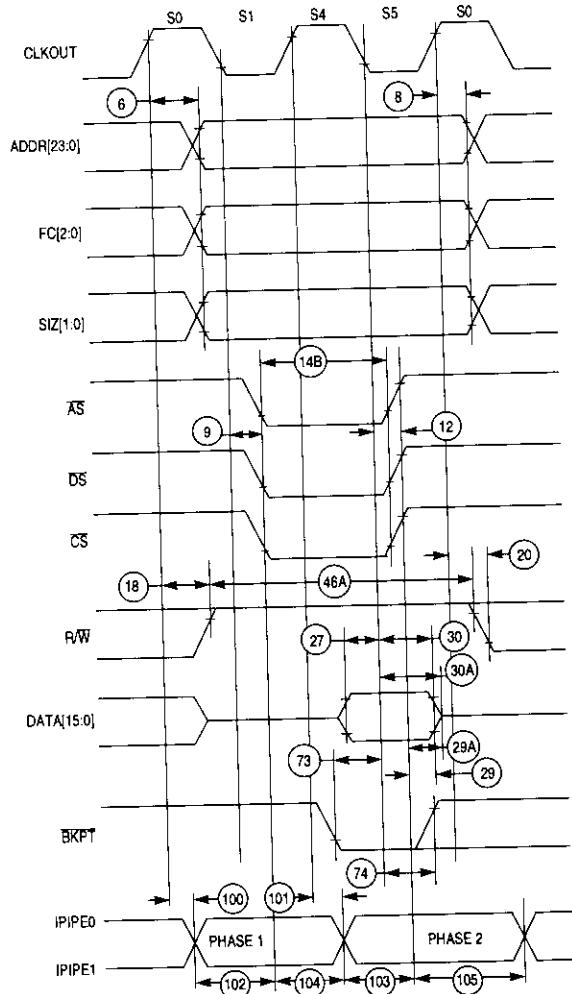

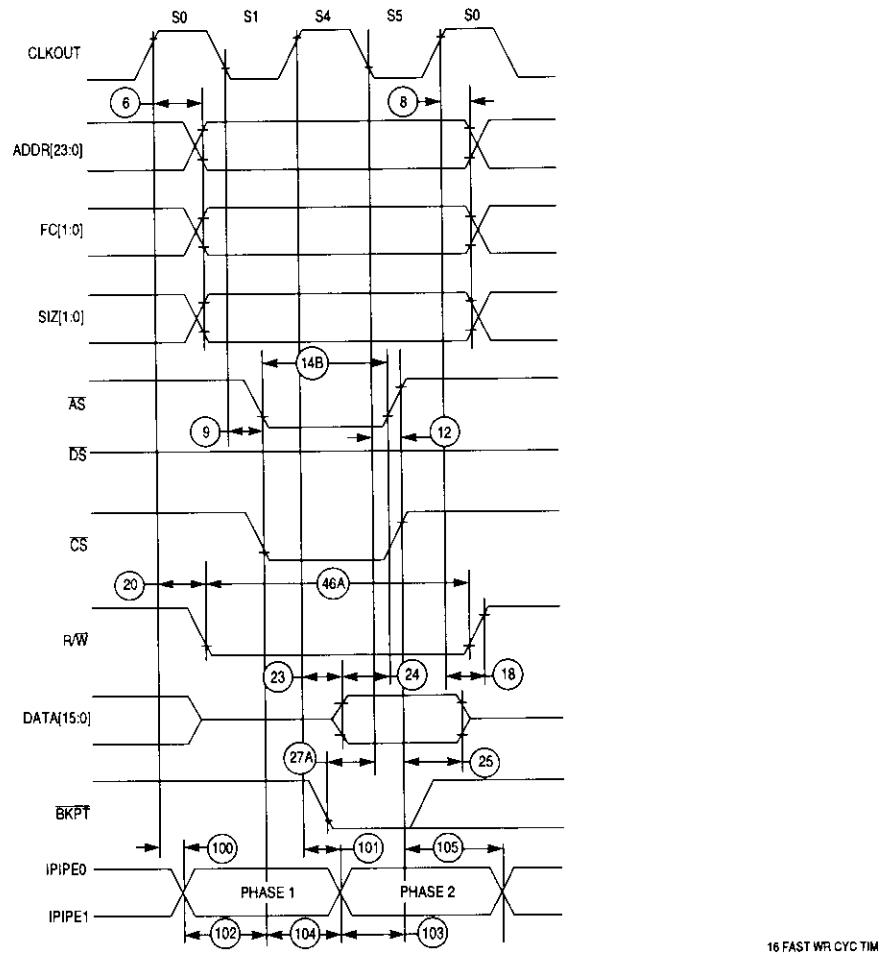

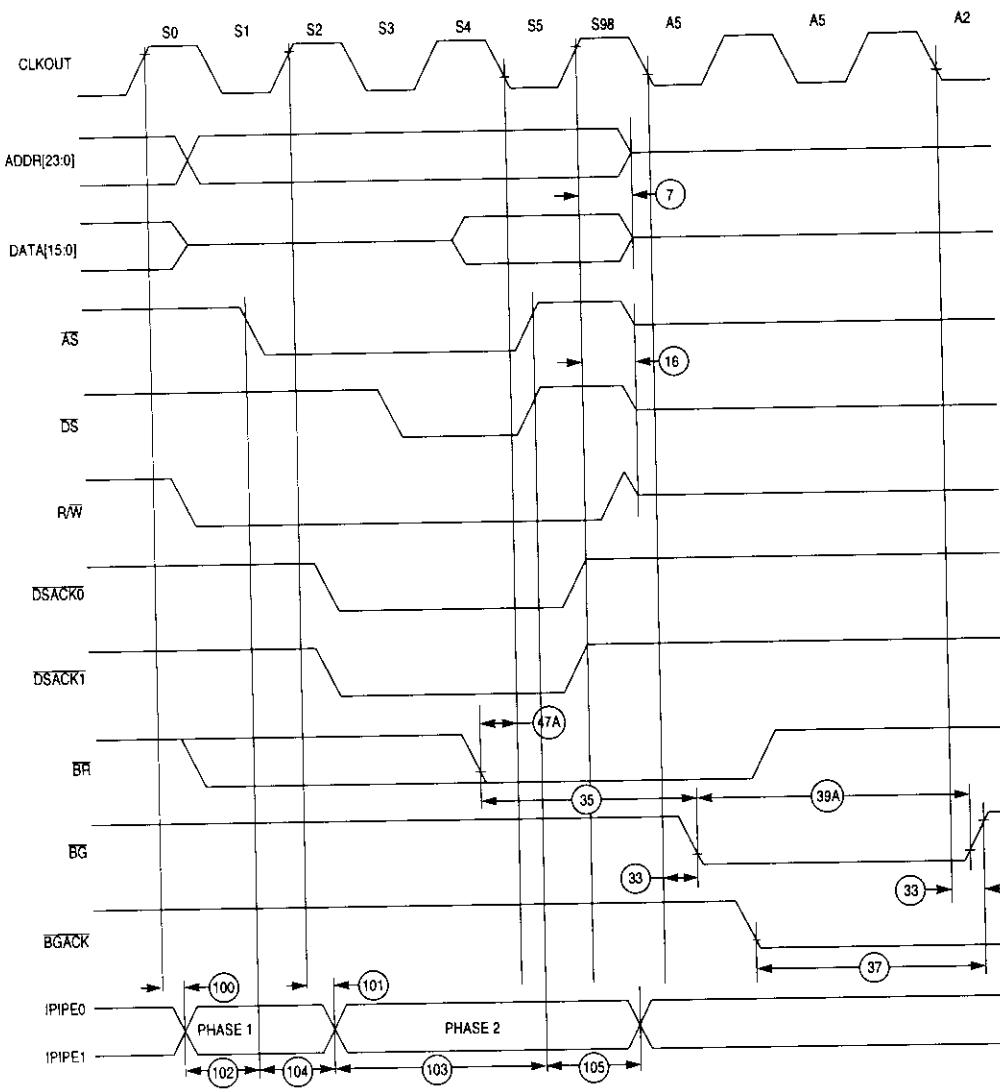

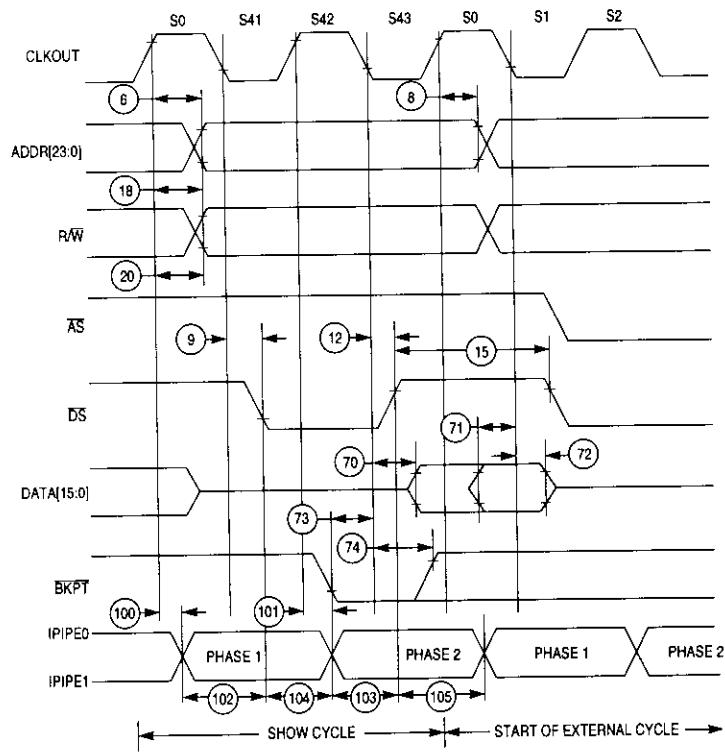

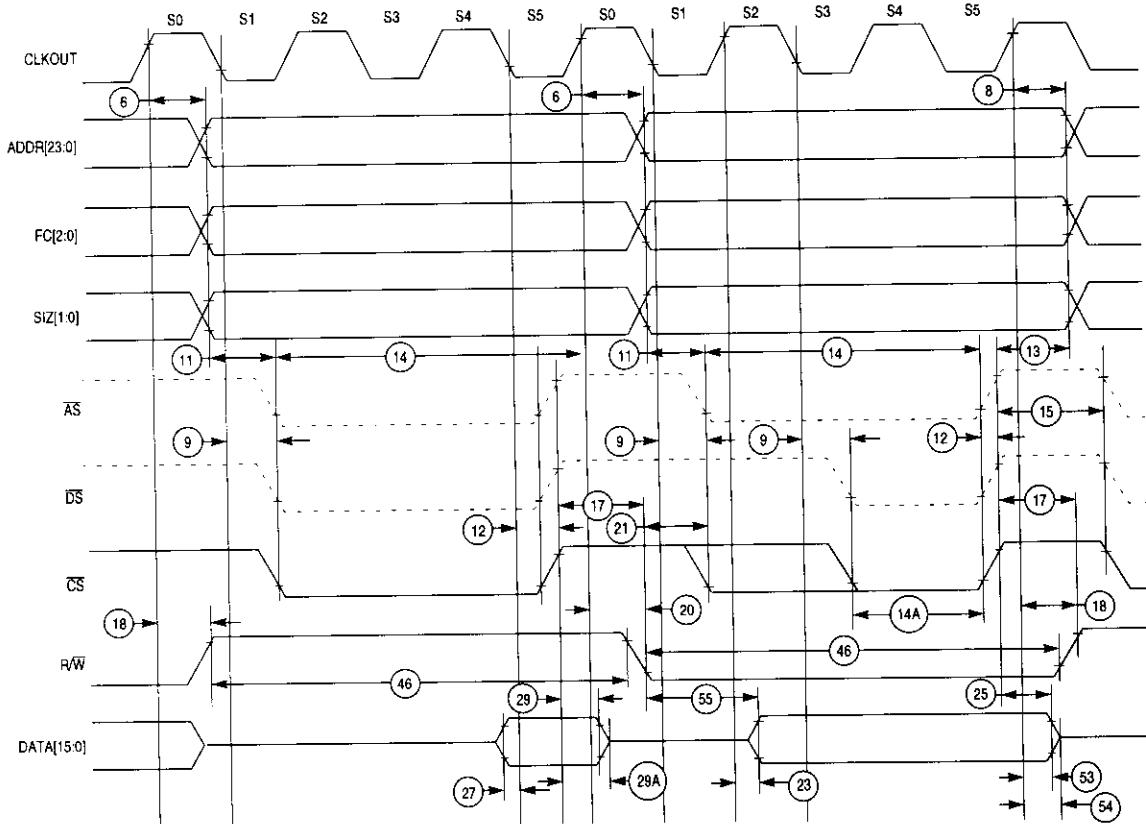

**Table A-6 AC Timing** $(V_{DD} \text{ and } V_{DDSYN} = 5.0 \text{ Vdc} \pm 5\%, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H)^1$

| Num    | Characteristic                                                                                      | Symbol             | Min                   | Max    | Unit |

|--------|-----------------------------------------------------------------------------------------------------|--------------------|-----------------------|--------|------|

| F1     | Frequency of Operation <sup>2</sup>                                                                 | f                  | 4 (f <sub>ref</sub> ) | 25.166 | MHz  |

| 1      | Clock Period                                                                                        | t <sub>cyc</sub>   | 39.7                  | —      | ns   |

| 1A     | ECLK Period                                                                                         | t <sub>Ecyc</sub>  | 318                   | —      | ns   |

| 1B     | External Clock Input Period <sup>3</sup>                                                            | t <sub>Xcyc</sub>  | 39.7                  | —      | ns   |

| 2, 3   | Clock Pulse Width                                                                                   | t <sub>CW</sub>    | 15                    | —      | ns   |

| 2A, 3A | ECLK Pulse Width                                                                                    | t <sub>ECW</sub>   | 155                   | —      | ns   |

| 2B, 3B | External Clock Input High/Low Time <sup>3</sup>                                                     | t <sub>XCHL</sub>  | 19.8                  | —      | ns   |

| 4, 5   | CLKOUT Rise and Fall Time                                                                           | t <sub>Cr</sub>    | —                     | 5      | ns   |

| 4A, 5A | Rise and Fall Time (All Outputs except CLKOUT)                                                      | t <sub>r</sub>     | —                     | 8      | ns   |

| 4B, 5B | External Clock Input Rise and Fall Time <sup>4</sup>                                                | t <sub>XCr</sub>   | —                     | 4      | ns   |

| 6      | Clock High to ADDR, FC, SIZE Valid                                                                  | t <sub>CHAV</sub>  | 0                     | 19     | ns   |

| 7      | Clock High to ADDR, Data, FC, SIZE, High Impedance                                                  | t <sub>CHAZx</sub> | 0                     | 39     | ns   |

| 8      | Clock High to ADDR, FC, SIZE, Invalid                                                               | t <sub>CHAZn</sub> | 0                     | —      | ns   |

| 9      | Clock Low to $\overline{AS}$ , $\overline{DS}$ , $\overline{CS}$ Asserted                           | t <sub>CLSA</sub>  | 2                     | 19     | ns   |

| 9A     | $\overline{AS}$ to $\overline{DS}$ or $\overline{CS}$ Asserted (Read) <sup>5</sup>                  | t <sub>STSA</sub>  | -10                   | 15     | ns   |

| 11     | ADDR, FC, SIZE Valid to $\overline{AS}$ , $\overline{CS}$ , (and $\overline{DS}$ Read) Asserted     | t <sub>AVSA</sub>  | 8                     | —      | ns   |

| 12     | Clock Low to $\overline{AS}$ , $\overline{DS}$ , $\overline{CS}$ Negated                            | t <sub>CLSN</sub>  | 2                     | 19     | ns   |

| 13     | $\overline{AS}$ , $\overline{DS}$ , $\overline{CS}$ Negated to ADDR, FC SIZE Invalid (Address Hold) | t <sub>SNAI</sub>  | 8                     | —      | ns   |

| 14     | $\overline{AS}$ , $\overline{CS}$ (and $\overline{DS}$ Read) Width Asserted                         | t <sub>SWA</sub>   | 65                    | —      | ns   |

| 14A    | $\overline{DS}$ , $\overline{CS}$ Width Asserted (Write)                                            | t <sub>SWAW</sub>  | 25                    | —      | ns   |

| 14B    | $\overline{AS}$ , $\overline{CS}$ (and $\overline{DS}$ Read) Width Asserted (Fast Cycle)            | t <sub>SWDW</sub>  | 22                    | —      | ns   |

| 15     | $\overline{AS}$ , $\overline{DS}$ , $\overline{CS}$ Width Negated <sup>6</sup>                      | t <sub>SN</sub>    | 22                    | —      | ns   |

| 16     | Clock High to $\overline{AS}$ , $\overline{DS}$ , R/W High Impedance                                | t <sub>CHSZ</sub>  | —                     | 39     | ns   |

| 17     | $\overline{AS}$ , $\overline{DS}$ , $\overline{CS}$ Negated to R/W High                             | t <sub>SNRN</sub>  | 10                    | —      | ns   |

| 18     | Clock High to R/W High                                                                              | t <sub>CHRH</sub>  | 0                     | 19     | ns   |

| 20     | Clock High to R/W Low                                                                               | t <sub>CHRL</sub>  | 0                     | 19     | ns   |

| 21     | R/W High to $\overline{AS}$ , $\overline{CS}$ Asserted                                              | t <sub>RAAA</sub>  | 10                    | —      | ns   |

| 22     | R/W Low to $\overline{DS}$ , $\overline{CS}$ Asserted (Write)                                       | t <sub>RASA</sub>  | 40                    | —      | ns   |

| 23     | Clock High to Data Out Valid                                                                        | t <sub>CHDO</sub>  | —                     | 19     | ns   |

| 24     | Data Out Valid to Negating Edge of $\overline{AS}$ , $\overline{CS}$ (Fast Write Cycle)             | t <sub>DVASN</sub> | 7                     | —      | ns   |

| 25     | $\overline{DS}$ , $\overline{CS}$ Negated to Data Out Invalid (Data Out Hold)                       | t <sub>SNDOI</sub> | 5                     | —      | ns   |

| 26     | Data Out Valid to $\overline{DS}$ , $\overline{CS}$ Asserted (Write)                                | t <sub>DVSA</sub>  | 8                     | —      | ns   |

**Table A-6 AC Timing (Continued)**

( $V_{DD}$  and  $V_{DDSYN} = 5.0$  Vdc  $\pm 5\%$ ,  $V_{SS} = 0$  Vdc,  $T_A = T_L$  to  $T_H$ )<sup>1</sup>

| Num | Characteristic                                                                           | Symbol      | Min | Max | Unit      |

|-----|------------------------------------------------------------------------------------------|-------------|-----|-----|-----------|

| 27  | Data In Valid to Clock Low (Data Setup)                                                  | $t_{DICL}$  | 5   | —   | ns        |

| 27A | Late BERR, HALT Asserted to Clock Low (Setup Time)                                       | $t_{BELCL}$ | 10  | —   | ns        |

| 28  | $\overline{AS}$ , $\overline{DS}$ Negated to DSACK[1:0], BERR, HALT, AVEC Negated        | $t_{SNDN}$  | 0   | 50  | ns        |

| 29  | $\overline{DS}$ , $\overline{CS}$ Negated to Data In Invalid (Data In Hold) <sup>7</sup> | $t_{SNDI}$  | 0   | —   | ns        |

| 29A | $\overline{DS}$ , $\overline{CS}$ Negated to Data In High Impedance <sup>7, 8</sup>      | $t_{SHDI}$  | —   | 45  | ns        |

| 30  | CLKOUT Low to Data In Invalid (Fast Cycle Hold) <sup>7</sup>                             | $t_{CLDI}$  | 8   | —   | ns        |

| 30A | CLKOUT Low to Data In High Impedance <sup>7</sup>                                        | $t_{CLDH}$  | —   | 60  | ns        |

| 31  | DSACK[1:0] Asserted to Data In Valid <sup>9</sup>                                        | $t_{DADI}$  | —   | 35  | ns        |

| 33  | Clock Low to $\overline{BG}$ Asserted/Negated                                            | $t_{CLBAN}$ | —   | 19  | ns        |

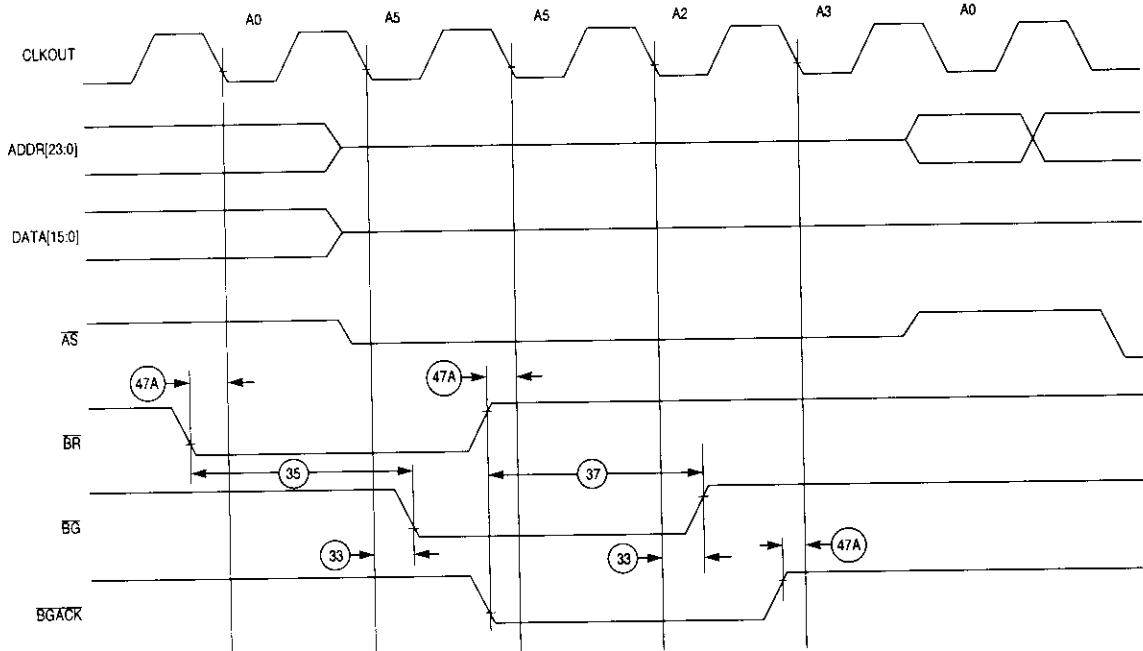

| 35  | BR Asserted to $\overline{BG}$ Asserted <sup>10</sup>                                    | $t_{BRAGA}$ | 1   | —   | $t_{cyc}$ |

| 37  | BGACK Asserted to $\overline{BG}$ Negated                                                | $t_{GAGN}$  | 1   | 2   | $t_{cyc}$ |

| 39  | $\overline{BG}$ Width Negated                                                            | $t_{GH}$    | 2   | —   | $t_{cyc}$ |

| 39A | $\overline{BG}$ Width Asserted                                                           | $t_{GA}$    | 1   | —   | $t_{cyc}$ |

| 46  | R/W Width Asserted (Write or Read)                                                       | $t_{RWA}$   | 90  | —   | ns        |

| 46A | R/W Width Asserted (Fast Write or Read Cycle)                                            | $t_{RWAS}$  | 55  | —   | ns        |

| 47A | Asynchronous Input Setup Time<br>BR, BGACK, DSACK[1:0], BERR, AVEC, HALT                 | $t_{AIST}$  | 5   | —   | ns        |

| 47B | Asynchronous Input Hold Time                                                             | $t_{AIHT}$  | 10  | —   | ns        |

| 48  | DSACK[1:0] Asserted to BERR, HALT Asserted <sup>11</sup>                                 | $t_{DABA}$  | —   | 27  | ns        |

| 53  | Data Out Hold from Clock High                                                            | $t_{DOCH}$  | 0   | —   | ns        |

| 54  | Clock High to Data Out High Impedance                                                    | $t_{CHDH}$  | —   | 23  | ns        |

| 55  | R/W Asserted to Data Bus Impedance Change                                                | $t_{RADC}$  | 25  | —   | ns        |