---

COMPAL Electronics, INC.

---

# **5G RML-N2x Module**

## **User Manual**

Update date : Oct 15, 2024

## Copyright

Copyright © 2024 COMPAL ELECTRONICS, INC. All rights reserved.

Without the prior written permission of the copyright holder, any company or individual is prohibited to excerpt, copy any part of or the entire document, or distribute the document in any form.

## Notice

The document is subject to update from time to time owing to the product version upgrade or other reasons. Unless otherwise specified, the document only serves as the user guide. All the statements, information and suggestions contained in the document do not constitute any explicit or implicit guarantee.

### Revision History

| Version | Date          | Name   | Major Changes                                                                                         |

|---------|---------------|--------|-------------------------------------------------------------------------------------------------------|

| AA      | July 01, 2024 | HW V01 | First release                                                                                         |

| AB      | Oct 15, 2024  | HW V02 | <ul style="list-style-type: none"><li>● Update Ch.2.1</li><li>● Update Antenna port mapping</li></ul> |

|         |               |        |                                                                                                       |

|         |               |        |                                                                                                       |

|         |               |        |                                                                                                       |

### Applicability Table

| No. | Product model | Description                                                                                                                                                 |

|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ZLN1          | 5G RML-N2x: (V01 module)<br><u>All relevant LGA HW spec , figures and design guidelines in this document are common specification for All 5G LGA model.</u> |

|     |               |                                                                                                                                                             |

#### Noted: Sample testing Scope and intended audience

When module version is Engineering samples (ES) and used in the early stages of development. This means these devices undergo limited testing and sometimes have significant feature limitations. They are suitable to assist with printed circuit board development, to conduct board-level electrical evaluation tests, and to explore manufacturing considerations.

Engineering samples should not be used for product-level & reliability qualification, power consumption optimize, and we also do not provide RMA analysis services on this version samples.

## Content

|           |                                   |           |

|-----------|-----------------------------------|-----------|

| <b>1.</b> | <b>Foreword .....</b>             | <b>5</b>  |

| 1.1       | Introduction .....                | 5         |

| 1.2       | Safety Information .....          | 5         |

| <b>2.</b> | <b>Overview.....</b>              | <b>9</b>  |

| 2.1       | Introduction .....                | 9         |

| 2.2       | Specification .....               | 9         |

| 2.3       | Operating Band.....               | 12        |

| 2.4       | Transmitting Power.....           | 13        |

| 2.5       | Receiver Sensitivity .....        | 13        |

| 2.6       | RF Antenna Interface .....        | 14        |

| <b>3.</b> | <b>Application Interface.....</b> | <b>17</b> |

| 3.1       | LGA Interface .....               | 17        |

| 3.2       | Pin Map.....                      | 17        |

| 3.2.1     | Pin Definition.....               | 17        |

## 1. Foreword

### 1.1 Introduction

This document describes the hardware of the COMPAL® 5G LGA Module product. It helps you quickly retrieve interface specifications, electrical and mechanical details, and information on the requirements to be considered for integrating further components. **All relevant LGA HW spec 、figures and design guidelines in this document are common specification for All 5G LGA mode.**

### 1.2 Safety Information

The following safety precautions must be observed during all phases of operation, such as usage, service or repair of any cellular terminal or mobile incorporating with 5G LGA module. Manufacturers of the cellular terminal should send the following safety information to users and operating personnel, and incorporate these guidelines into all manuals supplied with the product. If not so, we assume no liability for customers 'failure to comply with these precautions.

Full attention must be given to driving at all times in order to reduce the risk of an accident. Using a mobile while driving (even with a handsfree kit) causes distraction and can lead to an accident. Please comply with laws and regulations restricting the use of wireless devices while driving.

Switch off the cellular terminal or mobile before boarding an aircraft. The operation of wireless appliances in an aircraft is forbidden to prevent interference with communication systems. If the device offers an Airplane Mode, then it should be enabled prior to boarding an aircraft. Please consult the airline staff for more restrictions on the use of wireless devices on boarding the aircraft.

Wireless devices may cause interference on sensitive medical equipment, so please be aware of the restrictions on the use of wireless devices when in hospitals, clinics or other healthcare facilities.

**SOS**

Cellular terminals or mobiles operating over radio signals and cellular network cannot be guaranteed to connect in all possible conditions (for example, with unpaid bills or with an invalid SIM card). When emergent help is needed in such conditions, please remember using emergency call. In order to make or receive a call, the cellular terminal or mobile must be switched on in a service area with adequate cellular signal strength.

The cellular terminal or mobile contains a transmitter and receiver. When it is ON, it receives and transmits radio frequency signals. RF interference can occur if it is used close to TV set, radio, computer or other electric- equipment.

In locations with potentially explosive atmospheres, obey all posted signs to turn off wireless devices such as your phone or other cellular terminals. Areas with potentially explosive atmospheres include fueling areas, below decks on boats, fuel or chemical transfer or storage facilities, areas where the air contains chemicals or particles such as grain, dust or metal powders, etc.

## Safety of Children

Do not allow children to use the wireless device without guidance. Small and sharp components of the wireless device may cause danger to children or cause suffocation if children swallow the components.

## Environment Protection

Observe the local regulations regarding the disposal of your packaging materials, used wireless device and accessories, and promote their recycling.

## WEEE Approval

The wireless device is in compliance with the essential requirements and other relevant provisions of the Waste Electrical and Electronic Equipment Directive 2012/19/EU (WEEE Directive).

## RoHS Approval

The wireless device is in compliance with the restriction of the use of certain hazardous substances in electrical and electronic equipment Directive 2011/65/EU (RoHS Directive).

## 2. Overview

### 2.1 Introduction

RML-N2x is a highly integrated 5G NR wireless communication module that adopts standard PCIe interface and backward supports with LTE system. It is applicable to most broadband communication networks of the mobile operator across the world. **All relevant LGA HW spec、figures and design guidelines in this document are common specification for All 5G LGA mode.**

### 2.2 Specification

Table 2-1 LGA module features

| Specification                |                                                                                                                                                |                                         |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Platform                     | MTK MT6990 Quad-core Arm® Cortex-A55 MPCore™ 2.0GHz boost 2.2GHz                                                                               |                                         |

| Memory                       | Support LPDDR4 2GB, eMMC Flash 32GB ( <b>Optional</b> )                                                                                        |                                         |

| Operating Band<br>(Full SKU) | 5G <ul style="list-style-type: none"><li>• n29, n66, n70, n71</li></ul> Simultaneous GPS:<br>L1/L5, GLONASS(GLO), Galileo(GAL) and BeiDou(BDS) |                                         |

| Network option               | SA                                                                                                                                             | Option 2                                |

|                              | NSA                                                                                                                                            | Option 3x/3a                            |

| Downlink                     | LTE                                                                                                                                            | N/A                                     |

|                              | 5G sub-6                                                                                                                                       | 4CC; Max aggregated BW 300MHz; MIMO 4x4 |

| Uplink                       | LTE                                                                                                                                            | N/A                                     |

|                              | 5G sub-6                                                                                                                                       | 2CC SISO / 1CC MIMO 2x2                 |

| HPUE ( Class 2)              | n66, n70, n71                                                                                                                                  |                                         |

| UL 2x2 MIMO                  | n66, n70, n71                                                                                                                                  |                                         |

| DL 4x4 MIMO                  | All bands                                                                                                                                      |                                         |

| TAS                          | Support                                                                                                                                        |                                         |

| Carrier aggregation          | UL_CA/DL_CA/EN-DC                                                                                                                              |                                         |

| Power Supply                 | DC 3.4V~4.4V(Typical value is 4.2V)                                                                                                            |                                         |

| Temperature                  | Operating temperature <sup>[1]</sup> : -30°C ~+75°C                                                                                            |                                         |

|                          |                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Extended temperature <sup>[2]</sup> : -40°C ~+85°C                                                                                                                                                                                                                                                                              |

|                          | Storage temperature: -40°C ~+85°C                                                                                                                                                                                                                                                                                               |

| Physical characteristics | Dimension:45x45mm, Thickness=2.65mm(typ.)                                                                                                                                                                                                                                                                                       |

|                          | Weight: 14g ±0.3g                                                                                                                                                                                                                                                                                                               |

| <b>Interface</b>         |                                                                                                                                                                                                                                                                                                                                 |

| Antenna Port             | 4G/Sub-6G Antenna x 4 and GPS Antenna x 1                                                                                                                                                                                                                                                                                       |

|                          | Support 4x4 MIMO                                                                                                                                                                                                                                                                                                                |

| Function Interface       | DSSA (Dual SIM, Single Active)<br>SIM1 & SIM2, The SIM2 can be applied for ESIM (without SIM2 hotswap)                                                                                                                                                                                                                          |

|                          | I2S for Audio x 1                                                                                                                                                                                                                                                                                                               |

|                          | USB 2.0 HS or USB 3.2 Gen2 SS                                                                                                                                                                                                                                                                                                   |

|                          | UART0 2-wire UART for Debug<br>UART2 4-wire UART for Bluetooth command                                                                                                                                                                                                                                                          |

|                          | GPIO (General-Purpose I/O) x 11pin<br>Reserve Column Key x 2pin, Row Key x 3pin, it also can be used for GPIO Purpose<br>Reserve RF BPI Interface x 11, it also can be used for GPIO Purpose (only Pin242 need to pull low for detected as a client version, CUST Board)<br>Reserve OTG ID detection pin x 1 and Enable Pin x 1 |

|                          | Power on/off switch key pin<br>Support Cable Power On<br>Reserve FULL_CARD_POWER_OFF pin for module power enable/disable pin                                                                                                                                                                                                    |

|                          | Hardware reset pin                                                                                                                                                                                                                                                                                                              |

|                          | SPI interface x 1                                                                                                                                                                                                                                                                                                               |

|                          | SDIO 3.0 interface                                                                                                                                                                                                                                                                                                              |

|                          | DSI x1 (4lane) and DBI-C x1 (DBI IF only support type C) for LCM interface<br>(It needs to check if SW can support the driver or not)                                                                                                                                                                                           |

|                          | LED SINK control pin x3 (Support up to 12 mA) and PWM control pin x1 for LCM backlight                                                                                                                                                                                                                                          |

|                          | I2C Interface x2                                                                                                                                                                                                                                                                                                                |

|                          | Tunable antenna(3xMIPI)                                                                                                                                                                                                                                                                                                         |

|                 | PCIe Gen3 2-lane x2 (For MTK Wifi 802.11ax solution: MT7915)<br>PCIe Gen3 1-lane x 1 (Reserve)                                                                  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | USXGMII x2 (Support 1Gbit and 2.5Gbit Ethernet interface, additional components are required on the circuit), <b>RML-N2x default support SGMII/HSGMII only.</b> |

|                 | Others Interface: (The trigger and read control de-pend on SW)<br>AUXADC (PM6685) 15bit x 2pin<br>AUXADC (PM6361) 12bit x 3pin                                  |

|                 | Power supply: (Reserve)<br>a.Dual Voltage Support LV 1.8V/HV 3V IF for SIM Card Power.                                                                          |

| Software        |                                                                                                                                                                 |

| Driver          | Linux kernel <sup>[3]</sup>                                                                                                                                     |

| Protocol Stack  | IPV4/IPV6                                                                                                                                                       |

| AT commands     | 3GPP TS 27.007 and 27.005                                                                                                                                       |

| Firmware update | FOTA                                                                                                                                                            |

| Others feature  | Support 5G NR NSA and SA                                                                                                                                        |

|                 | Multiple carrier aggregation                                                                                                                                    |

|                 | AGNSS                                                                                                                                                           |

| Management tool | WebUI for user (Monitor data usage, manage device & network settings),<br>and Debug screen for engineer                                                         |

**▲ NOTE:**

[1] To meet this operating temperature range, you need to ensure effective thermal dissipation, for example, by adding passive or active heatsinks, heat pipes, vapor chambers, etc. Within this range, the module can meet 3GPP.

[2] To meet this extended temperature range, you need to ensure effective thermal dissipation, for example, by adding passive or active heatsinks, heat pipes, vapor chambers, etc.

When the LGA module works at this temperature, the module remains the ability to establish and maintain functions such as Voice, SMS, emergency call, etc.

Radio spectrum and radio network are not influenced, while one or more specifications, such as Pout, may undergo a reduction in value, exceeding the specified tolerances of 3GPP.

[3] SW driver plan to support Android platform.

## 2.3 Operating Band

The 5G LGA Module operating bands of the antennas are as follows Table 4-1:

Table 4-2 Full SKU operating

| Band name | Tx (MHz)    | Rx (MHz)    | LTE | 5G NR |

|-----------|-------------|-------------|-----|-------|

| FLO       | N/A         | 716 - 728   |     | n29   |

| B66       | 1710 - 1780 | 2110 - 2200 |     | n66   |

| B70       | 1695 - 1710 | 1995 - 2020 |     | n70   |

| B71       | 663 - 698   | 617 - 652   |     | n71   |

## 2.4 Transmitting Power

The transmitting power for each band of the LGA module as shown in the following table:

Table 4-3 Full SKU NR-FR1 FDD

| Mode   | Band     | Typical Value (dBm) | Tolerance |

|--------|----------|---------------------|-----------|

| NR-FR1 | n66      | 23                  | ±2        |

|        | n66 MIMO | 26                  | ±2        |

|        | n70      | 23                  | ±2        |

|        | n70 MIMO | 26                  | ±2        |

|        | n71      | 23                  | ±2        |

|        | n71 MIMO | 26                  | ±2        |

**▲ NOTE**

If device is operated in EN-DC mode, total TX power would be “LTE + NR  $\leq 23 \pm 2$ ” due to power sharing algorithm.

## 2.5 Receiver Sensitivity

The receiver sensitivity for each band of the 5G LGA Module as shown in the following table:

Table 4-4 Full SKU NR band

| Mode          | Band | Single Port |            |                 |                 | Combined Port |           |

|---------------|------|-------------|------------|-----------------|-----------------|---------------|-----------|

|               |      | PRx (Typ.)  | DRx (Typ.) | PRx MIMO (Typ.) | DRx MIMO (Typ.) | 4-RX          | 3GPP spec |

| NR(10MHZ,15K) | n29  | TBD         | TBD        | TBD             | TBD             | TBD           | -96.5     |

| NR(20MHZ,15K) | n66  | TBD         | TBD        | TBD             | TBD             | TBD           | -96       |

| NR(20MHZ,15K) | n70  | TBD         | TBD        | TBD             | TBD             | TBD           | -96.5     |

| NR(20MHZ,15K) | n71  | TBD         | TBD        | TBD             | TBD             | TBD           | -88.7     |

**▲ NOTE**

The above values are measured in one antenna situation.

## 2.6 RF Antenna Interface

The LGA module provides Nine antenna pads (ANT0~ANT8) for connecting the external antennas. (default is NC)

The RF pad difference is the most important difference between LGA modules; please refer to 45 mm x 45 mm LGA Module Hardware Migration Guide.

Route the antenna pad as close as possible to antenna connector. In addition, the impedance of RF signal traces must be 50 Ω.

Figure 3-1 Antenna port location

| Pin | ANT No. |

|-----|---------|

| 169 | ANT_0   |

| 193 | ANT_1   |

| 205 | ANT_2   |

| 217 | ANT_3   |

| 233 | ANT_4   |

| 181 | N/C     |

| 228 | N/C     |

| 158 | N/C     |

| 203 | N/C     |

Figure 3-2 Definition of the antenna pinout location

Table 3-5 Definition of the antenna port mapping

| Frequency |              | Ant_0                  | Ant_1 | Ant_2                  | Ant_3 | Ant_4 |

|-----------|--------------|------------------------|-------|------------------------|-------|-------|

| LB        | 600–960MHz   | Tx0 <sup>1</sup> /PRx2 | DRx2  | Tx1/PRX                | DRx   |       |

| MHB       | 1710–2690MHz | Tx0/PRX                | DRx   | Tx1 <sup>1</sup> /DRX2 | PRx2  |       |

| n41       | 2496–2690    | Tx0 <sup>1</sup> /PRx2 | DRx2  | Tx1/DRX                | PRx   |       |

| n77       | 3300–5000MHz | Tx0 <sup>1</sup> /DRX  | DRX2  | Tx1/PRx                | PRx2  |       |

| GPS L1    | 1575–1610MHz |                        |       |                        |       | Rx    |

| GPS L5    | 1176MHz      |                        |       |                        |       | Rx    |

**Note.1:**

For UL 2x2 MIMO , MB+MB/LB+LB ENDC/LTE UL CA/NR ULCA

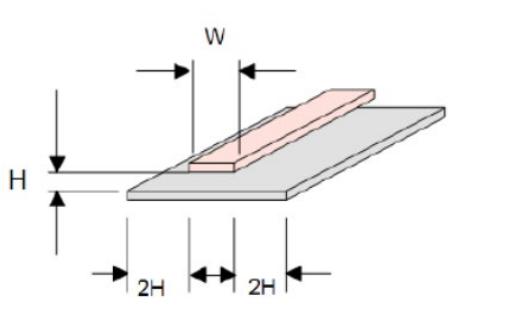

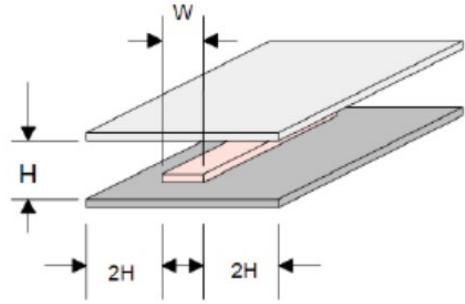

For the PCB designed by the user, the impedance of all the RF signal tracks must be  $50 \Omega$ . Generally, the impedance depends on the medium factor, track width, and distance from the floor.

In order to reflect the rules of design, the following figures indicate the complete structure of the microstrip and stripline with an impedance of  $50 \Omega$  as well as the reference design for stack.

Figure 3-3 Complete structure of the microstrip

Figure 3-4 Complete structure of the stripline

Please use impedance simulation tool to calculate RF MAIN pad impedance. The RF MAIN pad dimension of LGA module is  $\Phi 0.8\text{mm}$ . You can get the impedance with lower than  $50 \Omega$  calculated by the impedance simulation tool. Since the target impedance is  $50 \Omega$  for RF trace, the recommended solution is that to carve out the copper area of the second layer that projected by the RF MAIN pad at top layer. How many layers should be carved out depend on the PCB permittivity, track width, and distance from the floor of your own PCB. Our target is to make the RF MAIN pad impedance as closer to  $50 \Omega$  as possible.

Table 3-6

| Rated Condition          | Environment Condition |

|--------------------------|-----------------------|

| Frequency Range          | DC to 6GHz            |

| Characteristic Impedance | 50Ω                   |

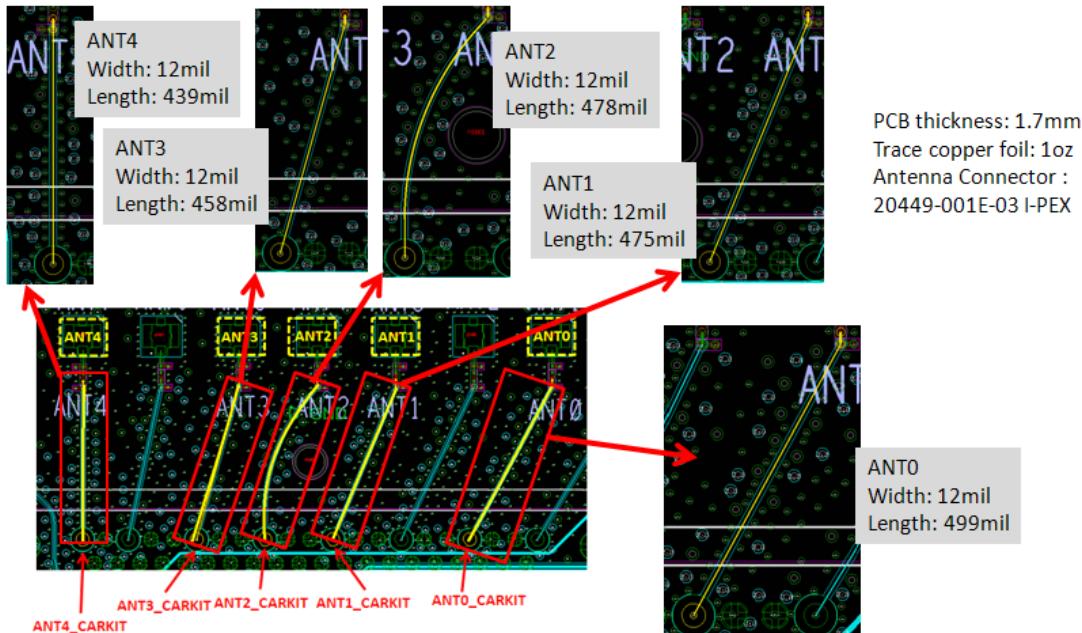

### Trace design

The trace from module transmitter to antenna connector on the EVB must be maintained identical as the above specification with i-pepx connector. Only trace designs approved by the module original grantee or through permissive change can be used by an host manufacturer. Any changes are deemed as antenna type change and should be reviewed to ensure compliance with the FCC regulation rules.

Verification must be conducted and the results shall not exceed below ranges to ensure identical antenna design is applied to subsequent integration and end product production.

### Test procedures of Verification

1. Set Transmission in the supported modulation mode, band and Channel.

2. Verify RF tuned-up power through conducted measurement with appropriate cable loss. The KDB guidance 971168 D01 can be followed to obtain the measurement results.

3. Verify the RF output power results obtained if it's accordance with the datasheet and test reports.

### 3. Application Interface

#### 3.1 LGA Interface

The RML-N2x uses a 412-pin LGA as its external interface. For details about the module and dimensions, see 5.4 Dimensions and Interfaces

#### 3.2 Pin Map

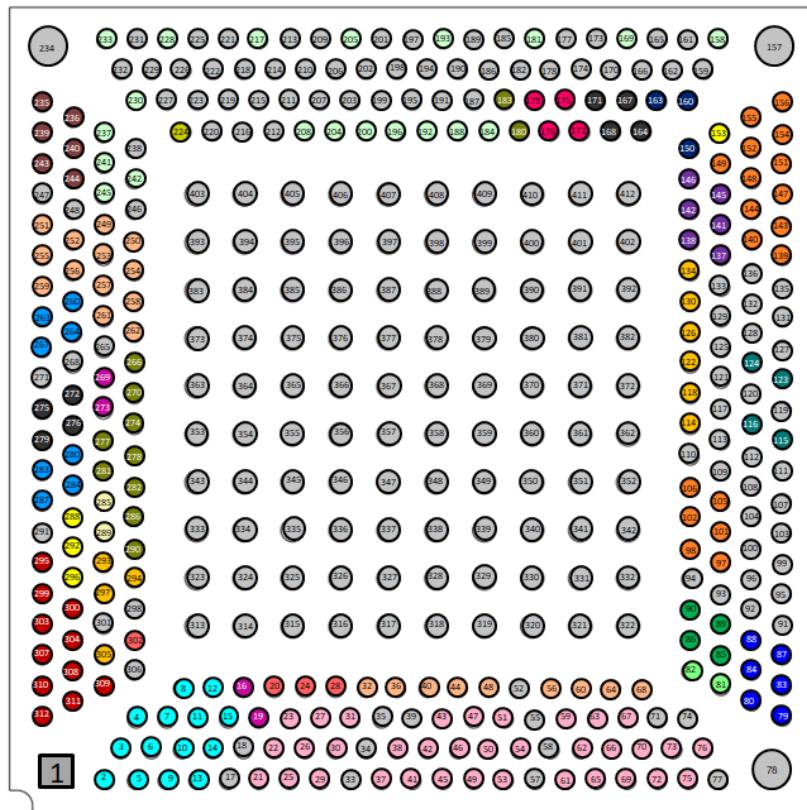

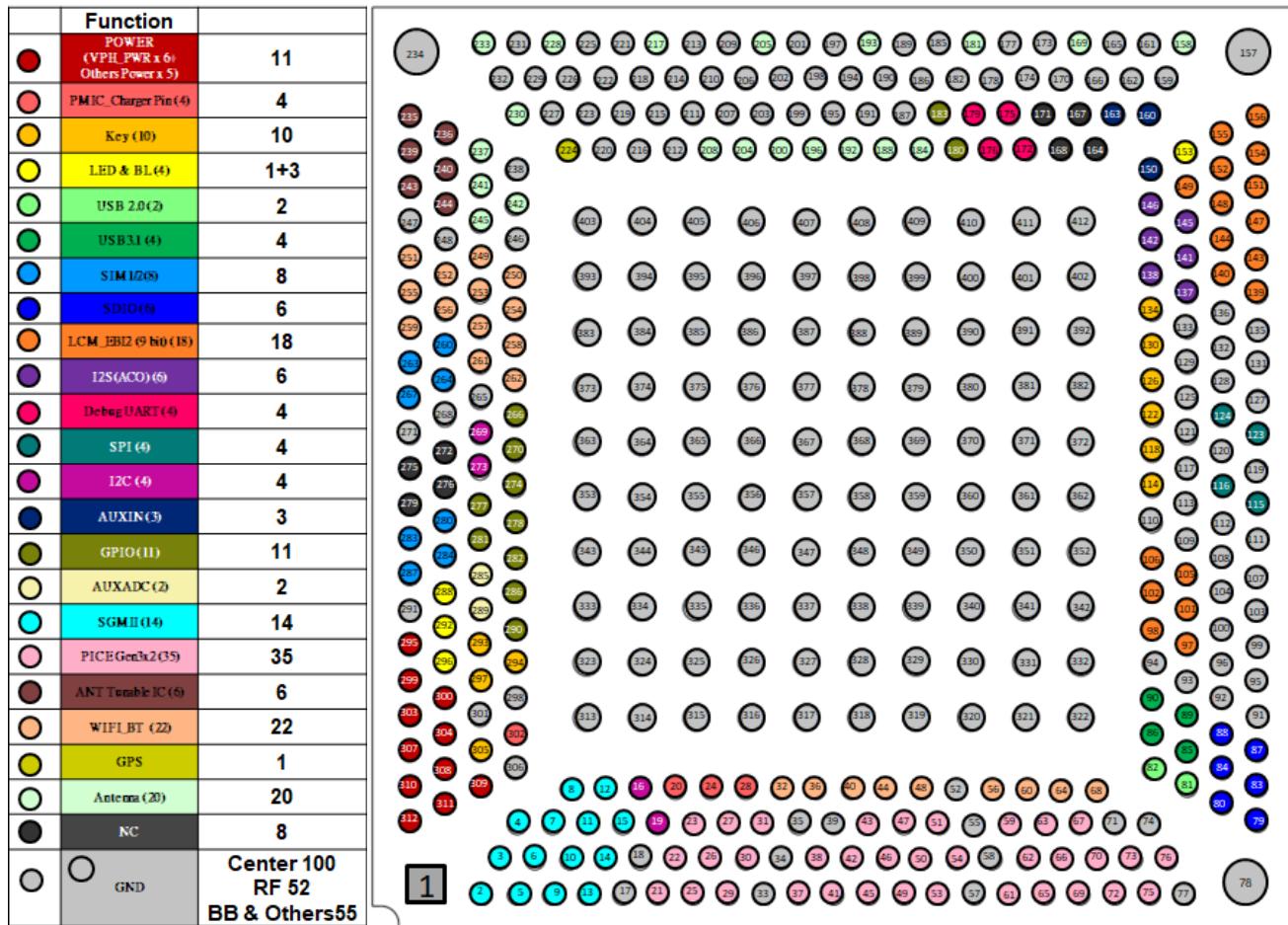

Figure 3-1 PAD Sequence of LGA module (Perspective View from TOP Side)

#### 3.2.1 Pin Definition

The pin definition is as follows Table 3-1:

Table 3-1 pin definition

| Pin NO. | Pin Name      | I/O | Pin Description       | Type(V) |

|---------|---------------|-----|-----------------------|---------|

| 2       | USXGMII_1_RXN | AI  | USXGMII IF RX Lane1_N |         |

| 3       | USXGMII_1_RXP | AI  | USXGMII IF RX Lane1_P |         |

| 4       | GBE1_INT      | DIO | Ethernet control pin  | 1.8V    |

| 5       | USXGMII_1_TXP | AO  | USXGMII IF TX Lane1_P |         |

| 6       | USXGMII_1_TXN | AO  | USXGMII IF TX Lane1_N |         |

|    |                |     |                                                                        |      |

|----|----------------|-----|------------------------------------------------------------------------|------|

| 7  | GBE1_RST       | DIO | Ethernet control pin                                                   | 1.8V |

| 8  | GBE0_RST       | DIO | Ethernet control pin                                                   | 1.8V |

| 9  | USXGMII_0_RXN  | AI  | USXGMII IF RX Lane0_N                                                  |      |

| 10 | USXGMII_0_RXP  | AI  | USXGMII IF RX Lane0_P                                                  |      |

| 11 | MDIO           | DIO | Ethernet control pin management data clock                             | 1.8V |

| 12 | GBE0_INT       | DIO | Ethernet control pin                                                   | 1.8V |

| 13 | USXGMII_0_TXN  | AO  | USXGMII IF TX Lane0_N                                                  |      |

| 14 | USXGMII_0_TXP  | AO  | USXGMII IF TX Lane0_P                                                  |      |

| 15 | MDC            | DIO | Ethernet control pin management data clock                             | 1.8V |

| 16 | SCL4           | DIO | I2C IF Reserve for Codec IC                                            | 1.8V |

| 19 | SDA4           | DIO | I2C IF Reserve for Codec IC                                            | 1.8V |

| 20 | IDDIG          | DI  | For USB ID, for OTG2.0                                                 | 1.8V |

| 21 | PCIE_D_CLKP    | AIO | PCIE IF Clock (1lane)                                                  |      |

| 22 | PCIE_D_CLKN    | AIO | PCIE IF Clock (1lane)                                                  |      |

| 23 | PCIE3_PERSTN   | DIO | For PCIE Control Pin                                                   | 1.8V |

| 24 | USB_VBUSVALID  | DI  | Detect pin for check VBUS insert or not(1.8V IO)                       | 1.8V |

| 25 | PCIE_D_LN0_TXN | AO  | PCIE TX Lane0_N (1lane)                                                |      |

| 26 | PCIE_D_LN0_TXP | AO  | PCIE TX Lane0_P (1lane)                                                |      |

| 27 | PCIE3_CLKREQN  | DIO | For PCIE Control Pin                                                   | 1.8V |

| 28 | USB_DRVBUS     | DO  | OTG Enable Pin for charging IC                                         | 1.8V |

| 29 | PCIE_D_LN0_RXP | AI  | PCIE RX Lane0_P (1lane)                                                |      |

| 30 | PCIE_D_LN0_RXN | AI  | PCIE RX Lane0_N (1lane)                                                |      |

| 31 | PCIE3_PEWAKEN  | DIO | For PCIE Control Pin                                                   | 1.8V |

| 32 | PCM0_DO        | AIO | I2S or PCM reserve for WIFI/BT connectivity MT7915/MT7975              | 1.8V |

| 36 | PCM0_DI        | AIO | I2S or PCM reserve for WIFI/BT connectivity MT7915/MT7975              | 1.8V |

| 37 | PCIE_B_LN1_TXN | AO  | For PCIE TX Lane1_N<br>Reserve for WIFI/BT connectivity MT7915/MT7975. |      |

| 38 | PCIE_B_LN1_TXP | AO  | For PCIE TX Lane1_P<br>Reserve for WIFI/BT connectivity MT7915/MT7975. |      |

| 40 | PCM0_SYNC      | AIO | I2S or PCM reserve for WIFI/BT connectivity MT7915/MT7975              | 1.8V |

| 41 | PCIE_B_LN1_RXN | AI  | For PCIE RX Lane1_N<br>Reserve for WIFI/BT connectivity MT7915/MT7975. |      |

|    |                |     |                                                                               |      |

|----|----------------|-----|-------------------------------------------------------------------------------|------|

| 42 | PCIE_B_LN1_RXP | AI  | For PCIE RX Lane1_P<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.     |      |

| 43 | PCIE1_CLKREQN  | DIO | For PCIE Control Pin,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.   | 1.8V |

| 44 | WLAN_ACT_1     | DIO | Connsys Co-Ex Interface (1.8V)                                                | 1.8V |

| 45 | PCIE_B_CLKN    | AIO | For PCIE Clock IF<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.       |      |

| 46 | PCIE_B_CLKP    | AIO | For PCIE Clock IF<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.       |      |

| 47 | PCIE1_PERSTN   | DIO | For PCIE Control Pin,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.   | 1.8V |

| 48 | PCM0_CLK       | AIO | I2S or PCM reserve for WIFI/BT<br>connectivity MT7915/MT7975                  | 1.8V |

| 49 | PCIE_B_LN0_TXN | AO  | For PCIE TX Lane0_N<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.     |      |

| 50 | PCIE_B_LN0_TXP | AO  | For PCIE TX Lane0_P<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.     |      |

| 51 | PCIE1_PEWAKEN  | DIO | For PCIE Control Pin,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.   |      |

| 53 | PCIE_B_LN0_RXP | AI  | For PCIE RX Lane0_P<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.     |      |

| 54 | PCIE_B_LN0_RXN | AI  | For PCIE RX Lane0_N<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.     |      |

| 56 | BT_PRI_RXD_1   | DIO | Connsys Co-Ex Interface (1.8V)                                                | 1.8V |

| 59 | PCIE0_PEWAKEN  | DIO | For PCIE Control Pin,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.   |      |

| 60 | PTA_RX_1       | DIO | Connsys Co-Ex Interface (1.8V)                                                | 1.8V |

| 61 | PCIE_A_LN0_RXP | AI  | For PCIE IF RX Lane0_P,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975. |      |

| 62 | PCIE_A_LN0_RXN | AI  | For PCIE IF RX Lane0_N,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975. |      |

| 63 | PCIE0_PERSTN   | DIO | For PCIE Control Pin,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.   | 1.8V |

| 64 | PTA_TX_1       | DIO | Connsys Co-Ex Interface (1.8V)                                                | 1.8V |

|     |                |     |                                                                               |      |

|-----|----------------|-----|-------------------------------------------------------------------------------|------|

| 65  | PCIE_A_LN0_TXP | AO  | For PCIE IF TX Lane0_P,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975. |      |

| 66  | PCIE_A_LN0_TXN | AO  | For PCIE IF TX Lane0_N,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975. |      |

| 67  | PCIE0_CLKREQN  | DIO | For PCIE Control Pin,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.   | 1.8V |

| 68  | BT_ACT_TXD_1   | DIO | Connssy Co-Ex Interface (1.8V)                                                | 1.8V |

| 69  | PCIE_A_LN1_RXP | AI  | For PCIE IF RX Lane1_P,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975. |      |

| 70  | PCIE_A_LN1_RXN | AI  | For PCIE IF RX Lane1_N,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975. |      |

| 72  | PCIE_A_LN1_TXP | AO  | For PCIE IF TX Lane1_P,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975. |      |

| 73  | PCIE_A_LN1_TXN | AO  | For PCIE IF TX Lane1_N,<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975. |      |

| 75  | PCIE_A_CLKN    | AIO | For PCIE IF Clock<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.       |      |

| 76  | PCIE_A_CLKP    | AIO | For PCIE IF Clock<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.       |      |

| 79  | MSDC1_CLK      | B   | SDC clock                                                                     | 1.8  |

| 80  | MSDC1_DAT0     | DIO | SDC data bit 0                                                                | 1.8  |

| 81  | USB_DM         | AIO | For USB2.0 HS data minus                                                      |      |

| 82  | USB_DP         | AIO | For USB2.0 HS data plus                                                       |      |

| 83  | MSDC1_DAT1     | DIO | SDC data bit 1                                                                | 1.8  |

| 84  | MSDC1_DAT3     | DIO | SDC data bit 3                                                                | 1.8  |

| 85  | SSUSB_TXP      | AIO | For USB SS Tx plus                                                            |      |

| 86  | SSUSB_TXN      | AIO | For USB SS Tx minus                                                           |      |

| 87  | MSDC1_DAT2     | DIO | SDC data bit 2                                                                | 1.8  |

| 88  | MSDC1_CMD      | DO  | SDC command                                                                   | 1.8  |

| 89  | SSUSB_RXP      | AIO | For USB SS Rx plus                                                            |      |

| 90  | SSUSB_RXN      | AIO | For USB SS Rx minus                                                           |      |

| 97  | LPCE0B         | AIO | DBI-C Interface for LCM                                                       | 1.8  |

| 98  | LPA0           | AIO | DBI-C Interface for LCM                                                       | 1.8  |

| 101 | LSDI           | AIO | DBI-C Interface for LCM                                                       | 1.8  |

| 102 | LPRDB          | AIO | DBI-C Interface for LCM                                                       | 1.8  |

| 105 | LPWRB          | AIO | DBI-C Interface for LCM                                                       | 1.8  |

| 106 | LPRSTB         | AIO | DBI-C Interface for LCM                                                       | 1.8  |

| 114 | KPROW2         | DIO | Row Key 2                                                                     | 1.8V |

| 115 | SPI0_MI        | DIO | SPI0 master in, slave out                                                     | 1.8V |

| 116 | SPI0_CLK       | DIO | SPI0 Clock                                                                    | 1.8V |

|     |                  |     |                                                 |         |

|-----|------------------|-----|-------------------------------------------------|---------|

| 118 | KPCOL2           | DIO | Column Key 2                                    | 1.8V    |

| 122 | KPCOL1           | DIO | Column Key 1                                    | 1.8V    |

| 123 | SPI0_CS_B        | DIO | SPI0 chips select                               | 1.8V    |

| 124 | SPI0_MO          | DIO | SPI0 master out, slave in                       | 1.8V    |

| 126 | KPROW1           | DIO | Row Key 1                                       | 1.8V    |

| 130 | KPROW0           | DIO | Row Key 0                                       | 1.8V    |

| 134 | KPCOL0           | DIO | Column Key 0 (Use for Force DL, low to trigger) | 1.8V    |

| 137 | I2S0_LRCK        | DIO | Primary audio interface, MI2S word select       | 1.8V    |

| 138 | I2S0_BCK         | DIO | Primary audio interface, MI2S clock             | 1.8V    |

| 139 | DSI0_D0N         | AIO | MIPI DSI Interface for LCM                      |         |

| 140 | DSI0_D0P         | AIO | MIPI DSI Interface for LCM                      |         |

| 141 | I2S0_MCK         | DIO | Audio master clock                              | 1.8V    |

| 142 | I2S0_DI          | DIO | I2S reserve for Audio codec                     | 1.8V    |

| 143 | DSI0_D3P         | AIO | MIPI DSI Interface for LCM                      |         |

| 144 | DSI0_D3N         | AIO | MIPI DSI Interface for LCM                      |         |

| 145 | I2S0_DO          | DIO | I2S reserve for Audio codec                     | 1.8V    |

| 146 | I2S4_MCK         | DIO | Audio master clock                              | 1.8V    |

| 147 | DSI0_D1N         | AIO | MIPI DSI Interface for LCM                      |         |

| 148 | DSI0_D1P         | AIO | MIPI DSI Interface for LCM                      |         |

| 149 | LCM_RST          | AIO | GPIO Reserve for LCD Reset                      | 1.8V    |

| 150 | AUXIN1           | AIO | PMIC Side AUX Channel Reserve for ADC 12bit     | 0~1.98V |

| 151 | DSI0_CKP         | AIO | MIPI DSI Interface for LCM                      |         |

| 152 | DSI0_CKN         | AIO | MIPI DSI Interface for LCM                      |         |

| 153 | DISP_PWM         | DIO | Display PWM Output                              | 1.8V    |

| 154 | DSI0_D2P         | AIO | MIPI DSI Interface for LCM                      |         |

| 155 | DSI_TE           | AIO | GPIO Reserve for LCD tearing effect             | 1.8V    |

| 156 | DSI0_D2N         | AIO | MIPI DSI Interface for LCM                      |         |

| 158 | NC_ANT           |     | NC                                              |         |

| 160 | AUXIN3           | AIO | PMIC Side AUX Channel Reserve for ADC 12bit     | 0~1.98V |

| 163 | AUXIN5           | AIO | PMIC Side AUX Channel Reserve for ADC 12bit     | 0~1.98V |

| 169 | ANT0_CARKIT      |     | ANT0                                            |         |

| 172 | AP_UTXD0         | DO  | UART0 transmit data – (used for debug)          | 1.8V    |

| 175 | AP_URXD0         | DI  | UART0 receive data (used for debug)             | 1.8V    |

| 176 | AP_UTRS0         | DO  | UART0 RTS Require To Send                       | 1.8V    |

| 179 | AP_UCTS0         | DI  | UART0 CTS Clear To Send                         | 1.8V    |

| 180 | EINT10           | DIO | GPIO Reserve for EN Pin                         | 1.8V    |

| 181 | NC_ANT           |     | NC                                              |         |

| 183 | EINT7            | DIO | GPIO Reserve                                    | 1.8V    |

| 184 | BPI_D_BUS17_ANT0 |     | RF BPI IF                                       | 1.8V    |

| 188 | BPI_D_BUS18_ANT1 |     | RF BPI IF                                       | 1.8V    |

| 192 | BPI_D_BUS19_ANT2 |     | RF BPI IF                                       | 1.8V    |

| 193 | ANT1_CARKIT      |     | ANT1                                            |         |

| 196 | BPI_D_BUS20_ANT3 |     | RF BPI IF                                       | 1.8V    |

|     |                       |     |                                                                                                                     |      |

|-----|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------|------|

| 200 | BPI_D_BUS16_OLAT5     |     | RF BPI IF                                                                                                           | 1.8V |

| 204 | BPI_D_BUS21_ANT4      |     | RF BPI IF                                                                                                           | 1.8V |

| 205 | ANT2_CARKIT           |     | ANT2                                                                                                                |      |

| 208 | BPI_D_BUS12_OLAT1     |     | RF BPI IF                                                                                                           | 1.8V |

| 217 | ANT3_CARKIT           |     | ANT3                                                                                                                |      |

| 224 | GPS_PPS               | DO  | Connsys GPS Interface (1.8V)                                                                                        | 1.8V |

| 228 | NC_ANT                |     | NC                                                                                                                  |      |

| 230 | NC_ANT                |     | NC                                                                                                                  |      |

| 233 | ANT4_CARKIT           |     | ANT4                                                                                                                |      |

| 235 | MIPI2_D_SCLK          | DIO | RF MIPI Need to Reserve jumper to GND for C-load tuning                                                             | 1.8V |

| 236 | MIPI2_D_SDATA         | DIO | RF MIPI Need to Reserve jumper to GND for C-load tuning                                                             | 1.8V |

| 237 | BPI_D_BUS15_OLAT4     |     | RF BPI IF                                                                                                           | 1.8V |

| 239 | MIPI1_D_SCLK          | DIO | RF MIPI Need to Reserve jumper to GND for C-load tuning                                                             | 1.8V |

| 240 | MIPI1_D_SDATA         | DIO | RF MIPI Need to Reserve jumper to GND for C-load tuning                                                             | 1.8V |

| 241 | BPI_D_BUS13_OLAT2     |     | RF BPI IF                                                                                                           | 1.8V |

| 242 | BPI_D_BUS14_OLAT3     |     | RF BPI IF,<br>Reserve pull-low for CUST Board detection                                                             | 1.8V |

| 243 | MIPI0_D_SCLK          | DIO | RF MIPI Need to Reserve jumper to GND for C-load tuning                                                             | 1.8V |

| 244 | MIPI0_D_SDATA         | DIO | RF MIPI Need to Reserve jumper to GND for C-load tuning                                                             | 1.8V |

| 245 | BPI_D_BUS11_OLAT0     |     | RF BPI IF                                                                                                           | 1.8V |

| 249 | AP_UTXD2              | DO  | UART2 transmit data – (used for debug),<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.                       | 1.8V |

| 250 | EINT4<br>(MT6685_INT) | DO  | Unused, please keep floating or NM.<br>Just reserve for WIFI/BT connectivity<br>MT7915/MT7975. (32KHz Clock output) | 1.8V |

| 251 | WLAN_ACT              | DIO | Connsys Co-Ex Interface (1.8V)                                                                                      | 1.8V |

| 252 | PTA_RX                | DIO | Connsys Co-Ex Interface (1.8V)                                                                                      | 1.8V |

| 253 | AP_UCTS2              | DI  | UART2 CTS Clear ToSend<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.                                        | 1.8V |

| 254 | EINT16                | DIO | GPIO Reserve for WIFI/BT connectivity<br>MT7915/MT7975.                                                             | 1.8V |

| 255 | PTA_TX                | DIO | Connsys Co-Ex Interface (1.8V)                                                                                      | 1.8V |

| 256 | BT_PRI_RXD            | DIO | Connsys Co-Ex Interface (1.8V)                                                                                      | 1.8V |

| 257 | AP_URXD2              | DI  | UART2 receive data (used for debug),<br>Reserve for WIFI/BT connectivity<br>MT7915/MT7975.                          | 1.8V |

| 258 | EINT15                | DIO | GPIO Reserve for WIFI/BT connectivity<br>MT7915/MT7975.                                                             | 1.8V |

| 259 | BT_ACT_TXD            | DIO | Connsys Co-Ex Interface (1.8V)                                                                                      | 1.8V |

| 260 | INT_SIM2              | DI  | For SIM2 interrupt for detect pin<br>(Does not support SIM2 hotswap)                                                | 1.8V |

|     |                          |     |                                                                                                                 |                     |

|-----|--------------------------|-----|-----------------------------------------------------------------------------------------------------------------|---------------------|

| 261 | AP_URTS2                 | DO  | UART2 RTS Require ToSend Reserve for WIFI/BT connectivity MT7915/MT7975 UART                                    | 1.8V                |

| 262 | EINT17                   | DIO | GPIO Reserve for WIFI/BT connectivity MT7915/MT7975.                                                            | 1.8V                |

| 263 | SIM2_SIO                 | DIO | For USIM2 Data                                                                                                  | 1.8V/3V             |

| 264 | SIM2_SRST                | DIO | For USIM2 reset                                                                                                 | 1.8V/3V             |

| 266 | NC(EVT)<br>EINT111(DVT)  | DIO | NC for EVT<br>DVT for GPIO Reserve                                                                              | NC/<br>1.8V         |

| 267 | SIM2_SCLK                | DIO | For USIM2 clock                                                                                                 | 1.8V/3V             |

| 269 | SCL3                     | DIO | I2C IF Reserve for CC detect or Gauge IC                                                                        | 1.8V                |

| 270 | EINT6                    | DIO | GPIO Reserve                                                                                                    | 1.8V                |

| 273 | SDA3                     | DIO | I2C IF Reserve for CC detect or Gauge IC                                                                        | 1.8V                |

| 274 | NC(EVT)<br>EINT110(DVT)  | DIO | NC for EVT<br>DVT for GPIO Reserve                                                                              | NC/<br>1.8V         |

| 277 | NC (EVT)<br>EINT109(DVT) | DIO | NC for EVT<br>DVT for GPIO Reserve                                                                              | NC/<br>1.8V         |

| 278 | EINT5                    | DIO | GPIO Reserve                                                                                                    | 1.8V                |

| 280 | SIM1_SRST                | DIO | For USIM reset                                                                                                  | 1.8V/3V             |

| 281 | EINT9                    | DIO | GPIO Reserve for EN Pin                                                                                         | 1.8V                |

| 282 | EINT8                    | DIO | GPIO Reserve                                                                                                    | 1.8V                |

| 283 | INT_SIM1                 | DIO | For SIM1 interrupt for detect pin (Active High)                                                                 | 1.8V                |

| 284 | SIM1_SIO                 | DIO | For USIM Data                                                                                                   | 1.8V/3V             |

| 285 | AUXADC_VIN7              | AIO | PMIC Side AUX ADC Channel Reserve for thermal detection monitor (15bit)                                         | 0~1.98              |

| 286 | EINT0                    | DIO | GPIO Reserve for Enter Meta Mode<br>(Module internal used, low trigger to Meta Mode)                            | 1.8V                |

| 287 | SIM1_SCLK                | DIO | For USIM clock                                                                                                  | 1.8V/3V             |

| 288 | MT6361_ISINK3            | AIO | Current SINK control pin for LED                                                                                | 0~ VPH              |

| 289 | AUXADC_VIN6              | AIO | PMIC Side AUX ADC Channel Reserve for thermal detection monitor (15bit)                                         | 0~1.98              |

| 290 | EINT11                   | DIO | GPIO Reserve for EN Pin                                                                                         | 1.8V                |

| 292 | MT6361_ISINK1            | AIO | Current SINK control pin for LED                                                                                | 0~ VPH              |

| 293 | PWRKEY                   | DI  | PWRKEY button (power on/off control)<br>active low                                                              | 1.8V                |

| 294 | FULL_CARD_POWER_OFF#     | DI  | PMIC Enable Control (Active High),<br>>1.45V, <3.3V<br>Must need Connect to GND, if unused                      | 1.8V/3.3V<br>Or GND |

| 295 | DVDD28_MSDC1             | PI  | If need support T-Card function, need connect to external 1.8V<br>If unused, need contact to VIO18_PMU(PIN 309) | VIO18               |

| 296 | MT6361_ISINK2            | AIO | Current SINK control pin for LED                                                                                | 0~ VPH              |

| 297 | SYSRSTB                  | DO  | System reset input from PMIC output<br>(should be just used for monitor)                                        | 1.8V                |

|                                                                                                                                                                                                                                                                                                                                                                     |             |     |                                                                                                                                        |           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 299                                                                                                                                                                                                                                                                                                                                                                 | VMC_PMU     | PO  | Reserve for MSDC1 SD Card function Power.(level shift)                                                                                 | 1.8/2.95V |

| 300                                                                                                                                                                                                                                                                                                                                                                 | SIM2_VCC    | PO  | VSIM2 Output voltage                                                                                                                   | 1.8/3V    |

| 302                                                                                                                                                                                                                                                                                                                                                                 | VDET        | PI  | Voltage for power input detect.<br>When VDET get high, it also can turn-on system, such as Cable Power on feature.                     | VBUS      |

| 303                                                                                                                                                                                                                                                                                                                                                                 | SIM1_VCC    | PO  | VSIM1 Output voltage                                                                                                                   | 1.8/3V    |

| 304                                                                                                                                                                                                                                                                                                                                                                 | VSYS        | PI  | For LGA Module power (4A/4.2V)                                                                                                         | 3.4~4.4V  |

| 305                                                                                                                                                                                                                                                                                                                                                                 | RESET#      | DI  | Reset Control for PMIC<br>(when H to L , will generate SYSRSTB to reset AP)                                                            | 1.8V      |

| 307                                                                                                                                                                                                                                                                                                                                                                 | VSYS        | PI  | For LGA Module power (4A/4.2V)                                                                                                         | 3.4~4.4V  |

| 308                                                                                                                                                                                                                                                                                                                                                                 | VSYS        | PI  | For LGA Module power (4A/4.2V)                                                                                                         | 3.4~4.4V  |

| 309                                                                                                                                                                                                                                                                                                                                                                 | VIO18_1_PMU | PO  | 1.8V Output, this is just reserve for Pin295, if no need SD Card function. Please do not connect to other Power Supply Source purpose. | 1.8V      |

| 310                                                                                                                                                                                                                                                                                                                                                                 | VSYS        | PI  | For LGA Module power (4A/4.2V)                                                                                                         | 3.4~4.4V  |

| 311                                                                                                                                                                                                                                                                                                                                                                 | VSYS        | PI  | For LGA Module power (4A/4.2V)                                                                                                         | 3.4~4.4V  |

| 312                                                                                                                                                                                                                                                                                                                                                                 | VSYS        | PI  | For LGA Module power (4A/4.2V)                                                                                                         | 3.4~4.4V  |

| 1,78,<br>157,234,313~412                                                                                                                                                                                                                                                                                                                                            | PAD GND     |     | PAD GND                                                                                                                                | GND       |

| 17,18,33~35,39,52,5<br>5,57,58,71,74,77,91~<br>96 , 99 , 100 , 103<br>, 104 , 107~113,11<br>7,119~121,125,127~<br>129,131~133,135,13<br>6,159,161,162,165,1<br>66,170,173,174,177,<br>178,182,185~187,18<br>9~191,194,195,197~<br>199,201~203,206 , 2<br>07 , 209~216,218,21<br>9,220~223 , 225~22<br>7,229,231,232,238,2<br>46~248,265,268,271,<br>291,298,301,306 | GND         | GND | GND                                                                                                                                    |           |

| 164,167,168,171,272<br>,275,276,279                                                                                                                                                                                                                                                                                                                                 | NC          |     | Not Connection                                                                                                                         | NC        |

AI : Analog input

AO : Analog output

B : Bidirectional digital with CMOS input

PD: Pull-Down

PU: Pull-Up

T: Tristate

OD: Open Drain

PP: Push-Pull

PI: Power Input

PO: Power Output

Z: High-impedance (Hi-Z) output

#### NOTE

The unused pins can be left floating.

- **P** indicates power pins; **I** indicate pins for digital signal input; **O** indicates pins for digital signal output; **PO** indicates power output pins; **PI** indicates power input pins.

- **VIL** indicates Low-level Input voltage; **VIH** indicates High-level Input voltage; **VOL** indicates Low-level Output voltage; **VOH** indicates High-level Output voltage.

- The **NC** pins are not connected, therefore, before you deal with these pins; please refer to the corresponding hardware guide.

The **Reserved** pins are internally connected to the module. Therefore, these pins should not be used, otherwise they may cause problems. Please contact with us for more details about this information.

## 4. FCC Notice

Model: RML-N2x

### Important Notice to OEM integrators

1. This module is limited to OEM installation ONLY.

2. This module is limited to installation in mobile or fixed applications, according to Part 2.1091(b). 3. The separate approval is required for all other operating configurations, including portable configurations with respect to Part 2.1093 and different antenna configurations 4. For FCC Part 15.31 (h) and (k): The host manufacturer is responsible for additional testing to verify compliance as a composite system. When testing the host device for compliance with Part 15 Subpart B, the host manufacturer is required to show compliance with Part 15 Subpart B while the transmitter module(s) are installed and operating. The modules should be transmitting and the evaluation should confirm that the module's intentional emissions are compliant (i.e. fundamental and out of band emissions). The host manufacturer must verify that there are no additional unintentional emissions other than what is permitted in Part 15 Subpart B or emissions are complaint with the transmitter(s) rule(s).

### Antenna Installation

- (1) The antenna must be installed such that 20 cm is maintained between the antenna and users.

- (2) The transmitter module may not be co-located with any other transmitter or antenna.

- (3) To comply with FCC regulations limiting both maximum RF output power and human exposure to RF radiation, the maximum antenna gain including cable loss in a mobile exposure condition must not exceed:

In the event that these conditions cannot be met (for example certain laptop configurations or co-location with another transmitter), then the FCC authorization is no longer considered valid and the FCC ID cannot be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC authorization.

## Manual Information to the End User

The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module in the user's manual of the end product which integrates this module. The end user manual shall include all required regulatory information/warning as show in this manual.

## Module Warning statements

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) This device may not cause harmful interference

- (2) This device must accept any interference received, including interference that may cause undesired operation.

Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

## RF Exposure

This device has been tested and meets applicable limits for Radio Frequency (RF) exposure. The antenna(s) used for this transmitter should be installed and operated with minimum distance 20 cm between the radiator & your body.

## Label requirements

Any device incorporating this module must include an external, visible, permanent marking or label which states:

“Contains FCC ID: GKRRMLN2X”

## Industry Canada Statement

This device contains licence-exempt transmitter(s)/receiver(s) that comply with Innovation, Science and Economic Development Canada's licence-exempt RSS(s). Operation is subject to the following two conditions:

- (1) This device may not cause interference.

- (2) This device must accept any interference, including interference that may cause undesired operation of the device.

L'émetteur/récepteur exempt de licence contenu dans le présent appareil est conforme aux CNR d'Innovation, Sciences et Développement économique Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes :

- (1) L'appareil ne doit pas produire de brouillage;

- (2) L'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

CAN ICES-3(B)/ NMB-3(B)

## Radiation Exposure Statement

This equipment complies with FCC/IC radiation exposure limits set forth for an uncontrolled environment. This equipment should be installed and operated with minimum distance 20 cm between the radiator & your body.

Cet équipement est conforme aux limites d'exposition aux rayonnements FCC/IC établies pour un environnement non contrôlé. Cet équipement doit être installé et utilisé avec une distance minimale de 20 cm entre le radiateur et votre corps.

OEM integrators must identify all possible combinations of simultaneous transmission configuration for all transmitters and antennas installed in the host platform. When there are multiple transmitting devices installed in a host platform, an RF exposure evaluation for the simultaneous transmission condition must be performed.

## End Product Labeling

When the module is installed in the host device, the IC ID label must be visible through a window on the final device or it must be visible when an access panel, door or cover is easily re-moved. If not, a second label must be placed on the outside of the final device that contains the following text:

"Contains IC: 2533B-RMLN2X"

### 1. Antenna Gain

| <b>Bands</b> | <b>Freq.</b>       | <b>Monopole</b>  |

|--------------|--------------------|------------------|

|              | <b>Uplink(MHz)</b> | <b>Gain(dBi)</b> |

| <b>n71</b>   | <b>663~698</b>     | 2.0              |

| <b>n66</b>   | <b>1710~1780</b>   | 2.0              |

| <b>n29</b>   | <b>716 - 728</b>   | 2.0              |

| <b>n70</b>   | <b>1695 - 1710</b> | 2.0              |