EXHIBIT I

FCC TYPE ACCEPTANCE REPORT

INFORMATION TRANSMISSION SYSTEMS CORP.

MODEL 6459A

FCC ID-CJJ79XITS-7036

BROAD BAND TRANSLATOR

Date Filed \_\_\_\_\_

This application is filed in compliance with

Part 2, Part 21 and Part 74

of the FCC Rules and Regulations.

ADC Telecommunications

102 Rahway Road

McMurray, PA 15317

## TABLE OF CONTENTS

### **1.0 IDENTIFICATION OF APPLICANT AND EQUIPMENT**

- 1.1 Applicant

- 1.2 Equipment Model Number

- 1.3 Manufacturing Plans

### **2.0 TECHNICAL DESCRIPTION**

- 2.1 Introduction

- 2.2 Technical Specifications

- 2.3 Performance Specifications

- 2.4 Circuit Description

- 2.5 Alignment Procedure

- 2.6 Block Diagrams

### **3.0 ENGINEERING DATA**

- 3.1 RF Power Measurement

- 3.2 Occupied Bandwidth

- 3.3 Out-of-Band Power

- 3.4 Radiated Emissions

- 3.5 Frequency Stability

- 3.6 Test Equipment

### **4.0 IDENTIFICATION TABLES/LABEL PLACEMENT AND PHOTOGRAPHS**

### **5.0 CERTIFICATION OF TEST DATA**

## **1.0 IDENTIFICATION OF APPLICANT AND EQUIPMENT**

### **1.1 Applicant:**

ADC Telecommunications

102 Rahway Road

McMurray, PA 15317

The above name and address is printed on a label attached to the rear panel of the equipment.

### **1.2 Equipment and Model Number: 6459A**

This information is provided on the front panel of the equipment.

### **1.3 ADC Telecommunications shall manufacture this product in quantities necessary to satisfy market demand.**

## **2.0 TECHNICAL DESCRIPTION - MODEL ITS-6459A**

### **2.1 Introduction**

The 6459A is a multi-channel translator/linear amplifier intended to be used as a multi-channel translator in the MMDS/ITFS frequency band (2500.00 to 2690.00 MHz).

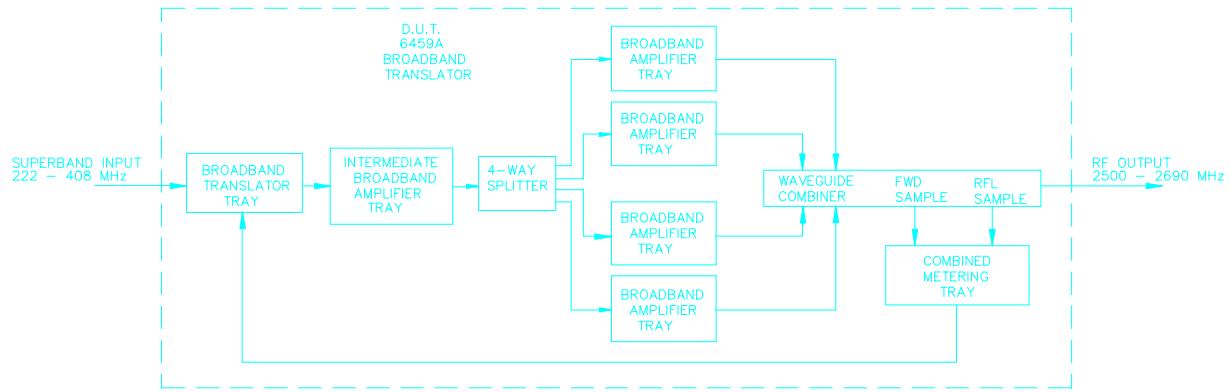

Functionally the 6459A is comprised of an ITS-717 translator tray, a ITS-5765 intermediate broadband amplifier driver tray, four ITS-5767 external broadband amplifier trays, 4-way splitter, waveguide combiner, and combined metering tray.

The multi-channel super band (222.00 to 408.00 MHz) input signal enters the system at the input of the translator where it is translated to the MMDS/ITFS frequency band and amplified to a sufficient level to drive the intermediate amplifier driver (5765). The translator tray also incorporates automatic level control to maintain the combined output power within the limits of the output amplifiers and all necessary control logic of the system. The 5765 broadband amplifier tray amplifies the multi-channel signal and feeds the signal to the input of a 4-way splitter. The 4-way splitter splits the multi-channel signal into four equal signals which drive the 5767 broadband amplifiers. The output signals from the four 5767 broadband amplifiers are combined in the waveguide combiner. The combined metering tray inputs forward and reflective RF power samples from the waveguide combiner and provides front panel metering as well as a system ALC signal which is routed to the translator tray. The combined metering tray also acts as an interface between the amplifier tray's status signals and the remote/SCADA (Supervisory Control and Data Acquisition) monitoring systems. The power per channel capability of the unit varies with the number of channels according to specifications.

The 6459A incorporates automatic level control to maintain the combined output power within the limits of the output amplifiers. The 6459A utilizes GaAS FET amplifier modules for amplification of the RF signal.

The trays comprising the unit are standard 19-inch rack mount assemblies and are supplied with or without a cabinet. The unit is supplied complete with mounting hardware and cabinet slides.

Parameters and specification for operation of the 6459A are provided on the following pages, and a complete circuit description and alignment procedure are also included in this report. Refer to the overall system block diagram and the particular referenced schematics in the attached circuit description section of this report.

## 2.0 TECHNICAL DESCRIPTION

### 2.2 Technical Specifications

|                                                             |                                    |

|-------------------------------------------------------------|------------------------------------|

| Type of Emissions .....                                     | TRANSLATOR (Analog)                |

| Frequency Range .....                                       | 2500 to 2690 MHz                   |

| DC voltage and total current of final amplifier stage ..... | 10 volts DC at 130 amps            |

| (Broadband Amplifier tray/4 per system)                     | (Class A - Not RF power dependent) |

| Total Output Power Capability .....                         | 189 to 378 Watts peak envelope     |

| Adjustable in the translator tray                           | (31.5 to 63.0 Watts total average) |

### 2.3 Performance Specifications

#### RF output (average):

|                   |                |

|-------------------|----------------|

| 4 Channels .....  | 15.8 W/Channel |

| 8 Channel .....   | 7.90 W/Channel |

| 12 Channels ..... | 5.25 W/Channel |

| 16 Channel .....  | 3.94 W/Channel |

| 24 Channels ..... | 2.63 W/Channel |

| 31 Channel .....  | 2.03 W/Channel |

Nominal Input Signal Range (average power): ..... -32 to -17 dBm/Channel

Connector ..... Type N

Impedance ..... 50 ohm

Out-of-Band Power ..... Per FCC Rules (21.908)

-25 dB max (at band edges):

-40 dB max (250.00 KHz above and 250.00 KHz below band edges):

-50 dB max (3.00 MHz above and 3.00 MHz below band edges):

-60 dB max (20.00 MHz above and 20.00 MHz below band edges):

Out-of-Band Power (Unoccupied Channel) ..... Per FCC Rules (21.908)

-25 dB max (at unoccupied channel edges)

-40 dB max (250.0 KHz above and 250.0 KHz below occupied channel edges)

-50 dB max (3.0 MHz above and 3.0 MHz below occupied channel edges)

Harmonic Products ..... -60 dB max

#### Electrical Requirements

Power Line Voltage ..... 110 VAC  $\pm 10\%$ , 60 Hz/240 VAC  $\pm 10\%$ , 50/60 Hz

Power Consumption (System) ..... 11.145 Watts

#### Environmental

Maximum Altitude (System) ..... 12,000 feet (3,660m)

Ambient Temperature (system) ..... 0° to 50°C

## 2.0 TECHNICAL DESCRIPTION

### 2.3 Performance Specifications-continued

#### **Mechanical**

Dimensions: (WxDxH)

|                                   |                                                   |

|-----------------------------------|---------------------------------------------------|

| 717 Translator Tray .....         | 19" x 21" x 8.75" (48.3cm x 53.3cm x 22.2cm)      |

| 5765 Broadband Amplifier Tray.... | 19" x 30" x 10.25" (48.3cm x 76.2cm x 26.0cm)     |

| 5767 Broadband Amplifier Tray.... | 19" x 30" x 10.25" (48.3cm x 76.2cm x 26.0cm)     |

| Combined Metering Tray .....      | 19" x 12.5" x 3.5" (48.3cm x 31.75cm x 8.9cm)     |

| AC Distribution Tray.....         | 19" x 11.75" x 8.75" (48.3cm x 29.85cm x 22.24cm) |

Weight:

|                                    |                     |

|------------------------------------|---------------------|

| 717 Translator Tray .....          | 55 lbs. (24.9 kgs)  |

| 5765 Broadband Amplifier Tray..... | 85 lbs. (38.6 kgs)  |

| 5767 Broadband Amplifier Tray..... | 145 lbs. (65.8 kgs) |

| Combined Metering Tray .....       | 15 lbs. (6.8 kgs)   |

| AC distribution Tray .....         | 14 lbs. (6.4 kgs)   |

## 2.0 TECHNICAL DESCRIPTION

### 2.4 Circuit Description

The ITS-6459A Multi-Channel Translator can be subdivided further as follows:

#### Translator Tray (ITS-717):

- Superband Bandpass Filter

- VHF Generator

- Frequency Multiplication

- Automatic Level Control

- Bias Circuits

- Amplifier Modules

- Power Detectors

- Control Logic

- Status Indicators

- Power Supplies

#### Broadband Amplifier Trays (ITS-5765/ITS-5767):

- RF Input

- RF Output

- Amplifier Modules

- Bias Circuits

- Feed Forward Correction

- Control Logic

- Switching Power Supplies

- DC to DC Converter

- Peak Detector

- Splitters

- Combiner

- Couplers

#### Combined Metering Tray :

- Metering

- Power Detection

- Remote Monitoring

- SCADA monitoring

- Splitters

- Power Supply

- Status Indicators

## 2.0 TECHNICAL DESCRIPTION

### 2.4 Circuit Description

#### General

The 6459A Broadband Translator is comprised of a translator tray, intermediate broadband amplifier driver tray and four broadband amplifier trays. The translator tray upconverts the multi-channel superband (202 to 408 MHz) input signal to the MMDS/ITFS frequency range. The translator tray includes automatic level control, LO frequency generation, power amplification stages, and control circuitry. The translator tray output signal is connected to an external 5765 intermediate broadband amplifier driver tray which amplifies the multi-channel signal to a sufficient level to drive four 5767 broadband amplifier trays. All five amplifier trays use GaAs FET amplifier stages for amplification of the RF signal. The combined peak envelope output power sample obtained from the crossguide coupler of the waveguide combiner is used to develop the system automatic level control voltage.

#### Translator (ITS-717)

The superband multi-channel input signal is applied to the input of the translator (J4) and fed to the SuperBand Bandpass Filter w/ Amplifier module (1509-1107) which consist of two lumped element bandpass filters and two MAV-11 amplifiers. The output of this module is padded and applied to the IF input of the mixer (ZFM-15) where it is mixed with the LO signal.

The LO signal is generated on the VHF Generator Board (1500-1102). This board is comprised internally of a voltage controlled crystal oscillator circuit that is a modified Colpitts design. The crystal is mounted in an oven set at 60° C and operates at 1/24 of the local oscillator frequency. A PLL circuit on the VHF generator board divides a sample of the channel VCXO frequency and compares it to a divided down reference frequency generated by the 10 MHz Oscillator module (1519-1037) or to an external precise reference. The difference between the phase of the reference frequency and the divided down VCXO frequency sample causes the PLL IC to create an error output voltage or Automatic Frequency Control (AFC) voltage which is used to bias a variable capacitor in the VCXO circuit.

The output signal from the VHF Generator board is applied to the input of the X\* Multiplier Board (1607-1109) which consist of three x2 broadband doublers ( $2^3 = 8$ ). The output signal is applied to a X3 Multiplier board which consist of multiplier board that generates harmonics if the inut signal and a two section cavity filter tuned to select the third harmonic. The LO (2278 MHz) output signal of the X3 Multiplier is fed to the LO input of the mixer where it is mixed with the IF signal to produce the RF output signal.

The RF output of the mixer is fed to a Four Section Bandpass Filter (2140-1033) then to the Broadband Filter Module (2500-2700). The output of the filter is fed to the Amplifier Attenuator Module (1132-11509) input (J1). The input signal is AC coupled and amplified then applied to a "tee" configuration Pin Diode attenuator circuit. By controlling the gain of this attenuator, the output power can be regulated, maintaining a constant output regardless of minor changes in the input signal.

An external ALC bias voltage is generated by the Peak/Average Detector Board (1510-1105), which detects the peak envelope power of the combined output signal. This bias voltage is fed to the input (J1) of the ALC Control Board (1510-1103).

## 2.0 TECHNICAL DESCRIPTION

### 2.4 Circuit Description -continued

On this board the signal is amplified and adjusted in level by ALC potentiometer R9 and buffered to three output jacks (J2, J5, an J6). One output (J5) is fed to the input of the ALC Fault Sense Board (1132-1501). The ALC Fault Sense Board compares the ALC bias voltage to reference voltages, set by on board potentiometers, and will light front panel LED indicators should an out of range ALC condition occur.

A second output from the ALC Control Board (J6) is fed to the front panel meter providing external monitoring. The third output of the board (J2) provides the ALC bias voltage for the PIN Diode attenuator in the Amplifier/Attenuator Module (1132-1509). The ALC circuit may be bypassed by moving W1 on J8 to the manual position. When the ALC is disabled, the loss through the PIN Diode attenuator is adjusted by the Manual Gain potentiometer R12, which then directly controls the output in a manual fashion.

The output of the Amplifier/Attenuator Module is connected to the Three stage Amplifier Module (1510-1106) driver amplifier, which consist of three cascaded GaAs FET amplifiers (FLLFSX52WF driving a FLL171ME driving a NES2527-20B-3) with an overall gain of approximately 40 dB. The output of the Three Stage Amplifier Module is fed to the input of the 50 Watt Amplifier Module (1506-1107).

The signal is input to the 50 Watt Amplifier Module at J1 and amplified by GaAs FET Q101 (FLM2527L-20XXA). Then the signal is split four ways by three by a Wilkinson in phase couplers and amplified by four parallel GaAs FET amplifiers, Q201 and Q301, Q401 and Q501 (all FLM2527L-20XXA's). The signal is then combined by a three additional Wilkinson in phase couplers and fed through a circulator then to the RF output of the module at jack J2.

A 20 dB microstrip directional coupler provides a forward power sample of the final output signal. A reflective power sample is obtained from the circulator. Both samples are sent to the Peak/Average Detector Board which detects both samples and produces a forward and reflected metering voltage which drives the booster's front panel meter.

The DC bias drain to source currents of each FET within the Three Stage Amplifier Module and the 25 Watt Amplifier Module are set by adjusting the negative gate to source voltages which are adjusted by potentiometers located next to the corresponding FET.

The Six Section Bias Protection Board (1500-1104) supplies the two amplifier modules with both +10 VDC (operating voltage) and -5 VDC (bias voltage).

The Transmitter Control Board (1510-1103) provides the capability to control and monitor the operating status of the translator. The board is designed to protect the booster in the event of the following faults: overtemperature, loss or reduction in output power and loss of the -5 VDC GaAs FET bias voltage. The Transmitter Control Board also provides the capability to remotely control and monitor the translator status through remote operate/standby commands and remote forward power metering.

## 2.0 TECHNICAL DESCRIPTION

### 2.4 Circuit Description -continued

The booster may be configured to be powered by either a 115 VAC/60 Hz or 230 VAC/50 Hz source. The AC source enters the tray at jack J1 and is distributed to a terminal block (TB2). Varistors VR1, VR2, VR3 and VR4 provide transient and overvoltage protection to the booster. The rear panel circuit breaker (CB1) applies AC voltage to the input of the toriod transformer.

The Toroid transformer provides two 15 VAC secondary windings. The first winding is sent to a full wave bridge rectifier which supplies a positive 18 VDC to several positive voltage regulators located on the  $\pm 12$  VDC Power Supply Board (1500-1145). The second winding is supplied to a full wave bridge rectifier circuit located on the  $\pm 12$  VDC whose output is sent to a negative voltage regulator. One +12 VDC switching supply (SPL250-1012), rated at 21 amperes, is used to supply the GaAs FET amplifier modules with power.

#### Intermediate Broadband Amplifier (ITS-5765)

The RF input signal from the driver transmitter enters the tray at J1 and is fed to the input of a 25W Power Amplifier Assembly (1586-3117). The 25W Power Amplifier Assembly consist of an Amplifier Module (1586-3104), 8 Section Bias Board (1586-3109), and DC to DC Converter (ITS-DC380-11).

The amplifier assembly provides both amplification and Feed Forward distortion cancellation. The module is subdivided into 5 functional sections: power amplifier section, feed forward correction signal section, correction signal preamplifier section, correction signal main amplifier section, and feed forward cancellation/RF output section.

The RF input signal enters the power amplifier section of the amplifier assembly at J2 and is phase and amplitude adjusted using a microstrip delay line and resistor pad network. The signal is then applied to a 3 dB Branch Line Coupler which provides a sample of the input signal to the feed forward correction signal section later in the signal path. The main output signal from the coupler is fed to the power amplifier which consist of five GaAs FET amplifiers (MGFS45V2527-1driving four parallel MGFS45V2527-1's) with an overall gain of approximately 24 dB. A 20 dB microstrip coupler provides and uncorrected (distorted) sample of the power amplifier output signal. This sample is used in the feed forward correction signal section of the module which the generates the correction signal that will be amplified and coupled with the RF output signal to cancel the distortion created in the power amplifier.

The input signal (undistorted) sample is phase shifted 180° through a delay line and fed to the feed forward correction signal section of the assembly where it is phase and amplitude adjusted and coupled with the uncorrected signal from the output amplifier. Combining these two signals (the phase shifted (180°) input signal, and the distorted power amplifier output signal) cancels the information carrying component of the signal, leaving only the distortion of the output amplifier.

## 2.0 TECHNICAL DESCRIPTION

### 2.4 Circuit Description -continued

This correction signal is fed to the correction signal preamplifier section of the module which consist of two cascaded GaAs FET amplifiers (FL1100 driving a FLL200) with an overall gain of approximately 24 dB. The signal is then fed to the feed forward correction signal main amplifier where it is amplified to a sufficient level to cancel the distortion created by the power amplifier. The correction signal main amplifier consist of two parallel GaAs FET amplifiers (both MGFS45V2527-1) with an overall gain of approximately 12 dB.

The amplified correction signal and the phase shifted (180°) output of the power amplifier are applied to a hybrid microstrip coupler in the feed forward distortion cancellation/RF output section of the module where the signals are coupled together using a 6.5 dB Branchline Coupler, effectively canceling the distortion in the output signal. The main output signal connects to the output of the amplifier assembly at J8.

The DC biasing of the FET amplifiers in each section of the module is controlled and filtered by corresponding daughter boards which are soldered directly to the main board. The DC bias drain to source currents are set by adjusting the negative gate to source voltages which are adjusted by potentiometers on the daughter boards.

The 8 Section Bias Board distributes the -5V bias voltages and +10.4V drain voltages to the Amplifier Module as well as providing protection from an over current condition with board mounted fuses.

The -5V bias voltage is generated on board using a voltage regulator (LM377T). This bias voltage is also used as an interlock which is fed to the Power Detector/Control Board (1586-1118). If the bias voltage is lost, the control circuitry on the Power Detector/Control Board will immediately shut down the switching supply, thereby removing the drain voltages from the amplifier modules and protecting the GaAs FET devices.

Differential amplifier OP Amp circuits are used to monitor the drain currents of the FET devices. The OP Amp outputs drive LED indicators as well as an opto-isolated O/P amplifier status line.

The DC to DC converter inputs +390VDC from the Power Factor Corrected Front End Module (1586-1111) and generates two 10.8 VDC outputs using three DC to DC converter IC's (VI-B61-EU). An Enable signal from the driver transmitter is used to activate the DC to DC converter.

The output signals from the 25 W Power Amplifier assembly is fed to a Reject Load Module (1586-1106) which is used to absorb any reflected power. The signal is then applied to a directional coupler (A13), which provides forward and reflective power samples to the Power Detector/Control Board, then to the RFoutput jack on the rear of the tray.

## 2.0

## TECHNICAL DESCRIPTION

### 2.4 Circuit Description -continued

The Power Detector/Control Board (1586-1118) provides the dual function of forward/reflective power detection and operating status control and monitoring capability. The board is designed to protect the amplifier in the event of one of the following faults: over temperature, loss or reduction in output power, and loss of the -5 VDC GaAs FET bias voltage. The Power Detector/Control Board also provides the capability to remotely control and monitor the amplifier status through external remote connections at J3 (25 pin D) on the rear of the tray.

The amplifier is powered through a standard 220 VAC 60 Hz source. The AC source enters the tray at jack J1, passes through a fuse protected circuit breaker, and is distributed to the Power Factor Corrected (PFC) Front End Module.

The AC source is applied to a to a terminal block (TB2) within the PFC Front End Module and distributed to a 40 W switching power supply (LPS23), a 80 W switching power supply (LPS63) and a AC/DC Power Factor Corrected 2000W supply.

The 40 W switching supply supplies +12 V to the other boards within the tray. The 80 W switching supply supplies -12 V to the other boards within the tray. The 200W AC/DC supply supplies +390 VDC to the DC to DC Converters within the 25W Amplifier Module.

### Broadband Amplifier (ITS-5767)

The RF input signal from the intermediate driver amplifier enters the tray at J1 and is fed to the input of a Four Way Splitter (1586-1102) which splits the signal into four equal signals that are fed to the inputs of four identical 25W Power Amplifier Assemblies (1586-3117).

The 25W Power Amplifier Assembly consist of an Amplifier Module (1586-3104), 8 Section Bias Board (1586-3109), and DC to DC Converter (ITS-DC380-11). The amplifier assembly provides both amplification and Feed Forward distortion cancellation. The module is subdivided into 5 functional sections: power amplifier section, feed forward correction signal section, correction signal preamplifier section, correction signal main amplifier section, and feed forward cancellation/RF output section.

The RF input signal enters the power amplifier section of the amplifier assembly at J2 and is phase and amplitude adjusted using a microstrip delay line and resistor pad network. The signal is then applied to a 3 dB Branch Line Coupler which provides a sample of the input signal to the feed forward correction signal section later in the signal path. The main output signal from the coupler is fed to the power amplifier which consist of five GaAs FET amplifiers (MGFS45V2527-1driving four parallel MGFS45V2527-1's) with an overall gain of approximately 24 dB. A 20 dB microstrip coupler provides and uncorrected (distorted) sample of the power amplifier output signal. This sample is used in the feed forward correction signal section of the module which the generates the correction signal that will be amplified and coupled with the RF output signal to cancel the distortion created in the power amplifier.

## 2.0 TECHNICAL DESCRIPTION

### 2.4 Circuit Description -continued

The input signal (undistorted) sample is phase shifted 180° through a delay line and fed to the feed forward correction signal section of the assembly where it is phase and amplitude adjusted and coupled with the uncorrected signal from the output amplifier. Combining these two signals (the phase shifted (180°) input signal, and the distorted power amplifier output signal) cancels the information carrying component of the signal, leaving only the distortion of the output amplifier.

This correction signal is fed to the correction signal preamplifier section of the module which consist of two cascaded GaAs FET amplifiers (FL1100 driving a FLL200) with an overall gain of approximately 24 dB. The signal is then fed to the feed forward correction signal main amplifier where it is amplified to a sufficient level to cancel the distortion created by the power amplifier. The correction signal main amplifier consist of two parallel GaAs FET amplifiers (both MGFS45V2527-1) with an overall gain of approximately 12 dB.

The amplified correction signal and the phase shifted (180°) output of the power amplifier are applied to a hybrid microstrip coupler in the feed forward distortion cancellation/RF output section of the module where the signals are coupled together using a 6.5 dB Branchline Coupler, effectively canceling the distortion in the output signal. The main output signal connects to the output of the amplifier assembly at J8.

The DC biasing of the FET amplifiers in each section of the module is controlled and filtered by corresponding daughter boards which are soldered directly to the main board. The DC bias drain to source currents are set by adjusting the negative gate to source voltages which are adjusted by potentiometers on the daughter boards.

The 8 Section Bias Board distributes the -5V bias voltages and +10.4V drain voltages to the Amplifier Module as well as providing protection from an over current condition with board mounted fuses.

The -5V bias voltage is generated on board using a voltage regulator (LM377T). This bias voltage is also used as an interlock which is fed to the Power Detector/Control Board (1586-1118). If the bias voltage is lost, the control circuitry on the Power Detector/Control Board will immediately shut down the switching supply, thereby removing the drain voltages from the amplifier modules and protecting the GaAs FET devices.

Differential amplifier OP Amp circuits are used to monitor the drain currents of the FET devices. The OP Amp outputs drive LED indicators as well as an opto-isolated O/P amplifier status line.

The DC to DC converter inputs +390VDC from the Power Factor Corrected Front End Module (1586-1111) and generates two 10.8 VDC outputs using three DC to DC converter IC's (VI-B61-EU). An Enable signal from the driver transmitter is used to activate the DC to DC converter.

## 2.0

## TECHNICAL DESCRIPTION

### 2.4 Circuit Description -continued

The output signals from the four 25 W Power Amplifier assemblies are combined into a single output signal using three 2-Way Combiner (2111-1008) modules. Reject Load Modules (1586-1106) are used to absorb any reflected power. The combined signal is applied to a directional coupler (A13) which provides forward and reflective power samples to the Power Detector/Control Board.

The Power Detector/Control Board (1586-1118) provides the dual function of forward/reflective power detection and operating status control and monitoring capability. The board is designed to protect the amplifier in the event of one of the following faults: over temperature, loss or reduction in output power, and loss of the -5 VDC GaAs FET bias voltage. The Power Detector/Control Board also provides the capability to remotely control and monitor the amplifier status through external remote connections at J3 (25 pin D) on the rear of the tray.

The amplifier is powered through a standard 220 VAC 60 Hz source. The AC source enters the tray at jack J1, passes through a fuse protected circuit breaker, and is distributed to the Power Factor Corrected (PFC) Front End Module.

The AC source is applied to a terminal block (TB2) within the PFC Front End Module and distributed to a 40 W switching power supply (LPS23), a 80 W switching power supply (LPS63) and a AC/DC Power Factor Corrected 2000W supply.

The 40 W switching supply supplies +12 V to the other boards within the tray. The 80 W switching supply supplies -12 V to the other boards within the tray. The 200W AC/DC supply supplies +390 VDC to the DC to DC Converters within the 25W Amplifier Module.

## 2.0 TECHNICAL DESCRIPTION

### 2.4 Circuit Description -continued

#### Combined Metering Tray

Combined Forward and Reflective power samples of the Broadband Amplifier trays, obtained from the crossguide coupler sample ports (-30 dB) of the waveguide combiner, enter the tray at J2 and J3 respectively. The Forward power input signal is split using a Mini-Circuits 2-way Splitter. One output connects to rear panel Forward power sample jack J4. The other output of the splitter connects to a second Mini-circuits 2-way Splitter. One output of the second splitter connects to a front panel Forward Power sample port (J5) providing easy measurement of the combined Forward power signal. The second output of the splitter, and the combined Reflective power input signal are fed to the Dual Average Detector Board (1569-1129) which detects the average power of both signals and produces forward and reflective metering voltages which drive the tray's front panel meter via the Combined Metering Control Board (1569-1401). On board potentiometers provide adjustment of the forward and reflective metering voltages. A system ALC reference voltage is provided at J4. This system ALC signal is fed to the ALC circuitry of the Agile Upconverter tray via the Combined Metering Control Board.

The Combined Metering Control Board provides the control and general fault detection functions for the Combined Metering tray. This Board also acts as the interface between the amplifier trays status signals and the remote/SCADA (Supervisory DATA Acquisition And Control) monitoring systems.

The combined Forward and Reflective power levels detected by the Dual Average Detector Board enter the board at J11. The DC levels are then buffered by unity gain amplifiers and distributed to three outputs. The Forward and Reflective power signals are distributed to the SCADA interface through J12, to the remote interface through J8, and to a front panel analog meter through J3.

The combined Forward power is also fed to a comparator that compares the DC level against a threshold level set by a variable resistor (R22). If the detected forward power falls below this threshold, a system low output fault signal will be sent to the SCADA interface (J7), the Remote interface (J8), and to a front panel LED indicator (Low O/P).

An Enable command from the Frequency Generator tray enters the board at J9 and is fed to a relay (K1). When the Enable command is given, the relay will energize, turning on FET devices which distribute the command to the amplifiers in the system. An additional FET delivers the operate/standby status to the SCADA interface.

The  $\pm 12$  VDC, supplied by the  $\pm 12$  VDC Power Supply Board (1265-1703) is monitored by an opto-isolator. If both supply voltages are present, the opto-isolator's output transistor will conduct, which in turn illuminates a front panel LED indicating proper supply voltages. If either voltage is lost the LED will extinguish, indicating a loss of tray operating power.

## 2.0 TECHNICAL DESCRIPTION

### 2.5 Alignment Procedure

In the following procedure, the complete multi-channel translator is adjusted for optimum performance. This alignment procedure is performed by adjusting each circuit for its specified performance while observing the appropriate output parameters of the board or subassembly being adjusted.

Because of the broadband nature of the amplifier stages, this is a straightforward procedure, easily accomplished if RF test equipment is available. In this procedure, the input signals are first connected and each circuit is adjusted in sequence by connecting the test equipment to the specified point.

Equipment required:

1. Spectrum Analyzer (with tracking generator)

2. Network Analyzer

3. Power Meter

4. Multi-channel test signal

5. 30 dB Coupler

6. Attenuators

7. Digital Multimeter (DMM)

8. Frequency Counter

#### Translator (ITS-717)

##### **VHF Generator, X8 Multiplier, UHF Bandpass Filter, X3 Multiplier** (A28, A29-1, A30, A31) 1500-1102, 1067-1109, 1107-1101, 1003-1004

1. Connect frequency counter to 10 MHz input cable (J3) of VHF Generator Board and adjust the 10 MHz oscillator for 10 MHz  $\pm 1$ Hz..

2. With J2 and J3 jumpers removed, adjust R19 for -3.0 volts at TP3.

3. Monitor J15 with a spectrum analyzer and J16 with a frequency counter.

4. Adjust L3, .L4, C12 and C21 to peak output signal at J15.

5. Adjust C11 for the correct frequency  $\pm 20$ Hz.

6. Reconnect jumpers on J2 and J3 and reconnect J15.

7. Visually monitor DS1 to verify PLL locks. If PLL remains unlocked, use oscilloscope to minimize spikes on chip U1 by adjusting R46.

8. Monitor J2 on X8 Multiplier assembly with spectrum analyzer with center frequency set to eight times the crystal frequency.

## 2.0 TECHNICAL DESCRIPTION

### 2.5 Alignment Procedure - continued

9. Maximize the eighth harmonic (10 to 13 dBm) and minimize the seventh and ninth harmonic by adjusting C4, C6, C10, C12, C18 and C20.

10. Reconnect J2 and connect analyzer to the output of the UHF Bandpass Filter (A30).

11. Tune filter to maximize the eighth harmonic of the crystal. Seventh and ninth harmonic should be at least 55 dB below eighth harmonic peak.

12. Monitor the output of the X3 Multiplier and tune filter to peak the LO (2278 MHz) signal.

#### **Superband Bandpass Filter, 4 Section Bandpass Filter, 3 Section Broadband Filter (A24-A1, A26, A11) 1509-1107, 2140-1043, 2500-2700**

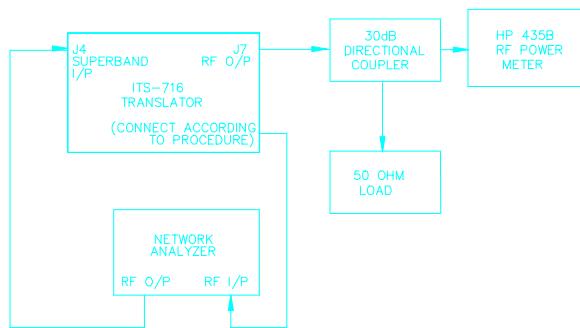

- 1 . Normalize cables of the network analyzer and connect the analyzer as shown below. Set analyzer to sweep the input frequency range. Note: The andlyzer will be used to monitor various points through the translator.

2. Connect the RF input of the analyzer to J3 of the Super band Bandpass Filter (A24-A1) and tune C2, C3, C4 C10, C11 and C12 to flatten the response of the module..

3. Move the input to the analyzer to the output of the Superband Bandpass Filter (J2) and retune capacitors for flat response

4. Disconnect analyzer and set to sweep from 2500 to 2700 MHz. Normalize cables then connect analyzer output to the input of the 4 Section Bandpass Filter (A26). Connect the analyzer input to J5 on the rear panel.

5. Tune the 4 Section Bandpass Filter to flatten response.

6. Connect the RF input of the analyzer to the output of the 3 Section Broadband Filter (A11) and tune the filter for flat response.

## 2.0 TECHNICAL DESCRIPTION

### 2.5 Alignment Procedure - continued

#### **ALC Control Board, Amplifier Attenuator Module**

(A17, A12) 151510-1103, 1132-1509

- 1 . Set S1 on ALC control Board to Manual Mode and adjust R12 for 1.6V at FL3 of Amplifier Attenuator Module (A12).

2. Connect the RF input to the analyzer to the output of the Amplifier Attenuator Module (J2). Place the translator into the operate mode and tune the module to flatten the response.

#### **Three Stage Amplifier Module (A13-A1) 1510-1106**

This amplifier does not contain any RF tuning adjustments. The module contains three cascaded broadband GaAsFET amplifier stages providing a nominal gain of 36 dB. The operating current for the first two stages (Q101, Q201) is controlled by a pot mounted on a bias board within the module and can be set by measuring the voltage drop across the across a resister located next to each FET. The bias for the third stage (Q301) is set by measureing the voltage drop across the 0.05 ohm resistor located on the Four Section Bias Protection Board (1500-1114).

1. With no RF signal applied and with the transrator off, unsolder the drain leads located near the ferrite beads of Q201 and Q301. Connect a digital voltmeter across R104 located next to Q101. Apply AC power to the transmitter and place the transmitter into the Operate mode.

2. Adjust the bias control resistor (R102) for a reading of 5.5 mV across R104. This voltage represents a bias current of 55 mAmps on Q101.

- 3 . Place the translator into the standby mode and then turn the translator off. Unsolder the drain lead of Q101 and resolder the drain lead of Q201. Apply AC power to the transmitter and place the transmitter into the Operate mode. Adjust the bias control (R202) for a reading of 60 mV across R204 located next to Q201. This voltage represents a bias current of 0.6 amps on Q201.

4. Place the transmitter into the standby mode and then turn the transmitter off. Resolder the drain leads of Q101 and Q301. Apply AC power to the transmitter and place the transmitter into the Operate mode. Adjust the bias control potentiometer R303 for a reading of 100 mV across R1 on the Four Section Bias Protection Board. This represents a bias current of 2.0 amps on Q301.

The output of this amplifier is fed to the 25 Watt Amplifier Module (A13-A2).

## 2.0 TECHNICAL DESCRIPTION

### 2.5 Alignment Procedure - continued

#### 25Watt Amplifier Module (A13-A2) 1510-1164

This amplifier does not contain any RF tuning adjustments. The module contains two cascaded broadband GaAsFET amplifier stages (one FLL105MK driving two parallel FLL200IB-3's) providing a nominal gain of ??? dB. The operating current for each device (Q101, Q201, Q301) is controlled by a pot mounted near each device within the module and can be set by measuring the voltage drop across the 0.05 ohm resistor located on the Four Section Bias Protection Board (1500-1114).

| GaAs FET Transistor | Potentiometer Adjustment | Bias Protection Board Resistor | Voltage Across Bias Protection Resistor | Drain Current Calculated |

|---------------------|--------------------------|--------------------------------|-----------------------------------------|--------------------------|

| Q101                | R106                     | R2                             | 9.0 mV                                  | 180 mA                   |

| Q201                | R202                     | R3                             | 240.0 mV                                | 4.8 A                    |

| Q301                | R302                     | R4                             | 240.0 mV                                | 4.8 A                    |

The voltages needed to operate the amplifier modules are provided by the + 12V/21 A switching supplies (A6 and A8) and the  $\pm$ 12 VDC Power Supply board (A3) which produces the -5VDC bias voltage.

The -5 VDC supply is non-adjustable with a regulated output. To prevent damage to the GaAs FET amplifiers, the +12VDC switching supplies will not turn on until the -5VDC bias supply is present.

The +12VDC/21A switching, regulated regulated power supplies do not require any adjustment.

The output of this module is fed to the RF output jack (J7) on the rear of the tray. Connect the RF output (J7) of the translator tray to the RF input (J2) of the amplifier tray. Connect the RF output (J4) of the amplifier tray to a RF power meter through a suitable directional coupler. Connect the main output of the coupler to a suitable load.

## 2.0 TECHNICAL DESCRIPTION

### 2.5 Alignment Procedure - continued

#### Broadband Amplifier (ITS-5765)

##### **PFC Switching Power Supply (A3, A5) VS3-73-450-0001**

The 2000W Power Factor Corrected Switching Power Supply operates from a standard 220 line voltage and outputs +390VDC which is applied to a DC to DC converter in the 25W Power Amplifier Assembly. The PFC Switching Power Supply contains no user adjustments.

##### **40W Switching Power Supply (A6) LPS-23**

The 40W Switching Power Supply supplies +12 VDC to the various boards within the tray. No user adjustments are provided..

##### **80W Switching Power Supply (A4) LPS-63**

The 80W Switching Power Supply supplies -12 VDC to the various boards within the tray. No user adjustments are provided..

##### **25W Amplifier Assembly (A1, A2, A3, A4) 1586-1117**

The 25 Watt Amplifier Assembly is a wideband GaAs FET array that is factory pre-tuned to cover the particular channel frequency.

This Amplifier module does not contain any RF tuning adjustments. The module contains GaAs FET amplifiers. The operating current for each device (Q4, Q5, Q6, Q7, Q8, Q9, Q10, Q11 and Q12), with no drive applied, is controlled by a pot mounted on a bias board within the module, next to each corresponding FET, and can be set by measuring the voltage drop across the the corresponding  $0.05\ \Omega$  resistors on the bias protection board. See chart below.

| GaAs FET Transistor | Potentiometer Adjustment | Bias Protection Board Resistor | Voltage Across Bias Protection Resistor | Drain Current Calculated |

|---------------------|--------------------------|--------------------------------|-----------------------------------------|--------------------------|

| Q4                  | R802                     | R58                            | .175V                                   | 7.0A                     |

| Q5                  | R802                     | R64                            | .175V                                   | 7.0A                     |

| Q6                  | R802                     | R121                           | .175V                                   | 7.0A                     |

| Q7                  | R802                     | R67                            | .175V                                   | 7.0A                     |

| Q8                  | R802                     | R122                           | .175V                                   | 7.0A                     |

| Q9 & Q10            | R802                     | R63                            | .175V                                   | 2.38A                    |

| Q11                 | R802                     | R2                             | .175V                                   | 7.0A                     |

| Q12                 | R802                     | R1                             | .175V                                   | 7.0A                     |

## **2.0 TECHNICAL DESCRIPTION**

### **2.5 Alignment Procedure--continued**

#### **8 Section Bias Protection Board (A1) 1586-1109**

There is one 8 Section Bias Protection Board located in each of the two 25 Watt Power Amplifier Assemblies.

These boards provide over current fuse protection and operating status LED indication of the amplifier modules. These boards also contain bias resistors used to set the operating current of the FET amplifiers within the amplifier modules (see 25 Watt Amplifier Assembly set up above). No user adjustments are provided on the board.

#### **Power Detector/Control Board (A6) 1586-1118**

Using a dummy load and a directional coupler with a calibrated power meter the Forward and Reflective power may be calibrated as follows:

1. To calibrate forward power on the front panel meter, first connect a suitable rated load and a calibrated power meter through a directional coupler to the RF output jack (J4) on the rear of the tray. Place the driver transmitter into manual mode operation.

2. Place the driver transmitter into the Operate mode.

3. Apply a digital IF test signal to the input of the driver transmitter and adjust the manual gain potentiometer of the driver transmitter for the full rated average output power level of the amplifier.

4. Adjust potentiometer R17 on the Power Detector/Control Board for 1V at TP2.

5. Remove the load connected to the amplifier and quickly Reflective Metering potentiometer for 1V at TP3. Note: This step must be performed quickly as to not sustain damage to the FET devices.

## 2.0 TECHNICAL DESCRIPTION

### 2.5 Alignment Procedure--continued

#### Broadband Amplifier (ITS-5767)

##### **PFC Switching Power Supply (A3, A5) VS3-73-450-0001**

The 2000W Power Factor Corrected Switching Power Supply operates from a standard 220 line voltage and outputs + 390VDC which is applied to a DC to DC converter in the 25W Power Amplifier Assembly. The PFC Switching Power Supply contains no user adjustments.

##### **40W Switching Power Supply (A6) LPS-23**

The 40W Switching Power Supply supplies +12 VDC to the various boards within the tray. No user adjustments are provided..

##### **80W Switching Power Supply (A4) LPS-63**

The 80W Switching Power Supply supplies -12 VDC to the various boards within the tray. No user adjustments are provided..

##### **25W Amplifier Assembly (A1, A2, A3, A4) 1586-1117**

The 25 Watt Amplifier Assembly is a wideband GaAs FET array that is factory pre-tuned to cover the particular channel frequency.

This Amplifier module does not contain any RF tuning adjustments. The module contains GaAs FET amplifiers. The operating current for each device (Q4, Q5, Q6, Q7, Q8, Q9, Q10, Q11 and Q12), with no drive applied, is controlled by a pot mounted on a bias board within the module, next to each corresponding FET, and can be set by measuring the voltage drop across the the corresponding  $0.05 \Omega$  resistors on the bias protection board. See chart below.

| GaAs FET Transistor | Potentiometer Adjustment | Bias Protection Board Resistor | Voltage Across Bias Protection Resistor | Drain Current Calculated |

|---------------------|--------------------------|--------------------------------|-----------------------------------------|--------------------------|

| Q4                  | R802                     | R58                            | .175V                                   | 7.0A                     |

| Q5                  | R802                     | R64                            | .175V                                   | 7.0A                     |

| Q6                  | R802                     | R121                           | .175V                                   | 7.0A                     |

| Q7                  | R802                     | R67                            | .175V                                   | 7.0A                     |

| Q8                  | R802                     | R122                           | .175V                                   | 7.0A                     |

| Q9 & Q10            | R802                     | R63                            | .175V                                   | 2.38A                    |

| Q11                 | R802                     | R2                             | .175V                                   | 7.0A                     |

| Q12                 | R802                     | R1                             | .175V                                   | 7.0A                     |

## **2.0 TECHNICAL DESCRIPTION**

### **2.5 Alignment Procedure--continued**

#### **8 Section Bias Protection Board (A1) 1586-1109**

There is one 8 Section Bias Protection Board located in each of the two 25 Watt Power Amplifier Assemblies.

These boards provide over current fuse protection and operating status LED indication of the amplifier modules. These boards also contain bias resistors used to set the operating current of the FET amplifiers within the amplifier modules (see 25 Watt Amplifier Assembly set up above). No user adjustments are provided on the board.

#### **Power Detector/Control Board (A6) 1586-1118**

Using a dummy load and a directional coupler with a calibrated power meter the Forward and Reflective power may be calibrated as follows:

1. To calibrate forward power on the front panel meter, first connect a suitable rated load and a calibrated power meter through a directional coupler to the RF output jack (J4) on the rear of the tray. Place the driver transmitter into manual mode operation.

2. Place the driver transmitter into the Operate mode.

3. Apply a digital IF test signal to the input of the driver transmitter and adjust the manual gain potentiometer of the driver transmitter for the full rated average output power level of the amplifier.

4. Adjust potentiometer R17 on the Power Detector/Control Board for 1V at TP2.

5. Remove the load connected to the amplifier and quickly Reflective Metering potentiometer for 1V at TP3. Note: This step must be performed quickly as to not sustain damage to the FET devices.

## 2.0 TECHNICAL DESCRIPTION

### 2.5 Alignment Procedure--continued

#### Combined Metering Tray

To begin alignment of the Combined metering tray, place the rear panel circuit breaker (CB1) into the on position.

#### **±12VDC Power Supply Board (A2) 1265-1703**

Check that all Green LED's on the board are illuminated. This indicates that the ±12VDC Power Supply Board is functioning correctly. Check that the front panel PWR LED is illuminated.

#### **Dual Average Detector Board (A5) 1569-1129**

1. Connect the output port of the waveguide combiner to an RF power meter using an appropriate coupler. With the translator tray in manual gain mode adjust Manual Gain potentiometer (R12) on the ALC control Board (1510-3103) within the translator tray for 100 Watts on the power meter.

2. Place a  $50\Omega$  load on the Reflective Sample port of the crossguide coupler on the waveguide combiner. Connect the Forward Sample port of the crossguide coupler on the waveguide combiner to the rear panel reflective input (REFL PWR I/P) jack (J3).

3. Set front panel meter switch to combined reflective power.

4. Adjust R10 for 100% on front panel meter.

5. Connect the Forward Sample port on the crossguide coupler to the rear panel forward sample input (J2) and the Reflective Sample port on the crossguide coupler to the rear panel Reflective Sample input (J3).

6. Check that the front panel meter combined reflective power reading is 10% or less.

7. Switch front panel meter to combined forward power and adjust R9 for 50% on front panel meter.

#### **Combined Metering Control Board (A3) 1569-1401**

1. Adjust R22 just until the front panel low output (LOW O/P) LED illuminates.

#### **Dual Average Detector Board (A5) 1569-1129**

1. Adjust R9 for a 100% combined forward power reading on front panel meter.

## 2.0 TECHNICAL DESCRIPTION

### 2.6 Block Diagrams

The following is a system block diagram for the 6459A Multi-Channel Translator. Detailed Block Diagrams and Schematics are included in Exhibit II.

System Block Diagram:

The 6459A multi-channel translator is capable of operating from 50% (31.5 Watts total average) to 100% (63.0 Watts total average) rated output power. The output power is set by adjusting a potentiometer on the ALC Control Board (1510-1103) located within the translator tray.

The data in the following sections was taken at both 50% and 100 % rated output power. First, the output power was adjusted to obtain 31.5 Watts as observed on the RF power meter and the tests were performed. Then the output power was adjusted to obtain 63.0 Watts as observed on the RF power meter and the tests were repeated at rated output power. For simplicity, however, the data for both output powers has been combined in each section, presenting the data at 50% output power followed by the data at 100% rated power.

## 3.0 ENGINEERING DATA

### 3.1 RF Power Measurements

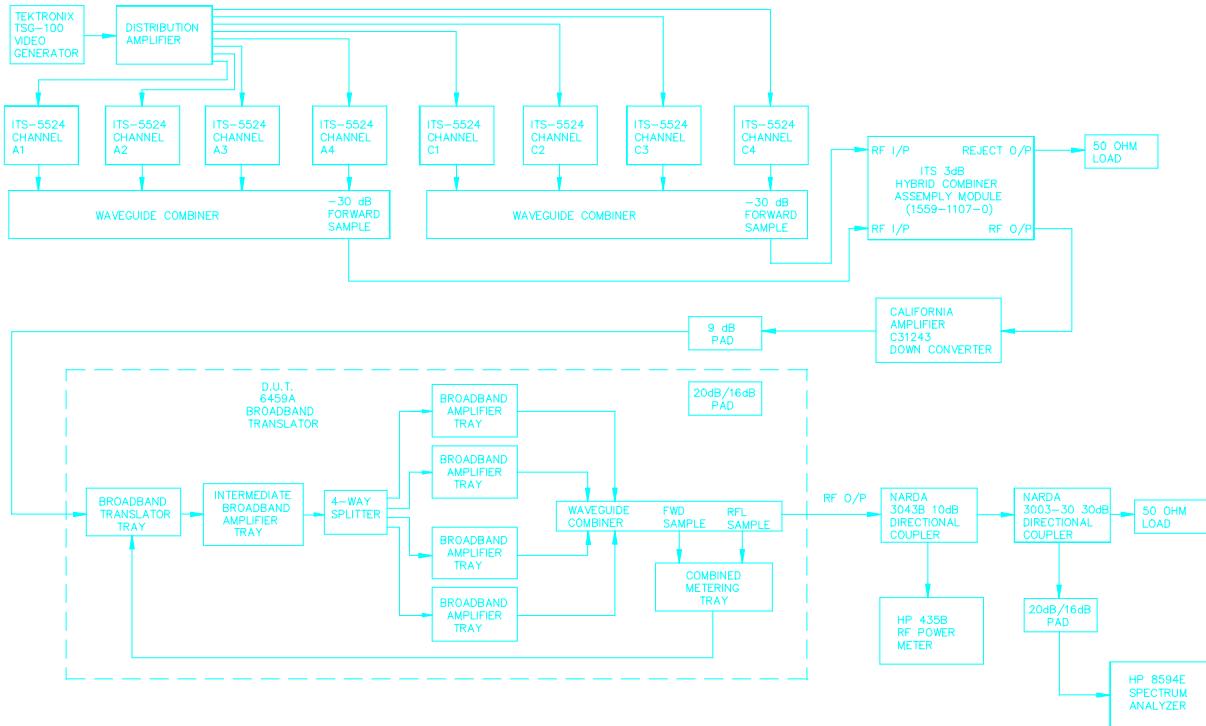

The following block diagram illustrates the test equipment set-up for RF power measurement:

Before testing the 6459A multi-channel translator, the ITS-5724 transmitters (FCC ID# CJ79SITS-7022) used to generate the multi-channel input signal to the translator were tested and observed to meet specifications. Then, the translator was tested and observed, as illustrated in the following sections, to reliably reproduce the transmitted signals in accordance with the rules set forth in the Rules and Regulations.

## 3.0 ENGINEERING DATA

### 3.1 RF Power Measurements - continued

With eight visual carriers present, the output power of the 6459A translator was adjusted to 50% rated output power (31.5 Watts total average) as observed on the RF power meter. With the power level properly set to 31.5 Watts, all required tests were performed and recorded in the following sections.

| <u>Number of channels</u> | <u>Average power/channel</u> | <u>Total Average Power</u> |

|---------------------------|------------------------------|----------------------------|

| 8                         | 3.94 W                       | 31.5 W                     |

After completing the necessary tests at half rated power, the translator was adjusted to 100% rated output power (63.0 Watts total average) as observed on the RF power meter and all required tests were performed and recorded in the following sections.

| <u>Number of channels</u> | <u>Average power/channel</u> | <u>Total Average Power</u> |

|---------------------------|------------------------------|----------------------------|

| 8                         | 7.90 W                       | 63.0 W                     |

Note: The peak envelope power has been determined and observed to be six times, or 7.8 dB, above the total average power. Therefore, the maximum peak envelope power for the 6459A is approximately 378.0 watts. In addition, for multi-channel loading, a doubling in the number of channels requires a 3 dB back-off in the peak power per channel. Also, in the case of 8 or more channels, the total average power remains constant at 63.0 watts. The average power per channel is 63.0 watts divided by the number of channels.

## 3.0 ENGINEERING DATA

### 3.2 Occupied Bandwidth

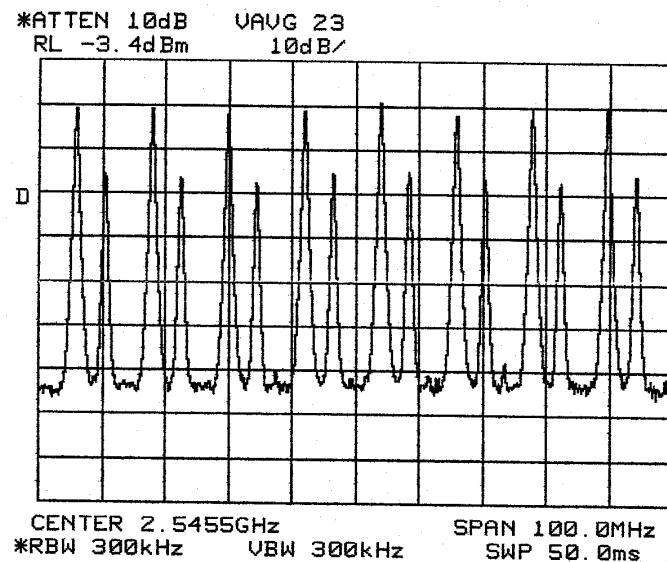

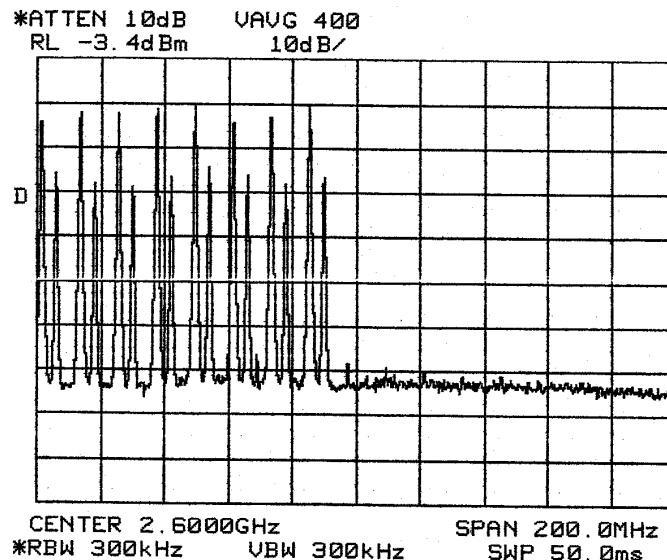

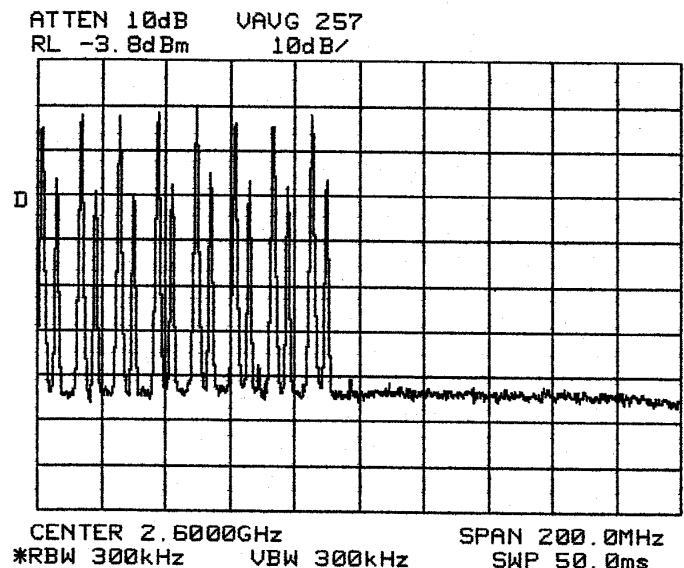

Using the test set-up in Section 3.1, with the booster operating at 31.5 Watts output power and with eight input signals (A1, A2, A3, A4, C1, C2, C3, C4) present, the analyzer was set to a span of 100 MHz and a reference level was established (see plot below). Then the analyzer was adjusted to a span of 200 MHz and the occupied bandwidth (2500.0 MHz – 2690.00 MHz) was observed and recorded below.

Note: The 190 MHz bandwidth permits a maximum of thirty one 6MHz channels.

#### Reference Level Plot/100 MHz Span (31.5 Watts total average):

#### Occupied Bandwidth Plot/200 MHz Span (31.5 Watts total average):

### 3.0 ENGINEERING DATA

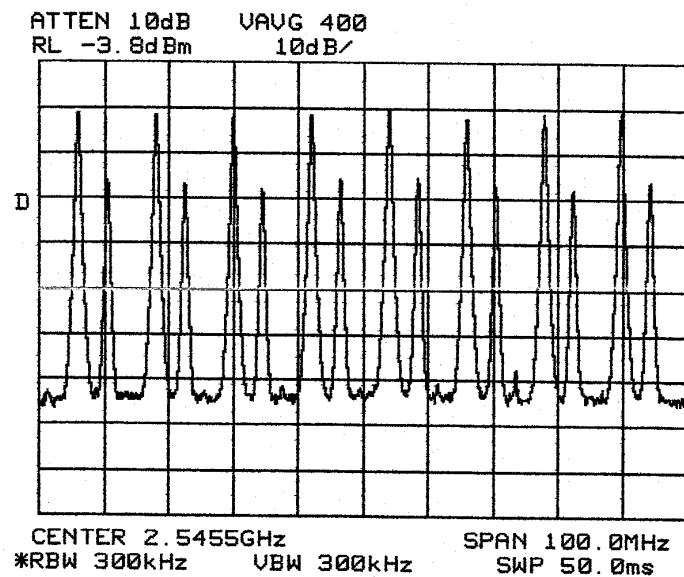

#### 3.2 Occupied Bandwidth - continued

Using the test set-up in Section 3.1, and with the booster operating at 63.0 Watts output power and with eight input signals (A1, A2, A3, A4, C1, C2, C3, C4) present, the analyzer was set to a span of 100 MHz and a reference level was established (see plot below). Then the analyzer was adjusted to a span of 200 MHz and the occupied bandwidth (2500.0 MHz – 2690.00 MHz) was observed and recorded below.

**Reference Level Plot/100 MHz Span (63.0 Watts total average):**

**Occupied Bandwidth Plot/200 MHz Span (63.0 Watts total average):**

### 3.0 ENGINEERING DATA

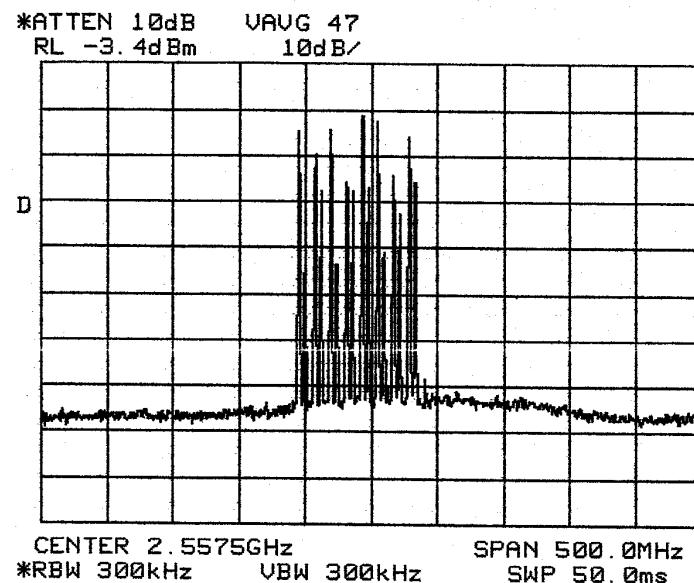

#### 3.3 Out-of-Band Power

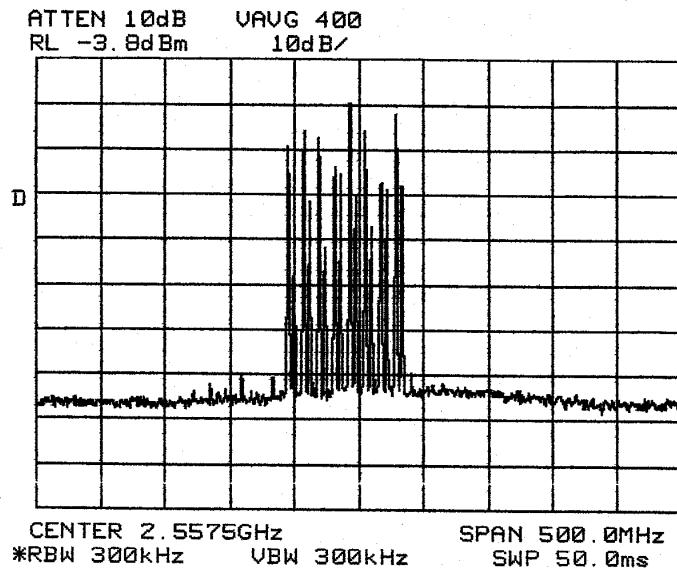

Using the test set-up of section 3.1, with the output power adjusted to 31.5 Watts total average, the spectrum outside of the specified band was observed and the data was taken on all products above the -70 dB noise floor of the spectrum analyzer (see spectrum plot below). All spectral points were measured at the same resolution bandwidth used to establish the reference level on the analyzer.

**Out-of-Band Power Plot/500 MHz Span (31.5 Watts total average):**

| Frequency (MHz) | Source                     | Level Observed   |

|-----------------|----------------------------|------------------|

| 2500 – 2690     | operating band             | 0 dB (reference) |

| 2500            | lower band edge            | -63.0 dB         |

| 2499.75         | -250.0 KHz below band edge | -63 dB           |

| 2497            | -3.0 MHz below band edge   | -66 dB           |

| 2480            | -20.0 MHz below band edge  | -65 dB           |

| <2480           | --                         | -63 dB (max)     |

| 2690            | upper band edge            | -63 dB           |

| 2690.25         | +250.0 KHz above band edge | -64 dB           |

| 2693            | +3.0 MHz above band edge   | -64 dB           |

| 2671            | +20.0 MHz above band edge  | -65 dB           |

| 5000 – 5380     | 2nd harmonic frequencies   | -69 dB           |

| 7500 – 8070     | 3rd harmonic frequencies   | -65 dB           |

| 10000 – 10760   | 4th harmonic frequencies   | -66 dB           |

| 12500 – 13450   | 5th harmonic frequencies   | -66 dB           |

| 15000 – 16140   | 6th harmonic frequencies   | -65 dB           |

| 17500 – 18830   | 7th harmonic frequencies   | -65 dB           |

| 20000 – 21520   | 8th harmonic frequencies   | -65 dB           |

| 22500 – 24210   | 9th harmonic frequencies   | -64 dB           |

| 25000 – 26900   | 10th harmonic frequencies  | -64 dB           |

### 3.0 ENGINEERING DATA

#### 3.3 Out-of-Band Power - continued

Using the test set-up in Section 3.1, and with the translator adjusted to 31.5 Watts total average output power, the emissions within an unoccupied channel were observed. With the peak visual carrier set as the reference, the spurious emissions were observed recorded (see spectrum plot and table below).

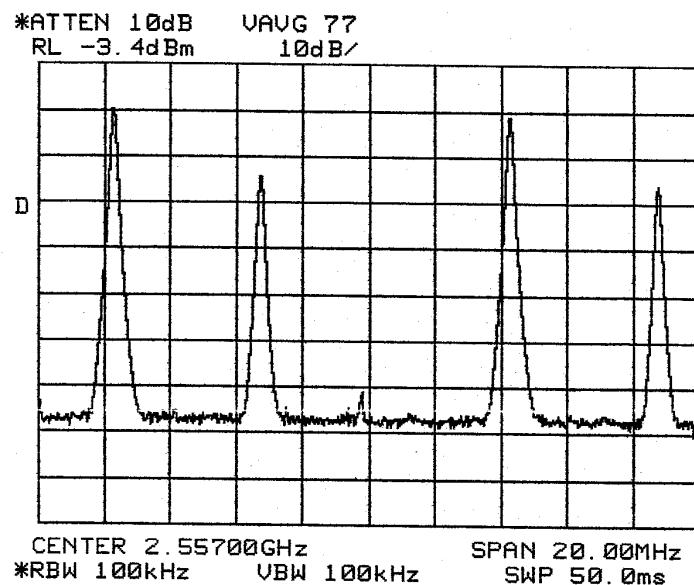

**Unoccupied Channel Emissions Plot (31.5 Watts total average):**

Note: The above plot shows unoccupied channel D1 (2557 MHz center channel)

| Frequency (MHz) | Source                         | Level Observed |

|-----------------|--------------------------------|----------------|

| 2554            | lower channel edge             | -46.1 dB       |

| 2554.25         | +250.0 KHz above lower ch edge | -66.0 dB       |

| 2555            | +1.0 MHz above lower ch edge   | -66.1 dB       |

| 2556            | +2.0 MHz above lower ch edge   | -66.5 dB       |

| 2557            | center channel (3.0 MHz)       | -67.5 dB       |

| 2558            | -2.0 MHz below upper ch edge   | -67.8 dB       |

| 2559            | -1.0 MHz below upper ch edge   | -67.8 dB       |

| 2559.75         | -250.0 KHz below upper ch edge | -67.6 dB       |

| 2560            | upper channel edge             | -68.1dB        |

### 3.0 ENGINEERING DATA

#### 3.3 Out-of-Band Power - continued

After observing the Out-of-Band performance of the translator at 50% rated power, the output power was adjusted to 100 % (63.0 Watts) and the data was retaken (see plots and tables below).

**Out-of-Band Power Plot/500 MHz Span (63.0 Watts total average):**

| Frequency (MHz) | Source                     | Level Observed   |

|-----------------|----------------------------|------------------|

| 2500 – 2690     | operating band             | 0 dB (reference) |

| 2500            | lower band edge            | -62.0 dB         |

| 2499.75         | -250.0 KHz below band edge | -63 dB           |

| 2497            | -3.0 MHz below band edge   | -65 dB           |

| 2480            | -20.0 MHz below band edge  | -66 dB           |

| <2480           | --                         | -62 dB (max)     |

| 2690            | upper band edge            | -64 dB           |

| 2690.25         | +250.0 KHz above band edge | -65 dB           |

| 2693            | +3.0 MHz above band edge   | -66 dB           |

| 2671            | +20.0 MHz above band edge  | -65 dB           |

| 5000 – 5380     | 2nd harmonic frequencies   | -70 dB           |

| 7500 – 8070     | 3rd harmonic frequencies   | -65 dB           |

| 10000 – 10760   | 4th harmonic frequencies   | -67 dB           |

| 12500 – 13450   | 5th harmonic frequencies   | -64 dB           |

| 15000 – 16140   | 6th harmonic frequencies   | -66 dB           |

| 17500 – 18830   | 7th harmonic frequencies   | -67 dB           |

| 20000 – 21520   | 8th harmonic frequencies   | -67 dB           |

| 22500 – 24210   | 9th harmonic frequencies   | -65 dB           |

| 25000 – 26900   | 10th harmonic frequencies  | -63 dB           |

### 3.0 ENGINEERING DATA

#### 3.3 Out-of-Band Power - continued

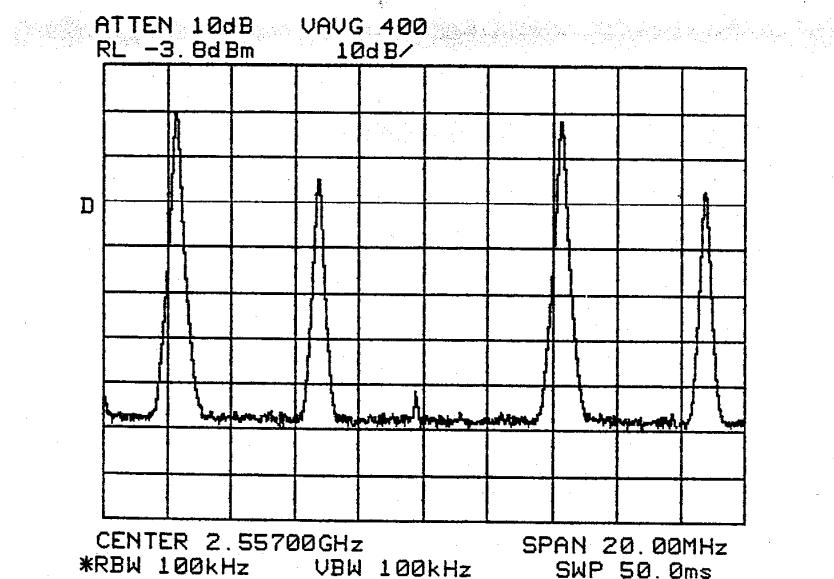

Unoccupied Channel Emissions Plot (63.0 Watts total average):

Note: The above plot shows unoccupied channel D1 (2557 MHz center channel)

| Frequency (MHz) | Source                         | Level Observed |

|-----------------|--------------------------------|----------------|

| 2554            | lower channel edge             | -46.6 dB       |

| 2554.25         | +250.0 KHz above lower ch edge | -65.5 dB       |

| 2555            | +1.0 MHz above lower ch edge   | -67.5 dB       |

| 2556            | +2.0 MHz above lower ch edge   | -67.6 dB       |

| 2557            | center channel (3.0 MHz)       | -67.8 dB       |

| 2558            | -2.0 MHz below upper ch edge   | -67.4 dB       |

| 2559            | -1.0 MHz below upper ch edge   | -68.1 dB       |

| 2559.75         | -250.0 KHz below upper ch edge | -67.3 dB       |

| 2560            | upper channel edge             | -67.5dB        |

## 3.0 ENGINEERING DATA

### 3.4 Radiated Emissions

Using the test set-up below, with the translator operating at full output power (63 Watts total average) and with eight input signals, the spectrum analyzer was moved 20 meters from the booster and connected to a dipole antenna cut to the visual carrier frequency of A1 (2501.25 MHz). This antenna was oriented to maximize the received level, and the data was recorded. The antenna was then cut to the remaining seven center channel frequencies and the second through the tenth harmonic frequencies and all signals received were maximized by antenna orientation, and their absolute levels were recorded (see table below).

Test Set-up:

#### MEASURED LEVELS

| Frequency (MHz) | Source                    | Level Observed (into 50 Ω) |

|-----------------|---------------------------|----------------------------|

| 2500 – 2690     | operating band            | None Observed              |

| 5000 – 5380     | 2nd harmonic frequencies  | None Observed              |

| 7500 – 8070     | 3rd harmonic frequencies  | None Observed              |

| 10000 – 10760   | 4th harmonic frequencies  | None Observed              |

| 12500 – 13450   | 5th harmonic frequencies  | None Observed              |

| 15000 – 16140   | 6th harmonic frequencies  | None Observed              |

| 17500 – 18830   | 7th harmonic frequencies  | None Observed              |

| 20000 – 21520   | 8th harmonic frequencies  | None Observed              |

| 22500 – 24210   | 9th harmonic frequencies  | None Observed              |

| 25000 – 26900   | 10th harmonic frequencies | None Observed              |

## 3.0 ENGINEERING DATA

### 3.4 Radiated Emissions - continued

Note: The spectrum analyzer had a maximum sensitivity of -100 dBm during these tests.

These levels were then compared to the following reference level:

If all of the transmitter's power (63 Watts) was radiated by an isotropic radiator, the power density at 20 meters would be:

$$P_d = P_t / 4\pi R^2 = 63 / 4\pi (20)^2 \cong 12.534 \times 10^{-3} \text{ W/m}^2$$

Using a dipole transmitting antenna increases this by 1.64 to:

$$1.64 * 12.534 \times 10^{-3} = 20.555 \times 10^{-3} \text{ W/m}^2$$

If a dipole receive antenna of area  $1.64 * \lambda^2 / 4\pi$  is used to receive the signal, the received level would be:

$$20.555 \times 10^{-3} * 1.64 * \lambda^2 / 4\pi = 38.1 \times 10^{-6} \text{ W} = -44.2 \text{ dBw} = -14.2 \text{ dBm}$$

Therefore, with a carrier reference level of -24.2 dBm, and a analyzer measurement threshold of -100 dBm, no measured values exceeded a level of:

**-100 dBm -(-14.2 dBm) = -85.8 dBc**

## 3.0 ENGINEERING DATA

### 3.5 Frequency Stability

#### Channel Oscillator Analysis

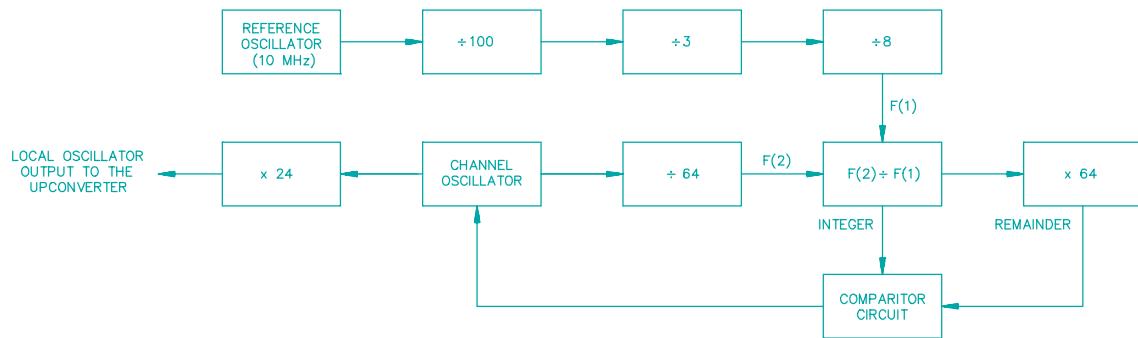

The following is the functional block diagram for phase-locking the channel oscillator:

$F_r$  = Reference oscillator frequency

$F_{co}$  = Channel oscillator frequency

$E_r$  = Reference oscillator error

$E_{co}$  = Channel oscillator error

$$F(1) = F_r/2400$$

$$F(2) = F_{co}/64$$

$$F(2)/F(1) = 37.5 \times (F_{co}/F_r) \quad (\text{Equation 1})$$

The comparitor circuit sends an error voltage to the channel VCXO, which maintains the value derived by equation 1. If error is introduced to the reference oscillator ( $E_r$ ), the comparitor offsets the channel VCXO in a manner that preserves the relationship in equation 1. This offset is defined as the channel oscillator error ( $E_{co}$ ). The following is an algebraic definition for the channel oscillator error:

$$37.5 \times (F_{co} + E_{co})/(F_r + E_r) = 37.5 \times F_{co}/F_r$$

$$(F_{co} + E_{co})/(F_r + E_r) = F_{co}/F_r$$

$$F_r \times (F_{co} + E_{co}) = F_{co} \times (F_r + E_r)$$

$$F_r \times E_{co} = F_{co} \times E_r$$

$$E_{co} = E_r \times (F_{co}/F_r) \quad (\text{Equation 2})$$

The local oscillator (L.O.) frequency is 24 times the channel oscillator, or  $24 \times F_{co}$ . The RF output frequency is the upper product of mixing the L.O. with the superband input signal ( $F_{input}$ ). The following is the algebraic expression for the output frequency:

$$RF = [24 \times F_{co}] + F_{input} \text{ or,}$$

$$RF = [24 \times (F_{co} + E_{co})] + F_{input} \quad (\text{error introduced into the equation})$$

## 3.0 ENGINEERING DATA

### 3.5 Frequency Stability - continued

Based on the above equation, the following equation gives the expression for the error in the output RF:

$$RF_{\text{error}} = [24 \times E_{\text{co}}]$$

Substituting equation 2 into the above error equation yields the following:

$$RF_{\text{error}} = [24 \times (E_r \times F_{\text{co}}/F_r)] \quad (\text{Equation 3})$$

Substituting the channel oscillator frequency (94.91667 MHz), and the reference oscillator frequency (10.0 MHz) into equation 3 yeilds:

$$F_r = 10 \text{ MHz} \quad F_{\text{co}} = 113.625 \text{ MHz} \quad E_{\text{if}} = 440 \text{ Hz}$$

$$RF_{\text{error}} = 227.80 \times E_r \quad (\text{Equation 4})$$

The 10 MHz reference oscillator was placed in a Thermotron temperature test chamber, and the temperature was varied from -30°C to +50°C. The frequency of the oscillator was measured at 10°C increments up to +50°C. The oscillator was allowed a reasonable amount of time to stabilize at each temperature increment. The data on the following pages records the reference oscillator frequency over a the temperature range and a calculation of the output frequency error. This data indicates that the transmitter's output frequency is within the FCC tolerance for this service.

### 3.0 ENGINEERING DATA

#### 3.5 Frequency Stability - continued

##### OSCILLATOR TEMPERATURE STABILITY DATA

| TEMP. (°C) | 10.00 MHz<br>Reference Oscillator | Reference Oscillator<br>Error (E <sub>r</sub> ) | Output Frequency Error<br>(227.80 x E <sub>r</sub> ) |

|------------|-----------------------------------|-------------------------------------------------|------------------------------------------------------|

| -30        | 10.000001.2 MHz                   | 1.2 Hz                                          | 273.46 Hz                                            |

| -20        | 10.000001.0 MHz                   | 1.0 Hz                                          | 227.80 Hz                                            |

| -10        | 10.000000.8 MHz                   | 0.8 Hz                                          | 182.24 Hz                                            |

| 0          | 10.000000.5 MHz                   | 0.5 Hz                                          | 113.90 Hz                                            |

| +10        | 10.000000.0 MHz                   | 0.0 Hz                                          | 0.0Hz                                                |

| +20        | 10.000000.0 MHz                   | 0.0 Hz                                          | 0.0Hz                                                |

| +30        | 10.000000.4 MHz                   | 0.4 Hz                                          | 91.12 Hz                                             |

| +40        | 10.000000.1 MHz                   | 0.1 Hz                                          | 22.78 Hz                                             |

| +50        | 10.000000.7 MHz                   | 0.7 Hz                                          | 159.46 Hz                                            |

## 3.0 ENGINEERING DATA

### 3.5 Frequency Stability - continued

#### FREQUENCY STABILITY VS. LINE VOLTAGE

| Line Voltage<br>(VAC at 60 Hz) | 10.00 MHz<br>Reference Oscillator | Reference Oscillator<br>Error (E <sub>r</sub> ) | Output Frequency Error<br>(227.80 x E <sub>r</sub> ) |

|--------------------------------|-----------------------------------|-------------------------------------------------|------------------------------------------------------|

| 95V                            | 10.000000 MHz                     | 0 Hz                                            | 0 Hz                                                 |

| 115V                           | 10000000 MHz                      | 0 Hz                                            | 0 Hz                                                 |

| 135V                           | 10000000 MHz                      | 0 Hz                                            | 0 Hz                                                 |

### **3.0 ENGINEERING DATA**

#### **3.6 Test Equipment**

| <b>MODEL</b> | <b>MANUFACTURER</b>  | <b>DESCRIPTION</b>                           | <b>SERIAL #</b> |

|--------------|----------------------|----------------------------------------------|-----------------|

| 8564E        | Hewlett Packard      | Spect. Analyzer 9 KHz - 40 GHz               | 3619A02932      |

| 8714B        | Hewlett Packard      | Network Analyzer .01 GHz - 40 GHz US35490400 |                 |

| 3003-30      | Narda                | 30 dB Directional Coupler                    | 20873           |

| 300340       | Narda                | 10 dB Directional Coupler                    | 1453            |

| 435A         | Hewlett Packard      | RF Power Meter                               | 1601A03842      |

| 8481B        | Hewlett Packard      | 30 Watt Power Sensor                         | 3318A09253      |

| 77           | Fluke                | Digital Multimeter                           | 81000244        |

| 8401         | Termaline            | Coaxial Resistor                             | 6622            |

| C31243       | Californai Amplifier | Low Noise Downconverter                      | 24866           |

## 4.0 IDENTIFICATION LABELS/LABEL PLACEMENT AND PHOTOGRAPHS

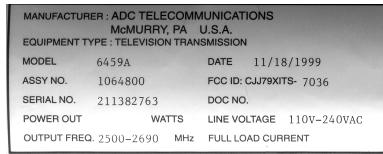

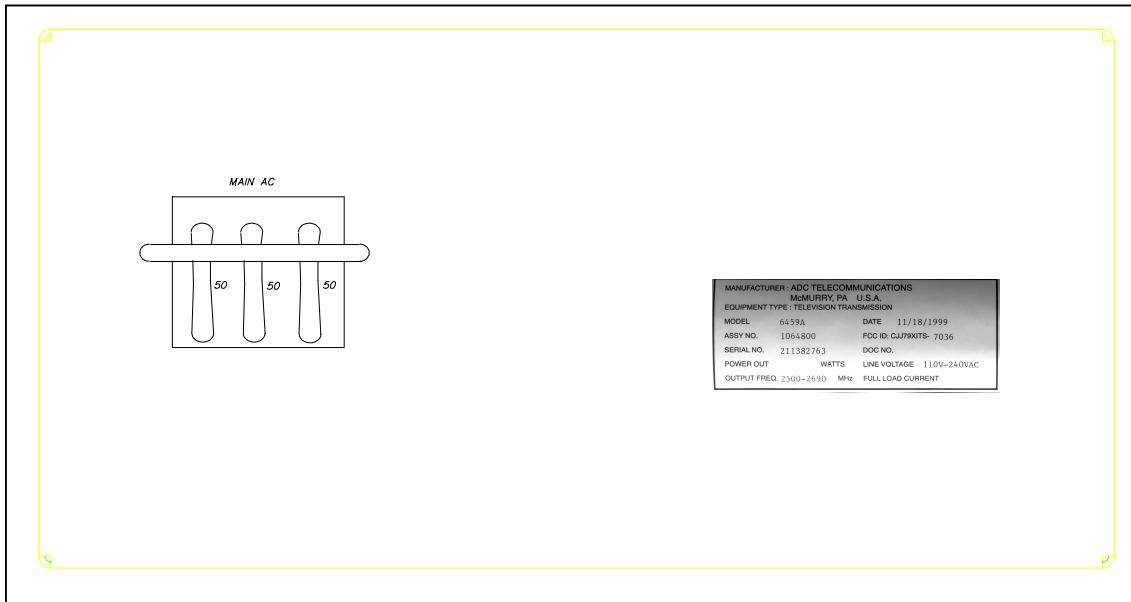

### 4.1 Rear Panel FCC Identification Label:

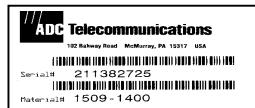

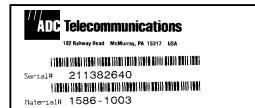

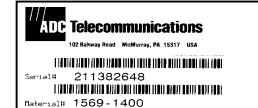

### 4.2 Rear Panel ADC Telecommunications Manufacturer's Labels:

Broadband Translator Tray

Intermediate Broadband Amplifier Tray

Combined Metering Tray

Broadband Amplifier Tray

Broadband Amplifier Tray

Broadband Amplifier Tray

Broadband Amplifier Tray

## 4.0 IDENTIFICATION LABELS/LABEL PLACEMENT AND PHOTOGRAPHS - continued

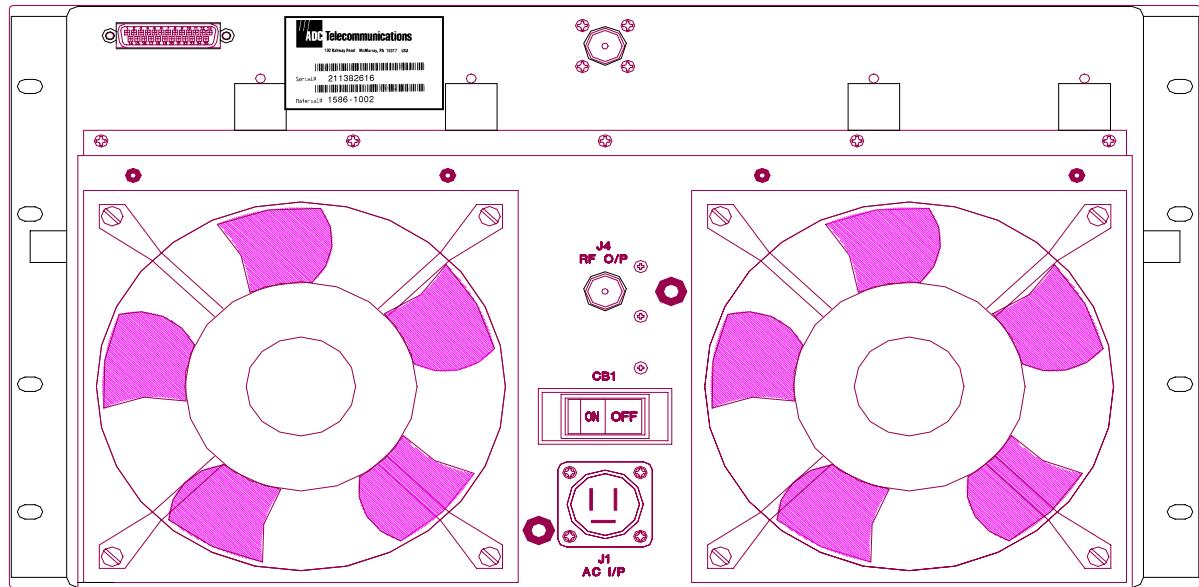

### 4.3 Rear Panel Drawing (Label Placement)

Rear Panel (AC Distribution Tray)

## 4.0 IDENTIFICATION LABELS/LABEL PLACEMENT AND PHOTOGRAPHS - continued

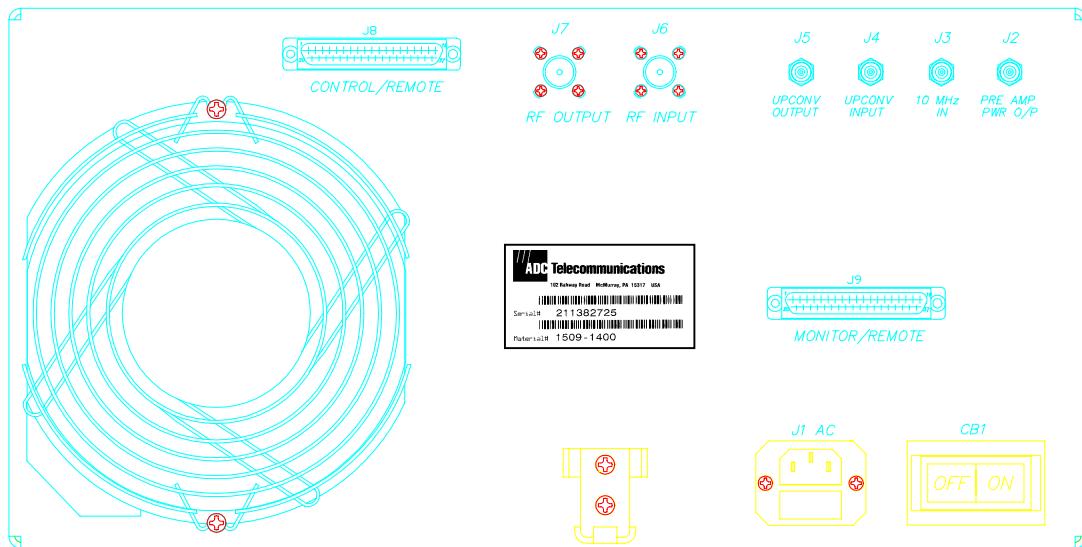

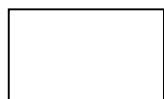

### 4.3 Rear Panel Drawing (Label Placement)

Rear Panel (Broadband Booster Tray)

## 4.0 IDENTIFICATION LABELS/LABEL PLACEMENT AND PHOTOGRAPHS - continued

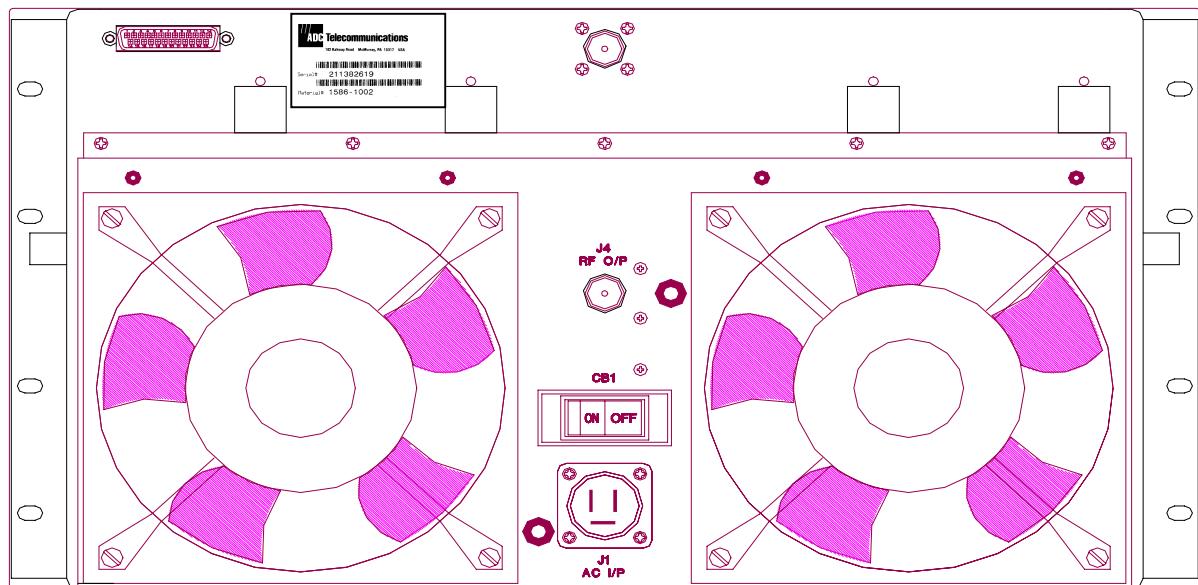

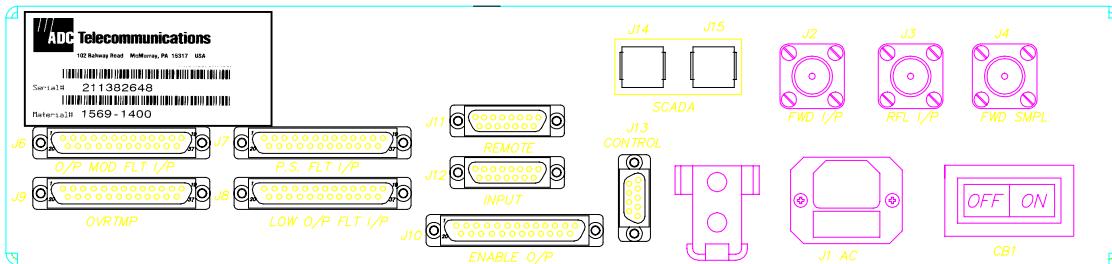

### 4.3 Rear Panel Drawing (Label Placement)

Rear Panel (Intermediate Broadband Amplifier Tray)

## 4.0 IDENTIFICATION LABELS/LABEL PLACEMENT AND PHOTOGRAPHS - continued

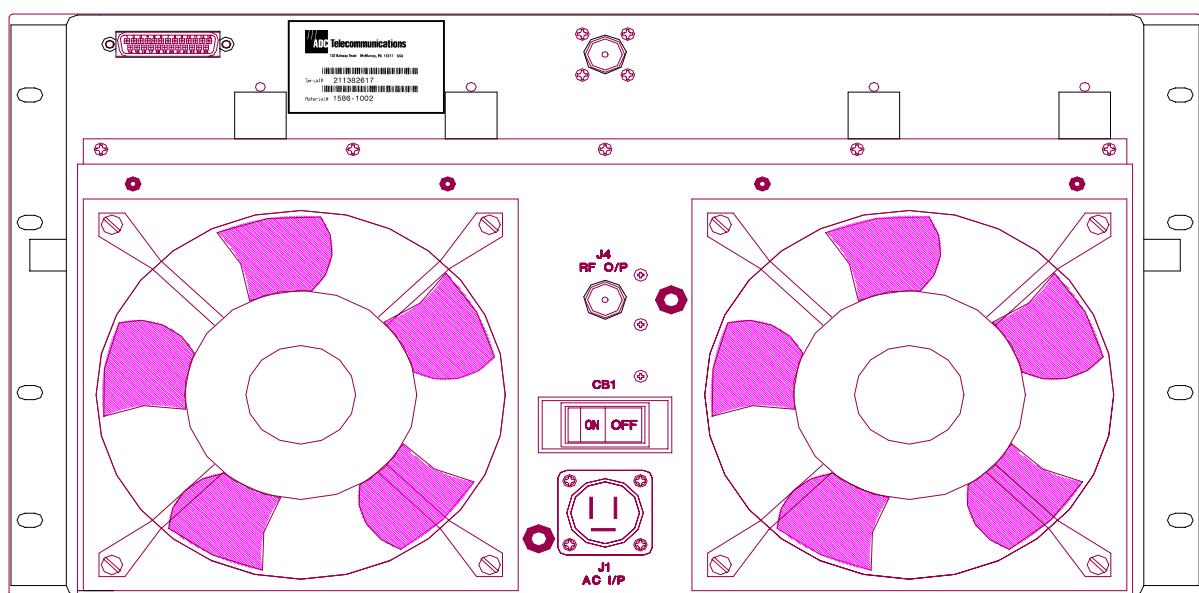

### 4.3 Rear Panel Drawing (Label Placement)

Rear Panel (Broadband Amplifier Tray #1)

## 4.0 IDENTIFICATION LABELS/LABEL PLACEMENT AND PHOTOGRAPHS - continued

### 4.3 Rear Panel Drawing (Label Placement)

Rear Panel (Broadband Amplifier Tray #2)

## 4.0 IDENTIFICATION LABELS/LABEL PLACEMENT AND PHOTOGRAPHS - continued

### 4.3 Rear Panel Drawing (Label Placement)

Rear Panel (Broadband Amplifier Tray #3)

## 4.0 IDENTIFICATION LABELS/LABEL PLACEMENT AND PHOTOGRAPHS - continued

### 4.3 Rear Panel Drawing (Label Placement)

Rear Panel (Broadband Amplifier Tray #4)

## 4.0 IDENTIFICATION LABELS/LABEL PLACEMENT AND PHOTOGRAPHS - continued

### 4.3 Rear Panel Drawing (Label Placement)

Rear Panel (Combined Metering Tray)

## 4.0 PHOTOGRAPHS AND LABELS - continued

### 4.4 Photograph List

**Note: The following photos can be found in the external photos attachment:**

- 4.4.1 Front view, complete 6459A Broadband Translator.

- 4.4.2 Rear view, complete 6459A Broadband Translator.

**Note: The following photos can be found in the internal photos attachment:**

- 4.4.3 Rear view, AC Distribution Panel.

- 4.4.4 Top view, AC Distribution Panel.

- 4.4.5 Front view, Combined Metering tray.

- 4.4.6 Rear view, Combined Metering tray.

- 4.4.7 Top view, Combined Metering tray.

- 4.4.8 Front view, Broadband Translator tray.

- 4.4.9 Rear view, Broadband Translator tray.

- 4.4.10 Top view, Broadband Translator tray flip plate (Filters/Amplifier Module/X3 Multiplier/Mixer).

- 4.4.11 Bottom view, Broadband Translator tray flip plate (VHF Generator/10 MHz Reference/X8 Multiplier).

- 4.4.12 Top view, Broadband Translator tray (Amplifier Modules/DC Power Supply /Translator Control).

- 4.4.13 Bottom view, Broadband Translator tray (Switching Power Supplies).

- 4.4.14 Front view, Intermediate Broadband Amplifier tray (closed front door).

- 4.4.15 Front view, Intermediate Broadband Amplifier tray (open front door).

- 4.4.16 Rear view, Intermediate Broadband Amplifier tray.

- 4.4.17 Top view, Intermediate Broadband Amplifier tray (Power Amplifier Module).

- 4.4.18 Top view, Intermediate Broadband Amplifier tray (Power Supply Module).

- 4.4.19 Front view, Broadband Amplifier tray (closed front door).

- 4.4.20 Front view, Broadband Amplifier tray (open front door).

- 4.4.21 Rear view, Broadband Amplifier tray.

- 4.4.22 Top view, Broadband Amplifier tray (Power Amplifier Module).

- 4.4.23 Top view, Broadband Amplifier tray (Power Supply Module).

- 4.4.24 Top view, 4-Way Splitter Module.

- 4.4.25 Top view, Waveguide Combiner.

## 5.0 CERTIFICATION OF TEST DATA

This equipment has been tested in accordance with the requirements contained in the appropriate Commission regulation. To the best of my knowledge, these tests were performed using measurement procedures consistent with industry or Commission standards and demonstrate that the equipment complies with the appropriate standards. Each unit manufactured, imported or marketed, as defined in the Commission's regulations, will conform to the sample(s) tested within the variations that can be expected due to quantity production and testing on a statistical basis. I further certify that the necessary measurements were made by ADC Telecommunications, 102 Rahway Road, McMurray, Pennsylvania 15317.

Dave Urban

Dave Urban, Chief Engineer

Todd Anderson

Todd Anderson, Engineer