# **TPL-100A RF Theory of Operation**

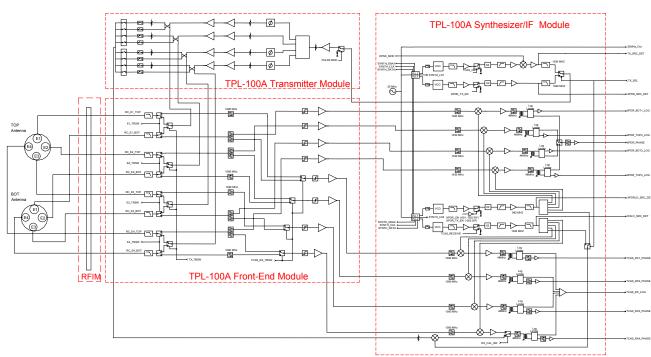

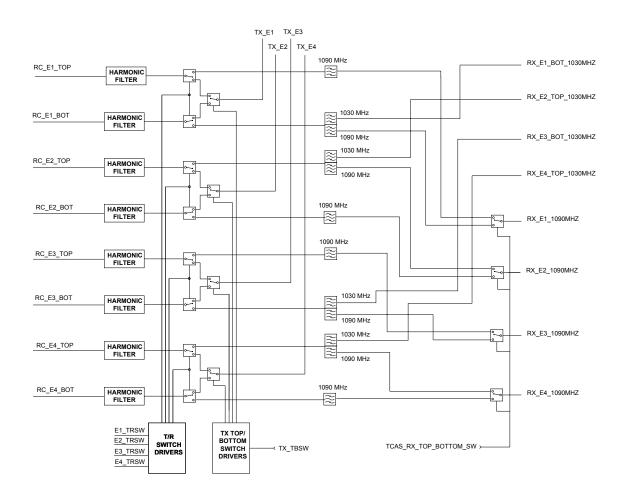

TPL-100A RF Block Diagram

# Transmitter Assembly

The transmitter consists of the following primary sub circuits:

- Digital interface control

- RF modulator / pulse forming network

- Four power amplifier channels

- RF amplifier bias control

- Integrated phase shifters

- Integrated Whisper/Shout attenuators

- Transmitter calibration

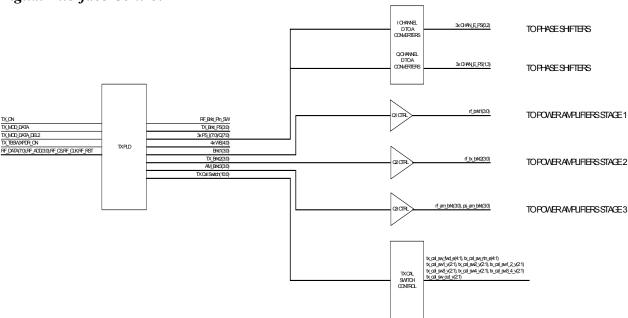

## Digital Interface Control

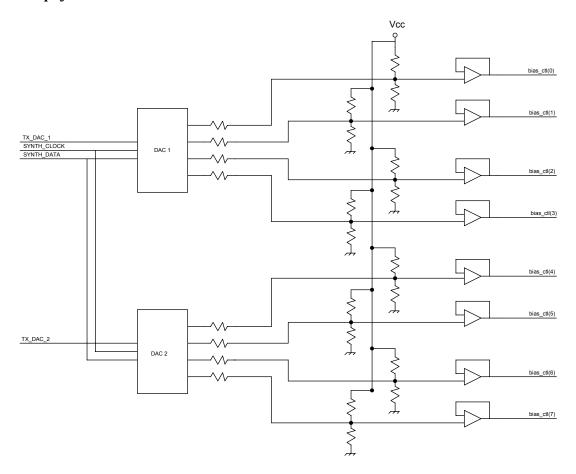

The digital interface control consists of a PLD, three sets of 8-bit digital to analog converter(s) (DAC), three sets of bias drivers and four quad analog switches.

The PLD contains one-time programmable logic gates configured to drive the phase shifters, digital attenuators, RF power amplifier gates, RF modulation signals and transmitter calibration switches. The PLD inputs are the timing brackets which drive the RF power amplifier gates, 4 address lines, 8 data lines and chip select, clock and reset lines. The output levels of the PLD are 3.3V Transistor-Transistor Logic (TTL).

RF channels 1, 3 and 4 contain phase shifters. Channel 2 is the reference channel and does not use a phase shifter. Three pairs of 8-bit DACs control the three RF phase shifters. Each 8-bit DAC controls an I channel or a O channel of the associated phase shifter.

Each DAC takes a TTL input from the PLD and outputs an analog level to the associated phase shifter in the RF channel.

Bias drivers which take TTL signals from the PLD control the timing of each of the three stages of the power amplifier channels. A current source controls stage 1. A bias control circuit controls the voltage levels at the gates of stages 2 and 3.

The transmitter calibration circuit consists of a network of Monolithic Microwave Integrated Circuit (MMIC) switches controlled using four quad analog switches. The PLD controls the analog switches using a logic map to switch the selected RF path to the calibration output connector.

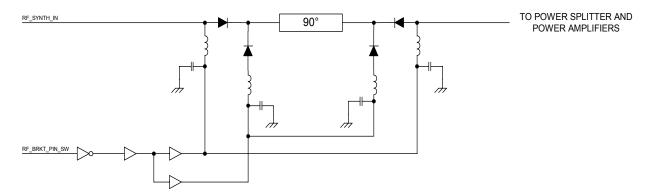

#### RF Modulator / PFN

The PFN directly modulates the RF signal generated from the receiver assembly.

The PLD drives a TTL signal to an inverter gate at RF\_BRKT\_PIN\_SW. The inverter gate shifts the voltage level into the PFN and drives the control amplifiers. The control amplifiers drive the PIN diodes of the RF circuit and modulate the RF signal received at RF\_SYNTH\_IN. The positive-intrinsic-negative (PIN) diodes in the RF circuit attenuate or pass the RF signal as they are activated by the control amplifiers.

The 90 degree phase shift, comprised of lumped components, increases the attenuating capability of the RF circuit.

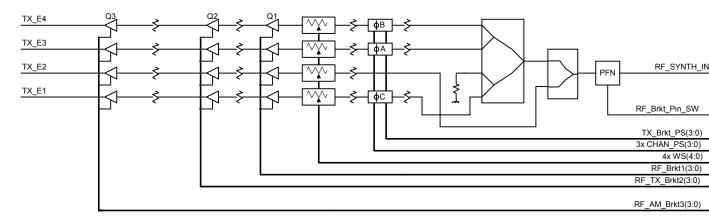

## Four power amplifier channels

The four power amplifiers comprise 3 stages. Each stage is gated on during the transmit cycle.

The first stage uses a MMIC gain block capable of delivering +9 dbm.

The second stage is a commercial IC which is made up of 3 stages. It is capable of delivering 10 watts of power. The gain is controlled by adjusting the level of each gate voltage driven separately by rf\_tx\_brkt2(0), rf\_tx\_brkt2(1), rf\_tx\_brkt2(2), and rf\_tx\_brkt2(3). The gain is adjusted to compensate for temperature variation of the chain. The drain voltage is set to 26 volts.

The output stage is a laterally diffused metal oxide semiconductor (LDMOS) device capable of delivering 200 watts. The gate voltage is adjusted for a drain current of 1.8 amp when no RF signal is present. The gate voltages are independently controlled with rf\_am\_brkt3(0), rf\_am\_brkt3(1), rf\_am\_brkt3(2), and rf\_am\_brkt3(3). The drain voltage is set to 32 volts using 4 linear voltage regulators.

### RF amplifier bias control

The peak current of the stage 1 IC is set to 27ma using feedback amplifiers Q13, Q14, Q15, and Q16.

The gate signal timing pulses tx\_brkt2(0), tx\_brkt2(1), tx\_brkt2(2), tx\_brkt2(3) going to the 2<sup>nd</sup> stage amplifier MHVIC910HR2 are ac coupled to prevent excessive duration of the transmitted pulse. The level of each gate signal bias\_ctl(0), bias\_ctl(2), bias\_ctl(4), bias\_ctl(6) is adjusted by measuring the drain current in each IC. The current is measured by measuring the voltage across R468 (1 ohm). This voltage is proportional to the 26 volt power supply going to the power amplifier.

The gate bias to the output stage is adjusted to control the drain current. The power supply voltage to the metal-oxide semiconductor field-effect transistor (MOSFET) driver is adjusted to control the 4 gate bias lines (bias\_ctl(1), bias\_ctl(3), bias\_ctl(5), bias\_ctl(7)). The gate bias is ac coupled to prevent CW transmission in the case of a digital fault. The drain current is measured by measuring the voltage across 1 ohm resistor, R468.

Software turns on each stage individually to make current measurements.

### Integrated phase shifters

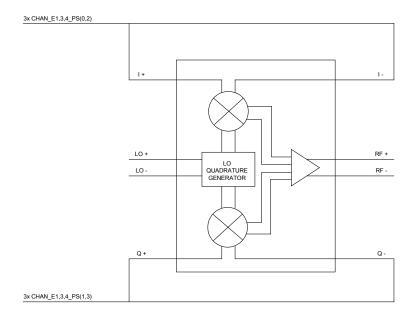

The 3 phase shifters use I/Q modulators to adjust the phase. The Q and I input levels are differential signals coming from 8 bit DACs.

The I and Q input signals also adjust the gain by up to 6 db. They are labeled chan\_e1\_ps(3:0), chan\_e3\_ps(3:0), chan\_e4\_ps(3:0). The phase shifters are turned on only during the transmit cycle by TTL signals rf tx brkt ps(0), rf tx brkt ps(2), and rf tx brkt ps(3).

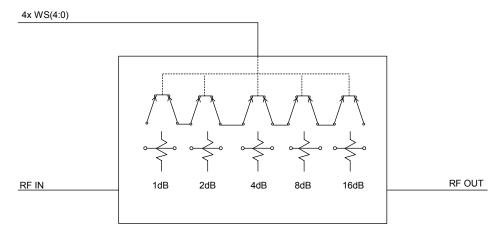

## Integrated WS attenuators

Each of the four power amplifier channels uses a WS attenuator. The WS attenuators use a commercial MMIC which is a 5-bit digital attenuator with integral TTL driver. The PLD directly controls the WS attenuator for each channel independently through signals WS\_E1(4:0), WS\_E2(4:0), WS\_E3(4:0) and WS\_E4(4:0). The attenuation step size is 1dB and provides 31dB of total attenuation range.

#### Transmitter calibration

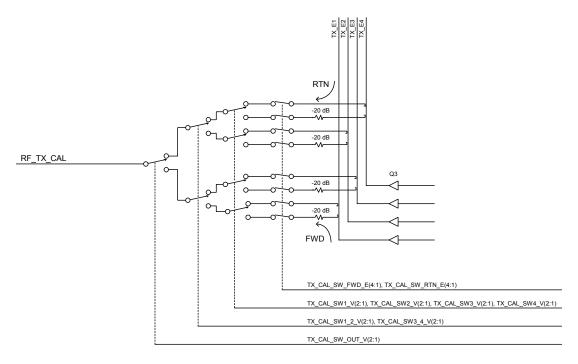

The transmitter calibration network consists of four printed couplers and three sets of MMIC switches.

At the output of each of the four power amplifier channels there is a printed coupler used to sample the RF power level at the output of the transmitter. The forward arm of each coupler contains a 20dB attenuator to protect the MMIC switches in the calibration network.

The first set of MMIC switches are single pole – single throw and switch either the forward or return arm of the printed coupler into the calibration network. These are controlled using the TX\_CAL\_SW\_FWD\_E(4:1) and TX\_CAL\_SW\_RTN\_E(4:1) signals.

The second set of MMIC switches selects the channel which is to be calibrated. These are controlled using the TX\_CAL\_SW1\_V(2:1), TX\_CAL\_SW2\_V(2:1), TX\_CAL\_SW3\_V(2:1) and TX\_CAL\_SW4\_V(2:1) signals.

The third set of MMIC switches connects the selected channel to the output connector. These are controlled using the TX\_CAL\_SW1\_2\_V(2:1) and TX\_CAL\_SW3\_4\_V(2:1) and TX\_CAL\_SW\_OUT\_V(2:1) signals.

## Receiver Assembly

The receiver consists of the following primary sub circuits.

- RF Switch

- LNA

- IF

- Synthesizer

#### RF Switch

The RF switch section contains the transmit top/bottom antenna switch, transmit/receive switch, TCAS receive top/bottom switch, transmit top/bottom switch drivers, and transmit/receive switch drivers. The RF switches consists of an arrangement of one-quarter wavelength microstrips with pin diodes that provide multiple RF signal pathways. The transmit top/bottom switch has common control for the four channels and the transmit/receive switch has individual control for each channel. Each of the eight antenna inputs has a harmonic filter before the RF switches.

The transmit/receive switching elements are controlled individually by four power MOSFET drivers and are controlled by the logic signals E1\_TRSW, E2\_TRSW, E3\_TRSW, and E4\_TRSW. The transmit TOP/BOTTOM switching elements are controlled by logic signal TX\_TBSW. Switching time is 400 nanoseconds (ns), or less. The transmit top/bottom switch provides 20 dB minimum isolation between elements. The transmit/receive switch provides 20 dB minimum isolation between paths.

The RF Switch section also contains the first stage of filtering for the receive signals. High-Q ceramic 2-pole bandpass filters are used in each receive signal path to attenuate out of band signals.

$RX_Ex_1030MHz$  and  $RX_Ex_1090MHz$  signals are then routed to the Limiter/LNA sections of the receiver.  $TX_E1$  through  $TX_E4$  are each routed to a connector that brings in the transmit signal from the transmitter module.

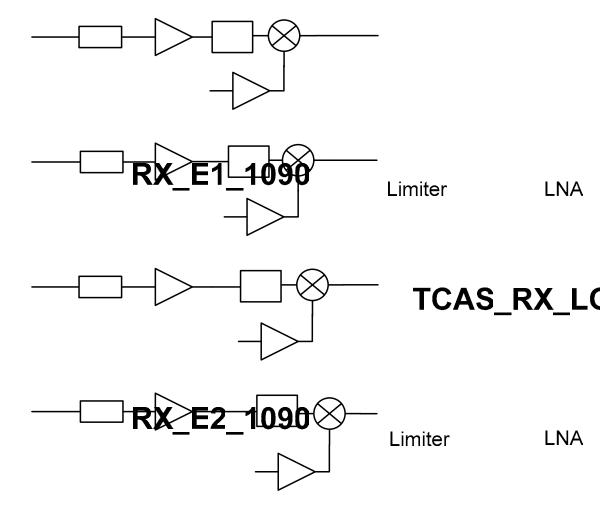

The LNA section is shown. This section includes a limiter, LNA and 1090 MHz bandpass filtering for the input RF signals for the four receiver channels. This section rejects image frequencies and any other necessary outside the selected band. The low-level received signals in each receiver channel are boosted to a higher level by the LNA, and then filtered by filtered by high-Q ceramic 2-pole bandpass filters,. A diode limiter circuit is used for protection from high input power. The 1090 MHz received signal is mixed with the 1042 MHz RX\_LO (1-4) to produce the 48 MHz IF output for each channel that is sent to the IF section. Each 1042 MHz RX\_LO signal is applied to a RF gain block amplifier to apply proper signal strength for the mixers.

TCAS\_R

**RX\_E4\_1090**

Limiter LNA

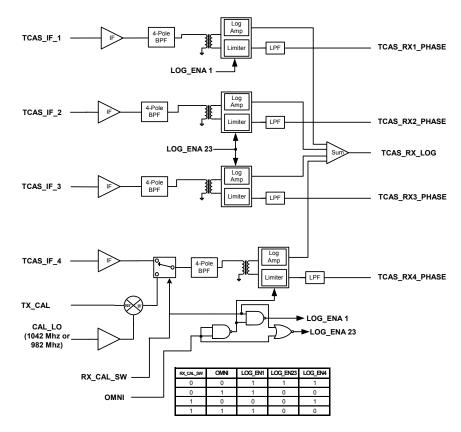

The IF section, shown in block diagram, provides an additional stage of amplification for each of the four receiver channels provides additional filtering for the 48MHz IF signals, and divides each channel into limited video to the digital module, and a summed log signal to the digital module.

The IF inputs from the LNA section (TCAS\_IF\_1, IF\_2, IF\_3, and IF\_4), that are received replies from the antenna are each amplified and filtered through a 4-pole band pass filter (BPF). The IF\_4 signal differs from the other channels in there is a single pole double throw (SPDT) which can route in the TX\_CAL signal for transmitter calibration of 1090 MHz and 1030 MHz transmissions. These signals are then applied to a limiting-logarithmic amplifier. A lumped element low pass filter (LPF) further filters the limiting signal. Each log amplifier produces an output that is a logarithmic function of its input. The outputs from the four log amplifiers are applied to a log summer and buffer circuit, which produces a negative pulse output scaled to 20 millivolts (mV) per dB. The TCAS\_RX\_LOG output is routed to the digital module where it is decoded to determine range and altitude.

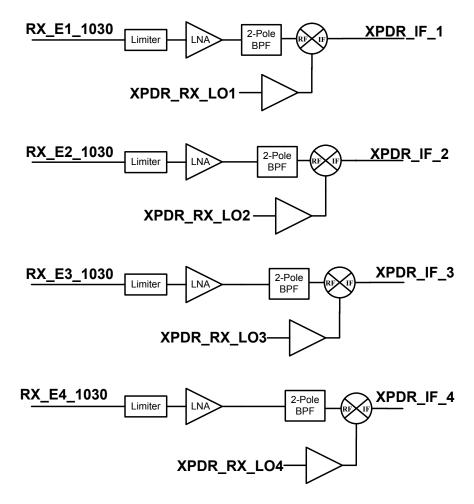

The LNA is shown. This section includes LNA and 1030 MHz bandpass filtering for the input RF signals for the four receiver channels. This section rejects image frequencies and any other noise outside the selected band. The low-level received signals in each receiver channel are boosted to a higher level by the LNA, and then filtered by high-Q ceramic 2-pole bandpass filters. A diode limiter circuit is used for protection from high input power. The 1030 MHz received signal is mixed with the 982 MHz RX\_LO (1-4) to produce the 48 MHz IF output for each channel that is sent to the IF section. Each 982 MHz RX\_LO signal is applied to a RF gain block amplifier to apply proper signal strength for the mixers.

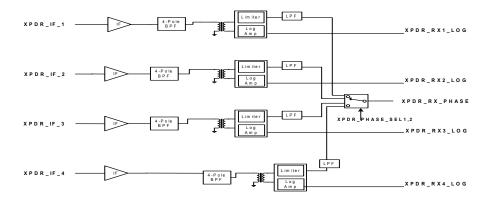

### Rx 1030 MHz - IF

The IF section, shown in block diagram, provides an additional stage of amplification for each of the four Transponder receiver channels provides additional filtering for the 48MHz IF signals and divides each channel into limited video to the digital module, and a summed log signal to the digital module.

The IF inputs from the LNA section (XPDR\_IF\_1, IF\_2, IF\_3, and IF\_4) that are received replies from the antenna are each amplified and filtered through a 4-pole BPF. These signals are then applied to a limiting-logarithmic amplifier. A lumped element LPF further filters the limiting signal. Each log amplifier produces an output that is a logarithmic function of its input. The outputs from the four limiter amplifiers are selected by a switch and the XPDR\_RX\_PHASE signal is routed to the digital module where it is decoded along with the four XPDR\_RX\_LOG outputs.

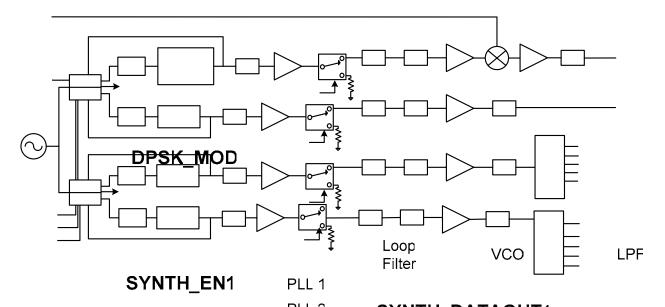

The synthesizer, shown in block diagram, produces the TX\_SIGNALs, SAL\_LOS, TCAS\_RX\_LO (1-4), XPDR\_RX\_LO (1-4) and 20 MHz. The TCAS\_TX\_SIGNAL generates the following frequencies, 1030MHz (TCAS\_TX\_SIGNAL), 1087MHz, 1090MHz, and 1093MHz (XPOR\_TX\_SIGNAL) as selected by TX\_SEL to the transmitter. The calibration LO (CAL\_LO) frequency Figure 2 MHz (XPDR\_CAL\_LO) or 1042 MHz (TCAS\_CAL\_LO) as selected by TX\_SEL. The transponder receiver LO (XPDR\_RX\_LOx) frequency is 982MHz. The TCAS receiver LO (TCAS\_RX\_LOx) frequency is 1042MHz.

Each signal is generated from a single 20 MHz crystal oscillator, which is installed in an oven for precise performance over a wide range of operation temperatures. The 20 MHz signal is applied to two separate dual Phase Lock Loop (PLL) IC. Each PLL circuit operates a voltage controlled oscillator with a loop filter to generate the synthesized frequency. The synthesized frequencies are 52 MHz for the XCAS\_RX\_LO, 545 MHz for the XPDR\_TX\_SIGNAL, and 491 MHz for the XPDR\_RX\_IOPT The TCAS\_TX\_SIGNAL can generate four different synthesized frequencies, 515, 543.5, 545, and 546.5 MHz, depending on transmitter operation.

PLL 2

SYNTH\_DATAOUT2

The following synthesized Signas HC/S\_IK\_SIGNAL, XPDR\_TX\_\$1000PAL, XPDR\_RX\_LO, and TCAS\_RX\_LO are applied to hybrid LPF and RF gain block. A single Figure double throw (SPDT) RF switch is used as an on-off witch. The synthesized frequency is an RF termination. This is controlled by a TTL signal for each synthesized frequency is then doubled to obtain the output frequency. It is filtered with a hybrid band pass filter (HBF) and isolated with RF gain block.

The TCAS\_TX\_SIGNAL is routed to the DPSK mixer, where it can be mixed with a modulated DPSK signal that is generated by 250ns pulse square wave with a 50% duty cycle from the digital module. An additional RF gain stage is used for isolation and then the signal is further filtered by hybrid LPF and then sent directly to the transmitter module.

The XPDR\_RX\_LO and TCAS\_RX\_LO frequencies are filtered by a hybrid LPF. Each signal is routed to the calibration mixer and the RX\_LO is split into five signals by an RF power divider. Four of these signals become Local Oscillator(s) (LO)s for the main receive channels. The fifth signal from each divider is routed to the cal mixer.

The 20MHz signal from the oven controlled crystal oscillator (OCXO) is buffered and then routed through the Front Interconnect to the digital module.

LPF

XPDR\_

**LPF**

XPDR\_

**LPF**

TCAS\_R