# **BR2551E Datasheet**

December 05, 2020

V1.0

# **Version History**

| Revision | Amendment       | Date      | Author       |

|----------|-----------------|-----------|--------------|

| 1.0      | Initial version | 2020-12-5 | Yongqiang Xu |

### Contents

| 1.  | Modu   | lle Block Diagram                | 6   |

|-----|--------|----------------------------------|-----|

|     | 1.1.   | Interface Description            | 6   |

| 2.  | Modu   | lle Performance                  | 7   |

| 3.  | PIN D  | efinition                        | . 8 |

|     | 3.1.   | PIN Descriptions                 | . 8 |

|     | 3.2.   | PIN assignment                   | 10  |

| 4.  | Electr | ical Characteristic              | 10  |

|     | 4.1.   | Recommended Operating Conditions | 10  |

|     | 4.2.   | Digital IO DC Characteristics    | 11  |

|     | 4.3.   | RF Characteristics               | 11  |

|     | 4.4.   | ADC Characteristics              | 11  |

|     | 4.5.   | Power Consumption                | 12  |

| 5.  | Timin  | g Diagram                        | 12  |

|     | 5.1.   | RESET Timing Diagram             | 12  |

| 6.  | Packa  | ge                               | 12  |

| 7.  | Recor  | nmended PCB Package Size         | 13  |

| 8.  | PCB D  | esign Notes                      | 14  |

|     | 8.1.   | Schematic Design Notes           | 14  |

|     | 8.2.   | PCB Layout Design Notes          | 14  |

| 9.  | Packa  | ge Information                   | 15  |

|     | 9.1.   | Package                          | 15  |

|     | 9.2.   | Storage Conditions               | 17  |

| 10. | С      | ompany Profile                   | 18  |

| 11. | С      | ontact Information               | 18  |

|     | 11.1.  | Beijing                          | 18  |

|     | 11.2.  | Shenzhen                         | 18  |

|     | 11.3.  | Shanghai                         | 18  |

| 12. | С      | opyright                         | 19  |

|     |        |                                  |     |

### **Descriptions**

BR2551E is Bluetooth Dual Mode SOC module. A highly integrated SOC for Bluetooth data stream process, BR2551E integrates a low power MCU, RF transceiver, Baseband, Modem, USB Device, SARADC and up to 16 GPIOs in the module. BR2551E offers low cost, low power consumption, flexible and more powerful Bluetooth application. BR2551E operates with a widely power supply range from 1.9V to 3.6V and has very low power consumption in both TX and RX modes, enabling long lifetimes in battery-operated systems while maintaining excellent RF performance. The device can enter an ultra-low power sleep mode in BT sniff mode and BLE connection interval.

### **Module Specifications**

#### Stack Features

- Support Bluetooth specification compliant

- Compatible with V2.1 + EDR

- Support the Bluetooth smart firmware includes Security Manager(SM), Attribute Protocol(ATT), the Generic Attribute Profile(GATT) and Generic Access Profile(GAP)

- Support SPP,HID,HOGP,IAP2

- High speed UART or USB port for BT HCI and AT commands

- Support up to 7 ACLs and 1 SCO/eSCO link for BR/EDR.

- Support up to 4 BLE links(Up to 3 links in slave mode)

#### **Hardware Features**

32-bit RISC processor up to 96MHz

- with on-chip ROM(384Kbytes) and RAM(96Kbytes)

- Operating temperature:  $-40^{\circ}$ C to  $+85^{\circ}$ C

- 1.9V to 3.6V power supply

- 512Kbytes build in flash

- Power modes included shutdown/deep sleep/light sleep/active

- Wake up by UART/GPIO(light sleep), and RTC(deep sleep)

- High speed UART port for BT HCI and Data interface, up to 4Mbps

- Single pin RF connection (50 ohm impedance in TX and Rx modes)

- High performance on-chip RF transceiver with integrated balun

- -94dbm receive sensitivity for LE(1Mbps) mode and -92dbm for BR/EDR mode

- GFSK/π/4-DQPSK/8DPSK modulator

- GFSK/π/4-DQPSK/8DPSK demodulator

- RF/Analog Control (AGC,PA, Ramp up/down timer, Low power)

- Embedded high speed and low power CPU with on-chip ROM(384Kbytes) and RAM(96Kbytes)

- Embedded 4 channel 11bit 1Mbps SARADC for peripheral controls

- Built-in PLL, support system run up to 96MHz, and built-in crystal oscillator 24MHz

- Embedded PMU for efficient power management

- 2x I2C master/slave, support standard and fast mode

- 4 sets PWM interface

- 4-wire SPI(master and slave)

- interface, up to 12MHz

- 8x channels DMA for peripheral interface (UART,USB,I2C,SPI)

- WDT/RTC/8x Timers

- 2x UARTs (uart0 has CTS/RTS)

- Various (total 16) GPIOs for various purposes

- Embedded SPI flash support XIP mode, Facilitate customer application development

- Support firmware upgrade over

### UART or Air(OTA)

### **Applications**

- Printer

- Bluetooth HID

- Free drive dongle

- TV remote controller

- Toys

- data communication application

# 1. Module Block Diagram

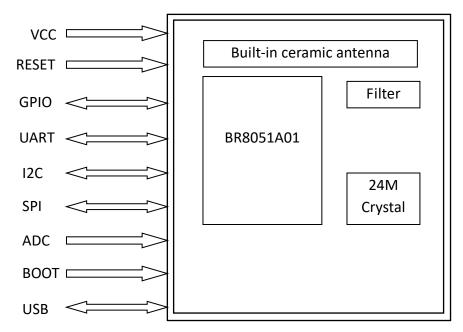

Figure 1 Module Block Diagram

## 1.1. Interface Description

### **VCC**

Standard 1.9 to 3.6V power supply power ripple≤50mV, 3.3V recommended.

### **RESET**

Support hardware reset.

### **BOOT**

Pull down when firmware upgrade, pull up or NC when normal working.

### **UART**

The module's UART is a standard four lines interface (RX/TX/RTS/CTS). Its baud rate can be selected via UART AT command.

Support hardware flow control.

Support speed of up to 4Mbit/s.

Uart0 can be served by the DMA controller.

### I2C

I2C interface supports standard mode (100kbit/s) and fast mode (400kbit/s). The I2C

work as either master or slave mode.

### **GPIO**

Floating level on input signals will cause unstable device operation and abnormal current consumption. Pull-up or Pull-down resistors should be used appropriately for input or bidirectional pins.

### **USB**

Support USB 2.0 full speed mode.

## 2. Module Performance

Table 1 Module Performance

| Module P/N                | BR2551e                                       |

|---------------------------|-----------------------------------------------|

| Bluetooth Specification   | Dual-module, Bluetooth                        |

| Bluetooth Class Type      | Class 2                                       |

| Distance                  | 50m (open area)                               |

| Maximum Output Power      | -2.36dBm                                      |

| Modulation                | GFSK,π/4-DQPSK,8-DPSK                         |

| Hardware Interfaces       | RESET,GPIO,UART, I2C,SPI,BOOT,ADC,USB         |

| Working voltage           | 1.9V to 3.6V                                  |

| Working power consumption | -                                             |

| Idle power consumption    | -                                             |

| Deep sleep power          |                                               |

| consumption               | -                                             |

| Operating temperature     | -40℃ to +85℃                                  |

| Storage temperature       | -55℃ to +125℃                                 |

| Size                      | 15mm*12mm*2.5mm(tolerance ±0.2mm With shield) |

| Shield case               | Yes                                           |

# 3. PIN Definition

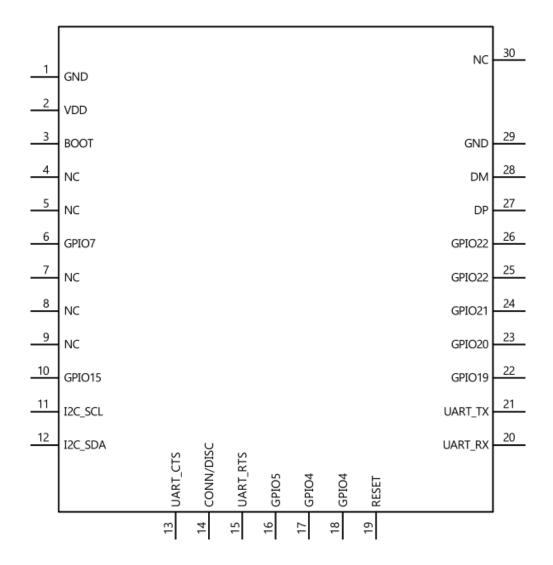

Figure 2 Module PIN Definition

## 3.1. PIN Descriptions

Table 2 PIN Descriptions

|         | 2 000p          |                                                          |

|---------|-----------------|----------------------------------------------------------|

| PIN     | PIN description | Functions                                                |

| 1       | GND             | Ground.                                                  |

| 2       | VDD             | 1.9V to 3.6V power supply, 3.3V recommended. Need        |

| 2   VDD |                 | external 10uF and 0.1uF capacitor connected to this pin. |

| 3 BOOT  |                 | Pull down when firmware upgrade, pull up or NC when      |

| 3       | BOOT            | normal working.                                          |

| 4       | NC              | No Connect                                               |

| 5       | NC              | No Connect                                               |

| 6       | GPIO7           | Configurable GPIO, NC if not used.                       |

| 8 NC No Connect  9 NC No Connect.  10 GPIO15 Configurable GPIO, NC if not used.  12C Clock  11 I2C_SCL GPIO17  NC if not used.  12C DATA |        |

|------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 10 GPIO15 Configurable GPIO, NC if not used.  11 I2C_SCL GPIO17  NC if not used.                                                         |        |

| 11 I2C_SCL I2C Clock GPIO17 NC if not used.                                                                                              |        |

| 11 I2C_SCL GPIO17 NC if not used.                                                                                                        |        |

| NC if not used.                                                                                                                          |        |

|                                                                                                                                          |        |

| I2C DATA                                                                                                                                 |        |

|                                                                                                                                          |        |

| 12   I2C_SDA   GPIO18                                                                                                                    |        |

| NC if not used.                                                                                                                          |        |

| UART flow control, Clear To Send, Pull up prohibited                                                                                     |        |

| 13 UART_CTS sending data, pull down to send. Pull down if not us                                                                         | ed.    |

| GPIO3                                                                                                                                    |        |

| Configurable GPIO, Default DICS PIN                                                                                                      |        |

| Pull up into working mode. Pull down more than 10                                                                                        | 0mS    |

| to disconnect the Bluetooth connection. NC if not u                                                                                      | sed.   |

| GPIO16                                                                                                                                   |        |

| UART flow control, Request To Send.                                                                                                      |        |

| When the Bluetooth serial port buffer is full, this pir                                                                                  | ı will |

| be pulled up, notify the master computer to stop se                                                                                      | rial   |

| port sending; When the buffer is sufficient, this pin                                                                                    | will   |

| be pulled down and allow the master computer to                                                                                          |        |

| continue to send data through the serial port. NC if                                                                                     | not    |

| used.                                                                                                                                    |        |

| GPIO2                                                                                                                                    |        |

| Configurable GPIO, Default conn_status PIN                                                                                               |        |

| 16 GPIO5 Bluetooth Connected is high, unconnected is low. No                                                                             | C if   |

| not used.                                                                                                                                |        |

| 17/18 GPIO4 Configurable GPIO, NC if not used.                                                                                           |        |

| 19 RESET Hardware reset                                                                                                                  |        |

| NC if not used; pull down time> 50ms if used.                                                                                            |        |

| 20 UART RX UARTO data receive                                                                                                            |        |

| 20 UART_RX GPIO1                                                                                                                         |        |

| 21 UART TX UARTO data send                                                                                                               |        |

| 21 UART_TX GPIO0                                                                                                                         |        |

| Configurable GPIO, NC if not used.                                                                                                       |        |

| ADC1                                                                                                                                     |        |

| Configurable GPIO, NC if not used.                                                                                                       |        |

| ADC2                                                                                                                                     |        |

|                                                                                                                                          | -      |

| Configurable GPIO, NC if not used.                                                                                                       |        |

| 25/26 | GPIO22 | Configurable GPIO, NC if not used. |

|-------|--------|------------------------------------|

| 23/20 |        | ADC4                               |

| 27    | DP     | USB DP, NC if not used.            |

| 28    | DM     | USB DM, NC if not used.            |

| 29    | GND    | Ground                             |

| 30    | NC     | No Connect                         |

## 3.2. PIN assignment

Table 3 PIN assignment

| DIM name  | Function0 | Function1          | Function2 | Function3        |

|-----------|-----------|--------------------|-----------|------------------|

| PIN name  | mode      | mode               | mode      | mode             |

| UART_TX   | UARTO_TX  | GPIO0              | TX_EN     | UARTO_TX(output) |

| UART_RX   | UARTO_RX  | GPIO1              | RX_EN     | UARTO_RX(input)  |

| UART_RTS  | UARTO_RTS | GPIO2              | PWM1      | N/A              |

| UART_CTS  | UARTO_CTS | GPIO3              | PWM2      | N/A              |

| BOOT      | BOOT Mode | N/A                | N/A       | N/A              |

| GPIO7     | GPIO7     | CLK_EXT_32K_IN(ext | PWM1      | N/A              |

| GPIO7     | GPIO7     | clock source)      | PVVIVII   | IN/ A            |

| GPIO4     | SWD_CLK   | GPIO4              | PWM3      | I2C_SCLK         |

| GPIO5     | SWD_DIO   | GPIO5              | PWM4      | I2C_SDA          |

| GPIO15    | GPIO      | UART1_TX           | SPIM_CLK  | SPIS_CLK         |

| CONN/DISC | GPIO16    | UART1_RX           | SPIM_CSN  | SPIS_CSN         |

| I2C_SCL   | GPIO17    | I2C_SCLK           | SPIM_MISO | SPIS_MISO        |

| I2C_SDA   | GPIO18    | I2C_SDA            | SPIM_MOSI | SPIS_MOSI        |

| GPIO19    | GPIO19    | (BB)PCM_CLK        | I2S_CLK   | UART1_TX         |

| GPIO20    | GPIO20    | (BB)PCM_SYNC       | I2S_FS    | UART1_RX         |

| GPIO21    | GPIO21    | (BB)PCM_IN         | I2S_IN    | TX_EN            |

| GPIO22    | GPIO22    | (BB)PCM_OUT        | I2S_OUT   | RX_EN            |

Note: need to customize the program to modify the pin assignment

# 4. Electrical Characteristic

## **4.1.** Recommended Operating Conditions

**Table 4 Recommended Operating Conditions**

| Rating           | Min | Typical | Max | Unit                 |

|------------------|-----|---------|-----|----------------------|

| Storage temp.    | -55 | -       | 125 | $^{\circ}\mathbb{C}$ |

| Operating temp.  | -40 | -       | 85  | $^{\circ}$ C         |

| VDD power supply | 1.9 | 3.3     | 3.6 | V                    |

# 4.2. Digital IO DC Characteristics

Table 5 Digital IO DC Characteristics (VDD=3.3V)

| Symbol | Parameter                 | Min  | Typical | Max  | Units |

|--------|---------------------------|------|---------|------|-------|

| VIL    | Low-level input voltage   | -    | 0       | 0.9  | ٧     |

| VIH    | High-level input voltage  | 2.0  | 3.3     | -    | V     |

| VOL    | Low-level output voltage  | 0    | -       | 0.33 | V     |

| VOH    | High-level output voltage | 2.97 | -       | 3.3  | V     |

| IOL    | Low-level output current  | -    | 8       | -    | mA    |

| IOH    | High-level output current | -    | 8       | -    | mA    |

| Rpull  | Pull up resistance        | 30K  | 50K     | 70K  | Ω     |

## 4.3. RF Characteristics

Table 6 RF Characteristics

| Parameter                 | Conditions | Min  | Typical | Max  | Units |

|---------------------------|------------|------|---------|------|-------|

| Frequency Range           | -          | 2400 | -       | 2484 | MHZ   |

| RX Sensitivity@1Mbps BLE  | PER=30.8%  | -70  | -94     | -    | dBm   |

| RX Sensitivity@1Mbps BT   | BER=0.1%   | -70  | -90     | -    | dBm   |

| RX Sensitivity@ EDR 2Mbps | BER=0.01%  | -70  | -92     |      | dBm   |

| RX Sensitivity@ EDR 3Mbps | BER=0.01%  | -70  | -85     | -    | dBm   |

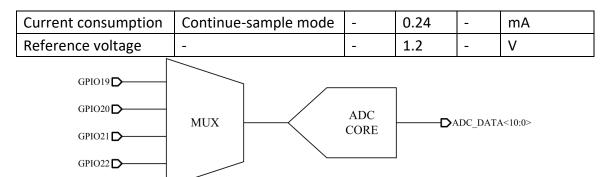

### 4.4. ADC Characteristics

Tc =  $27^{\circ}$ C, VDD=1.2V

Table 7 ADC characteristic

| Parameter           | Conditions           | Min   | Typical | Max | Units        |

|---------------------|----------------------|-------|---------|-----|--------------|

| Input voltage range | -                    | 0     | -       | 3.3 | V            |

| Resolution          | -                    | _     | 11      | -   | Bits         |

| Sample rate         | -                    | 93.75 | 375     | 750 | Kbps         |

| ENOB                | 375ksps              | -     | 10.57   | -   | Bits         |

| THD                 | 17KHz 1.1V Vpp input | _     | -71.19  | -   | dB           |

| SINAD               | tone                 | -     | 65.37   | -   | dB           |

| SFDR                |                      | _     | 73.14   | -   | dB           |

| Conversion time     | Time to output       |       | 64      |     | Clask system |

|                     | 24MHz clock          | -     | 64      | -   | Clock-cycles |

Figure 3 ADC Characteristics

## 4.5. Power Consumption

**Table 8 Power Consumption**

| Operation Mode | Min | Typical | Max | Unit |

|----------------|-----|---------|-----|------|

| Deep sleep     | -   | 4       | -   | uA   |

| sleep          | -   | 400     |     | uA   |

| idle           | -   | 5.5     |     | mA   |

| TX             |     | 21      |     | mA   |

| RX             |     | 16      |     | mA   |

# 5. Timing Diagram

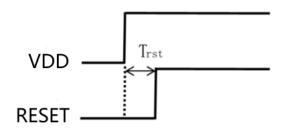

## 5.1. RESET Timing Diagram

Module reset timing diagram is shown in Figure below. Trst>50ms.

Figure 4 Reset Timing Diagram

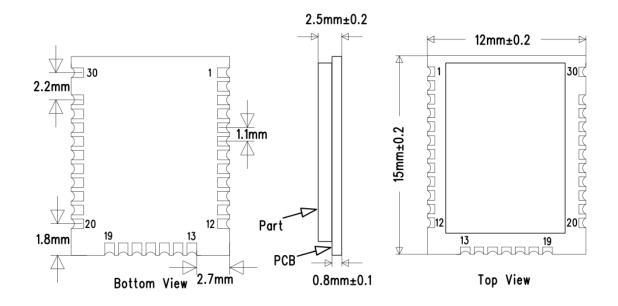

# 6. Package

The detailed size information of BR2551e as follows (With shield)

Figure 5 BR2551e Size Information

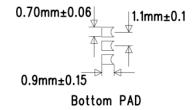

# 7. Recommended PCB Package Size

Figure 6 PCB Package Size

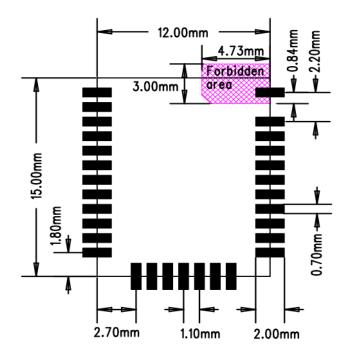

# 8. PCB Design Notes

### 8.1. Schematic Design Notes

Core components placement requirements: Bluetooth power decoupling capacitor should be placed close to the module, and the trace width should be over 20mil.

Figure 7 Bluetooth Power

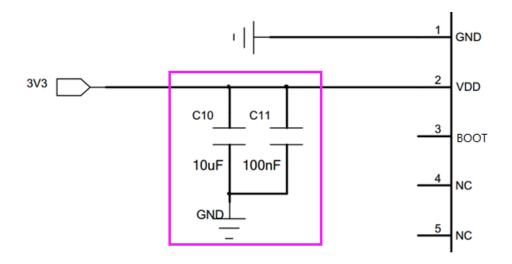

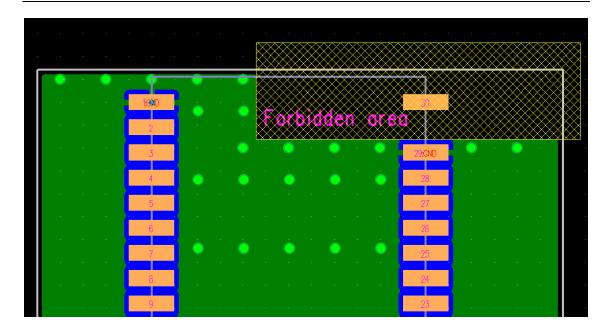

## 8.2. PCB Layout Design Notes

- The module should be placed as much as close to PCB's edge. The module internal antenna should be close to PCB's edge as much as possible. The module antenna area's all layers are copper prohibited.

- No power supply or other wiring should pass through antenna bottom.

- The antenna should be placed far away from interference (such as crystal) as much as possible.

Figure 8 RF Antenna Layout

# 9. Package Information

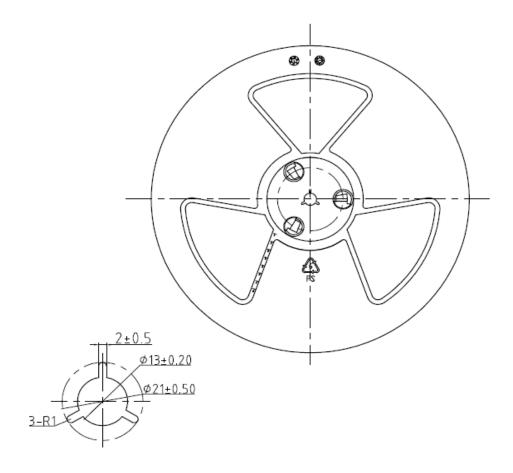

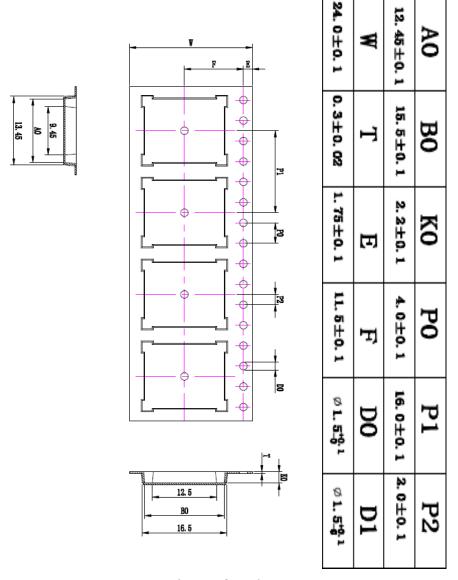

## 9.1. Package

Reel package: 1500pcs/reel Tray package: 100pcs/tray

MATERIAL ; PS COLOR : BLUE

| Width | 12mm | 16mm | 24mm | 32mm | 44mm | 56mm | 72mm | 88mm |

|-------|------|------|------|------|------|------|------|------|

| W1    | 13.5 | 17.5 | 25.5 | 33.5 | 45.5 | 57.5 | 74.0 | 90   |

| W2    | 17.5 | 21.5 | 29.5 | 37.5 | 49.5 | 61.5 | 78.0 | 94   |

Figure 9 Reels

Figure 10 Taping

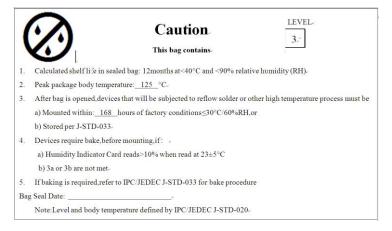

## 9.2. Storage Conditions

Figure 11 Storage Conditions

## 10. Company Profile

Barrot Technology – Barrot is a world leading one-stop chipset level solution provider who offers wireless connectivity and audio intelligent hardware solutions featuring with own IPs. The company is an associated member of The Bluetooth SIG, and it is the only one who contributes to Bluetooth specification definition in Greater China. Barrot owns three high-tech IPs: Bluetooth RF, Bluetooth stack and Acoustic algorithms, so Barrot offers most integrated, robust, reliable, and easy-to-use wireless turn-key solutions for IOT, Automotive and Wireless audio applications. Barrot devotes itself to being the most reliable short distance wireless technologies' solution provider in the world.

## 11. Contact Information

### 11.1. Beijing

Beijing Tel: +86 10 82702580

Fax: +86 10 82898219

Address: C710, Shangdi International Pioneering Park No.2, Shang Di Xin Xi Road, Haidi

an District, Beijing, 100089 P.R. China

Marketing Email: marketing@barrot.com.cn

**Support:** support@barrot.com.cn **Web site:** www.barrot.com.cn

### 11.2. Shenzhen

Shenzhen Tel: +86 755 27885822-603

Address: Room 601, No. 26, lane 2, seven stars 71 district, liuxian first road, baoan

district, Shenzhen

**Support:** support@barrot.com.cn **Web site:** www.barrot.com.cn

## 11.3. Shanghai

Address: 3rd Floor, No. 500, Bibo Road, Zhangjiang Gaoke, Pudong New Area,

Shanghai

**Support:** support@barrot.com.cn **Web site:** www.barrot.com.cn

# 12. Copyright

### Copyright ©1999-2020 Barrot Technology Limited

The Bluetooth trademark is owned by The Bluetooth SIG, and the usage of this trademark is licensed to Barrot Technology Limited.

Other trademarks included in this document are owned by their respective owners.

# **Appendix**

### 1. Storage Requirements

1.1 Temperature:  $22^28^{\circ}$ ;

1.2 Humidity: <70% (RH);

Vacuum packed and sealed in good condition to ensure 12 months of welding.

### 2. Humidity Sensitive Characteristic

2.1 MSL: 3 level

2.2 Once opened, SMT within 168 hours in the condition of temperature:  $22^28$  °C and humidity<60% (RH). Once production line stops, modules should either be stored in the drying box or be vacuum packed. If it fails to meet above storage conditions, *Bluetooth* modules need drying. Drying parameters refer to Table 2-1.

2.3 Handling, storage, and processing should follow IPC/JEDECJ-STD-033

**Table 2-1:** Mounted or un-mounted SMD package drying reference condition (User drying: Shop life starts after drying, Time=0)

| Drying und                      | der 125℃                       | Drying under                    | 90℃,≤5%RH                   | Drying under 40°C,≤5%RH         |                             |  |

|---------------------------------|--------------------------------|---------------------------------|-----------------------------|---------------------------------|-----------------------------|--|

| Over floor<br>life >72<br>hours | Over floor<br>life≤72<br>hours | Over floor<br>life >72<br>hours | Over floor<br>life≤72 hours | Over floor<br>life >72<br>hours | Over floor<br>life≤72 hours |  |

| 9 hours                         | 7 hours                        | 33 hours                        | 23 hours                    | 13 days                         | 9 days                      |  |

### 3. PCB Design Instruction

### 3.1 PCB Pad Surface Treatment

ENIG (Chemistry Ni/Au). OSP are recommended for PCB surface treatment. ENIG (Chemistry Ni/Au) is preferred.

- 3.2 PCB Pad Design

- 3.2.1 In order to ensure high production efficiency and high reliability of solder joints, PCB pad design refers to recommended PCB pad size in the corresponding product specification.

- 3.2.2 Even only part of PINs are used, it is recommended to do full pad design,

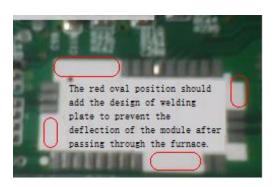

symmetric pad design, or asymmetric pad design(refer to Figure 3-1). During reflow, if the pad paste melts, the module is vulnerable to non-balanced force pull. It may lead to PIN short circuit if the module deflects under the action of torque.

Figure 3-1: Asymmetric Pad Design

### 3.3.3 Layout Requirements

- a. For PCB double sided layout, it is recommended to process on 2nd side.

- b. The layout of other elements should be avoided on the outermost end 1mm area of module pad. In order to increase repair space, other elements layouts should be as far away from the module as possible. The minimum distance between the module pad and PCB board edge is 1.5mm.

### 3.3.4 Compatible Design Considerations

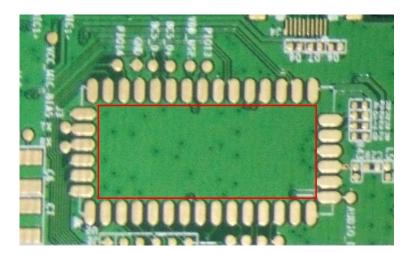

To prevent any hidden risks, module placement area (See the red rectangle in Figure 3-2 below) shouldn't include any pad design which intends to be compatible with other elements.

Figure 3-2: Module Placement Area Example

### 4. SMT Notes

4.1 All Bluetooth modules of our company are lead free. It is suggested to use lead

free process technique when SMT processing to prevent the reduction of the reliability of module welding technique which may be caused by the usage of lead production process technique.

Note: the lead BGA solder ball has low melting point  $(183^{\circ})$ , the lead-free BGA solder ball has high melting point  $(217^{\circ}\text{C}-221^{\circ}\text{C})$ . When the temperature rises to 183  $^{\circ}\text{C}$ , the solder paste is melting; When the temperature rises to 220  $^{\circ}\text{C}$ , lead free BGA solder ball starts to melt, and it is in the state of coexistence of solid and liquid. If lead technology is used and the furnace starts cooling, the original welding surface structure of BGA elements is damaged, and a new alloyed layer of the welding surface cannot be formed. This may lead to lead free BGA solder joint failure during reflow, which results in pseudo solder joints and other reliability issues in further.

### 4.2 SMT stencil Design

Ladder stencil is recommended. Stencil opening design requirements are as follows:

4.2.1 The PIN area of the module is recommended to be thickened. For modules with different PCB thickness, the thickened solder paste is shown in the following table. The thickening position should be kept at least 1mm apart from other parts.

| Number | Module PCB<br>thickness | Thickness of the steel mesh | Note                                                                                                               |  |

|--------|-------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------|--|

| 1      | 0.8mm                   | 0.15mm ladder               | If there is a precise IC pad                                                                                       |  |

| 2      | 1.0mm                   | 0.18mm ladder               | around the module, it is not recommended to exceed                                                                 |  |

| 3      | 1.2mm                   | 0.25mm ladder               | 0.15mm step thickness. The amount of solder paste can be increased by using the square of the epitaxial steel mesh |  |

| 4      | 1.6mm                   | 0.30mm ladder               |                                                                                                                    |  |

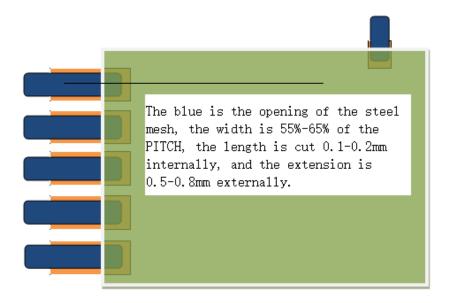

4.2.2 Opening width: 55%-65% of PCB PIN foot pad Pitch (centre-to-centre spacing)

(Since the actual width of the motherboard pad is not ensured, the opening width is determined by pitch.)

4.2.3 Opening length: based on PCB PIN foot, cutting 0.1-0.2mm towards inside, and extending 0.5-0.8mm towards outside. Outer extension pads maintain at least 0.25mm safety spacing with other elements. Cutting module pad opening if not enough space is left. Opening should be round corners.

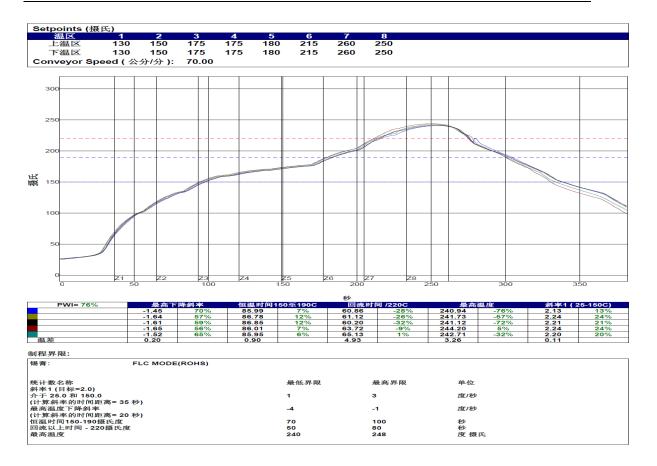

### 4.3 Reflow Profile

4.3.1When making the furnace temperature curve, it should add temperature measuring circuit under *Bluetooth* module's BGA to measure its real time temperature.

Recommended temperature parameters:

Increasing slope ( $^{\circ}$ C/SEC): 1~2

Descending slope ( $^{\circ}$ C/SEC): -4~-1

Reflow time (S): 40 $^{\sim}70$

Peak teamperature ( $^{\circ}$ C): 240-248

The actual furnace temperature curve for *Bluetooth* modules production:

### 4.4 Reflow Soldering

4.4.1 When PCBA which is mounted with *Bluetooth* module and it enters reflow, please strictly ensure PCBA boards to pass through furnace via track path. Passing through furnace via the net cover of reflow oven is prohibited.

Since *Bluetooth* contains BGA elements, the net cover vibration may lead to high rates of BGA solder welding defects.

- 4.4.2 During reflow, if it is not double-side board, it shouldn't place the side which is mounted *Bluetooth* as the first side to proceed. Mounting *Bluetooth* on the second sid is suggested. Note: During reflow, since BGA type components are downwards, BGA solder joints are stretched. This may lead to the vulnerability of solder joints. It may eventually result in the brokenness of solder joints and other hidden dangers under the influence of external forces.

- 4.4.3 Interference Design which may lead to offset of module's elements should be avoided during reflow soldering technique design (i.e. designing furnace jig).

- 4.4.4 No need to add red glue or other adhesive on the lower part of module. Module recommended pad design can ensure the good solder ability of module PIN foot. Even for any special reason, modules are designed on the first side and need to be reflowed.

- 4.5 Wave soldering of PCBA after module is mounted

- 4.5.1 If process requirements require PCBA which is mounted with modules do wave soldering, please ensure special protection to the module in order to prevent its elements from soldering shortcut or other unpredictable hidden risks which may be caused by splash or other abnormity during wave soldering.

- 4.5.2 Wave soldering on PCBA which is mounted with module is not recommended. Pls wave soldering PCBA at the first and then manually soldering module on it.

- 4.6 Manual welding of other elements after module is mounted on PCBA

- 4.6.1 If some elements needs to be manually soldered onto PCBA after PCBA is mounted with module, such as welding wires, please protect the module with the cover during manual welding process, especially when the manual welding area is close to the module.

- 4.6.2 PCBA should be placed in the upper part of the manual welding bench, or quickly flows to the next bench. It is not suggested to place it in the lower part of welding bench, such as under welding bench.

### 5. Repair Instructions

5.1 The process of rework depends on the condition of repair.

The recommended repair method in this document is not the only method. The selection of repair operations depends on the actual hardware, and it should follow the basic technique requirements during repair.

- 5.2 Repair Technique Instruction

- 5.2.1 No matter it is disassembly or welding, repairing requires for the condition of the temperature ascension requirement  $\leq$ 3 °C/sec, highest temperature  $\leq$ 260 °C

- 5.2.2 If repair elements exceed the storage period, it needs drying (refers to Table 2-1) before repairing

- 5.3 Module Disassembly

- 5.3.1 When disassembly, melting and reflowing soldering flux by proving fast, controllable and even heating. It ensures all solder joints melt at the same time. When disassembly, it should avoid any thermal or mechanical damage to modules, PCB, adjacent elements, and their solder joints.

- 5.3.2 It is recommended to adopt infrared heating or hot air heating method; It is recommended to design & use special jig for module disassembly or pickup

- 5.4 Module Welding/Replacement

- 5.4.1 Preparation Before Welding:

- 5.4.1.1 Using irons and woven materials which are able to moisten soldering flux to remove the old soldering flux on soldering pad.

- 5.4.1.2 Cleaning pad & remove flux residues

- 5.4.1.3 Soldering flux pre-fill: Before module is installed into the board, using the appropriate way to add soldering tin on solder pads, it ensures the closeness of the height of solder paste after it melts and re-solidifies.

- 5.4.1.4 It is suggested to make jig or small printed tin steel mesh to repair solder paste printing

- 5.4.2 Installing modules into solder pads and ensure the correction of its direction. In order to ensure the temperature of each assembly element stays same during reflow, it is suggested to preheat modules. After heating soldering flux, it reflows to ensure reliable connection. When the solder joint maintains the appropriate reflow time at a predetermined temperature, it forms better IMC.

- 5.4.3 When the module is installed into the pad after printing, it is suggested to use special jig to pick it up.

- 5.4.4 Special repair equipment is recommended to be either selected or designed for repairing.

#### **FCC Statement**

Any Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) This device may not cause harmful interference

- (2) This device must accept any interference received, including interference that may cause undesired operation.

#### FCC Radiation Exposure Statement:

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment .This equipment should be installed and operated with minimum distance 20cm between the radiator& your body.This transmitter must not be located or operating in conjunction with any other antenna or transmitter.

### **OEM Guidance**

1. Applicable FCC rules

This module has been tested and found to comply with part 15.247 requirements for Modular Approval.

2. The specific operational use conditions

This module can be used in IoT devices. The input voltage to the module is nominally 3.3V DC. The operational ambient temperature of the module is -40 to 85 degree C. Only the embedded Ceramic chip antenna is allowed. Any other external antenna is prohibited.

3. Limited module procedures

N/A

4. Trace antenna design

N/A

#### 5. Antenna

Antenna type :Ceramic chip Antenna ; Antenna Max. Peak Gain 1.36 dBi

### 6. Label and compliance information

When the module is installed in the host device, the FCC ID label must be visible through a window on the final device or it must be visible when an access panel, door or cover is easily re-moved. If not, a second label must be placed on the outside of the final device that contains the following text: "Contains FCC ID: 2BB6HBR2551E

The FCC ID can be used only when all FCC ID compliance requirements are met.

### 7. Information on test modes and additional testing requirements

a)The modular transmitter has been fully tested by the module grantee on the required number of channels,modulation types, and modes, it should not be necessary for the host installer to re-test all the available transmitter modes or settings. It is recommended that the host product manufacturer, installing the modular transmitter,perform some investigative measurements to confirm that the resulting composite system does not exceed the spurious emissions limits or band edge limits (e.g., where a different antenna may be causing additional emissions).

b)The testing should check for emissions that may occur due to the intermixing of emissions with the other transmitters, digital circuitry, or due to physical properties of the host product (enclosure). This investigation is especially important when integrating multiple modular transmitters where the certification is based on testing each of them in a stand-alone configuration. It is important to note that host product manufacturers should not assume that because the modular transmitter is certified that they do not have any responsibility for final product compliance.

c)If the investigation indicates a compliance concern the host product manufacturer is obligated to mitigate the issue. Host products using a modular transmitter are subject to all the applicable individual technical rules as well as to the general conditions of operation in Sections 15.5, 15.15, and 15.29 to not cause interference. The operator of the host product will be obligated to stop operating the device until the interference have been corrected.

### 8. Additional testing, Part 15 Subpart B disclaimer

The final host / module combination need to be evaluated against the FCC Part 15B criteria for unintentional radiators in order to be properly authorized for operation as a Part15 digital device. The host integrator installing this module into their product must ensure that the final composite product complies with the FCC requirements by a technical assessment or evaluation to the FCC rules,including the transmitter operation and should refer to guidance in KDB 996369. For host products with certified modular transmitter, the frequency range of investigation of the composite system is specified by rule in Sections 15.33(a)(1) through (a)(3), or the range applicable to the digital device, as shown in Section 15.33(b)(1), whichever is the higher frequency range of investigation. When testing the host product, all the transmitters must be operating. The transmitters can be enabled by using publiclyavailable drivers and turned on, so the transmitters are active. In certain conditions it might be appropriate to use a technology-specific call box (test set) where accessory devices or drivers are not available. When testing for emissions from the unintentional radiator, the transmitter shall be placed in the receive mode or idle mode, if possible. If receive mode only is not possible then, the radio shall be passive (preferred) and/or active scanning. In these cases, this would need to enable activity on the communication BUS (i.e., PCIe, SDIO, USB) to ensure the unintentional radiator circuitry is enabled.

Testing laboratories may need to add attenuation or filters depending on the signal strength of any active beacons (if applicable) from the enabled radio(s). See ANSI C63.4, ANSI C63.10 and ANSI C63.26 for further general testing details.