# SLM920 Hardware Design Guide

Release Date: 2023-07

Controlled version number: V 1.03

## IMPORTANT NOTICE

### COPYRIGHT NOTICE

**Copyright © MeiG Smart Technology Co., Ltd. All rights reserved.**

All contents of this manual are exclusively owned by MeiG Smart Technology Co., Ltd(MeiG Smart for short), which is under the protection of Chineselawsandcopyrightlaws in international conventions. Anyone shall not copy, spread, distribute, modify or use in other ways with its contents without the written authorization of MeiG Smart. Those who violated will be investigated by corresponding legal liability in accordance with the law.

### NO GUARANTEE

MeiG Smart makes no representation or warranty, either express or implied, for any content in this document, and will not be liable for any specific merchantability and applicable or any indirect, particular and collateral damage.

### CONFIDENTIALITY

All information contained here (including any attachments) is confidential. The recipient acknowledges the confidentiality of this document, and except for the specific purpose, this document shall not be disclosed to any third party.

### DISCLAIMER

MeiG Smart will not take any responsibility for any property and health damage caused by the abnormal operation of customers. Please develop the product according to the technical specification and designing reference guide which defined in the product manual. MeiG Smart have the right to modify the document according to technical requirement with no announcement to the customer.

## Safety Warnings

Pay attention to the following safety precautions when using or repairing any terminal or mobile phone that contains modules. The user should be informed of the following safety information on the terminal device. Otherwise Meig will not be liable for any consequences arising from the User's failure to follow these warnings.

| Logo | Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | When you are at a hospital or medical facility, observe the restrictions on using your phone. If necessary, please turn off the terminal or mobile phone, otherwise the medical device may malfunction due to radio frequency interference.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | Turn off the wireless terminal or mobile phone before boarding. To prevent interference with the communication system, wireless communication equipment is prohibited on the aircraft. Ignoring the above will violate local laws and may result in a flight accident.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | Do not use mobile terminals or mobile phones in front of flammable gases. Turn off the mobile terminal when you are near an explosion, chemical factory, fuel depot, or gas station. It is dangerous to operate a mobile terminal next to any potentially explosive electrical equipment.                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | The mobile terminal receives or transmits radio frequency energy when it is turned on. It can interfere with TV, radio, computer or other electrical equipment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | Road safety first! Do not use a handheld terminal or mobile phone while driving, please use a hands-free device. Stop before using your handheld terminal or mobile phone.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | GSM mobile terminals operate under RF signals and cellular networks, but are not guaranteed to be connected in all situations. For example, there is no credit or invalid SIM card. When in this situation and need emergency services, remember to use an emergency call. In order to be able to call and receive calls, the mobile terminal must be powered on and in a service area where the mobile signal is strong enough. Emergency calls are not allowed when certain network services or telephony features are in use, such as feature locks, keyboard locks. These functions should be removed before using an emergency call. Some networks require effective SIM card support. |

# SLM920 Hardware Design Guide\_V1.03

## Foreword

Thank you for using the SLM920 module from Meg Smart. This product can provide data communication services. Please read the user manual carefully before use, you will appreciate its perfect function and simple operation method.

The company does not assume responsibility for property damage or personal injury caused by improper operation of the user. Users are requested to develop the corresponding products according to the technical specifications and reference designs in the manual. Also pay attention to the general safety issues that mobile products should focus on.

Before the announcement, the company has the right to modify the contents of this manual according to the needs of technological development.

## Contents

|    |                                                 |    |

|----|-------------------------------------------------|----|

| 1. | Introduction .....                              | 9  |

| 2. | Module Overview .....                           | 10 |

|    | 2.1. Main features of the module .....          | 11 |

| 3. | Module package .....                            | 14 |

|    | 3.1. Pinout Diagram .....                       | 14 |

|    | 3.2. Module pin description .....               | 15 |

|    | 3.3. Mechanical Dimensions .....                | 21 |

| 4. | Interface application .....                     | 23 |

|    | 4.1. Power supply .....                         | 23 |

|    | 4.1.1. Power pin .....                          | 24 |

|    | 4.1.2. Power PCB layout .....                   | 25 |

|    | 4.2. Power on and off .....                     | 25 |

|    | 4.2.1. Module boot .....                        | 25 |

|    | 4.2.2. Module shutdown .....                    | 27 |

|    | 4.2.3. Module reset .....                       | 27 |

|    | 4.3. VCOIN power supply .....                   | 28 |

|    | 4.4. Power output .....                         | 29 |

|    | 4.5. Serial port .....                          | 30 |

|    | 4.6. MIPI Interface .....                       | 32 |

|    | 4.6.1. LCD Interface .....                      | 32 |

|    | 4.6.2. MIPI Camera Interface .....              | 35 |

|    | 4.6.3. MIPI PCB Layout .....                    | 38 |

|    | 4.7. Capacitive touch interface .....           | 38 |

|    | 4.8. Audio interface .....                      | 39 |

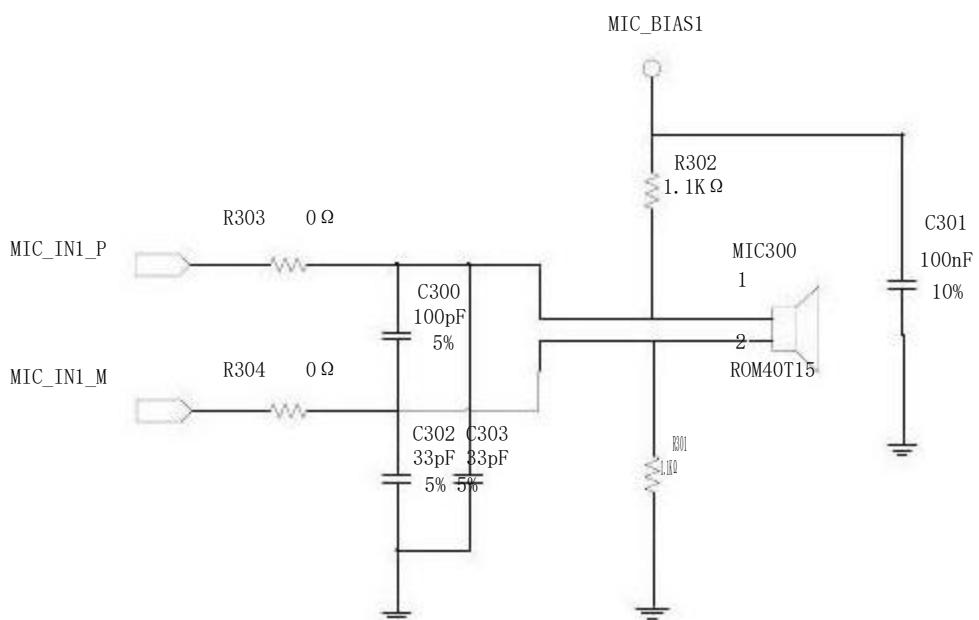

|    | 4.8.1. The handset interface circuit .....      | 40 |

|    | 4.8.2. Microphone receiver circuit .....        | 40 |

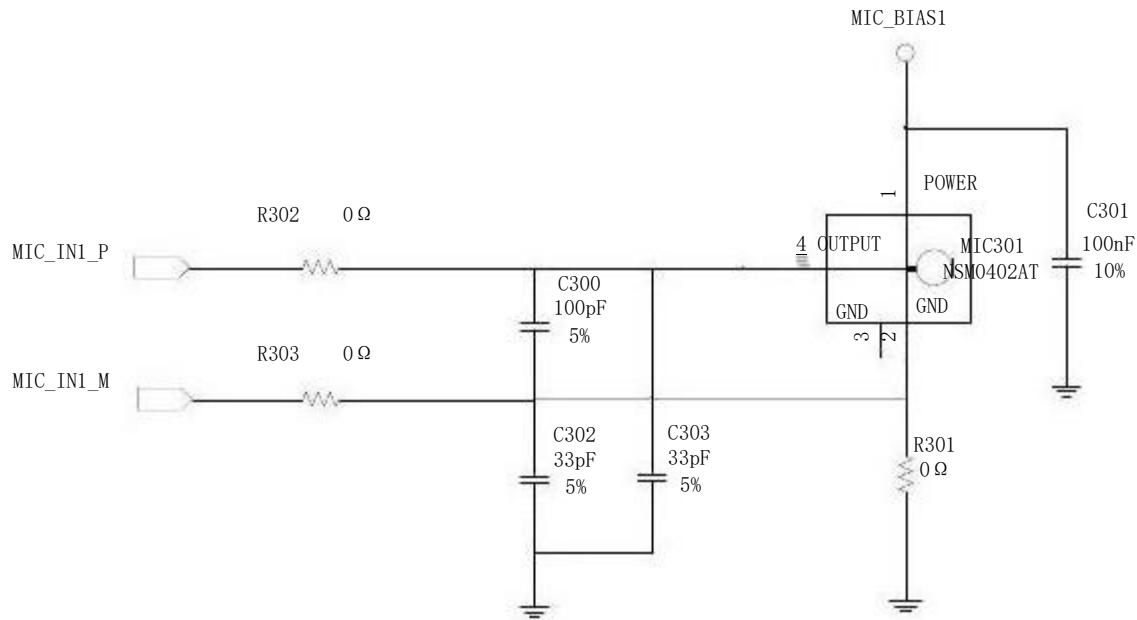

|    | 4.8.3. Headphone interface circuit .....        | 41 |

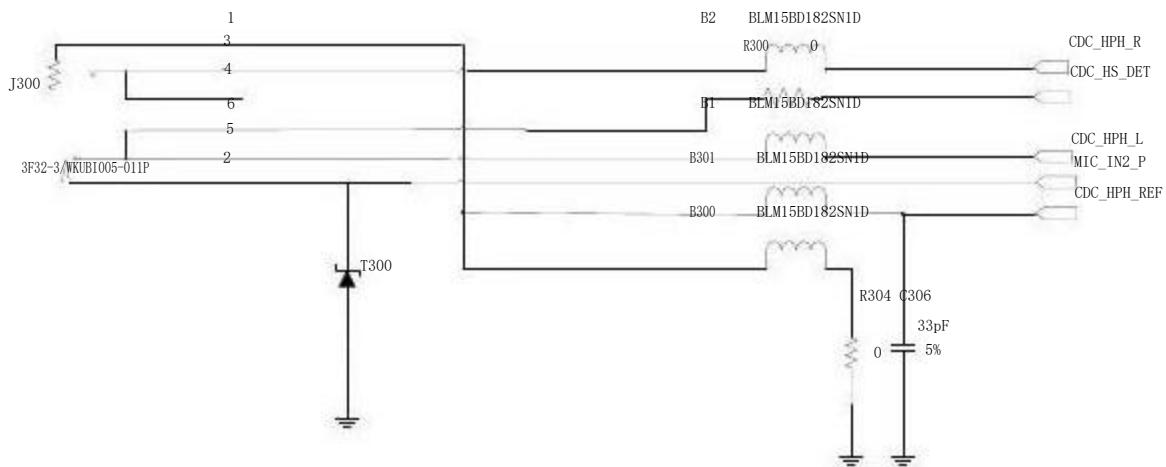

|    | 4.8.4. Speaker interface circuit .....          | 42 |

|    | 4.8.5. I2S interface .....                      | 42 |

|    | 4.8.6. Audio PCB Layout .....                   | 42 |

|    | 4.9. USB interface .....                        | 43 |

|    | 4.9.1. USB OTG .....                            | 44 |

|    | 4.9.2. USB PCB Layout .....                     | 45 |

|    | 4.10. Charging interface .....                  | 46 |

|    | 4.10.1. Charging detection .....                | 46 |

|    | 4.10.2. Charging control .....                  | 47 |

|    | 4.10.3. BAT_THERM .....                         | 47 |

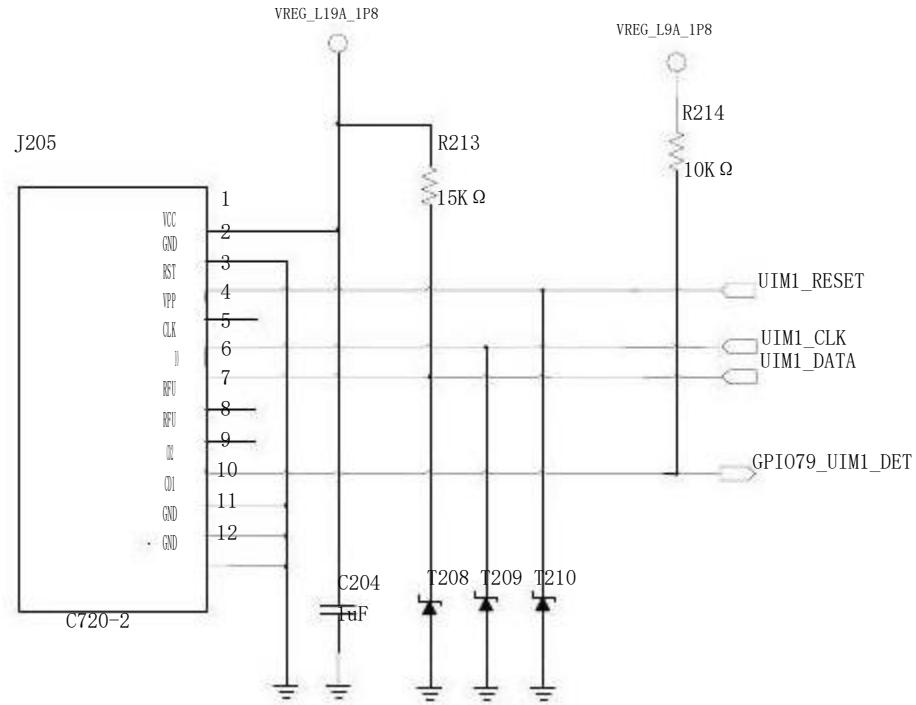

|    | 4.11. (U)SIM card interface .....               | 47 |

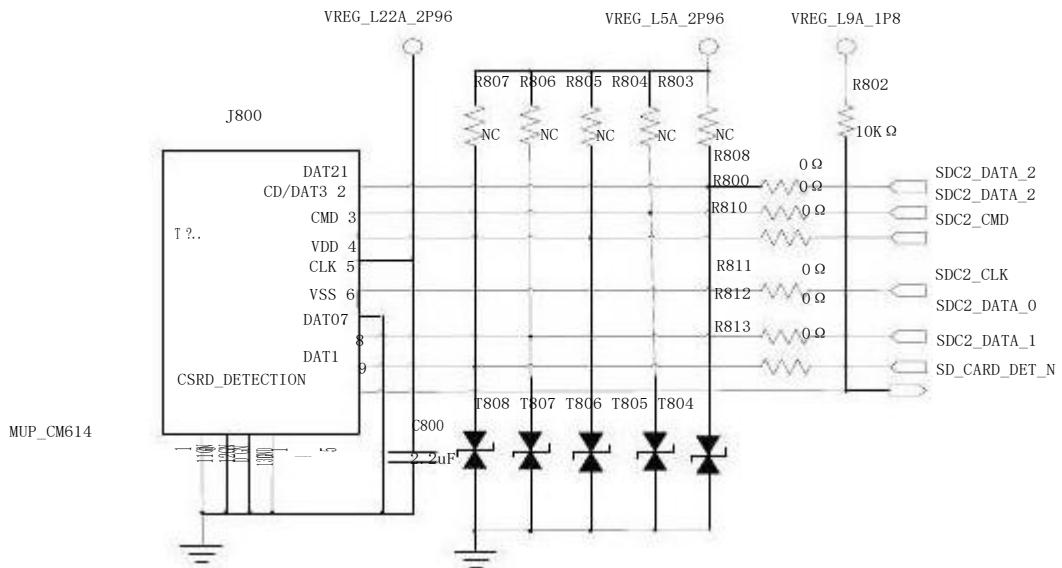

|    | 4.12. SD card interface .....                   | 48 |

|    | 4.13. I2C bus interface .....                   | 49 |

|    | 4.14. Analog-to-Digital Converter ( ADC ) ..... | 50 |

|    | 4.15. PWM .....                                 | 50 |

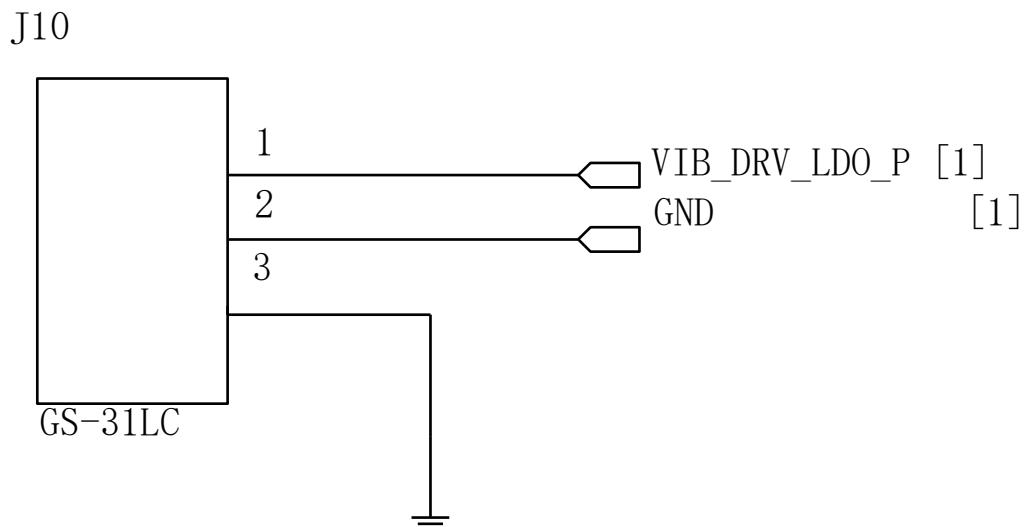

|    | 4.16. MOTOR .....                               | 50 |

|    | 4.17. Antenna interface .....                   | 51 |

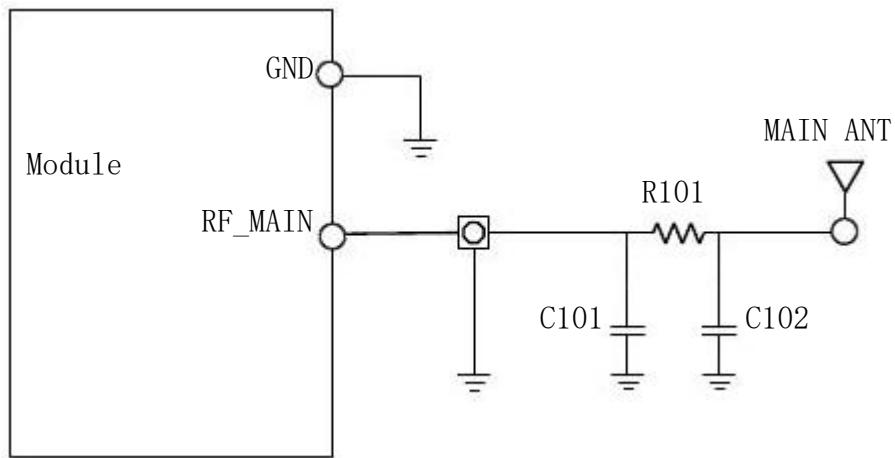

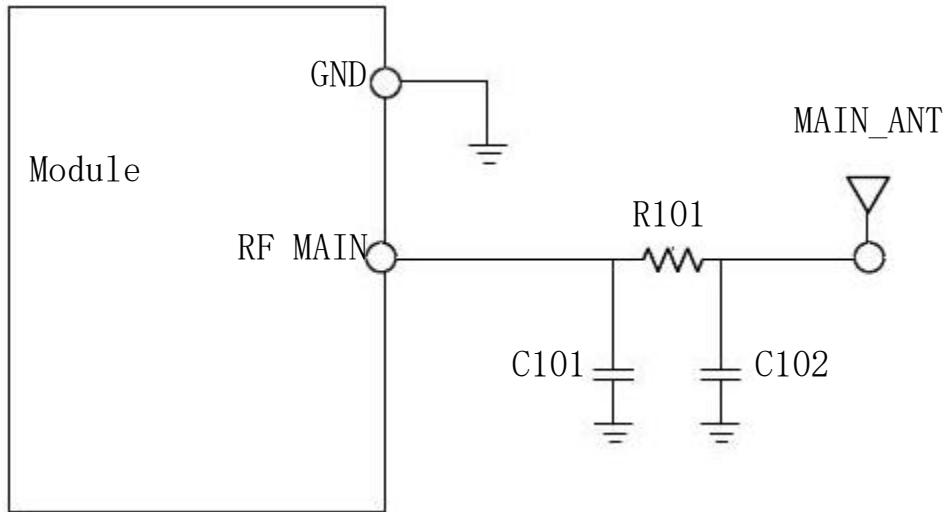

|    | 4.17.1. MAIN Antenna .....                      | 51 |

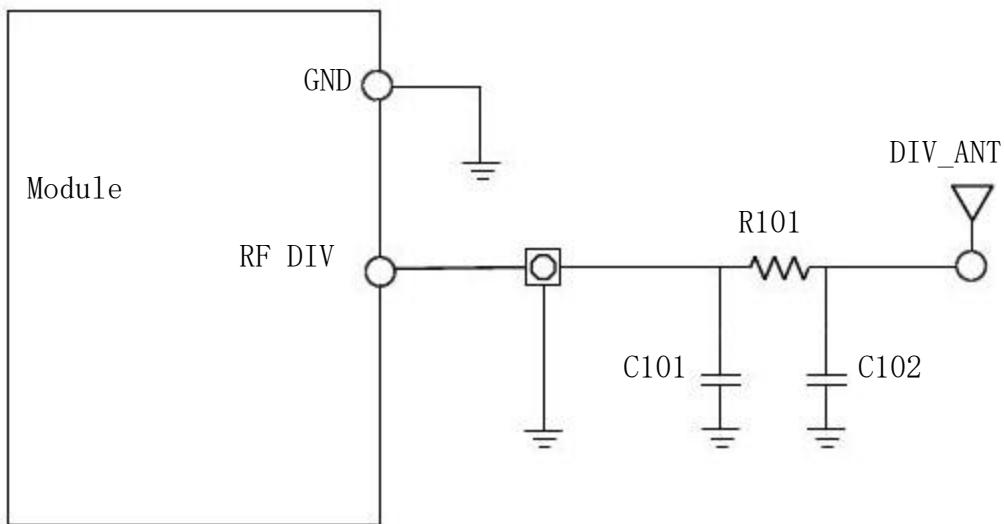

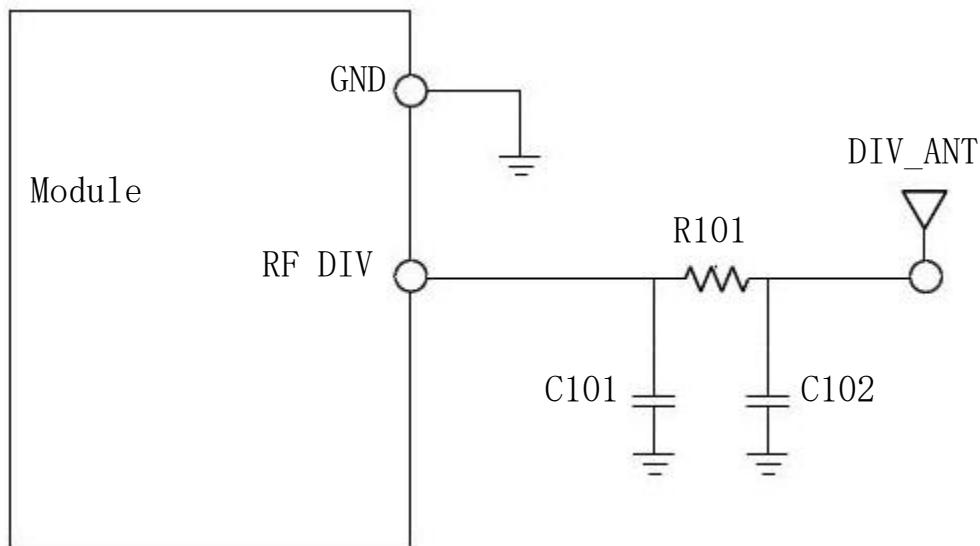

|    | 4.17.2. DRX Antenna .....                       | 52 |

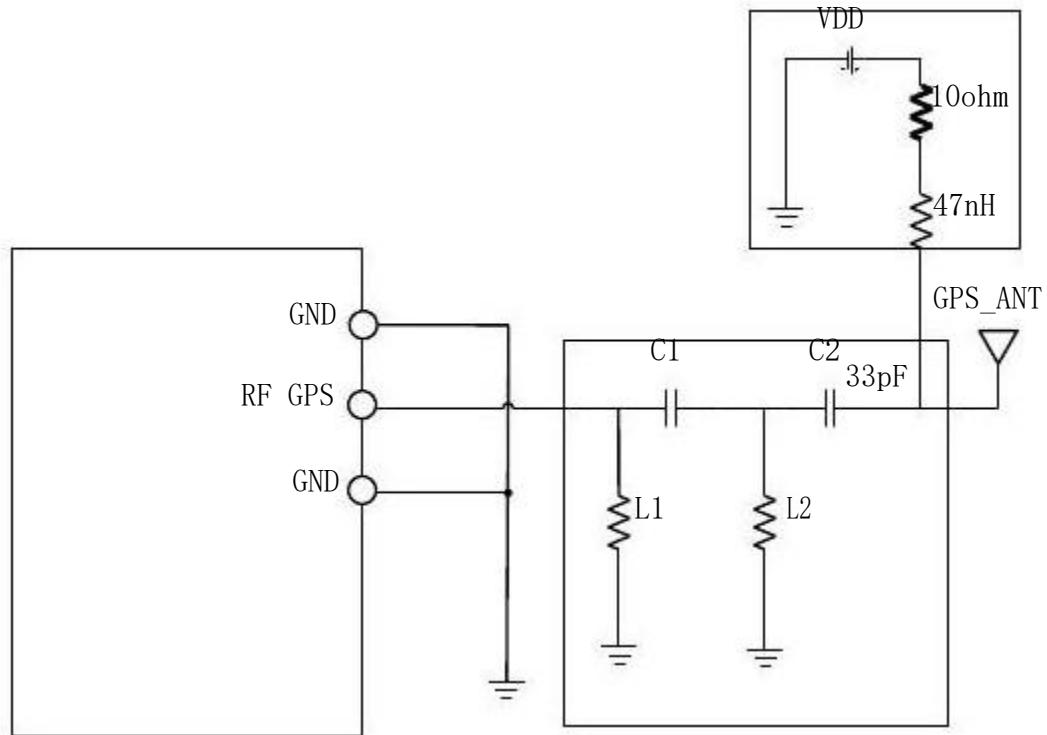

|    | 4.17.3. GPS Antenna .....                       | 53 |

|    | 4.17.4. WiFi/BT Antenna .....                   | 54 |

|    | 4.17.5. Antenna PCB Layout .....                | 55 |

| 5. | Electrical, reliability .....                   | 56 |

|    | 5.1. Absolute maximum value .....               | 56 |

|    | 5.2. Operating temperature .....                | 56 |

|    | 5.3. Working voltage .....                      | 56 |

|    | 5.4. Digital Interface Characteristics .....    | 57 |

|    | 5.5. SIM_VDD Characteristics .....              | 57 |

|    | 5.6. PWRKEY features .....                      | 57 |

|    | 5.7. VCOIN Characteristics .....                | 57 |

|    | 5.8. Static electricity protection .....        | 58 |

|    | 5.9. Main RF performance of GNSS .....          | 58 |

---

|      |                                                     |    |

|------|-----------------------------------------------------|----|

| 6.   | Production .....                                    | 60 |

| 6.1. | Top and bottom views of the module .....            | 60 |

| 6.2. | Recommended welding furnace temperature curve ..... | 60 |

| 6.3. | Moisture Sensitive Characteristics (MSL) .....      | 61 |

| 6.4. | Baking requirements .....                           | 62 |

| 7.   | Addendum .....                                      | 63 |

| 7.1. | Related Documentation .....                         | 65 |

| 7.2. | Terminology and interpretation .....                | 65 |

## Version History

| Date    | Version | Change description                                                                                                                                                            | Author              |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 2021-06 | 1.00    | First edition                                                                                                                                                                 | Hardware Department |

| 2021-08 | 1.01    | 1.Updated the description of the USB interface hardware switching circuit<br>2.Updated PIN pin description, the GPIO suffix that supports interrupt function is marked with * | Hardware Department |

| 2022-08 | 1.02    | Update formatting and illustrations                                                                                                                                           | Hardware Department |

| 2023-07 | 1.03    | Update the description of GPIO31 in Table 3.1                                                                                                                                 | Hardware Department |

# 1. Introduction

This document describes the hardware application interface of the module , including circuit connections and radio frequency interfaces in related applications . It can help users to quickly understand the detailed information of the module 's interface definition , electrical performance and structural dimensions . Combined with this document and other application documents , users can quickly use the module to design mobile communication applications .

## 2. Module overview

SLM920 series core board, the main chip used is Qualcomm Snapdragon 600 series, the CPU is made of 11nm FinFET, built-in 64bit ARM, 8-core Kryo 260 CPU , the highest frequency is 2GHz.

SLM920 module is a broadband intelligent wireless communication module suitable for TD-LTE/FDD-LTE/WCDMA multiple network standards.

The working frequency bands supported by the SLM 920 module are (take China as an example) :

- TDD-LTE:B41

- FD D-LTE: B2/B4/B5/B7/B12/B13/B14/B17/B25/B26/B66

- WCDMA: B2/B4/B5

- GSM:850/1900MHz

SLM920 can provide voice, SMS, address book, WiFi, BT and GPS functions ; it can be widely used in VR Camera, intelligent robot, video surveillance, security, vehicle equipment, smart platform handheld terminal , etc.

The physical interface of the module is a 272 - pin pad, which provides the following hardware interfaces :

- Four 1.8V UART serial ports .

- One LCD interface (MIPI) .

- Three Camera interface (MIPI) .

- One flash interface.

- One USB interface (supports USB2.0 and USB3.1) .

- Three analog MIC input interface .

- Two digital MIC interfaces

- Three analog audio output interface (handset, earphone, AUX)

- Two (U)SIM card interface.

- 17 GPIO ports.

- Eight I2C interfaces .

- Two SPI interfaces.

- One TF card interface .

- Support GNSS , WiFi , Bluetooth 5.0 function .

- One ERM motor interface

- One I2S interface

Note: The number of functional interfaces is subject to the default function of the PIN

## 2.1. Main features of the module

Table 2.1 : Module main features

| Product Features  | describe                                                                                                                                                                         |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Platform          | Qualcomm SM6125                                                                                                                                                                  |

| CPU               | Octa-core Kryo 260 CPU                                                                                                                                                           |

| GPU               | Adreno610@ 950MHz                                                                                                                                                                |

| System memory     | 32GB eMMC + 3GB LPDDR 4X (default)<br>64GB eMMC + 4GB LPDDR 4X (optional)<br>16GB eMMC + 2GB LPDDR 4X (optional)<br>128GB UFS2.1 + 6GB LPDDR 4X (optional)                       |

| Operating system  | Android 10                                                                                                                                                                       |

| Size              | 45.5x41.0x3.0mm, stamp hole package 160 pin+112pin LCC+LGA                                                                                                                       |

| Network frequency | TDD-LTE: B41<br>FDD-LTE: B2/B4/B5/B7/B12/B13/B14/B17/B25/B26/B66<br>WCDMA: B2/B4/B5<br>GSM:850/1900                                                                              |

| SLM920            |                                                                                                                                                                                  |

| Wi-Fi             | WCN3980: IEEE 802.11 a/ b/g/n /ac 2.4G &5G                                                                                                                                       |

| Bluetooth         | BT 3.0/4.2/5.0                                                                                                                                                                   |

| GNSS              | GPS/Beidou/Glonass/Galileo                                                                                                                                                       |

| Data access       | TD-LTE Cat4 TD-LTE 117/30Mbps                                                                                                                                                    |

|                   | FDD-LTE Cat4 FDD-LTE 150/50Mbps                                                                                                                                                  |

|                   | DC-HSPA+ 42/11.2Mbps                                                                                                                                                             |

|                   | TD-HSPA 2.8/2.3Mbps                                                                                                                                                              |

|                   | EDGE Class12, 236.8kbps/236.8kbps                                                                                                                                                |

|                   | GPRS Class12, 85.6kbps/85.6kbps                                                                                                                                                  |

| SIM               | DSD S Dual SIM Dual Standby ( 2.95V /1.8V )<br>Support SIM card hot swap<br>L/W/G /T +G<br>L/W/G /T + W<br>L/W/G /T + 1X<br>L /EVDO/CDMA1X+G<br>Does not support dual CDMA cards |

|                   | FHD+(2520X1080) 21:9@60fps                                                                                                                                                       |

|                   | LCD Size: User defined                                                                                                                                                           |

|                   | Interface: 1st LCM: MIPI DSI 4-lane ;                                                                                                                                            |

|                   | Interface: Can support three groups of CSI, each group is 4-Lane                                                                                                                 |

|                   |                                                                                                                                                                                  |

|                               |                                                         |                                                                                         |

|-------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------|

| (Dual cameras front and rear) | Dual 14 bit ISP 16+16MP, 25MP 30fps ZSL                 |                                                                                         |

| Video                         | Video decode                                            | 4K30 8 bit: H.264/VP8<br>4K30 10bit: HEVC, VP9<br>1080P60 MPEG-2                        |

|                               | Video encode                                            | 4K30 10 bit: HEVC and 4K30 H.264/VP8                                                    |

|                               | Decode+Encode 4K30 decode+1080p30 encode                |                                                                                         |

| Input device                  | Buttons (power button, reset, Home, volume +, volume -) |                                                                                         |

|                               | Capacitive TP                                           |                                                                                         |

| Reset                         | Support hardware reset                                  |                                                                                         |

| Application interface         | interface name                                          | Main function description                                                               |

|                               | VBAT                                                    | 2pin, module power input, 3.5V ~ 4.2V, nominal value 3.8V                               |

|                               | SDIO *1                                                 | SD3.0                                                                                   |

|                               | USB2.0(3.1)                                             | USB_BOOT (force USB boot, for emergency downloads)                                      |

|                               | BLSP ports                                              | 8 QUP ports                                                                             |

|                               | ADC*2                                                   | Support                                                                                 |

|                               | Charging function                                       | Support QC 3.0 _                                                                        |

|                               | Motor                                                   | Support                                                                                 |

|                               | GPIO                                                    | 17 GPIOs ( excluding GPIOs involved in LCM TP CAMERA and GPIOs with specific functions) |

|                               | RF interface                                            | Multimode LTE main antenna                                                              |

|                               |                                                         | Multimode LTE Diversity Antenna                                                         |

|                               |                                                         | GPS Antenna                                                                             |

|                               |                                                         | 2.4G WiFi /BT Antenna                                                                   |

|                               | Audio                                                   | 5G WIFI-Antenna                                                                         |

|                               |                                                         | 3 analog MIC input                                                                      |

|                               |                                                         | 3 analog audio output interface (handset, earphone, AUX)                                |

|                               |                                                         | 1 I2S interface                                                                         |

|                               |                                                         | 2 digital MIC interface                                                                 |

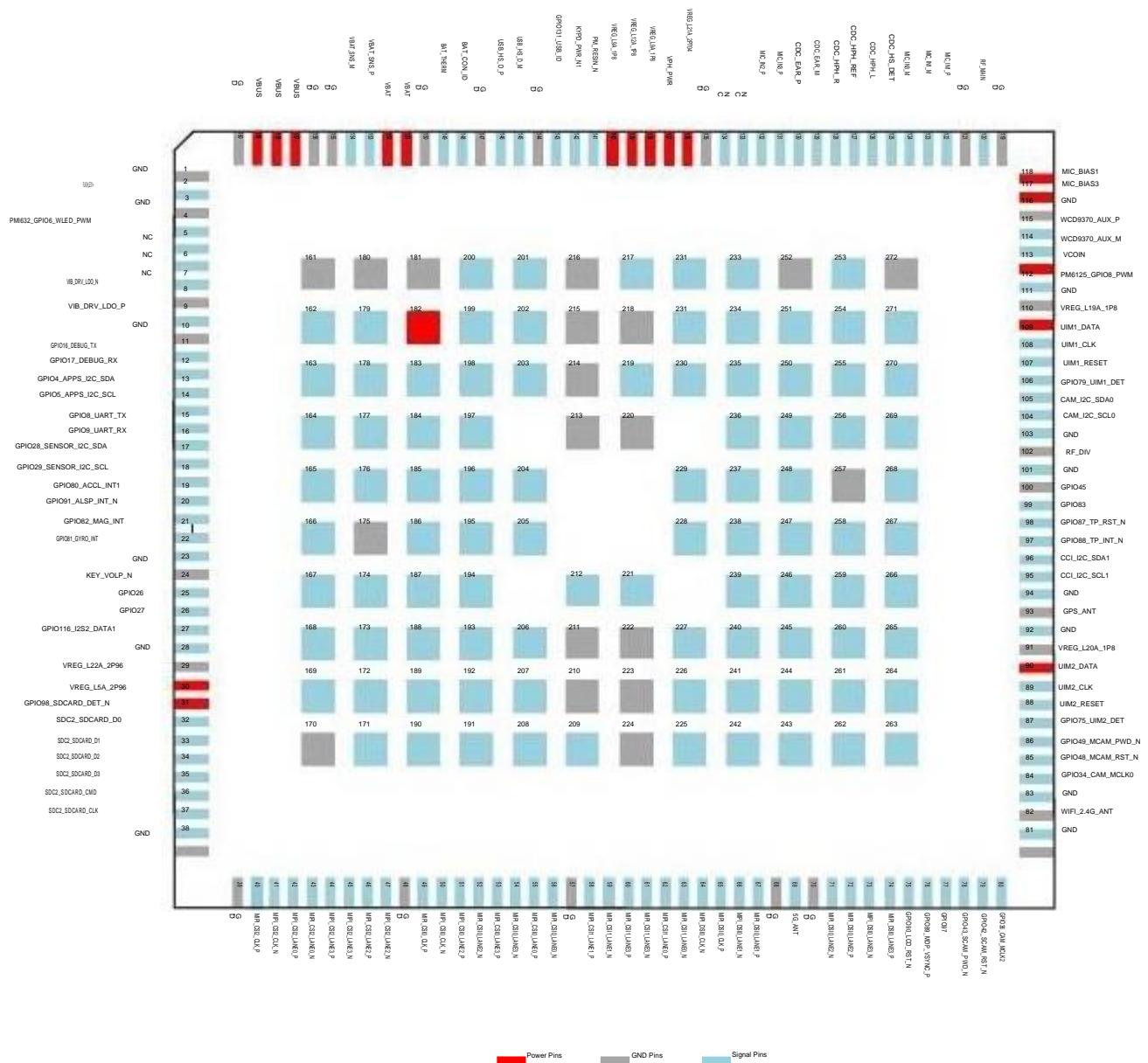

### 3. Module packaging

### 3.1. Pinout Diagram

Before PCB layout, we must first understand the pin distribution of the module, and rationally layout related devices and interfaces according to the distribution defined by the pins .

Figure 3.1 : Module Pin Diagram

( Top View )

### 3.2. Module pin description

Table 3.1 : Pin description (GPIO with \* supports interrupt function)

| PIN | pin name              | GPIO     | Attributes   | Function description                                         |

|-----|-----------------------|----------|--------------|--------------------------------------------------------------|

| 1   | GND                   |          | GND          | GND                                                          |

| 2   | FLASH_LED1+           |          | AO           | Flash output positive (1.5A)                                 |

| 3   | GND                   |          | GND          | GND                                                          |

| 4   | PMI632_GPIO6_WLED_PWM |          | AI           | ADC                                                          |

| 5   | NC                    |          |              | Reserved PIN                                                 |

| 6   | NC                    |          |              | Reserved PIN                                                 |

| 7   | NC                    |          |              | Reserved PIN                                                 |

| 8   | VIB_DRV_LDO_N_        |          | GND          | Motor drive negative, ground                                 |

| 9   | VIB_DRV_LDO_P         |          | AO           | Motor drive positive                                         |

| 10  | GND                   |          | GND          | GND                                                          |

| 11  | GPIO16_DEBUG_TX       | GPIO_16  | B-PD: nppukp | Module debug serial port                                     |

| 12  | GPIO17_DEBUG_RX       | GPIO_17* | B-PD: nppukp |                                                              |

| 13  | GPIO4_APPS_I2C_SDA    | GPIO_4*  | B-PD: nppukp | General-purpose GPIO, used as I2C by default                 |

| 14  | GPIO5_APPS_I2C_SCL    | GPIO_5   | B-PD: nppukp |                                                              |

| 15  | GPIO8_UART_TX         | GPIO_8   | B-PD: nppukp | General-purpose GPIO, used as UART by default                |

| 16  | GPIO9_UART_RX         | GPIO_9*  | B-PD: nppukp |                                                              |

| 17  | GPIO28_SENSOR_I2C_SDA | GPIO_28  | B-PD: nppukp | Dedicated for Sensor I2C                                     |

| 18  | GPIO29_SENSOR_I2C_SCL | GPIO_29* | B-PD: nppukp |                                                              |

| 19  | GPIO80_ACCL_INT1      | GPIO_80* | B-PD: nppukp | Used as accelerometer interrupt by default                   |

| 20  | GPIO91_ALSP_INT_N     | GPIO_91* | B-PD: nppukp | By default, it is used as a light distance sensor interrupt. |

| 21  | GPIO82_MAG_INT        | GPIO_82* | B-PD: nppukp | By default it is used as a geomagnetic interrupt             |

| 22  | GPIO81_GYRO_INT       | GPIO_81* | B-PD: nppukp | Used as a gyro interrupt by default                          |

| 23  | GND                   |          | GND          | GND                                                          |

| 24  | KEY_VOLP_N            |          | B-PD: nppukp | Volume up key                                                |

| 25  | GPIO26                | GPIO_26* | B-PD: nppukp | General purpose GPIO                                         |

| 26  | GPIO27                | GPIO_27* | B-PD: nppukp | General purpose GPIO                                         |

| 27  | GPIO116_I2S2_DATA1    | GPIO_116 | B-PD: nppukp | General-purpose GPIO, can be configured as I2S2_DATA1        |

| 28  | GND                   |          | GND          | GND                                                          |

| 29  | VREG_L22A_2P96        |          | PO           | T card power supply                                          |

| 30  | VREG_L5A_2P96         |          | PO           | T card signal pull-up power supply                           |

| 31  | GPIO98_SDCARD_DET_N   | GPIO_98* | B-PD: nppukp | T card hot plug detection signal                             |

| 32  | SDC2_SDCARD_D0        |          | BH-NP:pdpukp | T card data signal                                           |

| 33  | SDC2_SDCARD_D1        |          | BH-NP:pdpukp |                                                              |

| 34  | SDC2_SDCARD_D2        |          | BH-NP:pdpukp |                                                              |

| 35  | SDC2_SDCARD_D3        |          | BH-NP:pdpukp |                                                              |

| 36  | SDC2_SDCARD_CMD       |          | BH-NP:pdpukp | T card control signal                                        |

| 37  | SDC2_SDCARD_CLK       |          | BH-NP:pdpukp | T card clock signal                                          |

| 38  | GND                   |          | GND          | GND                                                          |

| 39  | GND                   |          | GND          | GND                                                          |

| 40  | MIPI_CSI2_CLK_P       |          | AI           | MIPI-CSI2 differential clock signal                          |

| 41  | MIPI_CSI2_CLK_N       |          | AI           |                                                              |

|    |                    |          |              |                                                                           |

|----|--------------------|----------|--------------|---------------------------------------------------------------------------|

| 42 | MIPI_CSI2_LANE0_P  |          | AI           | MIPI-CSI2 differential data signal                                        |

| 43 | MIPI_CSI2_LANE0_N  |          | AI           |                                                                           |

| 44 | MIPI_CSI2_LANE3_P  |          | AI           |                                                                           |

| 45 | MIPI_CSI2_LANE3_N  |          | AI           |                                                                           |

| 46 | MIPI_CSI2_LANE2_P  |          | AI           |                                                                           |

| 47 | MIPI_CSI2_LANE2_N  |          | AI           |                                                                           |

| 48 | GND                |          | GND          | GND                                                                       |

| 49 | MIPI_CSI0_CLK_P    |          | AI           | MIPI-CSI0 differential clock signal                                       |

| 50 | MIPI_CSI0_CLK_N    |          | AI           |                                                                           |

| 51 | MIPI_CSI0_LANE2_P  |          | AI           |                                                                           |

| 52 | MIPI_CSI0_LANE2_N  |          | AI           |                                                                           |

| 53 | MIPI_CSI0_LANE3_P  |          | AI           |                                                                           |

| 54 | MIPI_CSI0_LANE3_N  |          | AI           |                                                                           |

| 55 | MIPI_CSI0_LANE0_P  |          | AI           | MIPI-CSI0 differential data signal                                        |

| 56 | MIPI_CSI0_LANE0_N  |          | AI           |                                                                           |

| 57 | GND                |          | GND          |                                                                           |

| 58 | MIPI_CSI1_LANE1_P  |          | AI           |                                                                           |

| 59 | MIPI_CSI1_LANE1_N  |          | AI           |                                                                           |

| 60 | MIPI_CSI1_LANE3_P  |          | AI           |                                                                           |

| 61 | MIPI_CSI1_LANE3_N  |          | AI           | MIPI-CSI1 differential data signal                                        |

| 62 | MIPI_CSI1_LANE0_P  |          | AI           |                                                                           |

| 63 | MIPI_CSI1_LANE0_N  |          | AI           |                                                                           |

| 64 | MIPI_DSI0_CLK_N    |          | AO           |                                                                           |

| 65 | MIPI_DSI0_CLK_P    |          | AO           |                                                                           |

| 66 | MIPI_DSI0_LANE1_N  |          | AO           |                                                                           |

| 67 | MIPI_DSI0_LANE1_P  |          | AO           | MIPI-DSI0 differential data signal                                        |

| 68 | GND                |          | GND          |                                                                           |

| 69 | 5G_ANT             |          | AI           |                                                                           |

| 70 | GND                |          | GND          |                                                                           |

| 71 | MIPI_DSI0_LANE2_N  |          | AO           |                                                                           |

| 72 | MIPI_DSI0_LANE2_P  |          | AO           |                                                                           |

| 73 | MIPI_DSI0_LANE3_N  |          | AO           | MIPI-DSI0 differential data signal                                        |

| 74 | MIPI_DSI0_LANE3_P  |          | AO           |                                                                           |

| 75 | GPIO90_LCD_RST_N   | GPIO_90  | B-PD: nppukp | General-purpose GPIO, used as LCD reset signal by default                 |

| 76 | GPIO89_MDP_VSYNC_P | GPIO_89* | B-PD: nppukp | General-purpose GPIO, used as LCD frame synchronization signal by default |

| 77 | GPIO97             | GPIO_97* | B-PD: nppukp | General purpose GPIO                                                      |

| 78 | GPIO43_SCAM_PWD_N  | GPIO_43* | B-PD: nppukp | General-purpose GPIO, used as proactive sleep signal by default           |

| 79 | GPIO42_SCAM_RST_N  | GPIO_42* | B-PD: nppukp | General-purpose GPIO, used as a proactive reset signal by default         |

| 80 | GPIO36_CAM_MCLK2   | GPIO_36* | B-PD: nppukp | By default, it is used as the active master clock signal                  |

| 81 | GND                |          | GND          | GND                                                                       |

| 82 | WIFI_2.4G_ANT      |          | AI           | 2.4G WIFI interface                                                       |

| 83 | GND                |          | GND          | GND                                                                       |

| 84 | GPIO34_CAM_MCLK0   | GPIO_34  | B-PD: nppukp | By default, it is used as the master clock signal for the rear camera.    |

| 85 | GPIO48_MCAM_RST_N  | GPIO_48  | B-PD: nppukp | General-purpose GPIO, used as the rear camera reset signal by default     |

|     |                   |          |              |                                                                  |

|-----|-------------------|----------|--------------|------------------------------------------------------------------|

| 86  | GPIO49_MCAM_PWD_N | GPIO_49  | B-PD: nppukp | General-purpose GPIO, used as post-photo sleep signal by default |

| 87  | GPIO75_UIM2_DET   | GPIO_75* | B-PD: nppukp | SIM card 1 hot plug detection signal                             |

| 88  | UIM2_RESET        | GPIO_74  | B-PD: nppukp | SIM card 1 reset signal                                          |

| 89  | UIM2_CLK          | GPIO_73  | B-PD: nppukp | SIM card 1 clock signal                                          |

| 90  | UIM2_DATA         | GPIO_72* | B-PD: nppukp | SIM card 1 data signal                                           |

| 91  | VREG_L20A_1P8     |          | PO           | SIM card 1 power supply                                          |

| 92  | GND               |          | GND          | GND                                                              |

| 93  | GPS_ANT           |          | AI           | GPS antenna interface                                            |

| 94  | GND               |          | GND          | GND                                                              |

| 95  | CCI_I2C_SCL1      | GPIO_40  | B-PD: nppukp | Dedicated to camera I2C                                          |

| 96  | CCI_I2C_SDA1      | GPIO_39  | B-PD: nppukp |                                                                  |

| 97  | GPIO88_TP_INT_N   | GPIO_88* | B-PD: nppukp | General-purpose GPIO, default for TP interrupt signal            |

| 98  | GPIO87_TP_RST_N   | GPIO_87  | B-PD: nppukp | General-purpose GPIO, used as TP reset signal by default         |

| 99  | GPIO83            | GPIO_83* | B-PD: nppukp | General purpose GPIO                                             |

| 100 | GPIO45            | GPIO_45* | B-PD: nppukp | General purpose GPIO                                             |

| 101 | GND               |          | GND          | GND                                                              |

| 102 | RF_DIV            |          | AI           | Diversity Antenna Interface                                      |

| 103 | GND               |          | GND          | GND                                                              |

| 104 | CCI_I2C_SCL0      | GPIO_38  | B-PD: nppukp | Dedicated to camera I2C                                          |

| 105 | CCI_I2C_SDA0      | GPIO_37  | B-PD: nppukp |                                                                  |

| 106 | GPIO79_UIM1_DET   | GPIO_79* | B-PD: nppukp | SIM card 0 hot plug detection signal                             |

| 107 | UIM1_RESET        | GPIO_78  | B-PD: nppukp | SIM card 0 reset signal                                          |

| 108 | UIM1_CLK          | GPIO_77  | B-PD: nppukp | SIM 0 clock signal                                               |

| 109 | UIM1_DATA         | GPIO_76  | B-PD: nppukp | SIM card 0 data signal                                           |

| 110 | VREG_L19A_1P8     |          | PO           | SIM card 0 power                                                 |

| 111 | GND               |          | GND          | GND                                                              |

| 112 | PM6125_GPIO8_PWM  |          | DO           | PWM output                                                       |

| 113 | VCOIN             |          | AI, AO       | RTC power supply                                                 |

| 114 | WCD9370_AUX_M     |          | AO           | Class AB output, can be used as external PA input                |

| 115 | WCD9370_AUX_P     |          | AO           |                                                                  |

| 116 | GND               |          | GND          | GND                                                              |

| 117 | MIC_BIAS3         |          | AO           | MIC bias voltage                                                 |

| 118 | MIC_BIAS1         |          | AO           |                                                                  |

| 119 | GND               |          | GND          | GND                                                              |

| 120 | RF_MAIN           |          | AI           | Main antenna interface                                           |

| 121 | GND               |          | GND          | GND                                                              |

| 122 | MIC_IN1_P         |          | AI           | MIC1 differential input                                          |

| 123 | MIC_IN1_M         |          | AI           |                                                                  |

| 124 | MIC_IN3_M         |          | AI           | MIC3 differential input negative                                 |

| 125 | CDC_HS_DET        |          | AI           | Headphone plug-in detection signal                               |

| 126 | CDC_HPH_L         |          | AO           | Headphone left channel                                           |

| 127 | CDC_HPH_REF       |          | AI           | Headphone Ground Reference                                       |

| 128 | CDC_HPH_R         |          | AO           | Headphone right channel                                          |

| 129 | CDC_EAR_M         |          | AO           | Earpiece differential output                                     |

| 130 | CDC_EAR_P         |          | AO           |                                                                  |

| 131 | MIC_IN3_P         |          | AI           | MIC3 differential input positive                                 |

|     |                   |           |              |                                                                          |

|-----|-------------------|-----------|--------------|--------------------------------------------------------------------------|

| 132 | MIC_IN2_P         |           | AI           | MIC2 single-ended input                                                  |

| 133 | NC                |           |              | Reserved PIN                                                             |

| 134 | NC                |           |              | Reserved PIN                                                             |

| 135 | GND               |           | GND          | GND                                                                      |

| 136 | VREG_L21A_2P704   |           | PO           | 2.8V power output, can be used for TP, LCD power supply                  |

| 137 | VPH_PWR           |           | PO           | System power output, typical 3.8V                                        |

| 138 | VREG_L9A_1P8      |           | PO           | 1.8V power output. Always supply when power on, used for signal pull-up  |

| 139 | VREG_L12A_1P8     |           | PO           | 1.8V power output, always supply when power on, used for IO power supply |

| 140 | VREG_L9A_1P8      |           | PO           | 1.8V power output. Always supply when power on, used for signal pull-up  |

| 141 | PM_RESIN_N        |           | DI           | Module reset signal                                                      |

| 142 | KYPD_PWR_N1       |           | DI           | Module on/off signal                                                     |

| 143 | GPIO131_USB_ID    | GPIO_131* | DI           | USB ID                                                                   |

| 144 | GND               |           | GND          | GND                                                                      |

| 145 | USB_HS_DM         |           | AI, AO       | USB2.0 signal                                                            |

| 146 | USB_HS_DP         |           | AI, AO       |                                                                          |

| 147 | GND               |           | GND          | GND                                                                      |

| 148 | BAT_CON_ID        |           | AI           | Battery ID detection signal                                              |

| 149 | BAT_THERM         |           | AI           | Battery temperature detection signal                                     |

| 150 | GND               |           | GND          | GND                                                                      |

| 151 | VBAT              |           | PI,PO        | Module power supply input, voltage range 3.5~4.2V, typical value 3.8V    |

| 152 | VBAT              |           | PI,PO        |                                                                          |

| 153 | VBAT_SNS_P        |           | AI           | Battery voltage detection differential signal                            |

| 154 | VBAT_SNS_M        |           | AI           |                                                                          |

| 155 | GND               |           | GND          | GND                                                                      |

| 156 | GND               |           | GND          | GND                                                                      |

| 157 | VBUS              |           | PI,PO        | USB_VBUS                                                                 |

| 158 | VBUS              |           | PI,PO        |                                                                          |

| 159 | VBUS              |           | PI,PO        |                                                                          |

| 160 | GND               |           | GND          | GND                                                                      |

| 161 | GND               |           | GND          | GND                                                                      |

| 162 | USB3_SS_RX1_P     |           | AI           | USB3.1 channel 1 data receive differential signal                        |

| 163 | USB3_SS_RX1_M     |           | AI           |                                                                          |

| 164 | GPIO14_I2C_SDA    | GPIO_14*  | B-PD: nppukp | Configurable GPIO, used as I2C by default                                |

| 165 | GPIO15_I2C_SCL    | GPIO_15*  | B-PD: nppukp |                                                                          |

| 166 | GPIO84            | GPIO_84   | B-PD: nppukp | General purpose GPIO                                                     |

| 167 | GPIO85            | GPIO_85*  | B-PD: nppukp | General purpose GPIO                                                     |

| 168 | GPIO93            | GPIO_93*  | B-PD: nppukp | General purpose GPIO                                                     |

| 169 | GPIO113_I2S2_SCK  | GPIO_113  | B-PD: nppukp | General-purpose GPIO, can be configured as I2S2_SCK                      |

| 170 | GND               |           | GND          | GND                                                                      |

| 171 | MIPI_CSI1_LANE2_P |           | AI           | MIPI-CSI1 differential data signal                                       |

| 172 | MIPI_CSI1_LANE2_N |           | AI           |                                                                          |

| 173 | USB3_SS_RX0_M     |           | AI           | USB3.1 channel 0 data receive differential signal                        |

| 174 | USB3_SS_RX0_P     |           | AI           |                                                                          |

| 175 | GND               |           | GND          | GND                                                                      |

| 176 | GPIO24_UART_TX    | GPIO_24   | B-PD: nppukp | General-purpose GPIO, used as UART by default                            |

|     |                     |           |              |                                                               |

|-----|---------------------|-----------|--------------|---------------------------------------------------------------|

| 177 | GPIO25_UART_RX      | GPIO_25*  | B-PD: nppukp |                                                               |

| 178 | USB3_SS_TX1_M       |           | AO           | USB3.1 channel 1 data transmission differential signal        |

| 179 | USB3_SS_TX1_P       |           | AO           |                                                               |

| 180 | GND                 |           | GND          | GND                                                           |

| 181 | GND                 |           | GND          | GND                                                           |

| 182 | VREG_L15A_3P128     |           | PO           | 3.128V power output for USB related chip power supply         |

| 183 | OPTION              |           | DI           | USB interface type switching signal                           |

| 184 | GPIO22_I3C_SDA      | GPIO_22*  | B-PD: nppukp | General-purpose GPIO, used as I2C by default                  |

| 185 | GPIO23_I3C_SCL      | GPIO_23   | B-PD: nppukp |                                                               |

| 186 | USB3_SS_TX0_P       |           | AO           | USB3.1 channel 0 data transmission differential signal        |

| 187 | USB3_SS_TX0_M       |           | AO           |                                                               |

| 188 | USB_PHY_PS          | GPIO_102* | DI           | USB interface type switching signal                           |

| 189 | MIPI_DSI0_LANE0_N   |           | AO           | MIPI-DSI0 differential data signal                            |

| 190 | MIPI_DSI0_LANE0_P   |           | AO           |                                                               |

| 191 | MIPI_CSI2_LANE1_P   |           | AI           | MIPI-CSI2 differential data signal                            |

| 192 | MIPI_CSI2_LANE1_N   |           | AI           |                                                               |

| 193 | MIPI_CSI0_LANE1_P   |           | AI           | MIPI-CSI0 differential data signal                            |

| 194 | MIPI_CSI0_LANE1_N   |           | AI           |                                                               |

| 195 | GPIO128_DMIC_DAT2   | GPIO_128* | B-PD: nppukp | General-purpose GPIO, configurable as a digital MIC interface |

| 196 | GPIO127_DMIC_CLK2   | GPIO_127  | B-PD: nppukp |                                                               |

| 197 | GPIO101_WSA_EN      | GPIO_101* | B-PD: nppukp | General purpose GPIO                                          |

| 198 | GPIO124_WSA_INT     | GPIO_124* | B-PD: nppukp | General purpose GPIO                                          |

| 199 | NC                  |           |              | Reserved PIN                                                  |

| 200 | NC                  |           |              | Reserved PIN                                                  |

| 201 | PMI632_USB_CC1      |           | I/O          | Type-C configuration channel 1                                |

| 202 | PMI632_USB_CC2      |           | I/O          | Type-C configuration channel 2                                |

| 203 | CBL_PWR_N1          |           | DI           | Module power-on automatic power-on signal                     |

| 204 | GPIO125_DMIC_CLK1   | GPIO_125  | B-PD: nppukp | General-purpose GPIO, configurable as a digital MIC interface |

| 205 | GPIO126_DMIC_DAT1   | GPIO_126* | B-PD: nppukp |                                                               |

| 206 | FORCE_USB_BOOT      | GPIO_99*  | DI           | Emergency download mode interface                             |

| 207 | MIPI_CSI1_CLK_N     |           | AI           | MIPI-CSI1 differential clock signal                           |

| 208 | MIPI_CSI1_CLK_P     |           | AI           |                                                               |

| 209 | PM6125_GPIO3_ADC    |           | AI           | ADC                                                           |

| 210 | GND                 |           | GND          | GND                                                           |

| 211 | GND                 |           | GND          | GND                                                           |

| 212 | GPIO86              | GPIO_86*  | B-PD: nppukp | General purpose GPIO                                          |

| 213 | GND                 |           | GND          | GND                                                           |

| 214 | GND                 |           | GND          | GND                                                           |

| 215 | GND                 |           | GND          | GND                                                           |

| 216 | GND                 |           | GND          | GND                                                           |

| 217 | NC                  |           |              | Reserved PIN                                                  |

| 218 | GND                 |           | GND          | GND                                                           |

| 219 | NC                  |           |              | Reserved PIN                                                  |

| 220 | GND                 |           | GND          | GND                                                           |

| 221 | GPIO94_PRESSURE_INT | GPIO_94*  | B-PD: nppukp | General purpose GPIO                                          |

| 222 | GND                 |           | GND          | GND                                                           |

| 223 | GND                 |           | GND          | GND                                                           |

|     |                     |           |              |                                                                                        |

|-----|---------------------|-----------|--------------|----------------------------------------------------------------------------------------|

| 224 | GND                 |           | GND          | GND                                                                                    |

| 225 | NC                  |           |              | Reserved PIN                                                                           |

| 226 | NC                  |           |              | Reserved PIN                                                                           |

| 227 | NC                  |           |              | Reserved PIN                                                                           |

| 228 | GPIO117_WCD_ELD0_EN | GPIO_117  | B-PD: nppukp | General purpose GPIO                                                                   |

| 229 | USB0_DP_AUX_C_M     |           | AO, AI       | DP auxiliary channel differential signal                                               |

| 230 | USB0_DP_AUX_C_P     |           | AO, AI       |                                                                                        |

| 231 | GPIO100             | GPIO_100* | B-PD: nppukp | General purpose GPIO                                                                   |

| 232 | GPIO119             | GPIO_119  | B-PD: nppukp | General purpose GPIO                                                                   |

| 233 | GPIO7_TS_I2C_SCL    | GPIO_7    | B-PD: nppukp | General-purpose GPIO, configured as TP I2C by default                                  |

| 234 | GPIO6_TS_I2C_SDA    | GPIO_6    | B-PD: nppukp |                                                                                        |

| 235 | PM6125_GPIO2        |           | B-PD: nppukp | General purpose GPIO                                                                   |

| 236 | NC                  |           |              | Reserved PIN                                                                           |

| 237 | NC                  |           |              | Reserved PIN                                                                           |

| 238 | NC                  |           |              | Reserved PIN                                                                           |

| 239 | NC                  |           |              | Reserved PIN                                                                           |

| 240 | NC                  |           |              | Reserved PIN                                                                           |

| 241 | MIPI_DSI1_CLK_P     |           | AO           | MIPI-DSI1 differential clock signal                                                    |

| 242 | MIPI_DSI1_CLK_N     |           | AO           |                                                                                        |

| 243 | NC                  |           |              | Reserved PIN                                                                           |

| 244 | NC                  |           |              | Reserved PIN                                                                           |

| 245 | NC                  |           |              | Reserved PIN                                                                           |

| 246 | NC                  |           |              | Reserved PIN                                                                           |

| 247 | PM6125_GPIO1        |           | B-PD: nppukp | General purpose GPIO                                                                   |

| 248 | GPIO123             | GPIO_123* | B-PD: nppukp | General purpose GPIO                                                                   |

| 249 | GPIO41              | GPIO_41   | B-PD: nppukp | General purpose GPIO                                                                   |

| 250 | CC_OUT              |           | DO           | USB interface type switching signal                                                    |

| 251 | GPIO130             | GPIO_130* | B-PD: nppukp | General purpose GPIO                                                                   |

| 252 | GND                 |           | GND          | GND                                                                                    |

| 253 | GPIO1_I2C_SCL       | GPIO_1*   | B-PD: nppukp | General purpose GPIO, configurable as I2C                                              |

| 254 | GPIO0_I2C_SDA       | GPIO_0    | B-PD: nppukp |                                                                                        |

| 255 | GPIO3_UART_RX       | GPIO_3*   | B-PD: nppukp | General purpose GPIO, configurable as UART                                             |

| 256 | GPIO2_UART_TX       | GPIO_2    | B-PD: nppukp |                                                                                        |

| 257 | GND                 |           | GND          | GND                                                                                    |

| 258 | GPIO20_SPI_CLK      | GPIO_20   | B-PD: nppukp | General purpose GPIO, configurable as SPI                                              |

| 259 | GPIO21_SPI_CS       | GPIO_21*  | B-PD: nppukp |                                                                                        |

| 260 | GPIO18_SPI_MISO     | GPIO_18   | B-PD: nppukp |                                                                                        |

| 261 | GPIO19_SPI_MOSI     | GPIO_19*  | B-PD: nppukp |                                                                                        |

| 262 | GPIO44_DCAM_PWD_N   | GPIO_44*  | B-PD: nppukp | General-purpose GPIO, used as the sleep signal of the depth-of-field camera by default |

| 263 | GPIO46_DCAM_RST_N   | GPIO_46   | B-PD: nppukp | General-purpose GPIO, used as depth camera reset signal by default                     |

| 264 | GPIO35_CAM_MCLK1    | GPIO_35   | B-PD: nppukp | General-purpose GPIO, used as the main clock signal of the depth camera by default     |

| 265 | GPIO115_I2S2_DATA0  | GPIO_115  | B-PD: nppukp | General-purpose GPIO, can be configured as I2S2_DATA0                                  |

| 266 | GPIO30_SPI_MISO     | GPIO_30   | B-PD: nppukp | General purpose GPIO, configurable as SPI                                              |

| 267 | GPIO31_SPI_MOSI     | GPIO_31   | B-PD: nppukp |                                                                                        |

| 268 | GPIO33_SPI_CS       | GPIO_33*  | B-PD: nppukp |                                                                                        |

|     |                 |          |              |                                               |

|-----|-----------------|----------|--------------|-----------------------------------------------|

| 269 | GPIO32_SPI_CLK  | GPIO_32  | B-PD: nppukp |                                               |

| 270 | GPIO92_FP_INT_N | GPIO_92* | B-PD: nppukp | General purpose GPIO                          |

| 271 | GPIO114_I2S2_WS | GPIO_114 | B-PD: nppukp | General-purpose GPIO, configurable as I2S2_WS |

| 272 | GND             |          | GND          | GND                                           |

Note:

\* : Interrupt pin that can wake up the system

B: Bidirectional digital with CMOS input

H: High-voltage tolerant

NP: pdpukp=defaultno-pull with programmable options following the colon (:)

PD: nppukp=defaultpulldown with programmable options following the colon (:)

PU: nppdkp=defaultpullup with programmable options following the colon (:)

KP: nppdpu=defaultkeeper with programmable options following the colon (:)

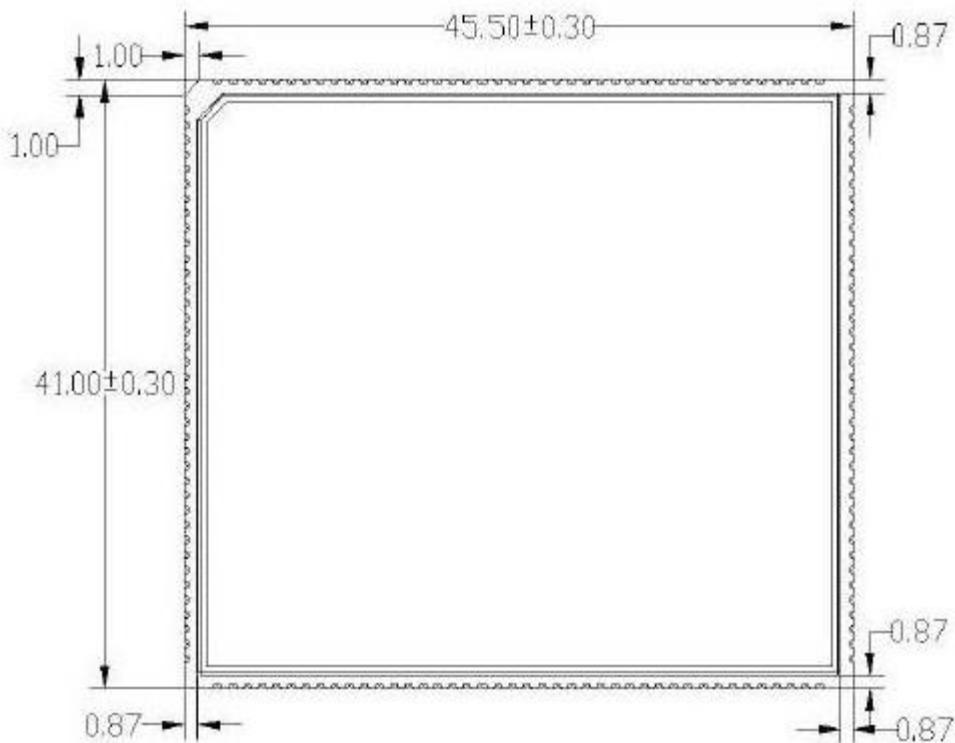

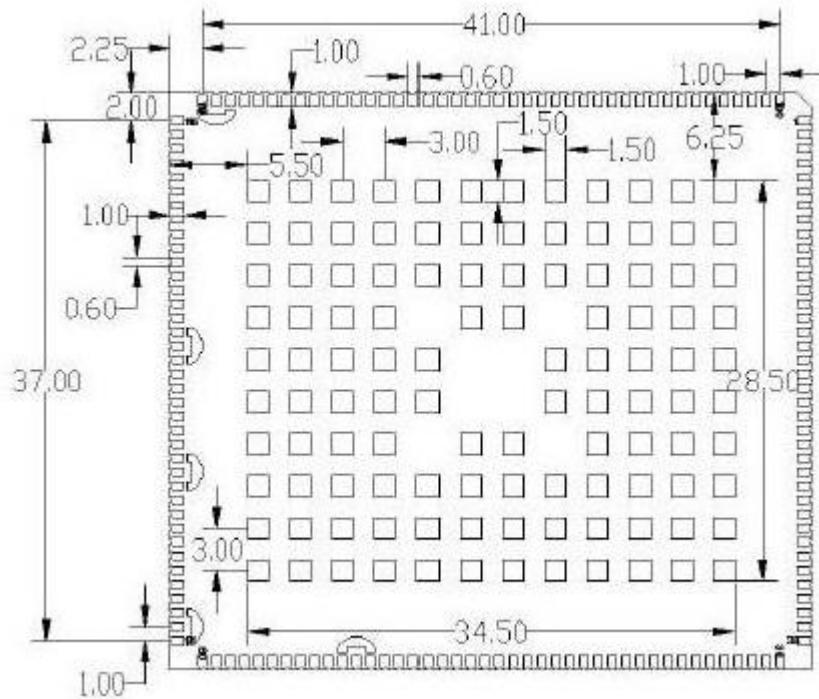

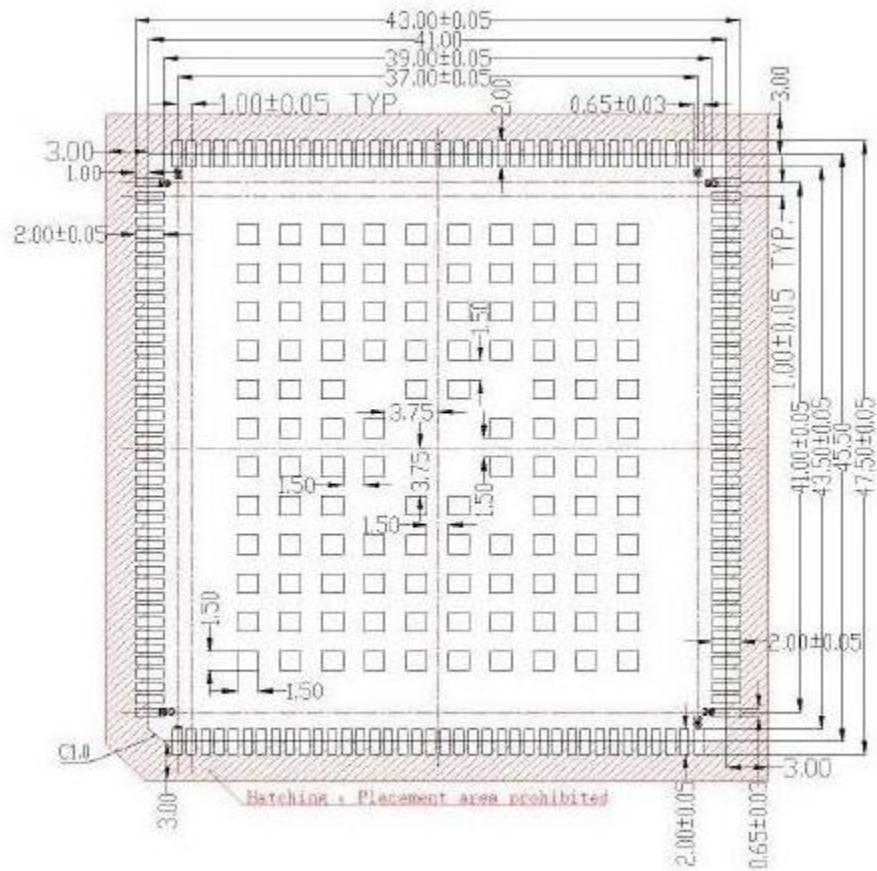

### 3.3. Mechanical Dimensions

Figure 3.2 : Module 3D Dimensions (Unit: mm)

Figure 3.3 Recommended package of modules

## 4. Interface application

### 4.1. Power supply

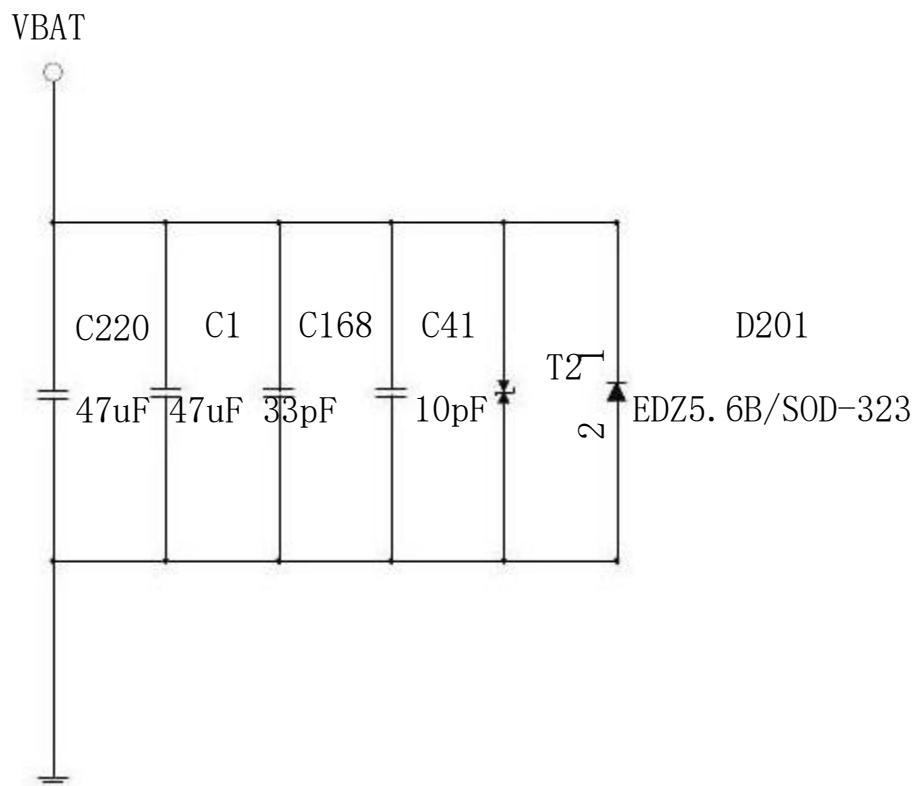

If it is a device with battery, the voltage input range of module VBAT is 3.5 V to 4.2 V, and the recommended voltage is 3.8 V. In the GSM frequency band, when the module transmits at the maximum power, the peak current can reach up to 3 A instantaneously, resulting in a large voltage drop on VBAT.

It is recommended to use a large capacitor for voltage regulation close to VBAT. It is recommended to use two 47uF ceramic capacitors. Parallel 33pF and 10pF capacitors can effectively remove high frequency interference. At the same time, in order to prevent ESD and surge damage to the chip, it is recommended to use a suitable TVS tube and a 5.1 V /500mW Zener diode on the VBAT pin of the module. During PCB layout, capacitors and diodes should be placed as close as possible to the VBAT pin of the module. Users can directly supply power to the module with a 3.8 V lithium-ion battery. When using a battery, the impedance between the VBAT pin and the battery should be less than 150mΩ.

Figure 4.1: VBAT input reference circuit

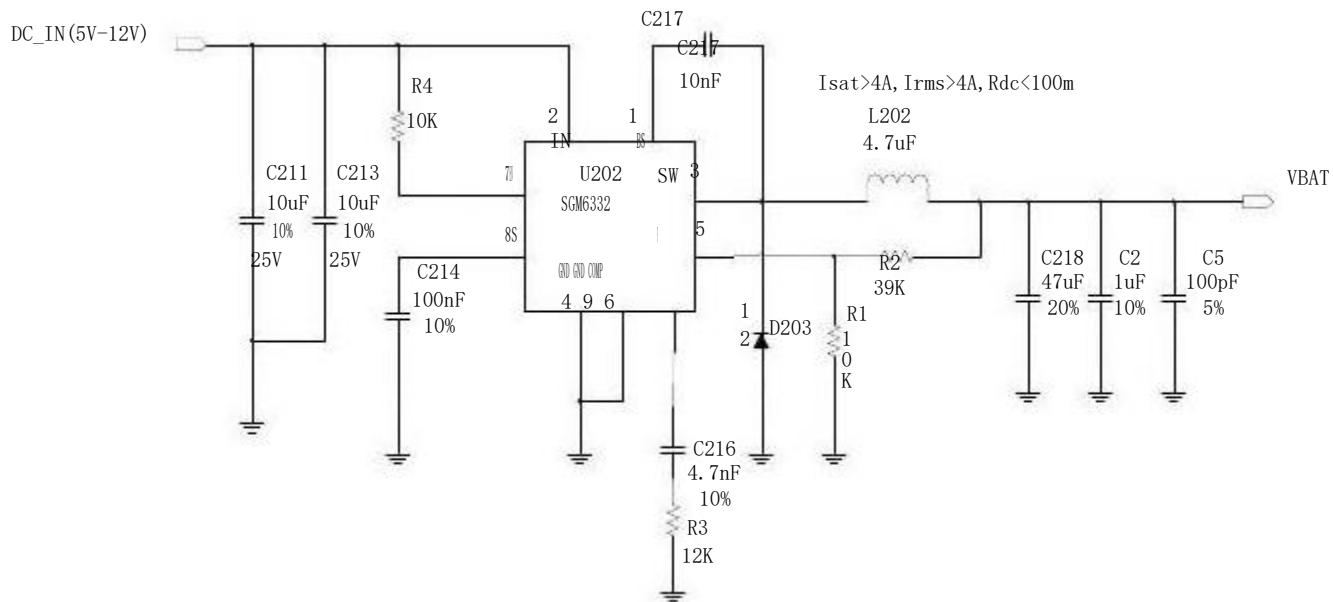

If it is a DC power supply device, the DC input voltage is 5V -12V , and the recommended circuit that can use DC-DC power supply at this time is shown in the figure below :

Figure 4.2 : DC-DC Power Supply Circuit

#### Notice:

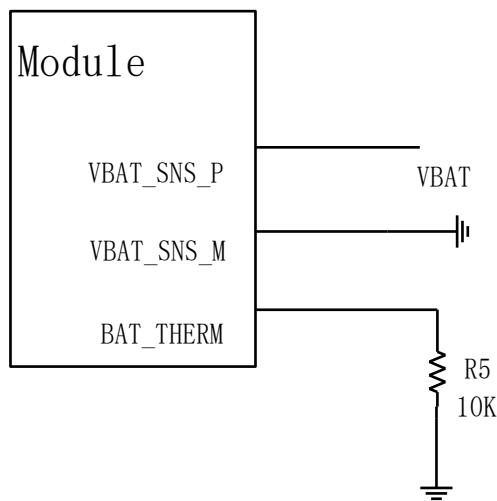

If the user does not use the battery for power supply, VBAT\_SNS\_P / M can not be left floating. It is necessary to connect VBAT\_SNS\_P to VBAT and VBAT\_SNS\_M to ground. Pin 149 (BAT\_THERM) of the module is connected to a 10K resistor and pulled down to GND to prevent the software from judging that the battery temperature is abnormal after the module is turned on, resulting in shutdown. The connection diagram is as follows :

Figure 4.3 : Connection diagram for non-battery power supply

### 4.1.1. Power supply pins

VBAT pins ( 151 , 152 ) are used for power input. In the user's design, please pay special attention to the design of the power supply part to ensure that even when the current consumption of the module reaches 3 A, the drop of VBAT will not be lower than 3.5 V . If the voltage drops below 3.5 V , the module may shut down . The

---

PCB trace from the VBAT pin to the power supply should be wide enough to reduce voltage droop during transmission burst mode.

VBAT

Figure 4.4 : Minimum voltage at which VBAT drops

### 4.1.2. Power PCB Layout

The power trace should not only consider VBAT, but also the return GND of the power supply. The trace of the positive pole of VBAT must be short and thick, and the trace must first pass through a large capacitor, a Zener diode, and then to the power PIN of the module. There are multiple PAD exposed coppers at the bottom of the module. It is necessary to ensure that the GND path from these exposed copper areas to the power supply is the shortest and most unobstructed. In this way, the current path of the entire power supply can be guaranteed to be the shortest and the interference can be minimized.

## 4.2. Power on and off

Do not turn on the module when the temperature and voltage limits of the module are exceeded. In extreme cases such operations can lead to permanent damage to the module.

### 4.2.1. Module power on

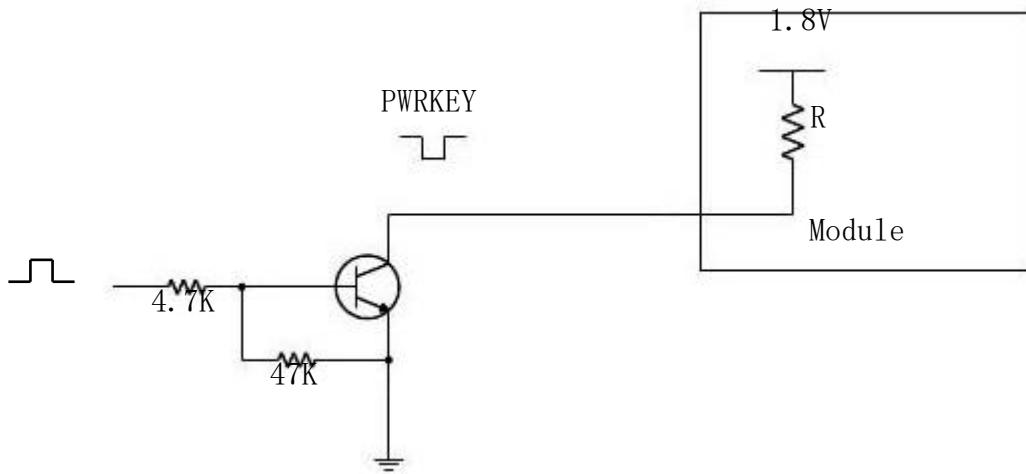

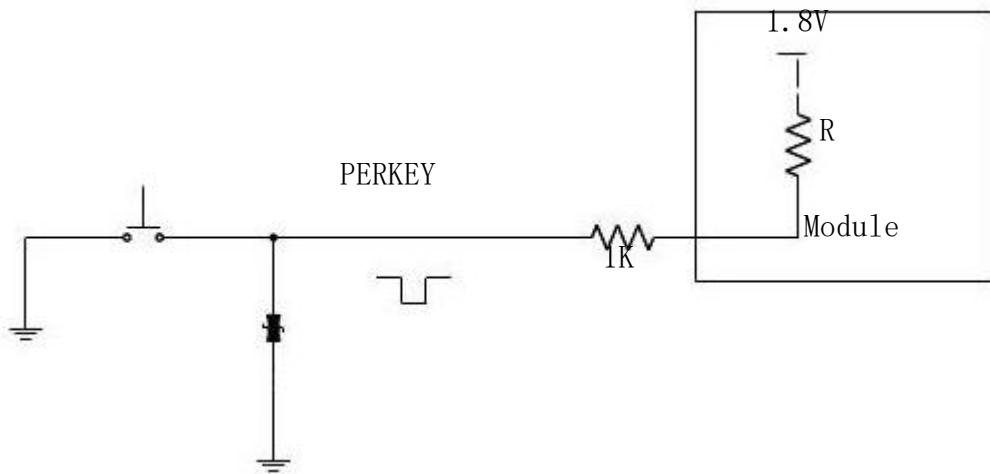

by pulling down the KYPD\_PWR\_N1 pin ( 142 ) for at least 2 seconds . This pin has been pulled up to 1.8V in the module. The recommended circuit is as follows ; or pull down the CBL\_PWR\_N pin (203), CBL\_PWR\_N can realize the function of automatic power-on after power-on by means of a 1K pull-down resistor to GND, and it is not necessary to release this signal after power-on.

Figure 4.5 : Use external signal to drive the module to power on

Figure 4.6 : Power on using the button circuit

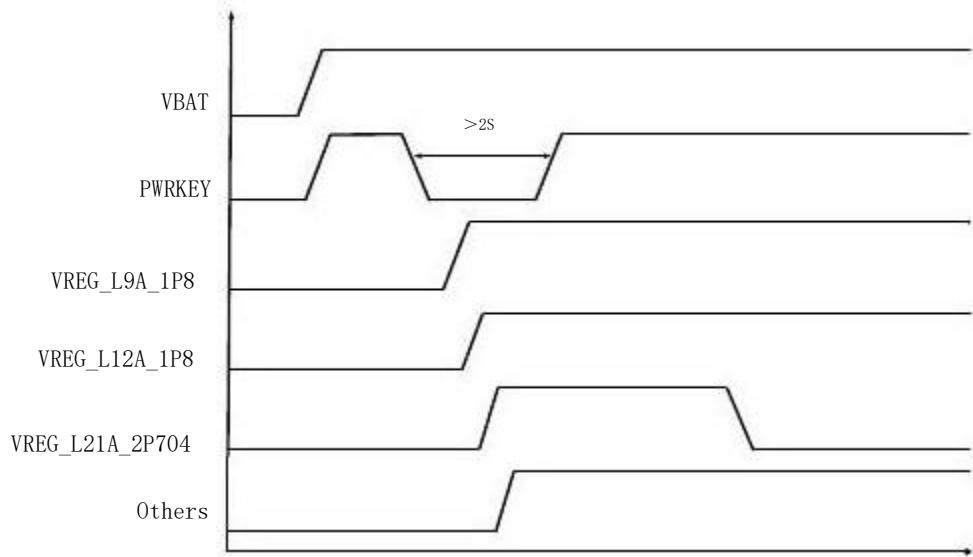

The following figure shows the boot sequence description:

Figure 4.7 : Use PWRKEY boot sequence diagram

## 4.2.2. Module shutdown

User can shutdown using PWRKEY pin

### 4.2.2.1. PWRKEY shutdown

The user can shut down by pulling the PWRKEY signal low for at least 3 seconds. The shutdown circuit can refer to the design of the startup circuit. After the module detects the shutdown action, a prompt window will pop up on the screen to confirm whether to perform the shutdown action.

restart by pulling down PWRKEY for at least 15 seconds.

## 4.2.3. Module reset

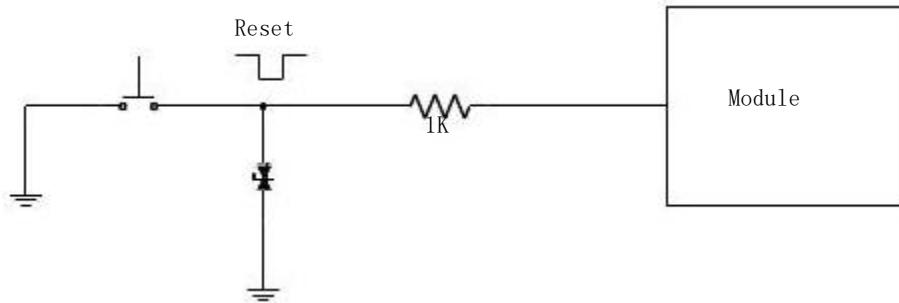

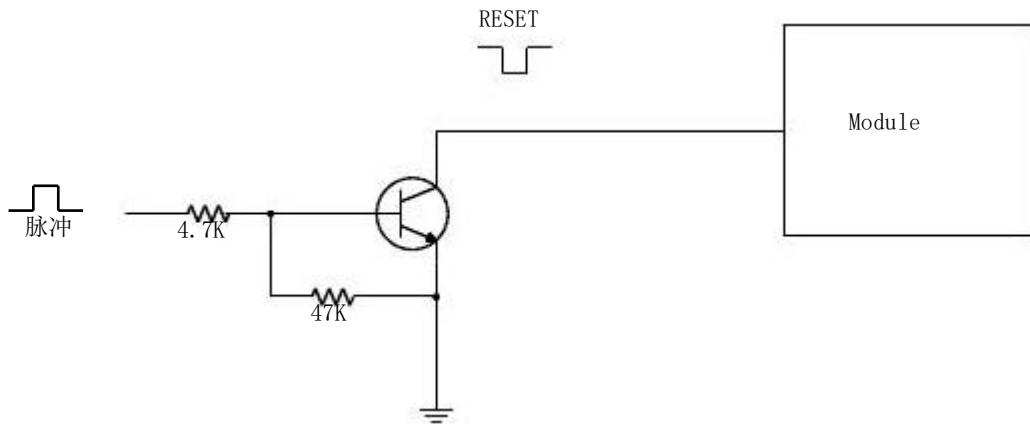

SLM920 module supports the reset function, and the user can quickly restart the module by pulling down the PM\_RESIN\_N (PIN141) pin of the module. The recommended circuit is as follows:

Figure 4.8 : Reset using key circuit

Figure 4.9 : Reset the module using an external signal

When the pin is at a high level, the voltage is typically 1.8V, so users with a level of 3V or 3.3V cannot directly use the GPIO of the MCU to drive this pin, and a voltage conversion circuit needs to be added. The hardware parameters of RESET can refer to the following table :

Table 4.1 : RESET Hardware Parameters

| Pin        | Describe             | Minimum | Typical value | Maximum value | Unit |

|------------|----------------------|---------|---------------|---------------|------|

| PM_RESET_N | Input high level     | 1.4 _   | 1.8           | -             | V    |

|            | Input low level      | -       | 0             | 0.6           | V    |

|            | Pull down valid time | 500     |               | -             | ms   |

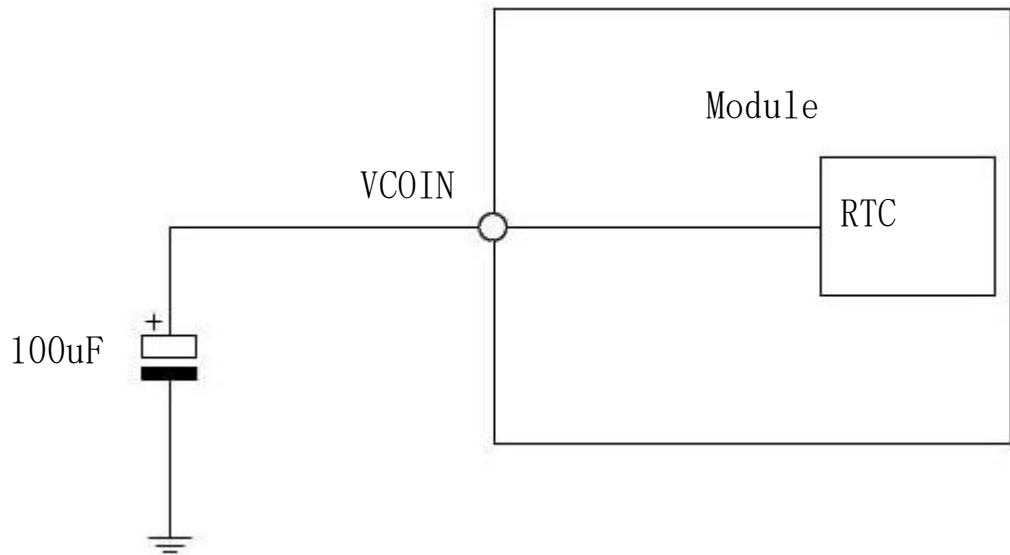

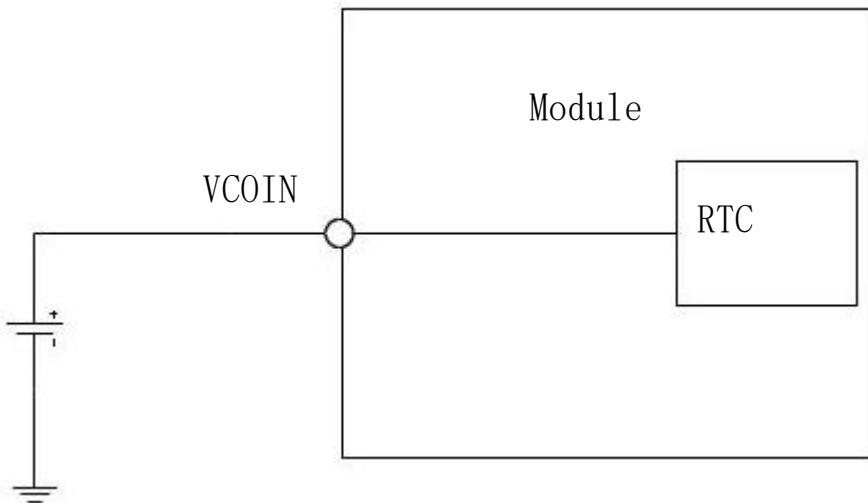

### 4.3. VCOIN power supply

When the VBAT is disconnected, the user needs to save the real-time clock, so the VCOIN (113) pin cannot be left floating, and should be connected to a large capacitor or a button battery. When an external large capacitor is connected, the recommended value is 100 uF. When the RTC power supply uses an external large capacitor or battery to supply power to the RTC inside the module, the reference design circuit is as follows:

Figure 4.10 : External Capacitor Powering the RTC

Rechargeable battery powered :

Figure 4.11 : Rechargeable battery powers RTC

The VCOIN power supply input voltage range is 2.5-3.1V, the typical value is 3.0V, and the current consumption is about 20 uA when VBAT is disconnected .

## 4.4. Power output

The SLM920 has multiple power outputs. For SD card, SIM card , Sensor , Touch panel , USB3.1 circuit, external LDO power supply , etc. In application, it is recommended to add parallel 33PF and 10PF capacitors to each power supply to effectively remove high-frequency interference.

Table 4.2 : Power Supply Description

| Signal          | Programmable Range ( V )    | Default voltage (V) | Drive current (mA) |

|-----------------|-----------------------------|---------------------|--------------------|

| VREG_L22A_2P96  | 1.504–3.544                 | 2.96                | 600                |

| VREG_L5A_2P96   | 1.504–3.544                 | 2.96                | 50                 |

| VREG_L20A_1P8   | 1.504–3.544                 | 1.8                 | 100                |

| VREG_L19A_1P8   | 1.504–3.544                 | 1.8                 | 100                |

| VREG_L21A_2P704 | 1.504–3.544                 | 2.8                 | 300                |

| VREG_L9A_1P8    | 1.504–2.000                 | 1.8                 | 100                |

| VREG_L12A_1P8   | 1.504–2.000                 | 1.8                 | 200                |

| VREG_L15A_3P128 | 1.504–3.544                 | 3.128               | 100                |

| VPH_PWR         | Variation with VBAT voltage | 3.8                 | 700                |

## 4.5. Serial port

SLM920 provides four serial ports for communication .

Table 4.3 : UART pin descriptions

| Name            | Pin | Direction | Function                     |

|-----------------|-----|-----------|------------------------------|

| GPIO16_DEBUG_TX | 11  | DO        | DEBUG UART data transmission |

| GPIO17_DEBUG_RX | 12  | DI        | DEBUG UART data reception    |

| GPIO9_UART_RX   | 16  | DI        | UART data reception          |

| GPIO8_UART_TX   | 15  | DO        | UART data transmission       |

| GPIO24_UART_TX  | 176 | DO        | UART data transmission       |

| GPIO25_UART_RX  | 177 | DI        | UART data reception          |

| GPIO2_UART_TX   | 256 | DO        | UART data transmission       |

| GPIO3_UART_RX   | 255 | DI        | UART data reception          |

If you need to use a four-wire serial port, you can refer to the GPIO multiplexing table for multiplexing.

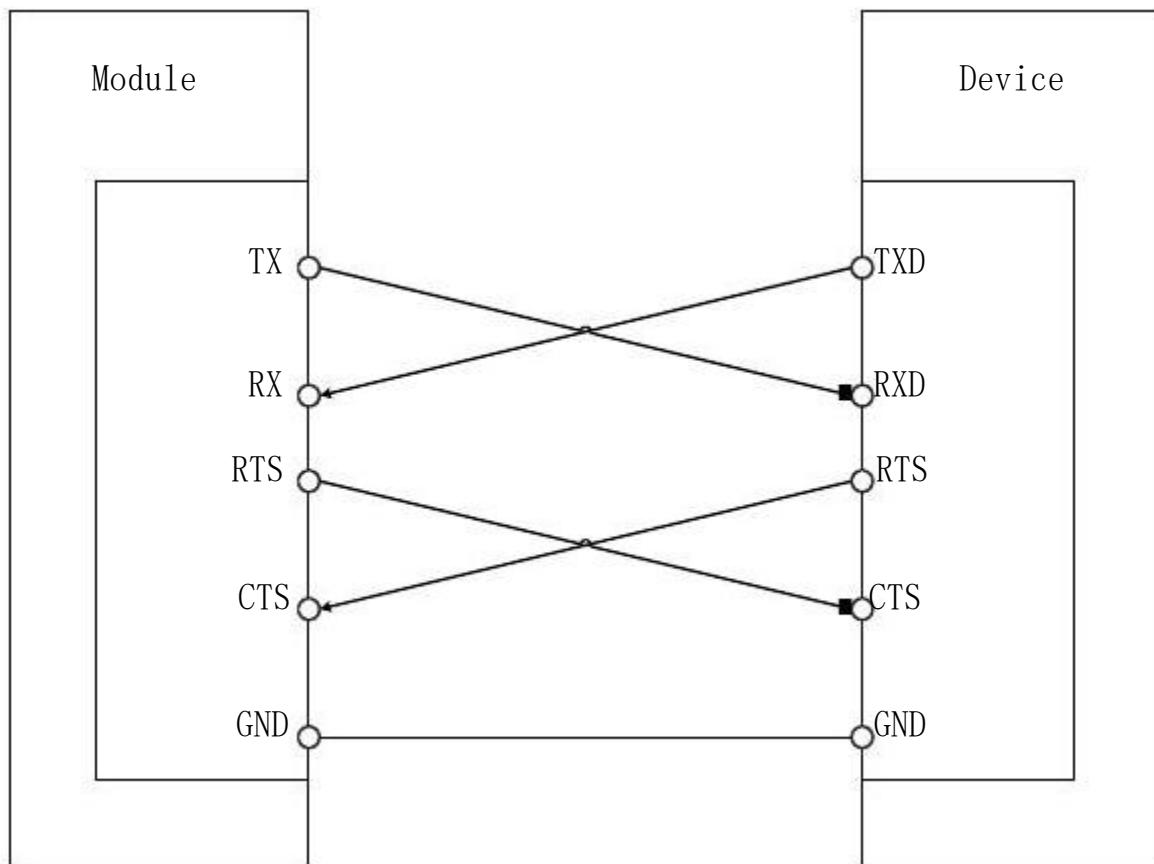

For serial connection , please refer to the connection method below :

Figure 4.12 : Serial port connection diagram

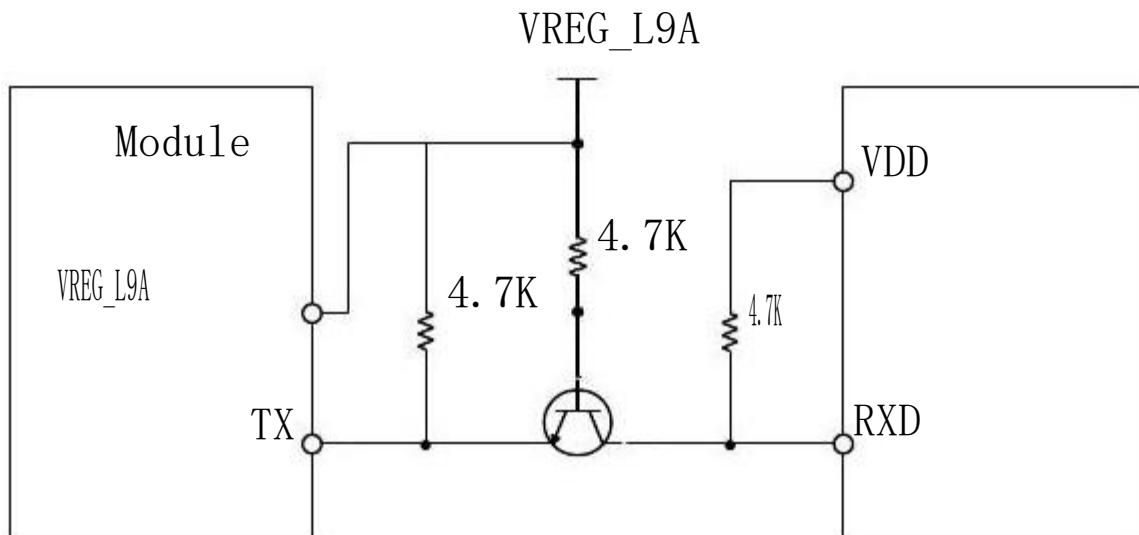

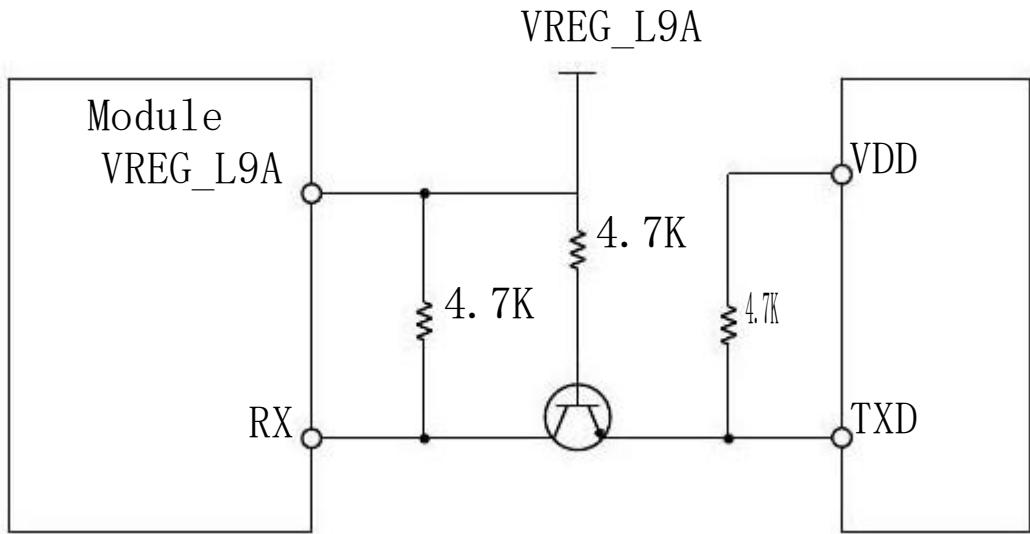

When the level of the serial port used by the user does not match the module, in addition to adding a level conversion IC, the following figure can also be used to achieve level matching. Only the matching circuits on TX and RX are listed here. Other low-speed signals can refer to this two circuits.

Figure 4.13 : TX Connection Diagram

Figure 4.14 : RX Connection Diagram

Note: When using Figure 4.13 and 4.14 for level isolation, it is recommended to use VREG\_L9A\_1P8 as the pull-up power supply .

Table 4.4 : Serial hardware parameters

| Describe          | Minimum | Maximum value | Unit |

|-------------------|---------|---------------|------|

| Input low level   | -       | 0.63          | V    |

| Input high level  | 1.17    | -             | V    |

| Output low level  | -       | 0.45          | V    |

| Output high level | 1.35    | -             | V    |

Note: 1. The serial port of the module is a CMOS interface and cannot be directly connected to RS232 signals. If needed, please use RS232 conversion chip.

2. If the 1.8V output of the module cannot meet the high level range of the user, please add a level conversion circuit.

## 4.6. MIPI interface

SLM920 supports MIPI interface for Camera and LCD.

MIPI is a high-speed signal line. In the layout stage, please strictly follow the impedance and length requirements , control the equal length of the differential pair within the group and between the groups, and keep the total length as short as possible.

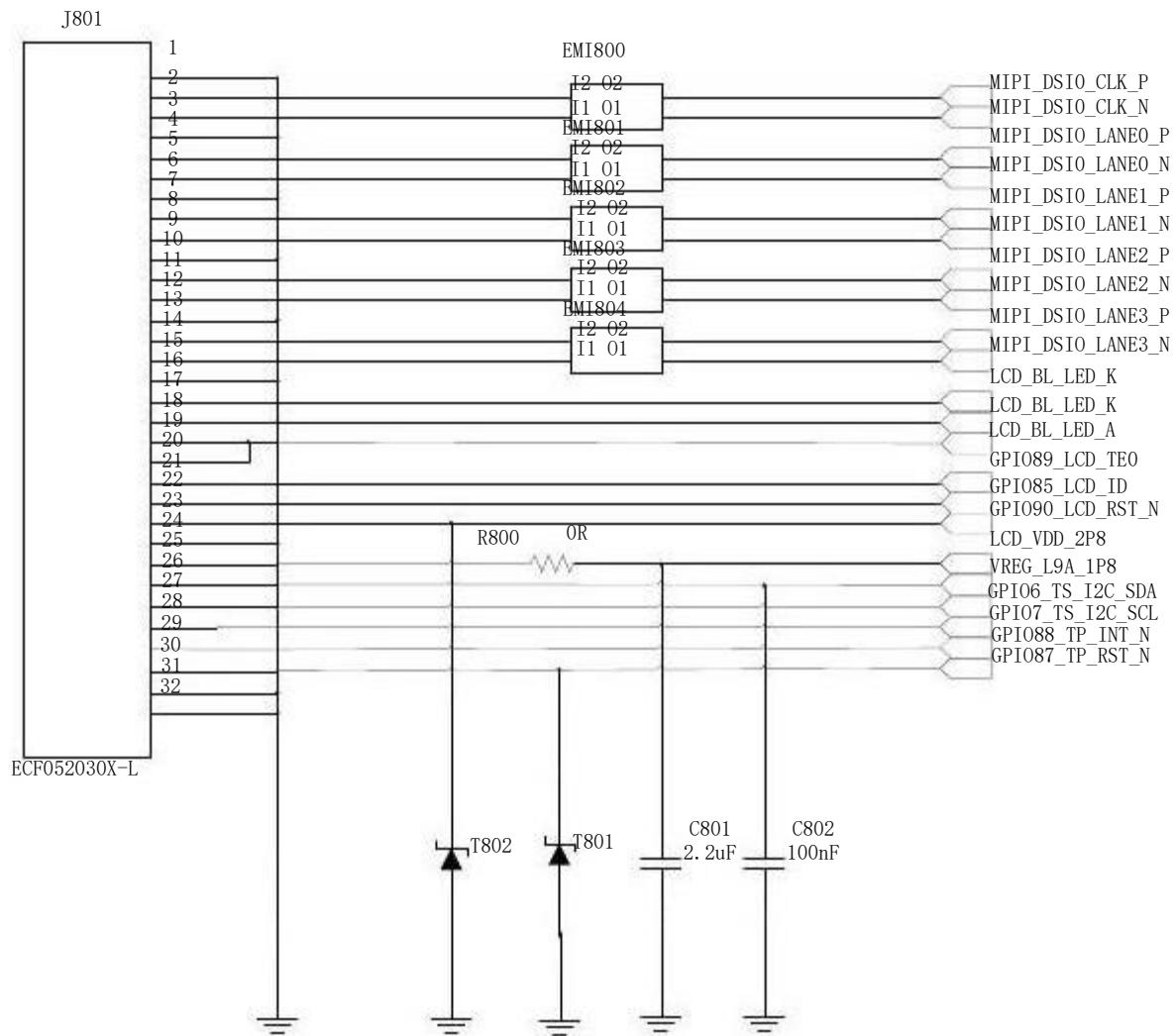

### 4.6.1. LCD interface

SLM920 module supports the MIPI interface of 1 group of LCD display screen, and the resolution of the screen can be up to FHD+ (2520X1080) . The signal interface is shown in the table below. During layout, please

strictly control the differential  $85 \pm 15 \Omega$  impedance of the MIPI signal line and the equal length of the signal line within and between groups .

The MIPI interface of the module is 1.2V power domain. When the user needs to be compatible with the screen design, the LCD\_ID pin or ADC pin of the module can be used. The LCD interface is as follows:

Table 4.5 : Screen Interface Definition

| Screen interface   |                   |     |                              |

|--------------------|-------------------|-----|------------------------------|

| MIPI_DSI0_CLK_N    | 64                | AO  | MIPI_LCD clock line          |

| MIPI_DSI0_CLK_P    | 65                | AO  |                              |

| MIPI_DSI0_LANE0_N  | 189               | AO  | MIPI_LCD data line           |

| MIPI_DSI0_LANE0_P  | 190               | AO  |                              |

| MIPI_DSI0_LANE1_N  | 66                | AO  |                              |

| MIPI_DSI0_LANE1_P  | 67                | AO  |                              |

| MIPI_DSI0_LANE3_N  | 73                | AO  |                              |

| MIPI_DSI0_LANE3_P  | 74                | AO  |                              |

| MIPI_DSI0_LANE2_N  | 71                | AO  |                              |

| MIPI_DSI0_LANE2_P  | 72                | AO  |                              |

| GPIO90_LCD_RST_N   | 75                | I/O | LCD reset pin                |

| GPIO89_MDP_VSYNC_P | 76                | I/O | LCD frame sync signal        |

| PM6125_GPIO8_PWM   | 112               | I/O | Screen backlight PWM control |

| VREG_L9A_1P8       | 138,140           | PO  | 1.8V power supply            |

| VREG_L21A_2P704    | 2.8V power output | PO  | 2.8V power supply            |

When the customer needs a compatible screen design, the LCD\_ID pin of the LCD should be connected to the ADC of the module, but it should be noted that the output voltage of the LCD\_ID cannot exceed the ADC pin voltage range.

MIPI is a high-speed signal line. To avoid EMI interference, it is recommended to place a common mode inductor on the side close to the LCD .

Figure 4.15 : LCD Interface Circuit

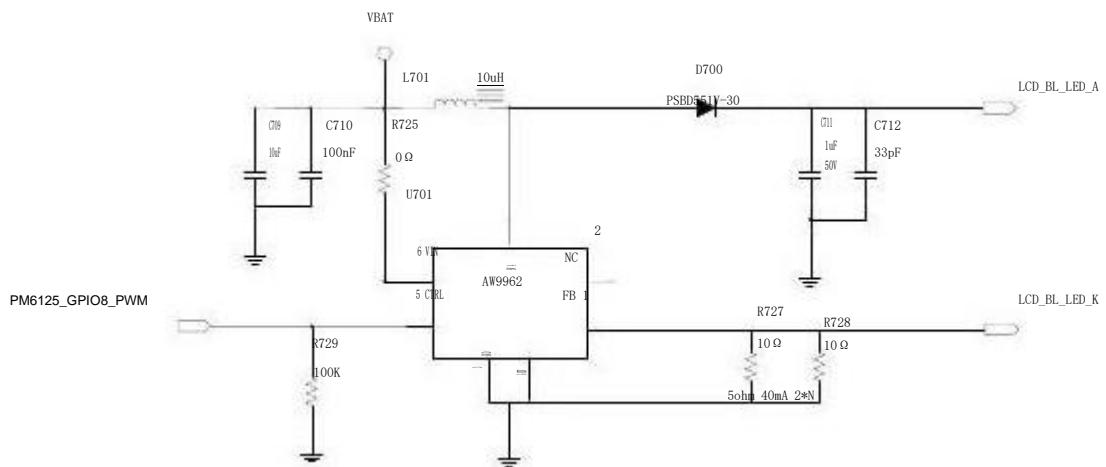

SLM920 module does not support backlight driver output, customers need to use external backlight driver. The backlight drive circuit can refer to Figure 4.16. The backlight brightness can be adjusted through PM6125\_GPIO8\_PWM (112) of the module , and the modulation mode is PWM mode.

Figure 4.16 : External backlight circuit diagram

Note: 1. The backlight circuit should select the chip according to the backlight circuit of the LCD, and the user **SLM920 Hardware Design Guide**

should read the LCD documentation carefully and select the correct driver chip. The reference circuit provided in this document is a series-type PWM dimming backlight drive circuit ; if it is a series-type one-line dimming backlight drive circuit, it needs to be controlled by GPIO.

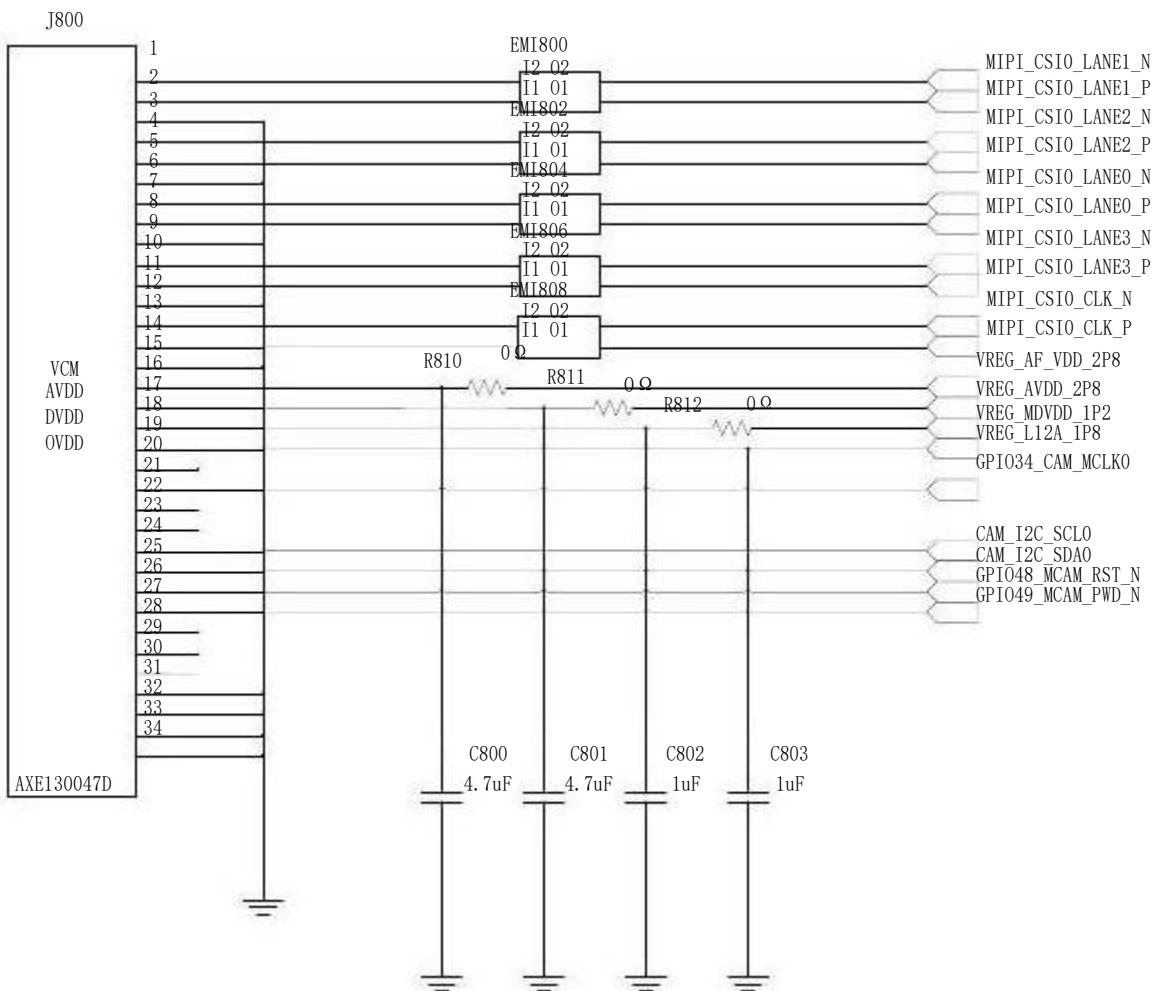

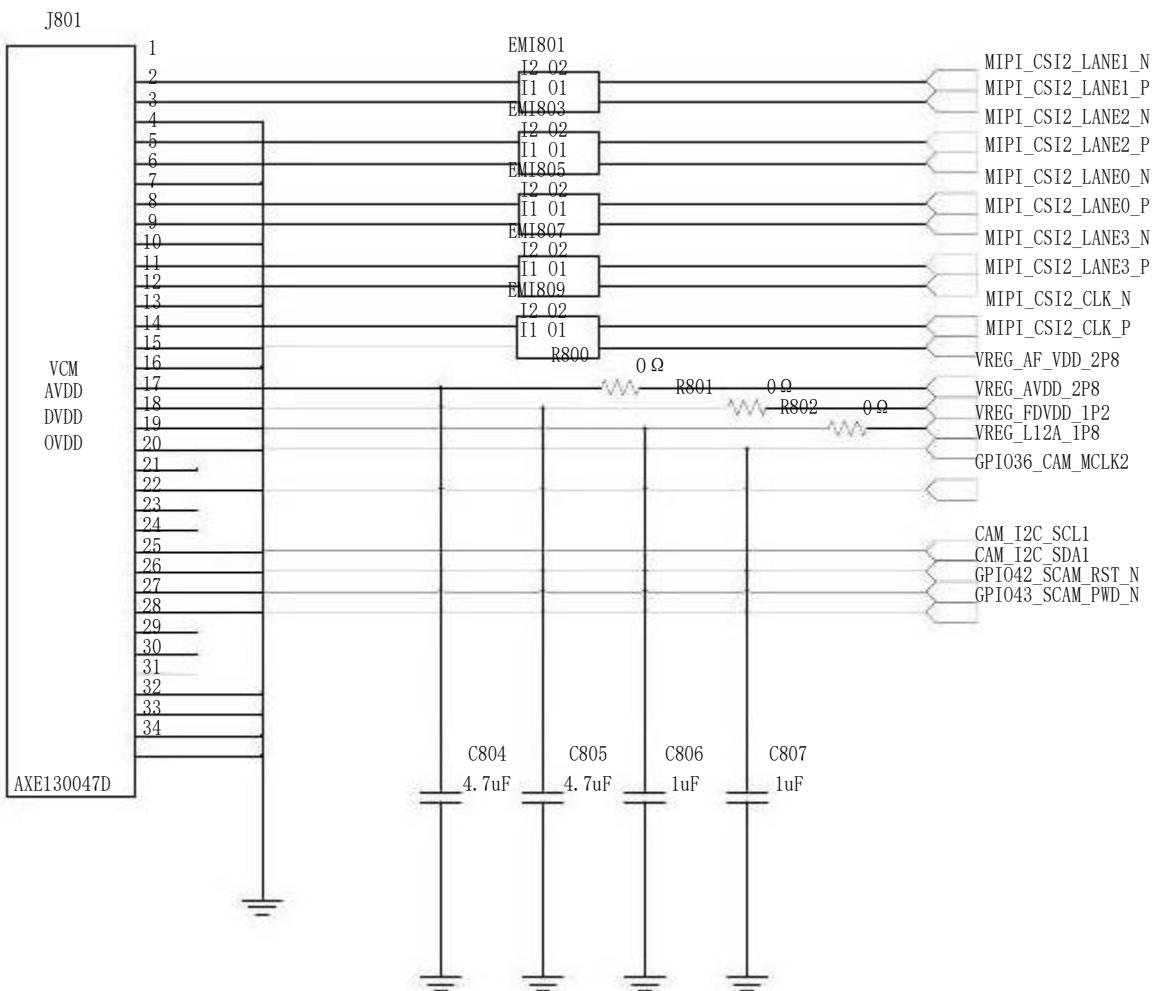

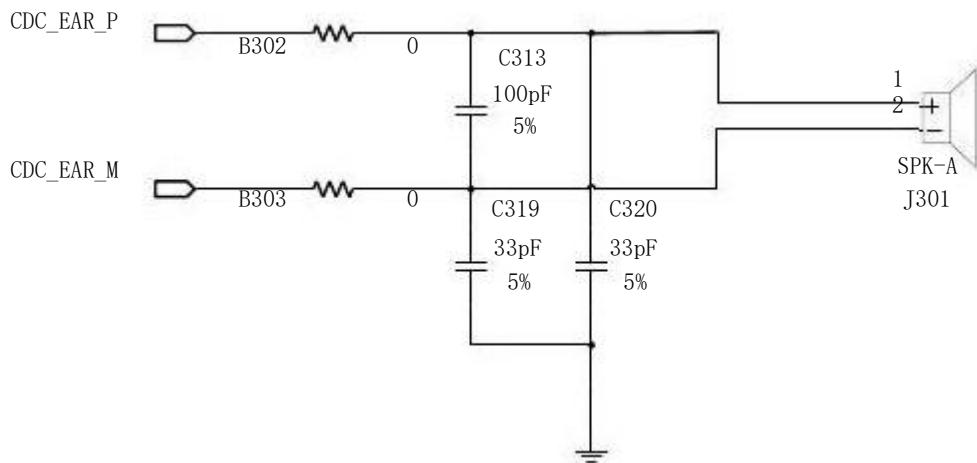

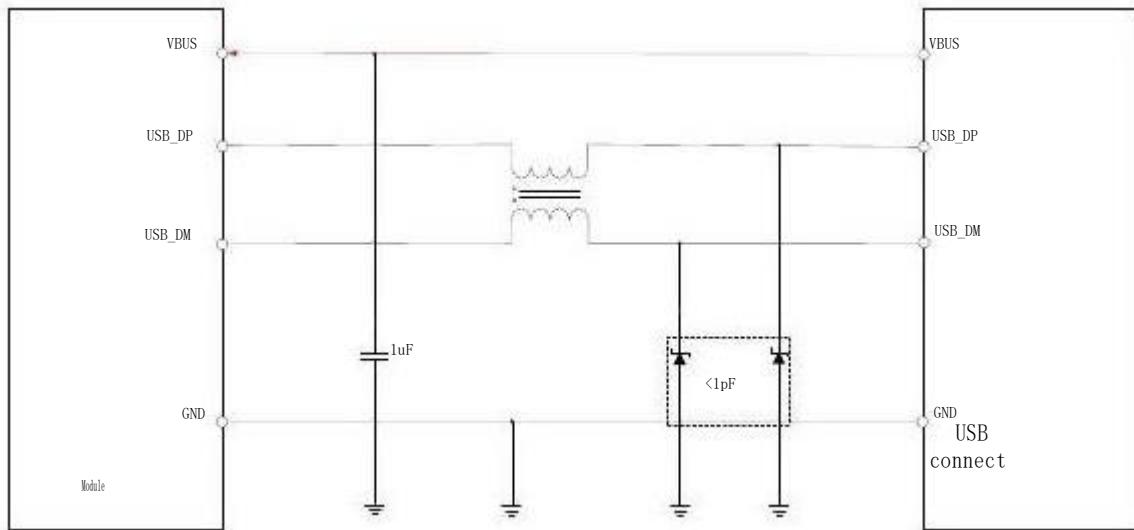

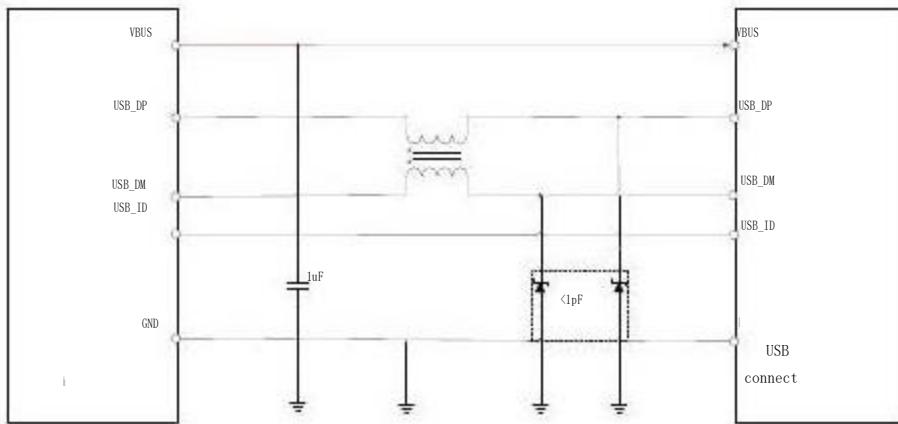

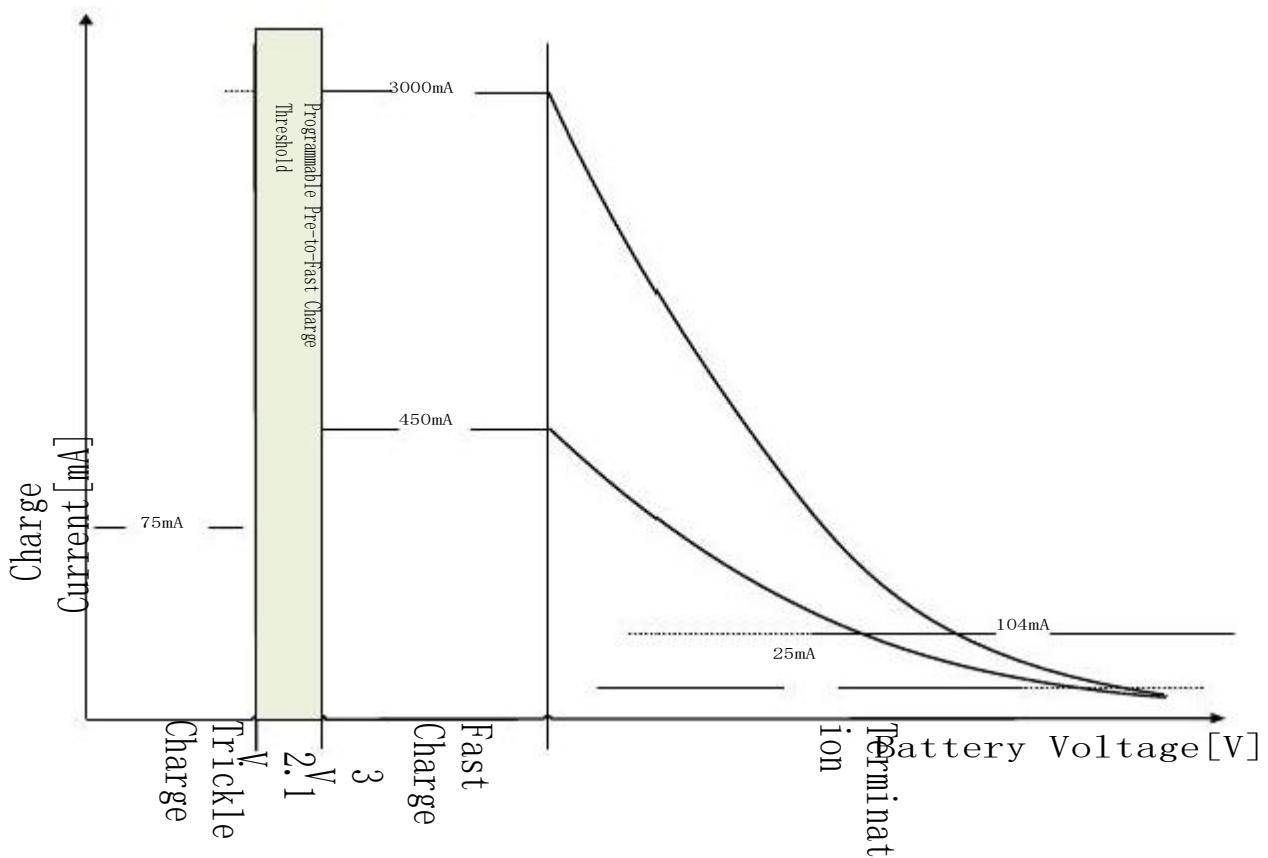

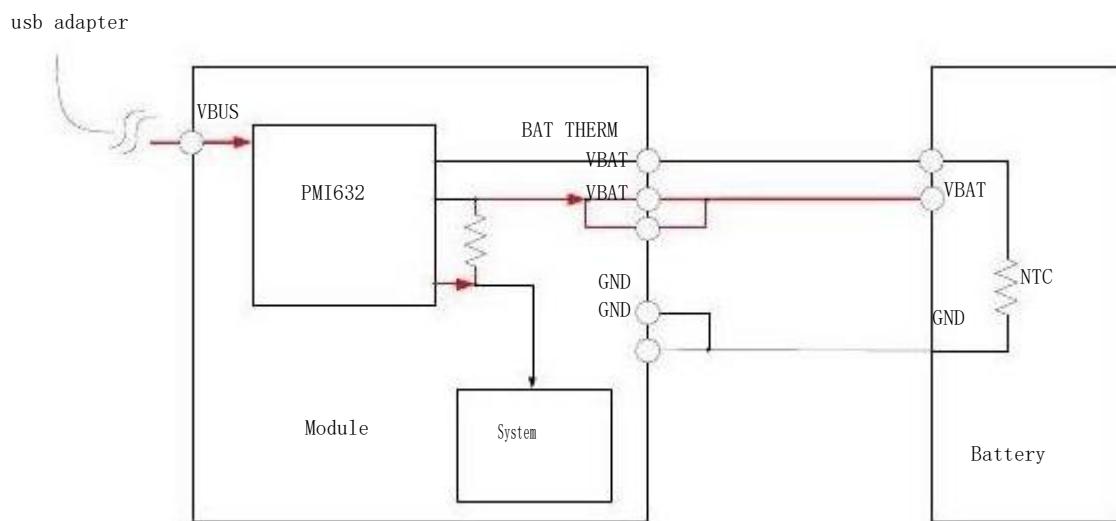

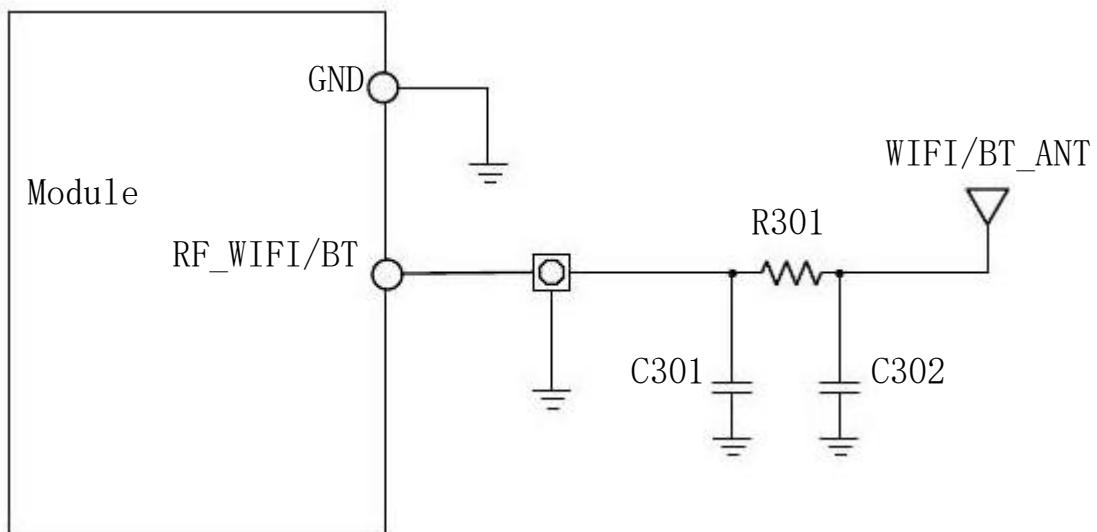

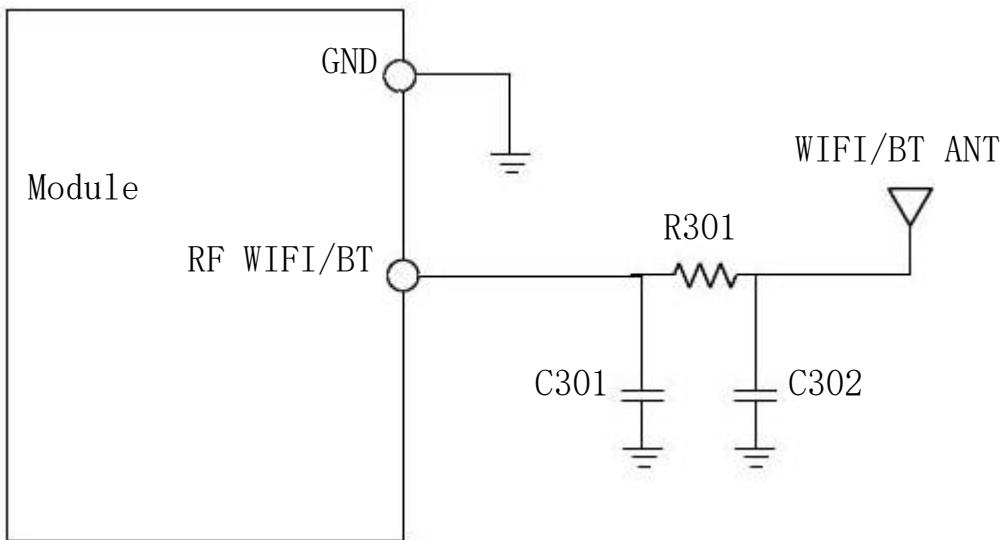

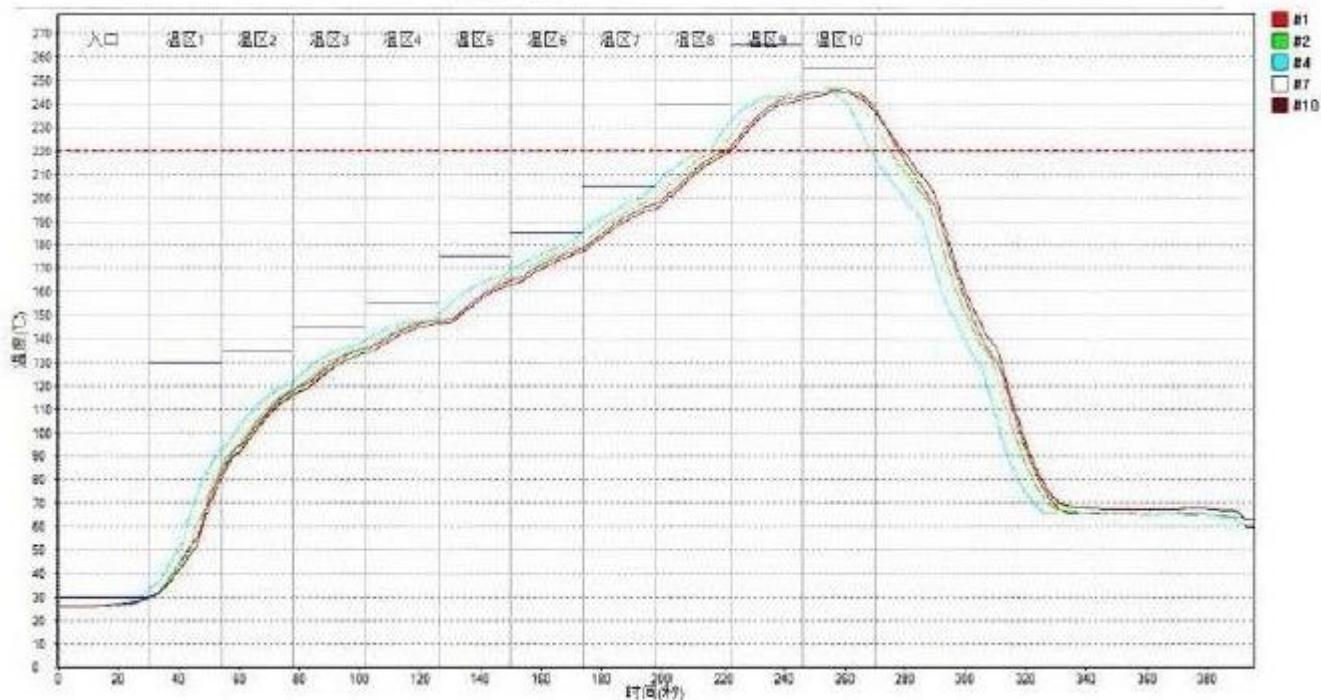

## 4.6.2. MIPI Camera interface