## User manual

Product Name:ESP Module

Model Name:0037

Manufacture:Syrp Limited

## Contents

|                                               |    |

|-----------------------------------------------|----|

| <b>1, Overview</b> .....                      | 3  |

| <b>2 Pin Definitions</b> .....                | 4  |

| 2.1 Pin Layout.....                           | 4  |

| 2.2 Pin Description.....                      | 5  |

| 2.3 Strapping Pins .....                      | 5  |

| <b>3 functional Description</b> .....         | 7  |

| 3.1 CPU and Internal Memory .....             | 7  |

| 3.2 External Flash and SRAM .....             | 7  |

| 3.3 Crystal Oscillators.....                  | 7  |

| 3.4 RTC and Low-Power Management .....        | 7  |

| <b>4. Peripherals and Sensors</b> .....       | 9  |

| 4.1 Peripherals and Sensors Description ..... | 9  |

| <b>5. Electrical Characteristics</b> .....    | 14 |

| 5.1 Absolute Maximum Ratings .....            | 14 |

| 5.2 Wi-Fi Radio .....                         | 14 |

| 5.3 BLE Radio.....                            | 15 |

| 5.3.1 Receiver.....                           | 15 |

| 5.3.2 Transmitter .....                       | 15 |

| 5.4 Reflow Profile.....                       | 16 |

| <b>6. ESP32-PICO-D4 Schematics</b> .....      | 17 |

| <b>7. ESP32-0031-7002 Schematics</b> .....    | 18 |

| <b>8. Peripheral Schematics</b> .....         | 19 |

| <b>9 Learning Resources</b> .....             | 20 |

| 9.1 Must-Read Documents .....                 | 20 |

| 9.2 Must-Have Resources .....                 | 20 |

## 1. Overview

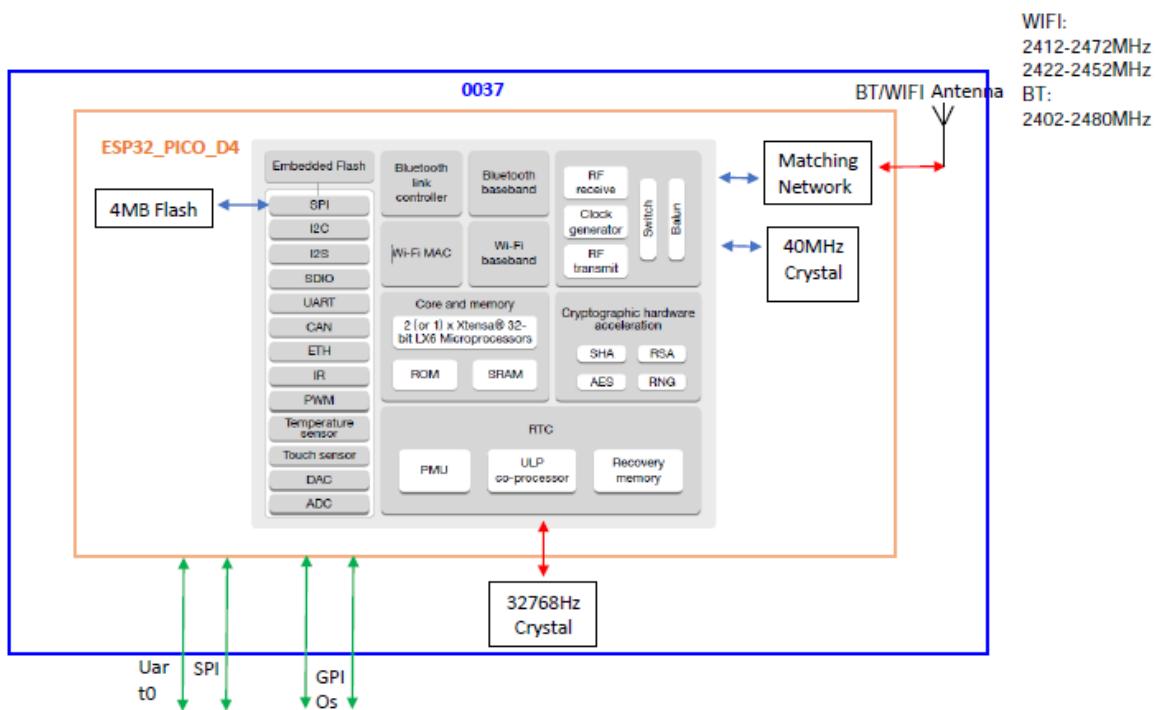

ESP32-0037-7002 is a wireless product, which mainly includes an ESP32-PICO-D4, a 32768Hz crystal and a 2.4GHz antenna. See the block diagram as Figure 1. 0037-7002 provides the WIFI and Blue Tooth (BLE) functions.

The ESP32-PICO-D4 is a System-in-Package (SIP) module that is based on ESP32, providing complete Wi-Fi and Bluetooth functionalities. The module integrates a 4-MB SPI flash.

At the core of this module is the ESP32 chip, which is a single 2.4 GHz Wi-Fi and Bluetooth combo chip. ESP32-PICO-D4 integrates all peripheral components seamlessly, including a crystal oscillator, flash, filter capacitors and RF matching links in one single package.

Figure 1 Block diagram of ESP32-0037-7002

## 2 Pin Definitions

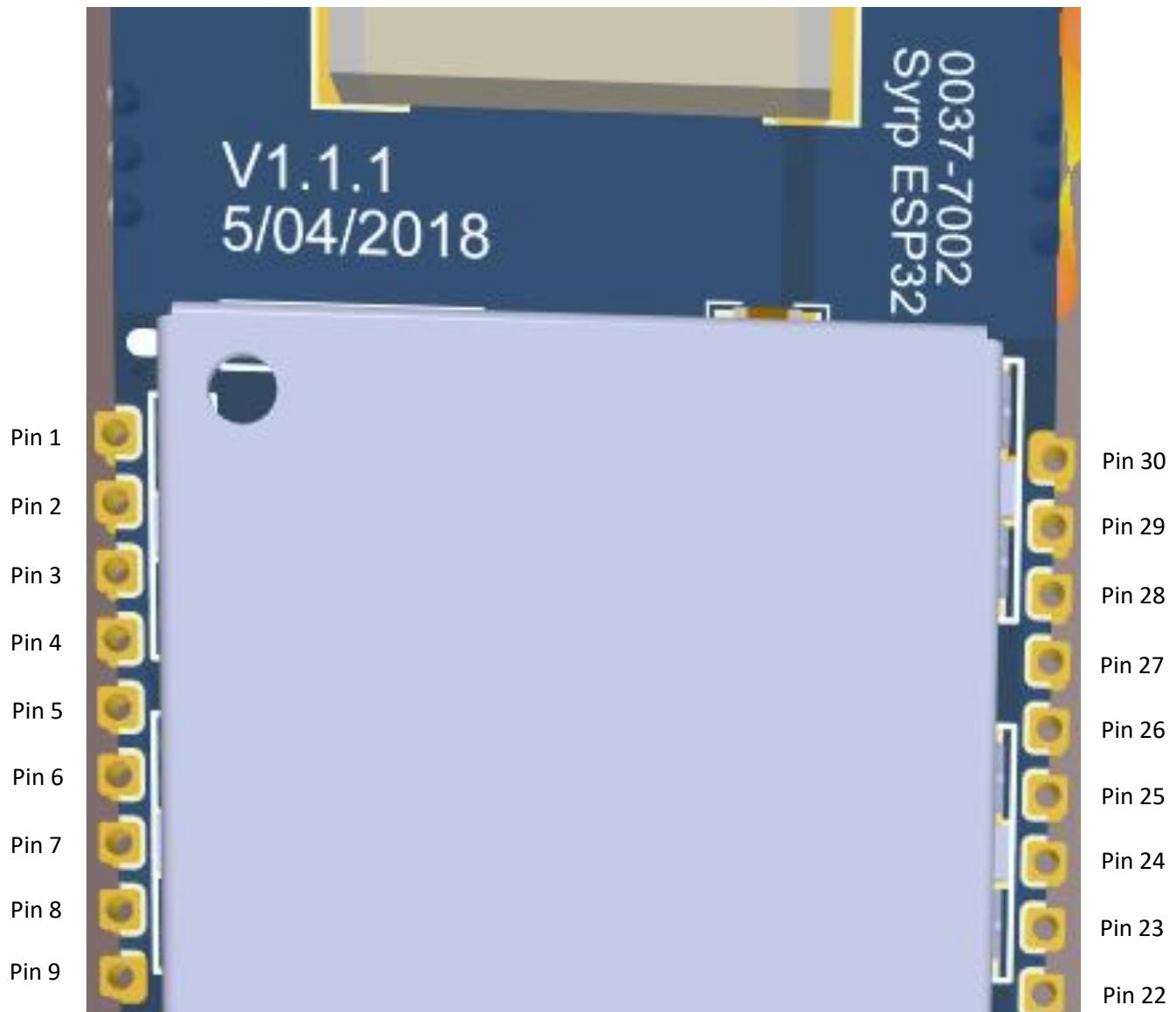

### 2.1 Pin Layout

Figure 2 Pin Layout of ESP32-0037-7002

|    |    |    |    |    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|----|----|----|----|

| Pi |

| n  | n  | n  | n  | n  | n  | n  | n  | n  | n  | n  | n  |

## 2.2 Pin Description

Table 2: Pin Description

| No. | Name  | Type | Function                                                                            |

|-----|-------|------|-------------------------------------------------------------------------------------|

| 1   | EN    | I    | Chip-enable signal. Active high.                                                    |

| 2   | IO34  | I    | GPIO34, ADC1_CH6, RTC_GPIO4                                                         |

| 3   | IO35  | I    | GPIO35, ADC1_CH7, RTC_GPIO5                                                         |

| 4   | IO25  | I/O  | GPIO25, DAC_1, ADC2_CH8, RTC_GPIO6, EMAC_RXD0                                       |

| 5   | IO26  | I/O  | GPIO26, DAC_2, ADC2_CH9, RTC_GPIO7, EMAC_RXD1                                       |

| 6   | IO27  | I/O  | GPIO27, ADC2_CH7, TOUCH7, RTC_GPIO17, EMAC_RX_DV                                    |

| 7   | IO14  | I/O  | GPIO14, ADC2_CH6, TOUCH6, RTC_GPIO16, MTMS, HSPICLK, HS2_CLK, SD_CLK, EMAC_TXD2     |

| 8   | IO12  | I/O  | GPIO12, ADC2_CH5, TOUCH5, RTC_GPIO15, MTDI, HSPIQ, HS2_DATA2, SD_DATA2, EMAC_TXD3   |

| 9   | GND   | P    | Ground                                                                              |

| 10  | VDD   | P    | Power supply (2.3V ~ 3.6V)                                                          |

| 11  | IO13  | I/O  | GPIO13, ADC2_CH4, TOUCH4, RTC_GPIO14, MTCK, HSPIID, HS2_DATA3, SD_DATA3, EMAC_RX_ER |

| 12  | IO15  | I/O  | GPIO15, ADC2_CH3, TOUCH3, MTDO, HSPICS0, RTC_GPIO13, HS2_CMD, SD_CMD, EMAC_RXD3     |

| 13  | IO2   | I/O  | GPIO2, ADC2_CH2, TOUCH2, RTC_GPIO12, HSPIWP, HS2_DATA0, SD_DATA0                    |

| 14  | IO0   | I/O  | GPIO0, ADC2_CH1, TOUCH1, RTC_GPIO11, CLK_OUT1, EMAC_TX_CLK                          |

| 15  | IO4   | I/O  | GPIO4, ADC2_CH0, TOUCH0, RTC_GPIO10, HSPIHD, HS2_DATA1, SD_DATA1, EMAC_TX_ER        |

| 16  | IO21  | I/O  | GPIO21, VSPIHD, EMAC_TX_EN                                                          |

| 17  | IO22  | I/O  | GPIO22, VSPIWP, U0RTS, EMAC_TXD1                                                    |

| 18  | IO5   | I/O  | GPIO5, VSPICS0, HS1_DATA6, EMAC_RX_CLK                                              |

| 19  | IO18  | I/O  | GPIO18, VSPICLK, HS1_DATA7                                                          |

| 20  | IO23  | I/O  | GPIO23, VSPIID, HS1_STROBE                                                          |

| 21  | GND   | P    | Ground                                                                              |

| 22  | VDD   | P    | Power supply (2.3V ~ 3.6V)                                                          |

| 23  | VDD   | P    | Power supply (2.3V ~ 3.6V)                                                          |

| 24  | IO19  | I/O  | GPIO19, VSPIQ, U0CTS, EMAC_TXD0                                                     |

| 25  | NC    | -    | Not Connected                                                                       |

| 26  | U0RXD | I/O  | GPIO3, U0RXD, CLK_OUT2                                                              |

| 27  | U0TXD | I/O  | GPIO1, U0TXD, CLK_OUT3, EMAC_RXD2                                                   |

| 28  | NC    | -    | Not connected                                                                       |

| 29  | VDD   | P    | Power supply (2.3V ~ 3.6V)                                                          |

| 30  | GND   | P    | Ground                                                                              |

## 2.3 Strapping Pins

ESP32 has five strapping pins, which can be seen in Section 5 Schematics:

- MTDI

- GPIO0

- GPIO2

- MTDO

- GPIO5

Software can read the value of these five bits from the register "GPIO\_STRAPPING".

During the chip power-on reset, the latches of the strapping pins sample the voltage level as strapping bits of "0" or "1", and hold these bits until the chip is powered down or shut down. The strapping bits configure the device boot mode, the operating voltage of VDD\_SDIO and other system initial settings.

Each strapping pin is connected with its internal pull-up/pull-down during the chip reset. Consequently, if a strapping pin is unconnected or the connected external circuit is high-impedance, the internal weak pull-up/pull-down will determine the default input level of the strapping pins.

To change the strapping bit values, users can apply the external pull-down/pull-up resistances, or apply the host

MCU's GPIOs to control the voltage level of these pins when powering on ESP32.

After reset, the strapping pins work as the normal functions pins.

Refer to Table 3 for detailed boot modes' configuration by strapping pins.

Table 3: Strapping Pins

| Voltage of Internal LDO (VDD_SDIO)    |           |                                           |                                         |                                          |                                         |

|---------------------------------------|-----------|-------------------------------------------|-----------------------------------------|------------------------------------------|-----------------------------------------|

| Pin                                   | Default   | 3.3V                                      | 1.8V                                    |                                          |                                         |

| MTDI                                  | Pull-down | 0                                         | 1                                       |                                          |                                         |

| Booting Mode                          |           |                                           |                                         |                                          |                                         |

| Pin                                   | Default   | SPI Boot                                  | Download Boot                           |                                          |                                         |

| GPIO0                                 | Pull-up   | 1                                         | 0                                       |                                          |                                         |

| GPIO2                                 | Pull-down | Don't-care                                | 0                                       |                                          |                                         |

| Debugging Log on U0TXD During Booting |           |                                           |                                         |                                          |                                         |

| Pin                                   | Default   | U0TXD Toggling                            | U0TXD Silent                            |                                          |                                         |

| MTDO                                  | Pull-up   | 1                                         | 0                                       |                                          |                                         |

| Timing of SDIO Slave                  |           |                                           |                                         |                                          |                                         |

| Pin                                   | Default   | Falling-edge Input<br>Falling-edge Output | Rising-edge Input<br>Rising-edge Output | Rising-edge Input<br>Falling-edge Output | Rising-edge Input<br>Rising-edge Output |

| MTDO                                  | Pull-up   | 0                                         | 0                                       | 1                                        | 1                                       |

| GPIO5                                 | Pull-up   | 0                                         | 1                                       | 0                                        | 1                                       |

**Note:**

Firmware can configure register bits to change the settings of "Voltage of Internal LDO (VDD\_SDIO)" and "Timing of SDIO Slave", after booting.

## 3 functionalDescription

This chapter describes the modules integrated in ESP32-0037-7002, and their functions.

### 3.1 CPU and Internal Memory

ESP32 contains two low-power Xtensa® 32-bit LX6 microprocessors. The internal memory includes:

- 448 KB of ROM for booting and core functions.

- 520 KB (8 KB RTC FAST Memory included) of on-chip SRAM for data and instruction.

- 8 KB of SRAM in RTC, which is called RTC FAST Memory and can be used for data storage; it is accessed by the main CPU during RTC Boot from the Deep-sleep mode.

- 8 KB of SRAM in RTC, which is called RTC SLOW Memory and can be accessed by the co-processor during the Deep-sleep mode.

- 1 kbit of eFuse, of which 256 bits are used for the system (MAC address and chip configuration) and the remaining 768 bits are reserved for customer applications, including Flash-Encryption and Chip-ID.

### 3.2 External Flash and SRAM

The ESP32-PICO-D4 module integrates 4 MB of external SPI flash. The 4-MB SPI flash can be memory-mapped onto the CPU code space, supporting 8, 16 and 32-bit access. Code execution is supported.

**Note:**

The operating voltage of ESP32-PICO-D4's integrated external SPI flash is 3.3V. Therefore, the strapping pin MTDI should hold bit "0" during the module power-on reset.

### 3.3 Crystal Oscillators

ESP32-PICO-D4 integrates a 40 MHz crystal oscillator.

### 3.4 RTC and Low-Power Management

With the use of advanced power-management technologies, ESP32 can switch between different power modes (see Table 5).

- Power modes

– Active mode: The chip radio is powered on. The chip can receive, transmit, or listen.

– Modem-sleep mode: The CPU is operational and the clock is configurable. The Wi-Fi/Bluetooth baseband and radio are disabled.

– Light-sleep mode: The CPU is paused. The RTC memory and RTC peripherals, as well as the ULP coprocessor are running. Any wake-up events (MAC, host, RTC timer, or external interrupts) will wake up the chip.

– Deep-sleep mode: Only RTC memory and RTC peripherals are powered on. Wi-Fi and Bluetooth connection data are stored in RTC memory. The ULP-coprocessor can work.

– Hibernation mode: The internal 8-MHz oscillator and ULP-coprocessor are disabled. The RTC recovery memory is powered down. Only one RTC timer on the slow clock and some RTC GPIOs are active. The RTC timer or the RTC GPIOs can wake up the chip from the Hibernation mode.

- Sleep Patterns

– Association sleep pattern: The power mode switches between the Active mode, Modem- and Lightsleep mode, during this sleep pattern. The CPU, Wi-Fi, Bluetooth, and radio are woken up at predetermined intervals to keep Wi-Fi/BT connections alive.

– ULP sensor-monitored pattern: The main CPU is in the Deep-sleep mode. The ULP-coprocessor takes sensor measurements and wakes up the main system, based on the data collected from sensors.

**Table 5: Functionalities Depending on the Power Modes**

| Power mode                     | Active                    | Modem-sleep | Light-sleep | Deep-sleep                   | Hibernation |

|--------------------------------|---------------------------|-------------|-------------|------------------------------|-------------|

| Sleep pattern                  | Association sleep pattern |             |             | ULP sensor-monitored pattern | -           |

| CPU                            | ON                        | ON          | PAUSE       | OFF                          | OFF         |

| Wi-Fi/BT baseband and radio    | ON                        | OFF         | OFF         | OFF                          | OFF         |

| RTC memory and RTC peripherals | ON                        | ON          | ON          | ON                           | OFF         |

| ULP-coprocessor                | ON                        | ON          | ON          | ON/OFF                       | OFF         |

The power consumption varies with different power modes/sleep patterns and work statuses of functional modules. Please see Table 6 for details.

**Table 6: Power Consumption by Power Modes**

| Power mode          | Description                                          | Power consumption                     |

|---------------------|------------------------------------------------------|---------------------------------------|

| Active (RF working) | Wi-Fi Tx packet 14 dBm ~ 19.5 dBm                    | Please refer to Table 10 for details. |

|                     | Wi-Fi / BT Tx packet 0 dBm                           |                                       |

|                     | Wi-Fi / BT Rx and listening                          |                                       |

|                     | Association sleep pattern (by Light-sleep)           |                                       |

| Modem-sleep         | The CPU is powered on.                               | 1 mA ~ 4 mA @DTIM3                    |

|                     |                                                      | Max speed 240 MHz: 30 mA ~ 50 mA      |

|                     |                                                      | Normal speed 80 MHz: 20 mA ~ 25 mA    |

| Light-sleep         | -                                                    | Slow speed 2 MHz: 2 mA ~ 4 mA         |

| Deep-sleep          | The ULP-coprocessor is powered on.                   | 0.8 mA                                |

|                     | ULP sensor-monitored pattern                         | 150 $\mu$ A                           |

|                     | RTC timer + RTC memory                               | 100 $\mu$ A @1% duty                  |

| Hibernation         | RTC timer only                                       | 10 $\mu$ A                            |

| Power off           | CHIP_PU is set to low level, the chip is powered off | 5 $\mu$ A                             |

**Note:**

- During Deep-sleep, when the ULP-coprocessor is powered on, peripherals such as GPIO and I2C are able to work.

- When the system works in the ULP sensor-monitored pattern, the ULP-coprocessor works with the ULP sensor periodically and ADC works with a duty cycle of 1%, so the power consumption is 100  $\mu$ A.

## 4. Peripherals and Sensors

### 4.1 Peripherals and Sensors Description

**Table 7: Peripherals and Sensors Description**

| Interface                               | Signal    | Pin       | Function                                                       |

|-----------------------------------------|-----------|-----------|----------------------------------------------------------------|

| ADC                                     | ADC1_CH0  | SENSOR_VP | Two 12-bit SAR ADCs                                            |

|                                         | ADC1_CH3  | SENSOR_VN |                                                                |

|                                         | ADC1_CH4  | IO32      |                                                                |

|                                         | ADC1_CH5  | IO33      |                                                                |

|                                         | ADC1_CH6  | IO34      |                                                                |

|                                         | ADC1_CH7  | IO35      |                                                                |

|                                         | ADC2_CH0  | IO4       |                                                                |

|                                         | ADC2_CH1  | IO0       |                                                                |

|                                         | ADC2_CH2  | IO2       |                                                                |

|                                         | ADC2_CH3  | IO15      |                                                                |

|                                         | ADC2_CH4  | IO13      |                                                                |

|                                         | ADC2_CH5  | IO12      |                                                                |

|                                         | ADC2_CH6  | IO14      |                                                                |

|                                         | ADC2_CH7  | IO27      |                                                                |

|                                         | ADC2_CH8  | IO25      |                                                                |

|                                         | ADC2_CH9  | IO26      |                                                                |

| Ultra Low Noise<br>Analog Pre-Amplifier |           | IO36      | Provides about 60 dB gain by using larger<br>capacitors on PCB |

|                                         |           | IO39      |                                                                |

| DAC                                     | DAC_1     | IO25      | Two 8-bit DACs                                                 |

|                                         | DAC_2     | IO26      |                                                                |

| Touch Sensor                            | TOUCH0    | IO4       | Capacitive touch sensors                                       |

|                                         | TOUCH1    | IO0       |                                                                |

|                                         | TOUCH2    | IO2       |                                                                |

|                                         | TOUCH3    | IO15      |                                                                |

|                                         | TOUCH4    | IO13      |                                                                |

|                                         | TOUCH5    | IO12      |                                                                |

|                                         | TOUCH6    | IO14      |                                                                |

|                                         | TOUCH7    | IO27      |                                                                |

|                                         | TOUCH8    | IO33      |                                                                |

|                                         | TOUCH9    | IO32      |                                                                |

| SD/SDIO/MMC Host<br>Controller          | HS2_CLK   | MTMS      | Supports SD memory card V3.01 standard                         |

|                                         | HS2_CMD   | MTDO      |                                                                |

|                                         | HS2_DATA0 | IO2       |                                                                |

|                                         | HS2_DATA1 | IO4       |                                                                |

|                                         | HS2_DATA2 | MTDI      |                                                                |

|                                         | HS2_DATA3 | MTCK      |                                                                |

| Interface | Signal             | Pin        | Function                                                                                                                                                                   |

|-----------|--------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Motor PWM | PWM0_OUT0~2        | Any GPIOs* | Three channels of 16-bit timers generate PWM waveforms; each has a pair of output signals. Three fault detection signals. Three event capture signals. Three sync signals. |

|           | PWM1_OUT_IN0~2     |            |                                                                                                                                                                            |

|           | PWM0_FLT_IN0~2     |            |                                                                                                                                                                            |

|           | PWM1_FLT_IN0~2     |            |                                                                                                                                                                            |

|           | PWM0_CAP_IN0~2     |            |                                                                                                                                                                            |

|           | PWM1_CAP_IN0~2     |            |                                                                                                                                                                            |

|           | PWM0_SYNC_IN0~2    |            |                                                                                                                                                                            |

|           | PWM1_SYNC_IN0~2    |            |                                                                                                                                                                            |

| LED PWM   | ledc_hs_sig_out0~7 | Any GPIOs* | 16 independent channels @80 MHz clock/RTC CLK. Duty accuracy: 16 bits.                                                                                                     |

|           | ledc_ls_sig_out0~7 |            |                                                                                                                                                                            |

| UART      | U0RXD_in           | Any GPIOs* | Two UART devices with hardware flow-control and DMA                                                                                                                        |

|           | U0CTS_in           |            |                                                                                                                                                                            |

|           | U0DSR_in           |            |                                                                                                                                                                            |

|           | U0TXD_out          |            |                                                                                                                                                                            |

|           | U0RTS_out          |            |                                                                                                                                                                            |

|           | U0DTR_out          |            |                                                                                                                                                                            |

|           | U1RXD_in           |            |                                                                                                                                                                            |

|           | U1CTS_in           |            |                                                                                                                                                                            |

|           | U1TXD_out          |            |                                                                                                                                                                            |

|           | U1RTS_out          |            |                                                                                                                                                                            |

|           | U2RXD_in           |            |                                                                                                                                                                            |

|           | U2CTS_in           |            |                                                                                                                                                                            |

|           | U2TXD_out          |            |                                                                                                                                                                            |

|           | U2RTS_out          |            |                                                                                                                                                                            |

| I2C       | I2CEXT0_SCL_in     | Any GPIOs* | Two I2C devices in slave or master modes                                                                                                                                   |

|           | I2CEXT0_SDA_in     |            |                                                                                                                                                                            |

|           | I2CEXT1_SCL_in     |            |                                                                                                                                                                            |

|           | I2CEXT1_SDA_in     |            |                                                                                                                                                                            |

|           | I2CEXT0_SCL_out    |            |                                                                                                                                                                            |

|           | I2CEXT0_SDA_out    |            |                                                                                                                                                                            |

|           | I2CEXT1_SCL_out    |            |                                                                                                                                                                            |

|           | I2CEXT1_SDA_out    |            |                                                                                                                                                                            |

| Interface         | Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin        | Function                                                                      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------|

| I2S               | I2S0I_DATA_in0~15<br>I2S0O_BCK_in<br>I2S0O_WS_in<br>I2S0I_BCK_in<br>I2S0I_WS_in<br>I2S0I_H_SYNC<br>I2S0I_V_SYNC<br>I2S0I_H_ENABLE<br>I2S0O_BCK_out<br>I2S0O_WS_out<br>I2S0I_BCK_out<br>I2S0I_WS_out<br>I2S0O_DATA_out0~23<br>I2S1I_DATA_in0~15<br>I2S1O_BCK_in<br>I2S1O_WS_in<br>I2S1I_BCK_in<br>I2S1I_WS_in<br>I2S1I_H_SYNC<br>I2S1I_V_SYNC<br>I2S1I_H_ENABLE<br>I2S1O_BCK_out<br>I2S1O_WS_out<br>I2S1I_BCK_out<br>I2S1I_WS_out<br>I2S1O_DATA_out0~23 | Any GPIOs* | Stereo input and output from/to the audio codec, and parallel LCD data output |

| Remote Controller | RMT_SIG_IN0~7<br>RMT_SIG_OUT0~7                                                                                                                                                                                                                                                                                                                                                                                                                        | Any GPIOs* | Eight channels of IR transmitter and receiver for various waveforms           |

| Interface           | Signal           | Pin                          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------------------|------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parallel QSPI       | SPIHD            | SHD/SD2                      | Supports Standard SPI, Dual SPI, and Quad SPI that can be connected to the external flash and SRAM                                                                                                                                                                                                                                                                                                                                                              |  |

|                     | SPIWP            | SWP/SD3                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | SPICS0           | SCS/CMD                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | SPICLK           | SCK/CLK                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | SPIQ             | SDO/SD0                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | SPID             | SDI/SD1                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | HSPICLK          | IO14                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | HSPICS0          | IO15                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | HSPIQ            | IO12                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | HSPID            | IO13                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | HSPIHD           | IO4                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | HSPIWP           | IO2                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | VSPICLK          | IO18                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | VSPICSO          | IO5                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | VSPIQ            | IO19                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| General Purpose SPI | VSPID            | IO23                         | Standard SPI consists of clock, chip-select, MOSI and MISO. These SPIs can be connected to LCD and other external devices. They support the following features: <ul style="list-style-type: none"> <li>• both master and slave modes;</li> <li>• 4 sub-modes of the SPI format transfer that depend on the clock phase (CPHA) and clock polarity (CPOL) control;</li> <li>• CLK frequencies by a divider;</li> <li>• up to 64 bytes of FIFO and DMA.</li> </ul> |  |

|                     | VSPIQ_in/_out    | Any GPIOs*                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | HSPIQ_in/_out    |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | HSPICLK_in/_out  |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | HSPI_CS0_in/_out |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | HSPI_CS1_out     |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | HSPI_CS2_out     |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | VSPIQ_in/_out    |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | VSPIID_in/_out   |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | VSPICLK_in/_out  |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| JTAG                | VSPI_CS0_in/_out | IO12<br>IO13<br>IO14<br>IO15 | JTAG for software debugging                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                     | VSPI_CS1_out     |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | VSPI_CS2_out     |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                     | MTDI             |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Interface  | Signal           | Pin        | Function                                                                           |

|------------|------------------|------------|------------------------------------------------------------------------------------|

| SDIO Slave | SD_CLK           | IO6        | SDIO interface that conforms to the industry standard SDIO 2.0 card specification. |

|            | SD_CMD           | IO11       |                                                                                    |

|            | SD_DATA0         | IO7        |                                                                                    |

|            | SD_DATA1         | IO8        |                                                                                    |

|            | SD_DATA2         | IO9        |                                                                                    |

|            | SD_DATA3         | IO10       |                                                                                    |

| EMAC       | EMAC_TX_CLK      | IO0        | Ethernet MAC with MII/RMII interface                                               |

|            | EMAC_RX_CLK      | IO5        |                                                                                    |

|            | EMAC_TX_EN       | IO21       |                                                                                    |

|            | EMAC_TXD0        | IO19       |                                                                                    |

|            | EMAC_TXD1        | IO22       |                                                                                    |

|            | EMAC_TXD2        | IO14       |                                                                                    |

|            | EMAC_TXD3        | IO12       |                                                                                    |

|            | EMAC_RX_ER       | IO13       |                                                                                    |

|            | EMAC_RX_DV       | IO27       |                                                                                    |

|            | EMAC_RXD0        | IO25       |                                                                                    |

|            | EMAC_RXD1        | IO26       |                                                                                    |

|            | EMAC_RXD2        | TXD0       |                                                                                    |

|            | EMAC_RXD3        | IO15       |                                                                                    |

|            | EMAC_CLK_OUT     | IO16       |                                                                                    |

|            | EMAC_CLK_OUT_180 | IO17       |                                                                                    |

|            | EMAC_TX_ER       | IO4        |                                                                                    |

|            | EMAC_MDC_out     | Any GPIOs* |                                                                                    |

|            | EMAC_MDI_in      | Any GPIOs* |                                                                                    |

|            | EMAC_MDO_out     | Any GPIOs* |                                                                                    |

|            | EMAC_CRS_out     | Any GPIOs* |                                                                                    |

|            | EMAC_COL_out     | Any GPIOs* |                                                                                    |

**Note:**

Functions of Motor PWM, LED PWM, UART, I2C, I2S, general purpose SPI and Remote Controller can be configured to any GPIO.

## 5. Electrical Characteristics

Note: The specifications in this chapter have been tested under the following general condition: VDD = 3.3V, TA = 27°C, unless otherwise specified.

### 5.1 Absolute Maximum Ratings

**Table 8: Absolute Maximum Ratings**

| Parameter                                 | Symbol           | Min                               | Typ | Max                               | Unit |

|-------------------------------------------|------------------|-----------------------------------|-----|-----------------------------------|------|

| Power supply <sup>1</sup>                 | VDD              | 2.3                               | 3.3 | 3.6                               | V    |

| Minimum current delivered by power supply | I <sub>VDD</sub> | 0.5                               | -   | -                                 | A    |

| Input low voltage                         | V <sub>IL</sub>  | -0.3                              | -   | 0.25×V <sub>IO</sub> <sup>2</sup> | V    |

| Input high voltage                        | V <sub>IH</sub>  | 0.75×V <sub>IO</sub> <sup>2</sup> | -   | V <sub>IO</sub> <sup>2</sup> +0.3 | V    |

| Input leakage current                     | I <sub>IL</sub>  | -                                 | -   | 50                                | nA   |

| Input pin capacitance                     | C <sub>pad</sub> | -                                 | -   | 2                                 | pF   |

| Output low voltage                        | V <sub>OL</sub>  | -                                 | -   | 0.1×V <sub>IO</sub> <sup>2</sup>  | V    |

| Output high voltage                       | V <sub>OH</sub>  | 0.8×V <sub>IO</sub> <sup>2</sup>  | -   | -                                 | V    |

| Maximum output drive capability           | I <sub>MAX</sub> | -                                 | -   | 40                                | mA   |

| Storage temperature range                 | T <sub>STR</sub> | -40                               | -   | 85                                | °C   |

| Operating temperature range               | T <sub>OPR</sub> | -40                               | -   | 85                                | °C   |

### 5.2 Wi-Fi Radio

**Table 9: Wi-Fi Radio Characteristics**

| Description                      | Min  | Typical | Max  | Unit |

|----------------------------------|------|---------|------|------|

| Input frequency                  | 2412 | -       | 2484 | MHz  |

| Output impedance                 | -    | 30+j10  | -    | Ω    |

| Input reflection                 | -    | -       | -10  | dB   |

| Tx power                         |      |         |      |      |

| Output power of PA for 72.2 Mbps | 13   | 14      | 15   | dBm  |

| Output power of PA for 11b mode  | 19.5 | 20      | 20.5 | dBm  |

| Sensitivity                      |      |         |      |      |

| DSSS, 1 Mbps                     | -    | -98     | -    | dBm  |

| CCK, 11 Mbps                     | -    | -91     | -    | dBm  |

| OFDM, 6 Mbps                     | -    | -93     | -    | dBm  |

| Description                | Min | Typical | Max | Unit |

|----------------------------|-----|---------|-----|------|

| OFDM, 54 Mbps              | -   | -75     | -   | dBm  |

| HT20, MCS0                 | -   | -93     | -   | dBm  |

| HT20, MCS7                 | -   | -73     | -   | dBm  |

| HT40, MCS0                 | -   | -90     | -   | dBm  |

| HT40, MCS7                 | -   | -70     | -   | dBm  |

| MCS32                      | -   | -89     | -   | dBm  |

| Adjacent channel rejection |     |         |     |      |

| OFDM, 6 Mbps               | -   | 37      | -   | dB   |

| OFDM, 54 Mbps              | -   | 21      | -   | dB   |

| HT20, MCS0                 | -   | 37      | -   | dB   |

| HT20, MCS7                 | -   | 20      | -   | dB   |

## 5.3 BLE Radio

### 5.3.1 Receiver

**Table 10: Receiver Characteristics – BLE**

| Parameter                          | Conditions                | Min | Typ | Max | Unit |

|------------------------------------|---------------------------|-----|-----|-----|------|

| Sensitivity @30.8% PER             | -                         | -   | -97 | -   | dBm  |

| Maximum received signal @30.8% PER | -                         | 0   | -   | -   | dBm  |

| Co-channel C/I                     | -                         | -   | +10 | -   | dB   |

| Adjacent channel selectivity C/I   | $F = F_0 + 1 \text{ MHz}$ | -   | -5  | -   | dB   |

|                                    | $F = F_0 - 1 \text{ MHz}$ | -   | -5  | -   | dB   |

|                                    | $F = F_0 + 2 \text{ MHz}$ | -   | -25 | -   | dB   |

|                                    | $F = F_0 - 2 \text{ MHz}$ | -   | -35 | -   | dB   |

|                                    | $F = F_0 + 3 \text{ MHz}$ | -   | -25 | -   | dB   |

|                                    | $F = F_0 - 3 \text{ MHz}$ | -   | -45 | -   | dB   |

| Out-of-band blocking performance   | 30 MHz ~ 2000 MHz         | -10 | -   | -   | dBm  |

|                                    | 2000 MHz ~ 2400 MHz       | -27 | -   | -   | dBm  |

|                                    | 2500 MHz ~ 3000 MHz       | -27 | -   | -   | dBm  |

|                                    | 3000 MHz ~ 12.5 GHz       | -10 | -   | -   | dBm  |

| Intermodulation                    | -                         | -36 | -   | -   | dBm  |

### 5.3.2 Transmitter

Table 11: Transmitter Characteristics – BLE

| Parameter              | Conditions | Min | Typ     | Max | Unit |

|------------------------|------------|-----|---------|-----|------|

| RF transmit power      | -          | -   | 0       | -   | dBm  |

| Gain control step      | -          | -   | $\pm 3$ | -   | dBm  |

| RF power control range | -          | -12 | -       | +12 | dBm  |

| Parameter                                       | Conditions                  | Min | Typ   | Max | Unit                 |

|-------------------------------------------------|-----------------------------|-----|-------|-----|----------------------|

| Adjacent channel transmit power                 | $F = F_0 + 1 \text{ MHz}$   | -   | -14.6 | -   | dBm                  |

|                                                 | $F = F_0 - 1 \text{ MHz}$   | -   | -12.7 | -   | dBm                  |

|                                                 | $F = F_0 + 2 \text{ MHz}$   | -   | -44.3 | -   | dBm                  |

|                                                 | $F = F_0 - 2 \text{ MHz}$   | -   | -38.7 | -   | dBm                  |

|                                                 | $F = F_0 + 3 \text{ MHz}$   | -   | -49.2 | -   | dBm                  |

|                                                 | $F = F_0 - 3 \text{ MHz}$   | -   | -44.7 | -   | dBm                  |

|                                                 | $F = F_0 + > 3 \text{ MHz}$ | -   | -50   | -   | dBm                  |

|                                                 | $F = F_0 - > 3 \text{ MHz}$ | -   | -50   | -   | dBm                  |

| $\Delta f_{1\text{avg}}$                        | -                           | -   | -     | 265 | kHz                  |

| $\Delta f_{2\text{max}}$                        | -                           | 247 | -     | -   | kHz                  |

| $\Delta f_{2\text{avg}}/\Delta f_{1\text{avg}}$ | -                           | -   | -0.92 | -   | -                    |

| ICFT                                            | -                           | -   | -10   | -   | kHz                  |

| Drift rate                                      | -                           | -   | 0.7   | -   | kHz/50 $\mu\text{s}$ |

| Drift                                           | -                           | -   | 2     | -   | kHz                  |

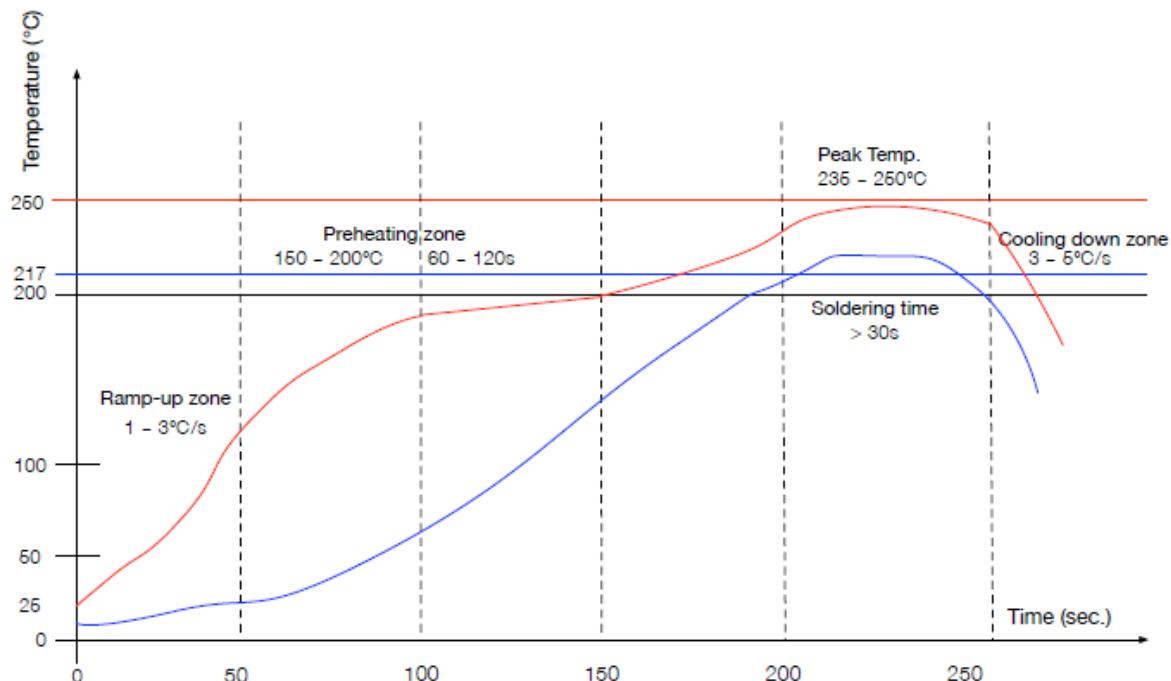

#### 5.4 Reflow Profile

Ramp-up zone — Temp.: <160°C Time: 0 - 90s Ramp-up rate: 1 - 3°C/s

Preheating zone — Temp.: 160 - 200°C Time: 60 - 120s Ramp-up rate: 0.3 - 0.8°C/s

Reflow soldering zone — Peak Temp.: 236 - 260°C (<246°C recommended) Time: 30 - 70s

Cooling down zone — Temp.: 217 - 170°C Ramp-down rate: 3 - 5°C/s

Solder — Sn&Ag&Cu Lead-free solder (SAC306)

Figure 2: Reflow Profile

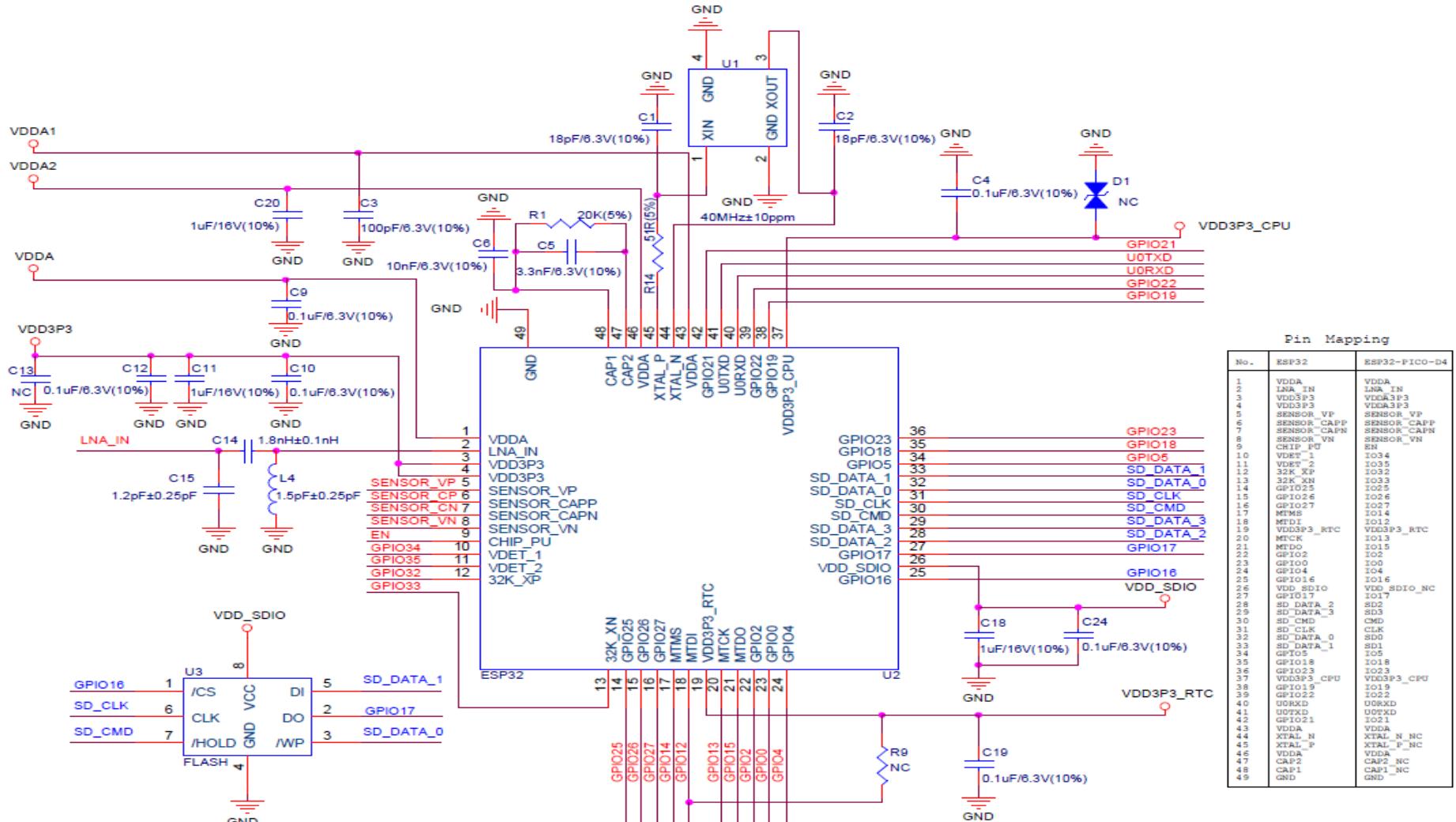

## 6. ESP32-PICO-D4 Schematics

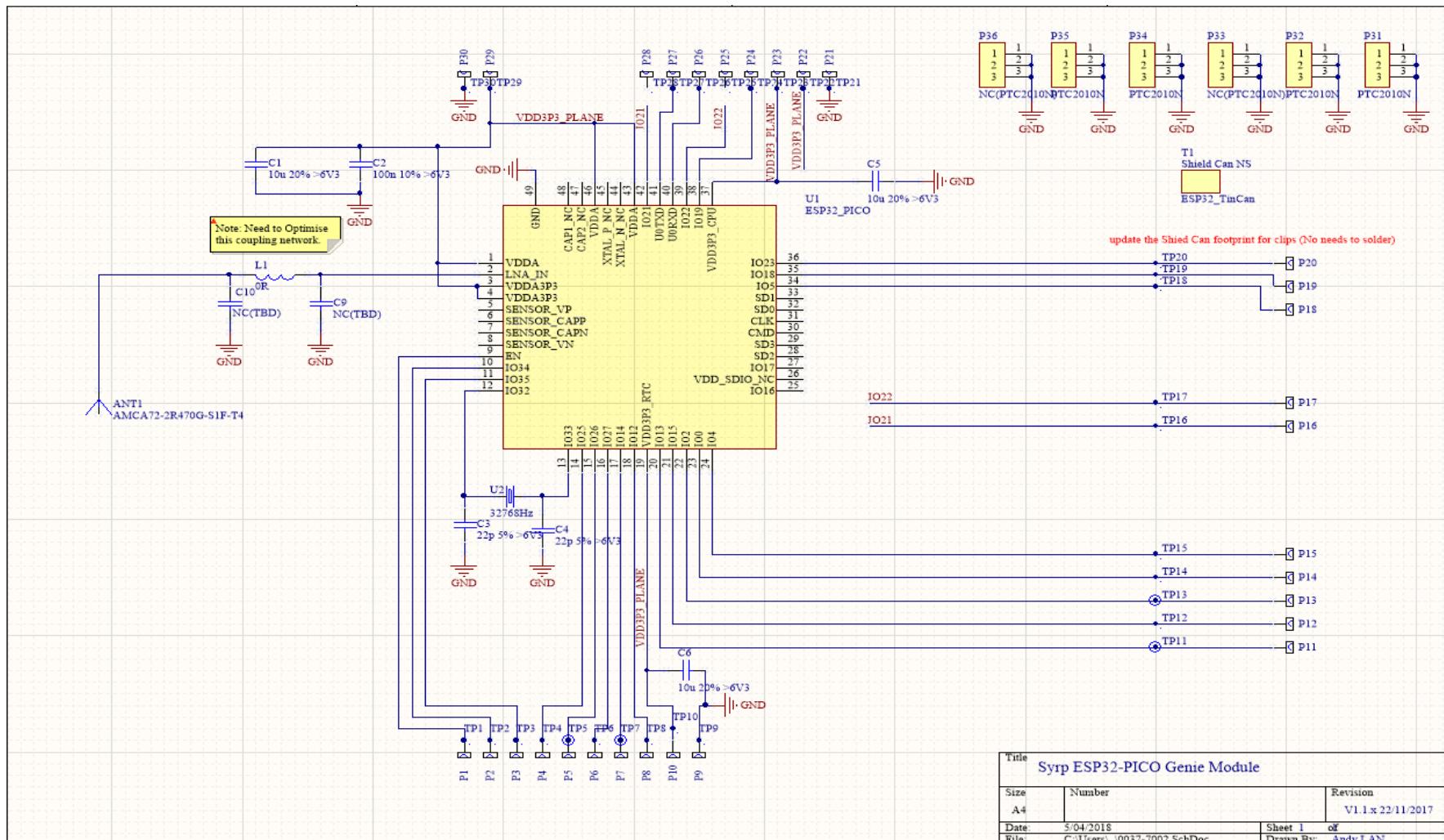

**Figure 3: ESP32-PICO-D4 Schematics**

## 7. ESP32-0031-7002 Schematics

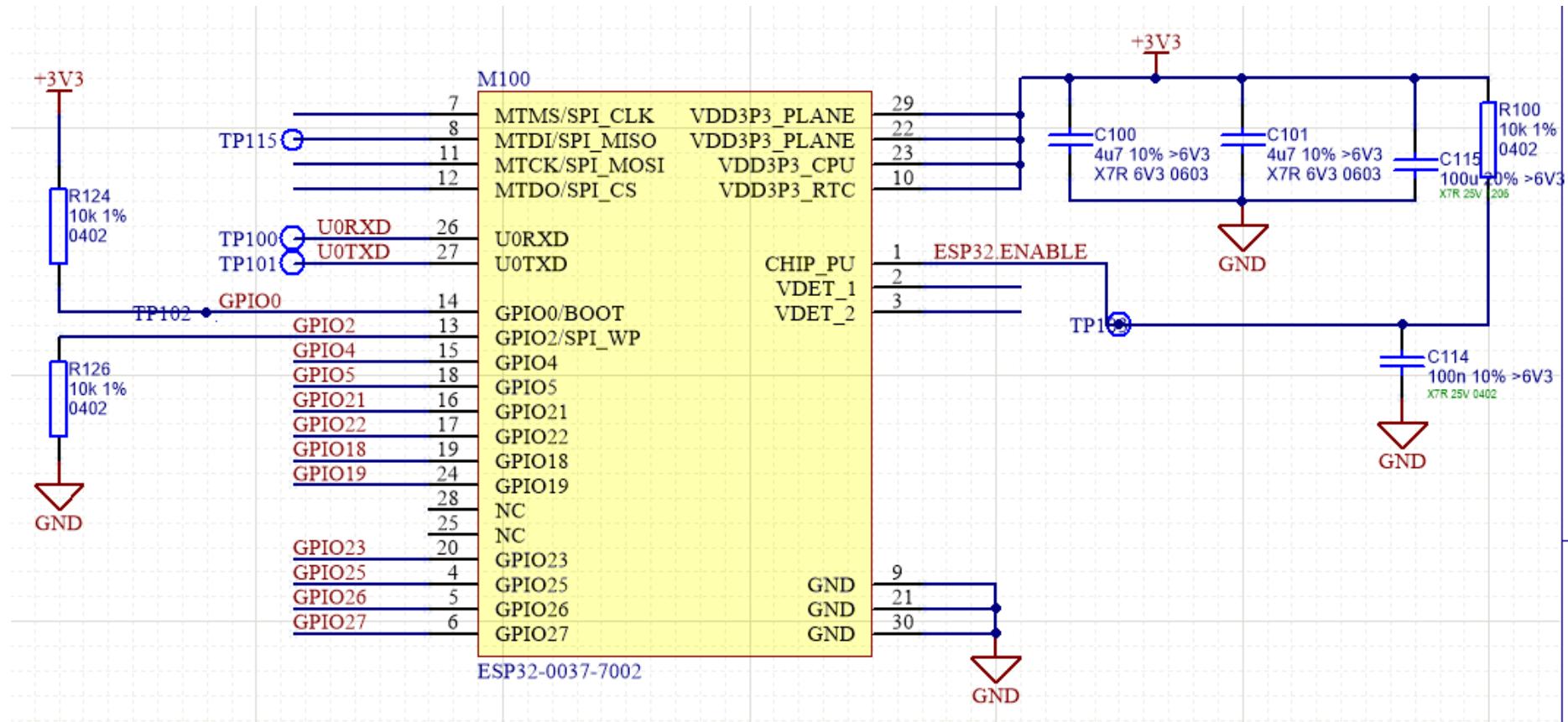

Figure 4: ESP32-0031-7002 Schematics

## 8. Peripheral Schematics

**Figure 4: ESP32-0031-7002 Peripheral Schematics**

## 9 Learning Resources

### 9.1 Must-Read Documents

The following link provides related documents of ESP32.

- [ESP32 Datasheet](#)

This document provides introduction to the specifications of the ESP32 hardware, including overview, pin definitions, functional description, peripheral interface, electrical characteristics, etc.

- [ESP32-PICO-D4 Datasheet](#)

- [ESP32 Technical Reference Manual](#)

The manual provides detailed information on how to use the ESP32 memory and peripherals.

- [ESP32 Hardware Resources](#)

The zip files include the schematics, PCB layout, Gerber and BOM list of ESP32 modules and development boards.

- [ESP32 Hardware Design Guidelines](#)

The guidelines outline recommended design practices when developing standalone or add-on systems based on the ESP32 series of products, including ESP32, the ESP-WROOM-32 module, and ESP32-DevKitC—the development board.

- [ESP32 AT Instruction Set and Examples](#)

This document introduces the ESP32 AT commands, explains how to use them and provides examples of several common AT commands.

### 9.2 Must-Have Resources

Here are the ESP32-related must-have resources.

- [ESP32 BBS](#)

This is an Engineer-to-Engineer (E2E) Community for ESP32 where you can post questions, share knowledge, explore ideas, and help solve problems with fellow engineers.

- [ESP32 Github](#)

ESP32 development projects are freely distributed under Espressif's MIT license on Github. It is established to help developers get started with ESP32 and foster innovation and the growth of general knowledge about the hardware and software surrounding ESP32 devices.

- [ESP32 Tools](#)

This is a web-page where users can download ESP32 Flash Download Tools and the zip file "ESP32 Certification and Test".

- [ESP32 IDF](#)

This web-page links users to the official IoT development framework for ESP32.

- [ESP32 Resources](#)

This webpage provides the links to all the available ESP32 documents, SDK and tools.

#### FCC Statement

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Any Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

The modular can be installed or integrated in mobile or fix devices only. This modular cannot be installed in any portable device.

#### FCC Radiation Exposure Statement

This modular complies with FCC RF radiation exposure limits set forth for an uncontrolled environment. This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter. This modular must be installed and operated with a minimum distance of 20 cm between the radiator and user body.

If the FCC identification number is not visible when the module is installed inside another device, then the outside of the device into which the module is installed must also display a label referring to the enclosed module. This exterior label can use wording such as the following:

“Contains Transmitter Module FCC ID: 2APDW0037 Or Contains FCC ID: 2APDW0037”

When the module is installed inside another device, the user manual of the host must contain below warning statements;

1. This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

(1) This device may not cause harmful interference.

(2) This device must accept any interference received, including interference that may cause undesired operation.

2. Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

The devices must be installed and used in strict accordance with the manufacturer's instructions as described in the user documentation that comes with the product.

Any company of the host device which install this modular with Single modular approval should perform the test of radiated emission and spurious emission according to FCC part 15C : 15.247 requirement, Only if the test result comply with FCC part 15C : 15.247 requirement, then the host can be sold legally.

IC statement

This device complies with Industry Canada's licence-exempt RSSs. Operation is subject to the following two conditions:

- (1) This device may not cause interference; and

- (2) This device must accept any interference, including interference that may cause undesired operation of the device.

Cet appareil est conforme aux CNR exemptes de licence d'Industrie Canada . Son fonctionnement est soumis aux deux conditions suivantes :

- ( 1 ) Ce dispositif ne peut causer d'interférences ; etc

- ( 2 ) Ce dispositif doit accepter toute interférence , y compris les interférences qui peuvent causer un mauvais fonctionnement de l'appareil.

A separation distance of at least 20 cm is maintained between the transmitter's radiating structure(s) and the body of the user or nearby persons.

Une distance de séparation d'au moins 20 cm est maintenue entre l'émetteur rayonnant structure (s) et le corps de l'utilisateur ou des personnes à proximité.

For a host manufacturer's using a certified modular, if (1) the module's IC number is not visible when installed in the host, or (2) if the host is marketed so that end users do not have straightforward commonly used methods for access to remove the module so that the IC number of the module is visible; then an additional permanent label referring to the enclosed module: "Contains Transmitter Module IC: " 23768-0037" or "Contains IC: 23768-0037" must be used.