# **FSC-BW121**

**Bluetooth 5.3 +WLAN 802.11 a/b/g/n/ac Module Datasheet**

**Version 1.9**

## Copyright © 2013-2023 Feasycom Technology. All Rights Reserved.

Feasycom Technology reserves the right to make corrections, modifications, and other changes to its products, documentation and services at anytime. Customers should obtain the newest relevant information before placing orders. To minimize customer product risks, customers should provide adequate design and operating safeguards. Without written permission from Feasycom Technology, reproduction, transfer, distribution or storage of part or all of the contents in this document in any form is prohibited.

## Revision History

| Version | Data       | Notes                                                                                                                                                                                                                                        |            |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.0     | 2019/02/20 | Initial Version                                                                                                                                                                                                                              | Devin Wan  |

| 1.1     | 2019/04/28 | 1, Correction module and package image<br>2, The Notice about the stencil making<br>3, Add solder mask slivers next to the locating hole of the shield to prevent soldering tin from diffusing to the bonding pad on the back of the module. | Devin Wan  |

| 1.2     | 2020/03/14 | Modify Bluetooth Features:<br>Require external MCU to execute Bluetooth protocol stack                                                                                                                                                       | Devin Wan  |

| 1.3     | 2020/06/17 | Modify the description and update the application circuit diagram<br>(SDIO CLK line adds 5.6pF capacitor to ground)                                                                                                                          | Devin Wan  |

| 1.4     | 2020/07/21 | Selection of version                                                                                                                                                                                                                         | Devin Wan  |

| 1.5     | 2020/12/03 | Update selection of version                                                                                                                                                                                                                  | Devin Wan  |

| 1.6     | 2021/08/19 | Add BW121D                                                                                                                                                                                                                                   | Marsh Chen |

| 1.7     | 2022/02/25 | Update sequence diagram and modify some wrong descriptions                                                                                                                                                                                   | Devin Wan  |

| 1.8     | 2022/05/24 | Added dual antenna version, model FSC-BW121E,<br>hardware version is V1.2                                                                                                                                                                    | Devin Wan  |

| 1.8.1   | 2022/09/20 | Updated Bluetooth version to V5.0, Recommended antenna and IPEX                                                                                                                                                                              | Devin Wan  |

| 1.8.2   | 2023/02/24 | Add BW121EA, BW121EB, BW121EC                                                                                                                                                                                                                | Devin Wan  |

| 1.9     | 2023/03/29 | Update Bluetooth version to 5.3                                                                                                                                                                                                              | Devin Wan  |

## Contact Us

Shenzhen Feasycom Co.,Ltd

Email: sales@feasycom.com

Address: Rm 508, Building A, Fenghuang Zhigu, No.50, Tiezai Road, Xixiang, Baoan District, Shenzhen, 518102, China.

Tel: 86-755-27924639

## Contents

|                                                          |           |

|----------------------------------------------------------|-----------|

| <b>1. INTRODUCTION .....</b>                             | <b>5</b>  |

| 1.1 SELECTION OF VERSION .....                           | 8         |

| <b>2. GENERAL SPECIFICATION .....</b>                    | <b>10</b> |

| <b>3. HARDWARE SPECIFICATION .....</b>                   | <b>10</b> |

| 3.1 BLOCK DIAGRAM AND PIN DIAGRAM .....                  | 10        |

| 3.2 PIN DEFINITION DESCRIPTIONS .....                    | 11        |

| <b>4. PHYSICAL INTERFACE .....</b>                       | <b>13</b> |

| 4.1 UART INTERFACE .....                                 | 13        |

| 4.2 BLUETOOTH PCM INTERFACE .....                        | 15        |

| 4.3 I2S INTERFACES .....                                 | 17        |

| 4.4 WLAN Host INTERFACES .....                           | 19        |

| 4.4.1 SDIO V3.0 .....                                    | 19        |

| 4.4.2 SDIO Default Mode Timing .....                     | 20        |

| 4.4.3 SDIO High-Speed Mode Timing .....                  | 21        |

| 4.4.4 SDIO Bus Timing Specifications in SDR Modes .....  | 22        |

| 4.4.5 Device Input Timing .....                          | 23        |

| 4.4.6 Device Output Timing .....                         | 23        |

| 4.4.7 SDIO Bus Timing Specifications in DDR50 Mode ..... | 25        |

| <b>5. ELECTRICAL CHARACTERISTICS .....</b>               | <b>26</b> |

| 5.1 ABSOLUTE MAXIMUM RATINGS .....                       | 26        |

| 5.2 RECOMMENDED OPERATING CONDITIONS .....               | 26        |

| 5.3 RF CHARACTERISTIC .....                              | 错误!未定义书签。 |

| 5.3.1 WLAN RF Characteristics(Transmitter) .....         | 错误!未定义书签。 |

| 5.3.2 WLAN RF Characteristics(Receive) .....             | 错误!未定义书签。 |

| 5.3.3 Bluetooth RF Characteristics .....                 | 错误!未定义书签。 |

| 5.4 SYSTEM POWER SEQUENCE .....                          | 27        |

| 5.4.1 System Power On Sequence .....                     | 27        |

| 5.4.2 SDIO Reset Sequence .....                          | 29        |

| 5.4.3 WLAN and G-SPI Reset Sequence .....                | 29        |

| 5.4.4 Power Off Sequence .....                           | 30        |

| 5.4.5 WLAN Radio On/Off Sequence .....                   | 31        |

| 5.4.6 BT Power On/Off Sequence .....                     | 32        |

| 5.4.7 Power Reset Sequence .....                         | 33        |

| 5.5 POWER CONSUMPTION .....                              | 33        |

| <b>6. MSL &amp; ESD .....</b>                            | <b>34</b> |

| <b>7. RECOMMENDED TEMPERATURE REFLOW PROFILE .....</b>   | <b>34</b> |

| <b>8. MECHANICAL DETAILS .....</b>                       | <b>35</b> |

| 8.1 MECHANICAL DETAILS .....                             | 35        |

|                                                                  |           |

|------------------------------------------------------------------|-----------|

| <b>9. HARDWARE INTEGRATION SUGGESTIONS .....</b>                 | <b>36</b> |

| 9.1 SOLDERING RECOMMENDATIONS .....                              | 36        |

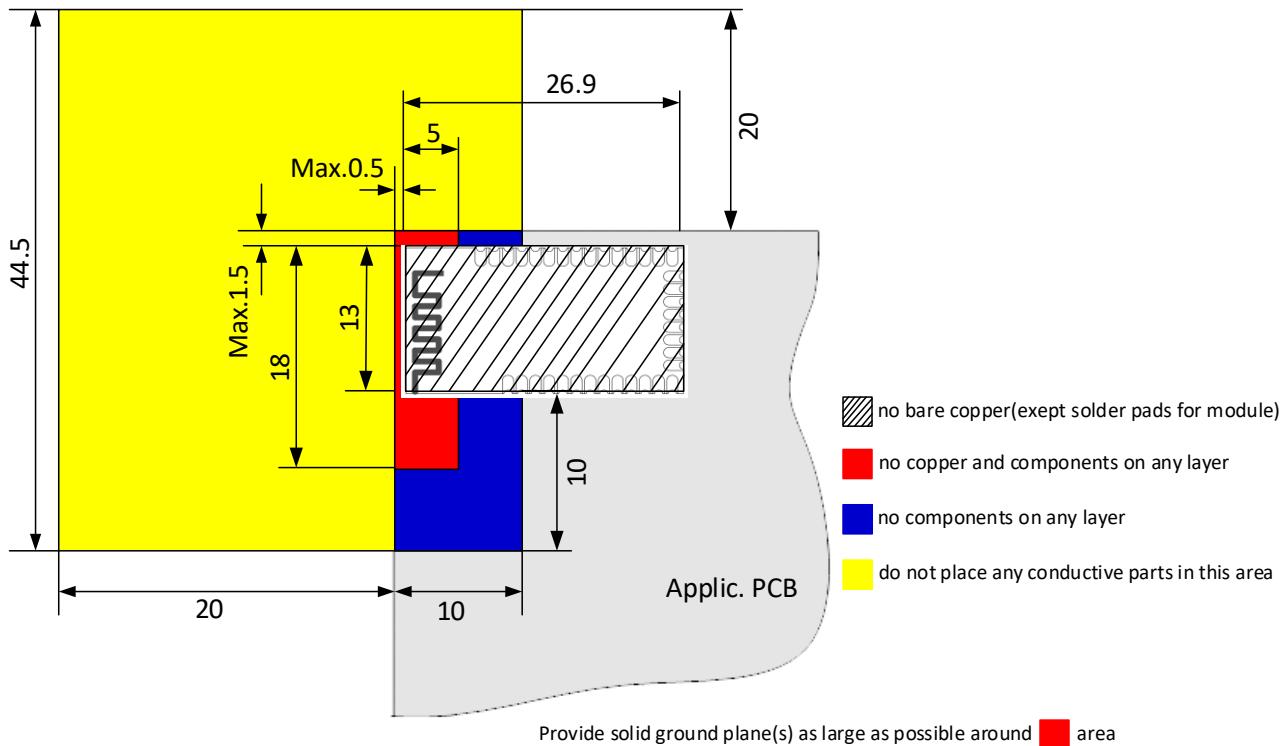

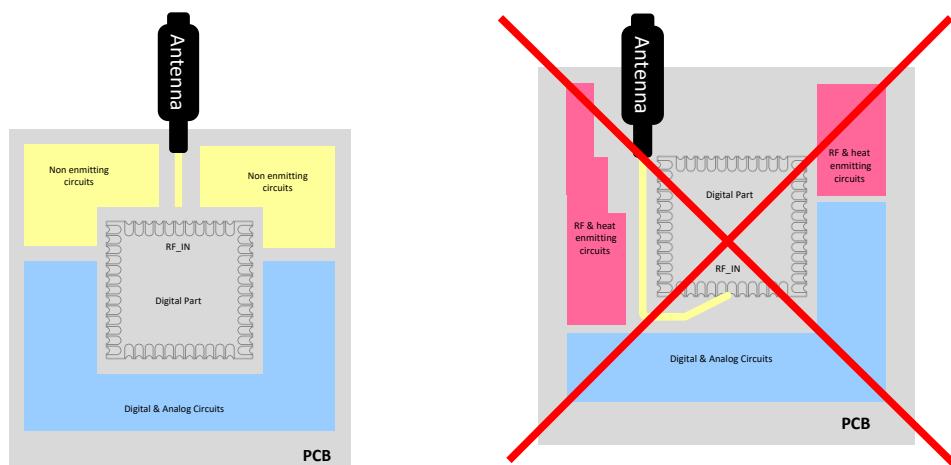

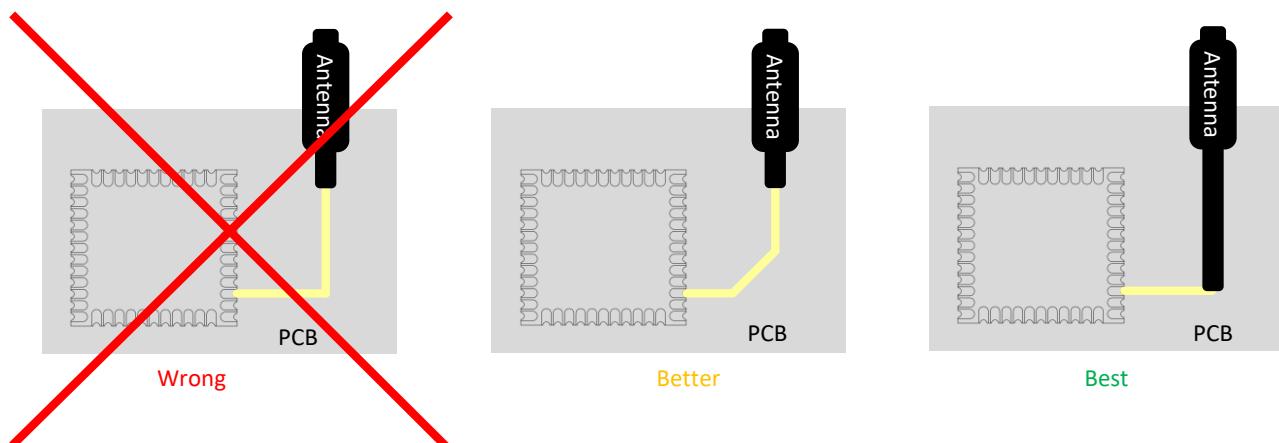

| 9.2 LAYOUT GUIDELINES(INTERNAL ANTENNA).....                     | 36        |

| 9.3 LAYOUT GUIDELINES(EXTERNAL ANTENNA).....                     | 37        |

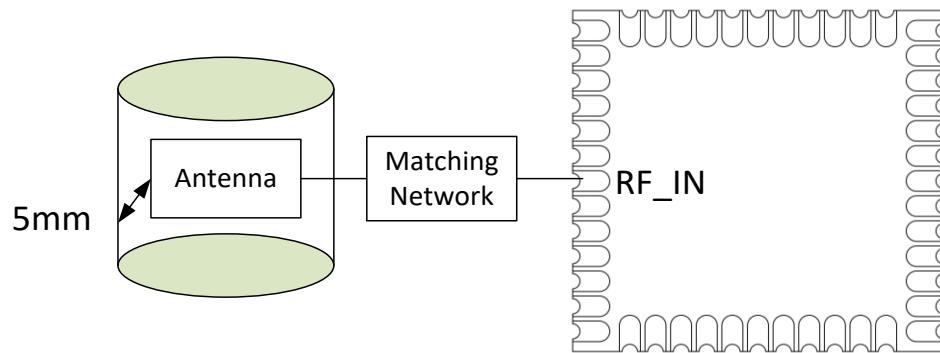

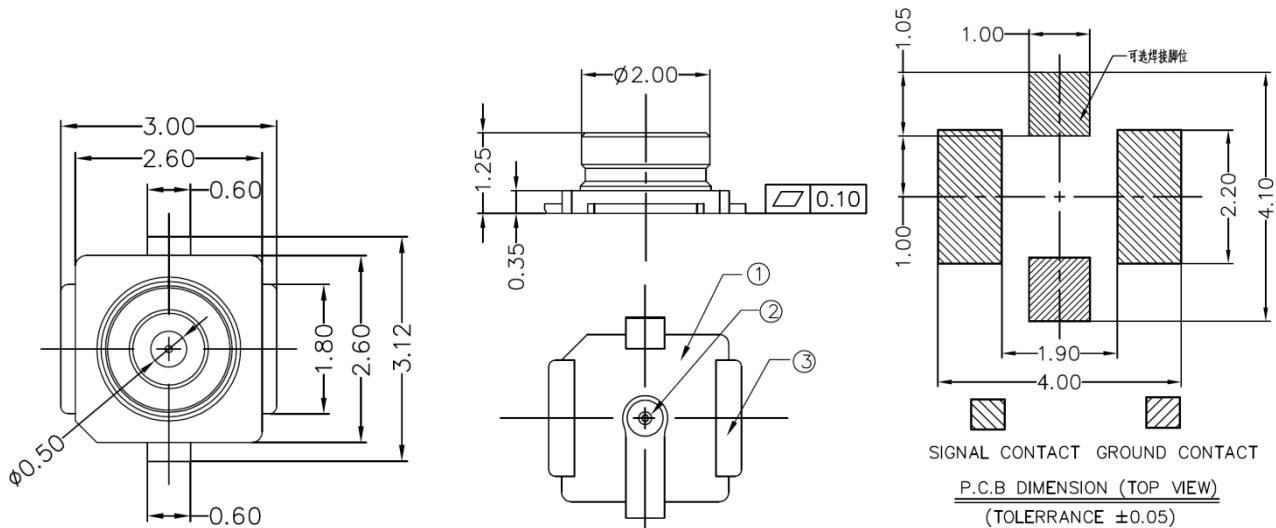

| 9.3.1 <i>Antenna Connection and Grounding Plane Design</i> ..... | 38        |

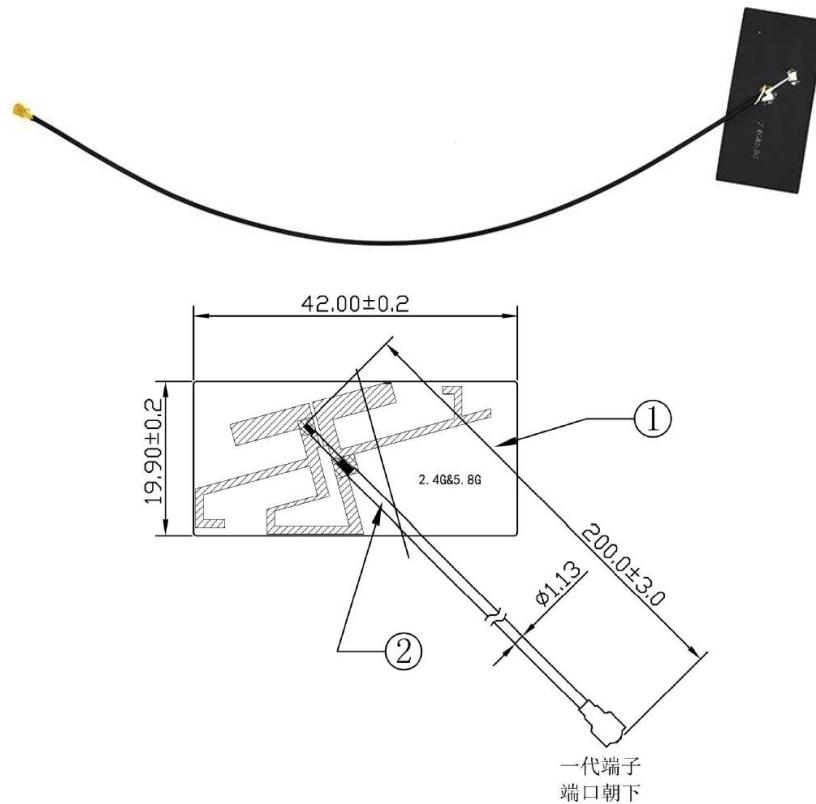

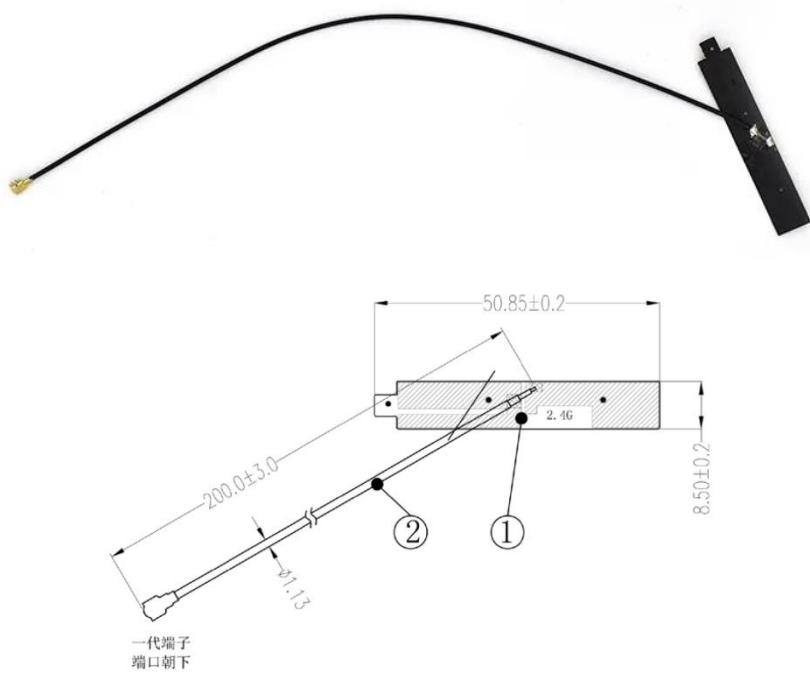

| 9.3.2 <i>Recommendable antenna &amp; IPEX by Feasycom</i> .....  | 39        |

| 9.4 SDIO LINES LAYOUT GUIDELINE.....                             | 41        |

| 9.5 HCI LINES LAYOUT GUIDELINE .....                             | 41        |

| 9.6 PCM LINES LAYOUT GUIDELINE .....                             | 41        |

| 9.7 RTC CLOCK(32.768kHz) LINES LAYOUT GUIDELINE.....             | 41        |

| 9.8 POWER TRACE LINES LAYOUT GUIDELINE .....                     | 41        |

| 9.9 GROUND LINES LAYOUT GUIDELINE .....                          | 42        |

| <b>10. PRODUCT PACKAGING INFORMATION.....</b>                    | <b>42</b> |

| 10.1 DEFAULT PACKING .....                                       | 42        |

| 10.2 PACKING BOX(OPTIONAL) .....                                 | 43        |

| <b>11. APPLICATION SCHEMATIC.....</b>                            | <b>44</b> |

## 1. INTRODUCTION

### Overview

FSC-BW121 is a Wi-Fi / Bluetooth combo module that support 1-stream 802.11ac solutions with Multi-user MIMO (Multiple-Input, Multiple-Output) STA mode with integrated Bluetooth Smart Ready controller, SDIO (SDIO 1.1/2.0/3.0) interface, and HS-UART mixed interface. It combines a WLAN MAC, a 1T1R capable WLAN baseband, and RF in a single chip. It provides a complete solution for a high-performance integrated wireless and Bluetooth device.

For legacy compatibility, Direct Sequence Spread Spectrum (DSSS), Complementary Code Keying (CCK) and OFDM baseband processing are included to support all IEEE 802.11b, 802.11g and 802.11a data rates. Differential phase shift keying modulation schemes, DBPSK and DQPSK with data scrambling capability are available, and CCK provides support for legacy data rates, with long or short preamble. The high speed FFT/IFFT paths, combined with BPSK, QPSK, 16QAM, 64QAM and 256QAM modulation of the individual subcarriers, and rate compatible coding rate of 1/2, 2/3, 3/4, and 5/6, provide up to 433.3Mbps for IEEE 802.11ac MIMO OFDM.

FSC-BW121 builds in an enhanced signal detector, an adaptive frequency domain equalizer, and a soft-decision Viterbi decoder to alleviate severe multi-path effects and mutual interference in the reception of multiple streams. Robust interference detection and suppression are provided to protect against Bluetooth, cordless phone, and microwave oven interference.

FSC-BW121 supports fast receiver Automatic Gain Control (AGC) with synchronous and asynchronous control loops among antennas, antenna diversity functions, and adaptive transmit power control functions to obtain better performance in the analog portions of the transceiver.

FSC-BW121 MAC supports 802.11e for multimedia applications, 802.11i and WAPI (Wireless Authentication Privacy Infrastructure) for security, and 802.11n/802.11ac for enhanced MAC protocol efficiency. Using packet aggregation techniques such as A-MPDU with BA and A-MSDU, protocol efficiency is significantly improved. Power saving mechanisms such as Legacy Power Save, U-APSD, and MIMO power saving reduce the power wasted during idle time, and compensate for the extra power required to transmit MIMO OFDM. FSC-BW121 provides simple legacy, 20MHz/40MHz/80MHz co-existence mechanisms to

ensure backward and network compatibility.

FSC-BW121 Bluetooth controller complies with Bluetooth core specification v5.3, and supports dual mode (BR/EDR + Low Energy Controllers). It is compatible with previous versions, including v2.1 + EDR. For BR/EDR, it supports scatternet topology and allows active links in slave mode, and active links in master mode. For Low Energy, it supports multiple states and allows active links in master mode. The links in BR/EDR and LE can be active simultaneously.

### General Features

- CMOS MAC, Baseband PHY and RF in a single chip for IEEE 802.11a/b/g/n/ac compatible WLAN

- Support 802.11ac 1x1, Wave-2 compliant with MU-MIMO STA mode

- Complete 802.11n MIMO solution for 2.4GHz and 5Ghz band

### Host Interface

- Complies with SDIO 1.1/2.0/3.0 for WLAN with clock rate up to 100MHz (SDR50 and DDR50)

### Standards Supported

- IEEE 802.11a/b/g/n/ac compatible WLAN

- IEEE 802.11e QoS Enhancement (WMM)

- IEEE 802.11i (WPA, WPA2). Open, shared key, and pair-wise key authentication services

- IEEE 802.11h DFS, TPC, Spectrum Measurement

### MAC Features

- Frame aggregation for increased MAC efficiency (A-MSDU, A-MPDU)

- Low latency immediate Block Acknowledgement (BA)

- Long NAV for media reservation with CF-End for NAV release

- Maximum PHY data rate up to 86.7Mbps using

- 20MHz bandwidth, 200Mbps using 40MHz bandwidth, and 433.3Mbps using 80MHz bandwidth.

- Backward compatible with 802.11a/b/g devices while operating at 802.11n data rates

- Backward compatible with 802.11a/n devices while operating at 802.11ac data rates.

- G-SPI interface for configurable endian for WLAN

- Complies with HS-UART with configurable baud rate for Bluetooth

- IEEE 802.11k Radio Resource Measurement

- WAPI (Wireless Authentication Privacy Infrastructure) certified.

- Cisco Compatible Extensions (CCX) for WLAN devices

- PHY-level spoofing to enhance legacy compatibility

- MIMO power saving mechanism

- Channel management and co-existence

- PHY-level spoofing to enhance legacy compatibility

- MIMO power saving mechanism

- Channel management and co-existence

- Multiple BSSID feature allows the BW121 to assume multiple MAC identities when used as a wireless bridge

- Transmit Opportunity (TXOP) Short Inter-Frame Space (SIFS) bursting for higher multimedia bandwidth

- WiFi Direct supports wireless peer to peer applications

## Other Features

- Supports Wake-On-WLAN via Magic Packet and Wake-up frame

- Transmit Beam forming

## PHY Features

- IEEE 802.11ac OFDM

- IEEE 802.11n OFDM

- One Transmit and One Receive path

- 5MHz / 10MHz / 20MHz / 40MHz / 80MHz bandwidth transmission

- Support 2.4Ghz and 5Ghz band channels

- Short Guard Interval (400ns)

- Sounding packet.

- DSSS with DBPSK and DQPSK, CCK modulation with long and short preamble

- OFDM with BPSK, QPSK, 16QAM, 64QAM and 256QAM modulation. Convolutional Coding Rate: 1/2, 2/3, 3/4, and 5/6

- WiFi NAN (Neighborhood Area Network) support

- WiFi FTM (Fine Time Measurement) supported

- WiFi TDLS (Tunneled Direct Link Setup) Supported

- CCA on secondary through RTS/CTS handshake.

- Support TCP/UDP/IP checksum offload

- Generates 40MHz clock for peripheral chip.

- Single external power source 3.3V only

- Maximum data rate 54Mbps in 802.11g, 150Mbps in 802.11n and 433Mbps in 802.11ac.

- Switch diversity used for DSSS/CCK

- Support STBC receiving

- Support LDPC transmitting

- Hardware antenna diversity

- Fast receiver Automatic Gain Control (AGC)

- On-chip ADC and DAC

- Build-in both 2.4GHz and 5GHz PA

- Build-in both 2.4GHz and 5GHz LNA

## Bluetooth Features

- Bluetooth 5.3 , Support Simultaneous LE & BR/EDR ,and High Duty Cycle Non-Connectable Advertising

- HS-UART interface for Bluetooth data transmission compliant with H4 and H5 specification

- PCM interface for audio data transmission via Bluetooth controller

- Require external MCU to execute Bluetooth protocol stack

- Supports all packet types in basic rate and enhanced data rate

## Bluetooth Transceiver

- Fast AGC control to improve receiving dynamic range

- Integrated internal Class 1, Class 2, and Class 3 PA

- Supports Enhanced Power Control

## Peripheral Interfaces

- Supports SCO/eSCO link (allows one link for PCM interface and three links for HS-UART)

- Supports Secure Simple Pairing

- Enhanced BT/WLAN Coexistence Control to improve transmission quality in different profiles

- Supports multiple Low Energy states

- Supports Bluetooth Low Energy

- Integrated 32K oscillator for power management

## Application

- Internet-of-Things (IoT) Applications, including:

- Home and Building Automation

- Low-Power Video Cameras

- Thermostats

- Access Control and Electronic Locks (E-Locks)

- Asset Tracking and Real Time Location System (RTLS) Tags

- Cloud Connectivity

- Internet Gateway

- Appliances

- Security Systems

- Smart Energy

- Industrial Control

- Smart Plug and Metering

- Wireless Audio

- IP Network Sensor Nodes

- Medical Devices

- Car audio and video system

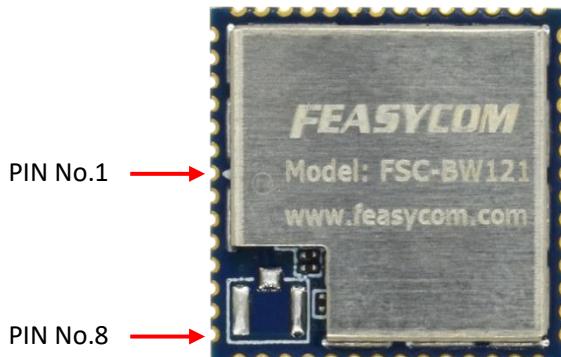

## Module picture as below showing

Figure 1: FSC-BW121 Picture

## 1.1 Selection of version

| Order Number                                       | Descriptions |                 | Module picture as below showing                                                       |

|----------------------------------------------------|--------------|-----------------|---------------------------------------------------------------------------------------|

| FSC-BW121<br><b>(Default)</b><br>(-40°C ~+85°C)    | PIN No.1     | RF_IO_Wi-Fi /BT |    |

| FSC-BW121B<br><b>(Optional)</b><br>(-40°C ~+85°C)  | PIN No.1     | NC              |   |

| FSC-BW121C<br><b>(Optional)</b><br>(-40°C ~+85°C)  | PIN No.1     | NC              |  |

| FSC-BW121D<br><b>(Optional)</b><br>(-20°C ~+70°C)  | PIN No.1     | RF_IO_Wi-Fi/BT  |  |

| FSC-BW121DI<br><b>(Optional)</b><br>(-20°C ~+70°C) | PIN No.1     | NC              |  |

|                                                       |                                                                                   |                        |

|-------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------|

| FSC-BW121E<br><br><b>(Optional)</b><br>(-40°C ~+85°C) | PIN No.1                                                                          | 2.4GHz Wi-Fi           |

|                                                       | PIN No.45                                                                         | 2.4GHz BT + 5GHz Wi-Fi |

|                                                       | 1, Two external antennas must be soldered<br>(stamp hole, PIN No.1 and PIN No.45) |                        |

|                                                       | 2, PCB hardware version is V1.2                                                   |                        |

|                                                        |                                                                      |                        |

|--------------------------------------------------------|----------------------------------------------------------------------|------------------------|

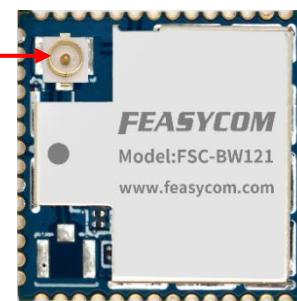

| FSC-BW121EA<br><br><b>(Optional)</b><br>(-40°C ~+85°C) | PIN No.1                                                             | NC                     |

|                                                        | PIN No.45                                                            | 2.4GHz BT + 5GHz Wi-Fi |

|                                                        | 1, Position 1, External antenna (IPEX connector):<br>2.4GHz Wi-Fi    |                        |

|                                                        | 2, One external antennas must be soldered<br>(stamp hole, PIN No.45) |                        |

|                                                        | 3, PCB hardware version is V1.2                                      |                        |

Position 1

|                                                        |                                                                             |              |

|--------------------------------------------------------|-----------------------------------------------------------------------------|--------------|

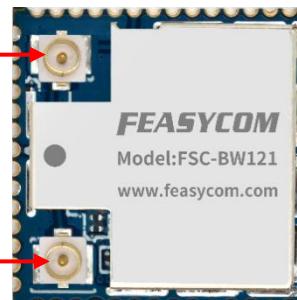

| FSC-BW121EB<br><br><b>(Optional)</b><br>(-40°C ~+85°C) | PIN No.1                                                                    | 2.4GHz Wi-Fi |

|                                                        | PIN No.45                                                                   | NC           |

|                                                        | 1, Position 2, External antenna (IPEX connector):<br>2.4GHz BT + 5GHz Wi-Fi |              |

|                                                        | 2, One external antennas must be soldered<br>(stamp hole, PIN No.1)         |              |

|                                                        | 3, PCB hardware version is V1.2                                             |              |

Position 2

|                                                        |                                                                             |    |

|--------------------------------------------------------|-----------------------------------------------------------------------------|----|

| FSC-BW121EC<br><br><b>(Optional)</b><br>(-40°C ~+85°C) | PIN No.1                                                                    | NC |

|                                                        | PIN No.45                                                                   | NC |

|                                                        | 1, Position 1, External antenna (IPEX connector):<br>2.4GHz Wi-Fi           |    |

|                                                        | 2, Position 2, External antenna (IPEX connector):<br>2.4GHz BT + 5GHz Wi-Fi |    |

|                                                        | 3, PCB hardware version is V1.2                                             |    |

Position 2

Position 1

■ See chapter 3.2 for details

## 2. General Specification

**Table 1:** General Specifications

| Categories            | Features                                                                                                                            | Implementation |                              |          |          |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------|----------|----------|--|

| <b>Bluetooth</b>      |                                                                                                                                     |                |                              |          |          |  |

| Bluetooth Standard    | Bluetooth V5.3 LE & BR/EDR                                                                                                          |                |                              |          |          |  |

| Frequency Band        | 2402MHz~2480MHz                                                                                                                     |                |                              |          |          |  |

| Interface             | UART/PCM                                                                                                                            |                |                              |          |          |  |

| <b>WIFI</b>           |                                                                                                                                     |                |                              |          |          |  |

| WiFi Standard         | 802.11 a/b/g/n/ac                                                                                                                   |                |                              |          |          |  |

| Frequency Band        | 2412MHz~2484MHz /4900MHz~5925MHz                                                                                                    |                |                              |          |          |  |

| Interface             | SDIO                                                                                                                                |                |                              |          |          |  |

| <b>General</b>        |                                                                                                                                     |                |                              |          |          |  |

| Size                  | 17mm × 17 mm × 2.4mm                                                                                                                |                |                              |          |          |  |

| Operating temperature | -40°C ~+85°C, -20°C ~+70°C(FSC-BW121D)                                                                                              |                |                              |          |          |  |

| Storage temperature   | -40°C ~+85°C                                                                                                                        |                |                              |          |          |  |

| VDD_3V3_WL            | 3.0V~3.6V                                                                                                                           |                |                              |          |          |  |

| VDD_IO                | 1.62V~3.6V                                                                                                                          |                |                              |          |          |  |

| Miscellaneous         | <table> <tr> <td>Lead Free</td> <td>Lead-free and RoHS compliant</td> </tr> <tr> <td>Warranty</td> <td>One Year</td> </tr> </table> | Lead Free      | Lead-free and RoHS compliant | Warranty | One Year |  |

| Lead Free             | Lead-free and RoHS compliant                                                                                                        |                |                              |          |          |  |

| Warranty              | One Year                                                                                                                            |                |                              |          |          |  |

| Humidity              | 10% ~ 90% non-condensing                                                                                                            |                |                              |          |          |  |

| MSL grade:            | MSL 3                                                                                                                               |                |                              |          |          |  |

| ESD grade:            | Human Body Model: Pass ±2000 V, all pins<br>Charge device model: Pass ±400 V, all pins                                              |                |                              |          |          |  |

## 3. HARDWARE SPECIFICATION

### 3.1 Block Diagram and PIN Diagram

Confidantiale

**Figure 2:** Block Diagram

Confidantiale

**Figure 3:** Block Diagram (Only FSC-BW121E/EA/EB/EC)

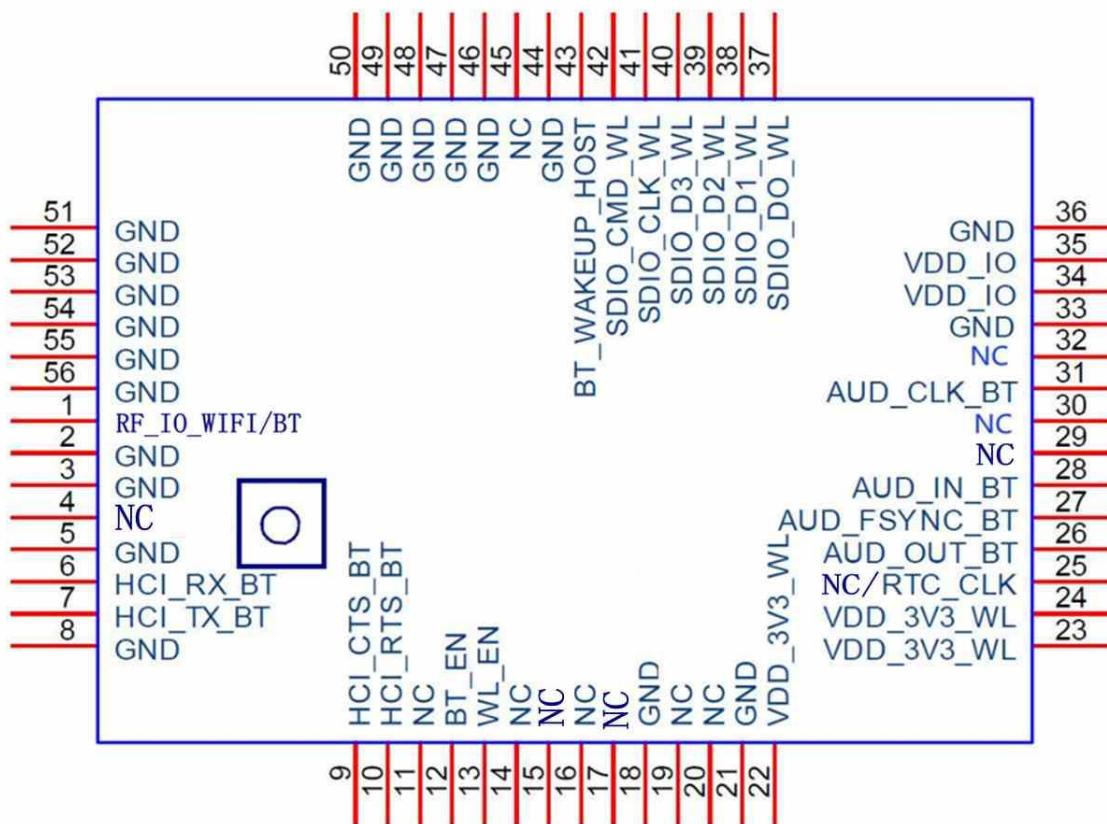

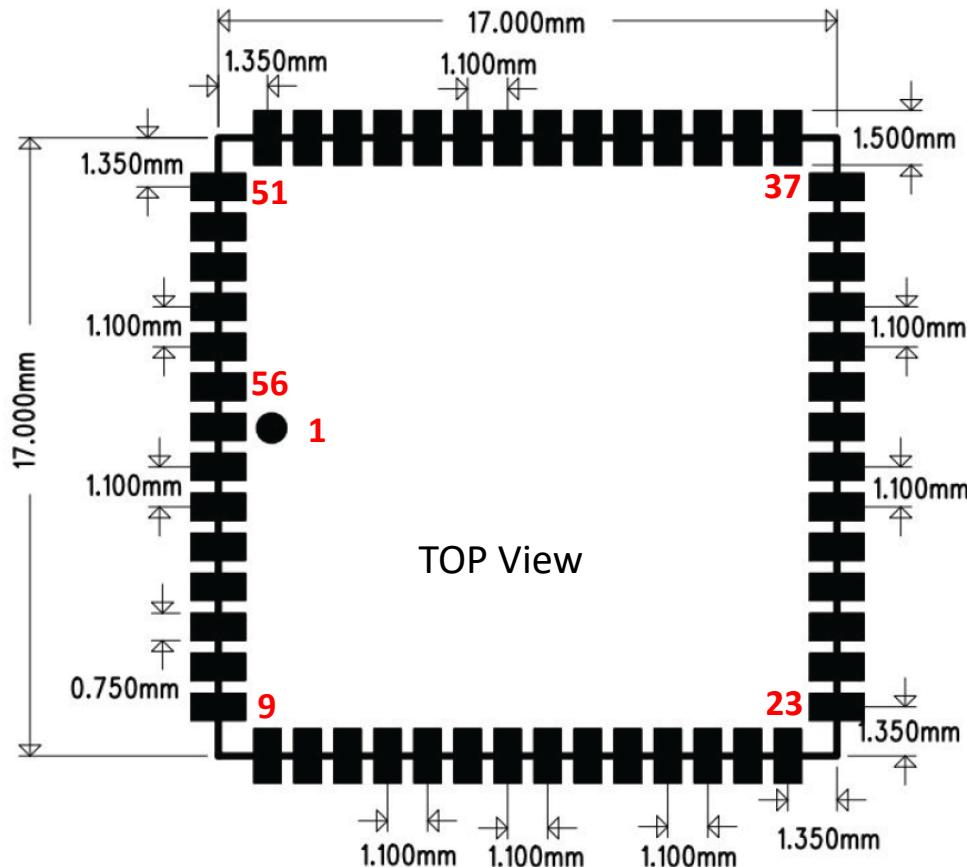

**Figure 4:** FSC-BW121 PIN Diagram (Top View)

## 3.2 PIN Definition Descriptions

**Table 2:** Pin definition

| Pin | Pin Name           | Type | Pin Descriptions                                                                                                                    | Notes |

|-----|--------------------|------|-------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1   | a. RF_IO_WIFI/BT   | RF   | a. WIFI 2.4G/5G RF and BT RF in/out port(FSC-BW121 and FSC-BW121D )<br><br>** <b>No function (FSC-BW121B and FSC-BW121C only, )</b> |       |

|     | b. RF_IO_2.4G WIFI |      | b. WIFI 2.4G RF in/out port(FSC-BW121E and FSC-BW121EB)                                                                             |       |

|     | c. NC              |      | c. No function (FSC-BW121EA and FSC-BW121EC)                                                                                        |       |

| 2   | GND                |      | Ground                                                                                                                              |       |

| 3   | GND                |      | Ground                                                                                                                              |       |

| 4   | NC                 |      |                                                                                                                                     |       |

| 5   | GND                |      | Ground                                                                                                                              |       |

| 6   | HCI_RX_BT          | I    | High-Speed UART Data In                                                                                                             |       |

| 7   | HCI_TX_BT          | O    | High-Speed UART Data Out                                                                                                            |       |

| 8   | GND                |      | Ground                                                                                                                              |       |

| 9   | HCI_CTS_BT         | I    | High-Speed UART CTS                                                                                                                 |       |

| 10  | HCI_RTS_BT         | O    | High-Speed UART RTS                                                                                                                 |       |

| 11  | NC                 |      |                                                                                                                                     |       |

|    |                                                                    |     |                                                                         |

|----|--------------------------------------------------------------------|-----|-------------------------------------------------------------------------|

| 12 | BT_EN                                                              | I   | Bluetooth Function Enable(High Active)(BT_Reset)                        |

| 13 | WL_EN                                                              | I   | Wi-Fi Function Enable(High Active) (Wi-Fi_Reset)                        |

| 14 | NC                                                                 |     |                                                                         |

| 15 | NC                                                                 |     |                                                                         |

| 16 | NC                                                                 |     |                                                                         |

| 17 | NC                                                                 |     |                                                                         |

| 18 | GND                                                                |     | Ground                                                                  |

| 19 | NC                                                                 |     |                                                                         |

| 20 | NC                                                                 |     |                                                                         |

| 21 | GND                                                                |     | Ground                                                                  |

| 22 | VDD_3V3_WL                                                         | PWR | 3.3V Supply Voltage                                                     |

| 23 | VDD_3V3_WL                                                         | PWR | 3.3V Supply Voltage                                                     |

| 24 | VDD_3V3_WL                                                         | PWR | 3.3V Supply Voltage                                                     |

| 25 | NC/RTC_CLK                                                         | I   | Sleep Clock(32.768kHz)                                                  |

|    | <i>By default, this pin is not connected and is left floating.</i> |     |                                                                         |

| 26 | AUD_OUT_BT                                                         | O   | BT PCM/I2S Bus. Data out ; NC if not used                               |

| 27 | AUD_FSYNC_BT                                                       | I   | BT PCM/I2S Bus. Frame sync ; NC if not used.                            |

| 28 | AUD_IN_BT                                                          | I   | BT PCM/I2S Bus. Data in ; NC if not used.                               |

| 29 | NC                                                                 |     |                                                                         |

| 30 | NC                                                                 |     |                                                                         |

| 31 | AUD_CLK_BT                                                         | I   | BT PCM/I2S Clock; NC if not used.                                       |

| 32 | NC                                                                 |     |                                                                         |

| 33 | GND                                                                |     | Ground                                                                  |

| 34 | VDD_IO                                                             | PWR | 1.8V~3.3V Supply Voltage                                                |

| 35 | VDD_IO                                                             | PWR | 1.8V~3.3V Supply Voltage                                                |

| 36 | GND                                                                |     | Ground                                                                  |

| 37 | SDIO_D0_WL                                                         | I/O | SDIO Data Line 0                                                        |

| 38 | SDIO_D1_WL                                                         | I/O | SDIO Data Line1                                                         |

| 39 | SDIO_D2_WL                                                         | I/O | SDIO Data Line 2                                                        |

| 40 | SDIO_D3_WL                                                         | I/O | SDIO Data Line 3                                                        |

| 41 | SDIO_CLK_WL                                                        | I   | WLAN SDIO Clock. Must be driven by the host                             |

| 42 | SDIO_CMD_WL                                                        | I   | SDIO Command Input                                                      |

| 43 | BT_WALEUP_HOST                                                     | O   | Host wakeup Bluetooth; NC if not used.                                  |

| 44 | GND                                                                |     | Ground                                                                  |

| 45 | a. NC                                                              | RF  | a. No function (FSC-BW121 and FSC-BW121C/D,FSC-BW121EB and FSC-BW121EC) |

|    | b. RF_IO_2.4G&5G                                                   |     | <b>** WIFI 2.4G/5G RF and BT RF in/out port (FSC-BW121B only)</b>       |

|    | WIFI                                                               |     | b. BT 2.4G/WIFI 5G RF in/out port(FSC-BW121E and FSC-BW121EA )          |

| 46 | GND                                                                |     | Ground                                                                  |

| 47 | GND                                                                |     | Ground                                                                  |

| 48 | GND                                                                |     | Ground                                                                  |

| 49 | GND                                                                |     | Ground                                                                  |

| 50 | GND                                                                |     | Ground                                                                  |

| 51 | GND                                                                |     | Ground                                                                  |

|    |     |        |

|----|-----|--------|

| 52 | GND | Ground |

| 53 | GND | Ground |

| 54 | GND | Ground |

| 55 | GND | Ground |

| 56 | GND | Ground |

## 4. PHYSICAL INTERFACE

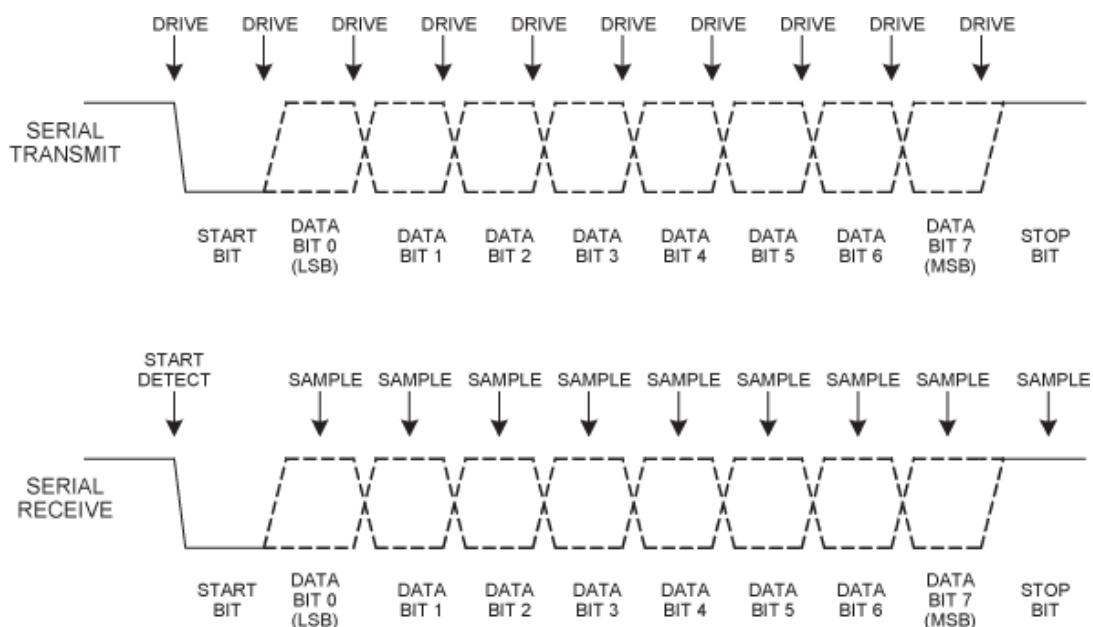

### 4.1 UART Interface

FSC-BW121 UART interface is a standard 4-wire interface with RX, TX, CTS, and RTS. The interface supports the Bluetooth UART HCI H4 and H5 specifications. The default baud rate is 115.2 kbaud. In order to support high and low speed baud rate, FSC-BW121 provides multiple UART clocks.

The UART signal level ranges from 1.8V to 3.3V. The host provides the power source with the targeted power level to the UART interface via the VIO\_HOST pin .

**Table 3:** Possible UART Settings

| Parameter           | Possible Values                                     |

|---------------------|-----------------------------------------------------|

| Baudrate            | Minimum 1200 baud ( $\leq 0\%$ Error)               |

|                     | Standard 115200bps( $\leq 0.08\%$ Error)            |

|                     | Maximum 4Mbps( $\leq 0\%$ Error)                    |

| Flow control        | Supports Automatic Flow Control (CTS and RTS lines) |

| Parity              | None, Odd or Even                                   |

| Number of stop bits | 1                                                   |

| Bits per channel    | 8                                                   |

**Figure 5:** UART Timing

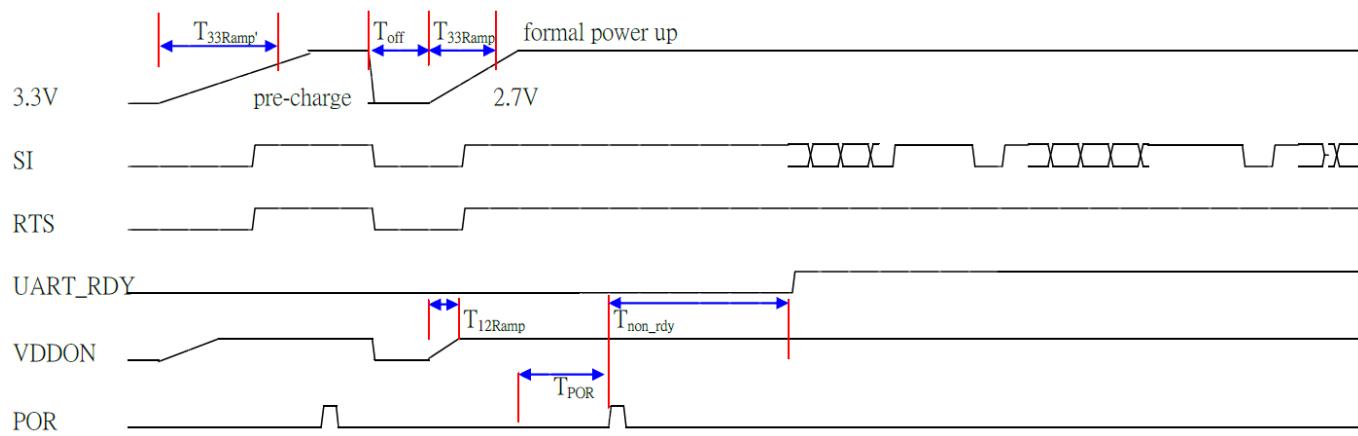

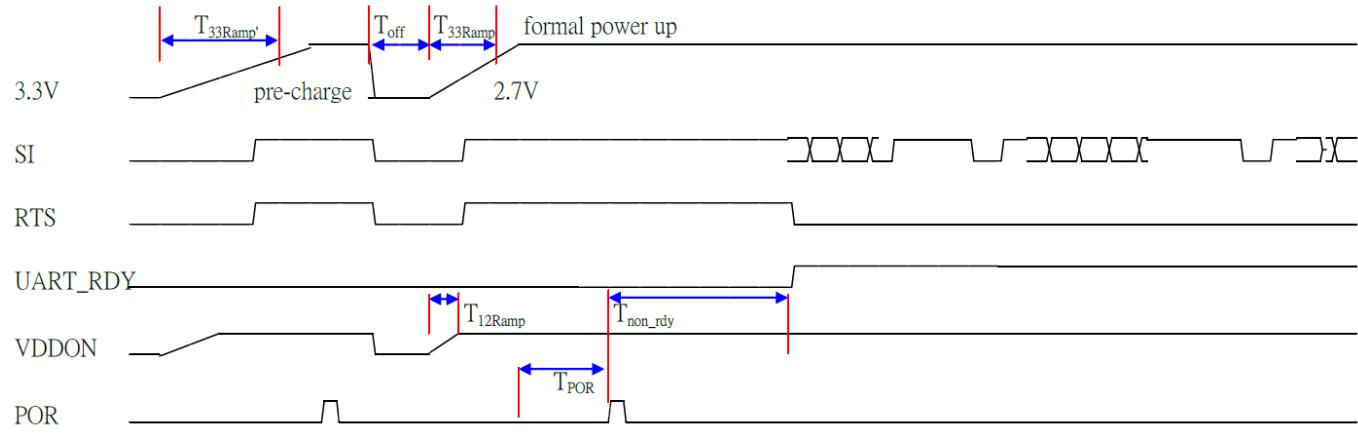

Figure 6: UART Power-On Sequence Without Hardware Flow Control

Figure 7: UART Power-On Sequence Without Hardware Flow Control

Table 4: UART Interface Power-On Sequence

| Symbol         | Description                                                                                                                                                                                                                                                                                                                                  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $T_{33ramp}$   | 3.3V Power Pre-Charge Ramp Up Duration Before Formal Power Up.<br>We recommend that a 3.3V power-on and then power-off sequence is executed by the host controller before the formal power on sequence. This procedure can eliminate host card detection issues when power ramp up duration is too long, or when a system warm reboot fails. |

| $T_{off}$      | The duration 3.3V is cut off before formal power up.                                                                                                                                                                                                                                                                                         |

| $T_{33ramp}$   | The 3.3V main power ramp up duration                                                                                                                                                                                                                                                                                                         |

| $T_{12ramp}$   | The internal 1.2V ramp up duration.                                                                                                                                                                                                                                                                                                          |

| $T_{POR}$      | The duration from when the power-on reset releases and the power management unit executes power on tasks. A power on reset will detect both 3.3V and 1.2V power ramp up after a predetermined duration.                                                                                                                                      |

| $T_{non\_rdy}$ | UART Not Ready Duration.<br>In this state, the FSC-BW121 will not respond to any commands.                                                                                                                                                                                                                                                   |

We recommend that the card detection procedures are divided into two phases: A 3.3V power pre-charge phase and a formal power-up phase.

During the 3.3V power pre-charge phase, the power ramp up duration is not limited. The 3.3V power is cut off and is turned on after the  $T_{off}$  period. The ramp up time is specified in the  $T_{33ramp}$  duration.

After main 3.3V ramp up and 1.2V ramp up, the power management unit is enabled by the power ready detection circuit. The power management unit enables the Bluetooth block. The Bluetooth firmware then initializes all circuits, included the UART. In addition to wait the  $T_{non\_rdy}$  time, if the host supports UART hardware flow control it can detect RTS signals and follow the formal UART flow control handshake.

**Table 5:** UART Interface Power On Timing Parameters

| Parameter     | Min | Type | Max      | Unit |

|---------------|-----|------|----------|------|

| $T_{33ramp}$  | -   | -    | No Limit | ms   |

| $T_{off}$     | 250 | 500  | 1000     | ms   |

| $T_{33ramp}$  | 0.1 | 0.5  | 2.5      | ms   |

| $T_{12ramp}$  | 0.1 | 0.5  | 1.5      | ms   |

| $T_{POR}$     | 2   | 2    | 8        | ms   |

| $T_{non\_rd}$ | 1   | 2    | 10       | ms   |

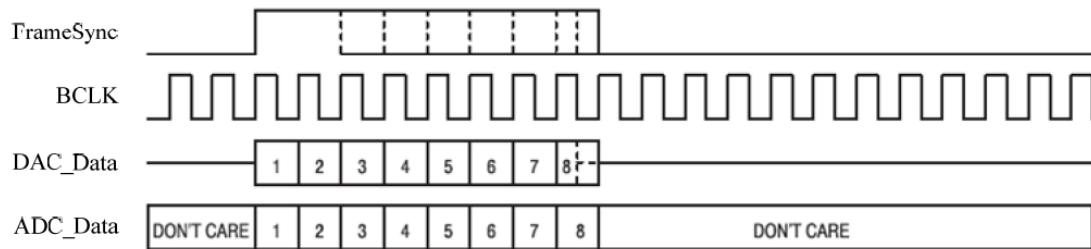

## 4.2 Bluetooth PCM Interface

FSC-BW121 supports a PCM digital audio interface that is used for transmitting digital audio/voice data to/from the Audio Codec. Features are supported as below:

- Supports Master and Slave mode

- Programmable long/short Frame Sync

- Supports 8-bit A-law/ $\mu$ -law, and 13/16-bit linear PCM formats

- Supports sign-extension and zero-padding for 8-bit and 13-bit samples

- Supports padding of Audio Gain to 13-bit samples

- PCM Master Clock Output: 64, 128, 256, or 512kHz

- Supports SCO/ESCO link

The PCM signal level ranges from 1.8V to 3.3V. The host provides the power source with the targeted power level to the PCM interface via the VDD-IO pin .

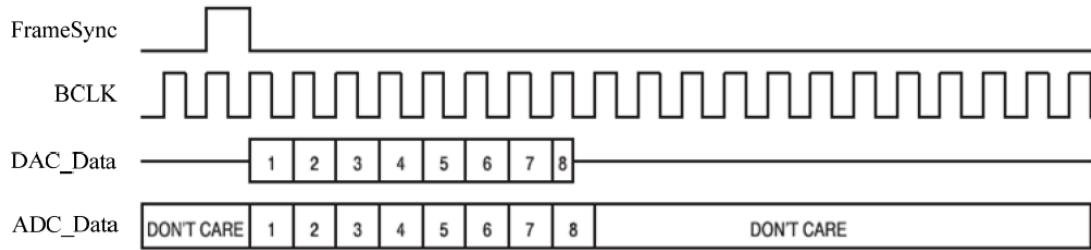

Figure 8: PCM Long FrameSync

Figure 9: PCM Short FrameSync

Figure 10: PCM interface timing (Long FrameSync)

Figure 11: PCM interface timing (Short FrameSync)

Table 6: PCM Interface Clock Specifications

| Parameter                        | Min | Type | Max | Unit  |

|----------------------------------|-----|------|-----|-------|

| Frequency of BCLK (Master)       | 64  | -    | 512 | KHz   |

| Frequency of Frame Sync (Master) | -   | 8    | -   | KHz   |

| Frequency of BCLK (Slave)        | 64  | -    | 512 | KHz   |

| Frequency of Frame Sync (Slave)  | -   | 8    | -   | KHz   |

| Data Size                        | 8   | 8    | 16  | KHz   |

| Number of Slots Per Frame        | 1   | 1    | 1   | Slots |

Table 7: PCM interface timing

| Parameter                                    | Min | Type | Max | Unit |

|----------------------------------------------|-----|------|-----|------|

| High Period of BCLK                          | 980 | -    | -   | ns   |

| Low Period of BCLK                           | 970 | -    | -   | ns   |

| Delay Time from BCLK High to Frame Sync High | -   | -    | 75  | ns   |

| Delay Time from BCLK High to Valid DAC_Data  | -   | -    | 125 | ns   |

| Set-up Time for ADC_Data Valid to BCLK Low   | 10  | -    | -   | ns   |

| Hold Time for BCLK Low to ADC_Data Invalid   | 125 | -    | -   | ns   |

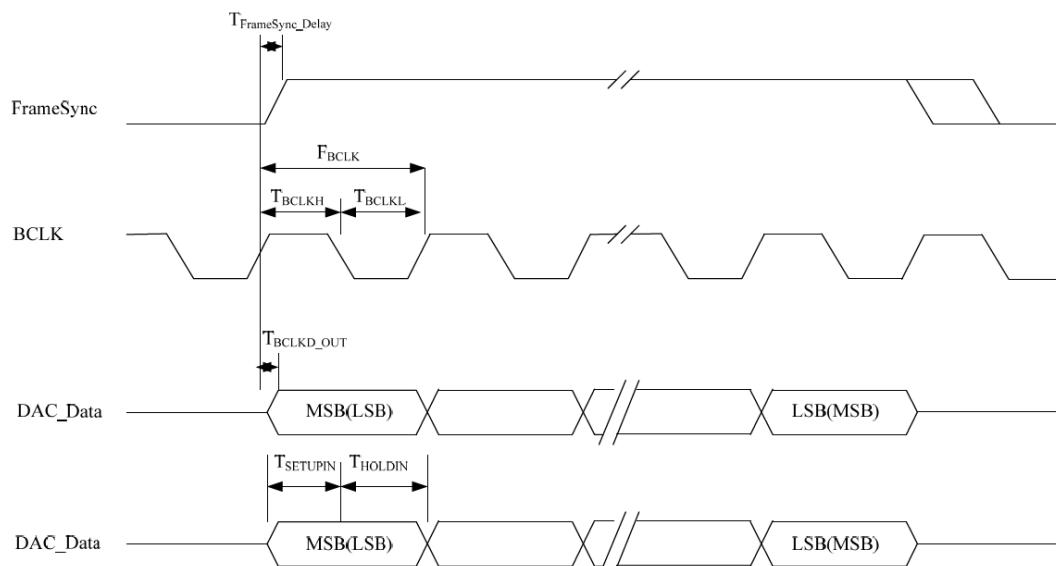

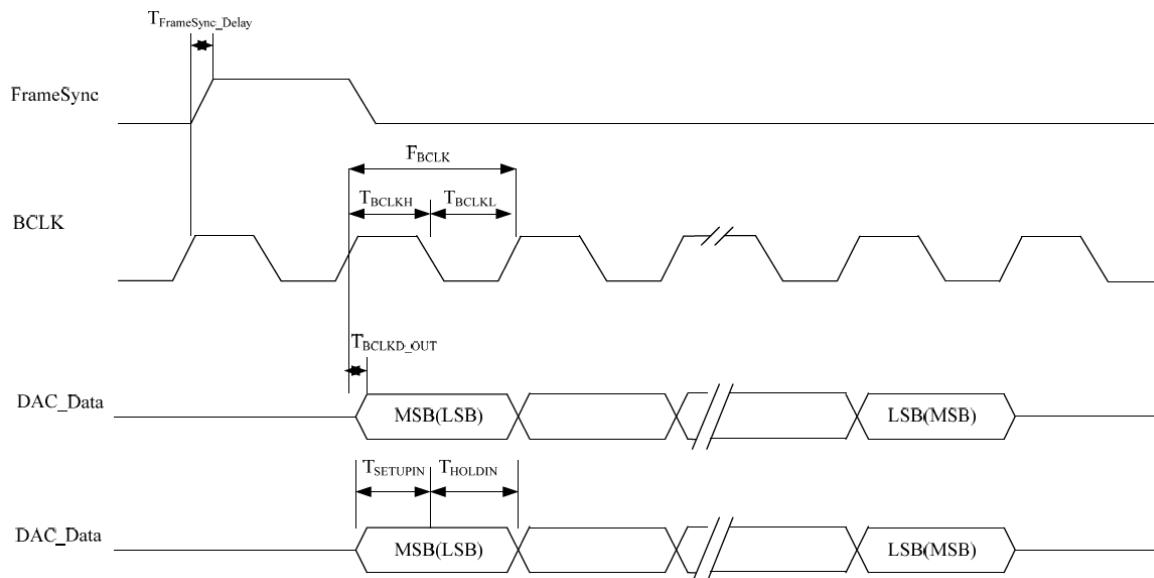

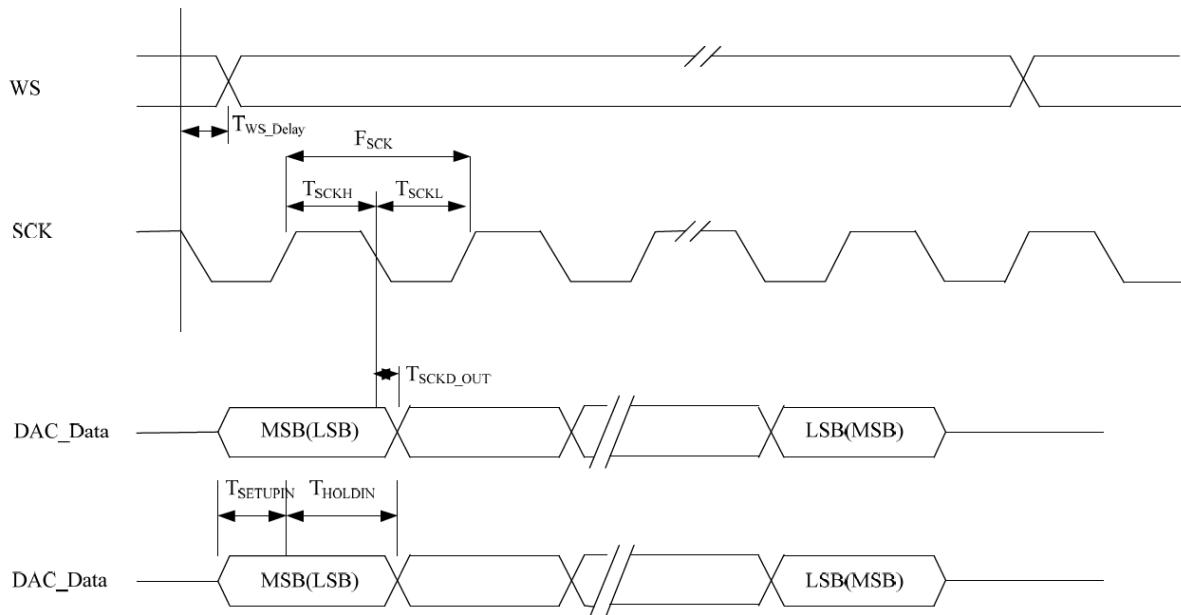

### 4.3 I2S Interfaces

FSC-BW121 supports I2S digital audio interface used for transmitting digital audio/voice data to/from Audio Codec. The Interface shares the same pins with PCM interface, but mutually exclusive in its stage. There are features supported by FSC-BW121:

- Support both Master and Slave mode

- Programmable MSB/LSB bit 1st SCK(Left-Justified) or 2nd SCK(I2S-Compatible) latch time

- Programmable SCK rising/falling edge trigger for latching data bits Support 8-bit a-Law/u-Law and 16-bit linear formats

- Support sign-extension and zero-padding for 8-bit and 13-bit samples

- Support padding of Audio Gain to 13-bit samples

- Programmable MSB/LSB first

- I2S Master clock output: 128/256kHz

- Support one SCO/ESCO link only

FSC-BW121 can be configured as either master or slave mode. As master mode, the FSC-BW121 generate SCK and WS, thus controls the data transfer over DAC\_Data and ADC\_Data. FSC-BW121 supports audio sampling rate 8kHz(FrameSync), depends on I2S data format. The clock output(SCK) will be up to 256kHz.

In slave mode, FSC-BW121 responds with DAC\_Data and ADC\_Data to SCK and WS it receives from Audio Codec. FSC-BW121 can receive audio sampling rate 8kHz(WS), depends on I2S data format. The clock input(BCLK) accepted will be up to 256kHz.

FSC-BW121 supports audio sampling rate 8kHz(WS), depends on the I2S data format, in Master mode the clock output(SCK) will be 128, 256kHz.

**Table 8:** I2S Interface Clock Specifications

| Parameter                      | Min | Type | Max | Unit  |

|--------------------------------|-----|------|-----|-------|

| Frequency of SCK (Master)      | 128 | -    | 256 | KHz   |

| Frequency of Frame WS (Master) | -   | 8    | -   | KHz   |

| Frequency of SCK (Slave)       | 128 | -    | 256 | KHz   |

| Frequency of Frame WS (Slave)  | -   | 8    | -   | KHz   |

| Data Size                      | 8   | 8    | 16  | KHz   |

| Number of Slots Per Frame      | 1   | 1    | 1   | Slots |

**Table 9:** I2S interface timing

| Parameter                                     | Min  | Type | Max | Unit |

|-----------------------------------------------|------|------|-----|------|

| High Period of SCK                            | 1960 | -    | -   | ns   |

| Low Period of SCK                             | 1950 | -    | -   | ns   |

| Delay time from SCK falling to WS high/low    | -    | -    | 75  | ns   |

| Delay time from SCK falling to valid DAC_Data | -    | -    | 125 | ns   |

| Set-up time for ADC_Data valid to SCK rising  | 10   | -    | -   | ns   |

| Hold time for SCK rising to ADC_Data invalid  | 125  | -    | -   | ns   |

Figure 12: I2S interface timing

## 4.4 WLAN Host Interfaces

### 4.4.1 SDIO V3.0

The module WLAN section supports SDIO version 3.0, including the new UHS-I modes:

- DS: Default speed (DS) up to 25 MHz, including 1- and 4-bit modes (3.3V signaling).

- HS: High speed up to 50 MHz (3.3V signaling).

- SDR12: SDR up to 25 MHz (1.8V signaling).

- SDR25: SDR up to 50 MHz (1.8V signaling).

- SDR50: SDR up to 100 MHz (1.8V signaling).

- SDR104: SDR up to 208 MHz (1.8V signaling).

- DDR50: DDR up to 50 MHz (1.8V signaling).

**Note:** The FSC-BW121 is backward compatible with SDIO v2.0 host interfaces.

The SDIO interface also has the ability to map the interrupt signal on to a GPIO pin for applications requiring an interrupt different from the one provided by the SDIO interface. The ability to force control of the gated clocks from within the device is also provided.

SDIO mode is enabled by strapping options. Refer to next Table WLAN GPIO Functions and Strapping Options.

The following three functions are supported:

- Function 0 Standard SDIO function (Max. BlockSize/ByteCount = 32B)

- Function 1 Backplane Function to access the internal system-on-chip (SoC) address space (Max.

BlockSize/ByteCount = 64B)

- Function 2 WLAN Function for efficient

**Table 10:** SDIO Pin Description

| SD 4-Bit Mode |                          |

|---------------|--------------------------|

| DATA0         | Data line 0              |

| DATA1         | Data line 1 or Interrupt |

| DATA2         | Data line 2 or Read Wait |

| DATA3         | Data line 3              |

| CLK           | Clock                    |

| CMD           | Command line             |

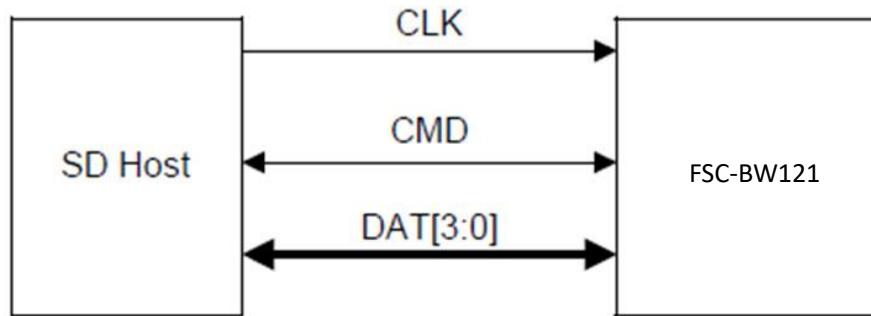

**Figure 13:** Signal Connections to SDIO Host (SD 4-Bit Mode)

#### 4.4.2 SDIO Default Mode Timing

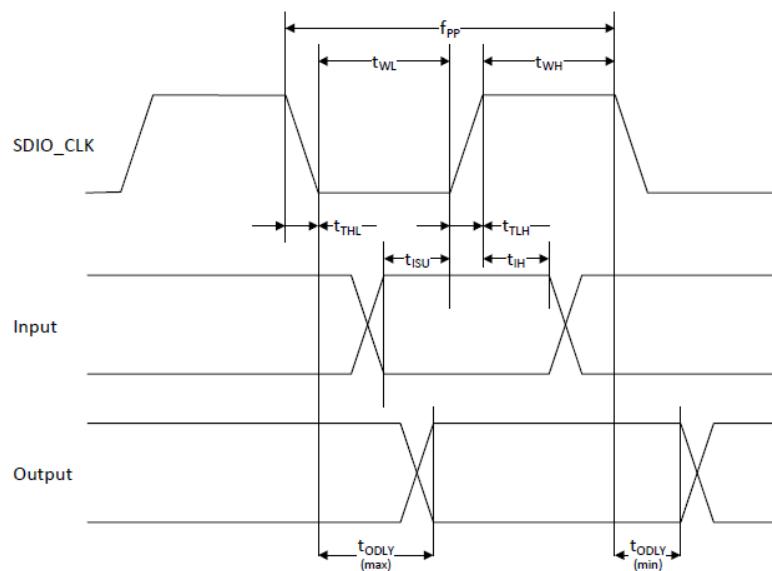

**Figure 14:** SDIO Bus Timing (Default Mode)

**Table 11: SDIO Bus Timing<sup>a</sup> Parameters (Default Mode)**

| Parameter                                                                            | Min | Type | Max | Unit |

|--------------------------------------------------------------------------------------|-----|------|-----|------|

| <b>SDIO CLK (All values are referred to minimum VIH and maximum Vil<sup>b</sup>)</b> |     |      |     |      |

| Frequency – Data Transfer mode                                                       | 0   | -    | 25  | MHz  |

| Frequency – Identification mode                                                      | 0   | -    | 400 | KHz  |

| Clock low time                                                                       | 10  | -    | -   | ns   |

| Clock high time                                                                      | 10  | -    | -   | ns   |

| Clock rise time                                                                      | 8   | -    | 10  | ns   |

| Clock fall time                                                                      | 0   | -    | 10  | ns   |

| <b>Inputs: CMD, DAT (referenced to CLK)</b>                                          |     |      |     |      |

| Input setup time                                                                     | 5   | -    | -   | ns   |

| Input hold time                                                                      | 5   | -    | -   | ns   |

| <b>Outputs: CMD, DAT (referenced to CLK)</b>                                         |     |      |     |      |

| Output delay time – Data Transfer mode                                               | 0   | -    | 14  | ns   |

| Output delay time – Identification mode                                              | 0   | -    | 50  | ns   |

a. Timing is based on CL <= 40pF load on CMD and Data.

b. Min. (Vih) = 0.7 X VDDIO and max (Vil) = 0.2 X VDDIO.

#### 4.4.3 SDIO High-Speed Mode Timing

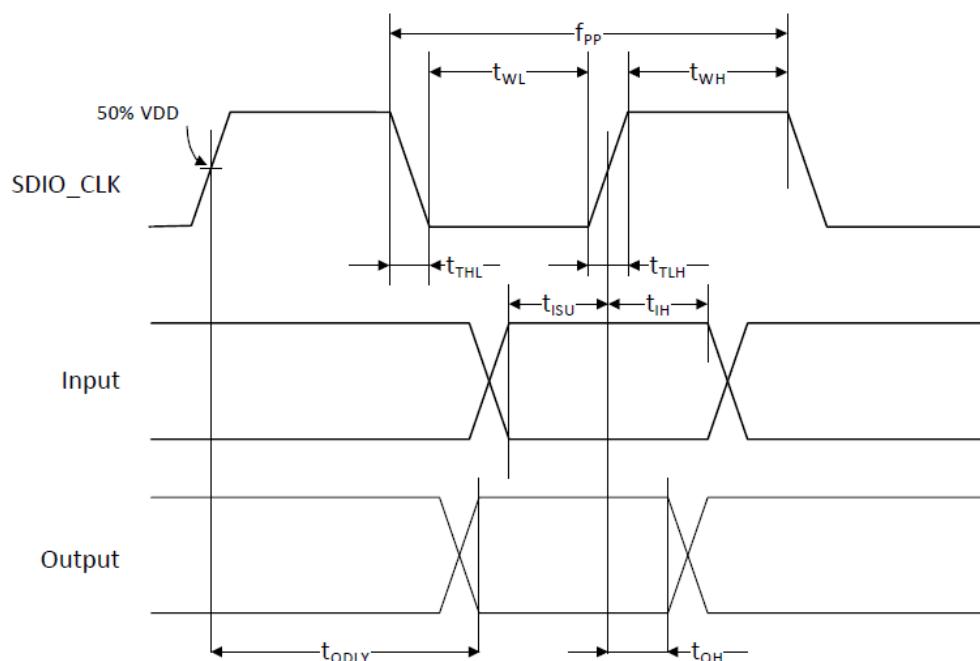

**Figure 15: SDIO Bus Timing (Default Mode)**

**Table 12: SDIO Bus Timing<sup>a</sup> Parameters (High-Speed Mode)**

| Parameter                                                                            | Min | Type | Max | Unit |

|--------------------------------------------------------------------------------------|-----|------|-----|------|

| <b>SDIO CLK (All values are referred to minimum VIH and maximum Vil<sup>b</sup>)</b> |     |      |     |      |

| Frequency – Data Transfer mode                                                       | 0   | -    | 50  | MHz  |

| Frequency – Identification mode                                                      | 0   | -    | 400 | KHz  |

| Clock low time                                                                       | 7   | -    | -   | ns   |

| Clock high time                                                                      | 7   | -    | -   | ns   |

| Clock rise time                                                                      | -   | -    | 3   | ns   |

| Clock fall time                                                                      | -   | -    | 3   | ns   |

| <b>Inputs: CMD, DAT (referenced to CLK)</b>                                          |     |      |     |      |

| Input setup time                                                                     | 6   | -    | -   | ns   |

| Input hold time                                                                      | 2   | -    | -   | ns   |

| <b>Outputs: CMD, DAT (referenced to CLK)</b>                                         |     |      |     |      |

| Output delay time – Data Transfer mode                                               | -   | -    | 14  | ns   |

| Output hold time                                                                     | 2.5 | -    | -   | ns   |

| Total system capacitance (each line)                                                 | -   | -    | 40  |      |

a. Timing is based on CL &lt;= 40pF load on CMD and Data.

b. Min. (Vih) = 0.7 X VDDIO and max (Vil) = 0.2 X VDDIO.

#### 4.4.4 SDIO Bus Timing Specifications in SDR Modes

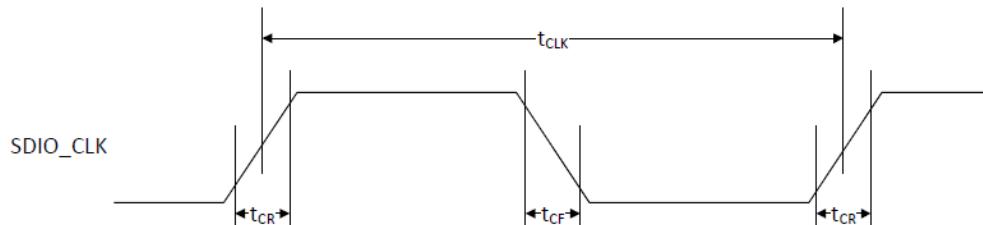

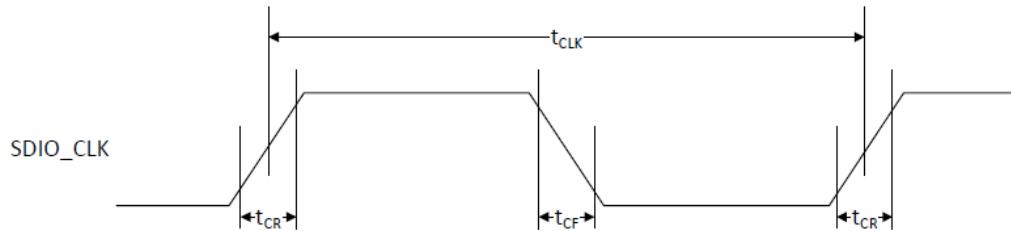

**Figure 16: SDIO Clock Timing (SDR Modes)****Table 13: SDIO Bus Clock Timing Parameters (SDR Modes)**

| Parameter        | Min | Type | Max | Unit | Unit                                                                                                   |

|------------------|-----|------|-----|------|--------------------------------------------------------------------------------------------------------|

|                  | 40  | -    | -   | ns   | SDR12 mode                                                                                             |

|                  | 20  | -    | -   | ns   | SDR25 mode                                                                                             |

|                  | 10  | -    | -   | ns   | SDR50 mode                                                                                             |

|                  | 4.8 | -    | -   | ns   | SDR104 mode                                                                                            |

|                  | -   | -    | 3   | ns   | tCR, tCF < 2.00 ns (max.) @100 MHz, CCARD = 10 pF<br>tCR, tCF < 0.96 ns (max.) @208 MHz, CCARD = 10 pF |

| Clock duty cycle | 30  | -    | 70  | %    | ns                                                                                                     |

#### 4.4.5 Device Input Timing

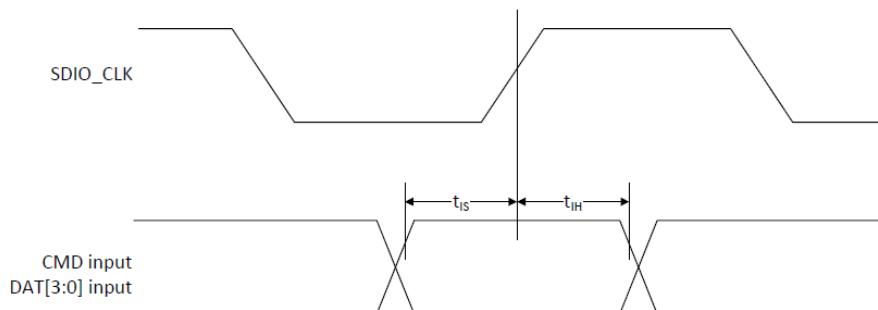

Figure 17: SDIO Bus Input Timing (SDR Modes)

Table 14: SDIO Bus Input Timing Parameters (SDR Modes)

| Symbol             | Min | Type | Max | Unit | Unit                                     |

|--------------------|-----|------|-----|------|------------------------------------------|

| <b>SDR104 Mode</b> |     |      |     |      |                                          |

| $t_{IS}$           | 1.4 | -    | -   | ns   | $C_{CARD} = 10 \text{ pF}, VCT = 0.975V$ |

| $t_{IH}$           | 0.8 | -    | -   | ns   | $C_{CARD} = 5 \text{ pF}, VCT = 0.975V$  |

| <b>SDR50 Mode</b>  |     |      |     |      |                                          |

| $t_{IS}$           | 3.0 | -    | -   | ns   | $C_{CARD} = 10 \text{ pF}, VCT = 0.975V$ |

| $t_{IH}$           | 0.8 | -    | -   | ns   | $C_{CARD} = 5 \text{ pF}, VCT = 0.975V$  |

| <b>SDR25 Mode</b>  |     |      |     |      |                                          |

| $t_{IS}$           | 3.0 | -    | -   | ns   | $C_{CARD} = 10 \text{ pF}, VCT = 0.975V$ |

| $t_{IH}$           | 0.8 | -    | -   | ns   | $C_{CARD} = 5 \text{ pF}, VCT = 0.975V$  |

| <b>SDR12 Mode</b>  |     |      |     |      |                                          |

| $t_{IS}$           | 3.0 | -    | -   | ns   | $C_{CARD} = 10 \text{ pF}, VCT = 0.975V$ |

| $t_{IH}$           | 0.8 | -    | -   | ns   | $C_{CARD} = 5 \text{ pF}, VCT = 0.975V$  |

#### 4.4.6 Device Output Timing

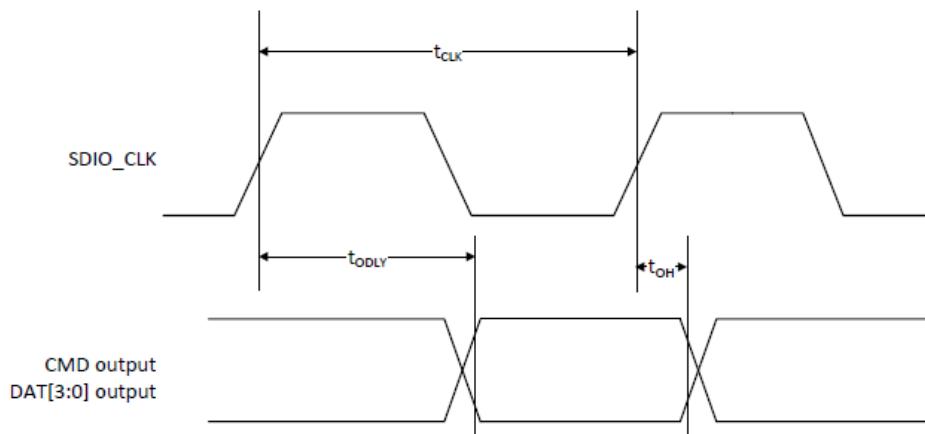

Figure 18: SDIO Bus Output Timing (SDR Modes up to 100MHz)

**Table 15:** SDIO Bus Output Timing Parameters (SDR Modes up to 100 MHz)

| Symbol     | Min | Type | Max  | Unit | Unit                                                             |

|------------|-----|------|------|------|------------------------------------------------------------------|

| $t_{ODLY}$ | -   | -    | 7.5  | ns   | $t_{CLK} \geq 10$ ns $C_L = 30$ pF using driver type B for SDR50 |

| $t_{ODLY}$ | -   | -    | 14.0 | ns   | $t_{CLK} \geq 20$ ns $C_L = 40$ pF using for SDR12, SDR25        |

| $T_{OH}$   | 1.5 | -    | -    | ns   | Hold time at the $t_{ODLY}$ (min) $C_L = 15$ pF                  |

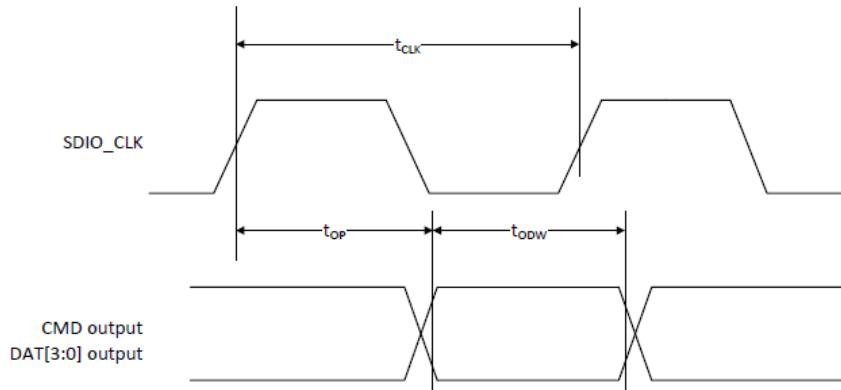

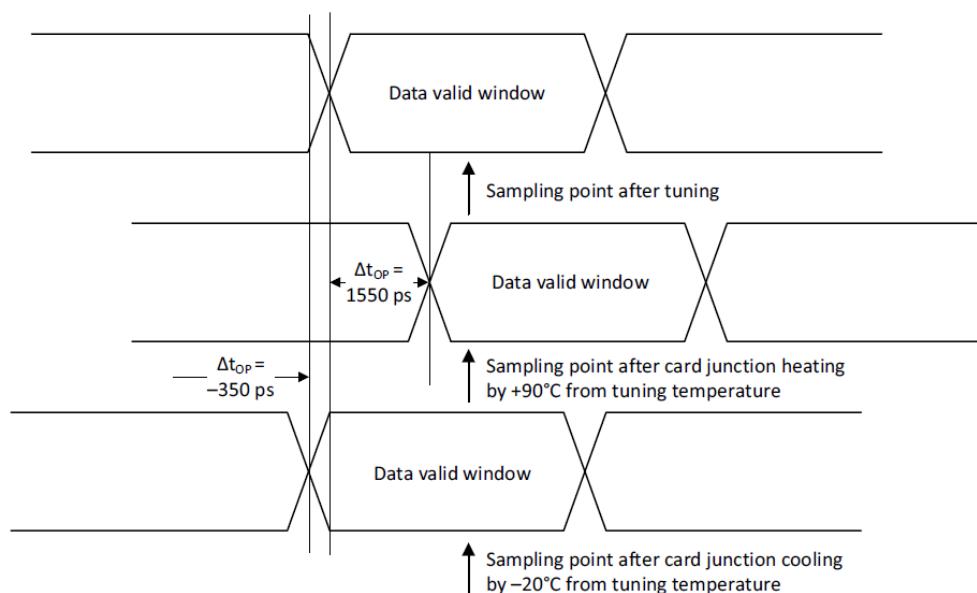

**Figure 19:** SDIO Bus Output Timing (SDR Modes 100 MHz to 208 MHz)**Table 16:** SDIO Bus Output Timing Parameters (SDR Modes 100 MHz to 208 MHz)

| Symbol          | Min  | Type | Max   | Unit | Unit                                            |

|-----------------|------|------|-------|------|-------------------------------------------------|

| $t_{OP}$        | 0    | -    | 2     | UI   | Card output phase                               |

| $\Delta t_{OP}$ | -350 | -    | +1550 | ps   | Delay variation due to temp change after tuning |

| $t_{ODW}$       | 0.60 | -    | -     | UI   | $t_{ODW}=2.88$ ns @208 MHz                      |

- $\Delta t_{OP} = +1550$  ps for junction temperature of  $\Delta t_{OP} = 90$  degrees during operation

- $\Delta t_{OP} = -350$  ps for junction temperature of  $\Delta t_{OP} = -20$  degrees during operation

- $\Delta t_{OP} = +2600$  ps for junction temperature of  $\Delta t_{OP} = -20$  to  $+125$  degrees during operation

**Figure 20:**  $\Delta t_{OP}$  Consideration for Variable Data Window (SDR 104 Mode)

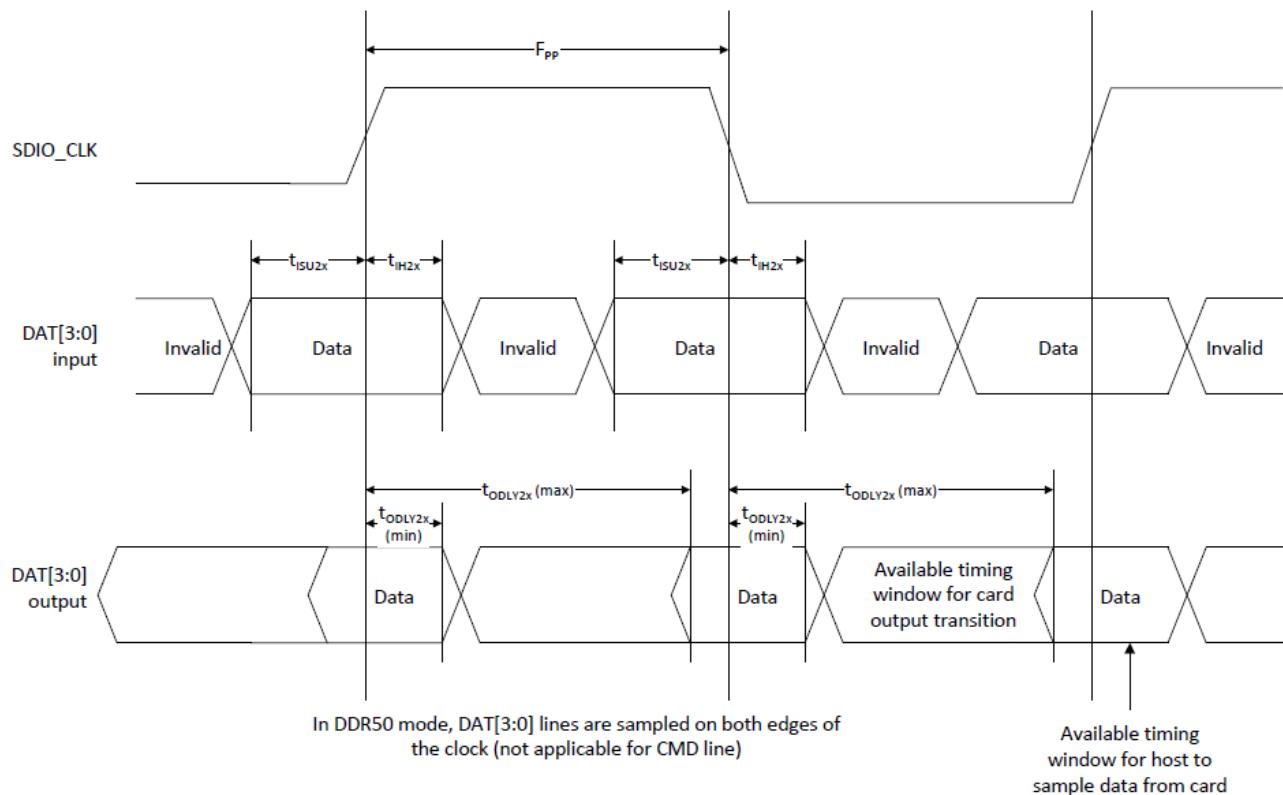

#### 4.4.7 SDIO Bus Timing Specifications in DDR50 Mode

Figure 21: SDIO Clock Timing (DDR50 Mode)

Table 17: SDIO Bus Clock Timing Parameters (DDR50 Mode)

| Parameter        | Min | Type | Max                    | Unit | Unit                                                                                 |

|------------------|-----|------|------------------------|------|--------------------------------------------------------------------------------------|

|                  | 20  | -    | 7.5                    | ns   | DDR50 mode                                                                           |

| Clock duty cycle | -   | -    | 0.2 x t <sub>CLK</sub> | ns   | t <sub>CR</sub> , t <sub>CF</sub> < 4.00 ns (max) @50 MHz, C <sub>CARD</sub> = 10 pF |

|                  | 45  | -    | 55                     | %    | -                                                                                    |

Figure 22: SDIO Data Timing (DDR50 Mode)

**Table 18:** SDIO Bus Timing Parameters (DDR50 Mode)

| Parameter          | Min | Type | Max  | Unit | Comments                          |

|--------------------|-----|------|------|------|-----------------------------------|

| <b>Input CMD</b>   |     |      |      |      |                                   |

| Input setup time   | 6   | -    | -    | ns   | $C_{CARD} < 10\text{pF}$ (1 Card) |

| Input hold time    | 0.8 | -    | -    | ns   | $C_{CARD} < 10\text{pF}$ (1 Card) |

| <b>Outputs CMD</b> |     |      |      |      |                                   |

| Output delay time  | -   | -    | 13.7 | ns   | $C_{CARD} < 30\text{pF}$ (1 Card) |

| Output hold time   | 1.5 | -    | -    | ns   | $C_{CARD} < 15\text{pF}$ (1 Card) |

| <b>Input DAT</b>   |     |      |      |      |                                   |

| Input setup time   | 3   | -    | -    | ns   | $C_{CARD} < 10\text{pF}$ (1 Card) |

| Input hold time    | 0.8 | -    | -    | ns   | $C_{CARD} < 10\text{pF}$ (1 Card) |

| <b>Outputs DAT</b> |     |      |      |      |                                   |

| Output delay time  | -   | -    | 7.0  | ns   | $C_{CARD} < 25\text{pF}$ (1 Card) |

| Output hold time   | 1.5 | -    | -    | ns   | $C_{CARD} < 15\text{pF}$ (1 Card) |

## 5. ELECTRICAL CHARACTERISTICS

### 5.1 Absolute Maximum Ratings

All measurements are referenced at the module pins unless otherwise indicated. All specifications are over process and voltage unless otherwise indicated.

Over operating free-air temperature range (unless otherwise noted)

**Table 19:** Absolute Maximum Rating

| Parameter                                 | Min  | Max  | Unit |

|-------------------------------------------|------|------|------|

| VDD_3V3_WL(SWREG Supply Input)            | -0.3 | +3.6 | V    |

| VDD_IO(DC supply voltage for digital I/O) | -0.3 | +3.6 | V    |

| Operating temperature ( $T_A$ )           | -40  | +85  | °C   |

| Storage temperature ( $T_{stg}$ )         | -40  | +85  | °C   |

| Maximum junction temperature( $T_j$ )     |      | +105 | °C   |

### 5.2 Recommended Operating Conditions

**Table 20:** Recommended Operating Conditions

| Parameter                         | Min          | Type    | Max          | Unit |

|-----------------------------------|--------------|---------|--------------|------|

| VDD_3V3_WL                        | 3.0          | 3.3     | 3.6          | V    |

| VDD_IO                            | 1.62         | 1.8~3.3 | 3.6          | °C   |

| Operating temperature ( $T_A$ )   | -40          | 25      | +85          | °C   |

| Storage temperature ( $T_{stg}$ ) | -40          | 25      | +85          | °C   |

| High-level input voltage          | 0.7 X VDD_IO |         | VDD_IO + 0.3 | V    |

|                           |              |              |    |

|---------------------------|--------------|--------------|----|

| Low-level input voltage   | -0.3         | 0.3 X VDD_IO | V  |

| Input low leakage current | -5.0         | 5.0          | uA |

| High-level output voltage | 0.9 X VDD_IO | VDD_IO       | V  |

| Low-level output voltage  | 0            | 0.1 X VDD_IO | V  |

| High-level output current | 3            |              | mA |

| Low-level output current  |              | -11          | mA |

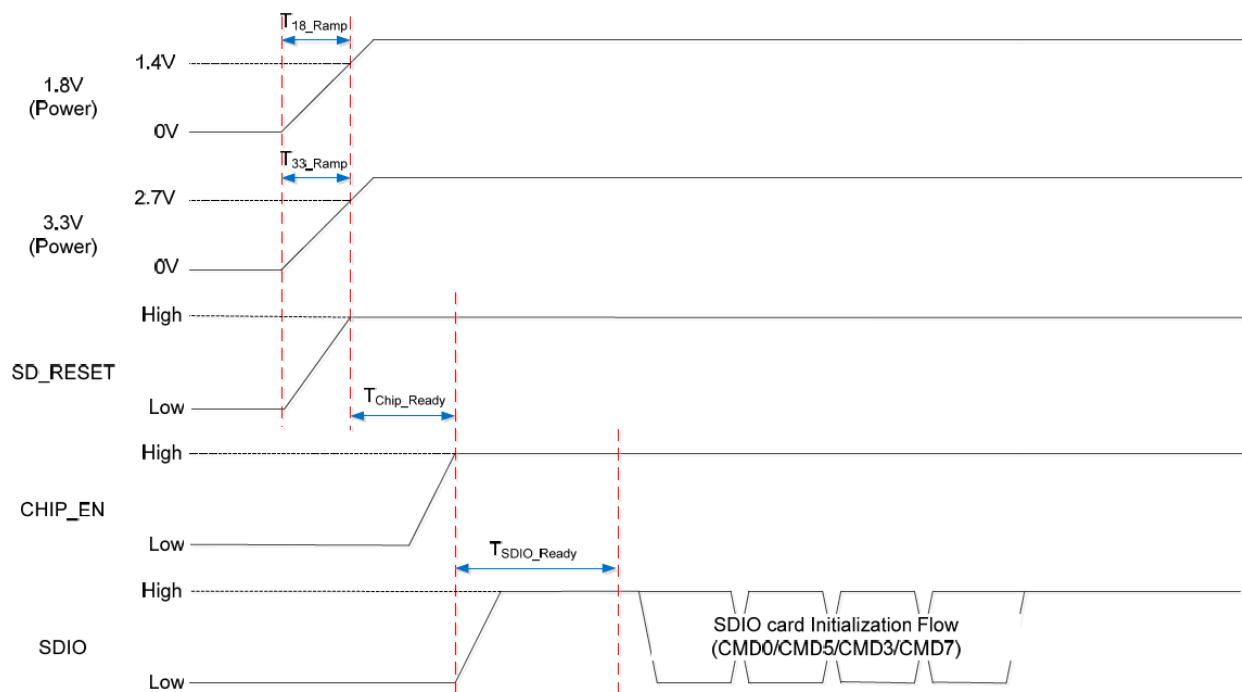

## 5.3 System Power Sequence

### 5.3.1 System Power On Sequence

Figure 23: System Power-On Sequence

#### Notes:

1. SD\_RESET=EN pin for power supply of control module; CHIP\_EN= BT\_EN or WL\_EN; SDIO=SDIO communication interface.

(SD\_RESET=控制模块供电的EN脚, CHIP\_EN= BT\_EN 或 WL\_EN, SDIO=SDIO通讯接口)

2. TChip\_Ready is set to at least 500mS according to the experience value, some customers need longer, for example, more than 1S.

(TChip\_Ready 按我们的经验值设定为最少500mS, 有的客户需要更长比如会需要1S以上)

Table 24: System Power On Timing Parameters

| Characteristics         | Description                           | Min | Type | Max | Unit |

|-------------------------|---------------------------------------|-----|------|-----|------|

| T <sub>18</sub> Ramp    | The 1.8V main power ramp up duration. | 0.1 | 0.5  | 2.5 | ms   |

| T <sub>33</sub> Ramp    | The 3.3V main power ramp up duration. | 0.1 | 0.5  | 2.5 | ms   |

| T <sub>Chip_Ready</sub> | CHIP_EN pull high timing              | 500 | -    | -   | ms   |

|                    |                                                                                                                                                                                                                    |   |   |    |    |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----|----|

| $T_{SDIO\_Ready}$  | SDIO Not Ready Duration.<br>In this state, the Chip may respond to commands without the ready bit being set. After the ready bit is set, the host will initiate complete card detection procedure.                 | 1 | 2 | 10 | ms |

| $T_{G-SPI\_Ready}$ | The duration G-SPI device internal initialization.<br>After $T_{G-SPI\_Ready}$ , SPI host can then send command to write REG_SPI_CFG register.<br>REG_SPI_CFG register is to control G-SPI endian and word length. | 3 | 4 | 18 | ms |

### SDIO Interface Power On Sequence

After power-on, the SDIO interface is selected by the RTL8821CS automatically when a valid SDIO command is received. To attain better SDIO host compatibility, the following power-on sequence is recommended.

We recommend that the card detection procedures are divided into two phases: A 3.3V/1.8V power pre-charge phase and a formal power-up phase.

After main 3.3V ramp up and 1.8V ramp up, the power management unit is enabled by the power ready detection circuit. The power management unit enables the SDIO block. eFUSE is then autoloaded to SDIO circuits during the  $T_{SDIO\_Ready}$  duration and then SDIO pins are pulled up. After CMD5/5/3/7 procedures, card detection is executed.

### G-SPI Interface Power On Sequence

The G-SPI interface is enabled automatically when a valid G-SPI command is first received. The recommended power on sequence is as follows:

After main 3.3V/1.8V ramp up, the power management unit will be enabled by power ready detection circuit, and enables G-SPI block. Efuse is then autoloaded to SPI circuits, and the internal power circuits are configured during  $T_{G-SPI\_Ready}$  duration.

### SD\_RESET Power On Sequence

To attain SD\_RESET capability, the following power sequence is recommended.

After main 3.3V/1.8V ramp up, the power management unit is enabled by the power ready detection circuit.

The power management unit enables the SD\_RESET function. After power management unit being enabled, SD\_RESET needs to keep high for ensuring WLAN and SDIO/G-SPI function being alive.

### CHIP\_EN Power On Sequence

To attain CHIP\_EN capability, the following power sequence is recommended.

After main 3.3V/1.8V ramp up, the power management unit is enabled by the power ready detection circuit.

The power management unit enables the CHIP\_EN function. After power management unit being enabled, CHIP\_EN needs to keep high for ensuring FSC-BW121 function being alive.

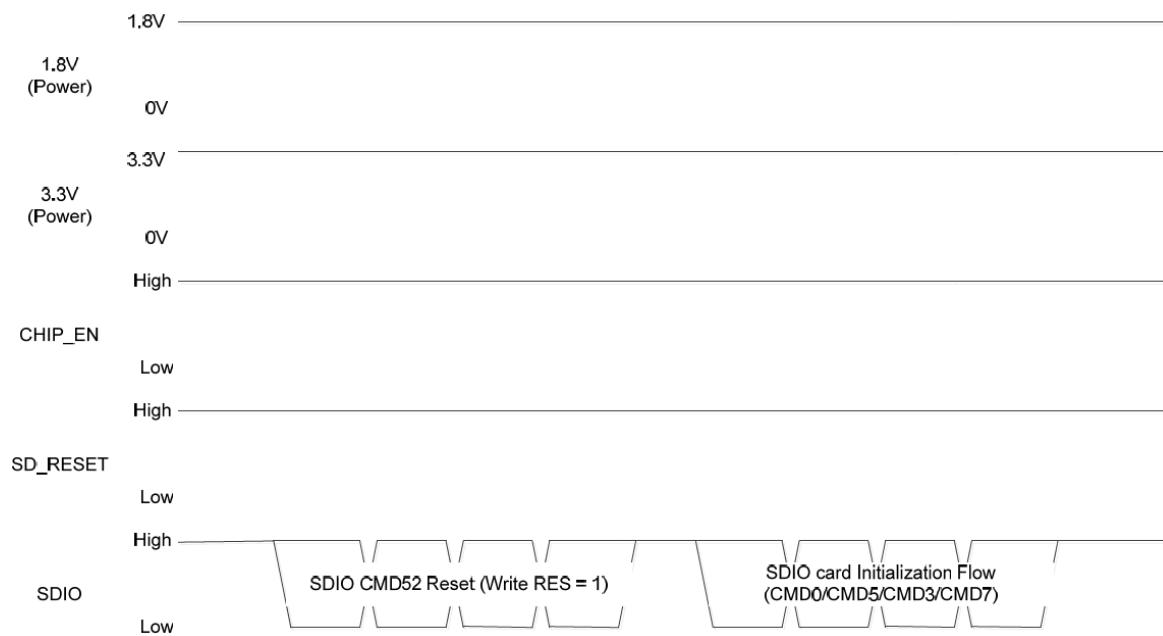

### 5.3.2 SDIO Reset Sequence

Figure 24: SDIO Reset Sequence

**Notes:**

1. SD\_RESET=EN pin for power supply of control module; CHIP\_EN= BT\_EN or WL\_EN; SDIO=SDIO communication interface.

(SD\_RESET=控制模块供电的 EN 脚, CHIP\_EN= BT\_EN 或 WL\_EN, SDIO=SDIO 通讯接口)

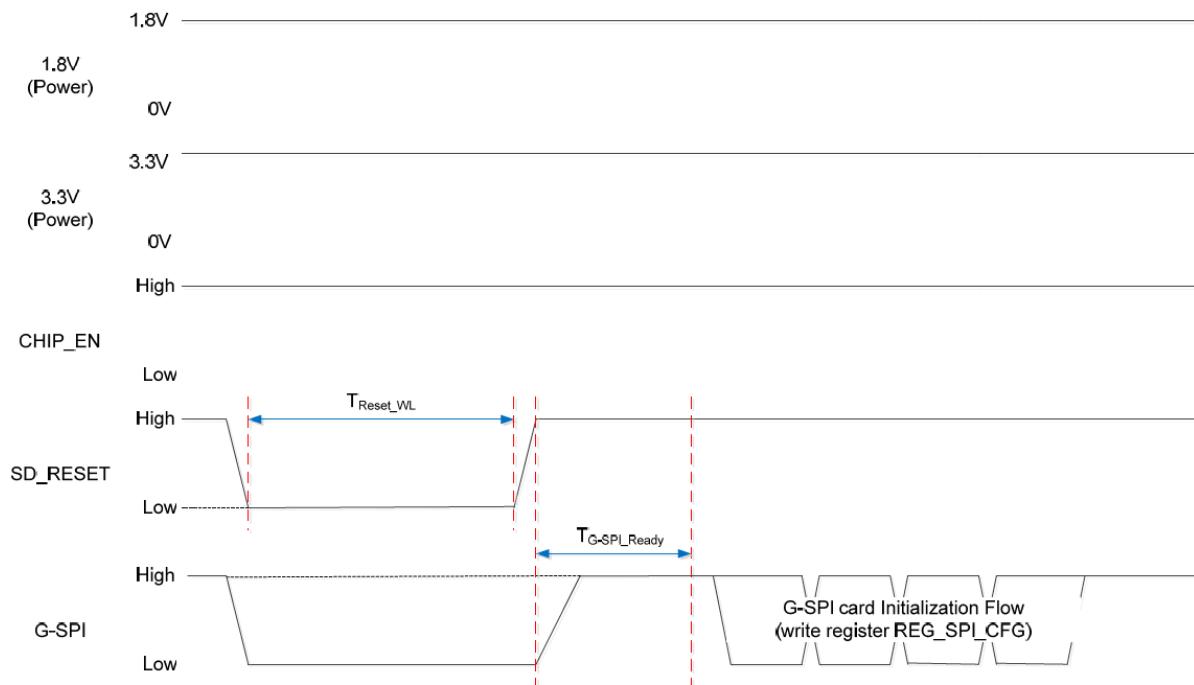

### 5.3.3 WLAN and G-SPI Reset Sequence

Figure 25: Wlan Reset Sequence

**Notes:**

1.SD\_RESET=EN pin for power supply of control module; CHIP\_EN= BT\_EN or WL\_EN; SDIO=SDIO communication interface.

(SD\_RESET=控制模块供电的EN脚, CHIP\_EN= BT\_EN 或 WL\_EN, SDIO=SDIO通讯接口)

**Table 25: WLAN and G-SPI Reset Timing Parameters**

| Characteristics    | Description                                                                                                                                                                                                        | Min | Type | Max | Unit |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| $T_{Reset\_WL}$    | SD_RESET keep low duration                                                                                                                                                                                         | 10  | 10   | x   | ms   |

| $T_{G-SPI\_Ready}$ | The duration G-SPI device internal initialization.<br>After $T_{G-SPI\_Ready}$ , SPI host can then send command to write REG_SPI_CFG register.<br>REG_SPI_CFG register is to control G-SPI endian and word length. | 3   | 4    | 18  | ms   |

SD\_RESET can externally reset G-SPI function by pulled SD\_RESET low and then pulled high. The keeping low duration must be more than  $T_{Reset\_WL}$ . After WLAN reset, G-SPI card initialization is needed.

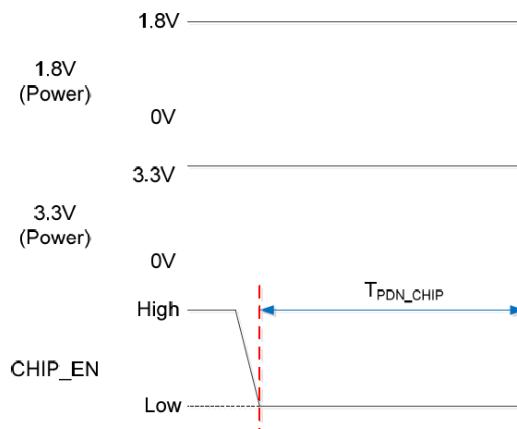

### 5.3.4 Power Off Sequence

**Figure 26: Power Off Sequence****Notes:**

1. CHIP\_EN= BT\_EN or WL\_EN.

**Table 26: Power Off Timing Parameters**

| Characteristics | Description               | Min | Type | Max | Unit |

|-----------------|---------------------------|-----|------|-----|------|

| $T_{PDN\_CHIP}$ | CHIP_EN keep low duration | 100 | 100  | x   | ms   |

CHIP\_EN can externally shutdown the chip when CHIP\_EN is pulled low. The keeping low duration must be more than  $T_{PDN\_CHIP}$ .

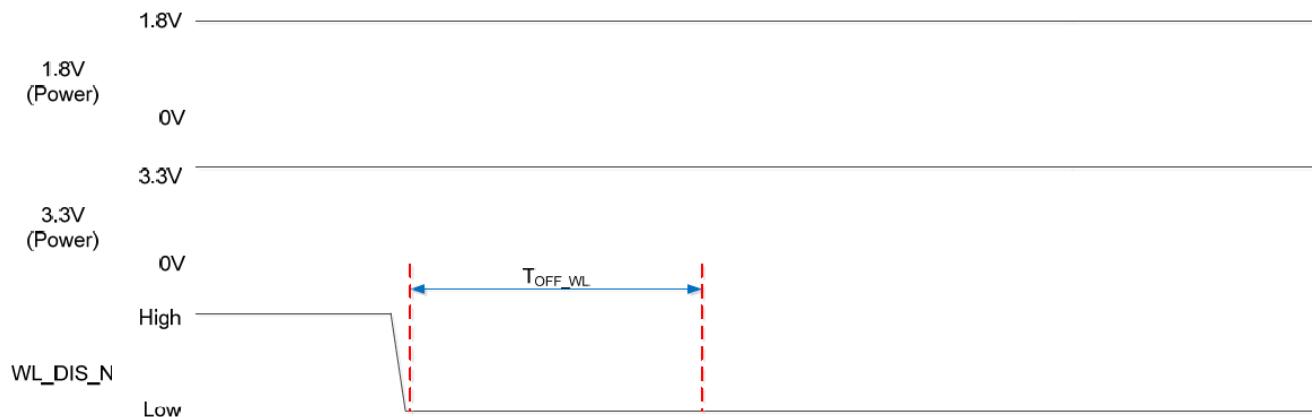

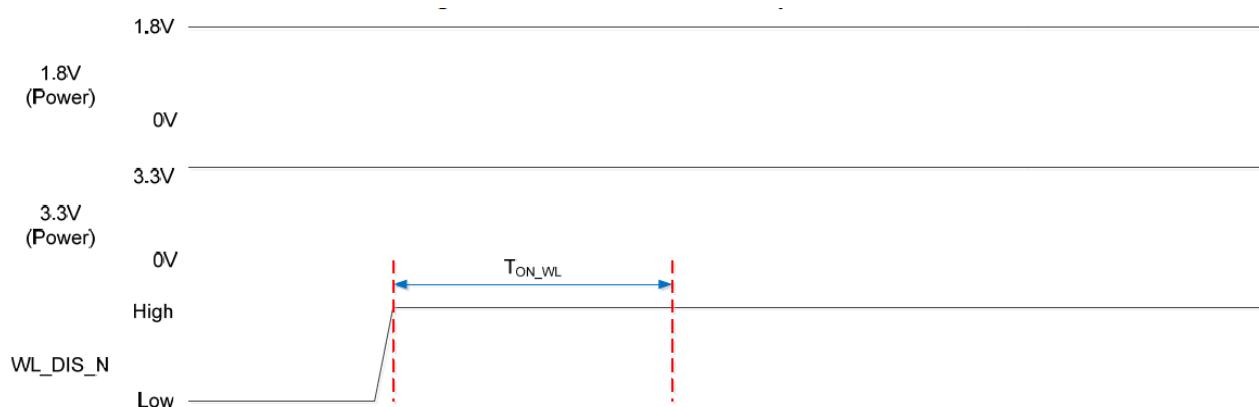

### 5.3.5 WLAN Radio On/Off Sequence

Figure 27: WLAN Radio Off Sequence

Figure 28: WLAN Radio On Sequence

**Notes:**

1.  $WL\_DIS\_N = WL\_EN$ .

$WL\_DIS\_N$  can be defined as the WLAN Radio-off function with host interface remaining connected. When  $WL\_DIS\_N$  is pulled low, WLAN Radio will be disabled. The keeping low duration must be more than  $T_{OFF\_WL}$ .

When  $WL\_DIS\_N$  is pulled high, WLAN Radio will be enabled. The keeping high duration must be more than  $T_{ON\_WL}$ .

Table 27: WLAN Radio On/Off Timing Parameters

| Characteristics | Description                     | Min | Type | Max | Unit |

|-----------------|---------------------------------|-----|------|-----|------|

| $T_{OFF\_WL}$   | $WL\_DIS\_N$ keep low duration  | 100 | 100  | x   | ms   |

| $T_{ON\_WL}$    | $WL\_DIS\_N$ keep high duration | 100 | 100  | x   | ms   |

### 5.3.6 BT Power On/Off Sequence

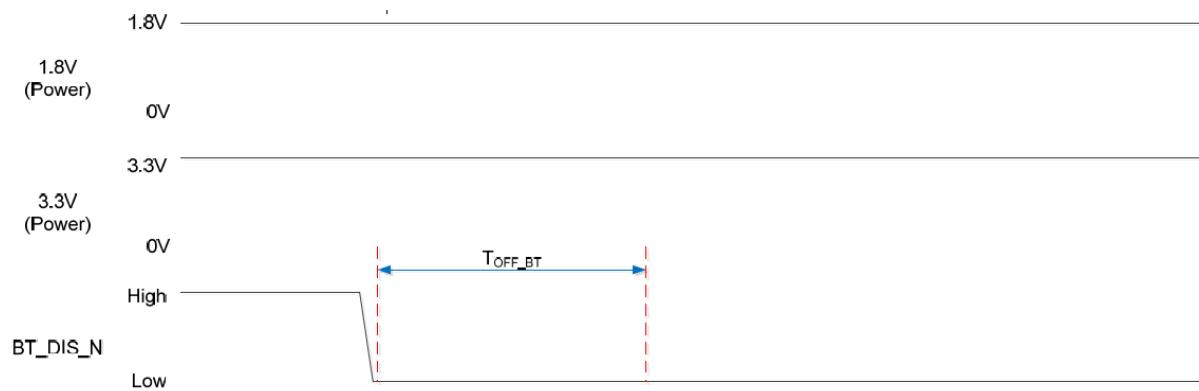

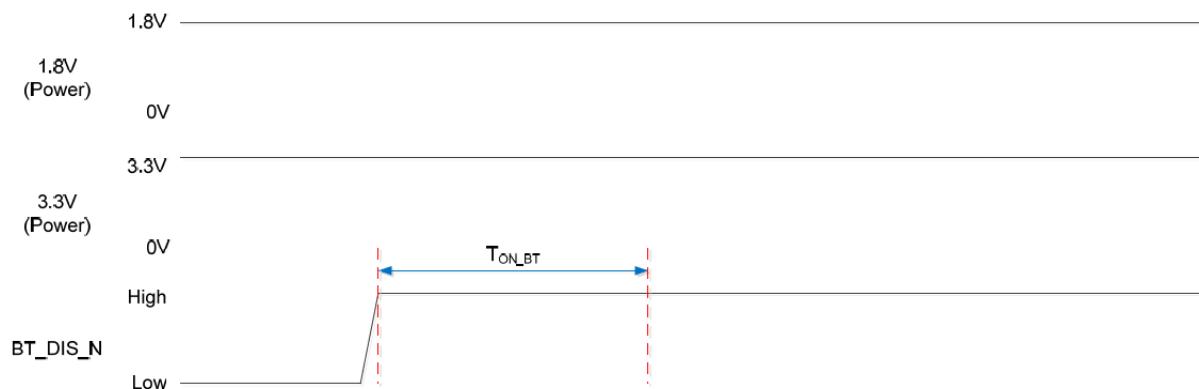

Figure 29: BT Power Off Sequence

Figure 30: BT Power On Sequence

**Notes:**

1. BT\_Dis\_N = WL\_EN.

BT\_Dis\_N can be defined as the BT Power-off function with host interface remaining connected.

When BT\_Dis\_N is pulled low, BT will be disabled. The keeping low duration must be more than  $T_{OFF\_BT}$ . When BT\_Dis\_N is pulled high, BT will be enabled. The keeping high duration must be more than  $T_{ON\_BT}$ .

Table 28: BT Radio On/Off Timing Parameters

| Characteristics | Description                 | Min | Type | Max | Unit |

|-----------------|-----------------------------|-----|------|-----|------|

| $T_{OFF\_BT}$   | BT_Dis_N keep low duration  | 100 | 100  | x   | ms   |

| $T_{ON\_BT}$    | BT_Dis_N keep high duration | 100 | 100  | x   | ms   |

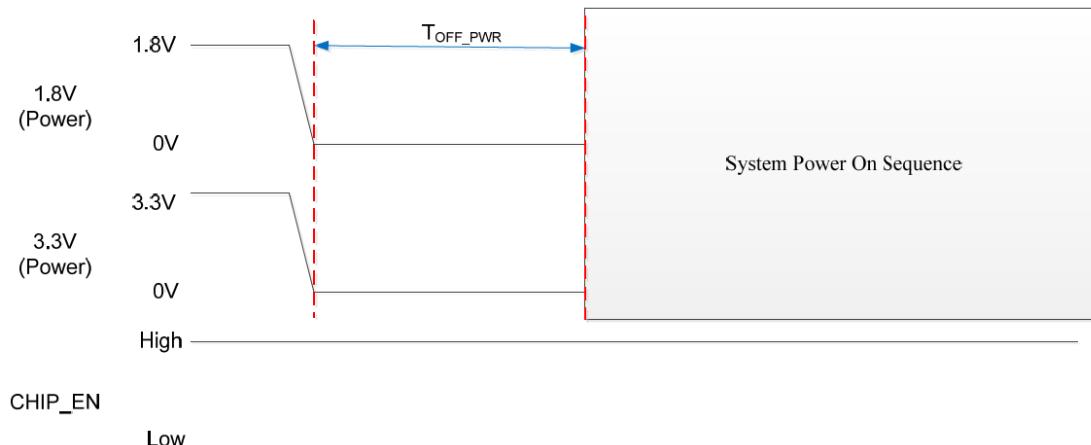

### 5.3.7 Power Reset Sequence

Figure 31: Power Reset Sequence

**Notes:**

1. CHIP\_EN= BT\_EN or WL\_EN.

Main 3.3V/1.8V power should keep low at least  $T_{OFF\_PWR}$  before calling system power on Sequence. CHIP\_EN should be pulled high during power reset sequence.

Table 29: Power Reset Timing Parameters

| Characteristics | Description                       | Min | Type | Max | Unit |

|-----------------|-----------------------------------|-----|------|-----|------|

| $T_{OFF\_PWR}$  | 3.3V/1.8V power keep low duration | 100 | 100  | x   | ms   |

## 5.4 Power Consumption

Table 30: Power Consumption:

| Internal Pull Resistor | Voltage | Power Consumption(mA)(Max) |

|------------------------|---------|----------------------------|

| VDD_3V3_WL             | 3.3V    | 500                        |

| VDD_IO                 | 3.3V    | 300                        |

| Testing Condition:     |         | 2.4GHz Tx MCS0 6.5Mbps     |

FSC-BW121 Module Power Consumption:

**500mA @ VDD\_3V3\_WL(Maximum) and 300mA @ VDD\_IO(Maximum)**

**Suggest customer design power capacity are 1000mA@VDD\_3V3\_WL and 500mA @ VDD\_IO for FSC-BW121 Module.**

## 6. MSL & ESD

Table 31: MSL and ESD

| Parameter                                                                                   | Value                          |

|---------------------------------------------------------------------------------------------|--------------------------------|

| MSL grade:                                                                                  | MSL 3                          |

| <b>ESD grade</b>                                                                            | <b>Electrostatic discharge</b> |

| ESD – Human-body model (HBM) rating, JESD22-A114-F<br>(Total samples from one wafer lot)    | Pass $\pm 2000$ V, all pins    |

| ESD – Charge-device model (CDM) rating, JESD22-C101-D<br>(Total samples from one wafer lot) | Pass $\pm 400$ V, all pins     |

|                                                                                             |                                |

|                                                                                             |                                |

|                                                                                             |                                |

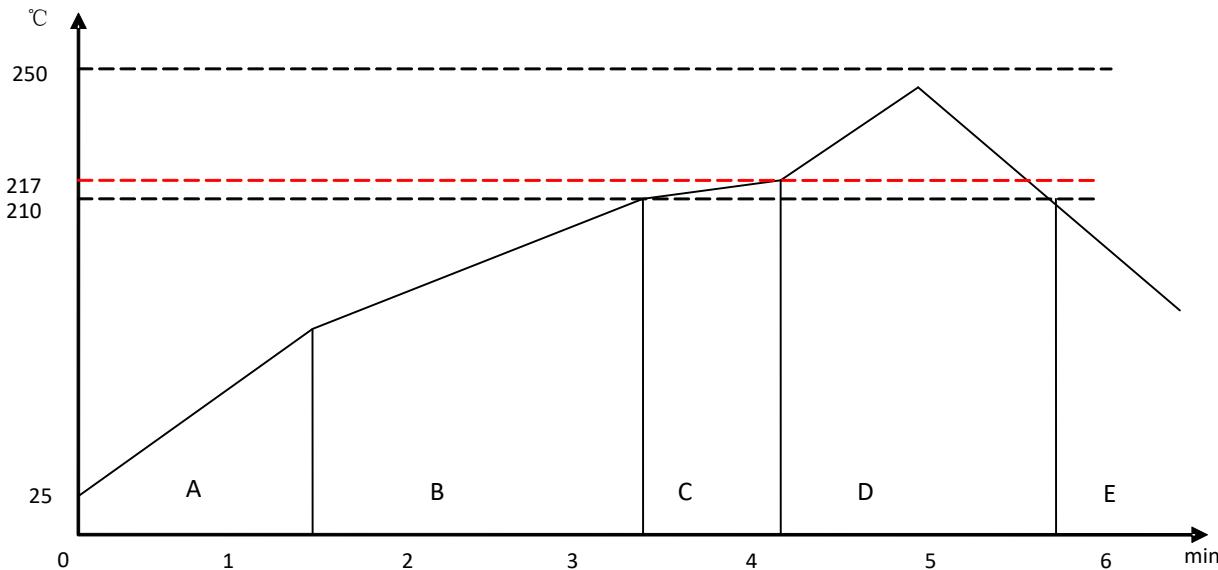

## 7. RECOMMENDED TEMPERATURE REFLOW PROFILE

Prior to any reflow, it is important to ensure the modules were packaged to prevent moisture absorption. New packages contain desiccant (to absorb moisture) and a humidity indicator card to display the level maintained during storage and shipment. If directed to bake units on the card, please check the below and follow instructions specified by IPC/JEDEC J-STD-033.

**Note:** The shipping tray cannot be heated above 65°C. If baking is required at the higher temperatures displayed in the below, the modules must be removed from the shipping tray.

Any modules not manufactured before exceeding their floor life should be re-packaged with fresh desiccant and a new humidity indicator card. Floor life for MSL (Moisture Sensitivity Level) 3 devices is 168 hours in ambient environment 30°C/60%RH.

### Notice (注意) :

Feasycom module must use Step-Stencil, suggestion using the stencil thickness about 0.16-0.2mm, it could be modify with the product.

使用我司模块，须使用阶梯钢网，建议阶梯钢网厚度0.16-0.20mm，可根据自己产品适应性，进行相应调整。

Table 32: Recommended baking times and temperatures

| MSL | 125°C Baking Temp.      |                                              | 90°C/≤ 5%RH Baking Temp. |                                              | 40°C/ ≤ 5%RH Baking Temp. |                                              |

|-----|-------------------------|----------------------------------------------|--------------------------|----------------------------------------------|---------------------------|----------------------------------------------|

|     | Saturated @<br>30°C/85% | Floor Life Limit<br>+ 72 hours @<br>30°C/60% | Saturated @<br>30°C/85%  | Floor Life Limit<br>+ 72 hours @<br>30°C/60% | Saturated @<br>30°C/85%   | Floor Life Limit<br>+ 72 hours @<br>30°C/60% |

| 3   | 9 hours                 | 7 hours                                      | 33 hours                 | 23 hours                                     | 13 days                   | 9 days                                       |

Feasycom surface mount modules are designed to be easily manufactured, including reflow soldering to a PCB. Ultimately it is the responsibility of the customer to choose the appropriate solder paste and to ensure oven temperatures during reflow meet the requirements of the solder paste. Feasycom surface mount modules conform to J-STD-020D1 standards for reflow temperatures.

The soldering profile depends on various parameters necessitating a set up for each application. The data here is given only for guidance on solder reflow.

Figure 32: Typical Lead-free Re-flow

**Pre-heat zone (A)** — This zone raises the temperature at a controlled rate, **typically 0.5 – 2 °C/s**. The purpose of this zone is to preheat the PCB board and components to 120 ~ 150 °C. This stage is required to distribute the heat uniformly to the PCB board and completely remove solvent to reduce the heat shock to components.

**Equilibrium Zone 1 (B)** — In this stage the flux becomes soft and uniformly encapsulates solder particles and spread over PCB board, preventing them from being re-oxidized. Also with elevation of temperature and liquefaction of flux, each activator and rosin get activated and start eliminating oxide film formed on the surface of each solder particle and PCB board. **The temperature is recommended to be 150° to 210° for 60 to 120 second for this zone.**

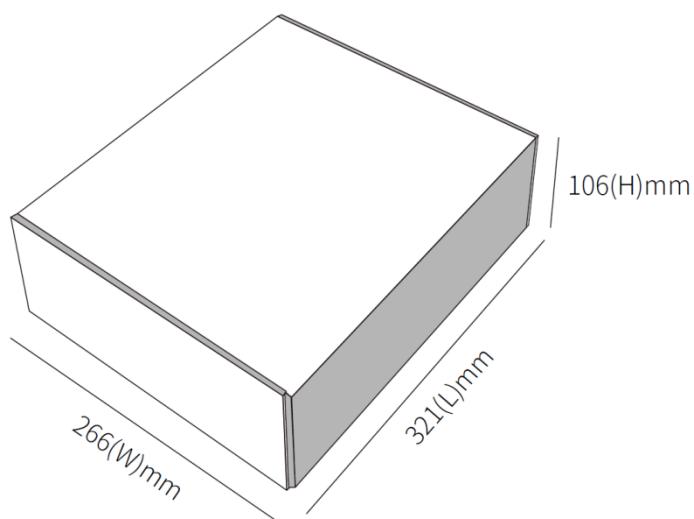

**Equilibrium Zone 2 (C) (optional)** — In order to resolve the upright component issue, it is recommended to keep the temperature in 210 – 217 ° for about 20 to 30 second.