## Technical Description

The Equipment Under Test (EUT) is a Bluetooth Speaker which equips with a 2.4GHz Bluetooth 4.2 Module. The EUT operates at frequency range of 2402MHz to 2480MHz. There are total 79 channels with 1MHz channel spacing. The EUT can accept wireless audio when paired with a Bluetooth devices. The audio signal is amplified and driving internal loudspeaker. The EUT is powered by a 12V internal rechargeable battery. The internal battery can be charged by 13.5V AC/DC adaptor (Model: YLS0301E-T135200. The applicant declared that the Bluetooth 4.0 BLE is not used.

**2.4GHz Bluetooth Module:**

**Modulation Type: GFSK**

**Antenna Type: Integral, Internal (PCB Trace)**

**Frequency Range: 2402MHz - 2480MHz, 1MHz channel spacing, 79 channels**

**Nominal field strength is 97.6dB $\mu$ V/m @ 3m**

**Production Tolerance of field strength is +/- 3dB**

**Antenna gain is 0dBi**

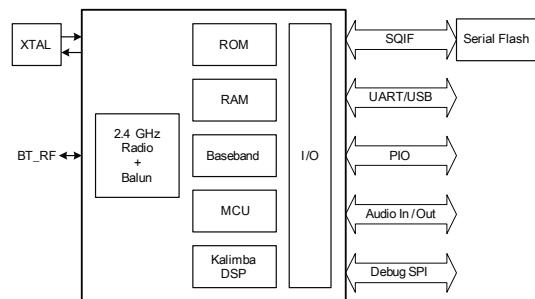

**The functions of main ICs are mentioned below.**

**1. Bluetooth module BM6420 (IC1):**

- 1) CSR64210 (U1) acts as the 2.4GHz radio core of Bluetooth module (IC1).

- 2) 26MHz crystal (Y1) provides clock for Bluetooth RF IC CSR64210 (U1).

- 3) U7 (KH25L8006) is flash memory for parameter storage.

- 4) F1 is 2.4GHz bandpass filter.

**2. Regulator and LED strip control portion:**

- 1) U7 (5802-3.3V) is 3.3V regulator.

- 2) U2 (24C02) is flash memory for controlling LED light strip.

**3. Audio portion:**

- 1) U3 (TDA3116) is stereo amplifier.

### Bluetooth 3.0

| CH. NO. | FRE.    | Hex Value |

|---------|---------|-----------|---------|---------|-----------|---------|---------|-----------|---------|---------|-----------|

| CH0     | 2402MHz | 0         | CH26    | 2428MHz | 1A        | CH52    | 2454MHz | 34        | CH78    | 2480MHz | 4E        |

| CH1     | 2403MHz | 1         | CH27    | 2429MHz | 1B        | CH53    | 2455MHz | 35        |         |         |           |

| CH2     | 2404MHz | 2         | CH28    | 2430MHz | 1C        | CH54    | 2456MHz | 36        |         |         |           |

| CH3     | 2405MHz | 3         | CH29    | 2431MHz | 1D        | CH55    | 2457MHz | 37        |         |         |           |

| CH4     | 2406MHz | 4         | CH30    | 2432MHz | 1E        | CH56    | 2458MHz | 38        |         |         |           |

| CH5     | 2407MHz | 5         | CH31    | 2433MHz | 1F        | CH57    | 2459MHz | 39        |         |         |           |

| CH6     | 2408MHz | 6         | CH32    | 2434MHz | 20        | CH58    | 2460MHz | 3A        |         |         |           |

| CH7     | 2409MHz | 7         | CH33    | 2435MHz | 21        | CH59    | 2461MHz | 3B        |         |         |           |

| CH8     | 2410MHz | 8         | CH34    | 2436MHz | 22        | CH60    | 2462MHz | 3C        |         |         |           |

| CH9     | 2411MHz | 9         | CH35    | 2437MHz | 23        | CH61    | 2463MHz | 3D        |         |         |           |

| CH10    | 2412MHz | A         | CH36    | 2438MHz | 24        | CH62    | 2464MHz | 3E        |         |         |           |

| CH11    | 2413MHz | B         | CH37    | 2439MHz | 25        | CH63    | 2465MHz | 3F        |         |         |           |

| CH12    | 2414MHz | C         | CH38    | 2440MHz | 26        | CH64    | 2466MHz | 40        |         |         |           |

| CH13    | 2415MHz | D         | CH39    | 2441MHz | 27        | CH65    | 2467MHz | 41        |         |         |           |

| CH14    | 2416MHz | E         | CH40    | 2442MHz | 28        | CH66    | 2468MHz | 42        |         |         |           |

| CH15    | 2417MHz | F         | CH41    | 2443MHz | 29        | CH67    | 2469MHz | 43        |         |         |           |

| CH16    | 2418MHz | 10        | CH42    | 2444MHz | 2A        | CH68    | 2470MHz | 44        |         |         |           |

| CH17    | 2419MHz | 11        | CH43    | 2445MHz | 2B        | CH69    | 2471MHz | 45        |         |         |           |

| CH18    | 2420MHz | 12        | CH44    | 2446MHz | 2C        | CH70    | 2472MHz | 46        |         |         |           |

| CH19    | 2421MHz | 13        | CH45    | 2447MHz | 2D        | CH71    | 2473MHz | 47        |         |         |           |

| CH20    | 2422MHz | 14        | CH46    | 2448MHz | 2E        | CH72    | 2474MHz | 48        |         |         |           |

| CH21    | 2423MHz | 15        | CH47    | 2449MHz | 2F        | CH73    | 2475MHz | 49        |         |         |           |

| CH22    | 2424MHz | 16        | CH48    | 2450MHz | 30        | CH74    | 2476MHz | 4A        |         |         |           |

| CH23    | 2425MHz | 17        | CH49    | 2451MHz | 31        | CH75    | 2477MHz | 4B        |         |         |           |

| CH24    | 2426MHz | 18        | CH50    | 2452MHz | 32        | CH76    | 2478MHz | 4C        |         |         |           |

| CH25    | 2427MHz | 19        | CH51    | 2453MHz | 33        | CH77    | 2479MHz | 4D        |         |         |           |

Qualcomm Technologies International, Ltd.

**Confidential and Proprietary – Qualcomm Technologies International, Ltd.**

*(formerly known as Cambridge Silicon Radio Ltd.)*

**NO PUBLIC DISCLOSURE PERMITTED:** Please report postings of this document on public servers or websites to:

[DocCtrlAgent@qualcomm.com](mailto:DocCtrlAgent@qualcomm.com).

**Restricted Distribution:** Not to be distributed to anyone who is not an employee of either Qualcomm Technologies International, Ltd. or its affiliated companies without the express approval of Qualcomm Configuration Management.

Not to be used, copied, reproduced, or modified in whole or in part, nor its contents revealed in any manner to others without the express written permission of Qualcomm Technologies International, Ltd.

Any software provided with this notice is governed by the Qualcomm Technologies International, Ltd. Terms of Supply or the applicable license agreement at <https://www.csrsupport.com/CSRTermsandConditions>.

Qualcomm is a trademark of Qualcomm Incorporated, registered in the United States and other countries. All Qualcomm Incorporated trademarks are used with permission. Other product and brand names may be trademarks or registered trademarks of their respective owners.

This technical data may be subject to U.S. and international export, re-export, or transfer ("export") laws. Diversion contrary to U.S. and international law is strictly prohibited.

© 2015 Qualcomm Technologies International, Ltd. All rights reserved.

Qualcomm Technologies International, Ltd.

Churchill House

Cambridge Business Park

Cambridge, CB4 0WZ

United Kingdom

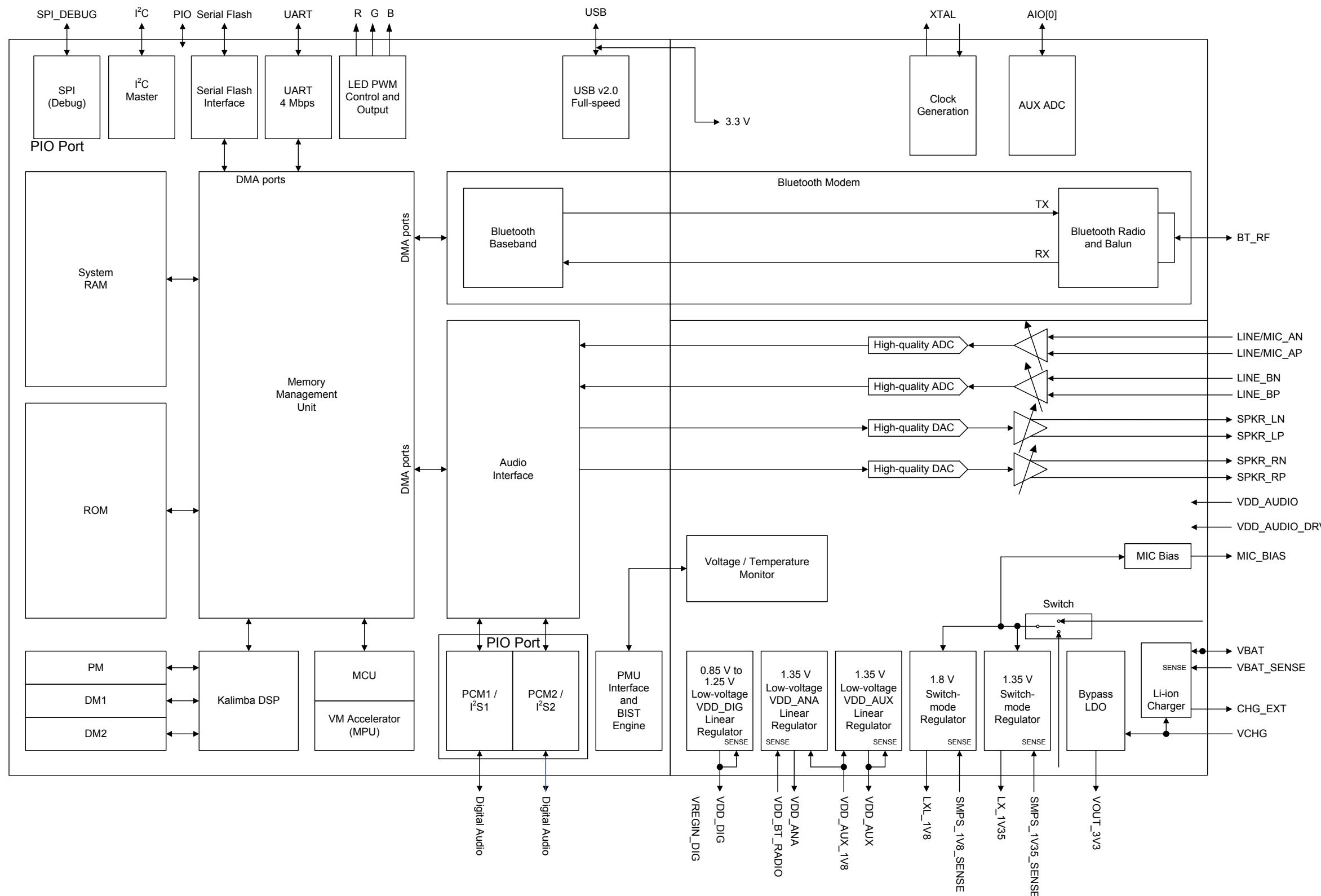

## Features

- Bluetooth® v4.2 specification compliant

- 80 MHz RISC MCU and 80 MIPS Kalimba DSP

- High-performance stereo codec with 1 microphone input (shared with line input) and 1 digital microphone (MEMS) interface

- Internal ROM and serial flash memory

- Radio includes integrated balun with RF performance of 8 dBm (typ) transmit power and -89 dBm (typ) BDR receiver sensitivity

- AVRCP v1.5

- TrueWireless Stereo™ (TWS)

- User and manufacturer configurable EQs

- Wideband speech supported by HFP v1.6 and mSBC codec

- CSR's latest cVc technology for narrowband and wideband voice connections including wind noise reduction

- Multipoint support for A2DP connection to 2 A2DP sources for music playback

- Secure simple pairing, CSR's proximity pairing and CSR's proximity connections

- Stereo line-in

- Serial interfaces: USB 2.0, UART, I<sup>2</sup>C and SPI

- SBC and AAC decoder support

- Wired audio support

- Integrated dual switch-mode regulators, linear regulators and battery charger

- External crystal load capacitors not required for typical crystals

- 3 LED outputs (RGB)

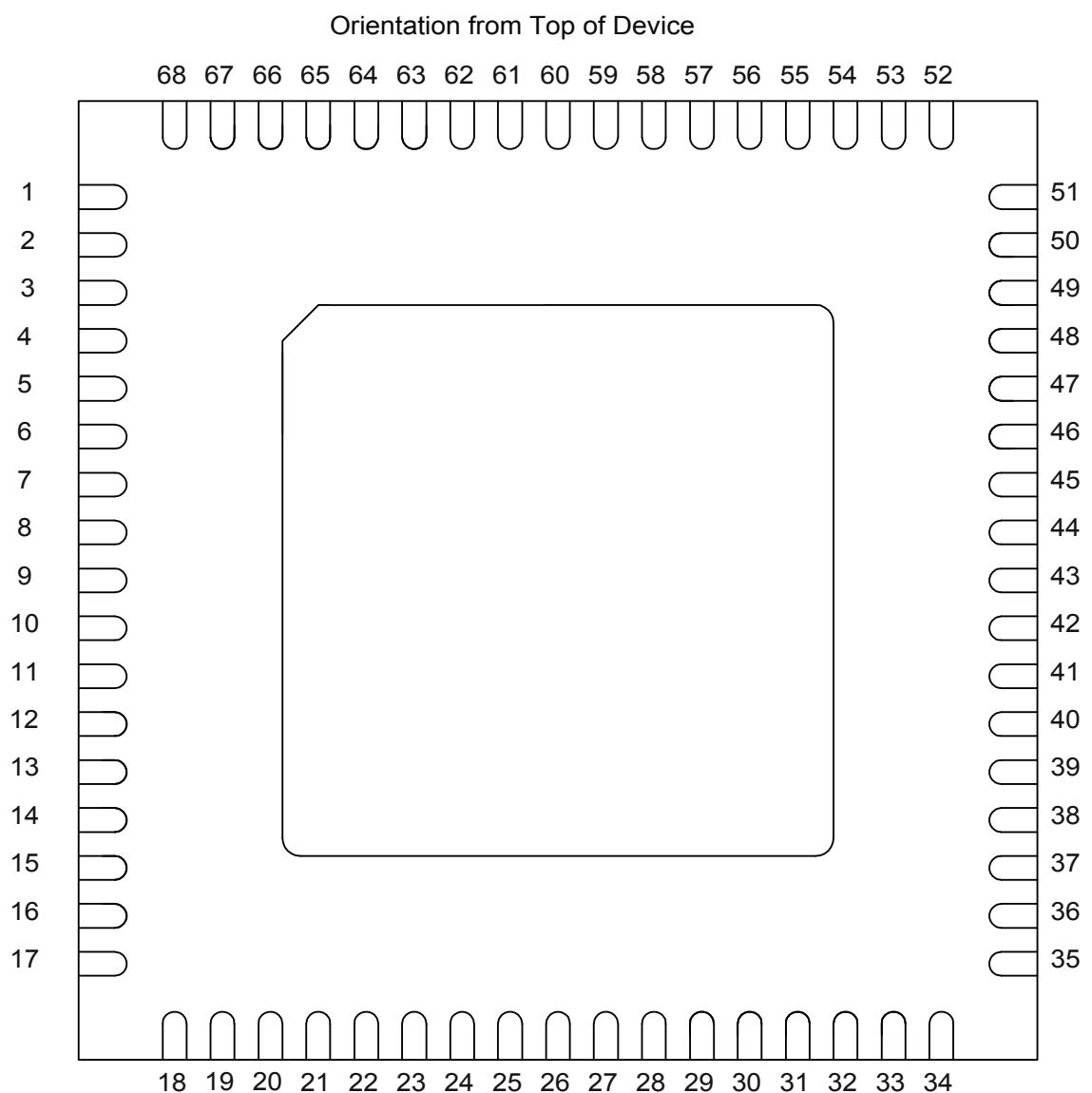

- 68-lead QFN 8 x 8 x 0.9 mm 0.4 mm pitch

- Green (RoHS compliant and no antimony or halogenated flame retardants)

## General Description

CSRA64210 QFN is a single-chip Bluetooth ROM audio solution for rapid evaluation and development of Bluetooth ROM stereo applications.

The CSRA64210 QFN consumer audio platform for wired and wireless applications using the QFN package integrates an ultra-low power DSP and application processor, high-performance stereo codec, a power management subsystem and LED drivers.

The CSR configuration tools and the development kit provide a flexible and powerful development platform to design advanced and high-quality Bluetooth stereo products using the CSRA64210 QFN single-chip Bluetooth audio solution.

## BlueCore® CSRA64210 QFN

### CSRA64210 Stereo ROM Solution

#### 1-mic cVc® Hands-free Audio Enhancement

#### Fully Qualified Single-chip Bluetooth® v4.2 System

Engineering Sample

CSRA64210A11

Issue 1

## Applications

- Stereo speakers

- Speakerphones

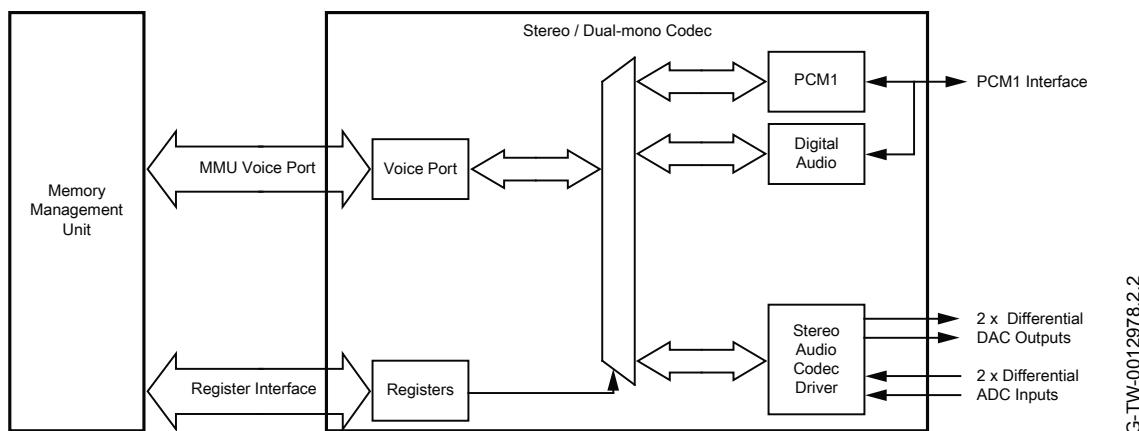

The enhanced Kalimba DSP coprocessor with 80 MIPS supports enhanced audio and DSP applications.

The integrated audio codec supports stereo input and output with 1-mic cVc hands-free input, 1 digital microphone (MEMS) interface, as well as a variety of audio standards.

See *CSR Glossary* at <https://www.csrsupport.com>

## Ordering Information

| Device                              | Package                  |                                |                 | Order Number        |

|-------------------------------------|--------------------------|--------------------------------|-----------------|---------------------|

|                                     | Type                     | Size                           | Shipment Method |                     |

| CSRA64210<br>Stereo ROM<br>Solution | QFN-68-lead<br>(Pb free) | 8 x 8 x 0.9 mm<br>0.4 mm pitch | Tape and reel   | CSRA64210A11-IQQF-R |

**Note:**

Until CSRA64210 QFN reaches **Production** status, engineering samples order number applies. This is ES-CSRA64210A11-IQQF, with no minimum order quantity.

CSRA64210 QFN is a ROM-based device where the product code has the form CSRA64210Axx. Axx is the specific ROM-variant, A11 is the ROM-variant for CSRA64210 Stereo ROM Solution.

At **Production** status minimum order quantity is 2kpcs taped and reeled.

Your attention is drawn to Cambridge Silicon Radio Limited's ("Seller"'s ) standard terms of supply which govern the supply of **Prototype Products** or **Engineering Samples** and which state in clause 5:

5.1 "Prototype Products" or "Engineering Samples" means any products that have not passed all the stages of full production acceptance as determined solely by the Seller. The Seller will usually identify which of the Goods ordered are considered Prototype Products designating them "ES" on the Quotation and any Order for Prototype Products shall be subject to the special terms contained in this clause 5.

5.2 The Seller has used reasonable efforts to design and build the Prototype Products in accordance with the relevant specification, but because the testing carried out by the Seller in respect of the Prototype Products is incomplete, the Seller does not give or enter into any warranties, conditions or other terms in relation to quality or fitness for purpose of the Prototype Products and/or that the Prototype Products are free from bugs, errors or omissions.

**Supply chain:** CSR's manufacturing policy is to multisource volume products. For further details, contact your local sales account manager or representative.

## Contacts

General information

[www.csr.com](http://www.csr.com)

Information on this product

[sales@csr.com](mailto:sales@csr.com)

Customer support for this product

[www.csrsupport.com](http://www.csrsupport.com)

Details of compliance and standards

[product.compliance@csr.com](mailto:product.compliance@csr.com)

Help with this document

[comments@csr.com](mailto:comments@csr.com)

## CSRA64210 Stereo ROM Solution Development Kit Ordering Information

| Description                                         | Order Number     |

|-----------------------------------------------------|------------------|

| CSRA64210 Stereo ROM Solution Audio Development Kit | DK-64210-TBD-TBD |

## Device Details

### Bluetooth low energy

- Dual-mode Bluetooth low energy radio

### Bluetooth Radio

- On-chip balun (50 Ω impedance)

- No production trimming of external components

- Bluetooth v4.2 specification compliant

### Bluetooth Transmitter

- 8 dBm (typ) RF transmit power with level control

- Class 1, Class 2 and Class 3 support, no external PA or TX/RX switch required

### Bluetooth Receiver

- -91 dBm (typ) π/4 DQPSK receiver sensitivity and -81 dBm (typ) 8DPSK receiver sensitivity

- Integrated channel filters

- Digital demodulator for improved sensitivity and co-channel rejection

- Real-time digitised RSSI available to application

- Fast AGC for enhanced dynamic range

- Channel classification for AFH

### Bluetooth Synthesiser

- Fully integrated synthesiser requires no external VCO, varactor diode, resonator or loop filter

- Compatible with crystals 16 MHz to 32 MHz

### Kalimba DSP

- Enhanced Kalimba DSP coprocessor, 80 MIPS, 24-bit fixed point core

- 2 single-cycle MACs: 24 x 24-bit multiply and 56-bit accumulator

- 32-bit instruction word, dual 24-bit data memory

- 6K x 32-bit program RAM including 1K instruction cache for executing out of internal ROM

- 16K x 24-bit + 16K x 24-bit 2-bank data RAM

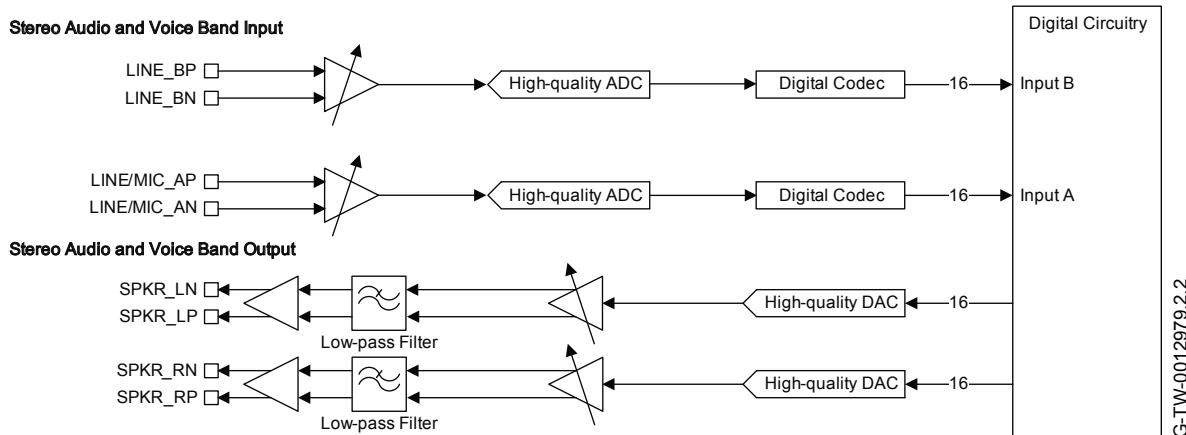

### Audio Interfaces

- Stereo audio ADC with line input

- Stereo audio DAC

- Supported sample rates of 8, 11.025, 16, 22.05, 32, 44.1, 48 and 96 kHz (DAC only)

### Auxiliary Features

- Crystal oscillator with built-in digital trimming

### Package Option

- 68-lead QFN 8 x 8 x 0.9 mm 0.4 mm pitch

### Physical Interfaces

- UART interface for debug

- USB 2.0 (full-speed) interface, including USB BC1.2 charger detection

- 4-bit SPI flash memory interface

- SPI interface for debug and programming

- I<sup>2</sup>C master for amp control

- Up to 14 general purpose PIOs with 3 extra open-drain PIOs available when LED not used

- PCM and I<sup>2</sup>S interfaces

- 3 LED drivers (includes RGB) with PWM flasher independent of MCU

### Integrated Power Control and Regulation

- Automatic power switching to charger when present

- 2 high-efficiency switch-mode regulators with 1.8 V and 1.35 V outputs direct from battery supply

- 3.3 V linear regulator for USB supply

- Low-voltage linear regulator for internal digital circuits

- Low-voltage linear regulator for internal analogue circuits

- Power-on-reset detects low supply voltage

- Power management includes digital shutdown and wake-up commands for ultra-low power modes

### Battery Charger

- Lithium ion / Lithium polymer battery charger

- Instant-on function automatically selects the power supply between battery and USB, which enables operation even if the battery is fully discharged

- Fast charging support up to 200 mA with no external components. Higher charge currents using external pass device.

- Supports USB charger detection

- Support for thermistor protection of battery pack

- Support to enable end product design to PSE law:

- Design to JIS-C 8712/8714 (batteries)

- Testing based on IEEE 1725

### Baseband and Software

- Internal ROM

- Memory protection unit supporting accelerated VM

- 56 KB internal RAM, enables full-speed data transfer, and full piconet support

- Logic for forward error correction, header error control, access code correlation, CRC, demodulation, encryption bit stream generation, whitening and transmit pulse shaping

## CSRA64210 Stereo ROM Solution Details

### Bluetooth Profiles

- Bluetooth v4.2 specification support

- A2DP v1.3

- AVRCP v1.5

- HFP v1.6

- HSP v1.2

- DI v1.3

### Music Enhancements

- SBC and AAC

- TrueWireless Stereo (TWS)

- Configurable Signal Detection to trigger events

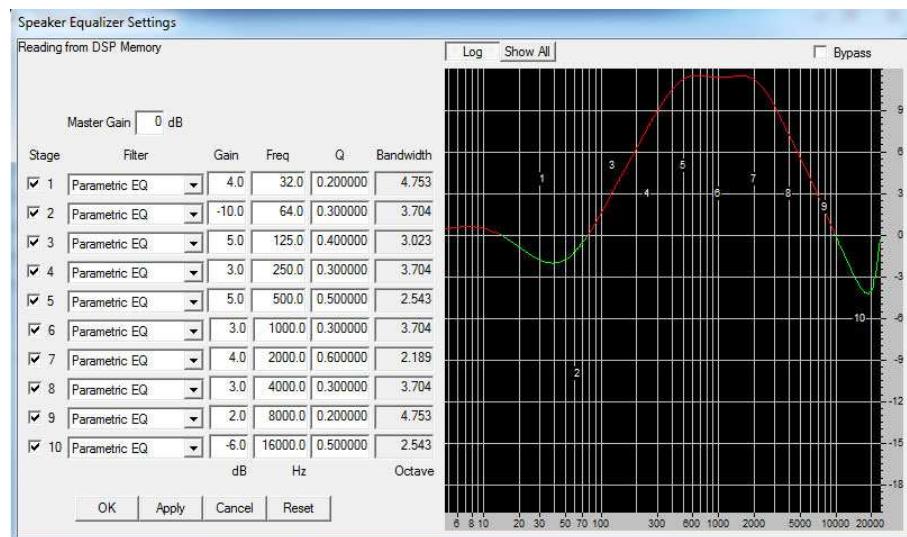

- Up to 10 stages of Speaker Parametric EQ

- Up to 6 banks of 5 stages of User Parametric EQ for music playback (user, rock, pop, classical, jazz, etc)

- MeloD® Expansion 3D stereo widening and phase shifting effect

- Volume Control

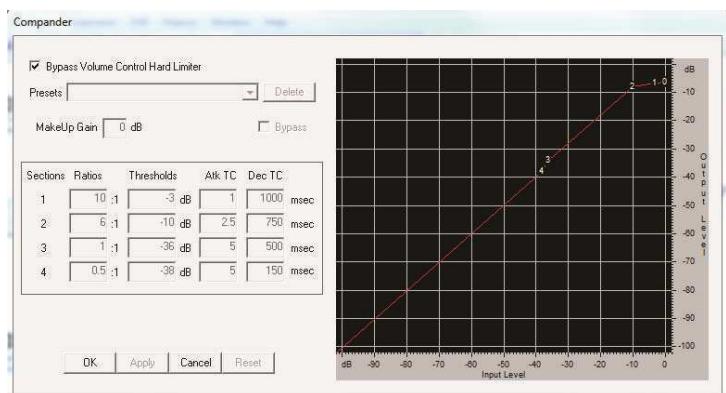

- Compander to compress or expand the dynamic range of the audio

- Post Mastering to improve DAC fidelity

- Volume Boost

### Additional Functionality

- Support for multi-language programmable audio prompts

- CSR's proximity pairing and CSR's proximity connection

- Multipoint support for A2DP connection to 2 A2DP sources for music playback

- Talk-time extension

### CSRA64xxx ROM Series Configuration Tool

Configures the CSRA64210 stereo ROM solution software features:

- Bluetooth v4.2 specification features

- Reconnection policies, e.g. reconnect on power-on

- Audio features, including default volumes

- Button events: configuring button presses and durations for certain events, e.g. double press on PIO for last number redial

- LED indications for states, e.g. device connected, and events, e.g. power on

- Indication tones for events and ringtones

- Battery divider ratios and thresholds, e.g. thresholds for battery low indication, full battery etc.

- Advanced Multipoint settings

### CSRA64210 Stereo ROM Solution Development Kit

- Example CSRA64210 QFN module design

- Carrier board

- Output stage: headphone amplifier

- Interface adapters and cables

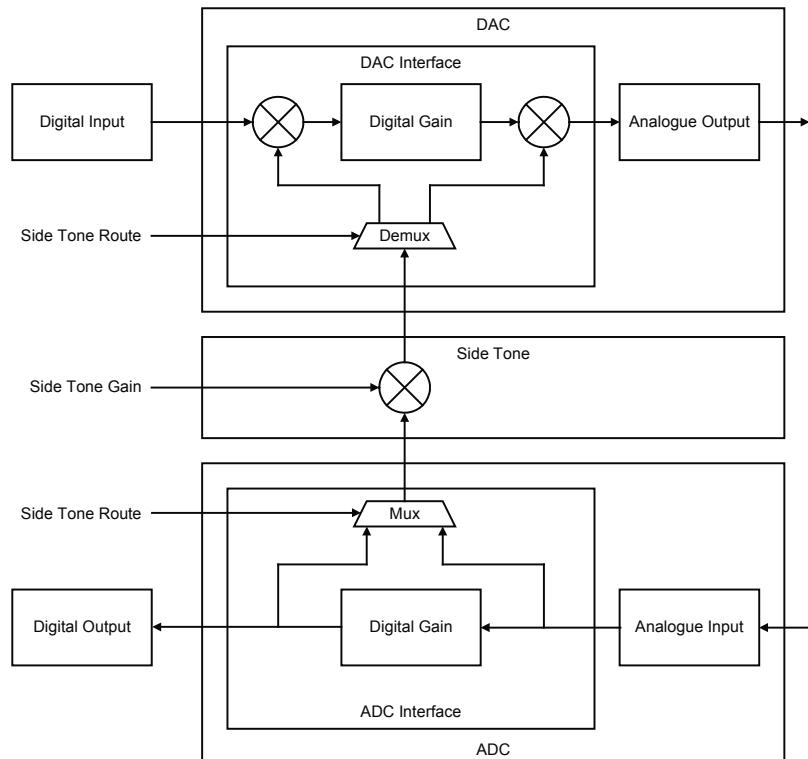

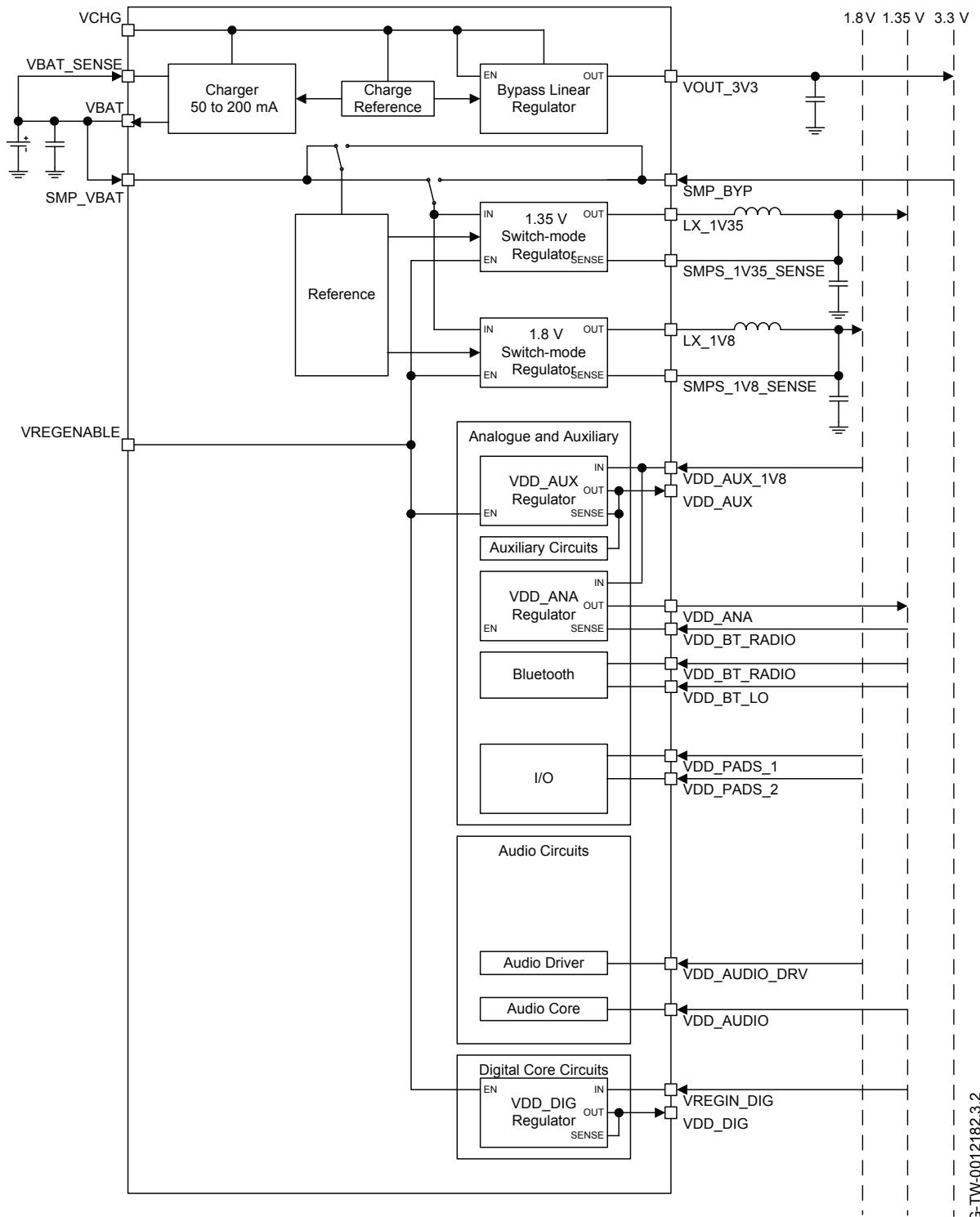

## Functional Block Diagram

GTW001441.23

## Document History

| Revision | Date      | Change Reason                          |

|----------|-----------|----------------------------------------|

| Issue 1  | 29 JUL 15 | Original publication of this document. |

## Status Information

The status of this Data Sheet is **Engineering Sample**. CSR Product Data Sheets progress according to the following format:

- **Advance Information:**

- Information for designers concerning CSR product in development. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

- **Engineering Sample:**

- Information about initial devices. Devices are untested or partially tested prototypes, their status is described in an Engineering Sample Release Note. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

- All detailed specifications including pinouts and electrical specifications may be changed by CSR without notice.

- **Pre-production Information:**

- Pinout and mechanical dimension specifications finalised. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

- All electrical specifications may be changed by CSR without notice.

- **Production Information:**

- Final Data Sheet including the guaranteed minimum and maximum limits for the electrical specifications.

- Production Data Sheets supersede all previous document versions.

### Device Implementation

#### Important Note:

As the feature-set of the CSRA64210 QFN is firmware build-specific, see the relevant software release note for the exact implementation of features on the CSRA64210 QFN.

### Life Support Policy and Use in Safety-critical Applications

CSR's products are not authorised for use in life-support or safety-critical applications. Use in such applications is done at the sole discretion of the customer. CSR will not warrant the use of its devices in such applications.

### CSR Green Semiconductor Products and RoHS Compliance

CSRA64210 QFN devices meet the requirements of Directive 2011/65/EU of the European Parliament and of the Council on the Restriction of Hazardous Substance (RoHS). CSRA64210 QFN devices are free from halogenated or antimony trioxide-based flame retardants and other hazardous chemicals. For more information, see CSR's *Environmental Compliance Statement for CSR Green Semiconductor Products*.

### Trademarks, Patents and Licences

Unless otherwise stated, words and logos marked with <sup>TM</sup> or <sup>®</sup> are trademarks registered or owned by CSR plc or its affiliates. Bluetooth <sup>®</sup> and the Bluetooth <sup>®</sup> logos are trademarks owned by Bluetooth <sup>®</sup> SIG, Inc. and licensed to CSR. Other products, services and names used in this document may have been trademarked by their respective owners.

The publication of this information does not imply that any license is granted under any patent or other rights owned by CSR plc and/or its affiliates.

CSR reserves the right to make technical changes to its products as part of its development programme.

While every care has been taken to ensure the accuracy of the contents of this document, CSR cannot accept responsibility for any errors.

Refer to [www.csrsupport.com](http://www.csrsupport.com) for compliance and conformance to standards information.

## Contents

|                                                                    |    |

|--------------------------------------------------------------------|----|

| <b>Ordering Information</b>                                        | 2  |

| Contacts                                                           | 2  |

| CSRA64210 Stereo ROM Solution Development Kit Ordering Information | 2  |

| <b>Device Details</b>                                              | 3  |

| <b>CSRA64210 Stereo ROM Solution Details</b>                       | 4  |

| <b>Functional Block Diagram</b>                                    | 5  |

| <b>1 Package Information</b>                                       | 13 |

| 1.1 Pinout Diagram                                                 | 13 |

| 1.2 Device Terminal Functions                                      | 14 |

| 1.3 Package Dimensions                                             | 20 |

| 1.4 PCB Design and Assembly Considerations                         | 21 |

| 1.5 Typical Solder Reflow Profile                                  | 21 |

| <b>2 Bluetooth Modem</b>                                           | 22 |

| 2.1 RF Ports (BT_RF)                                               | 22 |

| 2.2 RF Receiver                                                    | 22 |

| 2.2.1 Low Noise Amplifier                                          | 22 |

| 2.2.2 RSSI Analogue to Digital Converter                           | 22 |

| 2.3 RF Transmitter                                                 | 22 |

| 2.3.1 IQ Modulator                                                 | 22 |

| 2.3.2 Power Amplifier                                              | 23 |

| 2.4 Bluetooth Radio Synthesiser                                    | 23 |

| 2.5 Baseband                                                       | 23 |

| <b>3 Clock Generation</b>                                          | 24 |

| 3.1 Crystal                                                        | 24 |

| 3.1.1 Negative Resistance Model                                    | 25 |

| 3.1.2 Crystal Specification                                        | 25 |

| 3.1.3 Crystal Calibration                                          | 25 |

| 3.2 Non-crystal Oscillator                                         | 26 |

| 3.2.1 XTAL_IN Impedance in Non-crystal Mode                        | 27 |

| <b>4 Processors</b>                                                | 28 |

| 4.1 Bluetooth Stack Microcontroller                                | 28 |

| 4.2 Kalimba DSP                                                    | 28 |

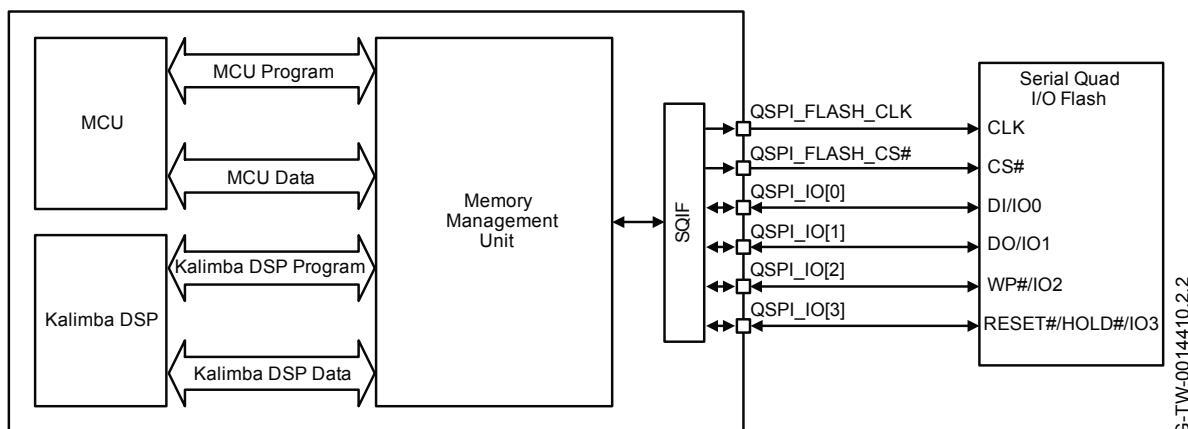

| <b>5 Memory Interface and Management</b>                           | 29 |

| 5.1 Memory Management Unit                                         | 29 |

| 5.2 System RAM                                                     | 29 |

| 5.3 Kalimba DSP RAM                                                | 29 |

| 5.4 Internal ROM                                                   | 29 |

| 5.5 Serial Quad I/O Flash Interface (SQIF)                         | 29 |

| <b>6 Serial Interfaces</b>                                         | 31 |

| 6.1 USB Interface                                                  | 31 |

| 6.2 UART Interface                                                 | 31 |

| 6.3 Programming and Debug Interface                                | 33 |

| 6.3.1 Multi-slave Operation                                        | 33 |

| 6.4 I <sup>2</sup> C Interface                                     | 33 |

| <b>7 Interfaces</b>                                                | 34 |

| 7.1 Programmable I/O Ports, PIO                                    | 34 |

| 7.2 Analogue I/O Ports, AIO                                        | 34 |

| 7.3 LED Drivers                                                    | 35 |

| <b>8 Audio Interface</b>                                           | 36 |

|           |                                                         |           |

|-----------|---------------------------------------------------------|-----------|

| 8.1       | Audio Input and Output .....                            | 36        |

| 8.2       | Audio Codec Interface .....                             | 37        |

| 8.2.1     | Audio Codec Block Diagram .....                         | 37        |

| 8.2.2     | ADC .....                                               | 37        |

| 8.2.3     | ADC Sample Rate Selection .....                         | 37        |

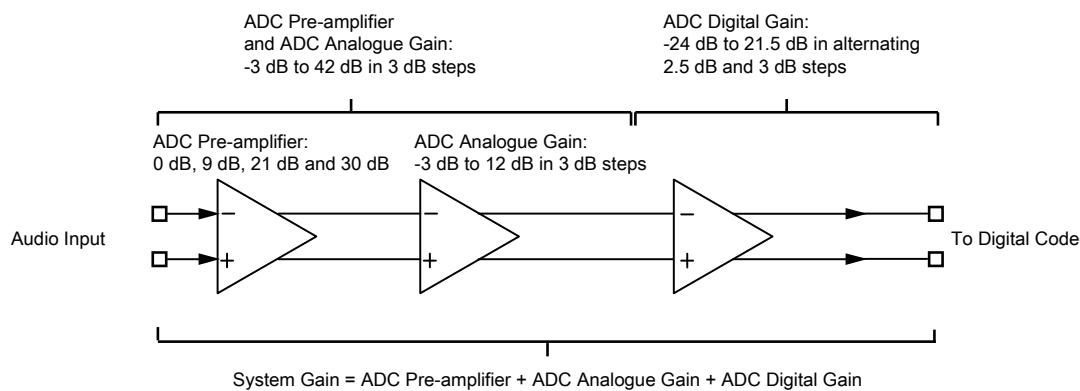

| 8.2.4     | ADC Audio Input Gain .....                              | 38        |

| 8.2.5     | ADC Pre-amplifier and ADC Analogue Gain .....           | 38        |

| 8.2.6     | ADC Digital Gain .....                                  | 38        |

| 8.2.7     | ADC Digital IIR Filter .....                            | 39        |

| 8.2.8     | DAC .....                                               | 39        |

| 8.2.9     | DAC Sample Rate Selection .....                         | 39        |

| 8.2.10    | DAC Digital Gain .....                                  | 39        |

| 8.2.11    | DAC Analogue Gain .....                                 | 39        |

| 8.2.12    | DAC Digital FIR Filter .....                            | 40        |

| 8.2.13    | Microphone Input .....                                  | 40        |

| 8.2.14    | Line Input .....                                        | 41        |

| 8.2.15    | Output Stage .....                                      | 41        |

| 8.2.16    | Mono Operation .....                                    | 42        |

| 8.2.17    | Side Tone .....                                         | 43        |

| 8.2.18    | Integrated Digital IIR Filter .....                     | 44        |

| 8.3       | PCM1 and PCM2 Interface .....                           | 45        |

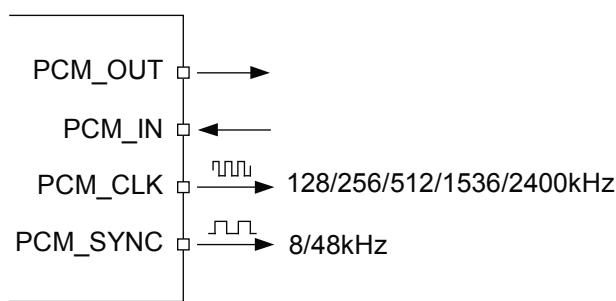

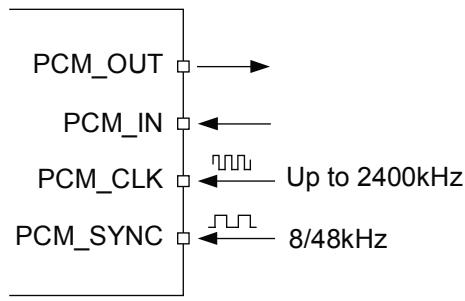

| 8.3.1     | PCM Interface Master/Slave .....                        | 45        |

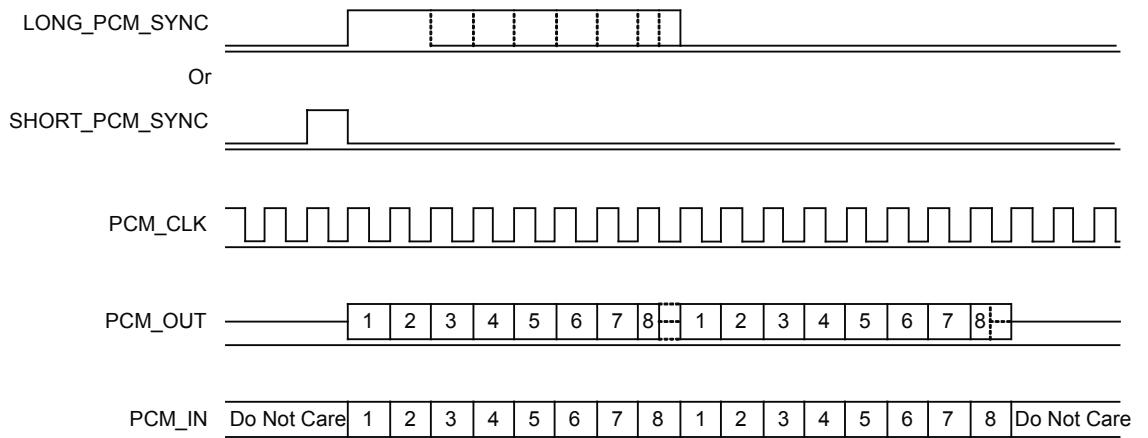

| 8.3.2     | Long Frame Sync .....                                   | 46        |

| 8.3.3     | Short Frame Sync .....                                  | 47        |

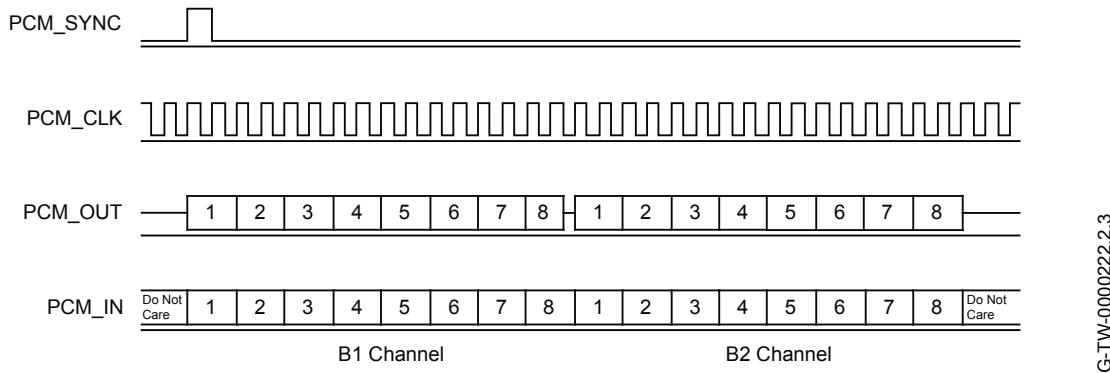

| 8.3.4     | Multi-slot Operation .....                              | 47        |

| 8.3.5     | GCI Interface .....                                     | 48        |

| 8.3.6     | Slots and Sample Formats .....                          | 48        |

| 8.3.7     | Additional Features .....                               | 49        |

| 8.3.8     | PCM Timing Information .....                            | 49        |

| 8.3.9     | PCM_CLK and PCM_SYNC Generation .....                   | 53        |

| 8.3.10    | PCM Configuration .....                                 | 53        |

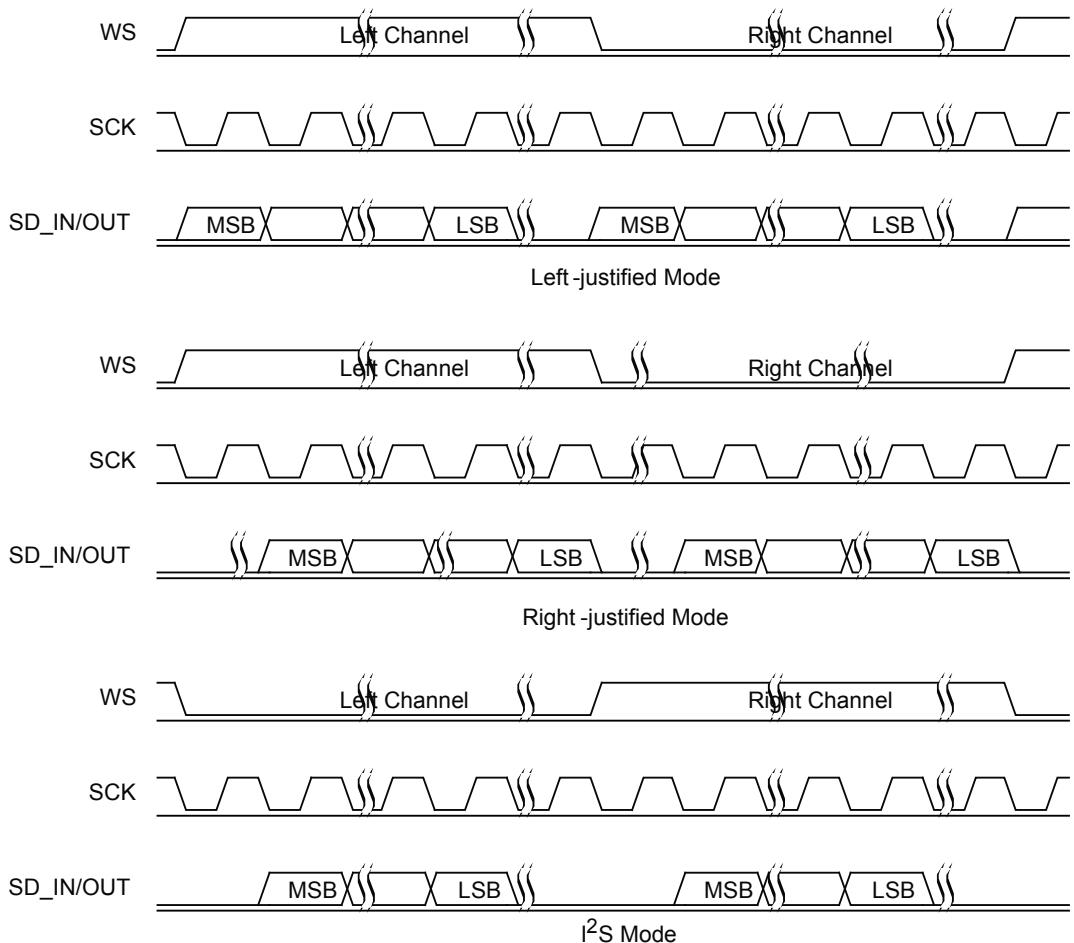

| 8.4       | I <sup>2</sup> S1 and I <sup>2</sup> S2 Interface ..... | 53        |

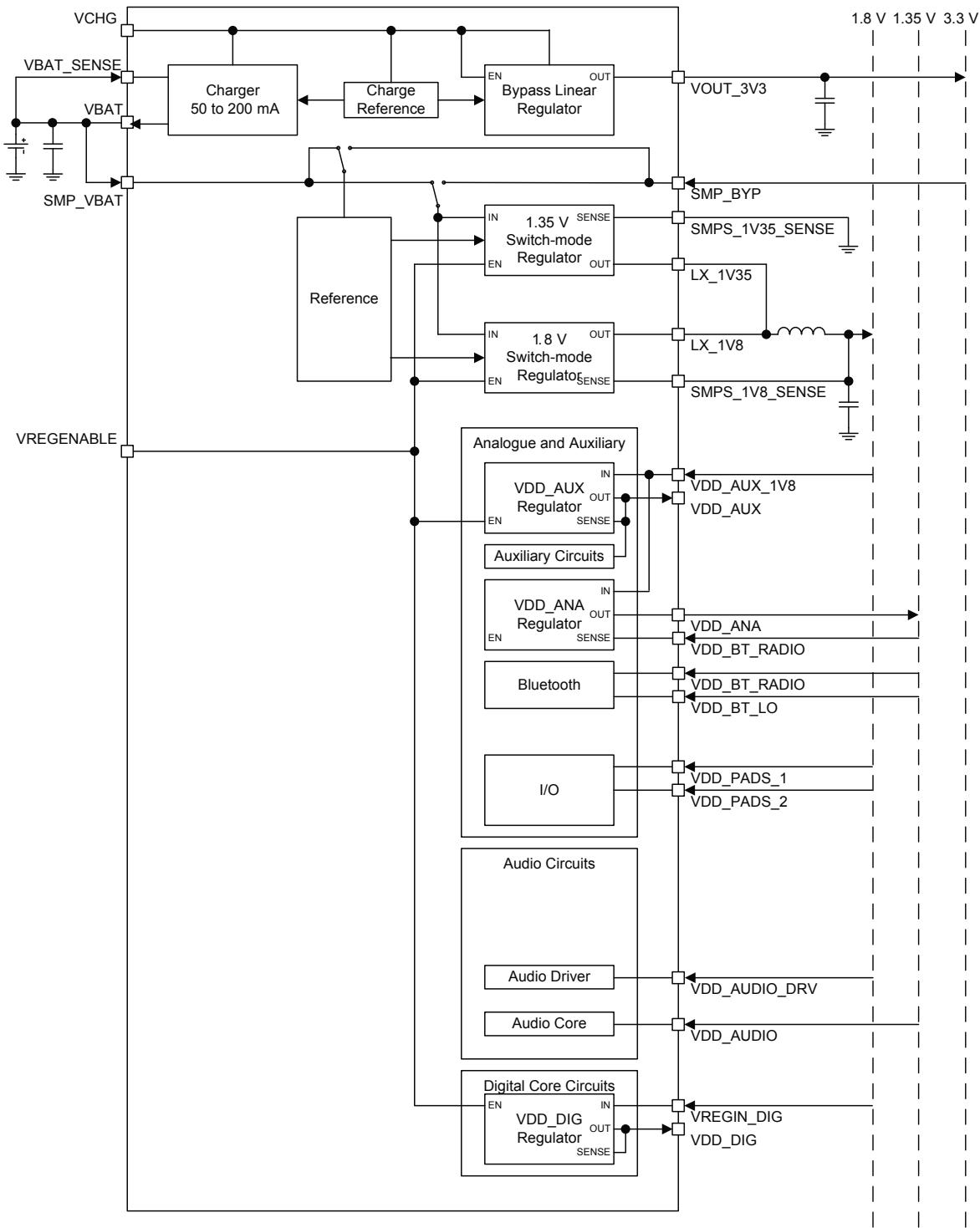

| <b>9</b>  | <b>Power Control and Regulation .....</b>               | <b>58</b> |

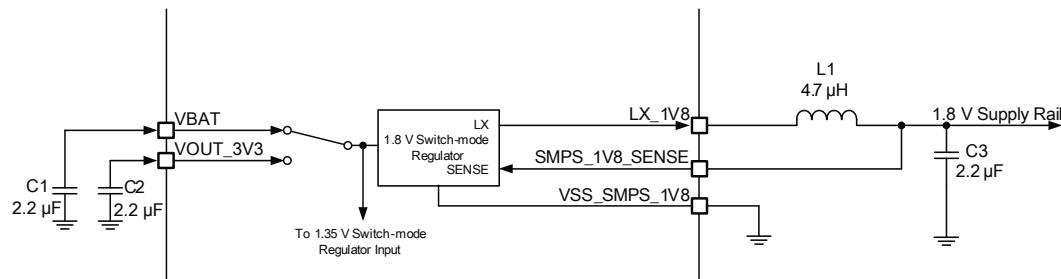

| 9.1       | 1.8 V Switch-mode Regulator .....                       | 61        |

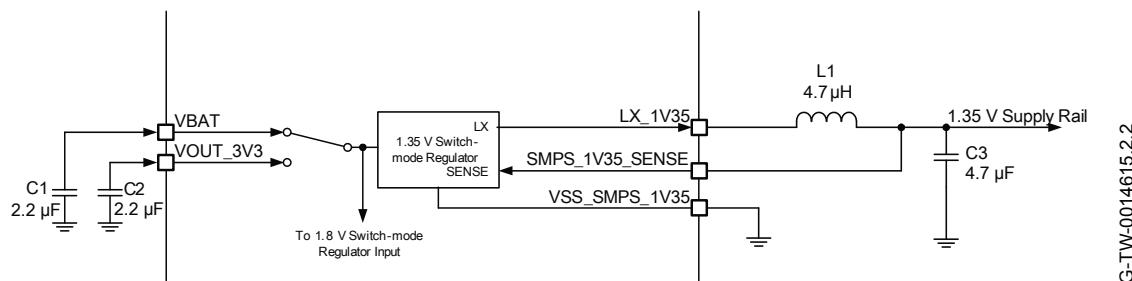

| 9.2       | 1.35 V Switch-mode Regulator .....                      | 62        |

| 9.3       | 1.8 V and 1.35 V Switch-mode Regulators Combined .....  | 63        |

| 9.3.1     | Inductor Choice .....                                   | 63        |

| 9.4       | Bypass LDO Linear Regulator .....                       | 64        |

| 9.5       | Low-voltage VDD_DIG Linear Regulator .....              | 64        |

| 9.6       | Low-voltage VDD_AUX Linear Regulator .....              | 65        |

| 9.7       | Low-voltage VDD_ANA Linear Regulator .....              | 65        |

| 9.8       | Voltage Regulator Enable .....                          | 65        |

| 9.9       | External Regulators and Power Sequencing .....          | 65        |

| 9.10      | Reset, RST# .....                                       | 65        |

| 9.10.1    | Digital Pin States on Reset .....                       | 66        |

| 9.10.2    | Status After Reset .....                                | 66        |

| 9.11      | Automatic Reset Protection .....                        | 66        |

| <b>10</b> | <b>Battery Charger .....</b>                            | <b>67</b> |

| 10.1      | Battery Charger Hardware Operating Modes .....          | 67        |

| 10.1.1    | Disabled Mode .....                                     | 68        |

| 10.1.2    | Trickle Charge Mode .....                               | 68        |

| 10.1.3    | Fast Charge Mode .....                                  | 68        |

|           |                                                                                                 |           |

|-----------|-------------------------------------------------------------------------------------------------|-----------|

| 10.1.4    | Standby Mode .....                                                                              | 68        |

| 10.1.5    | Error Mode .....                                                                                | 68        |

| 10.2      | Battery Charger Trimming and Calibration .....                                                  | 68        |

| 10.3      | VM Battery Charger Control .....                                                                | 68        |

| 10.4      | Battery Charger Firmware and PS Keys .....                                                      | 68        |

| 10.5      | External Mode .....                                                                             | 69        |

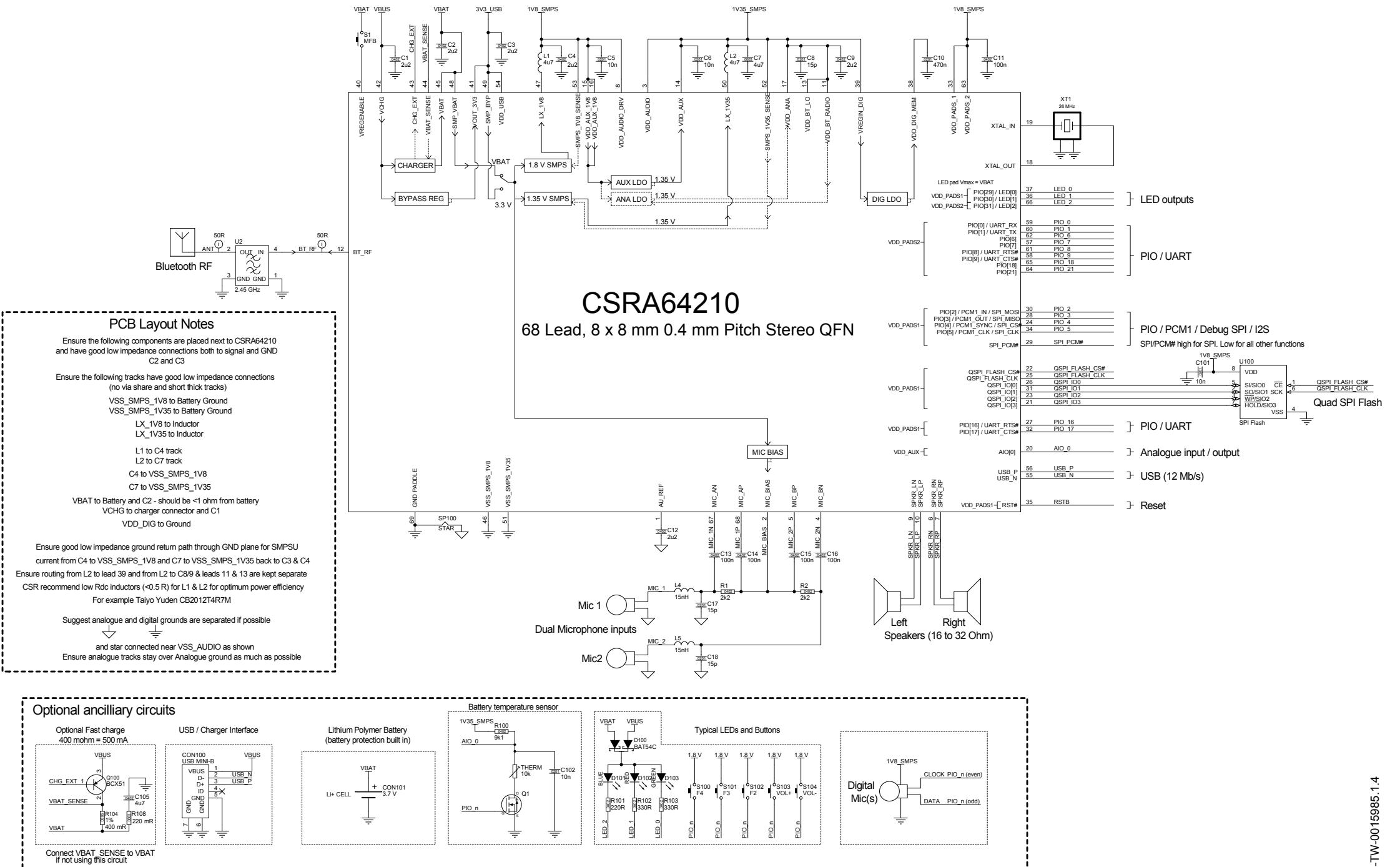

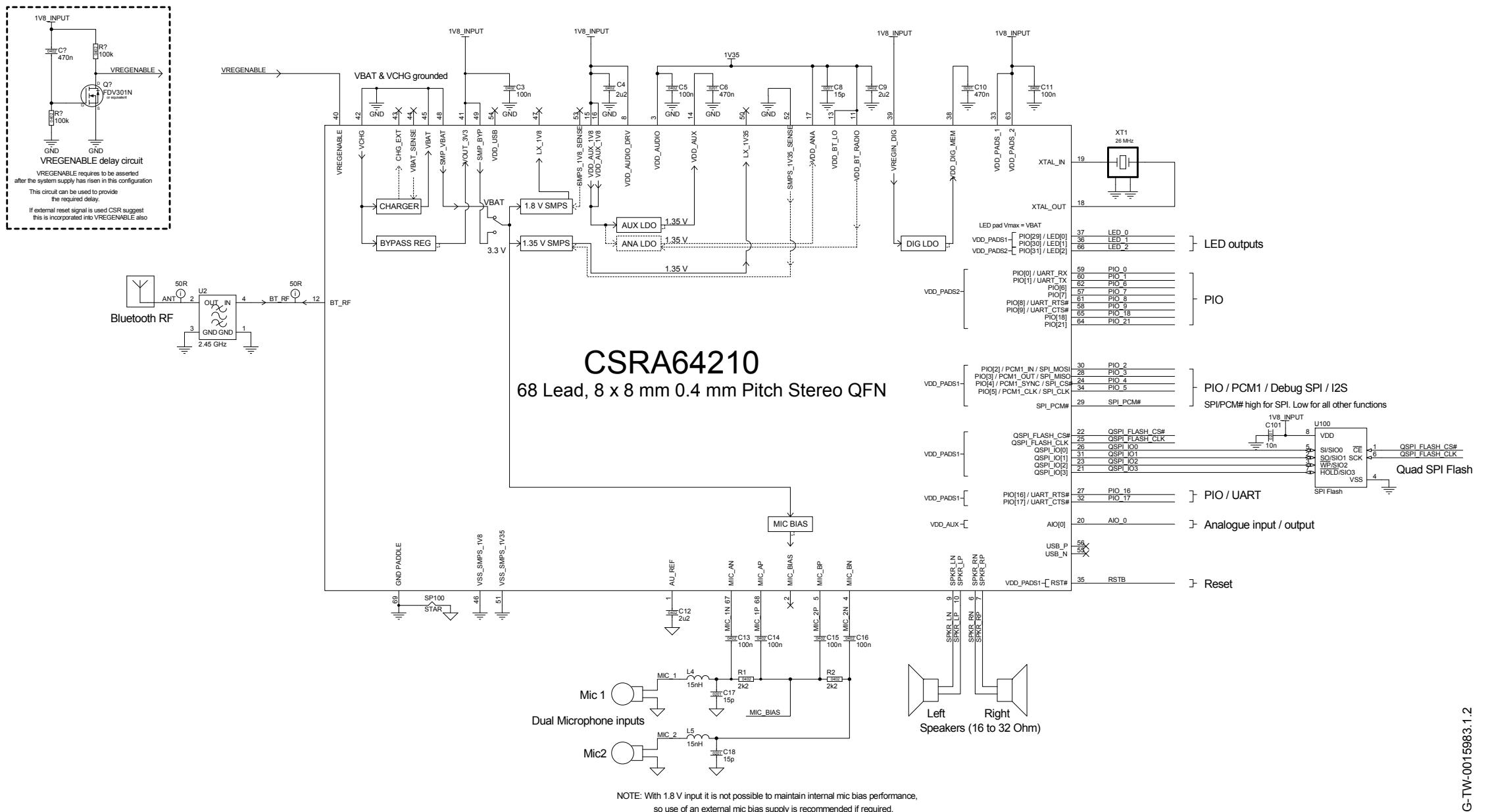

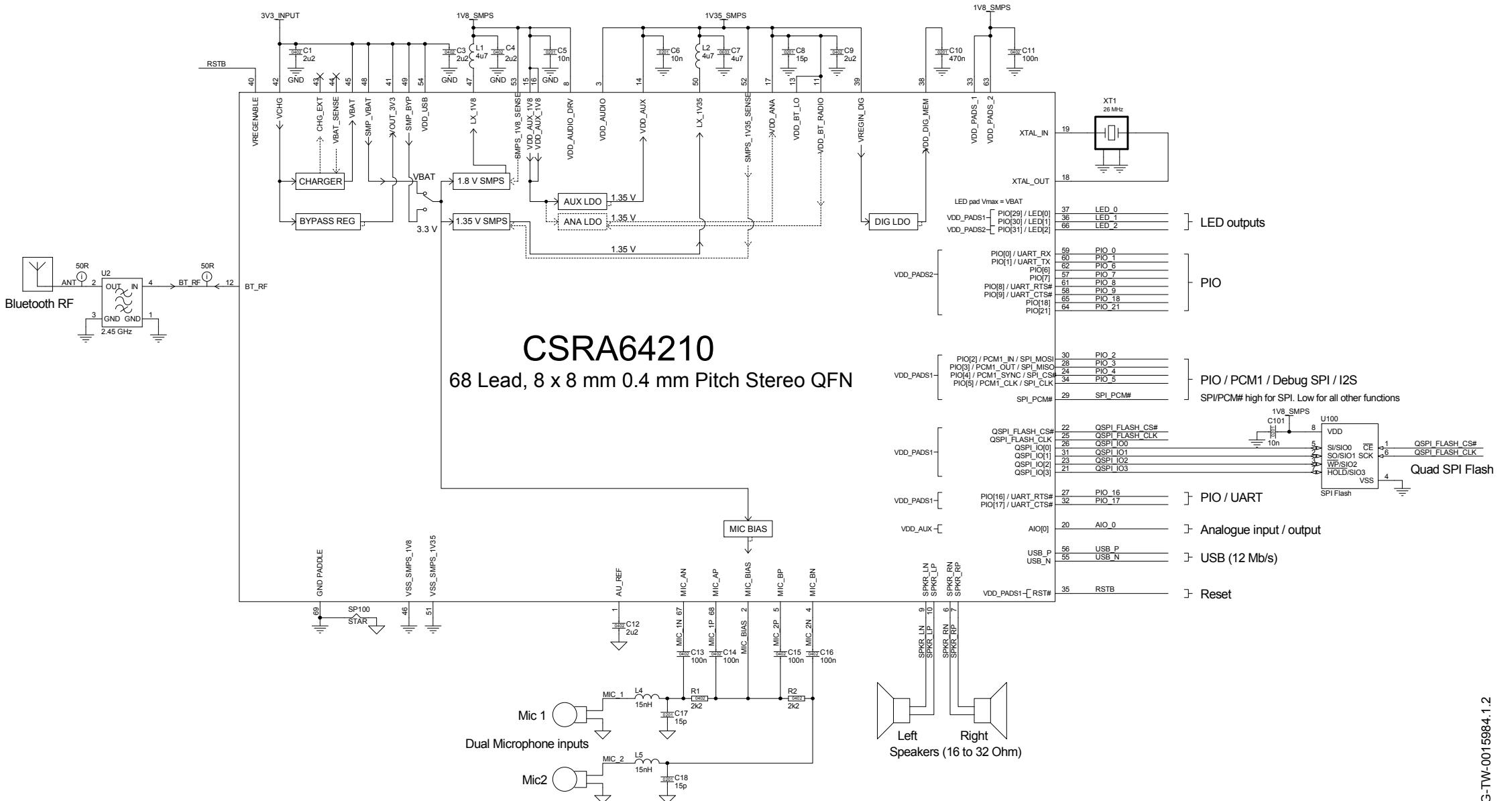

| <b>11</b> | <b>Example Application Schematic .....</b>                                                      | <b>70</b> |

| <b>12</b> | <b>Electrical Characteristics .....</b>                                                         | <b>73</b> |

| 12.1      | Absolute Maximum Ratings .....                                                                  | 73        |

| 12.2      | Recommended Operating Conditions .....                                                          | 74        |

| 12.3      | Input/Output Terminal Characteristics .....                                                     | 75        |

| 12.3.1    | Regulators: Available For External Use .....                                                    | 75        |

| 12.3.2    | Regulators: For Internal Use Only .....                                                         | 77        |

| 12.3.3    | Regulator Enable .....                                                                          | 78        |

| 12.3.4    | Battery Charger .....                                                                           | 78        |

| 12.3.5    | USB .....                                                                                       | 80        |

| 12.3.6    | Stereo Codec: Analogue to Digital Converter .....                                               | 81        |

| 12.3.7    | Stereo Codec: Digital to Analogue Converter .....                                               | 82        |

| 12.3.8    | Digital .....                                                                                   | 83        |

| 12.3.9    | LED Driver Pads .....                                                                           | 83        |

| 12.3.10   | Auxiliary ADC .....                                                                             | 84        |

| 12.3.11   | Auxiliary DAC .....                                                                             | 84        |

| 12.4      | ESD Protection .....                                                                            | 85        |

| 12.4.1    | USB Electrostatic Discharge Immunity .....                                                      | 85        |

| <b>13</b> | <b>Power Consumption .....</b>                                                                  | <b>87</b> |

| <b>14</b> | <b>CSR Green Semiconductor Products and RoHS Compliance .....</b>                               | <b>89</b> |

| <b>15</b> | <b>Software .....</b>                                                                           | <b>90</b> |

| 15.1      | CSRA64210 Stereo ROM Solution .....                                                             | 90        |

| 15.1.1    | Advanced Multipoint Support .....                                                               | 91        |

| 15.1.2    | A2DP Multipoint Support .....                                                                   | 91        |

| 15.1.3    | Wired Audio Mode .....                                                                          | 91        |

| 15.1.4    | USB Modes Including USB Audio Mode .....                                                        | 91        |

| 15.1.5    | Smartphone Applications (Apps) .....                                                            | 92        |

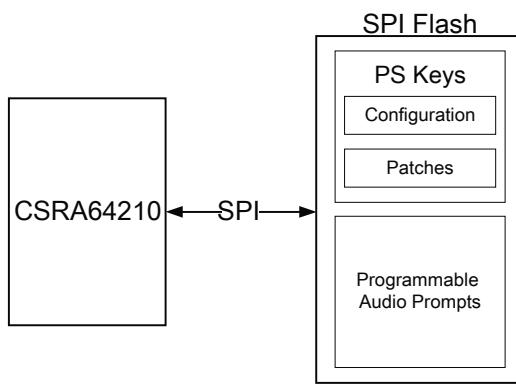

| 15.1.6    | Programmable Audio Prompts .....                                                                | 92        |

| 15.1.7    | CSR's Intelligent Power Management .....                                                        | 92        |

| 15.1.8    | Proximity Pairing .....                                                                         | 93        |

| 15.1.9    | Proximity Connection .....                                                                      | 93        |

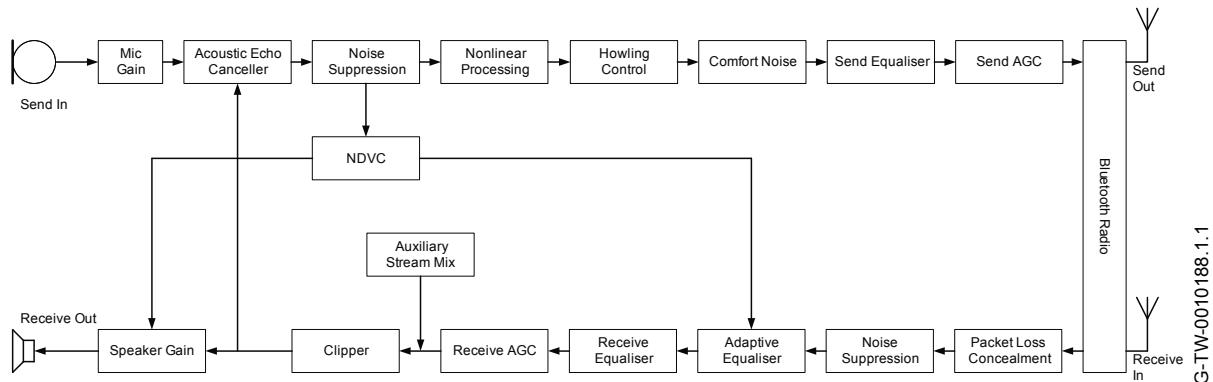

| 15.2      | 8 <sup>th</sup> Generation 1-mic cVc ENR Technology for Hands-free and Audio Enhancements ..... | 93        |

| 15.2.1    | Acoustic Echo Cancellation .....                                                                | 94        |

| 15.2.2    | Noise Suppression with Wind Noise Reduction .....                                               | 94        |

| 15.2.3    | Non-linear Processing .....                                                                     | 94        |

| 15.2.4    | Howling Control .....                                                                           | 94        |

| 15.2.5    | Comfort Noise Generator .....                                                                   | 94        |

| 15.2.6    | Equalisation .....                                                                              | 95        |

| 15.2.7    | Automatic Gain Control .....                                                                    | 95        |

| 15.2.8    | Packet Loss Concealment .....                                                                   | 95        |

| 15.2.9    | Adaptive Equalisation .....                                                                     | 95        |

| 15.2.10   | Auxiliary Stream Mix .....                                                                      | 96        |

| 15.2.11   | Clipper .....                                                                                   | 96        |

| 15.2.12   | Noise Dependent Volume Control .....                                                            | 96        |

| 15.2.13   | Input Output Gains .....                                                                        | 96        |

| 15.3      | Music Enhancements .....                                                                        | 96        |

|           |                                                     |            |

|-----------|-----------------------------------------------------|------------|

| 15.3.1    | Audio Decoders .....                                | 96         |

| 15.3.2    | Configurable EQ .....                               | 97         |

| 15.3.3    | Stereo Widening (S3D) .....                         | 97         |

| 15.3.4    | Volume Boost .....                                  | 97         |

| 15.4      | CSRA64210 Stereo ROM Solution Development Kit ..... | 98         |

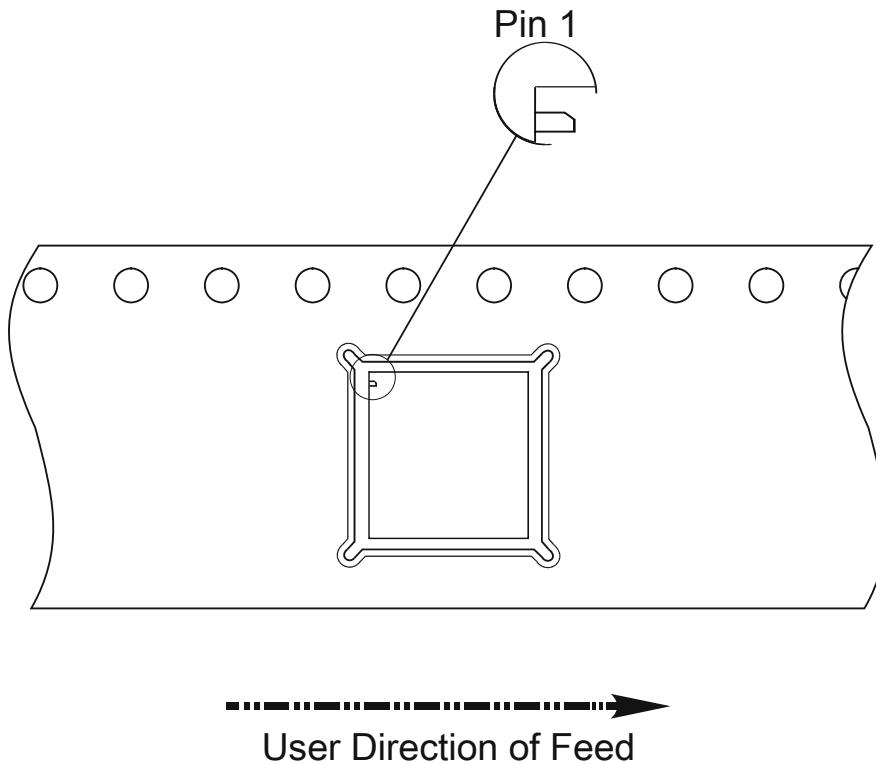

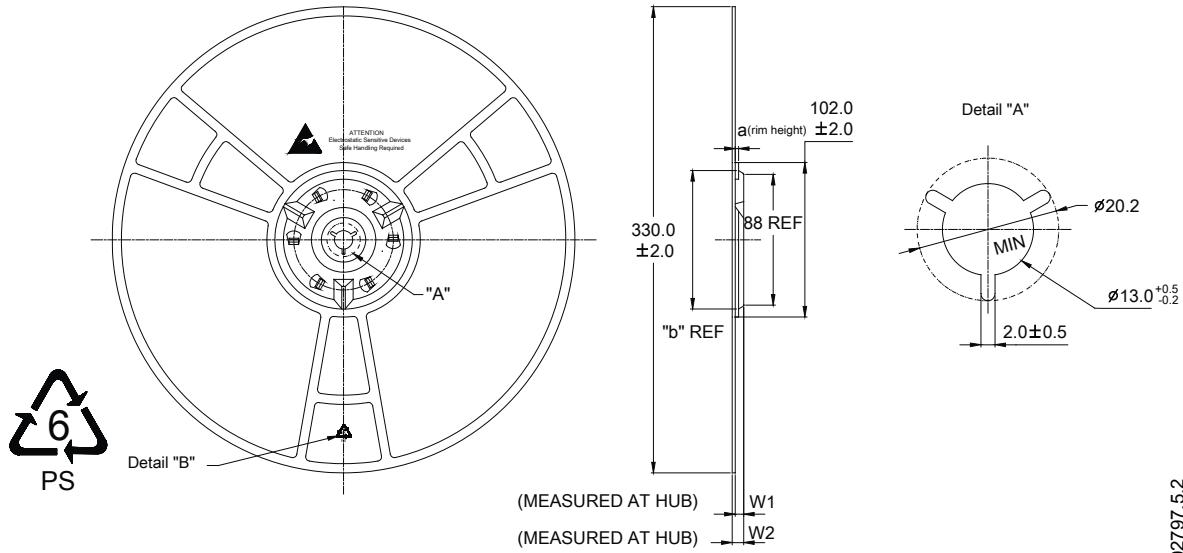

| <b>16</b> | <b>Tape and Reel Information .....</b>              | <b>99</b>  |

| 16.1      | Tape Orientation .....                              | 99         |

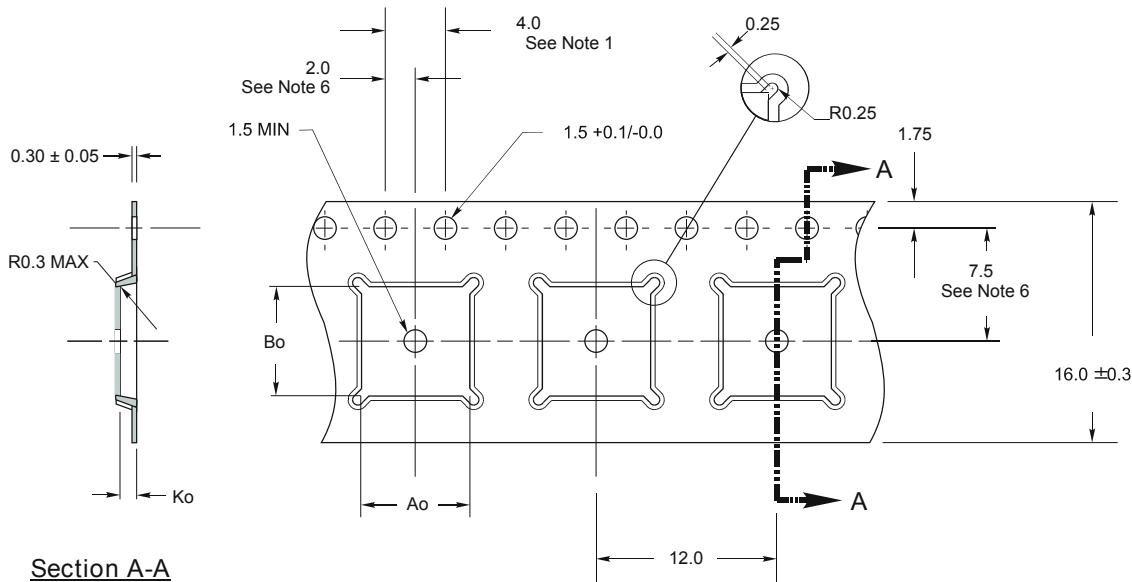

| 16.2      | Tape Dimensions .....                               | 100        |

| 16.3      | Reel Information .....                              | 101        |

| 16.4      | Moisture Sensitivity Level .....                    | 101        |

| <b>17</b> | <b>Document References .....</b>                    | <b>102</b> |

|           | <b>Terms and Definitions .....</b>                  | <b>103</b> |

## List of Figures

|             |                                                                              |    |

|-------------|------------------------------------------------------------------------------|----|

| Figure 1.1  | Device Pinout .....                                                          | 13 |

| Figure 2.1  | Simplified Circuit BT_RF .....                                               | 22 |

| Figure 3.1  | Crystal Oscillator Overview .....                                            | 24 |

| Figure 5.1  | Serial Quad I/O Flash Interface .....                                        | 29 |

| Figure 6.1  | Universal Asynchronous Receiver .....                                        | 32 |

| Figure 7.1  | LED Equivalent Circuit .....                                                 | 35 |

| Figure 8.1  | Audio Interface .....                                                        | 36 |

| Figure 8.2  | Audio Codec Input and Output Stages .....                                    | 37 |

| Figure 8.3  | Audio Input Gain .....                                                       | 38 |

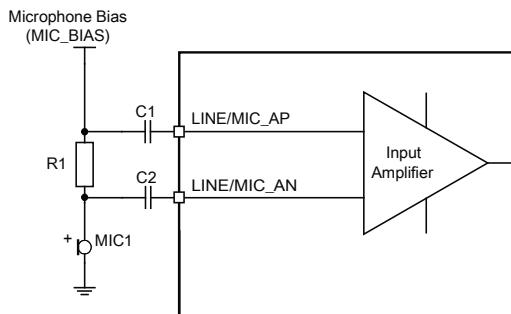

| Figure 8.4  | Microphone Biasing .....                                                     | 40 |

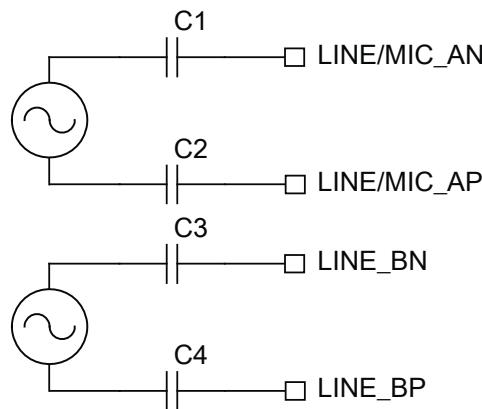

| Figure 8.5  | Differential Input .....                                                     | 41 |

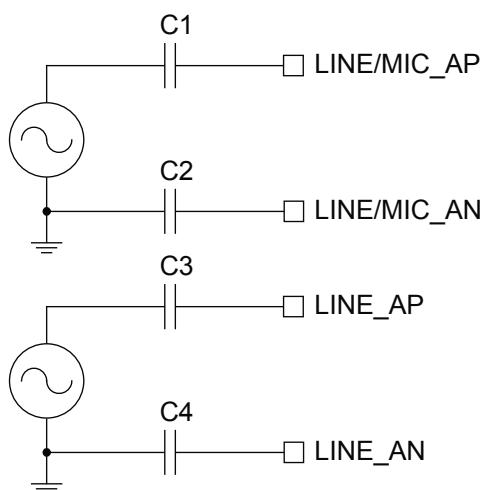

| Figure 8.6  | Single-ended Input .....                                                     | 41 |

| Figure 8.7  | Speaker Output .....                                                         | 42 |

| Figure 8.8  | Side Tone .....                                                              | 43 |

| Figure 8.9  | PCM Interface Master .....                                                   | 45 |

| Figure 8.10 | PCM Interface Slave .....                                                    | 46 |

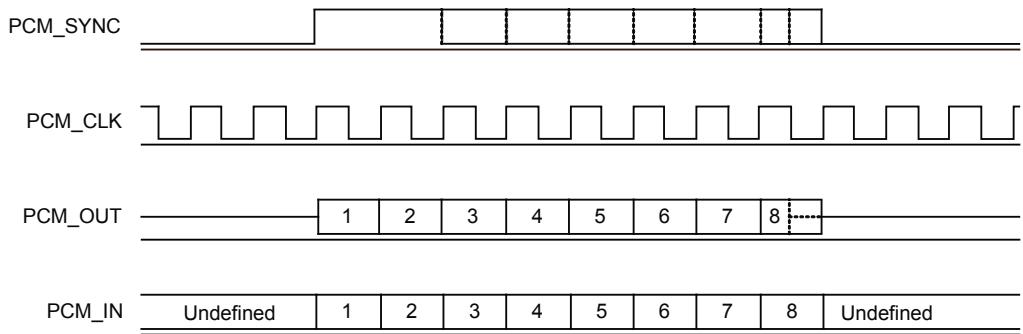

| Figure 8.11 | Long Frame Sync (Shown with 8-bit Companded Sample) .....                    | 46 |

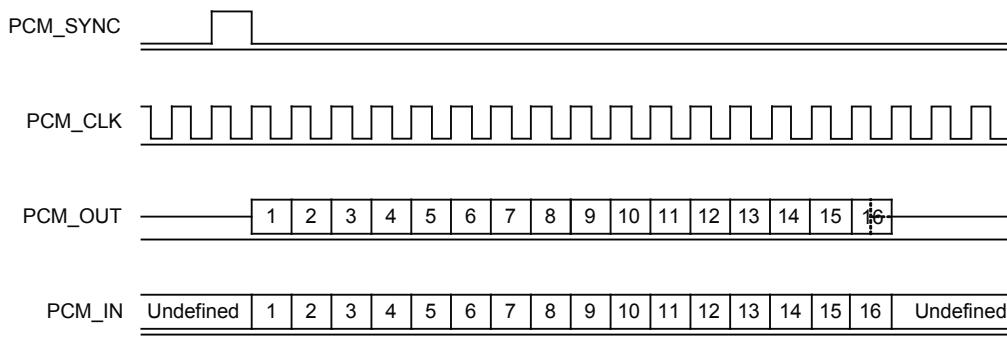

| Figure 8.12 | Short Frame Sync (Shown with 16-bit Sample) .....                            | 47 |

| Figure 8.13 | Multi-slot Operation with 2 Slots and 8-bit Companded Samples .....          | 47 |

| Figure 8.14 | GCI Interface .....                                                          | 48 |

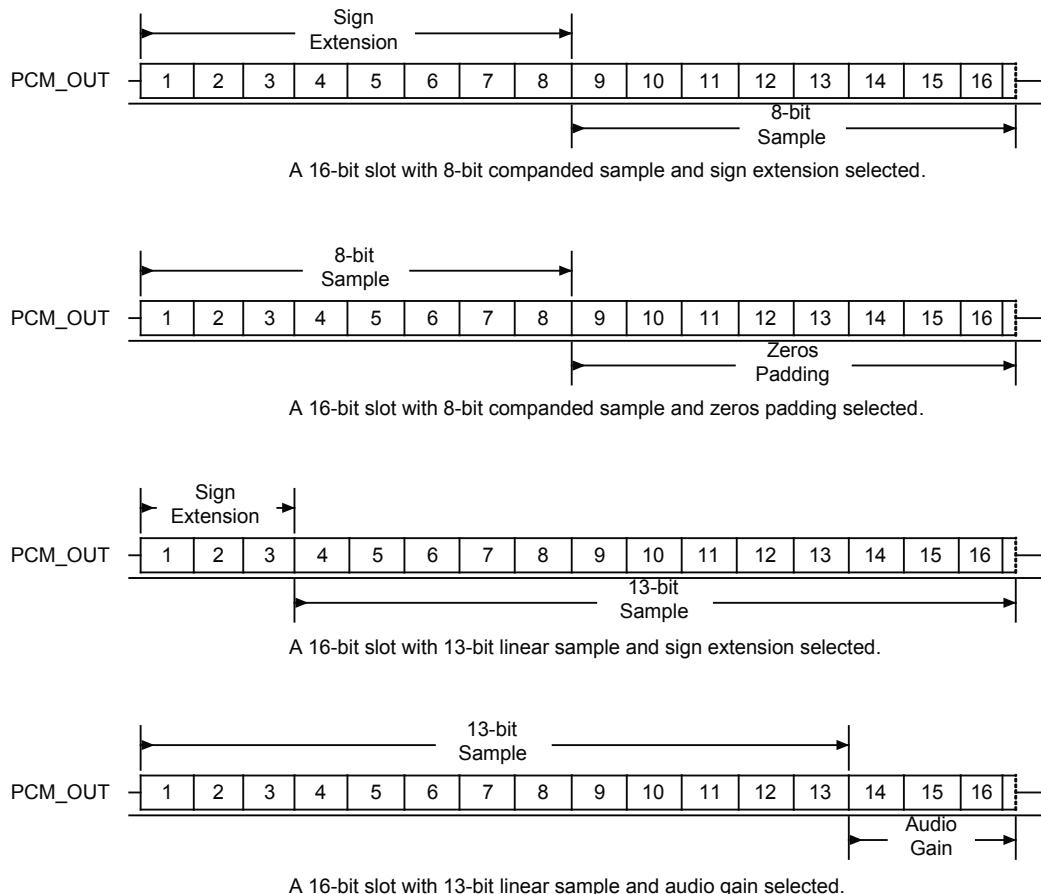

| Figure 8.15 | 16-bit Slot Length and Sample Formats .....                                  | 49 |

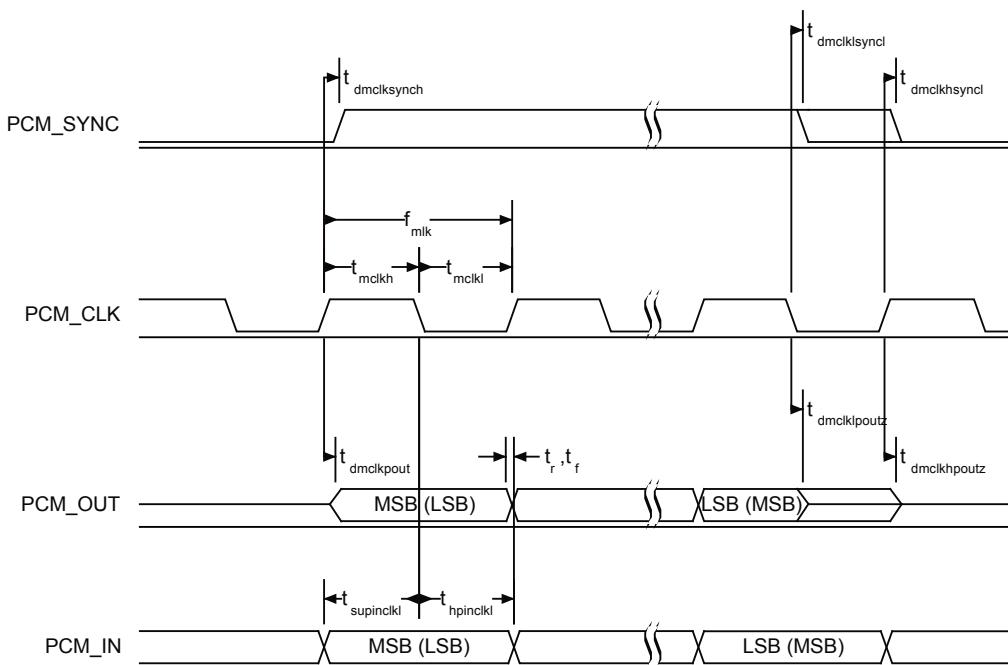

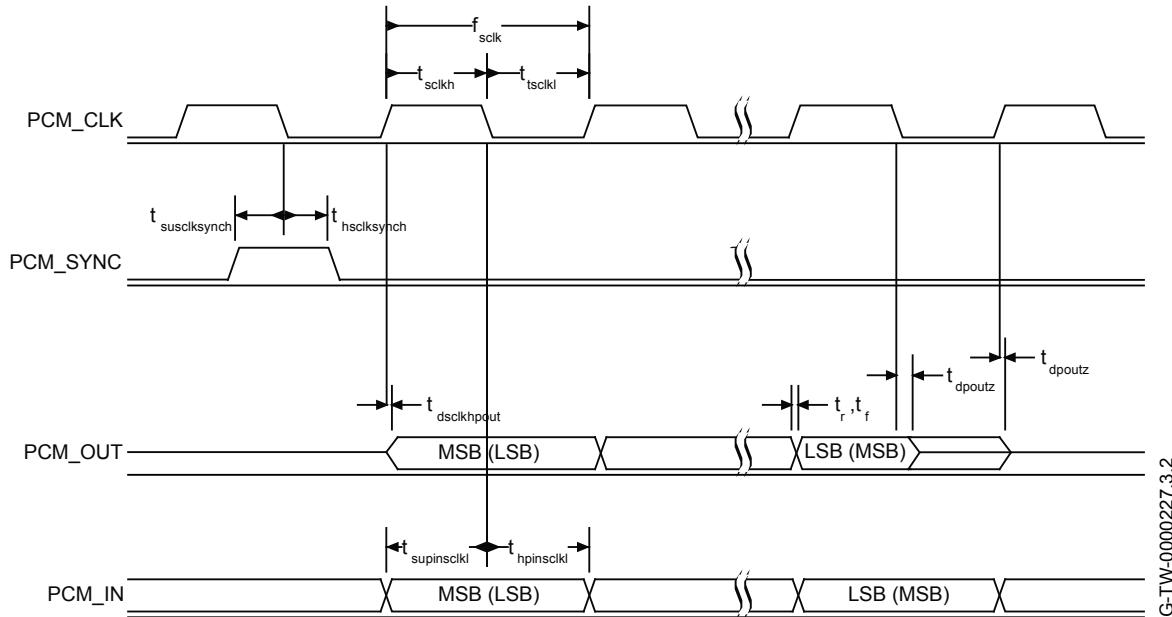

| Figure 8.16 | PCM Master Timing Long Frame Sync .....                                      | 50 |

| Figure 8.17 | PCM Master Timing Short Frame Sync .....                                     | 51 |

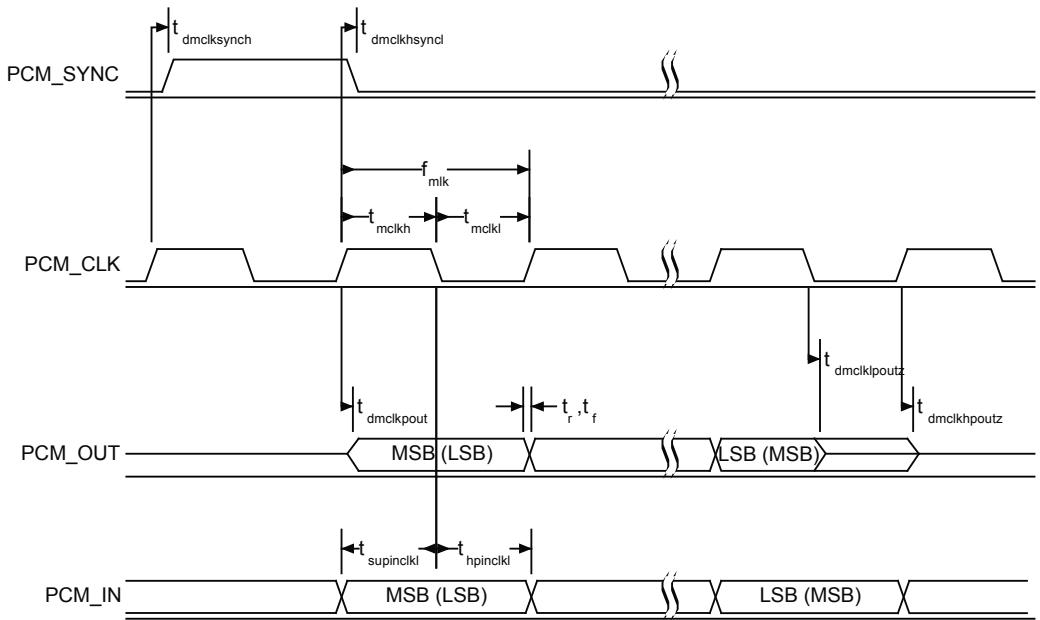

| Figure 8.18 | PCM Slave Timing Long Frame Sync .....                                       | 52 |

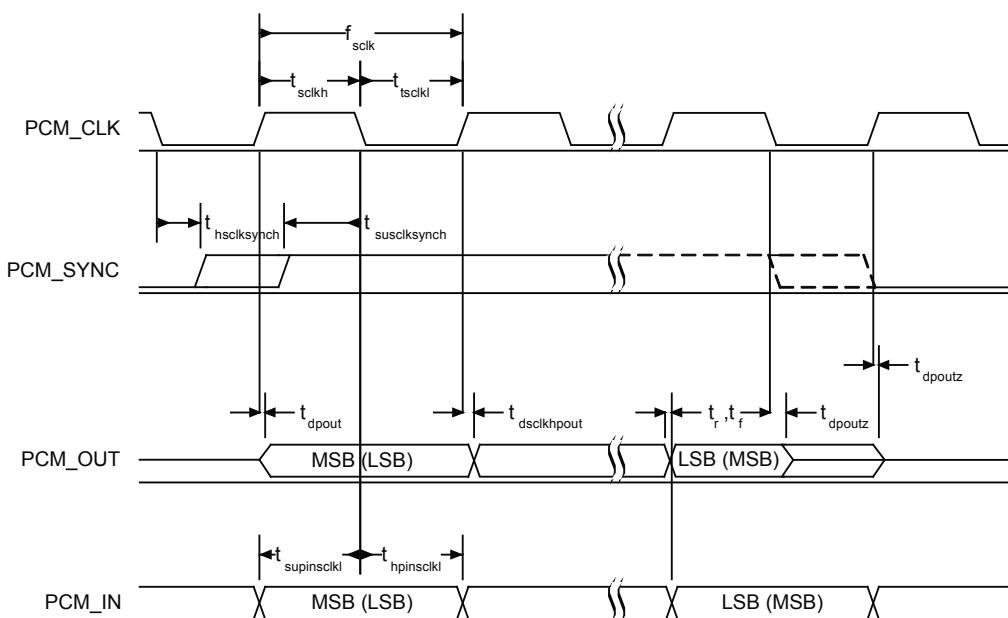

| Figure 8.19 | PCM Slave Timing Short Frame Sync .....                                      | 53 |

| Figure 8.20 | Digital Audio Interface Modes .....                                          | 55 |

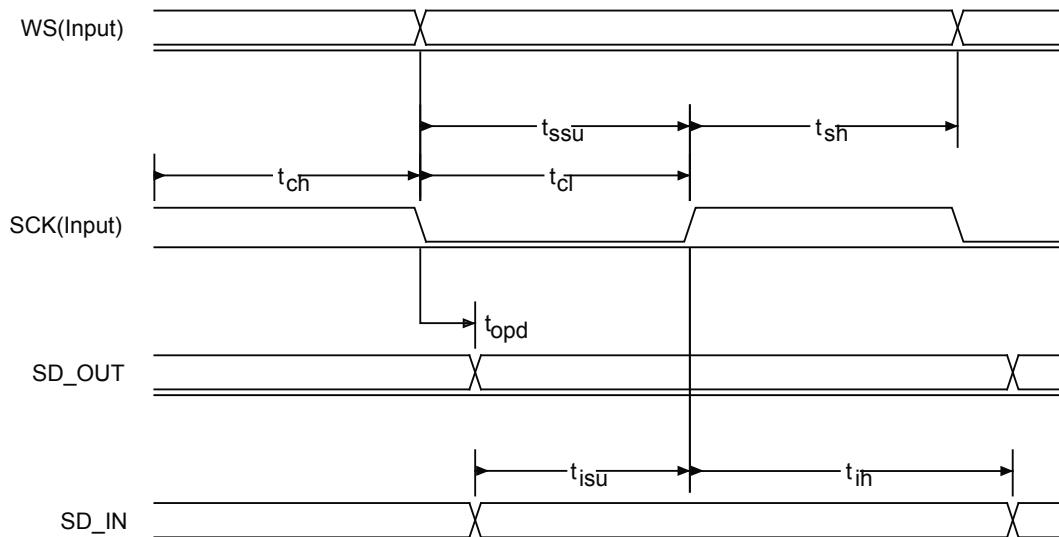

| Figure 8.21 | Digital Audio Interface Slave Timing .....                                   | 56 |

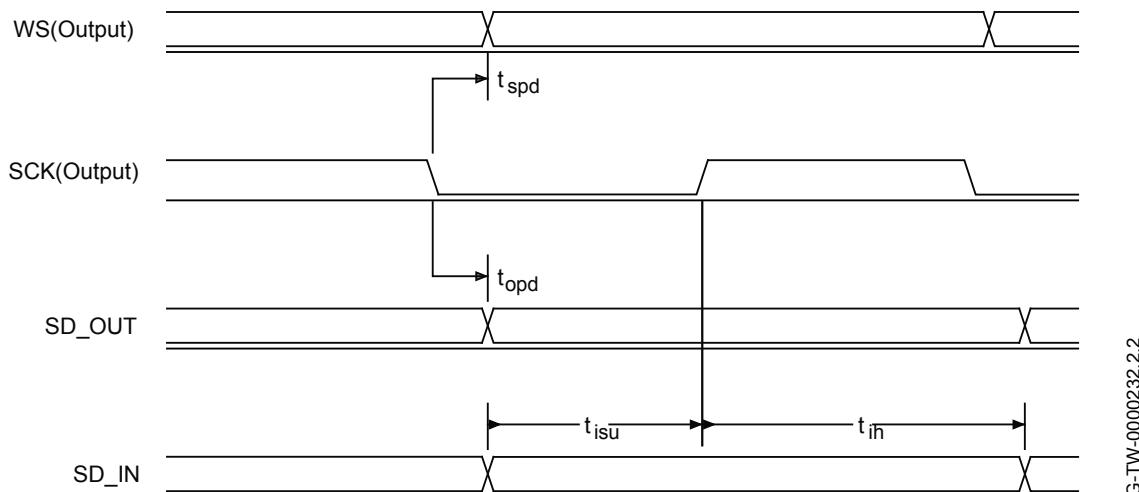

| Figure 8.22 | Digital Audio Interface Master Timing .....                                  | 57 |

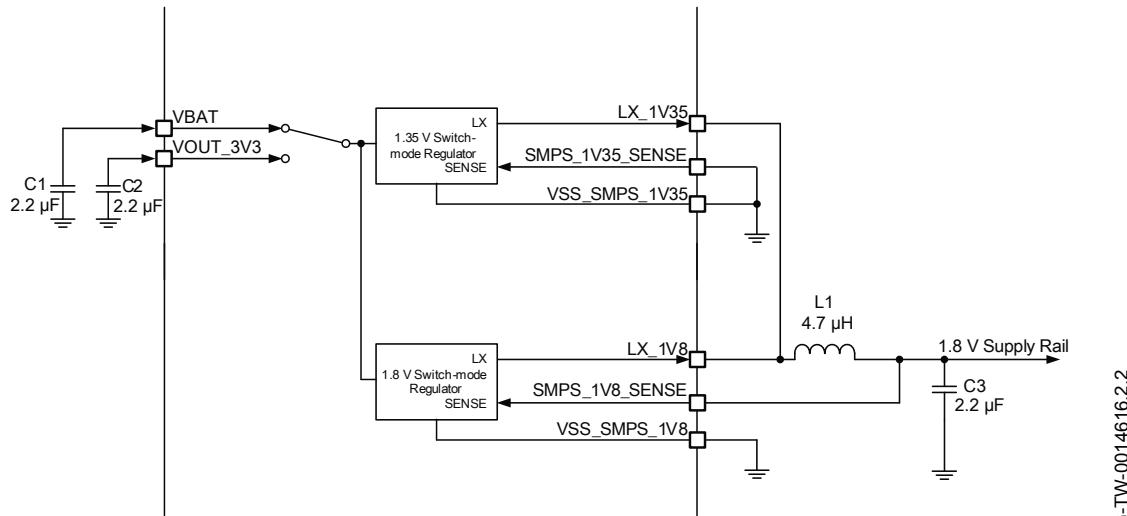

| Figure 9.1  | 1.80 V and 1.35 V Dual-supply Switch-mode System Configuration .....         | 59 |

| Figure 9.2  | 1.80 V Parallel-supply Switch-mode System Configuration .....                | 60 |

| Figure 9.3  | 1.8 V Switch-mode Regulator Output Configuration .....                       | 61 |

| Figure 9.4  | 1.35 V Switch-mode Regulator Output Configuration .....                      | 62 |

| Figure 9.5  | 1.8 V and 1.35 V Switch-mode Regulators Outputs Parallel Configuration ..... | 63 |

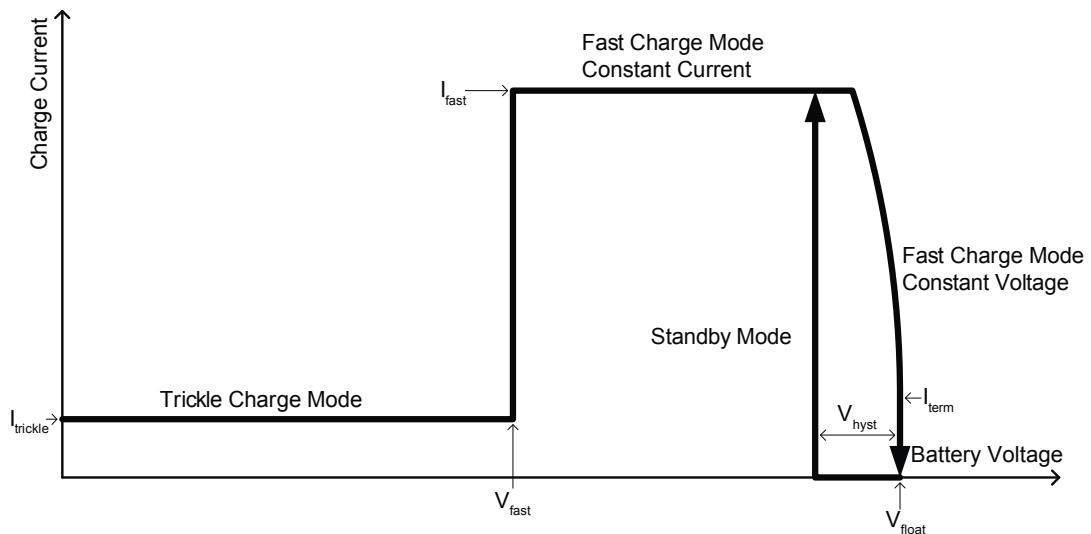

| Figure 10.1 | Battery Charger Mode-to-Mode Transition Diagram .....                        | 67 |

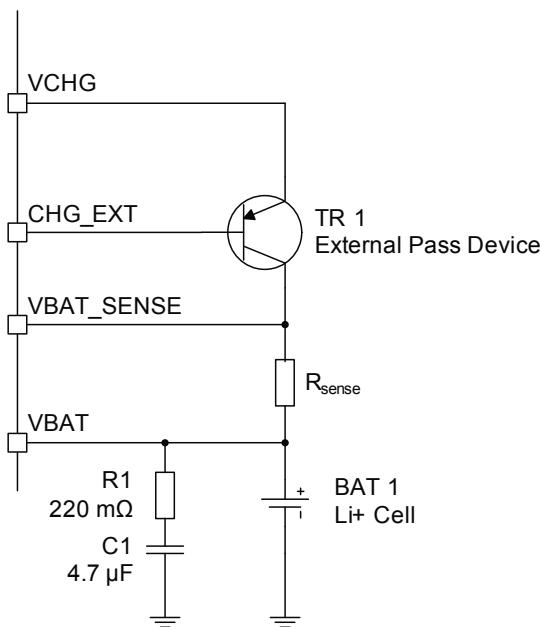

| Figure 10.2 | Battery Charger External Mode Typical Configuration .....                    | 69 |

| Figure 11.1 | Example Application Schematic .....                                          | 70 |

| Figure 11.2 | Single 1.8 V-only Supply, with no USB or SMPSS .....                         | 71 |

|             |                                                          |     |

|-------------|----------------------------------------------------------|-----|

| Figure 11.3 | Single 3.3 V-only Supply, with USB and Dual SMPSSs ..... | 72  |

| Figure 15.1 | Programmable Audio Prompts in External SPI Flash .....   | 92  |

| Figure 15.2 | 1-mic cVc Hands-free Block Diagram .....                 | 94  |

| Figure 15.3 | Configurable EQ GUI with Drag Points .....               | 97  |

| Figure 15.4 | Volume Boost GUI with Drag Points .....                  | 98  |

| Figure 16.1 | CSRA64210 QFN Tape Orientation .....                     | 99  |

| Figure 16.2 | Reel Dimensions .....                                    | 101 |

## List of Tables

|            |                                                                                               |    |

|------------|-----------------------------------------------------------------------------------------------|----|

| Table 3.1  | Typical On-chip Capacitance Values .....                                                      | 24 |

| Table 3.2  | Transconductance and On-chip Parasitic Capacitance .....                                      | 25 |

| Table 3.3  | Crystal Specification .....                                                                   | 25 |

| Table 3.4  | External Clock Specifications .....                                                           | 27 |

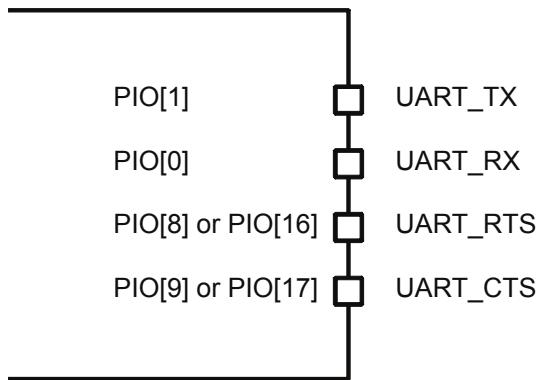

| Table 6.1  | PS Keys for UART/PIO Multiplexing .....                                                       | 31 |

| Table 6.2  | Possible UART Settings .....                                                                  | 32 |

| Table 6.3  | Standard Baud Rates .....                                                                     | 32 |

| Table 7.1  | Alternative PIO Functions .....                                                               | 34 |

| Table 8.1  | Alternative Functions of the Digital Audio Bus Interface on the PCM1 and PCM2 Interface ..... | 36 |

| Table 8.2  | ADC Audio Input Gain Rate .....                                                               | 38 |

| Table 8.3  | DAC Digital Gain Rate Selection .....                                                         | 39 |

| Table 8.4  | DAC Analogue Gain Rate Selection .....                                                        | 40 |

| Table 8.5  | Side Tone Gain .....                                                                          | 43 |

| Table 8.6  | PCM Master Timing .....                                                                       | 49 |

| Table 8.7  | PCM Slave Timing .....                                                                        | 52 |

| Table 8.8  | Alternative Functions of the Digital Audio Bus Interface on the PCM Interface .....           | 54 |

| Table 8.9  | Digital Audio Interface Slave Timing .....                                                    | 55 |

| Table 8.10 | I <sup>2</sup> S Slave Mode Timing .....                                                      | 56 |

| Table 8.11 | Digital Audio Interface Master Timing .....                                                   | 57 |

| Table 8.12 | I <sup>2</sup> S Master Mode Timing Parameters, WS and SCK as Outputs .....                   | 57 |

| Table 9.1  | Recommended Configurations for Power Control and Regulation .....                             | 58 |

| Table 9.2  | Inductor Choice, CSR's Testing and Characterisation .....                                     | 64 |

| Table 9.3  | Pin States on Reset .....                                                                     | 66 |

| Table 10.1 | Battery Charger Operating Modes Determined by Battery Voltage and Current .....               | 67 |

| Table 12.1 | ESD Handling Ratings .....                                                                    | 85 |

| Table 12.2 | USB Electrostatic Discharge Protection Level .....                                            | 86 |

## List of Equations

|              |                                                                          |    |

|--------------|--------------------------------------------------------------------------|----|

| Equation 3.1 | Negative Resistance .....                                                | 25 |

| Equation 3.2 | Crystal Calibration Using PSKEY_ANA_FTRIM_OFFSET .....                   | 26 |

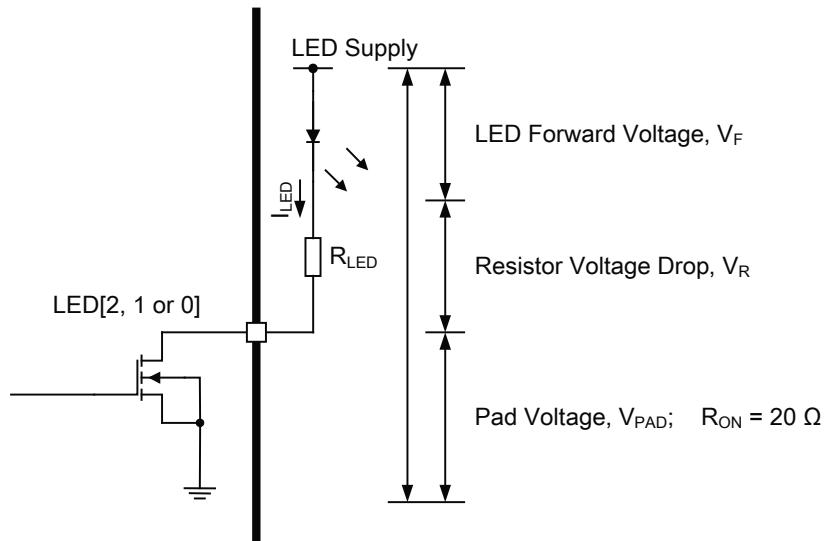

| Equation 7.1 | LED Current .....                                                        | 35 |

| Equation 7.2 | LED PAD Voltage .....                                                    | 35 |

| Equation 8.1 | IIR Filter Transfer Function, H(z) .....                                 | 44 |

| Equation 8.2 | IIR Filter Plus DC Blocking Transfer Function, H <sub>DC</sub> (z) ..... | 45 |

## 1 Package Information

### 1.1 Pinout Diagram

Figure 1.1: Device Pinout

## 1.2 Device Terminal Functions

| Radio | Lead | Pad Type | Supply Domain | Description                                        |

|-------|------|----------|---------------|----------------------------------------------------|

| BT_RF | 12   | RF       | VDD_BT_RADIO  | Bluetooth 50 Ω transmitter output / receiver input |

| Oscillator | Lead | Pad Type | Supply Domain | Description                         |

|------------|------|----------|---------------|-------------------------------------|

| XTAL_IN    | 19   | Analogue | VDD_AUX       | For crystal or external clock input |

| XTAL_OUT   | 18   | Analogue | VDD_AUX       | Drive for crystal                   |

| USB    | Lead | Pad Type      | Supply Domain | Description                                                    |

|--------|------|---------------|---------------|----------------------------------------------------------------|

| USB_DP | 56   | Bidirectional | VDD_USB       | USB data plus with selectable internal 1.5 kΩ pull-up resistor |

| USB_DN | 55   | Bidirectional | VDD_USB       | USB data minus                                                 |

| SPI/PCM Interface | Lead | Pad Type                  | Supply Domain | Description                                                                                                           |

|-------------------|------|---------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------|

| SPI_PCM#          | 29   | Input with weak pull-down | VDD_PADS_1    | SPI/PCM select input:<br><ul style="list-style-type: none"> <li>■ 0 = PCM/PIO interface</li> <li>■ 1 = SPI</li> </ul> |

**Note:**

SPI and PCM1 interfaces are mapped as alternative functions on the PIO port.

| SQIF           | Lead | Pad Type                            | Supply Domain | Description           |

|----------------|------|-------------------------------------|---------------|-----------------------|

| QSPI_FLASH_CLK | 25   | Bidirectional with strong pull-down | VDD_PADS_1    | SPI flash clock       |

| QSPI_FLASH_CS# | 22   | Bidirectional with strong pull-up   | VDD_PADS_1    | SPI flash chip select |

| QSPI_IO[3]     | 21   | Bidirectional with strong pull-up   | VDD_PADS_1    | SPI flash data bit 3  |

| QSPI_IO[2]     | 23   | Bidirectional with strong pull-up   | VDD_PADS_1    | SPI flash data bit 2  |

| QSPI_IO[1]     | 31   | Bidirectional with strong pull-down | VDD_PADS_1    | SPI flash data bit 1  |

| QSPI_IO[0]     | 26   | Bidirectional with strong pull-down | VDD_PADS_1    | SPI flash data bit 0  |

| PIO Port | Lead | Pad Type                            | Supply Domain | Description                                                                                                                                                                                                                                                           |

|----------|------|-------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO[21]  | 64   | Bidirectional with weak pull-down   | VDD_PADS_2    | Programmable input / output line 21.                                                                                                                                                                                                                                  |

| PIO[18]  | 65   | Bidirectional with weak pull-down   | VDD_PADS_2    | Programmable input / output line 18.                                                                                                                                                                                                                                  |

| PIO[17]  | 32   | Bidirectional with strong pull-down | VDD_PADS_1    | Programmable input / output line 17.<br>Alternative function: <ul style="list-style-type: none"><li>■ UART_CTS: UART clear to send, active low</li></ul>                                                                                                              |

| PIO[16]  | 27   | Bidirectional with strong pull-up   | VDD_PADS_1    | Programmable input / output line 16.<br>Alternative function: <ul style="list-style-type: none"><li>■ UART_RTS: UART request to send, active low</li></ul>                                                                                                            |

| PIO[9]   | 58   | Bidirectional with strong pull-down | VDD_PADS_2    | Programmable input / output line 9.<br>Alternative function: <ul style="list-style-type: none"><li>■ UART_CTS: UART clear to send, active low</li><li>■ PCM2_CLK: PCM2 synchronous data clock</li><li>■ I2S2_SCK: I<sup>2</sup>S2 synchronous data clock</li></ul>    |

| PIO[8]   | 61   | Bidirectional with strong pull-up   | VDD_PADS_2    | Programmable input / output line 8.<br>Alternative function: <ul style="list-style-type: none"><li>■ UART_RTS: UART request to send, active low</li><li>■ PCM2_IN: PCM2 synchronous data input</li><li>■ I2S2_SD_IN: I<sup>2</sup>S2 synchronous data input</li></ul> |

| PIO[7]   | 57   | Bidirectional with strong pull-down | VDD_PADS_2    | Programmable input / output line 7.<br>Alternative function: <ul style="list-style-type: none"><li>■ PCM2_SYNC: PCM2 synchronous data sync</li><li>■ I2S2_WS: I<sup>2</sup>S2 word select</li></ul>                                                                   |

| PIO[6]   | 62   | Bidirectional with strong pull-down | VDD_PADS_2    | Programmable input / output line 6.<br>Alternative function: <ul style="list-style-type: none"><li>■ PCM2_OUT: PCM2 synchronous data output</li><li>■ I2S2_SD_OUT: I<sup>2</sup>S2 synchronous data output</li></ul>                                                  |

| PIO[5]   | 34   | Bidirectional with weak pull-down   | VDD_PADS_1    | Programmable input / output line 5.<br>Alternative function: <ul style="list-style-type: none"><li>■ SPI_CLK: SPI clock</li><li>■ PCM1_CLK: PCM1 synchronous data clock</li><li>■ I2S1_SCK: I<sup>2</sup>S1 synchronous data clock</li></ul>                          |

| PIO Port | Lead | Pad Type                          | Supply Domain | Description                                                                                                                                                                                                                                                     |

|----------|------|-----------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO[4]   | 24   | Bidirectional with weak pull-down | VDD_PADS_1    | Programmable input / output line 4.<br>Alternative function:<br><ul style="list-style-type: none"> <li>■ SPI_CS#: chip select for SPI, active low</li> <li>■ PCM1_SYNC: PCM1 synchronous data sync</li> <li>■ I2S1_WS: I<sup>2</sup>S1 word select</li> </ul>   |

| PIO[3]   | 28   | Bidirectional with weak pull-down | VDD_PADS_1    | Programmable input / output line 3.<br>Alternative function:<br><ul style="list-style-type: none"> <li>■ SPI_MISO: SPI data output</li> <li>■ PCM1_OUT: PCM1 synchronous data output</li> <li>■ I2S1_SD_OUT: I<sup>2</sup>S1 synchronous data output</li> </ul> |

| PIO[2]   | 30   | Bidirectional with weak pull-down | VDD_PADS_1    | Programmable input / output line 2.<br>Alternative function:<br><ul style="list-style-type: none"> <li>■ SPI_MOSI: SPI data input</li> <li>■ PCM1_IN: PCM1 synchronous data input</li> <li>■ I2S1_SD_IN: I<sup>2</sup>S1 synchronous data input</li> </ul>      |

| PIO[1]   | 60   | Bidirectional with strong pull-up | VDD_PADS_2    | Programmable input / output line 1.<br>Alternative function:<br><ul style="list-style-type: none"> <li>■ UART_TX: UART data output</li> <li>■ AMP_I2C_SDA: I<sup>2</sup>C serial data line for external amplifier control</li> </ul>                            |

| PIO[0]   | 59   | Bidirectional with strong pull-up | VDD_PADS_2    | Programmable input / output line 0.<br>Alternative function:<br><ul style="list-style-type: none"> <li>■ UART_RX: UART data input</li> <li>■ AMP_I2C_SCL: I<sup>2</sup>C serial clock line for external amplifier control</li> </ul>                            |

| AIO[0]   | 20   | Bidirectional                     | VDD_AUX       | Analogue programmable input / output line 0.                                                                                                                                                                                                                    |

| Test and Debug | Lead | Pad Type                  | Supply Domain | Description                                               |

|----------------|------|---------------------------|---------------|-----------------------------------------------------------|

| RST#           | 35   | Input with strong pull-up | VDD_PADS_1    | Reset if low. Pull low for minimum 5 ms to cause a reset. |

| Codec    | Lead | Pad Type     | Supply Domain | Description                                            |

|----------|------|--------------|---------------|--------------------------------------------------------|

| MIC_BIAS | 2    | Analogue in  | VDD_AUDIO     | Microphone bias                                        |

| AU_REF   | 1    | Analogue in  | VDD_AUDIO     | Decoupling of audio reference (for high-quality audio) |

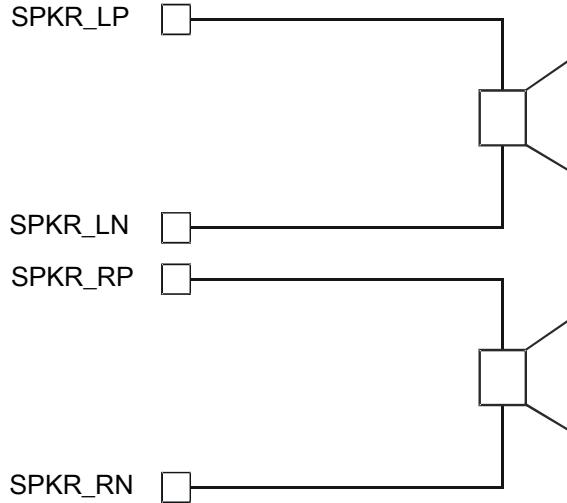

| SPKR_RN  | 6    | Analogue out | VDD_AUDIO_DRV | Speaker output negative, right                         |

| SPKR_RP  | 7    | Analogue out | VDD_AUDIO_DRV | Speaker output positive, right                         |

| Codec       | Lead | Pad Type     | Supply Domain | Description                                  |

|-------------|------|--------------|---------------|----------------------------------------------|

| SPKR_LN     | 9    | Analogue out | VDD_AUDIO_DRV | Speaker output negative, left                |

| SPKR_LP     | 10   | Analogue out | VDD_AUDIO_DRV | Speaker output positive, left                |

| LINE/MIC_AN | 67   | Analogue in  | VDD_AUDIO     | Line or microphone input negative, channel A |

| LINE/MIC_AP | 68   | Analogue in  | VDD_AUDIO     | Line or microphone input positive, channel A |

| LINE_BN     | 4    | Analogue in  | VDD_AUDIO     | Line input negative, channel B               |

| LINE_BP     | 5    | Analogue in  | VDD_AUDIO     | Line input positive, channel B               |

| LED Drivers | Lead | Pad Type      | Supply Domain | Description                                                                                                                                                                                                     |

|-------------|------|---------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED[2]      | 66   | Bidirectional | VDD_PADS_2    | <p>LED driver.<br/>Alternative function: programmable output PIO[31]</p> <p><b>Note:</b><br/>As output is open-drain, an external pull-up is required when PIO[31] is configured as a programmable output.</p>  |

| LED[1]      | 36   | Bidirectional | VDD_PADS_1    | <p>LED driver.<br/>Alternative function: programmable output PIO[30].</p> <p><b>Note:</b><br/>As output is open-drain, an external pull-up is required when PIO[30] is configured as a programmable output.</p> |

| LED[0]      | 37   | Bidirectional | VDD_PADS_1    | <p>LED driver.<br/>Alternative function: programmable output PIO[29].</p> <p><b>Note:</b><br/>As output is open-drain, an external pull-up is required when PIO[29] is configured as a programmable output.</p> |

| Power Supplies and Control | Lead | Description                                                                                                                                           |

|----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG_EXT                    | 43   | External battery charger control.<br>External battery charger transistor base control when using external charger boost. Otherwise leave unconnected. |

| LX_1V35                    | 50   | 1.35 V switch-mode power regulator inductor connection.                                                                                               |

| LX_1V8                     | 47   | 1.8 V switch-mode power regulator inductor connection.                                                                                                |

| SMPS_1V35_SENSE            | 52   | 1.35 V switch-mode power regulator sense input.                                                                                                       |

| SMPS_1V8_SENSE             | 53   | 1.8 V switch-mode power regulator sense input.                                                                                                        |

| Power Supplies and Control | Lead   | Description                                                                                                                                      |

|----------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| SMP_BYP                    | 49     | Supply via bypass regulator for 1.8 V and 1.35 V switch-mode power supply regulator inputs. Must be connected to the same potential as VOUT_3V3. |

| SMP_VBAT                   | 48     | 1.8 V and 1.35 V switch-mode power supply regulator inputs. Must be at the same potential as VBAT.                                               |

| VSS_SMPS_1V35              | 51     | 1.35 V switch-mode regulator ground.                                                                                                             |

| VSS_SMPS_1V8               | 46     | 1.8 V switch-mode regulator ground.                                                                                                              |

| VBAT                       | 45     | Battery positive terminal.                                                                                                                       |

| VBAT_SENSE                 | 44     | Battery charger sense input, connect as Section 11 shows.                                                                                        |

| VCHG                       | 42     | Charger input.<br>Typically connected to VBUS (USB supply) as Section 11 shows.                                                                  |

| VDD_ANA                    | 17     | Analogue LDO linear regulator output (1.35 V).<br>Connect to 1.35 V supply, see Section 11 for connections.                                      |

| VDD_AUDIO                  | 3      | Positive supply for audio.<br>Connect to 1.35 V supply, see Section 11 for connections.                                                          |

| VDD_AUDIO_DRV              | 8      | Positive supply for audio output amplifiers.<br>Connect to 1.8 V supply, see Section 11 for connections.                                         |

| VDD_AUX                    | 14     | Auxiliary supply.<br>Connect to 1.35 V supply, see Section 11 for connections.                                                                   |

| VDD_AUX_1V8                | 15, 16 | Auxiliary LDO regulator input.<br>Connect to 1.8 V supply, see Section 11 for connections.                                                       |

| VDD_BT_LO                  | 13     | Bluetooth radio local oscillator supply (1.35 V).<br>Connect to 1.35 V supply, see Section 11 for connections.                                   |

| VDD_BT_RADIO               | 11     | Bluetooth radio supply.<br>Connect to 1.35 V supply, see Section 11 for connections.                                                             |

| VDD_DIG                    | 38     | Digital LDO regulator output, see Section 11 for connections.                                                                                    |

| VDD_PADS_1                 | 33     | Positive supply input for input/output ports.                                                                                                    |

| Power Supplies and Control | Lead        | Description                                                                                                                                                                                                                                                    |

|----------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD_PADS_2                 | 63          | Positive supply input for input/output ports.                                                                                                                                                                                                                  |

| VDD_USB                    | 54          | Positive supply for USB port.                                                                                                                                                                                                                                  |

| VOUT_3V3                   | 41          | 3.3 V bypass linear regulator output.<br>Connect external minimum 2.2 $\mu$ F ceramic decoupling capacitor.                                                                                                                                                    |

| VREGENABLE                 | 40          | Regulator enable input.<br>Can also be sensed as an input.<br>Regulator enable and multifunction button. A high input (tolerant to VBAT) enables the on-chip regulators, which can then be latched on internally and the button used as a multifunction input. |

| VREGIN_DIG                 | 39          | Digital LDO regulator input, see Section 11 for connections.<br>Typically connected to a 1.35 V supply.                                                                                                                                                        |

| VSS                        | Exposed pad | Ground connections.                                                                                                                                                                                                                                            |

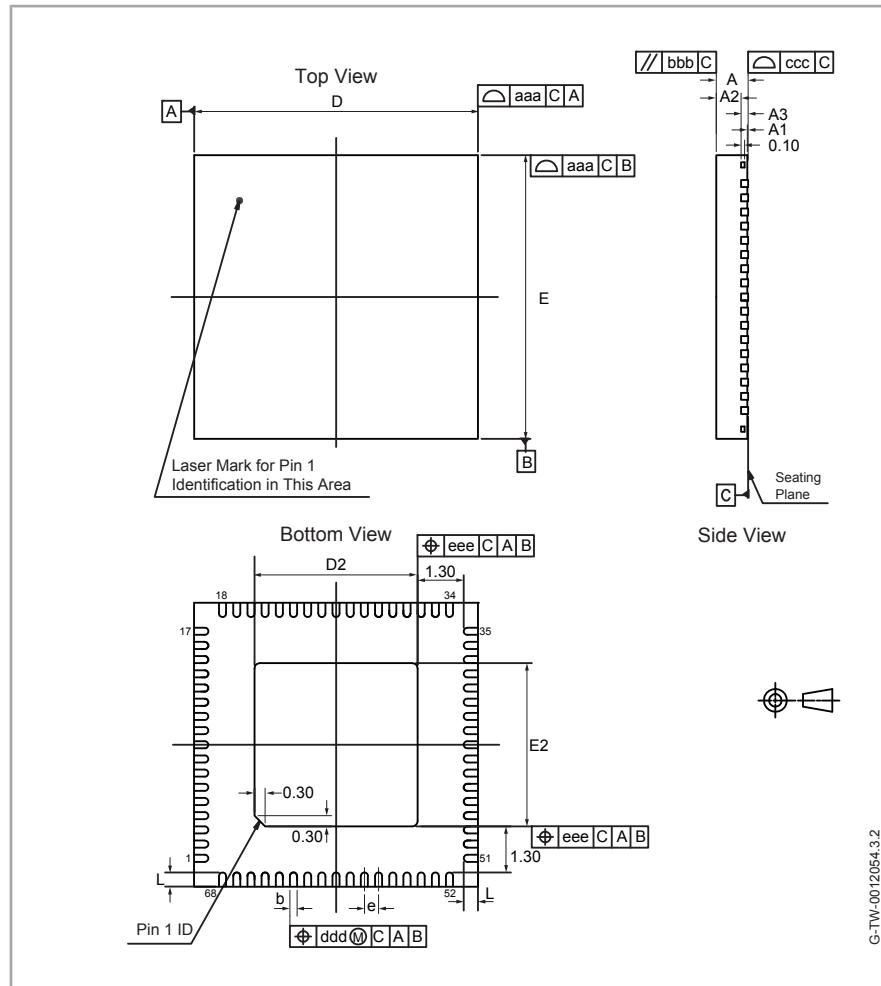

## 1.3 Package Dimensions

| Description        | Min                                                                                                                                                                                                                                                                                      | Typ   | Max   | Description  | Min    | Typ  | Max  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|--------------|--------|------|------|

| A                  | 0.80                                                                                                                                                                                                                                                                                     | 0.85  | 0.90  | E            | 7.90   | 8.00 | 8.10 |

| A1                 | 0.00                                                                                                                                                                                                                                                                                     | 0.035 | 0.05  | E2           | 4.50   | 4.60 | 4.70 |

| A2                 | -                                                                                                                                                                                                                                                                                        | 0.65  | 0.67  | L            | 0.35   | 0.40 | 0.45 |

| A3                 | -                                                                                                                                                                                                                                                                                        | 0.203 | -     | aaa          | -      | 0.10 | -    |

| b                  | 0.15                                                                                                                                                                                                                                                                                     | 0.20  | 0.25  | bbb          | -      | 0.10 | -    |

| D                  | 7.90                                                                                                                                                                                                                                                                                     | 8.00  | 8.10  | ccc          | -      | 0.08 | -    |

| D2                 | 4.50                                                                                                                                                                                                                                                                                     | 4.60  | 4.70  | ddd          | -      | 0.10 | -    |

| e                  | -                                                                                                                                                                                                                                                                                        | 0.40  | -     | eee          | -      | 0.10 | -    |

| <b>Notes</b>       | 1. Dimensions and tolerances conform to ASME Y14.5M. - 1994<br>2. Pin 1 identifier is placed on top surface of the package by using identification mark or other feature of package body.<br>3. Exact shape and size of this feature is optional.<br>4. Package warpage 0.08 mm maximum. |       |       |              |        |      |      |

| <b>Description</b> | 68-lead Quad-Flat No-lead (QFN) package                                                                                                                                                                                                                                                  |       |       |              |        |      |      |

| <b>Size</b>        | 8 x 8 x 0.9 mm                                                                                                                                                                                                                                                                           |       | JEDEC |              | MO-220 |      |      |

| <b>Pitch</b>       | 0.4 mm pitch                                                                                                                                                                                                                                                                             |       |       | <b>Units</b> | mm     |      |      |

## 1.4 PCB Design and Assembly Considerations

This section lists recommendations to achieve maximum board-level reliability of the 8 x 8 x 0.9 mm QFN 68-lead package:

- NSMD lands (lands smaller than the solder mask aperture) are preferred, because of the greater accuracy of the metal definition process compared to the solder mask process. With solder mask defined pads, the overlap of the solder mask on the land creates a step in the solder at the land interface, which can cause stress concentration and act as a point for crack initiation.

- CSR recommends that the PCB land pattern is in accordance with IPC standard IPC-7351.

- Solder paste must be used during the assembly process.

## 1.5 Typical Solder Reflow Profile

For information, see *Typical Solder Reflow Profile for Lead-free Devices Information Note*.

## 2 Bluetooth Modem

The Bluetooth modem includes:

- RF ports

- RF receiver

- RF transmitter

- Bluetooth radio synthesiser

- Baseband

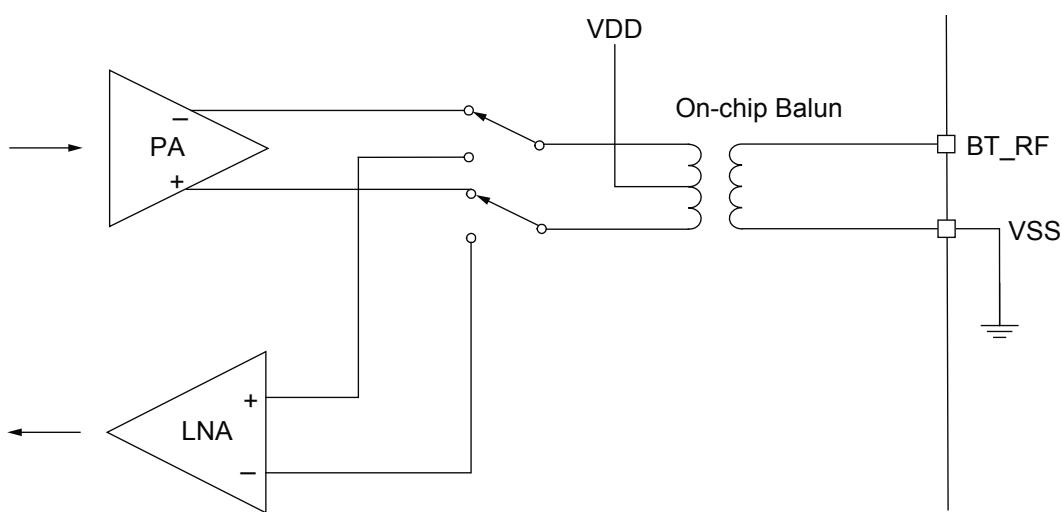

### 2.1 RF Ports (BT\_RF)

CSRA64210 QFN contains an on-chip balun which combines the balanced outputs of the PA on transmit and produces the balanced input signals for the LNA required on receive. No matching components are needed as the receive mode impedance is  $50\ \Omega$  and the transmitter has been optimised to deliver power into a  $50\ \Omega$  load.

G-TW-0012203.1.2

Figure 2.1: Simplified Circuit BT\_RF

### 2.2 RF Receiver

The receiver features a near-zero IF architecture that enables the channel filters to be integrated onto the die. Sufficient out-of-band blocking specification at the LNA input enables the receiver to operate in close proximity to GSM and W-CDMA cellular phone transmitters without being desensitised. A digital FSK discriminator means that no discriminator tank is needed and its excellent performance in the presence of noise enables CSRA64210 QFN to exceed the Bluetooth requirements for co-channel and adjacent channel rejection.

#### 2.2.1 Low Noise Amplifier

The LNA operates in differential mode and takes its input from the balanced port of the on-chip balun.

#### 2.2.2 RSSI Analogue to Digital Converter

The ADC implements fast AGC. The ADC samples the RSSI voltage on a slot-by-slot basis. The front-end LNA gain is changed according to the measured RSSI value, keeping the first mixer input signal within a limited range. This improves the dynamic range of the receiver, improving performance in interference-limited environments.

### 2.3 RF Transmitter

#### 2.3.1 IQ Modulator

The transmitter features a direct IQ modulator to minimise frequency drift during a transmit timeslot, which results in a controlled modulation index. Digital baseband transmit circuitry provides the required spectral shaping.

### 2.3.2 Power Amplifier

The internal PA output power is software controlled and configured through a PS Key. The internal PA on the CSRA64210 QFN has a maximum output power that enables it to operate as a Class 1, Class 2 and Class 3 Bluetooth radio without requiring an external RF PA.

### 2.4 Bluetooth Radio Synthesiser

The Bluetooth radio synthesiser is fully integrated onto the die with no requirement for an external VCO screening can, varactor tuning diodes, LC resonators or loop filter. The synthesiser is guaranteed to lock in sufficient time across the guaranteed temperature range to meet the Bluetooth v4.2 specification.

### 2.5 Baseband

The baseband handles the digital functions of the Bluetooth modem, for example the Burst Mode Controller and Physical Layer Hardware Engine.

### 3 Clock Generation

CSRA64210 QFN accepts a reference clock input from either a crystal or an external clock source, e.g. a TCXO.

The external reference clock is required in active and deep sleep modes and must be present when CSRA64210 QFN is enabled.

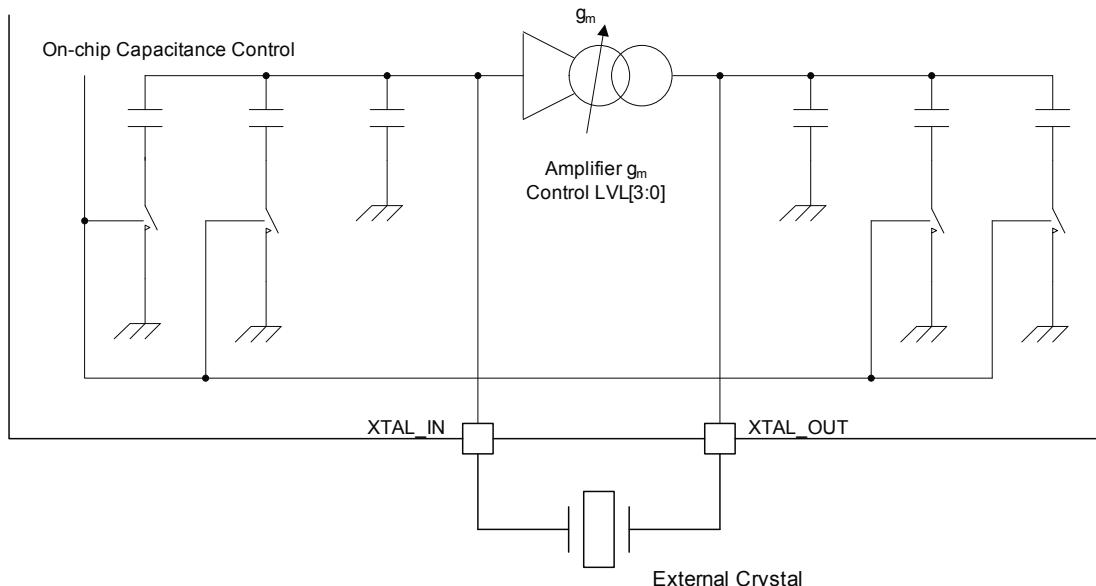

#### 3.1 Crystal

Figure 3.1 shows the CSRA64210 QFN contains a crystal driver circuit that acts as a transconductance amplifier that drives an external crystal connected between XTAL\_IN and XTAL\_OUT. The crystal driver circuit forms a Pierce oscillator with the external crystal. External capacitors are not required for standard crystals that require a load capacitance of around 9pF. CSR recommends this option.

G-TW-0014782

Figure 3.1: Crystal Oscillator Overview

The on-chip capacitance is adjusted using PSKEY\_XTAL\_OSC\_CONFIG, see Table 3.1. The default values suit a typical crystal requiring a 9 pF load capacitance. In deep sleep mode, the crystal oscillation is maintained, but at a lower drive strength to reduce power consumption. The drive strength and load capacitance are configured with a PS Key.

|                       | Normal Mode<br>PSKEY_XTAL_OSC_CONFIG [3:2] |         |         |        | Low Power Mode<br>PSKEY_XTAL_OSC_CONFIG [1:0] |         |        |        |

|-----------------------|--------------------------------------------|---------|---------|--------|-----------------------------------------------|---------|--------|--------|

|                       | 00                                         | 01      | 10      | 11     | 00                                            | 01      | 10     | 11     |

| XTAL_IN<br>(Typical)  | 15.6 pF                                    | 10.8 pF | 6.0 pF  | 1.1 pF | 15.6 pF                                       | 10.8 pF | 6.0 pF | 1.1 pF |

| XTAL_OUT<br>(Typical) | 20.8 pF                                    | 16.0 pF | 11.2 pF | 6.4 pF | 16.0 pF                                       | 11.2 pF | 6.4 pF | 1.5 pF |

Table 3.1: Typical On-chip Capacitance Values

The drive strength is configured with PSKEY\_XTAL\_LVL. The default level for this PS Key is sufficient for typical crystals. The level control is set in the range 0 to 15, where 15 is the maximum drive level.