## 28.3 Operation

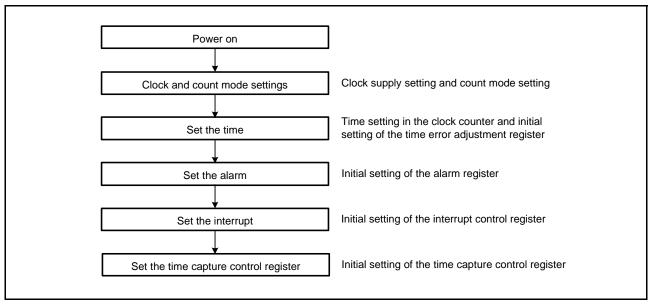

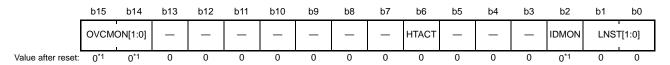

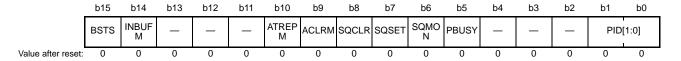

## 28.3.1 Outline of Initial Settings of Registers after Power On

After the power is turned on, the initial settings for the clock setting, count mode setting, time error adjustment, time setting, alarm, interrupt, and time capture control register should be performed.

Figure 28.2 Outline of Initial Settings after Power On

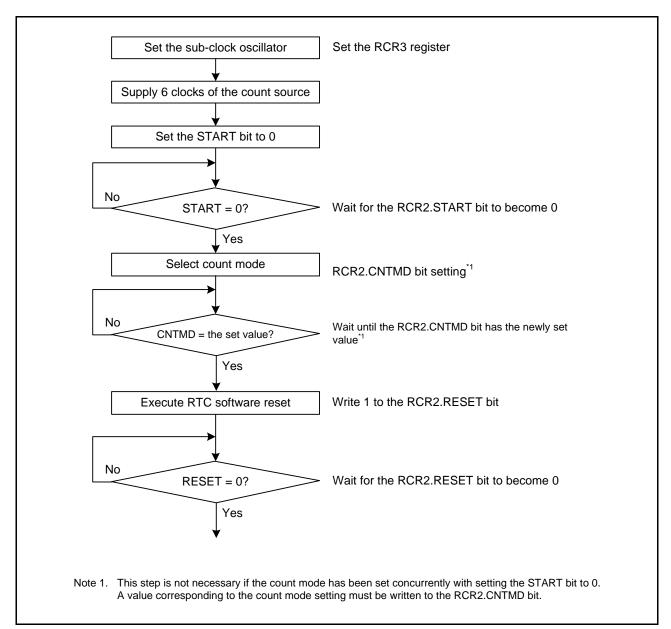

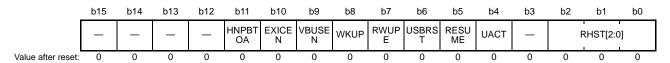

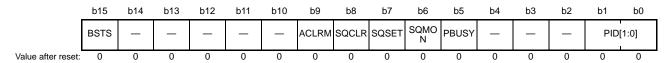

## 28.3.2 Clock and Count Mode Setting Procedure

Figure 28.3 shows how to set the clock and the count mode.

Figure 28.3 Clock and Count Mode Setting Procedure

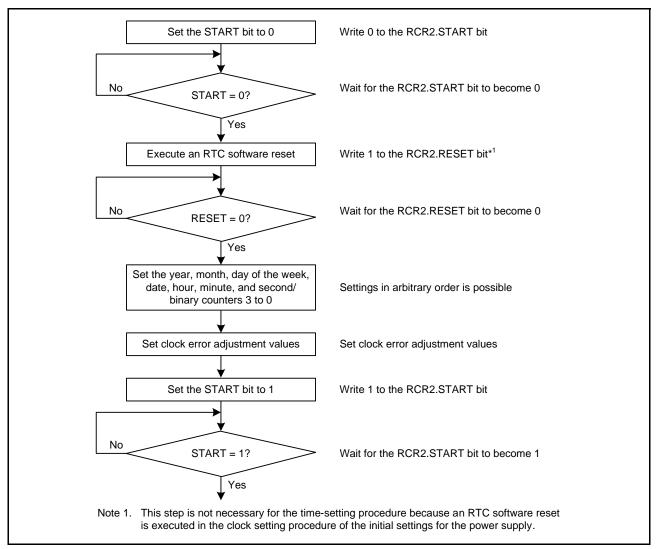

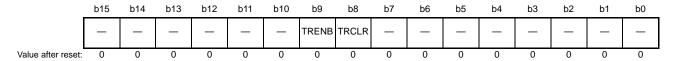

#### 28.3.3 Setting the Time

Figure 28.4 shows how to set the time.

Figure 28.4 Setting the Time

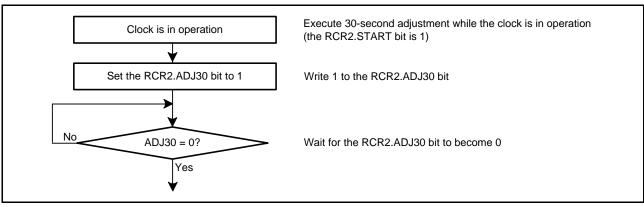

## 28.3.4 30-Second Adjustment

Figure 28.5 shows how to execute 30-second adjustment.

Figure 28.5 30-Second Adjustment

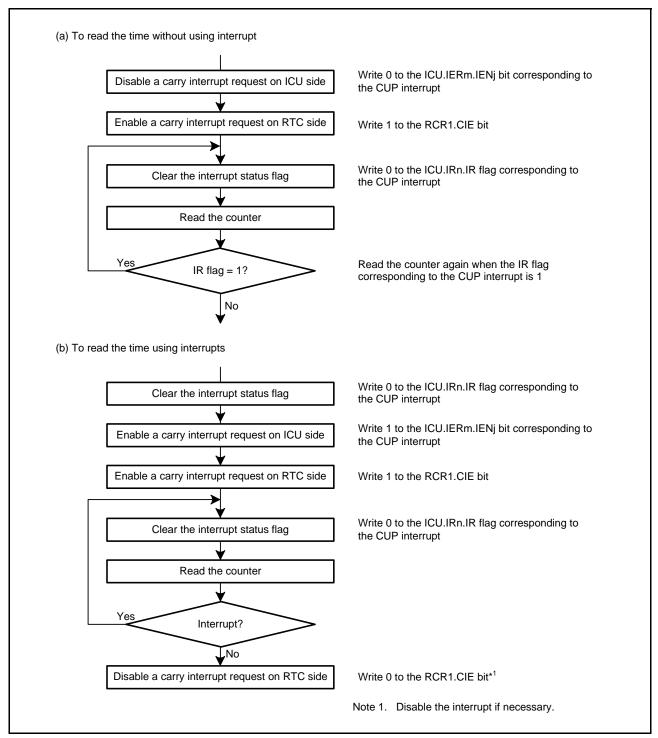

## 28.3.5 Reading 64-Hz Counter and Time

Figure 28.6 shows how to read the 64-Hz counter and time.

Figure 28.6 Reading Time

If a carry occurs while the 64-Hz counter and time are being read, the correct time will not be obtained, so they must be read again. The procedure for reading the time without using interrupts is shown in (a) in Figure 28.6, and the procedure using carry interrupts in (b). To keep the program simple, method (a) should be used in most cases.

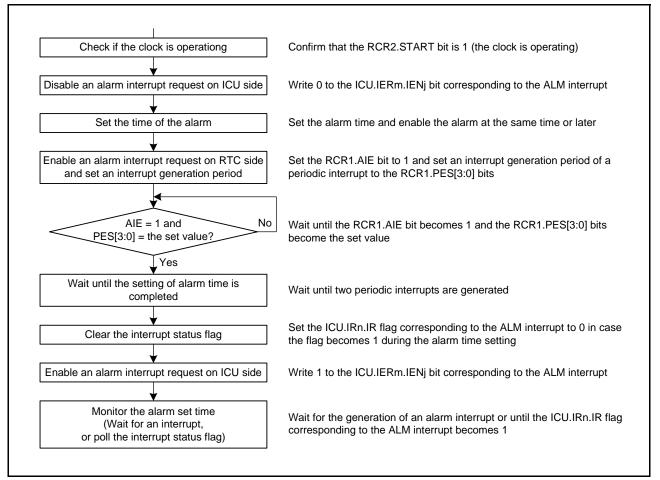

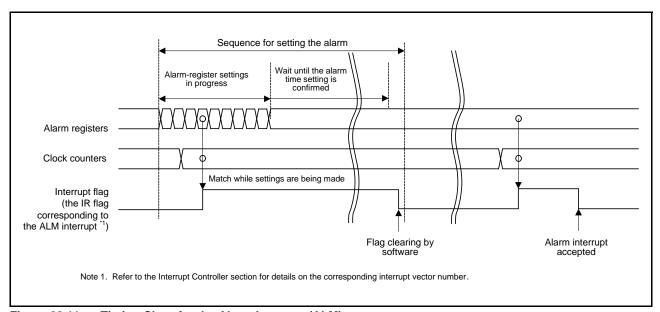

#### 28.3.6 Alarm Function

Figure 28.7 shows how to use the alarm function.

Figure 28.7 Using Alarm Function

In calendar count mode, an alarm can be generated by any one of year, month, date, day-of-week, hour, minute or second, or any combination of those. Write 1 to the ENB bit in the alarm registers involved in the alarm setting, and set the alarm time in the lower bits. Write 0 to the ENB bit in registers not involved in the alarm setting.

In binary count mode, an alarm can be generated in any bit combination of 32 bits. Write 1 to the ENB bit of the alarm enable register corresponding to the target bit of the alarm, and set the alarm time to the alarm register. For bits that are not target of the alarm, write 0 to the ENB bit of the alarm enable register.

When the counter and the alarm time match, the IR flag corresponding to the ALM interrupt is set to 1. Alarm detection can be confirmed by reading this bit, but an interrupt should be used in most cases. If 1 has been set in the interrupt request enable bit corresponding to the ALM interrupt, an alarm interrupt is generated in the event of alarm, enabling the alarm to be detected.

Writing 0 sets the IR flag corresponding to the ALM interrupt to 0.

When the counter and the alarm time match in a low power consumption state, the MCU returns from the low power consumption state.

## 28.3.7 Procedure for Disabling Alarm Interrupt

Figure 28.8 shows the procedure for disabling the enabled alarm interrupt request.

Figure 28.8 Procedure for Disabling Alarm Interrupt Request

### 28.3.8 Time Error Adjustment Function

The time error adjustment function is used to correct errors (running fast or slow) in the time due to the precision of oscillation by the sub-clock. Since 32,768 cycles of the sub-clock constitute 1 second of operation when the sub-clock is selected, the clock runs fast if the sub-clock frequency is high and slow if the sub-clock frequency is low. This function can be used to correct errors due to the clock running fast or slow.

Two types of time error adjustment functions are provided: automatic adjustment and adjustment by software. Use the RCR2.AADJE bit to select automatic adjustment or adjustment by software.

#### 28.3.8.1 Automatic Adjustment

Enable automatic adjustment by setting the RCR2.AADJE bit to 1.

Automatic adjustment is the addition or subtraction of the value counted by the prescaler to or from the value in the RADJ register every time the adjustment period selected by the RCR2.AADJE bit elapses. Examples are shown below.

[Example 1] Sub-clock running at 32.769 kHz

Adjustment procedure:

When the sub-clock is running at 32.769 kHz, 1 second elapses every 32,769 clock cycles. The RTC is meant to run at 32,768 clock cycles, so the clock runs fast by one clock cycle every second. The time on the clock is fast by 60 clock cycles per minute, so adjustment can take the form of setting the clock back by 60 cycles every minute.

Register settings: (when RCR2.CNTMD = 0)

- RCR2.AADJP = 0 (adjustment every minute)

- RADJ.PMADJ[1:0] = 10b (adjustment is performed by the subtraction from the prescaler.)

- RADJ.ADJ[5:0] = 60 (3Ch)

[Example 2] Sub-clock running at 32.766 kHz

Adjustment procedure:

When the sub-clock is running at 32.766 kHz, 1 second elapses every 32,766 clock cycles. The RTC is meant to run at 32,768 clock cycles, so the clock runs slow by two clock cycles every second. The time on the clock is slow by 20 clock cycles every 10 seconds, so adjustment can take the form of setting the clock forward by 20 cycles every 10 seconds.

Register settings: (when RCR2.CNTMD = 0)

- RCR2.AADJP = 1 (adjustment every 10 seconds)

- RADJ.PMADJ[1:0] = 01b (adjustment is performed by the addition to the prescaler.)

- RADJ.ADJ[5:0] = 20 (14h)

[Example 3] Sub-clock running at 32.764 kHz

Adjustment procedure:

At 32.764 kHz, 1 second elapses on 32,764 clock cycles. Since the RTC operates for 32,768 clock cycles as 1 second, the clock is delayed for four clock cycles per second. In 8 seconds, the delay is 32 clock cycles, so correction can be made by proceeding the clock for 32 clock cycles every 8 seconds.

Register settings when the RCR2.CNTMD bit is 1

- RCR2.AADJP = 1 (adjustment every 8 seconds)

- RADJ.PMADJ[1:0] = 01b (adjustment is performed by the addition to the prescaler.)

- RADJ.ADJ[5:0] = 32 (20h)

#### 28.3.8.2 Adjustment by Software

Enable adjustment by software by setting the RCR2.AADJE bit to 0.

Adjustment by software is the addition or subtraction of the value counted by the prescaler to or from the value in the RADJ register at the time of execution of an instruction for writing to the RADJ register.

An example is shown below.

[Example 1] Sub-clock running at 32.769 kHz

Adjustment procedure:

When the sub-clock is running at 32.769 kHz, 1 second elapses every 32,769 clock cycles. The RTC is meant to run at 32,768 clock cycles, so the clock runs fast by one clock cycle every second. The time on the clock is fast by one clock cycle per second, so adjustment can take the form of setting the clock back by one cycle every second.

#### Register settings:

- RADJ.PMADJ[1:0] = 10b (adjustment is performed by the subtraction from the prescaler.)

- RADJ.ADJ[5:0] = 1 (01h)

This is written to the RADJ register once per 1-second interrupt.

## 28.3.8.3 Procedure for Changing the Mode of Adjustment

When changing the mode of adjustment, change the value of the AADJE bit in RCR2 after setting the RADJ.PMADJ[1:0] bits to 00b (adjustment is not performed).

Changing from adjustment by software to automatic adjustment:

- (1) Set the RADJ.PMADJ[1:0] bits to 00b (adjustment is not performed).

- (2) Set the RCR2.AADJE bit to 1 (automatic adjustment is enabled).

- (3) Use the RCR2.AADJP bit to select the period of adjustment.

- (4) In RADJ, set the PMADJ[1:0] bits for addition or subtraction and the ADJ[5:0] bits to the value for use in time error adjustment.

Changing from adjustment by software to automatic adjustment:

- (1) Set the RADJ.PMADJ[1:0] bits to 00b (adjustment is not performed).

- (2) Set the RCR2.AADJE bit to 0 (adjustment by software is enabled).

- (3) Proceed with adjustment by setting the RADJ.PMADJ[1:0] bits for addition or subtraction and the RADJ.ADJ[5:0] bits to the value for use in time error adjustment at the desired time. After that, the time is adjusted every time a value is written to the RADJ register.

#### 28.3.8.4 Procedure for Stopping Adjustment

Stop adjustment by setting the RADJ.PMADJ[1:0] bits to 00b (adjustment is not performed).

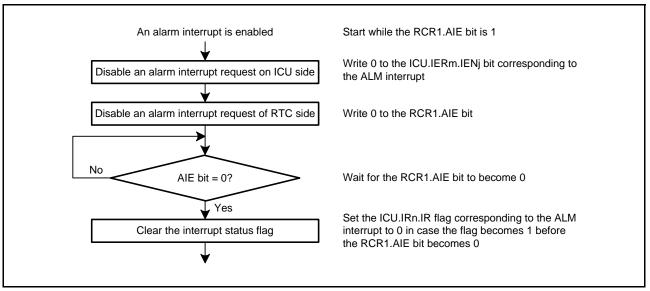

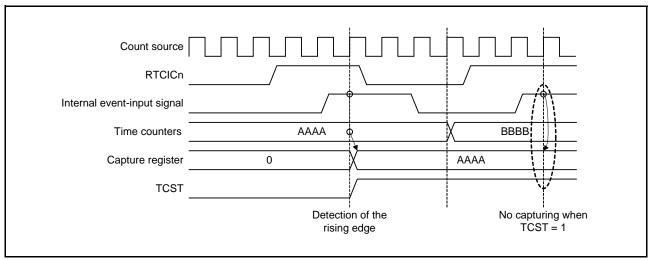

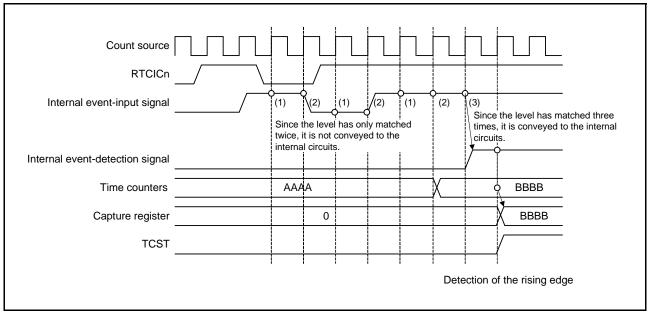

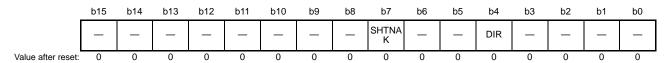

## 28.3.9 Time Capture Function

The RTC is capable of storing the month, date, hour, minute and second/binary counters 3 to 0 by detecting an edge of a signal on a time capture event input pin.

A noise filter can also be used on a time capture event input pin. If the noise filter is enabled, the TCST bit is set to 1 when the input level on the pin matches three times.

The noise filter can be switched on or off for each of the time capture event input pins. Operation when the noise filter is off is shown in Figure 28.9 and operation when the noise filter is on is shown in Figure 28.10.

Figure 28.9 Timing of a Time Capture Operation (with the Filter Off) (n = 0, 1)

Figure 28.10 Timing of a Time Capture Operation (with the Filter On) (n = 0, 1)

#### 28.4 Interrupt Sources

There are three interrupt sources in the realtime clock. Table 28.3 lists interrupt sources for the RTC.

Table 28.3 RTC Interrupt Sources

| Name | Interrupt Sources  |

|------|--------------------|

| ALM  | Alarm interrupt    |

| PRD  | Periodic interrupt |

| CUP  | Carry interrupt    |

#### (1) Alarm interrupt (ALM)

This interrupt is generated according to the result of comparison between the alarm registers and realtime clock counters (for details, refer to section 28.3.6, Alarm Function).

Since there is a possibility that the interrupt flag may be set to 1 when the settings of the alarm registers match the clock counters, wait for the alarm time settings to be confirmed and set the IR flag corresponding to the ALM interrupt to 0 again after modifying values of the alarm registers. Once the interrupt flag for the alarm interrupt has been set to 1 and the state has returned to non-matching of the alarm registers and clock counters, the flag will not be set again until there is a further match or the values of the alarm registers are modified again.

Figure 28.11 Timing Chart for the Alarm Interrupt (ALM)

#### (2) Periodic interrupt (PRD)

This interrupt is generated at intervals of 2 seconds, 1 second, 1/2 second, 1/4 second, 1/8 second, 1/16 second, 1/32 second, 1/64 second, 1/128 second, or 1/256 second. The interrupt interval can be selected through the RCR1.PES[3:0] bits.

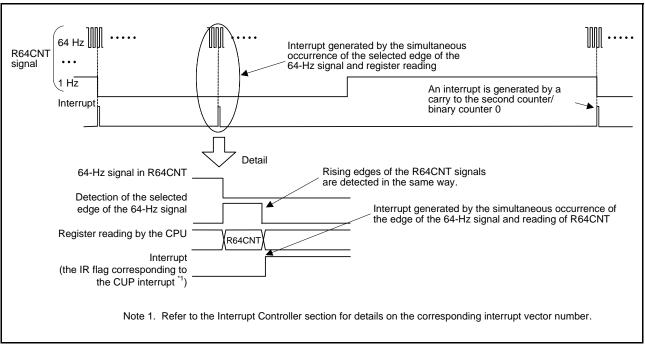

#### (3) Carry interrupt (CUP)

This interrupt is generated when a carry to the second counter/binary counter 0 occurred or a carry to the R64CNT counter occurred during read access to the 64-Hz counter.

Figure 28.12 Carry Interrupt (CUP) Timing Chart

#### 28.5 Event Link Output

The RTC outputs the following event signals for the event link controller (ELC), and these can be used to initiate operations by other modules selected in advance.

#### (1) Periodic event output

The periodic event signal is output at the interval selected from among 1/256, 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2, 1, and 2 seconds by the setting of the RCR1.PES[3:0] bits.

The event generation period immediately after the event generation is selected is not guaranteed.

Note: If event linking from the RTC is to be used, only make the ELC settings after making the RTC settings (initialization, time settings, etc.). Making the RTC settings after the ELC settings can lead to the output of unexpected event signals.

## 28.5.1 Interrupt Handling and Event Linking

The RTC has a bit to enable or disable periodic interrupts. An interrupt request signal is output for the CPU when an interrupt source is generated while the corresponding enable bit is enabled.

In contrast, an event link output signal is sent to other modules as an event signal via the ELC when an interrupt source is generated, regardless of the setting of the corresponding interrupt enable bit.

Note: Although alarm and periodic interrupts can still be output during software standby, the periodic event signals for the ELC are not output.

#### 28.6 Usage Notes

## 28.6.1 Register Writing during Counting

The following registers should not be written to during counting (while the RCR2.START bit = 1).

RSECCNT/BCNT0, RMINCNT/BCNT1, RHRCNT/BCNT2, RDAYCNT, RWKCNT/BCNT3, RMONCNT, RYRCNT, RCR1.RTCOS, RCR2.RTCOE, RCR2.HR24

The counter must be stopped before writing to any of the above registers.

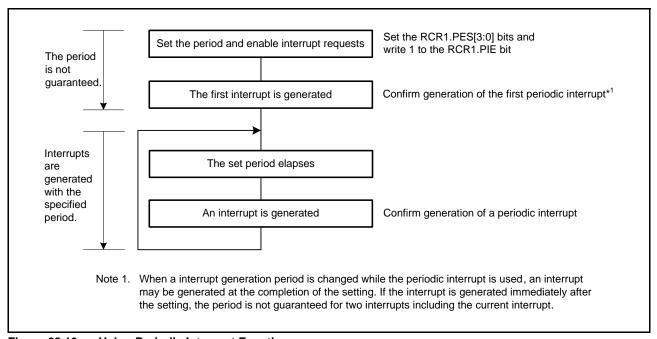

#### 28.6.2 Use of Periodic Interrupts

The procedure for using periodic interrupts is shown in Figure 28.13.

The generation and period of the periodic interrupt can be changed by the setting of the RCR1.PES[3:0] bits. However, since the prescaler, R64CNT, and RSECCNT/BCNT0 are used to generate interrupts, the interrupt period is not guaranteed immediately after setting of the RCR1.PES[3:0] bits.

Furthermore, stopping/restarting or resetting counter operation, reset by RTC software, and the 30-second adjustment by changing the RCR2 value affects the interrupt period. When the time error adjustment function is used, the interrupt generation period after adjustment is added or subtracted according to the adjustment value.

Figure 28.13 Using Periodic Interrupt Function

#### 28.6.3 RTCOUT (1-Hz/64-Hz) Clock Output

Stopping/restarting or resetting counter operation, reset by RTC software, and the 30-second adjustment by changing the RCR2 value affects the period of RTCOUT (1-Hz/64-Hz) output. When the time error adjustment function is used, the period of RTCOUT (1-Hz/64-Hz) output after adjustment is added or subtracted according to the adjustment value.

#### 28.6.4 Transitions to Low Power Consumption Modes after Setting Registers

A transition to a low power consumption state (software standby mode, or battery backup) during writing to or updating of an RTC register might destroy the register's value. After setting a register, confirm that the setting is in place before initiating a transition to a low power consumption state.

## 28.6.5 Notes on Writing to and Reading from Registers

- When reading a counter register such as the second counter after having written to the counter register, follow the procedure in section 28.3.5, Reading 64-Hz Counter and Time.

- The value written to the count registers, alarm registers, year alarm enable register, bits RCR2.AADJE, AADJP, and HR24, or RCR3 register is reflected when four read operations are performed after writing.

- The values written to the RCR1.CIE, RTCOS, and RCR2.RTCOE bits can be read immediately after writing.

- To read the value from the timer counter after return from a reset, software standby mode, or the battery backup state, wait for 1/128 second while the clock is operating (RCR2.START bit = 1).

- After a reset is generated, write to the RTC register when six cycles of the count source have elapsed.

## 28.6.6 Changing the Count Mode

When changing the count mode (calendar/binary), set the RCR2.START bit to 0, stop counting operation, then start again from the initial setting. For details on initial setting, refer to section 28.3.1, Outline of Initial Settings of Registers after Power On.

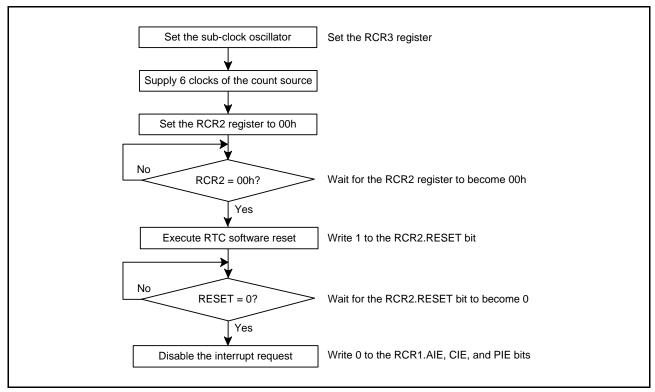

#### 28.6.7 Initialization Procedure When the Realtime Clock is Not to be Used

Registers in the RTC are not initialized by a reset. Accordingly, depending on the initial state, the generation of an unintentional interrupt request or operation of the counter may lead to increased power consumption.

For products that do not require a realtime clock, initialize the registers by following the initialization procedure shown in Figure 28.14.

Figure 28.14 Initialization Procedure

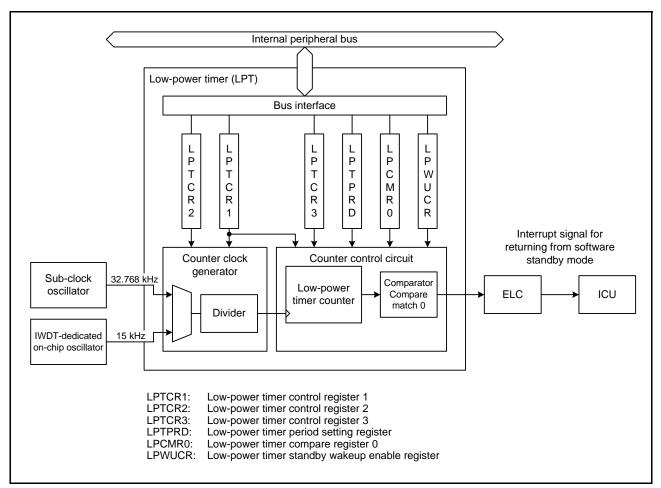

# 29. Low-Power Timer (LPT)

#### 29.1 Overview

This MCU integrates a low-power timer (LPT) that consists of a single-channel 16-bit timer. The LPT uses a sub-clock or IWDT-dedicated clock as the clock source, and can continue counting operation even in software standby mode. A compare match signal can be used to return from software standby mode to normal operating mode.

Table 29.1 lists the specifications of the LPT and Figure 29.1 shows a block diagram of the LPT.

Table 29.1 LPT Specifications

| Item                         | Description                                                                                                                         |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Clock source                 | Sub-clock or IWDT-dedicated clock                                                                                                   |

| Clock division ratio         | Divided by 2, 4, 8, 16, or 32                                                                                                       |

| Counting operation           | <ul> <li>Count up using the 16-bit up-counter</li> <li>Counting operation can be continued even in software standby mode</li> </ul> |

| Compare match                | Compare match 0 (a compare match signal is generated only in software standby mode)                                                 |

| Event link function (output) | Compare match 0 (a compare match signal is generated only in software standby mode)                                                 |

Figure 29.1 LPT Block Diagram

## 29.2 Register Descriptions

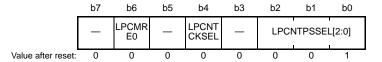

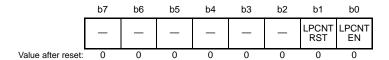

## 29.2.1 Low-Power Timer Control Register 1 (LPTCR1)

Address(es): LPT.LPTCR1 0008 00B0h

| Bit                                                    | Symbol     | Bit Name Description          |                                                                                                                                                       |     |

|--------------------------------------------------------|------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b2 to b0 LPCNTPSSEL[2:0] Clock Division Ratio Select*1 |            | Clock Division Ratio Select*1 | b2 b0 0 0 1: Divided by 2 0 1 0: Divided by 4 0 1 1: Divided by 8 1 0 0: Divided by 16 1 0 1: Divided by 32 Settings other than above are prohibited. | R/W |

| b3                                                     | _          | Reserved                      | This bit is read as 0. The write value should be 0.                                                                                                   | R/W |

| b4                                                     | LPCNTCKSEL | Clock Source Select*1, *2     | 0: Sub-clock<br>1: IWDT-dedicated clock (IWDTCLK)*3                                                                                                   | R/W |

| b5                                                     | _          | Reserved                      | This bit is read as 0. The write value should be 0.                                                                                                   | R/W |

| b6                                                     | LPCMRE0    | Compare Match 0 Enable*4      | 0: Compare match 0 is disabled 1: Compare match 0 is enabled                                                                                          | R/W |

| b7                                                     | _          | Reserved                      | This bit is read as 0. The write value should be 0.                                                                                                   | R/W |

- Note: Set the PRCR.PRC2 bit to 1 (write enabled) before rewriting this register.

- Note 1. Rewrite these bits while the LPTCR2.LPCNTSTP bit is 1 (supply of clock to the low-power timer is stopped).

- Note 2. Satisfy that the frequency of the system clock (ICLK) and peripheral module clock (PCLKB) ≥ 4 x (the frequency of the clock source).

- Note 3. A clock generated by the IWDT-dedicated on-chip oscillator (IWDTCLK) is supplied to the low-power timer. When modifying this bit, make sure that the IWDT-dedicated on-chip oscillator is oscillating stably.

When the IWDTCLK is used as the clock source for the low-power timer, set the OFS0.IWDTSLCSTP bit to 0 (counting stop is disabled) in IWDT auto-start mode operation, and set the IWDTCSTPR.SLCSTP bit to 0 (count stop is disabled) in other modes. Without this setting, the IWDT-dedicated on-chip oscillator is stopped in software standby mode.

- Note 4. Rewrite this bit while the LPTCR3.LPCNTEN bit is 0 (low-power timer counter stops).

The LPTCR1 register is used to control the low-power timer.

#### LPCNTCKSEL Bit (Clock Source Select)

This bit is used to select the sub-clock or IWDT-dedicated clock as the clock source for the low-power timer.

#### LPCMRE0 Bit (Compare Match 0 Enable)

This bit enables or disables low-power timer compare match 0.

When the low-power timer is put into operation and the MCU makes a transition to software standby mode while this bit and the LPWUCR.LPWKUPEN bit are set to 1 (wakeup from software standby mode using low-power timer is enabled), the MCU returns from software standby mode to normal operating mode through the event link controller (ELC) when the value of the low-power timer counter matches the value of the LPCMR0 register.

Settings for the interrupt and ELC are necessary to use a compare match 0 as a trigger source to return from software standby mode.

Refer to section 20, Event Link Controller (ELC) for details on the ELC settings, and refer to section 15, Interrupt Controller (ICUb) for details on the interrupt settings.

An interrupt request at compare match 0 is generated only in software standby mode. It is not generated in normal operating mode, sleep mode, and deep sleep mode.

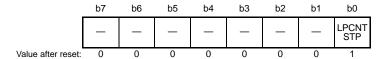

## 29.2.2 Low-Power Timer Control Register 2 (LPTCR2)

Address(es): LPT.LPTCR2 0008 00B1h

| Bit      | Symbol   | Bit Name             | Description                                                                                                                  | R/W |

|----------|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------|-----|

| b0       | LPCNTSTP | Clock Supply Control | <ul><li>0: Clock is supplied to the low-power timer.</li><li>1: Supply of clock to the low-power timer is stopped.</li></ul> | R/W |

| b7 to b1 | _        | Reserved             | These bits are read as 0. The write value should be 0.                                                                       | R/W |

Note: Set the PRCR.PRC2 bit to 1 (write enabled) before rewriting this register.

The LPTCR2 register is used to control supply of the clock to be used for the low-power timer.

#### **LPCNTSTP Bit (Clock Supply Control)**

This bit is used to supply or stop the clock to be used for the low-power timer. When this bit is set to 0, the clock signal is supplied to the low-power timer counter and divider.

## 29.2.3 Low-Power Timer Control Register 3 (LPTCR3)

Address(es): LPT.LPTCR3 0008 00B2h

| Bit      | Symbol   | Bit Name                                                                                                       | Description                                                                                                                                                                                   | R/W |

|----------|----------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0       | LPCNTEN  | Low-Power Timer Counter 0: Low-power timer counter stops Operation Control 1: Low-power timer counter operates |                                                                                                                                                                                               | R/W |

| b1       | LPCNTRST | Low-Power Timer Counter<br>Clear*1, *2                                                                         | <ul> <li>When writing</li> <li>0: Has no effect</li> <li>1: Clears divider and counter</li> <li>When reading</li> <li>0: Clearing is completed</li> <li>1: Clearing is in progress</li> </ul> | R/W |

| b7 to b2 | _        | Reserved                                                                                                       | These bits are read as 0. The write value should be 0.                                                                                                                                        | R/W |

Note: Set the PRCR.PRC2 bit to 1 (write enabled) before rewriting this register.

Note: Rewrite this register while the LPTCR2.LPCNTSTP bit is 0 (clock is supplied to the low-power timer).

Note 1. Rewrite this bit while the LPTCR3.LPCNTEN bit is 0 (low-power timer counter stops).

Note 2. When clearing the low-power timer counter successively, confirm that the LPCNTRST bit becomes 0, wait for at least one cycle of the clock selected by the LPTCR1.LPCNTCKSEL bit, and then write 1 to the LPCNTRST bit again.

The LPTCR3 register controls operations of and clears the low-power timer counter and divider.

#### **LPCNTEN Bit (Low-Power Timer Counter Operation Control)**

This bit is used to operate or stop the low-power timer counter and divider.

When this bit is set to 1 while the LPTCR2.LPCNTSTP bit is 0 (clock is supplied to the low-power timer), the low-power timer counter and divider start operating.

Do not write 1 to the LPCNTRST bit while this bit is 1.

#### **LPCNTRST Bit (Low-Power Timer Counter Clear)**

This bit is used to clear the low-power timer counter and divider.

When this bit is set to 1 while the LPTCR2.LPCNTSTP bit is 0 (clock is supplied to the low-power timer), the low-power timer counter and divider are cleared in synchronization with the clock used for the low-power timer. Once clearing is complete, this bit automatically becomes 0.

When 1 is written to this bit, confirm that its value becomes 0 before executing the next processing.

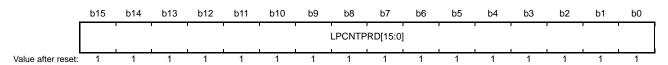

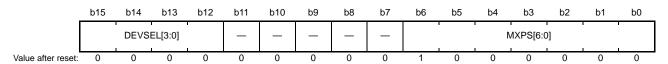

## 29.2.4 Low-Power Timer Period Setting Register (LPTPRD)

Address(es): LPT.LPTPRD 0008 00B4h

| Bit       | Symbol         | Bit Name               | Description                            | R/W |

|-----------|----------------|------------------------|----------------------------------------|-----|

| b15 to b0 | LPCNTPRD[15:0] | Low-Power Timer Period | Set the period of the low-power timer. | R/W |

|           |                | Setting                | Setting range: 0001h to FFFFh          |     |

Note: Set the PRCR.PRC2 bit to 1 (write enabled) before rewriting this register.

Note: Rewrite this register while the LPTCR3.LPCNTEN bit is 0 (low-power timer counter stops).

The LPTPRD register is used to set the period of the low-power timer.

The period of the low-power timer is proportional to "LPTPRD + 1" and calculated by the following formula:

Period of low-power timer = period of clock source × division ratio × (LPTPRD + 1)

When the value of the low-power timer counter matches the set value, the counter is cleared to 0000h and continues counting.

Do not set this register to 0000h.

Table 29.2, and Table 29.3 list examples of setting the periods of the low-power timer. These examples show values most approximate to the periods.

Table 29.2 Example of Low-Power Timer Period Settings for IWDTCLK

| Division ratio     | Divided by 2 |                    |              | Divided by 4 |                   |              | Divided by 8 |                   |              |

|--------------------|--------------|--------------------|--------------|--------------|-------------------|--------------|--------------|-------------------|--------------|

| Target period (ms) | Set<br>Value | Actual period (ms) | Error<br>(%) | Set<br>Value | Actual period (ms | Error<br>(%) | Set<br>Value | Actual period (ms | Error<br>(%) |

| 1                  | 0006h        | 0.93               | -6.67        | 0003h        | 1.07              | 6.67         | 0001h        | 1.07              | 6.67         |

| 2                  | 000Dh        | 1.87               | -6.67        | 0006h        | 1.87              | -6.67        | 0003h        | 2.13              | 6.67         |

| 5                  | 0024h        | 4.93               | -1.33        | 0011h        | 4.80              | -4.00        | 0008h        | 4.80              | -4.00        |

| 10                 | 004Ah        | 10.00              | 0.00         | 0024h        | 9.87              | -1.33        | 0011h        | 9.60              | -4.00        |

| 20                 | 0095h        | 20.00              | 0.00         | 004Ah        | 20.00             | 0.00         | 0024h        | 19.73             | -1.33        |

| 50                 | 0176h        | 50.00              | 0.00         | 00BAh        | 49.87             | -0.27        | 005Ch        | 49.60             | -0.80        |

| 100                | 02EDh        | 100.00             | 0.00         | 0176h        | 100.00            | 0.00         | 00BAh        | 99.73             | -0.27        |

| 200                | 05DBh        | 200.00             | 0.00         | 02EDh        | 200.00            | 0.00         | 0176h        | 200.00            | 0.00         |

| 500                | 0EA4h        | 499.87             | -0.03        | 0751h        | 499.73            | -0.05        | 03A8h        | 499.73            | -0.05        |

| 1000               | 1D4Ah        | 999.87             | -0.01        | 0EA4h        | 999.73            | -0.03        | 0751h        | 999.47            | -0.05        |

| 2000               | 3A96h        | 1999.87            | -0.01        | 1D4Ah        | 1999.73           | -0.01        | 0EA4h        | 1999.47           | -0.03        |

| 5000               | 927Bh        | 5000.00            | 0.00         | 493Dh        | 5000.00           | 0.00         | 249Eh        | 5000.00           | 0.00         |

| 10000              | _            | _                  |              | _            | _                 | _            | 493Dh        | 10000.00          | 0.00         |

| 20000              | _            | _                  | _            | _            | _                 | _            | 927Bh        | 20000.00          | 0.00         |

| 50000              | _            | _                  | _            | _            | _                 | _            | _            | _                 | _            |

| Division ratio     | Divided      | ed by 16 Divided by 32 |              |              |                   |              |

|--------------------|--------------|------------------------|--------------|--------------|-------------------|--------------|

| Target period (ms) | Set<br>Value | Actual period (ms      | Error<br>(%) | Set<br>Value | Actual period (ms | Error<br>(%) |

| 1                  | _            | _                      | _            | _            | _                 | _            |

| 2                  | 0001h        | 2.13                   | 6.67         | _            | _                 | _            |

| 5                  | 0004h        | 5.33                   | 6.67         | 0001h        | 4.27              | -14.67       |

| 10                 | 0008h        | 9.60                   | -4.00        | 0004h        | 10.67             | 6.67         |

| 20                 | 0011h        | 19.20                  | -4.00        | 0008h        | 19.20             | -4.00        |

| 50                 | 002Dh        | 49.07                  | -1.87        | 0016h        | 49.07             | -1.87        |

| 100                | 005Ch        | 99.20                  | -0.80        | 002Dh        | 98.13             | -1.87        |

| 200                | 00BAh        | 199.47                 | -0.27        | 005Ch        | 198.40            | -0.80        |

| 500                | 01D3h        | 499.20                 | -0.16        | 00E9h        | 499.20            | -0.16        |

| 1000               | 03A8h        | 999.47                 | -0.05        | 01D3h        | 998.40            | -0.16        |

| 2000               | 0751h        | 1998.93                | -0.05        | 03A8h        | 1998.93           | -0.05        |

| 5000               | 124Eh        | 4999.47                | -0.01        | 0926h        | 4998.40           | -0.03        |

| 10000              | 249Eh        | 10000.00               | 0.00         | 124Eh        | 9998.93           | -0.01        |

| 20000              | 493Dh        | 20000.00               | 0.00         | 249Eh        | 20000.00          | 0.00         |

| 50000              | B71Ah        | 50000.00               | 0.00         | 5B8Ch        | 49998.93          | 0.00         |

Table 29.3 Example of Low-Power Timer Period Settings for Sub-Clock

| Division ratio     | Divided by 2 |                    |              |              | Divided by 4      |              |              | Divided by 8      |              |  |

|--------------------|--------------|--------------------|--------------|--------------|-------------------|--------------|--------------|-------------------|--------------|--|

| Target period (ms) | Set<br>Value | Actual period (ms) | Error<br>(%) | Set<br>Value | Actual period (ms | Error<br>(%) | Set<br>Value | Actual period (ms | Error<br>(%) |  |

| 1                  | 000Fh        | 0.98               | -2.34        | 0007h        | 0.98              | -2.34        | 0003h        | 0.98              | -2.34        |  |

| 2                  | 001Fh        | 1.95               | -2.34        | 000Fh        | 1.95              | -2.34        | 0007h        | 1.95              | -2.34        |  |

| 5                  | 0050h        | 4.94               | -1.12        | 0027h        | 4.88              | -2.34        | 0013h        | 4.88              | -2.34        |  |

| 10                 | 00A2h        | 9.95               | -0.51        | 0050h        | 9.89              | -1.12        | 0027h        | 9.77              | -2.34        |  |

| 20                 | 0146h        | 19.96              | -0.21        | 00A2h        | 19.90             | -0.51        | 0050h        | 19.78             | -1.12        |  |

| 50                 | 0332h        | 49.99              | -0.02        | 0198h        | 49.93             | -0.15        | 00CBh        | 49.80             | -0.39        |  |

| 100                | 0665h        | 99.98              | -0.02        | 0332h        | 99.98             | -0.02        | 0198h        | 99.85             | -0.15        |  |

| 200                | 0CCBh        | 199.95             | -0.02        | 0665h        | 199.95            | -0.02        | 0332h        | 199.95            | -0.02        |  |

| 500                | 1FFFh        | 500.00             | 0.00         | 0FFFh        | 500.00            | 0.00         | 07FFh        | 500.00            | 0.00         |  |

| 1000               | 3FFFh        | 1000.00            | 0.00         | 1FFFh        | 1000.00           | 0.00         | 0FFFh        | 1000.00           | 0.00         |  |

| 2000               | 7FFFh        | 2000.00            | 0.00         | 3FFFh        | 2000.00           | 0.00         | 1FFFh        | 2000.00           | 0.00         |  |

| 5000               |              | _                  | _            | 9FFFh        | 5000.00           | 0.00         | 4FFFh        | 5000.00           | 0.00         |  |

| 10000              |              | _                  | _            | _            | _                 | _            | 9FFFh        | 10000.00          | 0.00         |  |

| 20000              | _            | _                  | _            | _            | _                 | _            | _            | _                 | _            |  |

| 50000              | _            | _                  | _            | _            | _                 | _            | _            | _                 | _            |  |

| Division ratio     | Divided      | by 16             |              | Divided by 32 |                   |              |  |

|--------------------|--------------|-------------------|--------------|---------------|-------------------|--------------|--|

| Target period (ms) | Set<br>Value | Actual period (ms | Error<br>(%) | Set<br>Value  | Actual period (ms | Error<br>(%) |  |

| 1                  | 0001h        | 0.98              | -2.34        | _             | _                 | _            |  |

| 2                  | 0003h        | 1.95              | -2.34        | 0001h         | 1.95              | -2.34        |  |

| 5                  | 0009h        | 4.88              | -2.34        | 0004h         | 4.88              | -2.34        |  |

| 10                 | 0013h        | 9.77              | -2.34        | 0009h         | 9.77              | -2.34        |  |

| 20                 | 0027h        | 19.53             | -2.34        | 0013h         | 19.53             | -2.34        |  |

| 50                 | 0065h        | 49.80             | -0.39        | 0032h         | 49.80             | -0.39        |  |

| 100                | 00CBh        | 99.61             | -0.39        | 0065h         | 99.61             | -0.39        |  |

| 200                | 0198h        | 199.71            | -0.15        | 00CBh         | 199.22            | -0.39        |  |

| 500                | 03FFh        | 500.00            | 0.00         | 01FFh         | 500.00            | 0.00         |  |

| 1000               | 07FFh        | 1000.00           | 0.00         | 03FFh         | 1000.00           | 0.00         |  |

| 2000               | 0FFFh        | 2000.00           | 0.00         | 07FFh         | 2000.00           | 0.00         |  |

| 5000               | 27FFh        | 5000.00           | 0.00         | 13FFh         | 5000.00           | 0.00         |  |

| 10000              | 4FFFh        | 10000.00          | 0.00         | 27FFh         | 10000.00          | 0.00         |  |

| 20000              | 9FFFh        | 20000.00          | 0.00         | 4FFFh         | 20000.00          | 0.00         |  |

| 50000              | _            | _                 |              | C7FFh         | 50000.00          | 0.00         |  |

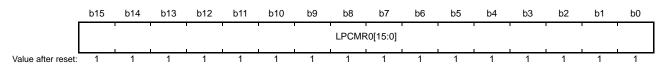

## 29.2.5 Low-Power Timer Compare Register 0 (LPCMR0)

Address(es): LPT.LPCMR0 0008 00B8h

| Bit       | Symbol       | Bit Name                  | Description                                                   | R/W |

|-----------|--------------|---------------------------|---------------------------------------------------------------|-----|

| b15 to b0 | LPCMR0[15:0] | Low-Power Timer Compare 0 | Set the value of compare match 0 for comparison with the low- | R/W |

|           |              |                           | power timer counter.                                          |     |

Note: Set the PRCR.PRC2 bit to 1 (write enabled) before rewriting this register.

Note: Rewrite this register while the LPTCR3.LPCNTEN bit is 0 (low-power timer counter stops).

The LPCMR0 register is used to set the value of compare match 0 for comparison with the low-power timer counter. Set the LPCMR0 register to a value smaller than or equal to the value of the LPTPRD register.

## 29.2.6 Low-Power Timer Standby Wakeup Enable Register (LPWUCR)

Address(es): LPT.LPWUCR 0008 00BCh

| Bit       | Symbol   | Bit Name                                   | Description                                                                                                                                | R/W |

|-----------|----------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b14 to b0 | _        | Reserved                                   | These bits are read as 0. The write value should be 0.                                                                                     | R/W |

| b15       | LPWKUPEN | Low-Power Timer Standby<br>Wakeup Enable*1 | Wakeup from software standby mode using low-power timer is disabled     Wakeup from software standby mode using low-power timer is enabled | R/W |

Note: Set the PRCR.PRC2 bit to 1 (write enabled) before rewriting this register.

Note 1. Rewrite this bit while the LPTCR3.LPCNTEN bit is 0 (low-power timer counter stops).

The LPWUCR register is used to enable the function that allows to return from software standby mode to normal operating mode when compare match 0 occurs in the low-power timer.

#### LPWKUPEN Bit (Low-Power Timer Standby Wakeup Enable)

This bit enables or disables the function that allows to return from software standby mode to normal operating mode when compare match 0 occurs in the low-power timer.

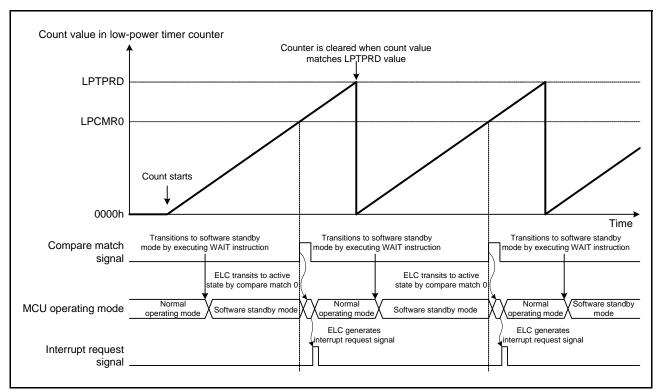

## 29.3 Operation

## 29.3.1 Periodic Counting Operation

The low-power timer is a 16-bit up-counter that operates regardless of the MCU operating mode\*1.

When the LPTCR3.LPCNTEN bit is set to 1 (low-power timer counter operates) after setting the

LPTCR1.LPCNTPSSEL[2:0] bits to select the division ratio, the LPTCR1.LPCNTCKSEL bit to select the clock source, and the LPTCR2.LPCNTSTP bit to 0 (clock is supplied to the low-power timer), the low-power timer counter starts counting with the selected clock.

When the value of the low-power timer counter matches the value of the LPTPRD register, the counter restarts counting from 0000h.

When the value of the low-power timer counter matches the value of the LPCMR0 register in software standby mode while the LPTCR1.LPCMRE0 bit is set to 1 (Compare match 0 is enabled) and the LPWUCR.LPWKUPEN bit is set to 1 (wakeup from software standby mode using low-power timer is enabled), the MCU returns from software standby mode to normal operating mode by the function of the event link controller (ELC).

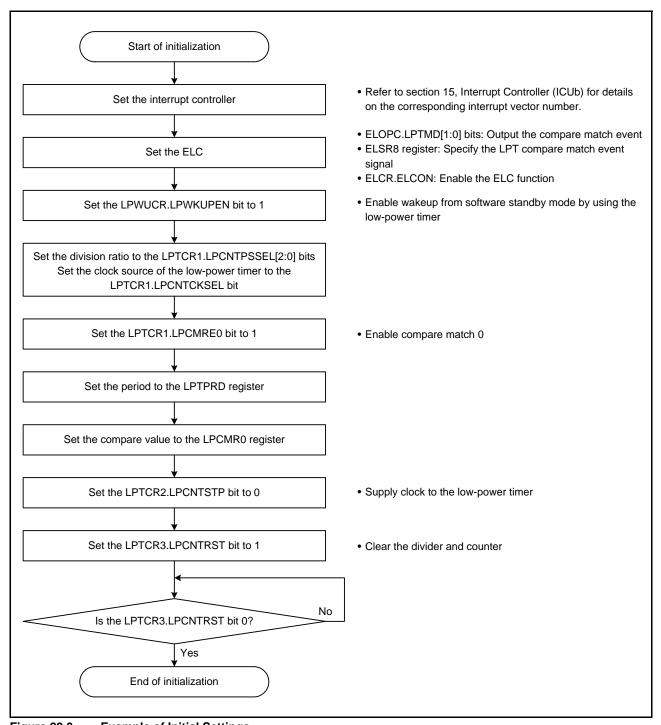

Figure 29.2 shows operation of the low-power timer and Figure 29.3 shows an example of procedure for the initial settings.

Note 1. When the LPTCR1.LPCNTCKSEL bit is set to 1 (IWDT-dedicated clock), the counter stops because the IWDTCLK stops in the low-power consumption mode under the following settings:

The OFS0.IWDTSLCSTP bit is set to 1 (counting stop is enabled) while IWDT is activated in auto-start mode, or the IWDTCSTPR.SLCSTP bit is set to 1 (counting stop is enabled) while IWDT is activated in register start mode.

Figure 29.2 Operation of Low-Power Timer

Figure 29.3 Example of Initial Settings

#### 29.3.2 Count Timing of Low-Power Timer Counter

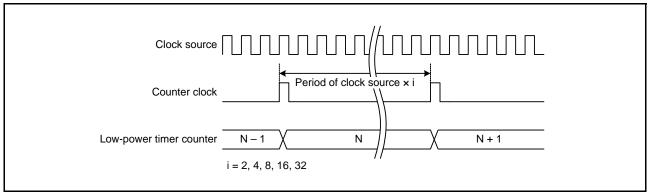

The LPTCR1.LPCNTPSSEL[2:0] bits are used to select the counter clock to be input to the low-power timer counter from among five clocks derived from dividing the clock source selected by the LPTCR1.LPCNTCKSEL bit by 2 to 32, respectively.

Figure 29.4 shows the count timing of the low-power timer counter in this case.

Figure 29.4 Count Timing of Low-Power Timer Counter

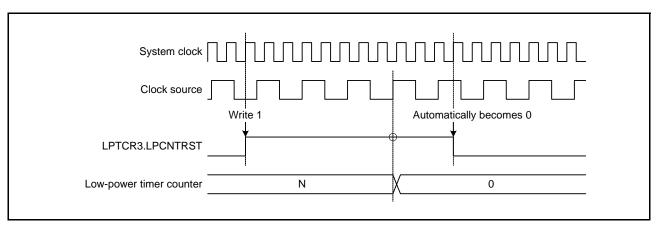

## 29.3.3 Clearing Timing of Low-Power Timer Counter

Writing 1 to the LPTCR3.LPCNTRST bit\*1 clears the low-power timer counter.

This bit automatically becomes 0 when the clearing of the counter is completed.

Figure 29.5 shows the clearing timing of the low-power timer counter in this case.

Note 1. Write to the LPTCR3.LPCNTRST bit while the LPTCR3.LPCNTEN bit is 0 (low-power timer counter stops).

Figure 29.5 Clearing Timing of Low-Power Timer Counter

# 29.4 Wakeup from Software Standby Mode by an Interrupt through the Event Link Controller (ELC)

The low-power timer generates an event signal upon LPT compare match 0 to the event link controller (ELC) only in software standby mode.

Setting the ELOPC.LPTMD[1:0] bits to 00b (output the compare match 0 event to ICU as an interrupt request) and the ELSR8 register to 32h (LPT compare match 0) leads to the generation of an interrupt from the event signal, and the MCU returns from software standby mode to normal operating mode.

## 29.5 Usage Notes

## 29.5.1 Notes on Transition to Software Standby Mode

When the MCU is to re-enter to software standby mode after returning from software standby mode to normal operating mode, wait for at least one cycle of the clock selected by the LPTCR1.LPCNTCKSEL bit before executing the WAIT instruction.

# 30. Watchdog Timer (WDTA)

The watchdog timer (WDT) is a 14-bit down-counter. It can be used to reset this MCU when the counter underflows because its value cannot be refreshed due to the system being out of control.

In addition, a non-maskable interrupt can be generated by an underflow.

The refresh-permitted period can be set to refresh the counter and used as the condition to detect when the system runs out of control.

In this section, "PCLK" is used to refer to PCLKB.

#### 30.1 Overview

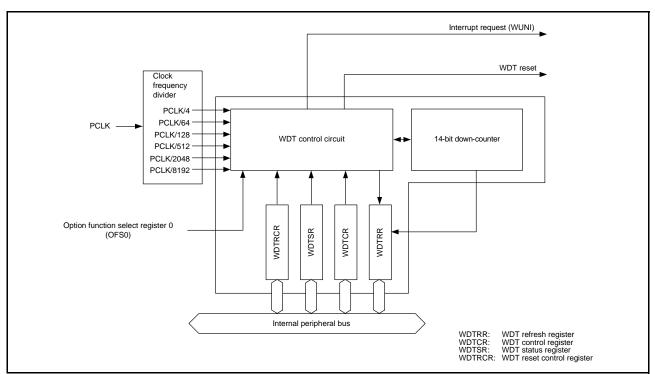

Table 30.1 lists the specifications of the WDT and Figure 30.1 shows a block diagram of the WDT.

Table 30.1 WDT Specifications

| Item                                | Specifications                                                                                                                                                                                                                 |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Count source                        | Peripheral module clock (PCLK)                                                                                                                                                                                                 |

| Clock division ratio                | Divide by 4, 64, 128, 512, 2048, or 8192                                                                                                                                                                                       |

| Counter operation                   | Counting down using a 14-bit down-counter                                                                                                                                                                                      |

| Conditions for starting the counter | <ul> <li>Auto-start mode: Counting automatically starts after a reset is released</li> <li>Register start mode: Counting is started by refresh operation (writing 00h and then FFh to the WDTRR register)</li> </ul>           |

| Conditions for stopping the counter | <ul> <li>Reset (the down-counter and other registers return to their initial values)</li> <li>In low power consumption states</li> <li>A counter underflows or a refresh error occurs (only in register start mode)</li> </ul> |

| Window function                     | Window start and end positions can be specified (refresh-permitted and refresh-prohibited periods)                                                                                                                             |

| Watchdog timer<br>Reset sources     | <ul> <li>Down-counter underflows</li> <li>Refreshing outside the refresh-permitted period (refresh error)</li> </ul>                                                                                                           |

| Non-maskable interrupt sources      | <ul> <li>Down-counter underflows</li> <li>Refreshing outside the refresh-permitted period (refresh error)</li> </ul>                                                                                                           |

| Reading the counter value           | The down-counter value can be read by the WDTSR register.                                                                                                                                                                      |

Figure 30.1 WDT Block Diagram

## 30.2 Register Descriptions

## 30.2.1 WDT Refresh Register (WDTRR)

Address(es): 0008 8020h

| Bit      | Description                                                                        | R/W |

|----------|------------------------------------------------------------------------------------|-----|

| b7 to b0 | The down-counter is refreshed by writing 00h and then writing FFh to this register | R/W |

WDTRR refreshes the down-counter of the WDT.

The down-counter of the WDT is refreshed by writing 00h and then writing FFh to WDTRR (refresh operation) within the refresh-permitted period.

After the down-counter has been refreshed, it starts counting down from the value selected by setting the

WDTTOPS[1:0] bits in option function select register 0 (OFS0) in auto-start mode. In register start mode, counting down starts from the value selected by setting the WDTCR.TOPS[1:0] bits.

When 00h is written, the read value is 00h, when a value other than 00h is written, the read value is FFh.

For details of the refresh operation, refer to section 30.3.3, Refresh Operation.

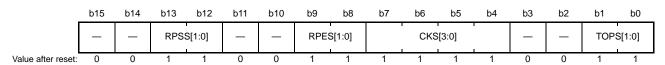

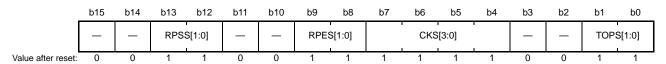

## 30.2.2 WDT Control Register (WDTCR)

Address(es): 0008 8022h

| Bit      | Symbol    | Bit Name                        | Description                                                                                                                                                                             | R/W |

|----------|-----------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b1, b0   | TOPS[1:0] | Timeout Period Selection        | b1 b0<br>0 0: 1024 cycles (03FFh)<br>0 1: 4096 cycles (0FFFh)<br>1 0: 8192 cycles (1FFFh)<br>1 1: 16384 cycles (3FFFh)                                                                  |     |

| b3, b2   | _         | Reserved                        | These bits are read as 0 and cannot be modified.                                                                                                                                        | R   |

| b7 to b4 | CKS[3:0]  | Clock Division Ratio Selection  | b7 b4 0 0 0 1: Divide-by-4 0 1 0 0: Divide-by-64 1 1 1 1: Divide-by-128 0 1 1 0: Divide-by-512 0 1 1 1: Divide-by-2048 1 0 0 0: Divide-by-8192 Setting other than above are prohibited. | R/W |

| b9, b8   | RPES[1:0] | Window End Position Selection   | b9 b8<br>0 0: 75%<br>0 1: 50%<br>1 0: 25%<br>1 1: 0% (window end position is not specified)                                                                                             | R/W |

| b11, b10 | _         | Reserved                        | These bits are read as 0 and cannot be modified.                                                                                                                                        | R   |

| b13, b12 | RPSS[1:0] | Window Start Position Selection | b13 b12<br>0 0: 25%<br>0 1: 50%<br>1 0: 75%<br>1 1: 100% (window start position is not specified)                                                                                       | R/W |

| b15, b14 | _         | Reserved                        | These bits are read as 0 and cannot be modified.                                                                                                                                        | R   |

There are some restrictions on writing to the WDTCR register. For details, refer to section 30.3.2, Control over Writing to the WDTCR and WDTRCR Registers.

In auto-start mode, the settings in the WDTCR register are disabled, and the settings in option function select register 0 (OFS0) are enabled. The bit setting made to the WDTCR register can also be made in OFS0 register. For details, refer to section 30.3.7, Correspondence between Option Function Select Register 0 (OFS0) and WDT Registers.

#### TOPS[1:0] Bits (Timeout Period Selection)

These bits select the timeout period (period until the down-counter underflows) from among 1024, 4096, 8192, and 16384 cycles, taking the divided clock specified by the CKS[3:0] bits as one cycle.

After the down-counter is refreshed, the combination of the CKS[3:0] and TOPS[1:0] bits determines the time (number of PCLK cycles) until the counter underflows.

Relations between the CKS[3:0] and TOPS[1:0] bit settings, the timeout period, and the number of PCLK cycles are listed in Table 30.2.

Table 30.2 Timeout Period Settings

| CKS[3:0] Bits |    | TOPS[1:0] Bits             |    |      | Timeout Period |                      |                    |                      |  |

|---------------|----|----------------------------|----|------|----------------|----------------------|--------------------|----------------------|--|

| b7            | b6 | b5                         | b4 | b1   | b0             | Clock Division Ratio | (Number of Cycles) | Cycles of PCLK Clock |  |

| 0             | 0  | 0 0 1 0 0 Divide-by-4 1024 |    | 1024 | 4096           |                      |                    |                      |  |

|               |    |                            | _  | 0    | 1              |                      | 4096               | 16384                |  |

|               |    |                            | _  | 1    | 0              |                      | 8192               | 32768                |  |

|               |    |                            | _  | 1    | 1              |                      | 16384              | 65536                |  |

| 0             | 1  | 0                          | 0  | 0    | 0              | Divide-by-64         | 1024               | 65536                |  |

|               |    |                            | _  | 0    | 1              |                      | 4096               | 262144               |  |

|               |    |                            | _  | 1    | 0              |                      | 8192               | 524288               |  |

|               |    |                            | _  | 1    | 1              |                      | 16384              | 1048576              |  |

| 1             | 1  | 1                          | 1  | 0    | 0              | Divide-by-128        | 1024               | 131072               |  |

|               |    |                            | _  | 0    | 1              |                      | 4096               | 524288               |  |

|               |    |                            | _  | 1    | 0              |                      | 8192               | 1048576              |  |

|               |    |                            | _  | 1    | 1              |                      | 16384              | 2097152              |  |

| 0             | 1  | 1                          | 0  | 0    | 0              | Divide-by-512        | 1024               | 524288               |  |

|               |    |                            | _  | 0    | 1              |                      | 4096               | 2097152              |  |

|               |    |                            | _  | 1    | 0              |                      | 8192               | 4194304              |  |

|               |    |                            | _  | 1    | 1              |                      | 16384              | 8388608              |  |

| 0             | 1  | 1                          | 1  | 0    | 0              | Divide-by-2048       | 1024               | 2097152              |  |

|               |    |                            | _  | 0    | 1              |                      | 4096               | 8388608              |  |

|               |    |                            | _  | 1    | 0              |                      | 8192               | 16777216             |  |

|               |    |                            | _  | 1    | 1              |                      | 16384              | 33554432             |  |

| 1             | 0  | 0                          | 0  | 0    | 0              | Divide-by-8192       | 1024               | 8388608              |  |

|               |    |                            | _  | 0    | 1              | <del>_</del>         | 4096               | 33554432             |  |

|               |    |                            | _  | 1    | 0              | <del>_</del>         | 8192               | 67108864             |  |

|               |    |                            | _  | 1    | 1              | _                    | 16384              | 134217728            |  |

#### CKS[3:0] Bits (Clock Division Ratio Selection)

These bits specify the division ration of the clock used for the down-counter. The division ration can be selected from among the peripheral module clock (PCLK) divided by 4, 64, 128, 512, 2048, and 8192. Combined with the TOPS[1:0] bit setting, a count period between 4,096 and 134,217,728 cycles of the PCLK clock can be selected for the WDT.

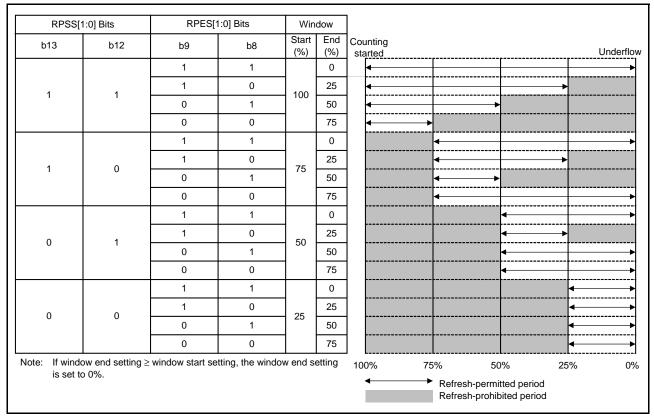

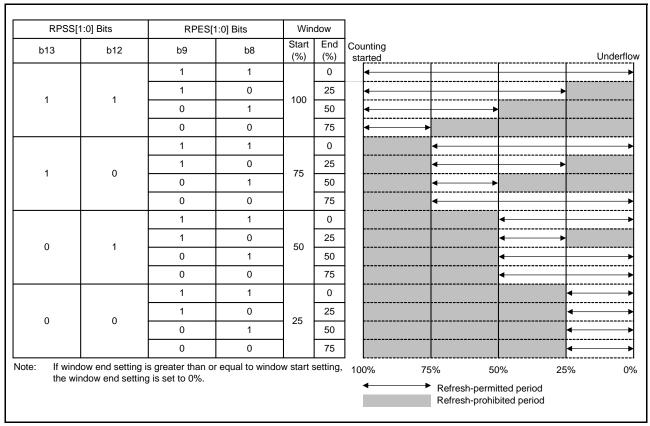

#### RPES[1:0] Bits (Window End Position Selection)

These bits specify the window end position that indicates the refresh-permitted period. 75%, 50%, 25%, or 0% of the timeout period can be selected for the window end position. The selected window end position should be a value smaller than the window start position (window start position > window end position). If the window end position is greater than the window start position, only the window start position setting is enabled.

#### RPSS[1:0] Bits (Window Start Position Selection)

These bits specify the window start position that indicates the refresh-permitted period. 25%, 50%, 75%, or 100% of the timeout period can be selected for the window end position. The window start position should be set to a value greater the window end position. If the window start position is set to a value smaller than or equal to the window end position, the window end position is set to 0%.

Table 30.3 lists the counter values for the window start and end positions and Figure 30.2 shows the refresh-permitted period set by the RPSS[1:0], RPES[1:0], and TOPS[1:0] bits.

Table 30.3 Relationship between Timeout Period and Window Start and End Counter Values

| Timeout Period |   |        | Window Start and End Counter Value |       |       |       |       |

|----------------|---|--------|------------------------------------|-------|-------|-------|-------|

| TOPS[1:0] Bits |   | Cycles | Counter Value                      | 100%  | 75%   | 50%   | 25%   |

| 0              | 0 | 1024   | 03FFh                              | 03FFh | 02FFh | 01FFh | 00FFh |

| 0              | 1 | 4096   | 0FFFh                              | 0FFFh | 0BFFh | 07FFh | 03FFh |

| 1              | 0 | 8192   | 1FFFh                              | 1FFFh | 17FFh | 0FFFh | 07FFh |

| 1              | 1 | 16384  | 3FFFh                              | 3FFFh | 2FFFh | 1FFFh | 0FFFh |

Figure 30.2 RPSS[1:0] and RPES[1:0] Bit Settings and the Refresh-Permitted Period

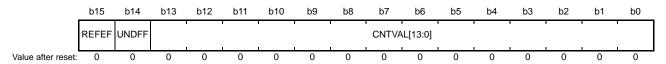

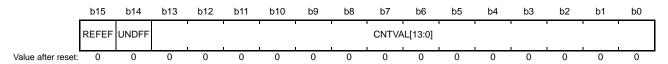

## 30.2.3 WDT Status Register (WDTSR)

Address(es): 0008 8024h

| Bit       | Symbol       | Bit Name           | Description                                            | R/W         |

|-----------|--------------|--------------------|--------------------------------------------------------|-------------|

| b13 to b0 | CNTVAL[13:0] | Down-Counter Value | Value counted by the down-counter                      | R           |

| b14       | UNDFF        | Underflow Flag     | 0: No underflow occurred 1: Underflow occurred         | R(/W)<br>*1 |

| b15       | REFEF        | Refresh Error Flag | 0: No refresh error occurred 1: Refresh error occurred | R(/W)<br>*1 |

Note 1. Only 0 can be written to clear the flag.

#### CNTVAL[13:0] Bits (Down-Counter Value)

Read these bits to confirm the value of the down-counter, but note that the read value may differ from the actual count by a value of one count.

## **UNDFF Flag (Underflow Flag)**

Read this flag to confirm whether or not an underflow has occurred in the down-counter.

The value 1 indicates that the down-counter has underflowed. The value 0 indicates that the down-counter has not underflowed

Write 0 to the UNDFF flag to set the value to 0. Writing 1 has no effect.

#### **REFEF Flag (Refresh Error Flag)**

Read this flag to confirm whether or not a refresh error (performing a refresh operation during a refresh-prohibited period) has occurred.

The value 1 indicates that a refresh error has occurred. The value 0 indicates that no refresh error has occurred. Write 0 to the REFEF flag to set the value to 0. Writing 1 has no effect.

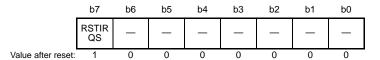

## 30.2.4 WDT Reset Control Register (WDTRCR)

Address(es): 0008 8026h

| Bit      | Symbol  | Bit Name                          | Description                                                                  | R/W |

|----------|---------|-----------------------------------|------------------------------------------------------------------------------|-----|

| b6 to b0 | _       | Reserved                          | These bits are read as 0 and cannot be modified.                             | R   |

| b7       | RSTIRQS | Reset Interrupt Request Selection | Non-maskable interrupt request output is enabled     Reset output is enabled | R/W |

There are some restrictions on writing to the WDTRCR register. For details, refer to section 30.3.2, Control over Writing to the WDTCR and WDTRCR Registers.

In auto-start mode, the WDTRCR register settings are disabled, and the settings in option function select register 0 (OFS0) are enabled. The bit setting made to the WDTCR register can also be made in the OFS0 register. For details, refer to section 30.3.7, Correspondence between Option Function Select Register 0 (OFS0) and WDT Registers.

## 30.2.5 Option Function Select Register 0 (OFS0)

For details on the OFS0 register, refer to section 30.3.7, Correspondence between Option Function Select Register 0 (OFS0) and WDT Registers.

## 30.3 Operation

#### 30.3.1 Count Operation in Each Start Mode

The WDT has two start modes: auto-start mode, in which counting automatically starts after a reset is released, and register start mode, in which counting is started by refresh operation (writing to the register).

In auto-start mode, counting automatically starts after a reset is released in accordance with the settings in option function select register 0 (OFS0) in the ROM.

In register start mode, counting is started by refresh operation (writing to the register) after the respective registers are set after a reset is released.

Select auto-start mode or register start mode by setting the OFS0.WDTSTRT bit.

When the auto-start mode is selected, the settings in the WDTCR and WDTRCR registers are disabled, and the settings in the OFS0 register are enabled.

On the other hand, when the register start mode is selected, the setting of the OFS0 register is disabled, and the settings of the WDTCR and WDTRCR registers are enabled.

## 30.3.1.1 Register Start Mode

When the OFS0.WDTSTRT bit is 1, register start mode is selected, and the WDTCR and WDTRCR registers are enabled.

After a reset is released, set the clock division ratio, window start and end positions, and timeout period in the WDTCR register, and the reset output or interrupt request output in the WDTRCR register. Then, refresh the down-counter to start counting down from the value set by the WDTCR.TOPS[1:0] bits.

Thereafter, as long as the counter is refreshed in the refresh-permitted period, the value in the counter is re-set each time the counter is refreshed and counting down continues. The WDT does not output the reset signal as long as this continues. However, if the down-counter underflows because the down-counter cannot be refreshed due to a program runaway, or if a refresh error occurs because the counter was refreshed outside the refresh-permitted period, the WDT outputs a reset signal or a non-maskable interrupt request (WUNI). Reset output or interrupt request output can be selected by setting the WDTRCR.RSTIRQS bit.

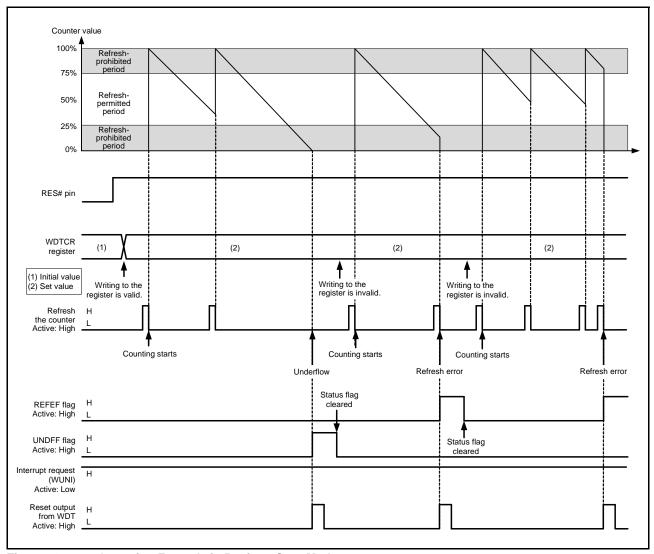

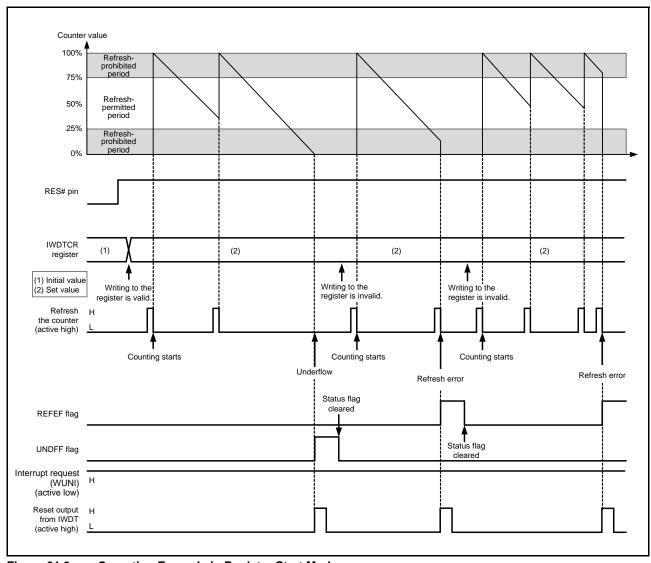

Figure 30.3 shows an example of operation under the following conditions.

- Register start mode (OFS0.WDTSTRT = 1)

- Reset output is enabled (WDTRCR.RSTIRQS = 1)

- The window start position is 75% (WDTCR.RPSS[1:0] = 10b)

- The window end position is 25% (WDTCR.RPES[1:0] = 10b)

Figure 30.3 Operation Example in Register Start Mode

#### 30.3.1.2 Auto-Start Mode

When the WDTSTRT bit in option function select register 0 (OFS0) is 0, auto-start mode is selected, the WDTCR and WDTRCR registers are disabled, and the settings in the OFS0 register are enabled.

Within the reset state, the setting values (clock division ratio, window start and end positions, timeout period, and reset output or interrupt request) of the OFS0 register are set in the WDT registers.

When the reset is released, the down-counter automatically starts counting down from the value set by the OFS0.WDTTOPS[1:0] bits.

After that, as long as the counter is refreshed in the refresh-permitted period, the value in the counter is re-set each time the counter is refreshed and counting down continues. The WDT does not output the reset signal as long as this continues.

However, if the down-counter underflows because refreshing of the down-counter is not possible due to the program having entered crashed execution or if a refresh error occurs due to refreshing outside the refresh-permitted period, the WDT outputs the reset signal or non-maskable interrupt request (WUNI).

After the reset signal or non-maskable interrupt request is output of for one cycle of counting, the value of the timeout period is set in the down-counter counting is restarted.

Reset output or interrupt request output can be selected by setting the OFS0.WDTRSTIRQS bit.

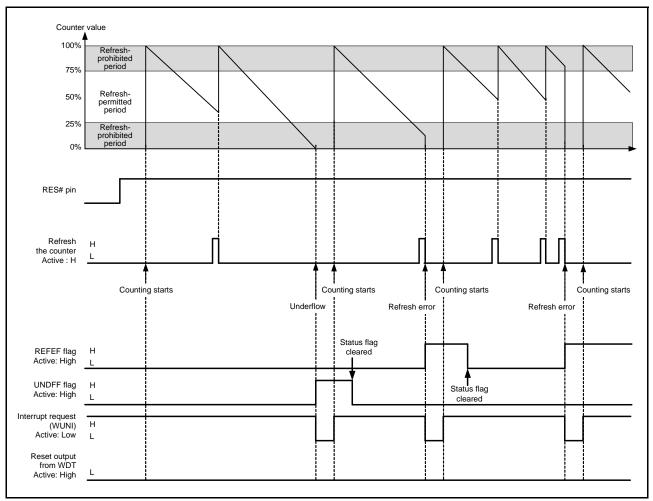

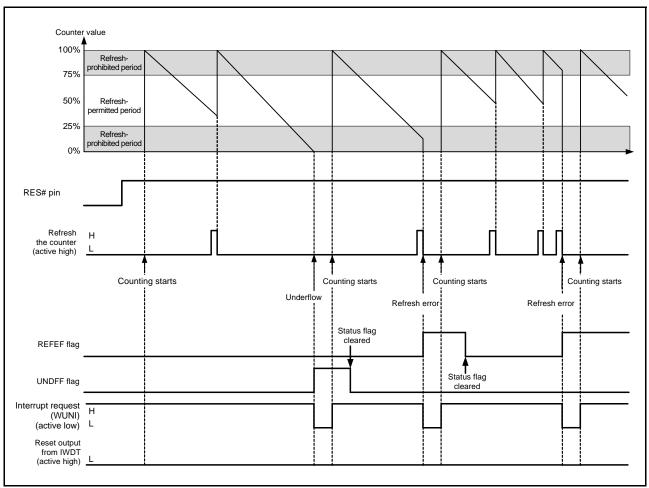

Figure 30.4 shows an example of operation (non-maskable interrupt) under the following conditions.

- Auto start mode (OFS0.WDTSTRT = 0)

- Non-maskable interrupt request output is enabled (OFS0.WDTRSTIRQS = 0)

- The window start position is 75% (OFS0.WDTRPSS[1:0] = 10b)

- The window end position is 25% (OFS0.WDTRPES[1:0] = 10b)

Figure 30.4 Operation Example in Auto-Start Mode

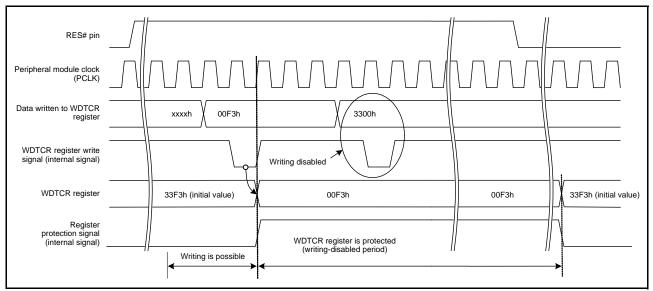

# 30.3.2 Control over Writing to the WDTCR and WDTRCR Registers

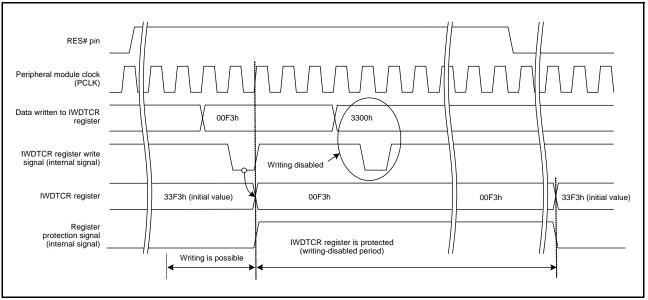

Writing to the WDTCR or WDTRCR register is only possible once between the release from the reset state and the first refresh operation.

After a refresh operation (counting starts) or by writing to the WDTCR or WDTRCR register, the protection signal in the WDT becomes 1 to protect the WDTCR and WDTRCR registers against subsequent attempts at writing.

This protection is released by the reset source of the WDT. With other reset sources, the protection is not released.

Figure 30.5 shows control waveforms produced in response to writing to the WDTCR register.

Figure 30.5 Control Waveforms Produced in Response to Writing to the WDTCR Register

# 30.3.3 Refresh Operation

The down-counter is refreshed by writing the values 00h and then FFh to the WDTRR register. If a value other than FFh is written after 00h, the down-counter is not refreshed. After such invalid writing, correct refreshing is performed by again writing to 00h and then FFh to the WDTRR register.

Even if a register other than the WDTRR register is accessed or the WDTRR register is read between writing 00h and writing FFh to the WDTRR register, correct refreshing will be done.

Writing to refresh the counter must be performed within the refresh-permitted period. Whether writing is done within the refresh-permitted period is determined when writing FFh. For this reason, correct refreshing will be done even if 00h is written outside the refresh-permitted period.

[Sample sequences of writing that are valid for refreshing the counter]

- $00h \rightarrow FFh$

- $00h (n-1-th time) \rightarrow 00h (nth time) \rightarrow FFh$

- $00h \rightarrow access$  to another register or read from the WDTRR register  $\rightarrow$  FFh

[Sample sequences of writing that are not valid for refreshing the counter]

- 23h (a value other than 00h)  $\rightarrow$  FFh

- $00h \rightarrow 54h$  (a value other than FFh)

- $00h \rightarrow AAh (00h \text{ and a value other than } FFh) \rightarrow FFh$

After FFh is written to the WDTRR register, refreshing the down-counter requires up to four cycles of the signal for counting. Therefore, writing FFh to the WDTRR register should be completed four-count cycles before the down-counter underflows.

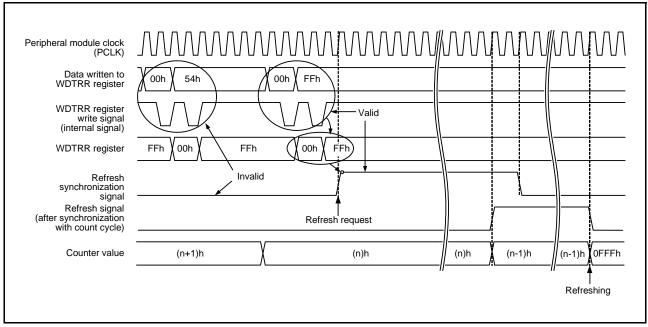

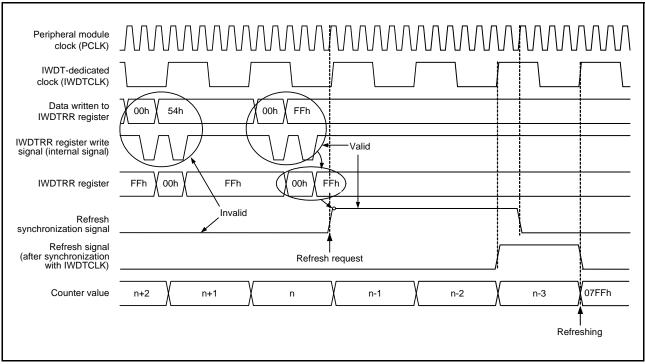

Figure 30.6 shows the WDT refresh-operation waveforms when the clock division ratio = PCLK/64.

Figure 30.6 WDT Refresh Operation Waveforms (WDTCR.CKS[3:0] = 0100b, WDTCR.TOPS[1:0] = 01b)

# 30.3.4 Reset Output

When the WDTRCR.RSTIRQS bit is set to 1 in register start mode or when the WDTRSTIRQS bit in option function select register 0 (OFS0) is set to 1 in auto-start mode, a reset signal is output for one-count cycle when an underflow in the down-counter or a refresh error occurs.

In register start mode, the down-counter is initialized (all bits set to 0) and stopped in that state after output of the reset signal. After the reset is released and the program is restarted, the counter is set up again and counting down is started by refreshing.

In auto-start mode, counting down automatically starts after the reset is released.

# 30.3.5 Interrupt Source

When the WDTRCR.RSTIRQS bit is set to 0 in register start mode or when the OFS0.WDTRSTIRQS bit is set to 0 in auto-start mode, an interrupt (WUNI) signal is generated when an underflow in the counter or a refresh error occurs. This interrupt can be used as a non-maskable interrupt. For details, refer to section 15, Interrupt Controller (ICUb).

Table 30.4 WDT Interrupt Source

| Name | Interrupt Source       | DTC Activation | DMAC Activation |

|------|------------------------|----------------|-----------------|

| WUNI | Down-counter underflow | Not possible   | Not possible    |

|      | Refresh error          |                |                 |

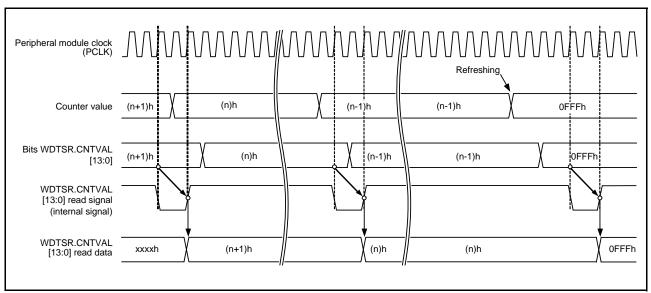

# 30.3.6 Reading the Down-Counter Value

The WDT stores the counter value in the WDTSR.CNTVAL[13:0] bits. Thus, the counter value can be checked through the WDTSR.CNTVAL[13:0] bits.

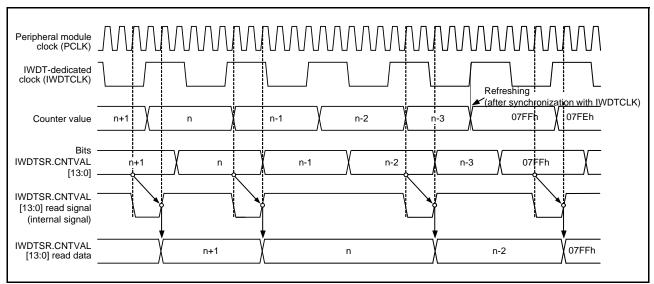

Figure 30.7 shows the processing for reading the WDT down-counter value when the clock division ratio = PCLK/64.

Figure 30.7 Processing for Reading WDT Down-Counter Value (WDTCR.CKS[3:0] = 0100b, WDTCR.TOPS[1:0] = 01b)

# 30.3.7 Correspondence between Option Function Select Register 0 (OFS0) and WDT Registers

Table 30.5 lists the correspondence between option function select register 0 (OFS0) used in auto-start mode and the registers used in register start mode.

Do not change the OFS0 register setting during WDT operation.

For details on the OFS0 register, refer to section 7.2.1, Option Function Select Register 0 (OFS0).

Table 30.5 Correspondence between Option Function Select Register 0 (OFS0) and WDT Registers

| Target of Control                        | Function                                           | OFS0 Register<br>(Enabled in Auto-Start Mode)<br>OFS0.WDTSTRT = 0 | WDT Registers<br>(Enabled in Register Start Mode)<br>OFS0.WDTSTRT = 1 |

|------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|

| Down-counter                             | Timeout period selection                           | OFS0.WDTTOPS[1:0]                                                 | WDTCR.TOPS[1:0]                                                       |

|                                          | Clock division ratio selection                     | OFS0.WDTCKS[3:0]                                                  | WDTCR.CKS[3:0]                                                        |

|                                          | Window start position selection                    | OFS0.WDTRPSS[1:0]                                                 | WDTCR.RPSS[1:0]                                                       |

|                                          | Window end position selection                      | OFS0.WDTRPES[1:0]                                                 | WDTCR.RPES[1:0]                                                       |

| Reset output or interrupt request output | Reset output or interrupt request output selection | OFS0.WDTRSTIRQS                                                   | WDTRCR.RSTIRQS                                                        |

# 31. Independent Watchdog Timer (IWDTa)

In this section, "PCLK" is used to refer to PCLKB.

#### 31.1 Overview

The independent watchdog timer (IWDT) can be used to detect programs being out of control.

The user can detect when a program runs out of control if an underflow occurs, by creating a program that refreshes the IWDT counter before it underflows.

The functions of the IWDT are different from those of the WDT in the following respects.

- The divided IWDT-dedicated clock (IWDTCLK) is used as the count source (not affected by the PCLK).

- When making a transition to sleep mode, software standby mode, or deep sleep mode, the IWDTCSTPR.SLCSTP bit or the OFS0.IWDTSLCSTP bit can be used to select whether to stop the counter or not.

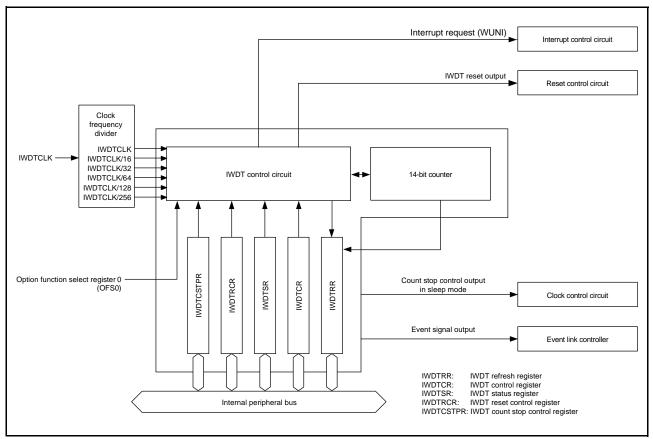

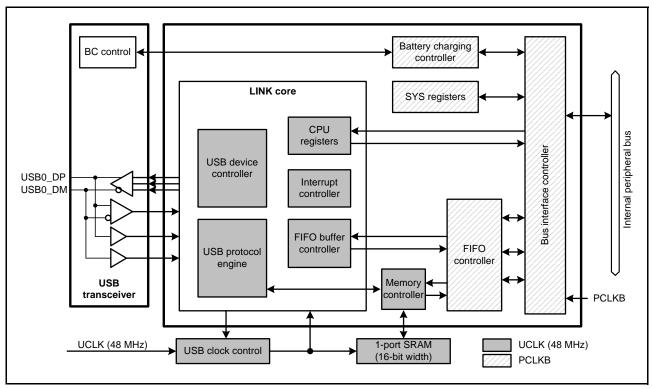

Table 31.1 lists the specifications of the IWDT and Figure 31.1 shows a block diagram of the IWDT.

Table 31.1 IWDT Specifications

| Item                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Count source*1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IWDT-dedicated clock (IWDTCLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |