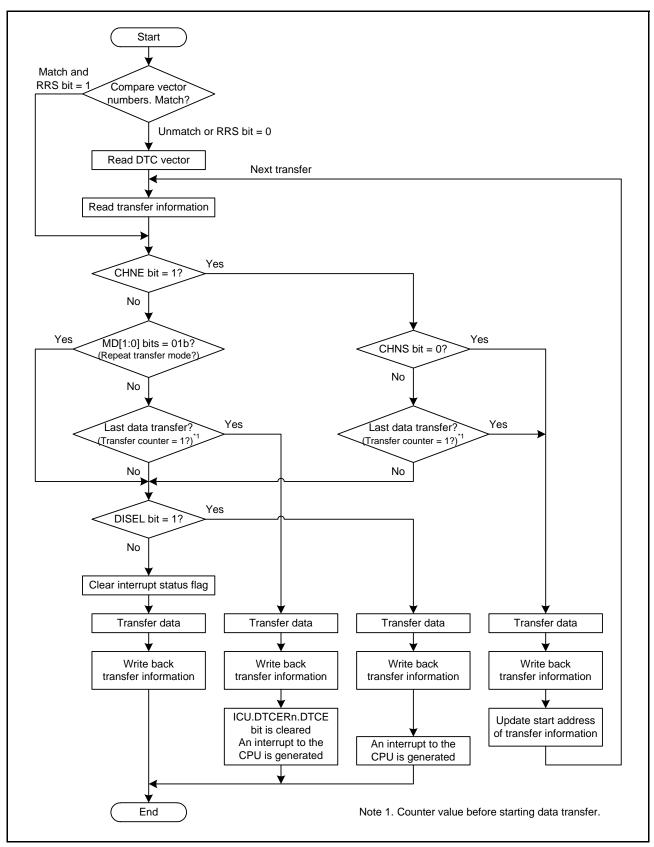

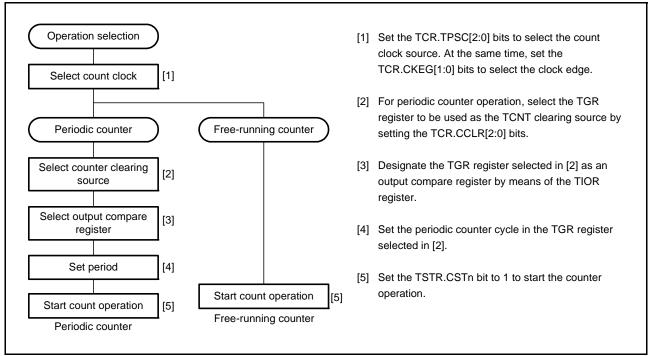

Figure 19.4 Operation Flowchart of the DTC

**Table 19.3 Chain Transfer Conditions**

|             |             | First Tran   | sfer                                 |             | Se          | cond Trai    | nsfer* <sup>3</sup>                  |                                                                          |

|-------------|-------------|--------------|--------------------------------------|-------------|-------------|--------------|--------------------------------------|--------------------------------------------------------------------------|

| CHNE<br>Bit | CHNS<br>Bit | DISEL<br>Bit | Transfer<br>Counter* <sup>1,*2</sup> | CHNE<br>Bit | CHNS<br>Bit | DISEL<br>Bit | Transfer<br>Counter* <sup>1,*2</sup> | Data Transfer                                                            |

| 0           | _           | 0            | Other than $(1 \rightarrow 0)$       | _           | _           | _            | _                                    | Ends after the first transfer                                            |

| 0           | _           | 0            | (1 → 0)                              | _           | _           | _            | _                                    | Ends after the first                                                     |

| 0           | _           | 1            | _                                    | _           | _           | _            | _                                    | transfer with an interrupt request to the CPU                            |

| 1           | 0           | _            | _                                    | 0           | _           | 0            | Other than $(1 \rightarrow 0)$       | Ends after the second transfer                                           |

|             |             |              |                                      | 0           | _           | 0            | (1 → 0)                              | Ends after the second                                                    |

|             |             |              |                                      | 0           | _           | 1            | _                                    | transfer with an interrupt request to the CPU                            |

| 1           | 1           | 0            | Other than (1 → *)                   | _           | _           | _            | _                                    | Ends after the first transfer                                            |

| 1           | 1           | _            | (1 → *)                              | 0           | _           | 0            | Other than $(1 \rightarrow 0)$       | Ends after the second transfer                                           |

|             |             |              |                                      | 0           | _           | 0            | (1 → 0)                              | Ends after the second                                                    |

|             |             |              |                                      | 0           | _           | 1            | _                                    | transfer with an interrupt request to the CPU                            |

| 1           | 1           | 1            | Other than (1 → *)                   | _           | _           | _            | _                                    | Ends after the first<br>transfer with an interrupt<br>request to the CPU |

Note 1. The transfer counters used depend on transfer modes as follows:

Normal transfer mode: CRA register Repeat transfer mode: CRAL register Block transfer mode: CRB register

Note 2. On completion of data transfer, the counters operate as follows:

$1 \rightarrow 0$  in normal and block transfer modes

$1 \rightarrow CRAH$  in repeat transfer mode

$(1 \rightarrow *)$  in the table indicates both of the two operations above.

Note 3. Chain transfer can be selected for the second or subsequent transfers. The condition combination of "second transfer and the CHNE bit is 1" is omitted.

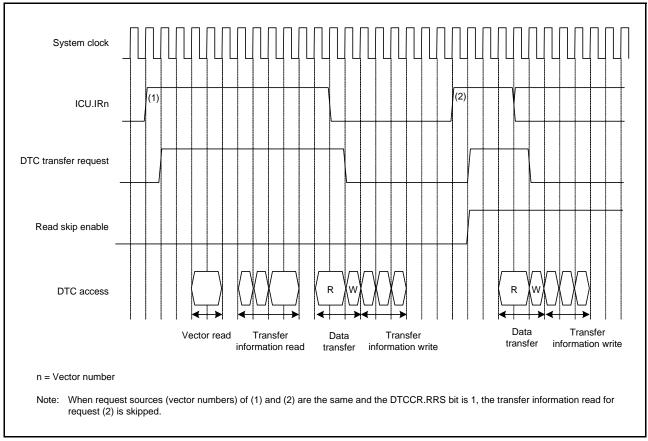

## 19.4.1 Transfer Information Read Skip Function

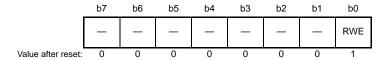

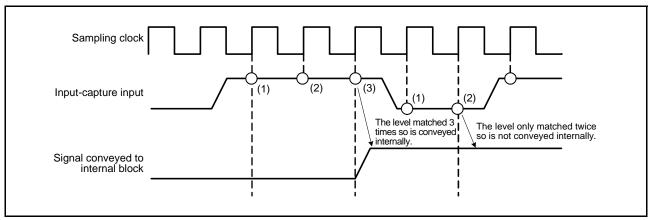

Reading of DTC vector and transfer information can be skipped by the setting of the DTCCR.RRS bit.

When a DTC transfer request is accepted, the current DTC vector number is compared with the DTC vector number in the previous data transfer. When these vector numbers match and the RRS bit is 1, the DTC does not read the DTC vector and transfer information, and transfers data according to the transfer information remained in the DTC.

However, when the previous transfer was chain transfer, the DTC vector and transfer information are read. Furthermore, when the transfer counter (CRA register) became 0 during the previous normal transfer and when the transfer counter (CRB register) became 0 during the previous block transfer, transfer information is read regardless of the value of the RRS bit. Figure 19.13 shows an example of transfer information read skip.

When updating the vector table and transfer information, set the RRS bit to 0, update the vector table and transfer information, and then set the RRS bit to 1. Setting the RRS bit to 0 discards the vector numbers retained in the DTC. The updated DTC vector table and transfer information are read in the next data transfer.

# 19.4.2 Transfer Information Write-Back Skip Function

When the MRA.SM[1:0] bits or the MRB.DM[1:0] bits are set to "address is fixed" (00b or 01b), a part of transfer information is not written back. This function is performed independently of the setting of short-address mode or full-address mode.

Table 19.4 lists transfer information write-back skip conditions and applicable registers. The CRA and CRB registers are written back independently of the setting of short-address mode or full-address mode.

Furthermore, in full-address mode, write-back of registers MRA and MRB is skipped.

Table 19.4 Transfer Information Write-Back Skip Conditions and Applicable Registers

| MRA.SM | [1:0] Bits | MRB.DM | [1:0] Bits |              |              |

|--------|------------|--------|------------|--------------|--------------|

| b3     | b2         | b3     | b2         | SAR Register | DAR Register |

| 0      | 0          | 0      | 0          | Skip         | Skip         |

| 0      | 0          | 0      | 1          |              |              |

| 0      | 1          | 0      | 0          |              |              |

| 0      | 1          | 0      | 1          |              |              |

| 0      | 0          | 1      | 0          | Skip         | Write-back   |

| 0      | 0          | 1      | 1          | <del></del>  |              |

| 0      | 1          | 1      | 0          | <del></del>  |              |

| 0      | 1          | 1      | 1          | <del></del>  |              |

| 1      | 0          | 0      | 0          | Write-back   | Skip         |

| 1      | 0          | 0      | 1          |              |              |

| 1      | 1          | 0      | 0          |              |              |

| 1      | 1          | 0      | 1          |              |              |

| 1      | 0          | 1      | 0          | Write-back   | Write-back   |

| 1      | 0          | 1      | 1          |              |              |

| 1      | 1          | 1      | 0          |              |              |

| 1      | 1          | 1      | 1          |              |              |

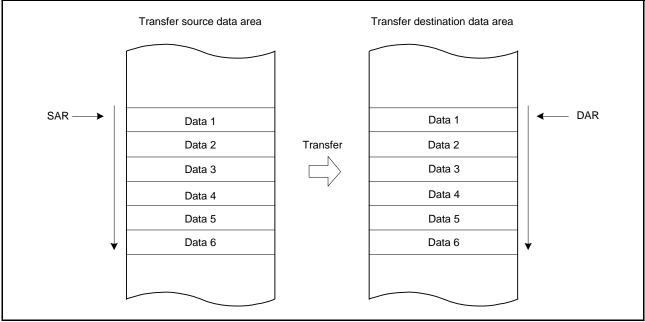

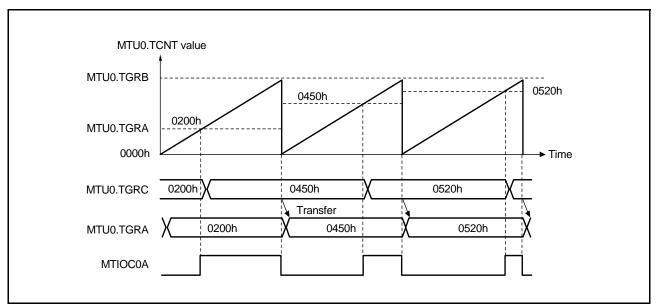

# 19.4.3 Normal Transfer Mode

This mode allows 1-byte, 1-word, or 1-longword data transfer on a single transfer request. The transfer count can be set to 1 to 65536.

Transfer source addresses and transfer destination addresses can be set to increment, decrement, or fixed independently. This mode enables an interrupt request to the CPU to be generated at the end of specified-count transfer.

Table 19.5 lists register functions in normal transfer mode, and Figure 19.5 shows the memory map of normal transfer mode.

Table 19.5 Register Functions in Normal Transfer Mode

| Register | Description                  | Value Written Back by Writing Transfer Information |

|----------|------------------------------|----------------------------------------------------|

| SAR      | Transfer source address      | Increment/decrement/fixed*1                        |

| DAR      | Transfer destination address | Increment/decrement/fixed*1                        |

| CRA      | Transfer counter A           | CRA – 1                                            |

| CRB      | Transfer counter B           | Not updated                                        |

Note 1. Write-back operation is skipped when address is fixed.

Figure 19.5 Memory Map of Normal Transfer Mode

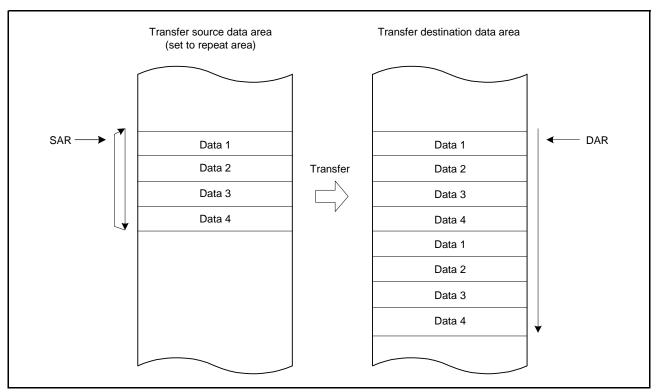

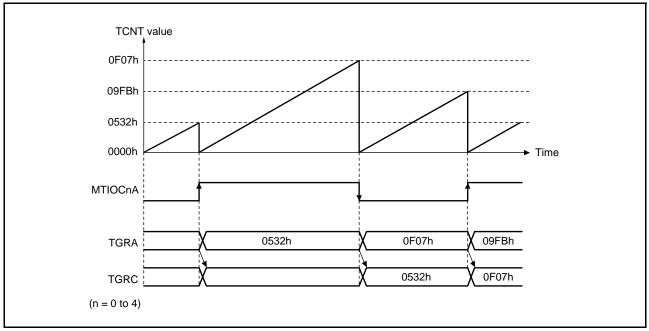

## 19.4.4 Repeat Transfer Mode

This mode allows 1-byte, 1-word, or 1-longword data transfer on a single transfer request.

Specify either transfer source or transfer destination for the repeat area by the MRB.DTS bit. The transfer count can be set to 1 to 256. When the specified-count transfer is completed, the initial value of the address register specified in the transfer counter and the repeat area is restored and transfer is repeated. The other address register is incremented or decremented continuously or remains unchanged.

When the transfer counter CRAL is decreased to 00h in repeat transfer mode, the CRAL value is updated to the value set in the CRAH register. Thus the transfer counter does not become 00h, which disables an interrupt request to be generated to the CPU when the MRB.DISEL bit is set to 0 (an interrupt request to the CPU is generated on completion of the specified number of data transfers).

Table 19.6 lists the register functions in repeat transfer mode, and Figure 19.6 shows the memory map of repeat transfer mode.

Table 19.6 Register Functions in Repeat Transfer Mode

|          | _                                         | Value Written Back by Writing Transfer Information |                             |                             |  |  |  |

|----------|-------------------------------------------|----------------------------------------------------|-----------------------------|-----------------------------|--|--|--|

|          |                                           |                                                    | When CRAL = 1               |                             |  |  |  |

| Register | Description                               | When CRAL ≠ 1                                      | When the MRB.DTS Bit is 0   | When the MRB.DTS Bit is 1   |  |  |  |

| SAR      | Transfer source address                   | Increment/decrement/fixed*1                        | Increment/decrement/fixed*1 | SAR register initial value  |  |  |  |

| DAR      | Transfer destination address              | Increment/decrement/fixed*1                        | DAR register initial value  | Increment/decrement/fixed*1 |  |  |  |

| CRAH     | Retains initial value of transfer counter | CRAH                                               | CRAH                        |                             |  |  |  |

| CRAL     | Transfer counter A                        | CRAL – 1                                           | CRAH                        |                             |  |  |  |

| CRB      | Transfer counter B                        | Not updated                                        | Not updated                 |                             |  |  |  |

Note 1. Write-back operation is skipped when address is fixed.

Figure 19.6 Memory Map of Repeat Transfer Mode (Transfer Source: Repeat Area)

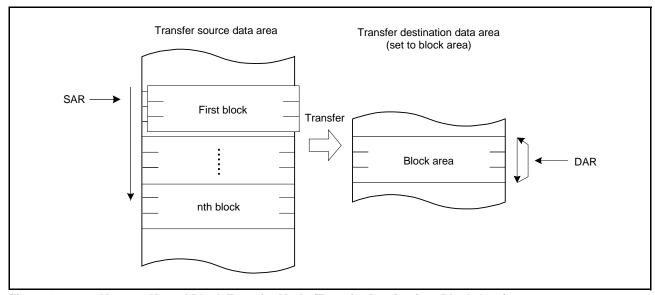

## 19.4.5 Block Transfer Mode

This mode allows single-block data transfer on a single transfer request.

Specify either transfer source or transfer destination for the block area by the MRB.DTS bit. The block size can be set to 1 to 256 bytes, 1 to 256 words, or 1 to 256 longwords.

When transfer of the specified one block is completed, the initial values of the block size counter CRAL and the address register (the SAR register when the MRB.DTS bit is 1 or the DAR register when the DTS bit is 0) specified in the block area are restored. The other address register is incremented or decremented continuously or remains unchanged.

The transfer count (block count) can be set to 1 to 65536. This mode enables an interrupt request to the CPU to be generated at the end of specified-count block transfer.

Table 19.7 lists register functions in block transfer mode, and Figure 19.7 shows the memory map of block transfer mode.

Table 19.7 Register Functions in Block Transfer Mode

| _        |                                     | Value Written Back by Writing Transfer Information |                            |  |  |  |

|----------|-------------------------------------|----------------------------------------------------|----------------------------|--|--|--|

| Register | Description                         | When MRB.DTS Bit is 0                              | When MRB.DTS Bit is 1      |  |  |  |

| SAR      | Transfer source address             | Increment/decrement/fixed*1                        | SAR register initial value |  |  |  |

| DAR      | Transfer destination address        | DAR register initial value                         | Increment/decrement/fixed* |  |  |  |

| CRAH     | Retains initial value of block size | CRAH                                               |                            |  |  |  |

| CRAL     | Block size counter                  | CRAH                                               |                            |  |  |  |

| CRB      | Block transfer counter              | CRB – 1                                            |                            |  |  |  |

Note 1. Write-back operation is skipped when address is fixed.

Figure 19.7 Memory Map of Block Transfer Mode (Transfer Destination: Block Area)

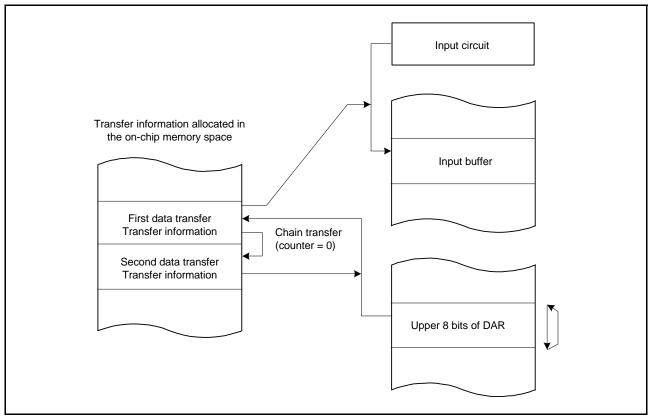

## 19.4.6 Chain Transfer

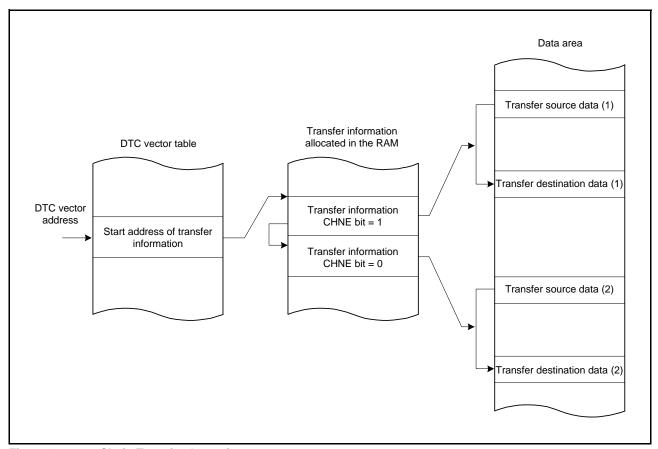

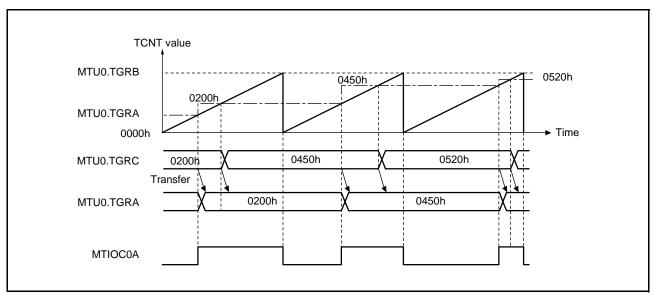

Setting the MRB.CHNE bit to 1 allows chain transfer to be performed continuously on a single transfer request. If the MRB.CHNE bit is 1 and the MRB.CHNS bit is 0, an interrupt request to the CPU is not generated when the specified number of data transfers is completed, or while the MRB.DISEL bit is 1 (an interrupt request to the CPU is generated for every data transfer). Data transfer has no effect on the interrupt status flag, which is the request source. The transfer information (SAR, DAR, CRA, CRB, MRA, and MRB) that define a data transfer can be specified independently of each other. Figure 19.8 shows chain transfer operation.

Figure 19.8 Chain Transfer Operation

If the MRB.CHNE bit is 1 and the CHNS bit is 1, chain transfer is performed only after completion of specified number of data transfers. In repeat transfer mode, chain transfer is performed after completion of specified number of data transfers.

For details on chain transfer conditions, refer to Table 19.3, Chain Transfer Conditions.

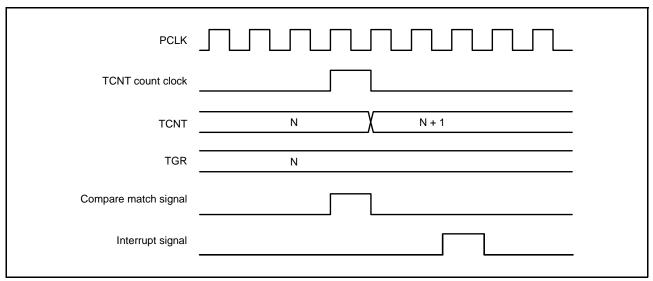

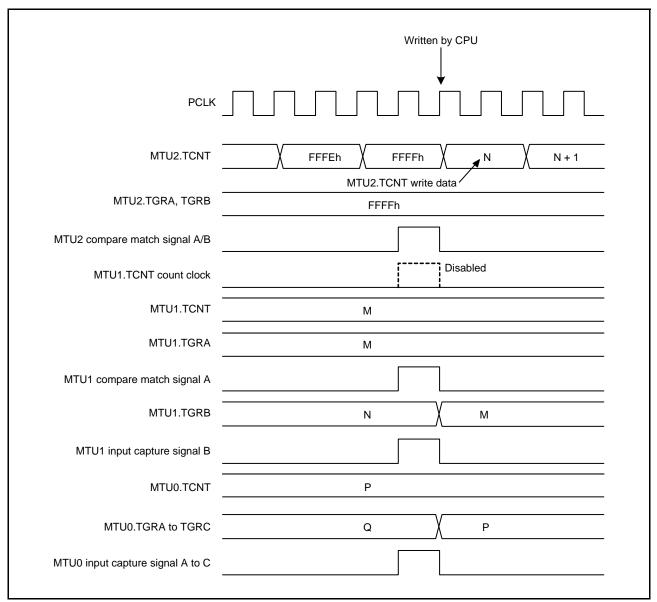

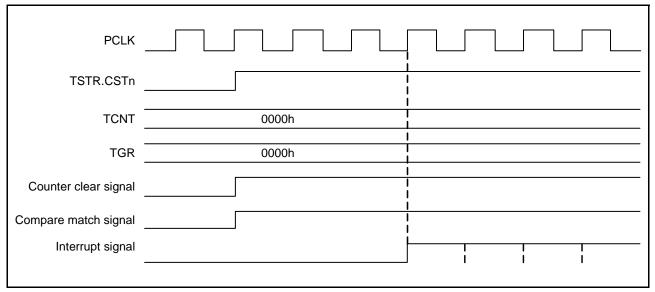

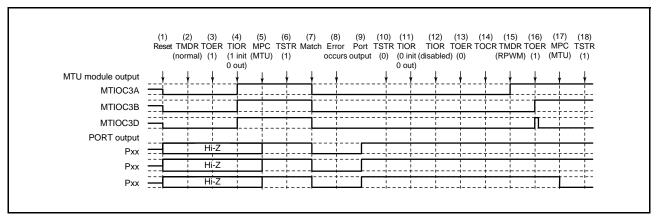

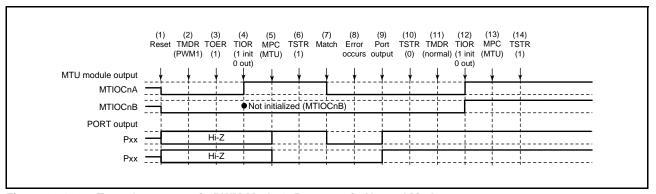

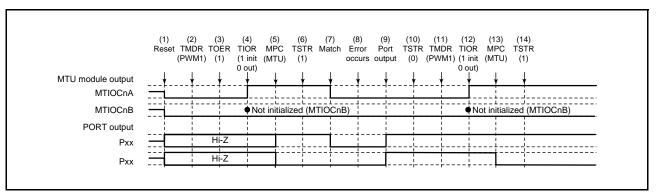

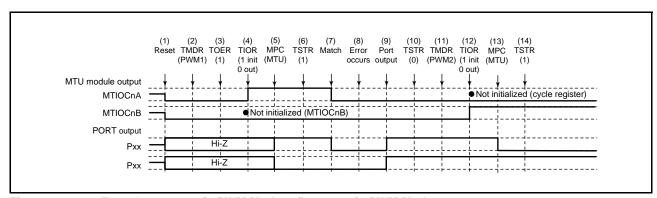

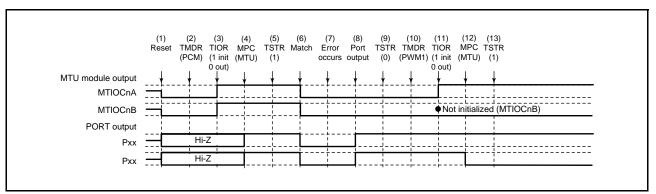

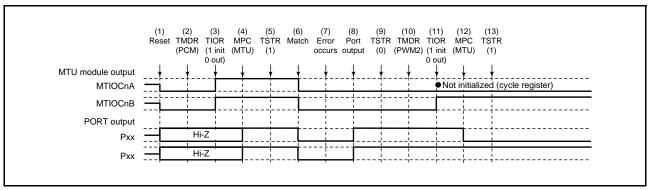

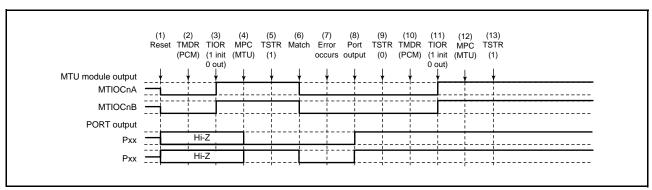

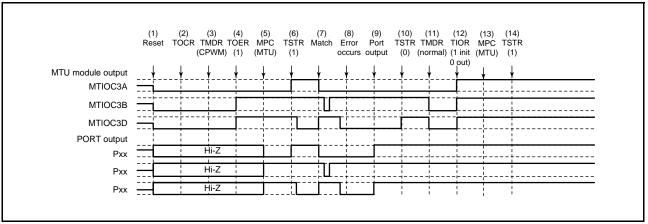

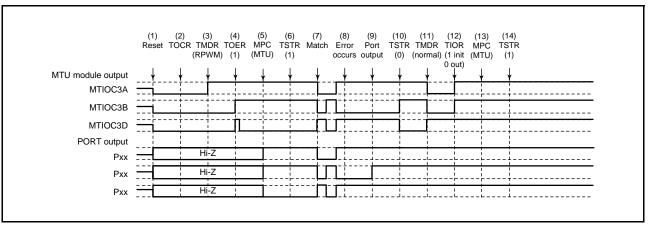

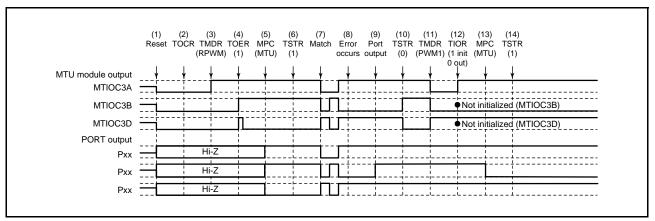

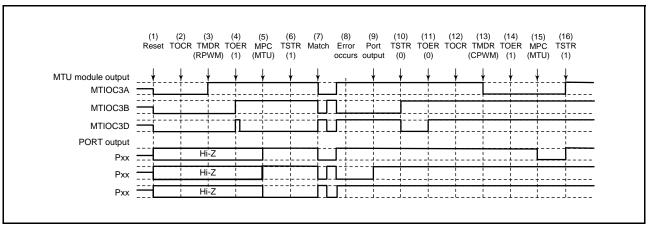

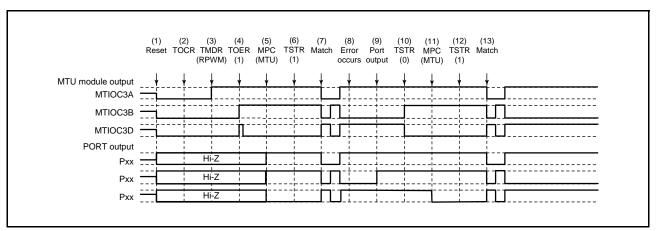

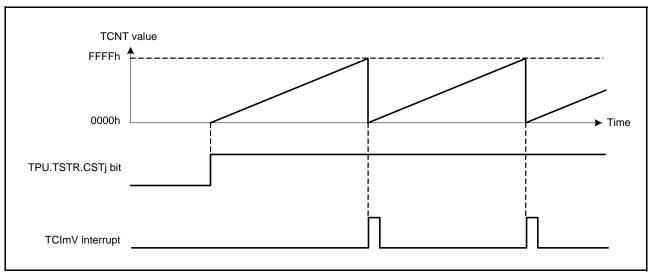

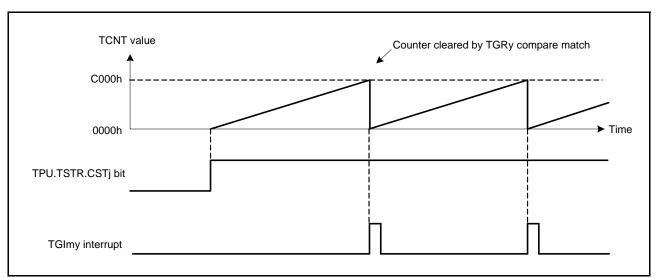

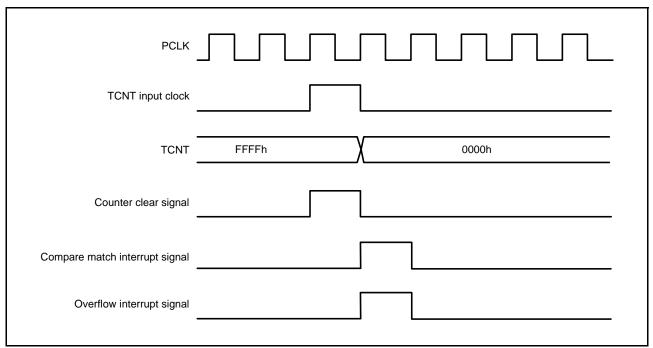

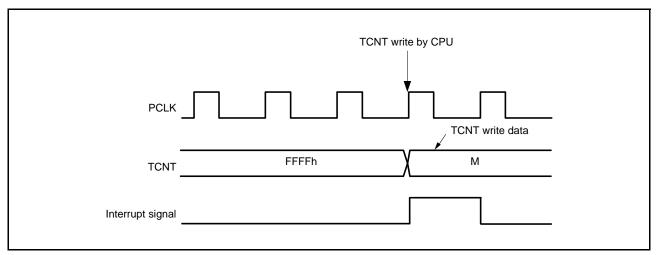

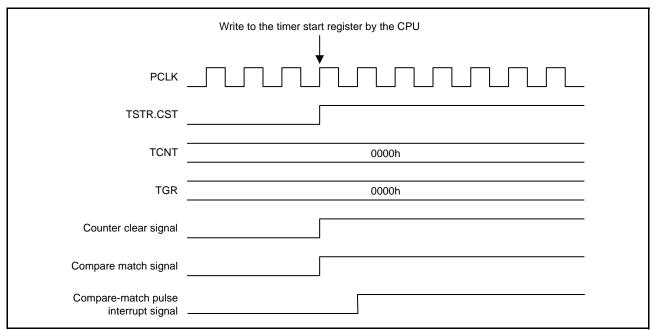

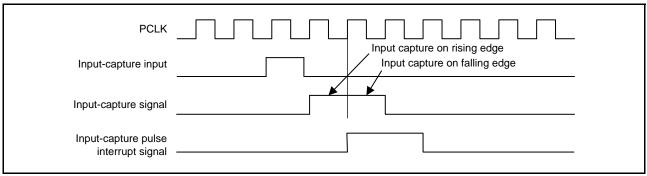

# 19.4.7 Operation Timing

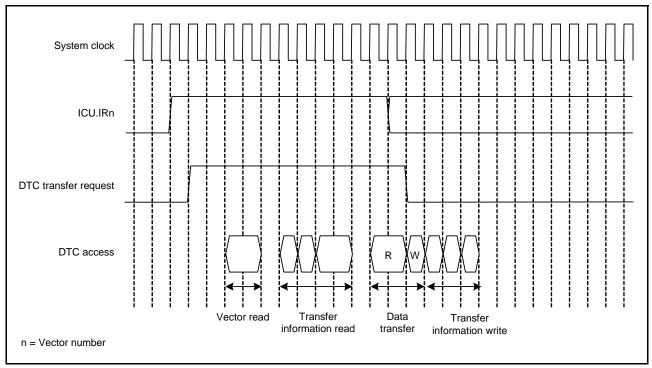

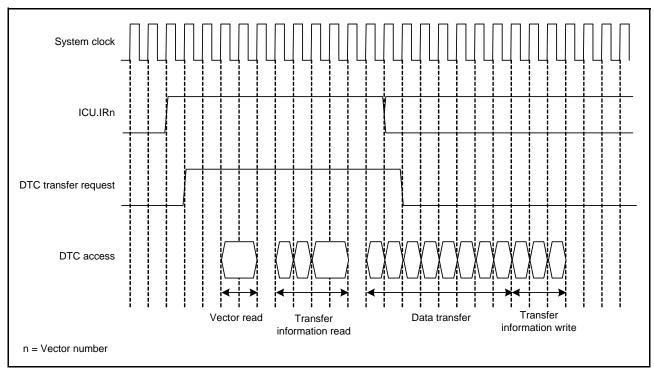

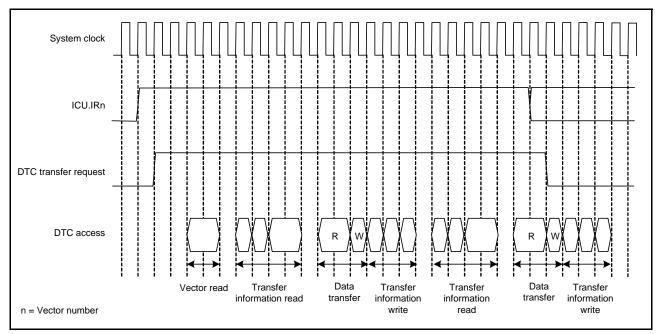

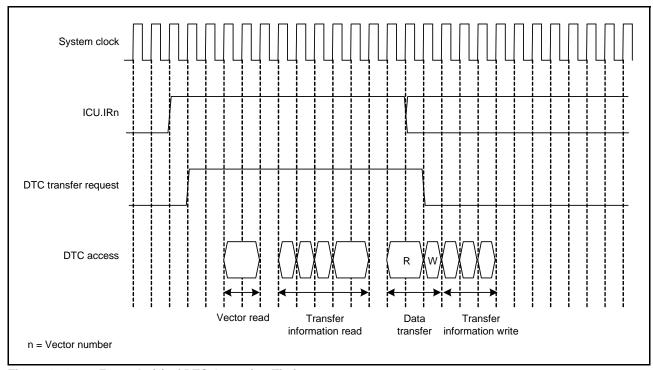

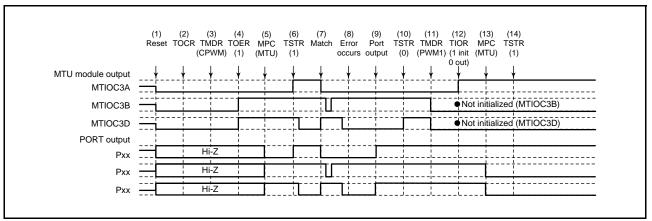

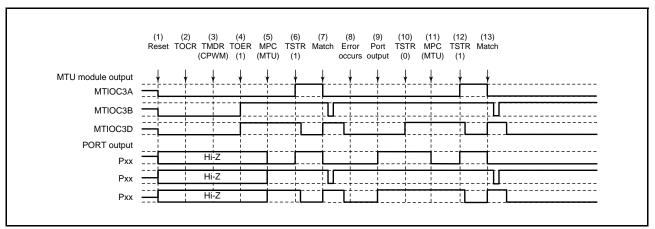

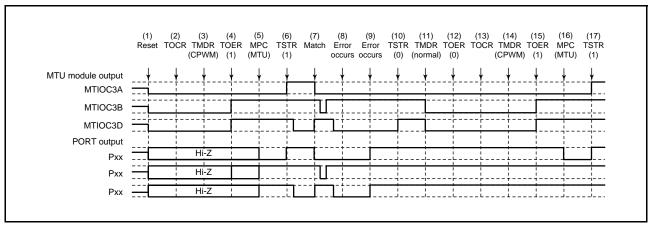

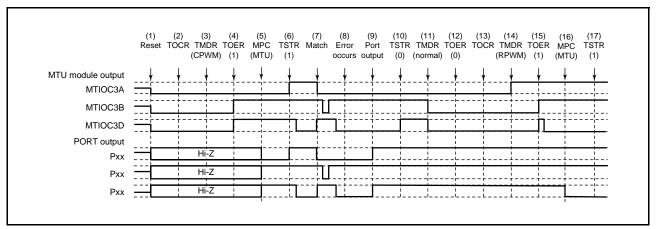

Figure 19.9 to Figure 19.13 show examples of DTC operation timing.

Figure 19.9 Example (1) of DTC Operation Timing

(Short-Address Mode, Normal Transfer Mode, Repeat Transfer Mode)

Figure 19.10 Example (2) of DTC Operation Timing (Short-Address Mode, Block Transfer Mode, Block Size = 4)

Figure 19.11 Example (3) of DTC Operation Timing (Short-Address Mode, Chain Transfer)

Figure 19.12 Example (4) of DTC Operation Timing

(Full-Address Mode, Normal Transfer Mode, Repeat Transfer Mode)

Figure 19.13 Example of Operation When Transfer Information Read Skip is Executed (Vector, Transfer Information, and Transfer Destination Data on the RAM, and Transfer Source Data on the Peripheral Module)

# 19.4.8 Execution Cycles of the DTC

Table 19.8 lists the execution cycles of single data transfer of the DTC.

For the order of the execution states, refer to section 19.4.7, Operation Timing.

Table 19.8 Execution Cycles of the DTC

| Transfer |        |      |               |              |     | Transfer | Informati | on   | Data T | ransfer | Interna | al   |

|----------|--------|------|---------------|--------------|-----|----------|-----------|------|--------|---------|---------|------|

| Mode     | Vector | Read | Transfer Info | rmation Read |     | Write    |           |      | Read   | Write   | Opera   | tion |

| Normal   | Cv + 1 | 0*1  | 4 × Ci + 1*2  | 3 x Ci + 1*3 | 0*1 | 3 × Ci*4 | 2 x Ci*5  | Ci*6 | Cr + 1 | Cw      | 2       | 0*1  |

| Repeat   |        |      |               |              |     |          |           |      | Cr + 1 | Cw      |         |      |

| Block*7  |        |      |               |              |     |          |           |      | P x Cr | P × Cw  |         |      |

- Note 1. When transfer information read is skipped

- Note 2. In full-address mode

- Note 3. In short-address mode

- Note 4. When neither SAR nor DAR is set to address-fixed

- Note 5. When SAR or DAR is set to address-fixed

- Note 6. When SAR and DAR are set to address-fixed

- Note 7. When the block size is 2 or more. If the block size is 1, the cycle number for normal transfer is applied.

- P: Block size (initial settings of CRAH and CRAL)

- Cv: Cycles for access to vector transfer information storage destination

- Ci: Cycles for access to transfer information storage destination address

- Cr: Cycles for access to data read destination

- Cw: Cycles for access to data write destination

(The unit is system clocks (ICLK) for "+ 1" in the Vector Read, Transfer Information Read, and Data Transfer Read columns and "2" in the Internal Operation column.)

(Cv, Ci, Cr, and Cw vary depending on the corresponding access destination. For the number of cycles for respective access destinations, refer to section 49, RAM, section 50, Flash Memory (FLASH), and section 5, I/O Registers.)

## 19.4.9 DTC Bus Mastership Release Timing

The DTC does not release the bus mastership during transfer information read and transfer information write. While transfer information is not read or written, bus arbitration is made according to the priority determined by the bus master arbitrator.

For bus arbitration, refer to section 16, Buses.

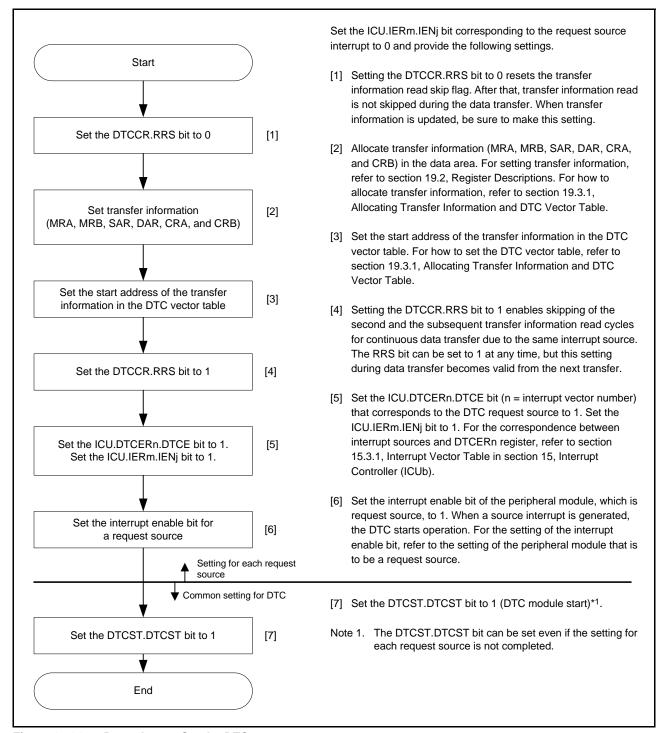

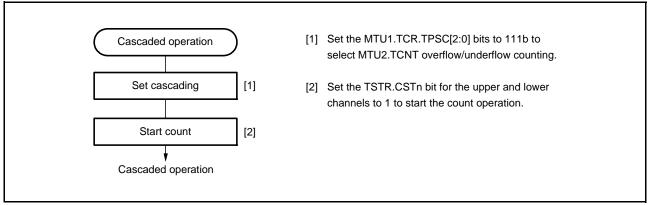

# 19.5 DTC Setting Procedure

Before using the DTC, set the DTC vector base register (DTCVBR).

Figure 19.14 shows the procedure to set the DTC.

Figure 19.14 Procedure to Set the DTC

## 19.6 Examples of DTC Usage

## 19.6.1 Normal Transfer

As an example of DTC usage, its employment in the reception of 128 bytes of data by an SCI is described below.

## (1) Transfer Information Setting

Set the MRA.MD[1:0] bits to 00b (normal transfer mode), the MRA.SZ[1:0] bits to 00b (byte transfer), and the MRA.SM[1:0] bits to 00b (source address is fixed). Set the MRB.CHNE bit to 0 (chain transfer is disabled), the MRB.DISEL bit to 0 (an interrupt request to the CPU is generated on completion of the specified number of data transfers), and the MRB.DM[1:0] bits to 10b (DAR is incremented after data transfer). The MRB.DTS bit can be set to any value. Set the RDR register address of the SCI in the SAR register, the start address of the RAM area for data storage in the DAR register, and 128 (0080h) in the CRA register. The CRB register can be set to any value.

## (2) DTC Vector Table Setting

The start address of the transfer information for the RXI interrupt is set in the vector table for the DTC.

## (3) ICU Setting and DTC Module Activation

Set the corresponding ICU.DTCERn.DTCE bit to 1 and the ICU.IERm.IENj bit to 1. Set the DTCST.DTCST bit to 1.

## (4) SCI Setting

Enable the RXI interrupt by setting the SCR.RIE bit in the SCI to 1. If a reception error occurs during the SCI receive operation, further reception is not performed. Accordingly, make settings so that the CPU can accept receive error interrupts.

## (5) DTC Transfer

Every time the reception of 1 byte by the SCI is completed, an RXI interrupt is generated to start the data transfer. The DTC transfers the received byte from the RDR of the SCI to RAM, after which the DAR register is incremented and the CRA register is decremented.

#### (6) Interrupt Handling

After 128 times of data transfers have been completed and the value in the CRA register becomes 0, an RXI interrupt request is output to the CPU. Complete the process in the handling routine for this interrupt.

#### 19.6.2 Chain Transfer When the Counter is 0

The second data transfer is performed only when the transfer counter is set to 0 in the first data transfer, and the first data transfer information is repeatedly changed in the second data transfer. Repeating this chain transfer enables transfers to be repeated more than 256 times.

The following shows an example of configuring a 128-Kbyte input buffer to addresses 20 0000h to 21 FFFFh (where the input buffer is set so that its lower address starts with 0000h). Figure 19.15 shows a chain transfer when the counter is 0.

- (1) Set normal transfer mode for input data for the first data transfer. Set the following:

Transfer source address: Fixed, the CRA register is 0000h (65,536 times), the MRB.CHNE bit is 1 (chain transfer is enabled), the MRB.CHNS bit is 1 (chain transfer is performed only when the transfer counter becomes 0), and the MRB.DISEL bit is 0 (an interrupt request to the CPU is generated on completion of the specified number of data transfers).

- (2) Prepare the upper 8 bits (in this case, 21h and 20h) of the start address at every 65,536 times of the transfer destination address for the first data transfer in another area (such as ROM).

- (3) For the second data transfer, set repeat transfer mode (source is repeat area) for rewriting the transfer destination address of the first data transfer. The transfer destination is the address where the upper 8 bits of the DAR register in the first transfer information is allocated. In this case, set the MRB.CHNE bit to 0 (chain transfer is disabled) and the MRB.DISEL bit to 0 (an interrupt request to the CPU is generated on completion of the specified number of data transfers). In this case, set the transfer counter to 2.

- (4) When a transfer request is accepted, the first data transfer is executed. When transfer is executed 65,536 times and the transfer counter of the first data transfer becomes 0, the second data transfer is started and the upper 8 bits of the transfer destination address of the first data transfer is set to 21h. At this time, the lower 16 bits of the transfer destination address and the transfer counter of the first data transfer have become 0000h.

- (5) In succession, when another transfer request is accepted, the first data transfer is executed. When transfer is executed 65,536 times and the transfer counter of the first data transfer becomes 0, the second data transfer is started and the upper 8 bits of the transfer destination address of the first data transfer is set to 20h. At this time, the lower 16 bits of the transfer destination address and the transfer counter of the first data transfer have become 0000h.

- (6) Steps (4) and (5) above are repeated infinitely. Because the second data transfer is in repeat transfer mode, no interrupt request to the CPU is generated.

Figure 19.15 Chain Transfer When the Counter is 0

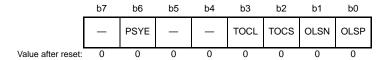

## 19.7 Interrupt Source

When the DTC has finished data transfer of specified count or when data transfer with the MRB.DISEL bit set to 1 (an interrupt request to the CPU is generated each time the data transfer is performed) has been completed, an interrupt to the CPU is generated by the DTC trigger source. Such interrupts to the CPU are controlled according to the PSW.I bit (interrupt enable) of the CPU, the PSW.IPL[3:0] bits (processor interrupt priority level), and the priority level of the interrupt controller.

## 19.8 Event Link

The DTC outputs an event signal on completing data transfer in response to one request.

## 19.9 Low Power Consumption Function

Before making a transition to the module stop state, deep sleep mode, or software standby mode, set the DTCST.DTCST bit to 0 (DTC module stop), and then perform the following.

## (1) Module Stop Function

Writing 1 (transition to the module-stop state is made) to the MSTPCRA.MSTPA28 bit enables the module stop function of the DTC. If data transfer is in progress at the time 1 is written to the MSTPCRA.MSTPA28 bit, the transition to the module stop state proceeds after data transfer has ended. While the MSTPCRA.MSTPA28 bit is 1, accessing the DTC registers is prohibited.

Writing 0 (release from the module-stop state) to the MSTPCRA.MSTPA28 bit releases the DTC from the module stop state.

## (2) Deep Sleep Mode

Make settings according to the procedure under section 11.6.2.1, Entry to Deep Sleep Mode, in section 11, Low Power Consumption.

If any data transfer is in progress at the time the WAIT instruction is executed, the transition to deep sleep mode follows the completion of the data transfer.

The DTC is released from the module stop state by writing 0 to the MSTPCRA.MSTPA28 bit following recovery from deep sleep mode.

## (3) Software Standby Mode

Make settings according to the procedure under section 11.6.3.1, Entry to Software Standby Mode, in section 11, Low Power Consumption.

If any data transfer is in progress at the time the WAIT instruction is executed, the transition to software standby mode follows the completion of the data transfer.

## (4) Notes on Low Power Consumption Function

For the WAIT instruction and the register setting procedure, refer to section 11.7.5, Timing of WAIT Instructions in section 11, Low Power Consumption.

To perform data transfer after returning from a low power consumption mode, set the DTCST.DTCST bit to 1 again. To use a request that is generated in deep sleep mode or software standby mode as an interrupt request to the CPU but not as a DTC transfer request, specify the CPU as the interrupt request destination according to the description in section 15.4.3, Selecting Interrupt Request Destinations in section 15, Interrupt Controller (ICUb), and then execute the WAIT instruction.

## 19.10 Usage Notes

## 19.10.1 Start Address of Transfer Information

Set multiples of 4 for the start addresses of the transfer information to be specified in the DTC vector table. If any value other than a multiple of 4 is specified, access still proceeds with the lower 2 bits of the address regarded as 00b.

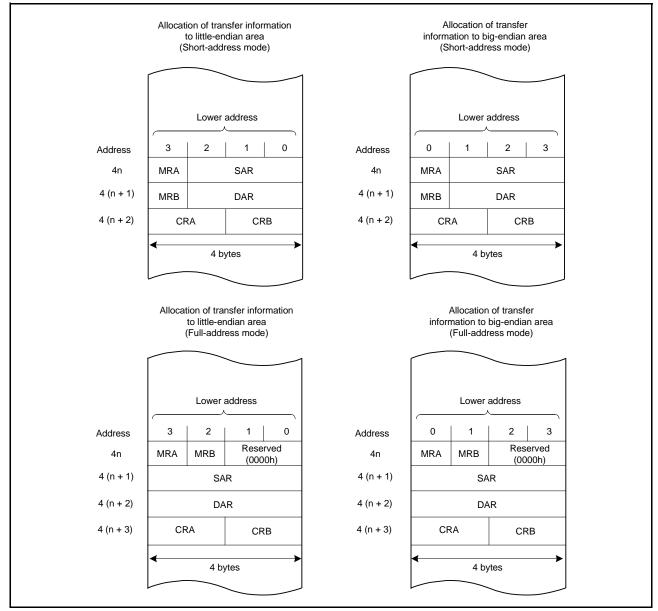

# 19.10.2 Allocating Transfer Information

Allocate transfer information in the memory area according to the endian of the area as shown in Figure 19.16. For example, when writing CRA and CRB settings in 16-bit units in big endian, write the CRA setting to the address plus 8h (Ch) and the CRB setting to the address plus Ah (Eh). In little endian, write the CRB setting to the address plus 8h (Ch) and the CRA setting to the address plus Ah (Eh). When writing CRA and CRB settings in 32-bit units, allocate the CRA setting at the MSB side of the 32 bits and the CRB setting at the LSB side, and write the settings to the address plus 8h (Ch), regardless of endian.

Figure 19.16 Allocation of Transfer Information

# 19.10.3 Setting the DTC Transfer Request Enable Register in the Interrupt Controller (ICU.DTCERn)

The DMA request should not be issued by setting the DMAC trigger select register (ICU.DMRSRm (m = DMAC channel number)) to the same vector number that has been specified by setting the ICU.DTCERn.DTCE bit to 1 (the corresponding interrupt source is selected as the DTC trigger). For details on the ICU.DTCERn and ICU.DMRSRm registers (m = DMAC channel number), refer to section 15, Interrupt Controller (ICUb).

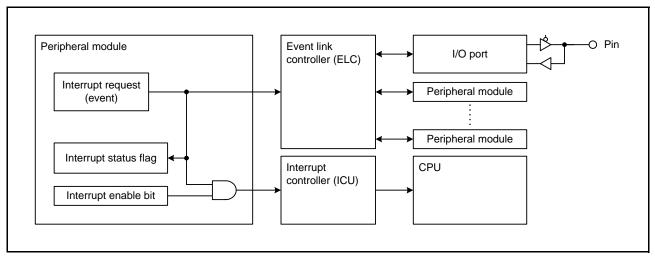

# 20. Event Link Controller (ELC)

## 20.1 Overview

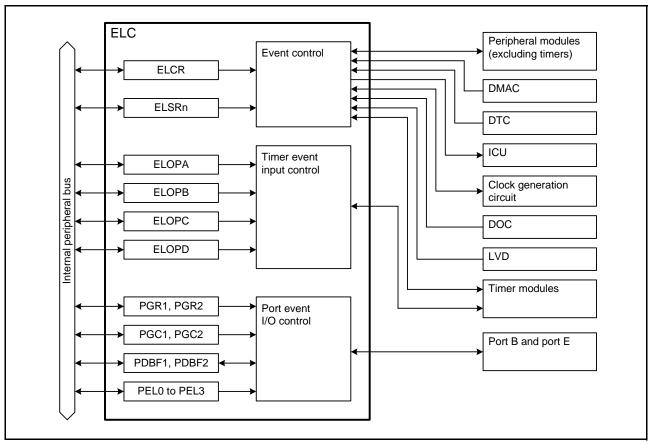

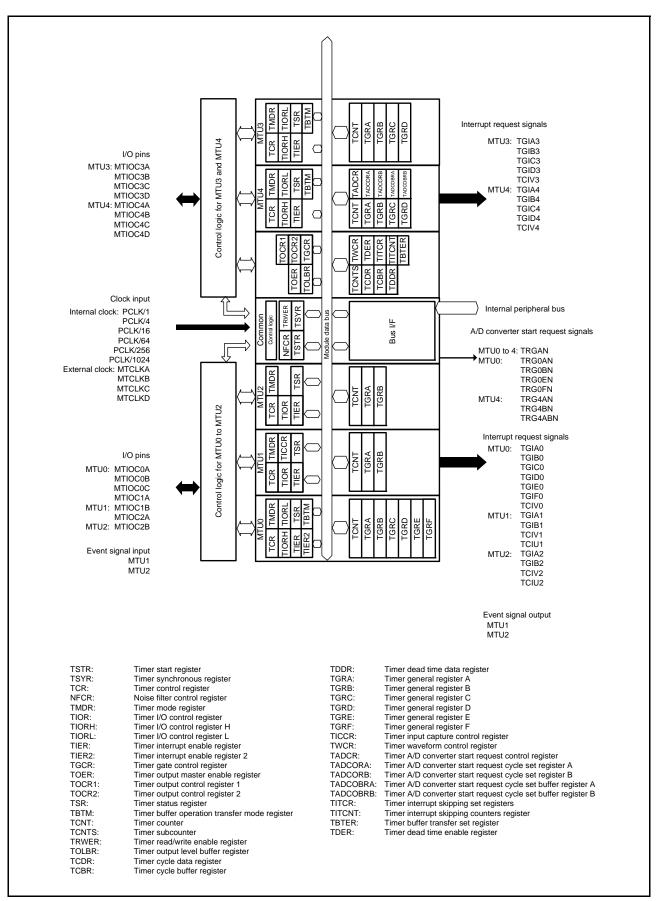

The event link controller (ELC) uses the interrupt requests generated by various peripheral modules as event signals, and interconnects (links) peripheral modules. As a result, peripheral modules can directly perform interlinked operation among them without using software.

Event signals can be output regardless of the settings of the corresponding interrupt request enable bits.

Table 20.1 lists the specifications of the ELC, and Figure 20.1 shows a block diagram of the ELC.

Table 20.1 ELC Specifications

| Item                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Event link function            | <ul> <li>60 types of event signals can be directly interconnected to modules.</li> <li>Operation for timer modules when inputting an event signal can be selected.</li> <li>Event linkage operation is possible for port B and port E.         Single port*1: Event linkage operation can be set in a single specified port.         Port group*1: Event linkage operation can be set by grouping multiple specified ports among total of eight ports.     </li> </ul> |  |  |  |

| Low power consumption function | Module stop state can be set.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

Note 1. When an input signal to a corresponding pin changes, an event is generated in a single port or in a port group specified as the input.

Figure 20.1 ELC Block Diagram (n = 1 to 4, 7, 8, 10, 12, 14 to 16, 18 to 29)

# 20.2 Register Descriptions

# 20.2.1 Event Link Control Register (ELCR)

Address(es): ELC.ELCR 0008 B100h

| Bit      | Symbol | Bit Name              | Description                                            | R/W |

|----------|--------|-----------------------|--------------------------------------------------------|-----|

| b6 to b0 | _      | Reserved              | These bits are read as 1. The write value should be 1. | R/W |

| b7       | ELCON  | All Event Link Enable | ELC function is disabled.     ELC function is enabled. | R/W |

The ELCR register controls operation of the ELC.

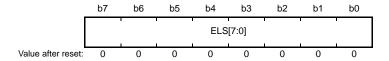

# 20.2.2 Event Link Setting Register n (ELSRn) (n = 1 to 4, 7, 8, 10, 12, 14 to 16, 18 to 29)

Address(es): ELC.ELSR1 0008 B102h, ELC.ELSR2 0008 B103h, ELC.ELSR3 0008 B104h, ELC.ELSR4 0008 B105h, ELC.ELSR7 0008 B108h, ELC.ELSR8 0008 B109h, ELC.ELSR10 0008 B108h, ELC.ELSR12 0008 B100h, ELC.ELSR14 0008 B10Fh, ELC.ELSR15 0008 B110h, ELC.ELSR16 0008 B111h, ELC.ELSR18 0008 B113h, ELC.ELSR19 0008 B114h, ELC.ELSR20 0008 B115h, ELC.ELSR21 0008 B116h, ELC.ELSR22 0008 B117h, ELC.ELSR23 0008 B118h, ELC.ELSR24 0008 B119h, ELC.ELSR25 0008 B114h, ELC.ELSR26 0008 B118h, ELC.ELSR27 0008 B116h, ELC.ELSR27 0008 B116h, ELC.ELSR28 0008 B110h, ELC.ELSR29 0008 B116h

| Bit      | Symbol   | Bit Name          | Description                                                                                                                                                                                                            | R/W |

|----------|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b7 to b0 | ELS[7:0] | Event Link Select | <ul><li>00h: Event signal output to the corresponding peripheral module is disabled.</li><li>08h to 6Ah: Set the number for the event signal to be linked.</li><li>Settings other than above are prohibited.</li></ul> | R/W |

The ELSRn register specifies an event signal to be linked to for each peripheral module. Table 20.2 shows the correspondence between the ELSRn register and the peripheral modules. Table 20.3 shows the correspondence between values set in the ELSRn register and event signals.

Table 20.2 Correspondence between the ELSRn Register and the Peripheral Modules

| ELSR1         MTU1           ELSR2         MTU2           ELSR3         MTU3           ELSR4         MTU4           ELSR7         CMT1           ELSR8         ICU (LPT dedicated interrupt)*1           ELSR8         ICU (LPT dedicated interrupt)*1           ELSR10         TMR0           ELSR12         TMR2           ELSR14         CTSU           ELSR15         S12AD           ELSR16         DA0           ELSR18         ICU (Interrupt 1)*2           ELSR19         ICU (Interrupt 2)*2           ELSR20         Output port group 1           ELSR21         Output port group 2           ELSR22         Input port group 1           ELSR23         Input port group 2           ELSR24         Single port 0*3           ELSR25         Single port 1*3           ELSR26         Single port 2*3 | Peripheral Module                  | Register Name |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------|

| ELSR3         MTU3           ELSR4         MTU4           ELSR7         CMT1           ELSR8         ICU (LPT dedicated interrupt)*1           ELSR10         TMR0           ELSR12         TMR2           ELSR14         CTSU           ELSR15         S12AD           ELSR16         DA0           ELSR18         ICU (Interrupt 1)*2           ELSR19         ICU (Interrupt 2)*2           ELSR20         Output port group 1           ELSR21         Output port group 2           ELSR22         Input port group 2           ELSR23         Input port group 2           ELSR24         Single port 0*3           ELSR25         Single port 1*3           ELSR26         Single port 2*3                                                                                                                   | MTU1                               | ELSR1         |

| ELSR4 MTU4  ELSR7 CMT1  ELSR8 ICU (LPT dedicated interrupt)*1  ELSR10 TMR0  ELSR12 TMR2  ELSR14 CTSU  ELSR15 S12AD  ELSR16 DA0  ELSR18 ICU (Interrupt 1)*2  ELSR19 ICU (Interrupt 2)*2  ELSR20 Output port group 1  ELSR21 Output port group 2  ELSR22 Input port group 2  ELSR23 Input port group 2  ELSR24 Single port 0*3  ELSR25 Single port 1*3  ELSR26 Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                        | MTU2                               | ELSR2         |

| ELSR7  ELSR8  ICU (LPT dedicated interrupt)*1  ELSR10  TMR0  ELSR12  TMR2  ELSR14  CTSU  ELSR15  S12AD  ELSR16  DA0  ELSR18  ICU (Interrupt 1)*2  ELSR19  ICU (Interrupt 2)*2  ELSR20  Output port group 1  ELSR21  ELSR21  Input port group 2  ELSR23  Input port group 2  ELSR23  ELSR24  Single port 0*3  ELSR25  ELSR26  Single port 1*3  ELSR26                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MTU3                               | ELSR3         |

| ELSR8  ICU (LPT dedicated interrupt)*1  ELSR10  TMR0  ELSR12  TMR2  ELSR14  CTSU  ELSR15  S12AD  ELSR16  DA0  ELSR18  ICU (Interrupt 1)*2  ELSR19  ICU (Interrupt 2)*2  ELSR20  Output port group 1  ELSR21  ELSR22  Input port group 2  ELSR23  ELSR23  Input port group 2  ELSR24  Single port 0*3  ELSR25  ELSR26  Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MTU4                               | ELSR4         |

| ELSR10       TMR0         ELSR12       TMR2         ELSR14       CTSU         ELSR15       S12AD         ELSR16       DA0         ELSR18       ICU (Interrupt 1)*2         ELSR19       ICU (Interrupt 2)*2         ELSR20       Output port group 1         ELSR21       Output port group 2         ELSR22       Input port group 1         ELSR23       Input port group 2         ELSR24       Single port 0*3         ELSR25       Single port 1*3         ELSR26       Single port 2*3                                                                                                                                                                                                                                                                                                                        | CMT1                               | ELSR7         |

| ELSR12  ELSR14  CTSU  ELSR15  S12AD  ELSR16  DA0  ELSR18  ICU (Interrupt 1)*2  ELSR19  ICU (Interrupt 2)*2  ELSR20  Output port group 1  ELSR21  Output port group 2  ELSR22  Input port group 2  ELSR23  Input port group 2  ELSR24  Single port 0*3  ELSR25  Single port 1*3  ELSR26  Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ICU (LPT dedicated interrupt)*1    | ELSR8         |

| ELSR14       CTSU         ELSR15       S12AD         ELSR16       DA0         ELSR18       ICU (Interrupt 1)*2         ELSR19       ICU (Interrupt 2)*2         ELSR20       Output port group 1         ELSR21       Output port group 2         ELSR22       Input port group 1         ELSR23       Input port group 2         ELSR24       Single port 0*3         ELSR25       Single port 1*3         ELSR26       Single port 2*3                                                                                                                                                                                                                                                                                                                                                                            | TMR0                               | ELSR10        |

| ELSR15       S12AD         ELSR16       DA0         ELSR18       ICU (Interrupt 1)*2         ELSR19       ICU (Interrupt 2)*2         ELSR20       Output port group 1         ELSR21       Output port group 2         ELSR22       Input port group 1         ELSR23       Input port group 2         ELSR24       Single port 0*3         ELSR25       Single port 1*3         ELSR26       Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                      | TMR2                               | ELSR12        |

| ELSR16  ELSR18  ICU (Interrupt 1)*2  ELSR19  ICU (Interrupt 2)*2  ELSR20  Output port group 1  ELSR21  Output port group 2  ELSR22  Input port group 1  ELSR23  Input port group 2  ELSR24  Single port 0*3  ELSR25  ELSR25  Single port 1*3  ELSR26  Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CTSU                               | ELSR14        |

| ELSR18       ICU (Interrupt 1)*2         ELSR19       ICU (Interrupt 2)*2         ELSR20       Output port group 1         ELSR21       Output port group 2         ELSR22       Input port group 1         ELSR23       Input port group 2         ELSR24       Single port 0*3         ELSR25       Single port 1*3         ELSR26       Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                          | S12AD                              | ELSR15        |

| ELSR19       ICU (Interrupt 2)*2         ELSR20       Output port group 1         ELSR21       Output port group 2         ELSR22       Input port group 1         ELSR23       Input port group 2         ELSR24       Single port 0*3         ELSR25       Single port 1*3         ELSR26       Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DA0                                | ELSR16        |

| ELSR20 Output port group 1  ELSR21 Output port group 2  ELSR22 Input port group 1  ELSR23 Input port group 2  ELSR24 Single port 0*3  ELSR25 Single port 1*3  ELSR26 Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ICU (Interrupt 1)*2                | ELSR18        |

| ELSR21 Output port group 2  ELSR22 Input port group 1  ELSR23 Input port group 2  ELSR24 Single port 0*3  ELSR25 Single port 1*3  ELSR26 Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ICU (Interrupt 2)*2                | ELSR19        |

| ELSR22 Input port group 1  ELSR23 Input port group 2  ELSR24 Single port 0*3  ELSR25 Single port 1*3  ELSR26 Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Output port group 1                | ELSR20        |

| ELSR23 Input port group 2  ELSR24 Single port 0*3  ELSR25 Single port 1*3  ELSR26 Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Output port group 2                | ELSR21        |

| ELSR24 Single port 0*3  ELSR25 Single port 1*3  ELSR26 Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Input port group 1                 | ELSR22        |

| ELSR25 Single port 1*3 ELSR26 Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Input port group 2                 | ELSR23        |

| ELSR26 Single port 2*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Single port 0*3                    | ELSR24        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <br>Single port 1*3                | ELSR25        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <br>Single port 2*3                | ELSR26        |

| ELSR27 Single port 3*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <br>Single port 3*3                | ELSR27        |

| ELSR28 Clock source switching to LOCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <br>Clock source switching to LOCO | ELSR28        |

| ELSR29 POE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <br>POE                            | ELSR29        |

Note 1. Specify an event number to 32h (LPT compare match).

Note 2. Specify an event number from among 63h to 6Ah. Do not set other values.

Note 3. Do not set the DOC data operation condition met signal (6Ah) in the ELSR24, ELSR25, ELSR26, and ELSR27 registers.

Table 20.3 Correspondence between Values Set in ELSRn.ELS[7:0] Bits and Event Signals (1/2)

| ELS[7:0] Bit Value | Peripheral Modules               | Event Signal Set in ELSRn                                                                  |

|--------------------|----------------------------------|--------------------------------------------------------------------------------------------|

| 08h                | Multifunction timer pulse unit 2 | MTU1 compare match 1A                                                                      |

| 09h                |                                  | MTU1 compare match 1B                                                                      |

| 0Ah                |                                  | MTU1 overflow                                                                              |

| 0Bh                | ]                                | MTU1 underflow                                                                             |

| 0Ch                | 1                                | MTU2 compare match 2A                                                                      |

| 0Dh                | 1                                | MTU2 compare match 2B                                                                      |

| 0Eh                |                                  | MTU2 overflow                                                                              |

| 0Fh                |                                  | MTU2 underflow                                                                             |

| 10h                | 1                                | MTU3 compare match 3A                                                                      |

| 11h                |                                  | MTU3 compare match 3B                                                                      |

| 12h                | 1                                | MTU3 compare match 3C                                                                      |

| 13h                | 1                                | MTU3 compare match 3D                                                                      |

| 14h                | 1                                | MTU3 overflow                                                                              |

| 15h                | 1                                | MTU4 compare match 4A                                                                      |

| 16h                | 1                                | MTU4 compare match 4B                                                                      |

| 17h                |                                  | MTU4 compare match 4C                                                                      |

| 18h                | -                                | MTU4 compare match 4D                                                                      |

| 19h                | -                                | MTU4 overflow                                                                              |

| 1Ah                | 1                                | MTU4 underflow                                                                             |

| 1Fh                | Compare match timer              | CMT1 compare match 1                                                                       |

| 22h                | 8-bit timers                     | TMR0 compare match A0                                                                      |

| 23h                |                                  | TMR0 compare match B0                                                                      |

| 24h                | 1                                | TMR0 overflow                                                                              |

| 28h                | 1                                | TMR2 compare match A2                                                                      |

| 29h                | 1                                | TMR2 compare match B2                                                                      |

| 2Ah                | 1                                | TMR2 overflow                                                                              |

| 2Eh                | Realtime clock                   | RTC periodic event (select 1/256, 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2, 1, or 2 seconds) |

| 31h                | Independent watchdog timer       | IWDT underflow or refresh error                                                            |

| 32h                | Low power timer                  | LPT compare match 0                                                                        |

| 34h                | 12-bit A/D converter             | S12AD comparison conditions are met                                                        |

| 35h                | 1                                | S12AD comparison conditions are not met                                                    |

| 3Ah                | Serial communications interfaces | SCI5 error (receive error or error signal detection)                                       |

| 3Bh                | -                                | SCI5 receive data full                                                                     |

| 3Ch                | 1                                | SCI5 transmit data empty                                                                   |

| 3Dh                | 1                                | SCI5 transmit end                                                                          |

| 4Eh                | I <sup>2</sup> C-bus interface   | RIIC0 communication error or event generation                                              |

| 4Fh                | 1                                | RIIC0 receive data full                                                                    |

| 50h                | 1                                | RIIC0 transmit data empty                                                                  |

| 51h                | 1                                | RIIC0 transmit end                                                                         |

| 52h                | Serial peripheral interface      | RSPI0 error (mode fault, overrun, or parity error)                                         |

| 53h                | 1                                | RSPI0 idle                                                                                 |

| 54h                | 1                                | RSPI0 receive buffer full                                                                  |

| 55h                | 1                                | RSPI0 transmit buffer empty                                                                |

| 56h                | 1                                | RSPI0 transmit end                                                                         |

Table 20.3 Correspondence between Values Set in ELSRn.ELS[7:0] Bits and Event Signals (2/2)

|                        | <u> </u>                  |                                                        |

|------------------------|---------------------------|--------------------------------------------------------|

| ELS[7:0] Bit Value     | Peripheral Modules        | Event Signal Set in ELSRn                              |

| 58h                    | 12-bit A/D converter      | S12AD A/D conversion end                               |

| 5Bh                    | Voltage detection circuit | LVD1 voltage detection                                 |

| 5Dh                    | DMA controller            | DMAC0 transfer end                                     |

| 5Eh                    |                           | DMAC1 transfer end                                     |

| 5Fh                    |                           | DMAC2 transfer end                                     |

| 60h                    |                           | DMAC3 transfer end                                     |

| 61h                    | Data transfer controller  | DTC transfer end                                       |

| 62h                    | Clock generation circuit  | Oscillation stop detection of clock generation circuit |

| 63h                    | I/O ports                 | Input edge detection of input port group 1             |

| 64h                    |                           | Input edge detection of input port group 2             |

| 65h                    |                           | Input edge detection of single input port 0            |

| 66h                    |                           | Input edge detection of single input port 1            |

| 67h                    |                           | Input edge detection of single input port 2            |

| 68h                    |                           | Input edge detection of single input port 3            |

| 69h                    | Event link controller     | Software event                                         |

| 6Ah                    | Data operation circuit    | DOC data operation condition met                       |

| Settings other than at | pove are prohibited.      | •                                                      |

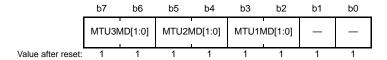

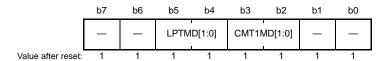

# 20.2.3 Event Link Option Setting Register A (ELOPA)

Address(es): ELC.ELOPA 0008 B11Fh

| Bit    | Symbol      | Bit Name              | Description                                                                                                     | R/W |

|--------|-------------|-----------------------|-----------------------------------------------------------------------------------------------------------------|-----|

| b1, b0 | _           | Reserved              | These bits are read as 1. The write value should be 1.                                                          | R/W |

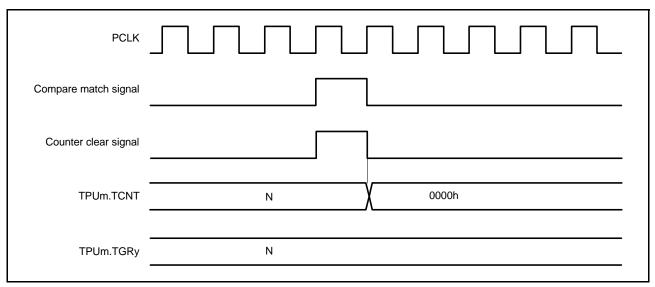

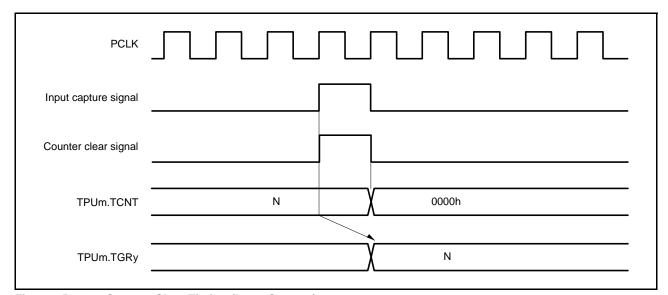

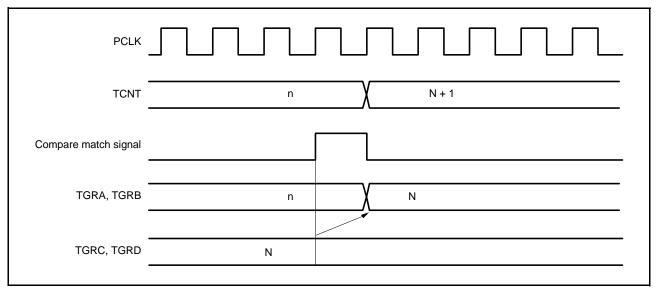

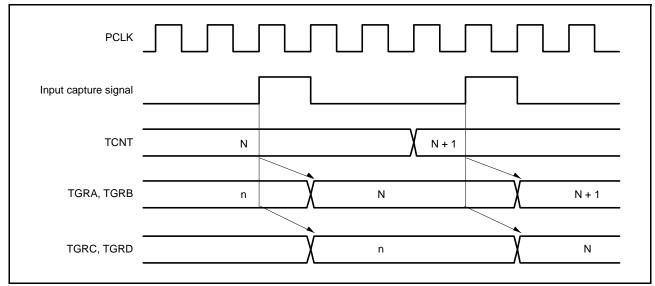

| b3, b2 | MTU1MD[1:0] | MTU1 Operation Select | b3 b2 0 0: Counting is started. 0 1: Counting is restarted. 1 0: Input capture*1 1 1: Event output is disabled. | R/W |

| b5, b4 | MTU2MD[1:0] | MTU2 Operation Select | b5 b4 0 0: Counting is started. 0 1: Counting is restarted. 1 0: Input capture*2 1 1: Event output is disabled. | R/W |

| b7, b6 | MTU3MD[1:0] | MTU3 Operation Select | b7 b6 0 0: Counting is started. 0 1: Counting is restarted. 1 0: Input capture*3 1 1: Event output is disabled. | R/W |

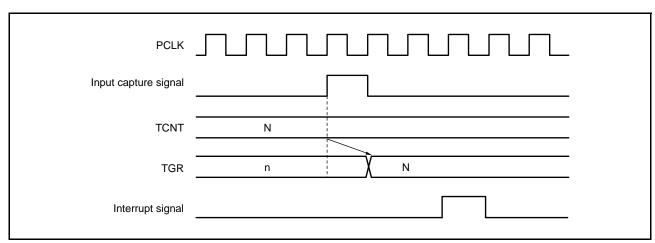

Note 1. The MTU1.TCNT value is captured into the MTU1.TGRA register.

Note 2. The MTU2.TCNT value is captured into the MTU2.TGRA register.

Note 3. The MTU3.TCNT value is captured into the MTU3.TGRA register.

The ELOPA register specifies the operations of MTU1 to MTU3 when an event signal is input. Set 11b (event output is disabled) when the ELC function is not used.

# 20.2.4 Event Link Option Setting Register B (ELOPB)

Address(es): ELC.ELOPB 0008 B120h

| Bit      | Symbol      | Bit Name              | Description                                                                                                     | R/W |

|----------|-------------|-----------------------|-----------------------------------------------------------------------------------------------------------------|-----|

| b1, b0   | MTU4MD[1:0] | MTU4 Operation Select | b1 b0 0 0: Counting is started. 0 1: Counting is restarted. 1 0: Input capture*1 1 1: Event output is disabled. | R/W |

| b7 to b2 | _           | Reserved              | These bits are read as 1. The write value should be 1.                                                          | R/W |

Note 1. The MTU4.TCNT value is captured into the MTU4.TGRA register.

The ELOPB register specifies the operation of MTU4 when an event signal is input. Set 11b (event output is disabled) when the ELC function is not used.

# 20.2.5 Event Link Option Setting Register C (ELOPC)

Address(es): ELC.ELOPC 0008 B121h

| Bit    | Symbol      | Bit Name              | Description                                                                                                                                                                                            | R/W |

|--------|-------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b1, b0 | _           | Reserved              | These bits are read as 1. The write value should be 1.                                                                                                                                                 | R/W |

| b3, b2 | CMT1MD[1:0] | CMT1 Operation Select | b3 b2 0 0: Counting is started. 0 1: Counting is restarted. 1 0: Event counter 1 1: Event output is disabled.                                                                                          | R/W |

| b5, b4 | LPTMD[1:0]  | LPT Operation Select  | <ul> <li>b5 b4</li> <li>0 0: Output the LPT compare match 0 event to ICU as an interrupt request</li> <li>1 1: Event output is disabled.</li> <li>Settings other than above are prohibited.</li> </ul> |     |

| b7, b6 | _           | Reserved              | These bits are read as 1. The write value should be 1.                                                                                                                                                 |     |

The ELOPC register specifies the operations of CMT1 and LPT when an event signal is input. Set 11b (event output is disabled) when the ELC function is not used.

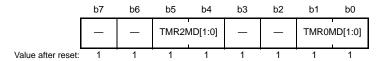

# 20.2.6 Event Link Option Setting Register D (ELOPD)

Address(es): ELC.ELOPD 0008 B122h

| Bit    | Symbol      | Bit Name              | Description                                                                                                   | R/W |  |

|--------|-------------|-----------------------|---------------------------------------------------------------------------------------------------------------|-----|--|

| b1, b0 | TMR0MD[1:0] | TMR0 Operation Select | b1 b0 0 0: Counting is started. 0 1: Counting is restarted. 1 0: Event counter 1 1: Event output is disabled. | R/W |  |

| b3, b2 | _           | Reserved              | These bits are read as 1. The write value should be 1.                                                        |     |  |

| b5, b4 | TMR2MD[1:0] | TMR2 Operation Select | b5 b4 0 0: Counting is started. 0 1: Counting is restarted. 1 0: Event counter 1 1: Event output is disabled. |     |  |

| b7, b6 | _           | Reserved              | These bits are read as 1. The write value should be 1.                                                        |     |  |

The ELOPD register specifies the operations of TMR0 and TMR2 when an event signal is input. Set 11b (event output is disabled) when the ELC function is not used.

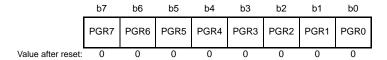

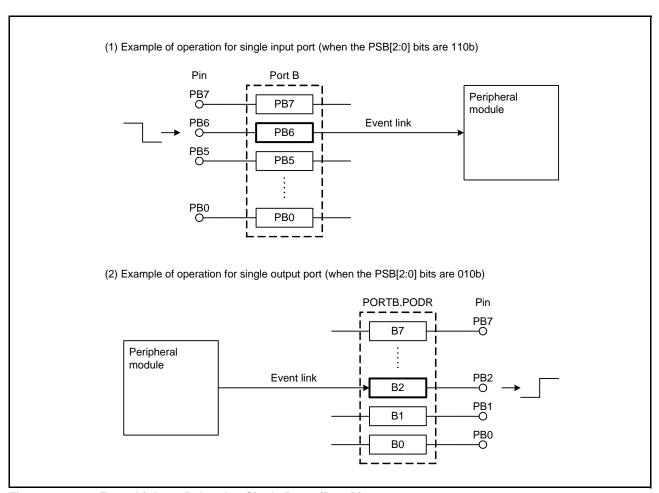

# 20.2.7 Port Group Setting Register n (PGRn) (n = 1, 2)

Address(es): ELC.PGR1 0008 B123h, ELC.PGR2 0008 B124h

| Bit | Symbol | Bit Name             | Description                                                 | R/W |

|-----|--------|----------------------|-------------------------------------------------------------|-----|

| b0  | PGR0   | Port Group Setting 0 | 0: Does not specify the port as a member of the port group. | R/W |

| b1  | PGR1   | Port Group Setting 1 | 1: Specifies the port as a member of the port group.        | R/W |

| b2  | PGR2   | Port Group Setting 2 |                                                             | R/W |

| b3  | PGR3   | Port Group Setting 3 |                                                             | R/W |

| b4  | PGR4   | Port Group Setting 4 |                                                             | R/W |

| b5  | PGR5   | Port Group Setting 5 |                                                             | R/W |

| b6  | PGR6   | Port Group Setting 6 |                                                             | R/W |

| b7  | PGR7   | Port Group Setting 7 |                                                             | R/W |

The PGRn register specifies a group of I/O ports. Among the ports, ports corresponding to bits set to 1 in the register are selected for a port group.

For example, when the PGR6 and PGR3 bits in the PGR1 register are set to 1, the PB6 and PB3 pins are selected to a port group.

Table 20.4 shows the PGRn register and corresponding ports.

Table 20.4 Registers Related to Port Groups and Corresponding Port Numbers

| Port Number | Port Group Setting Register (PGR) | Port Group Control Register (PGC) | Port Buffer Register (PDBF) |

|-------------|-----------------------------------|-----------------------------------|-----------------------------|

| Port B      | PGR1 register                     | PGC1 register                     | PDBF1 register              |

| Port E      | PGR2 register                     | PGC2 register                     | PDBF2 register              |

# 20.2.8 Port Group Control Register n (PGCn) (n = 1, 2)

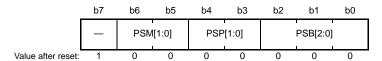

Address(es): ELC.PGC1 0008 B125h, ELC.PGC2 0008 B126h

| Bit      | Symbol    | Bit Name                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W |

|----------|-----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b1, b0   | PGCI[1:0] | Event Output Edge Select    | <ul> <li>b1 b0</li> <li>0 0: Event signal is output upon detection of the rising edge of the input signal to the port.</li> <li>0 1: Event signal is output upon detection of the falling edge of the input signal to the port.</li> <li>1 x: Event signal is output upon detection of both the rising and falling edges of the input signal to the port.</li> </ul>                                                         | R/W |

| b2       | PGCOVE    | PDBF Overwrite              | Overwriting the PDBFn register is disabled.     Overwriting the PDBFn register is enabled.                                                                                                                                                                                                                                                                                                                                   |     |

| b3       | _         | Reserved                    | This bit is read as 1. The write value should be 1.                                                                                                                                                                                                                                                                                                                                                                          |     |

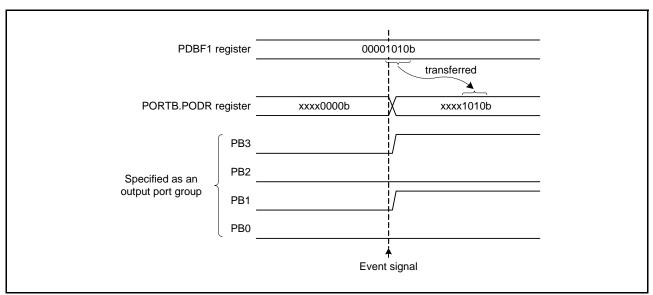

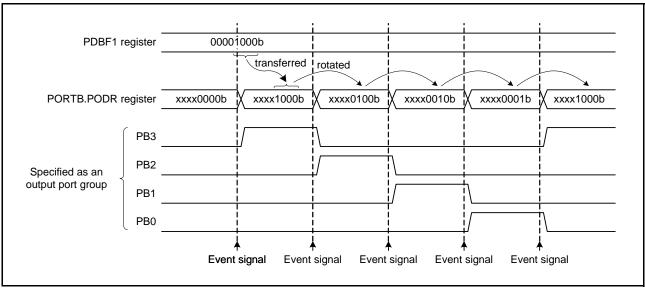

| b6 to b4 | PGCO[2:0] | Port Group Operation Select | <ul> <li>b6 b4</li> <li>0 0 0: Low is output when an event signal is input.</li> <li>0 0 1: High is output when an event signal is input.</li> <li>0 1 0: The output is toggled (inverted) when an event signal is input.</li> <li>0 1 1: The buffer value is output when an event signal is input.</li> <li>1 x x: The output data is rotated (from MSB to LSB) in the port group when an event signal is input.</li> </ul> | R/W |

| b7       | _         | Reserved                    | This bit is read as 1. The write value should be 1.                                                                                                                                                                                                                                                                                                                                                                          | R/W |

#### x: Don't care

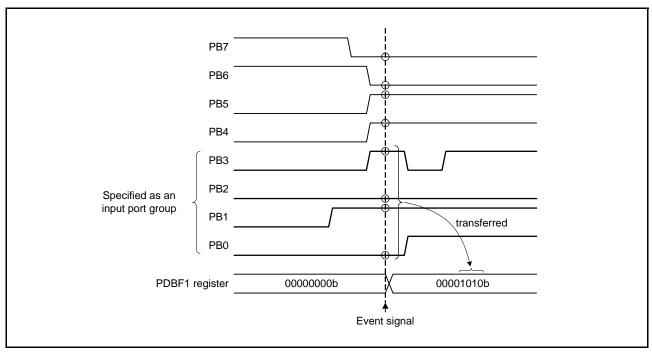

For the port group set as an output, the PGCn register specifies the form of outputting the signal from the port when an event signal is input. For the port group set as an input, the PGCn register enables/disables overwriting of the PDBFn register and specifies the conditions of event generation (edge of the input signal).

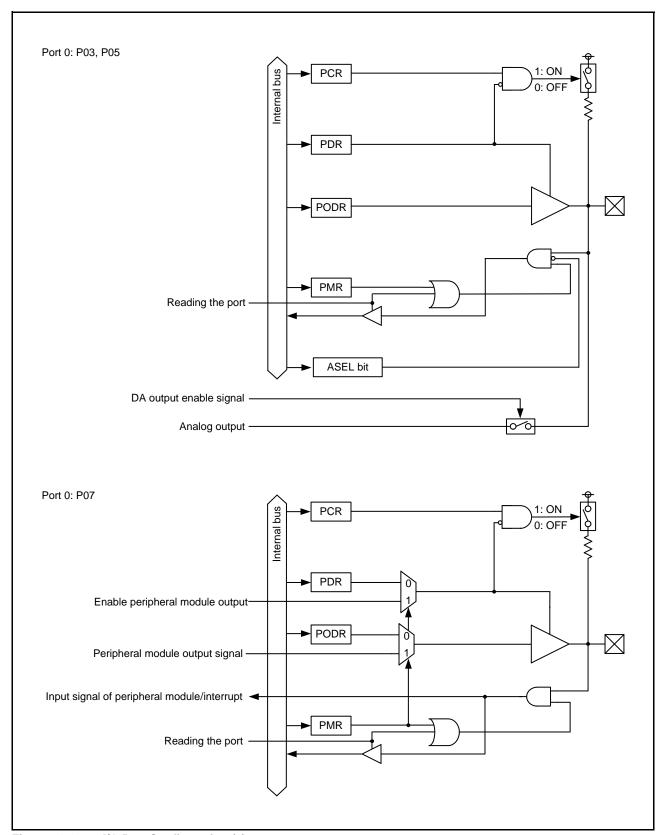

Specify the I/O direction of the port by the corresponding bit in the PDR register.

Refer to Table 20.4 for the PGCn register and corresponding ports.

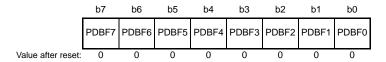

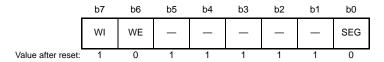

# 20.2.9 Port Buffer Register n (PDBFn) (n = 1, 2)

Address(es): ELC.PDBF1 0008 B127h, ELC.PDBF2 0008 B128h

| Bit | Symbol | Bit Name      | Description                                                                                                                                                                                                                                                                                        | R/W |

|-----|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | PDBF0  | Port Buffer 0 | Specify the data to be transferred to the PODR register when an event signal is input. The setting value is valid when the PGCn.PGC0[2:0] bits are 011b or 1xxb. Write access to the bit specified as a member of the input port group is disabled. For details, refer to section 20.3, Operation. | R/W |

| b1  | PDBF1  | Port Buffer 1 |                                                                                                                                                                                                                                                                                                    | R/W |

| b2  | PDBF2  | Port Buffer 2 |                                                                                                                                                                                                                                                                                                    | R/W |

| b3  | PDBF3  | Port Buffer 3 |                                                                                                                                                                                                                                                                                                    | R/W |

| b4  | PDBF4  | Port Buffer 4 |                                                                                                                                                                                                                                                                                                    | R/W |

| b5  | PDBF5  | Port Buffer 5 |                                                                                                                                                                                                                                                                                                    | R/W |