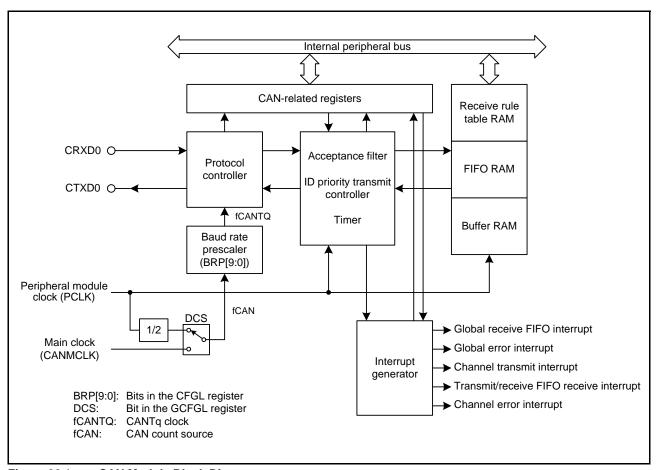

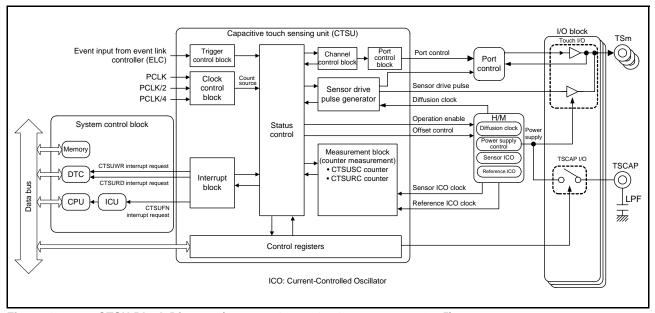

Figure 36.1 CAN Module Block Diagram

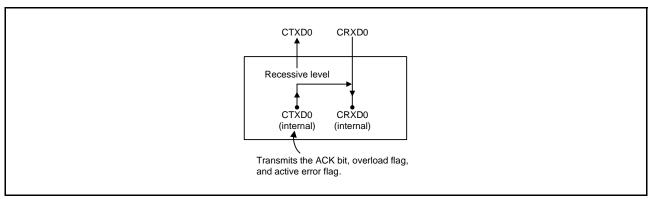

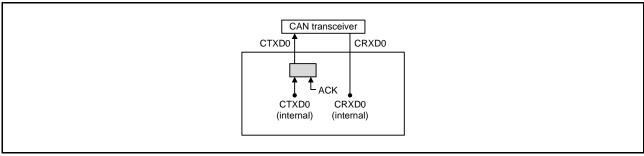

• CRXD0/CTXD0: CAN input/output pins

• Protocol controller: Handles CAN protocol processing such as bus arbitration, bit timing at transmission

and reception, stuffing, and error handling, etc.

• Receive rule table RAM: Stores the rules for filtering received messages. Each receive rule specifies an ID/

frame format/data length code of the message to be received, a label to be attached to the message that has passed through the filter, and the location of such message

to be stored.

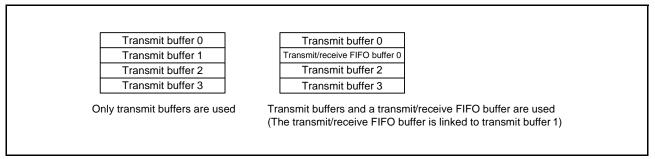

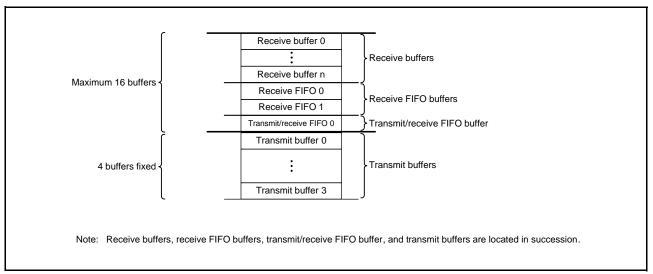

• FIFO RAM: Includes three 16-stage FIFO buffers. There are two FIFOs for reception only and

one FIFO for transmission or reception.

• Buffer RAM: Used as a transmit and receive buffer. There are 4 buffers for transmission and 16

buffers for reception.

Acceptance filter: Performs filtering of received messages.

• Timer: There are a timer for timestamp function during reception and a timer which

determines the message transmission intervals while using the transmit FIFO buffer.

Table 36.2 I/O Pins of the CAN Module

| Pin Name | I/O    | Description                             |

|----------|--------|-----------------------------------------|

| CRXD0    | Input  | Receive data input pins of the RSCAN0   |

| CTXD0    | Output | Transmit data output pins of the RSCAN0 |

# 36.2 Register Descriptions

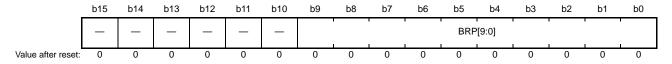

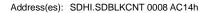

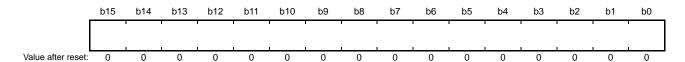

# 36.2.1 Bit Configuration Register L (CFGL)

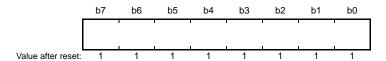

Address(es): RSCAN0.CFGL 000A 8300h

| Bit        | Symbol   | Bit Name                     | Description                                                                              | R/W |

|------------|----------|------------------------------|------------------------------------------------------------------------------------------|-----|

| b9 to b0   | BRP[9:0] | Prescaler Division Ratio Set | When these bits are set to P (0 to 1023), the baud rate prescaler divides fCAN by P + 1. | R/W |

| b15 to b10 | _        | Reserved                     | These bits are read as 0. The write value should be 0.                                   | R/W |

Modify the CFGL register only in channel reset mode or channel halt mode. Set this register in channel reset mode before making a transition to channel communication mode or channel halt mode. For setting bit timing, see section 36.9, Initial Settings.

## BRP[9:0] Bits (Prescaler Division Ratio Set)

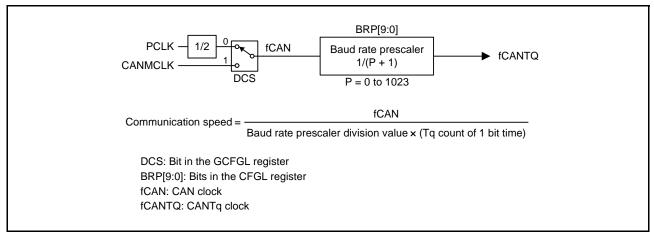

The CAN Tq clock (fCANTQ) is obtained by the CAN clock source (fCAN) and setting the clock division ratio with the BRP[9:0] bits and one clock cycle of the CAN Tq clock is 1 Time Quantum (Tq).

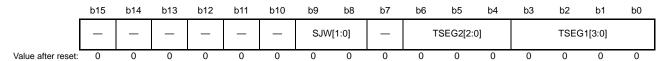

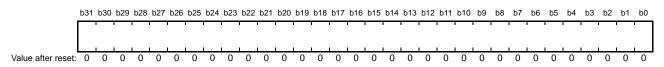

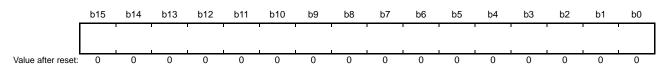

# 36.2.2 Bit Configuration Register H (CFGH)

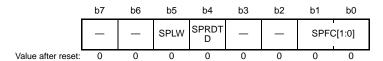

Address(es): RSCAN0.CFGH 000A 8302h

| Bit        | Symbol     | Bit Name                             | Description                                                                                                         | R/W |

|------------|------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|

| b3 to b0   | TSEG1[3:0] | Time Segment 1 Control               | b3                                                                                                                  | R/W |

| b6 to b4   | TSEG2[2:0] | Time Segment 2 Control               | b6 b4 0 0 0: Setting prohibited 0 0 1: 2 Tq 0 1 0: 3 Tq 0 1 1: 4 Tq 1 0 0: 5 Tq 1 0 1: 6 Tq 1 1 0: 7 Tq 1 1 1: 8 Tq | R/W |

| b7         | _          | Reserved                             | This bit is read as 0. The write value should be 0.                                                                 | R/W |

| b9, b8     | SJW[1:0]   | Resynchronization Jump Width Control | b9 b8<br>0 0: 1 Tq<br>0 1: 2 Tq<br>1 0: 3 Tq<br>1 1: 4 Tq                                                           | R/W |

| b15 to b10 | _          | Reserved                             | These bits are read as 0. The write value should be 0.                                                              | R/W |

Modify the CFGH register only in channel reset mode or channel halt mode. Set this register in channel reset mode before making a transition to channel communication mode or channel halt mode. For setting bit timing, see section 36.9, Initial Settings.

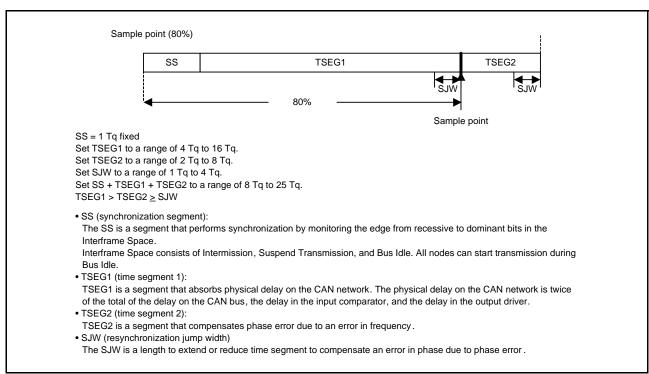

# TSEG1[3:0] Bits (Time Segment 1 Control)

These bits are used to specify a Tq value for the total length of the propagation time segment (PROP\_SEG) and phase buffer segment 1 (PHASE\_SEG1). A value of 4 Tq to 16 Tq can be set.

#### TSEG2[2:0] Bits (Time Segment 2 Control)

These bits are used to specify a Tq value for the length of phase buffer segment 2 (PHASE\_SEG2). A value of 2 Tq to 8 Tq can be set. Set a value smaller than the value of the TSEG1[3:0] bits.

#### SJW[1:0] Bits (Resynchronization Jump Width Control)

These bits are used to specify a Tq value for the resynchronization jump width. A value of 1 Tq to 4 Tq can be set. Set a value equal to or smaller than the value of the TSEG2[3:0] bits.

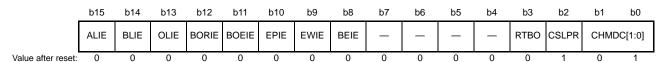

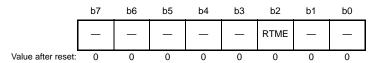

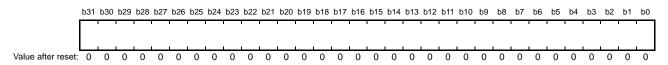

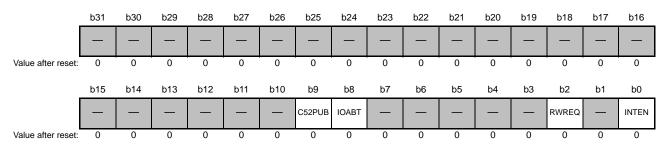

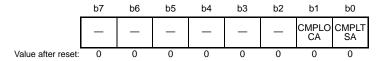

# 36.2.3 Control Register L (CTRL)

Address(es): RSCAN0.CTRL 000A 8304h

| Bit      | Symbol     | Bit Name                                    | Description                                                                                                                                                        | R/W |

|----------|------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b1, b0   | CHMDC[1:0] | Mode Select                                 | <ul> <li>b1 b0</li> <li>0 0: Channel communication mode.</li> <li>1: Channel reset mode.</li> <li>1: Channel halt mode.</li> <li>1: Setting prohibited.</li> </ul> | R/W |

| b2       | CSLPR      | Channel Stop Mode                           | O: Other than channel stop mode.     Channel stop mode.                                                                                                            | R/W |

| b3       | RTBO       | Forcible Return from Bus-off                | When this bit is set to 1, forcible return from the bus off state is made. This bit is read as 0.                                                                  | R/W |

| b7 to b4 | _          | Reserved                                    | These bits are read as 0. The write value should be 0.                                                                                                             | R/W |

| b8       | BEIE       | Protocol Error Interrupt Enable             | Protocol error interrupt is disabled.     Protocol error interrupt is enabled.                                                                                     | R/W |

| b9       | EWIE       | Error Warning Interrupt Enable              | Error warning interrupt is disabled.     Error warning interrupt is enabled.                                                                                       | R/W |

| b10      | EPIE       | Error Passive Interrupt Enable              | Error passive interrupt is disabled.     Error passive interrupt is enabled.                                                                                       | R/W |

| b11      | BOEIE      | Bus Off Entry Interrupt Enable              | Bus off entry interrupt is disabled.     Bus off entry interrupt is enabled.                                                                                       | R/W |

| b12      | BORIE      | Bus Off Recovery Interrupt<br>Enable        | Bus off recovery interrupt is disabled.     Bus off recovery interrupt is enabled.                                                                                 | R/W |

| b13      | OLIE       | Overload Frame Transmit<br>Interrupt Enable | Overload frame transmit interrupt is disabled.     Overload frame transmit interrupt is enabled.                                                                   | R/W |

| b14      | BLIE       | Bus Lock Interrupt Enable                   | Bus lock interrupt is disabled.     Bus lock interrupt is enabled.                                                                                                 | R/W |

| b15      | ALIE       | Arbitration Lost Interrupt Enable           | O: Arbitration lost interrupt is disabled.     1: Arbitration lost interrupt is enabled.                                                                           | R/W |

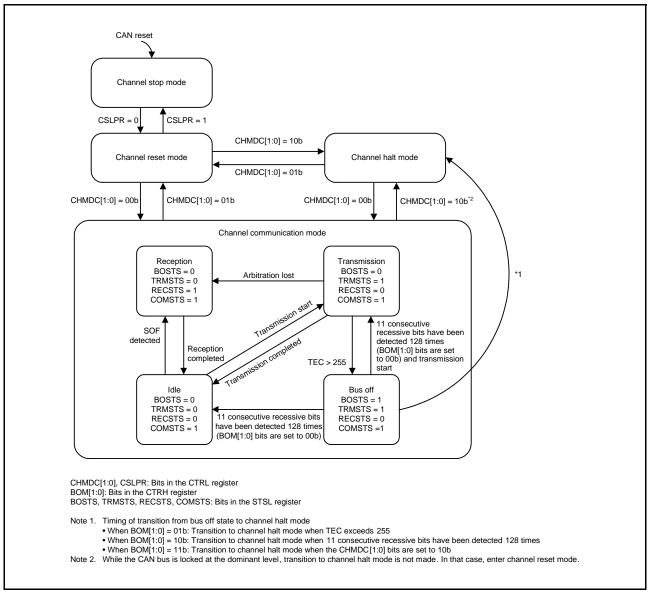

## CHMDC[1:0] Bits (Mode Select)

These bits are used to select a channel mode (channel communication mode, channel reset mode, or channel halt mode). For details, see section 36.3.2, Channel Modes. Setting the CSLPR bit to 1 in channel reset mode allows transition to channel stop mode. Do not set the CHMDC[1:0] bits to 11b. When the CAN module has transitioned to channel halt mode depending on the setting of the CTRH.BOM[1:0] bits, the CHMDC[1:0] bits automatically become 10b.

## **CSLPR Bit (Channel Stop Mode)**

Setting this bit to 1 places the channel in channel stop mode.

Setting this bit to 0 makes the channel leave from channel stop mode.

Do not modify this bit in channel communication mode or channel halt mode.

#### RTBO Bit (Forcible Return from Bus-off)

Setting this bit to 1 (forcible return from the bus off state) in the bus off state forcibly returns the state from the bus off state to the error active state. This bit is automatically set to 0. Setting this bit to 1 sets the STSH.TEC[7:0] and STSH.REC[7:0] flags to 00h and also sets the STSL.BOSTS flag to 0 (not in bus off state). The other registers remain unchanged. No bus off recovery interrupt request due to return from the bus off state is generated. Use this bit only when the CTRH.BOM[1:0] bits are 00b (ISO 11898-1 compliant).

A delay of up to 1 CAN bit time occurs after the RTBO bit is set to 1 until the CAN module transitions to the error active state. Set this bit to 1 in channel communication mode.

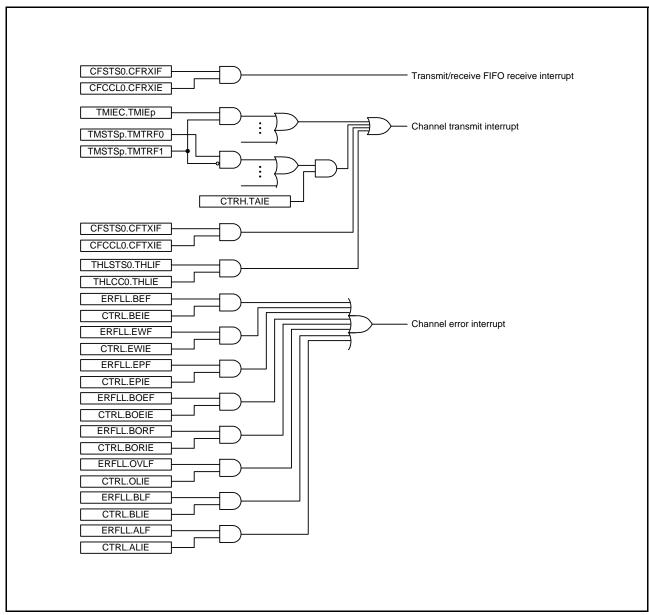

#### **BEIE Bit (Protocol Error Interrupt Enable)**

When the ERFLL.BEF flag becomes 1 while the BEIE bit is 1, an error interrupt request is generated. Modify this bit only in channel reset mode.

#### **EWIE Bit (Error Warning Interrupt Enable)**

When the ERFLL.EWF flag becomes 1 while the EWIE bit is 1, an error interrupt request is generated. Modify this bit only in channel reset mode.

#### **EPIE Bit (Error Passive Interrupt Enable)**

When the ERFLL.EPF flag becomes 1 while the EPIE bit is 1, an error interrupt request is generated. Modify this bit only in channel reset mode.

#### **BOEIE Bit (Bus Off Entry Interrupt Enable)**

When the ERFLL.BOEF flag becomes 1 while the BOEIE bit is 1, an error interrupt request is generated. Modify this bit only in channel reset mode.

#### **BORIE Bit (Bus Off Recovery Interrupt Enable)**

When the ERFLL.BORF flag becomes 1 while the BORIE bit is 1, an error interrupt request is generated. Modify this bit only in channel reset mode.

#### **OLIE Bit (Overload Frame Transmit Interrupt Enable)**

When the ERFLL.OVLF flag becomes 1 while the OLIE bit is 1, an error interrupt request is generated. Modify this bit only in channel reset mode.

#### **BLIE Bit (Bus Lock Interrupt Enable)**

When the ERFLL.BLF flag becomes 1 while the BLIE bit is 1, an error interrupt request is generated. Modify this bit only in channel reset mode.

#### **ALIE Bit (Arbitration Lost Interrupt Enable)**

When the ERFLL.ALF flag becomes 1 while the ALIE bit is 1, an error interrupt request is generated. Modify this bit only in channel reset mode.

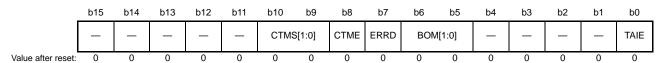

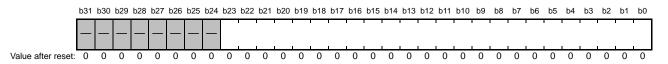

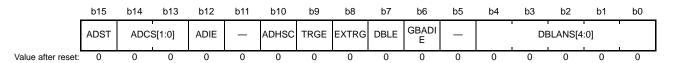

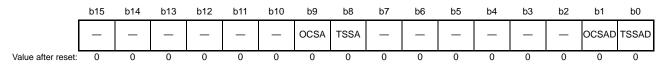

## 36.2.4 Control Register H (CTRH)

Address(es): RSCAN0.CTRH 000A 8306h

| Bit        | Symbol    | Bit Name                          | Description                                                                                                                                                                                                                                                                 | R/W |

|------------|-----------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0         | TAIE      | Transmit Abort Interrupt Enable   | Transmit abort interrupt is disabled.     Transmit abort interrupt is enabled.                                                                                                                                                                                              | R/W |

| b4 to b1   | _         | Reserved                          | These bits are read as 0. The write value should be 0.                                                                                                                                                                                                                      | R/W |

| b6, b5     | BOM[1:0]  | Bus Off Recovery Mode Select      | <ul> <li>b6 b5</li> <li>0 0: ISO 11898-1 compliant</li> <li>1: Transition to channel halt mode at bus-off entry</li> <li>0: Transition to channel halt mode at bus-off end</li> <li>1: Transition to channel halt mode in the bus off state by a program request</li> </ul> | R/W |

| b7         | ERRD      | Error Display Mode Select         | O: Only the first error is indicated after b14 to b8 in the ERFLL register have all been cleared.  The error flags of all errors are indicated.                                                                                                                             | R/W |

| b8         | CTME      | Communication Test Mode<br>Enable | Communication test mode is disabled.     Communication test mode is enabled.                                                                                                                                                                                                | R/W |

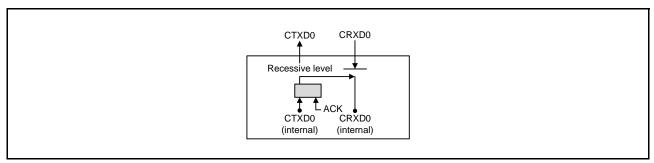

| b10, b9    | CTMS[1:0] | Communication Test Mode<br>Select | b10 b9 0 0: Standard test mode 0 1: Listen-only mode 1 0: Self-test mode 0 (external loopback mode) 1 1: Self-test mode 1 (internal loopback mode)                                                                                                                          | R/W |

| b15 to b11 | _         | Reserved                          | These bits are read as 0. The write value should be 0.                                                                                                                                                                                                                      | R/W |

#### **TAIE Bit (Transmit Abort Interrupt Enable)**

When transmit abort of the transmit buffer is completed with the TAIE bit set to 1, an interrupt request is generated. Modify this bit only in channel reset mode.

#### BOM[1:0] Bits (Bus Off Recovery Mode Select)

These bits are used to select a bus off recovery mode of the CAN module.

When the BOM[1:0] bits are set to 00b, return to the error active state from the bus off state is compliant with the ISO 11898-1 standard. That is, the CAN module reenters the CAN communication (error active state) after 11 consecutive recessive bits are detected 128 times. A bus off recovery interrupt request is generated at the time of return from the bus off state. Even if the CTRL.CHMDC[1:0] bits are set to 10b (channel halt mode) before recessive bits are detected 128 times, the CAN module does not transition to channel halt mode until recessive bits are detected 128 times.

When the CAN module reaches the bus off state while the BOM[1:0] bits are set to 01b, the CTRL.CHMDC[1:0] bits are set to 10b and the CAN module transitions to channel halt mode. No bus off recovery interrupt request is generated at the time of return from the bus off state and the STSH.TEC[7:0] and STSH.REC[7:0] flags are set to 00h.

When the CAN module reaches the bus off state when the BOM[1:0] bits are set to 10b, the CTRL.CHMDC[1:0] bits are set to 10b and the CAN module transitions to channel halt mode after return from the bus off state (11 consecutive recessive bits are detected 128 times). A bus off recovery interrupt request is generated at the time of return from the bus off state and the STSH.TEC[7:0] and STSH.REC[7:0] flags are set to 00h.

When the BOM[1:0] bits are set to 11b and the CTRL.CHMDC[1:0] bits are set to 10b while the CAN module is in the bus off state, the CAN module transitions to channel halt mode. No bus off recovery interrupt request is generated at the time of return from the bus off state and the STSH.TEC[7:0] and STSH.REC[7:0] flags are set to 00h. However, if 11 consecutive recessive bits are detected 128 times and the CAN module has recovered to the error active state from the

bus off state before the CTRL.CHMDC[1:0] bits are set to 10b, a bus off recovery interrupt request is generated. If the CPU requests transition to channel reset mode at the same time when the CAN module transitions to channel halt mode (at bus off entry when the BOM[1:0] bits are 01b or at bus off end when the BOM[1:0] bits are 10b), the CPU's request takes precedence. Modify these bits only in channel reset mode.

#### **ERRD Bit (Error Display Mode Select)**

This bit is used to control display mode of b14 to b8 in the ERFLL register.

When this bit is 0, only the flags of the first error become 1. If two or more errors occur first, all the flags of detected errors become 1.

When this bit is 1, all the flags of errors that have occurred become 1 regardless of the error occurrence order. Modify this bit only in channel reset mode or channel halt mode.

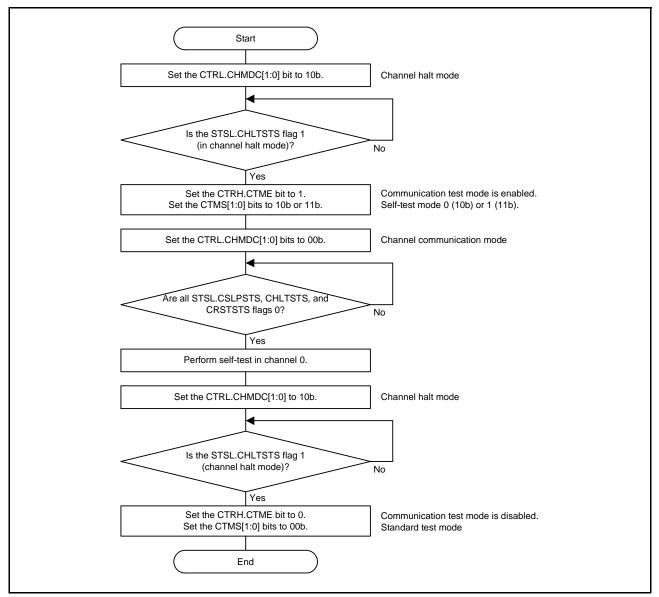

#### **CTME Bit (Communication Test Mode Enable)**

Setting this bit to 1 enables communication test mode. Modify this bit only in channel halt mode. This bit becomes 0 in channel reset mode.

#### CTMS[1:0] Bits (Communication Test Mode Select)

These bits are used to select a communication test mode. Modify these bits only in channel halt mode. These bits become 0 in channel reset mode.

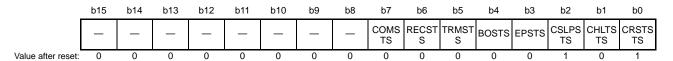

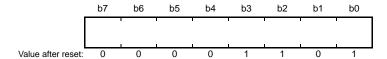

# 36.2.5 Status Register L (STSL)

Address(es): RSCAN0.STSL 000A 8308h

| Bit       | Symbol  | Bit Name                  | Description                                                   | R/W |

|-----------|---------|---------------------------|---------------------------------------------------------------|-----|

| b0        | CRSTSTS | Channel Reset Status Flag | 0: Not in channel reset mode 1: In channel reset mode         | R   |

| b1        | CHLTSTS | Channel Halt Status Flag  | 0: Not in channel halt mode 1: In channel halt mode           | R   |

| b2        | CSLPSTS | Channel Stop Status Flag  | 0: Not in channel stop mode 1: In channel stop mode           | R   |

| b3        | EPSTS   | Error Passive Status Flag | 0: Not in error passive state 1: In error passive state       | R   |

| b4        | BOSTS   | Bus Off Status Flag       | 0: Not in bus off state 1: In bus off state                   | R   |

| b5        | TRMSTS  | Transmit Status Flag      | Bus idle or in reception     In transmission or bus off state | R   |

| b6        | RECSTS  | Receive Status Flag       | 0: Bus idle, in transmission or bus off state 1: In reception | R   |

| b7        | COMSTS  | Communication Status Flag | Communication is not ready.     Communication is ready.       | R   |

| b15 to b8 | _       | Reserved                  | These bits are read as 0.                                     | R   |

#### **CRSTSTS Flag (Channel Reset Status Flag)**

This flag becomes 1 when the CAN module has transitioned to channel reset mode, and becomes 0 when the CAN module has transitioned to channel communication mode or channel halt mode. This flag remains 1 even if the CAN module transitions from channel reset mode to channel stop mode.

# **CHLTSTS Flag (Channel Halt Status Flag)**

This flag becomes 1 when the CAN module has transitioned to channel halt mode, and becomes 0 when the CAN module has exited channel halt mode.

## **CSLPSTS Flag (Channel Stop Status Flag)**

This flag becomes 1 when the CAN module has transitioned to channel stop mode, and becomes 0 when the CAN module has returned from channel stop mode.

#### **EPSTS Flag (Error Passive Status Flag)**

This flag becomes 1 when the CAN module has entered the error passive state ( $128 \le STSH.TEC[7:0]$  value  $\le 255$  or  $128 \le STSH.REC[7:0]$  value), and becomes 0 when the CAN module has exited the error passive state or has entered channel reset mode.

#### **BOSTS Flag (Bus Off Status Flag)**

This flag becomes 1 when the CAN module has entered the bus off state (STSH.TEC[7:0] value > 255), and becomes 0 when the CAN module has exited the bus off state.

## **TRMSTS Flag (Transmit Status Flag)**

This flag becomes 1 when transmission has started, and becomes 0 when the bus has become idle or reception has started. This flag remains 1 in the bus off state.

## **RECSTS Flag (Receive Status Flag)**

This flag becomes 1 when reception has started, and becomes 0 when the bus has become idle or transmission has started.

#### **COMSTS Flag (Communication Status Flag)**

This flag indicates that communication is ready.

This flag becomes 1 when the CAN module has detected 11 consecutive recessive bits after it has transitioned from channel reset mode or channel halt mode to channel communication mode. This flag becomes 0 in channel reset mode or channel halt mode.

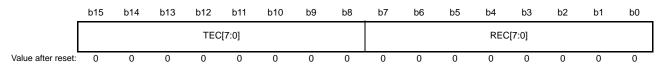

# 36.2.6 Status Register H (STSH)

Address(es): RSCAN0.STSH 000A 830Ah

| Bit       | Symbol   | Description                                   | R/W |

|-----------|----------|-----------------------------------------------|-----|

| b7 to b0  | REC[7:0] | The receive error counter (REC) can be read.  | R   |

| b15 to b8 | TEC[7:0] | The transmit error counter (TEC) can be read. | R   |

## REC[7:0] Flags

These flags indicate the receive error counter value. For receive error counter increment/decrement conditions, see the CAN standard (ISO 11898-1).

These flags become 00h in channel reset mode.

#### TEC[7:0] Flags

These flags indicate the transmit error counter value. For transmit error counter increment/decrement conditions, see the CAN standard (ISO 11898-1).

These flags become 00h in channel reset mode.

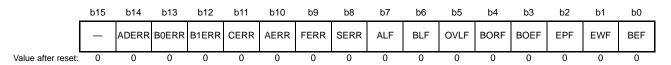

# 36.2.7 Error Flag Register L (ERFLL)

Address(es): RSCAN0.ERFLL 000A 830Ch

| Bit | Symbol | Bit Name                 | Description                                                                              | R/W         |

|-----|--------|--------------------------|------------------------------------------------------------------------------------------|-------------|

| b0  | BEF    | Bus Error Flag           | No channel bus error is detected.     Channel bus error is detected.                     | R/(W)<br>*1 |

| b1  | EWF    | Error Warning Flag       | O: No error warning is detected. Error warning is detected.                              | R/(W)<br>*1 |

| b2  | EPF    | Error Passive Flag       | <ul><li>0: No error passive is detected.</li><li>1: Error passive is detected.</li></ul> | R/(W)<br>*1 |

| b3  | BOEF   | Bus Off Entry Flag       | O: No bus off entry is detected.  Bus off entry is detected.                             | R/(W)<br>*1 |

| b4  | BORF   | Bus Off Recovery Flag    | O: No bus off recovery is detected.  Bus off recovery is detected.                       | R/(W)<br>*1 |

| b5  | OVLF   | Overload Flag            | No overload is detected.     Overload is detected.                                       | R/(W)<br>*1 |

| b6  | BLF    | Bus Lock Flag            | O: No channel bus lock is detected. Channel bus lock is detected.                        | R/(W)<br>*1 |

| b7  | ALF    | Arbitration Lost Flag    | No arbitration lost is detected.     Arbitration lost is detected.                       | R/(W)<br>*1 |

| b8  | SERR   | Stuff Error Flag         | O: No stuff error is detected. Stuff error is detected.                                  | R/(W)<br>*1 |

| b9  | FERR   | Form Error Flag          | O: No form error is detected. T: Form error is detected.                                 | R/(W)<br>*1 |

| b10 | AERR   | ACK Error Flag           | 0: No ACK error is detected.<br>1: ACK error is detected.                                | R/(W)<br>*1 |

| b11 | CERR   | CRC Error Flag           | 0: No CRC error is detected. 1: CRC error is detected.                                   | R/(W)<br>*1 |

| b12 | B1ERR  | Recessive Bit Error Flag | O: No recessive bit error is detected. Recessive bit error is detected.                  | R/(W)<br>*1 |

| b13 | B0ERR  | Dominant Bit Error Flag  | O: No dominant bit error is detected. Dominant bit error is detected.                    | R/(W)<br>*1 |

| b14 | ADERR  | ACK Delimiter Error Flag | No ACK delimiter error is detected.     ACK delimiter error is detected.                 | R/(W)<br>*1 |

| b15 | _      | Reserved                 | This bit is read as 0. The write value should be 0.                                      | R/W         |

Note 1. Only 0 can be written to this bit, to clear the flag. Writing 1 does not affect the flag value.

See the CAN standard (ISO 11898-1) if you want to check error occurrence conditions. To clear each flag of this register, write 0 by the program. These flags cannot be set to 1 by the program. If any of these flags becomes 1 at the timing when the program writes 0 to the flag, the flag becomes 1. Each flag becomes 0 in channel reset mode.

With respect to b14 to b8 in the ERFLL register, if an error is detected with all flags of b14 to b8 set to 0 when the CTRH.ERRD bit is set to 0 (only the first error information is displayed), the corresponding flag becomes 1.

#### **BEF Flag (Bus Error Flag)**

This flag becomes 1 when any one of the ADERR, B0ERR, B1ERR, CERR, AERR, FERR, and SERR flags becomes 1.

#### **EWF Flag (Error Warning Flag)**

This flag becomes 1 only when the STSH.REC[7:0] or STSH.TEC[7:0] value exceeds 95 for the first time. Therefore, if the program writes 0 to this flag with the STSH.REC[7:0] or STSH.TEC [7:0] value remaining over 95, this bit is not set to 1 until both STSH.REC[7:0] and STSH.TEC[7:0] values become 95 or less and then the STSH.REC[7:0] or STSH.TEC[7:0] value exceeds 95 again.

### **EPF Flag (Error Passive Flag)**

This flag becomes 1 when the CAN module becomes error passive state (STSH.REC[7:0] or STSH.TEC[7:0] value > 127). This flag becomes 1 only when the STSH.REC[7:0] or STSH.TEC[7:0] value exceeds 127 for the first time. Therefore, if the program writes 0 to this flag with the STSH.REC[7:0] or STSH.TEC[7:0] value remaining over 127, this bit is not set to 1 until both STSH.REC[7:0] and STSH.TEC[7:0] values become 127 or less and then the STSH.REC[7:0] or STSH.TEC[7:0] value exceeds 127 again.

#### **BOEF Flag (Bus Off Entry Flag)**

This flag becomes 1 when the state becomes bus off state (STSH.TEC[7:0] value > 255). This flag also becomes 1 when the state becomes bus off state with the CTRH.BOM[1:0] bits set to 01b (transition to channel halt mode at bus off entry).

#### **BORF Flag (Bus Off Recovery Flag)**

This flag becomes 1 when 11 consecutive recessive bits have been detected 128 times and the CAN module returns from the bus off state. However, this flag is not set to 1 if the CAN module returns from the bus off state in any of the following ways before 11 consecutive recessive bits are detected 128 times.

- The CTRL.CHMDC[1:0] bits are set to 01b (channel reset mode).

- The CTRL.RTBO bit is set to 1 (forcible return from the bus off state is made).

- The CTRH.BOM[1:0] bits are set to 01b (transition to channel halt mode at bus off entry).

- The CTRL.CHMDC[1:0] bits are set to 10b (channel halt mode) before 11 consecutive recessive bits are detected 128 times with the CTRH.BOM[1:0] bits set to 11b (transition to channel halt mode upon a request from the program during bus off).

#### **OVLF Flag (Overload Flag)**

This flag becomes 1 when the overload frame transmit condition has been detected when performing reception or transmission.

#### **BLF Flag (Bus Lock Flag)**

This flag becomes 1 when 32 consecutive dominant bits have been detected on the CAN bus in channel communication mode. After that, detection of the bus lock becomes possible again if either of the following conditions is met.

- A recessive bit is detected after the BLF flag has been modified from 1 to 0.

- The CAN module transitions to channel reset mode and returns to channel communication mode after the BLF flag has been modified from 1 to 0.

# **ALF Flag (Arbitration Lost Flag)**

This flag becomes 1 when an arbitration lost has been detected.

## **SERR Flag (Stuff Error Flag)**

This flag becomes 1 when a stuff error has been detected.

#### FERR Flag (Form Error Flag)

This flag becomes 1 when a form error has been detected.

#### **AERR Flag (ACK Error Flag)**

This flag becomes 1 when an ACK error has been detected.

#### **CERR Flag (CRC Error Flag)**

This flag becomes 1 when a CRC error has been detected.

#### **B1ERR Flag (Recessive Bit Error Flag)**

This flag becomes 1 when a dominant bit has been detected though a recessive bit was transmitted.

#### **B0ERR Flag (Dominant Bit Error Flag)**

This flag becomes 1 when a recessive bit has been detected though a dominant bit was transmitted.

### **ADERR Flag (ACK Delimiter Error Flag)**

This flag becomes 1 when a form error has been detected in the ACK delimiter during transmission.

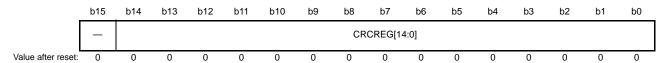

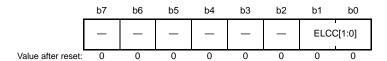

## 36.2.8 Error Flag Register H (ERFLH)

Address(es): RSCAN0.ERFLH 000A 830Eh

| Bit       | Symbol       | Bit Name             | Description                                                                           | R/W |

|-----------|--------------|----------------------|---------------------------------------------------------------------------------------|-----|

| b14 to b0 | CRCREG[14:0] | CRC Calculation Data | A CRC value calculated based on the transmit message or receive message is indicated. | R   |

| b15       | _            | Reserved             | This bit is read as 0.                                                                | R   |

## CRCREG[14:0] Bits (CRC Calculation Data)

When the CTRH.CTME bit is set to 1 (communication test mode is enabled), the CRC value calculated based on the transmit or receive message can be read. When the CTRH.CTME bit is set to 0 (communication test mode is disabled), these bits are read as 0.

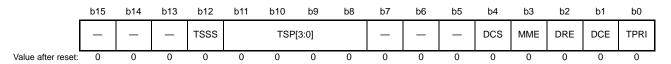

# 36.2.9 Global Configuration Register L (GCFGL)

Address(es): RSCAN.GCFGL 000A 8322h

| Bit        | Symbol   | Bit Name                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W |

|------------|----------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0         | TPRI     | Transmit Priority Select           | ID priority     Transmit buffer number priority                                                                                                                                                                                                                                                                                                                                                                                 | R/W |

| b1         | DCE      | DLC Check Enable                   | 0: DLC check is disabled. 1: DLC check is enabled.                                                                                                                                                                                                                                                                                                                                                                              | R/W |

| b2         | DRE      | DLC Replacement Enable             | DLC replacement is disabled.     DLC replacement is enabled.                                                                                                                                                                                                                                                                                                                                                                    | R/W |

| b3         | MME      | Mirror Function Enable             | O: Mirror function is disabled.  1: Mirror function is enabled.                                                                                                                                                                                                                                                                                                                                                                 | R/W |

| b4         | DCS      | CAN Clock Source Select            | 0: PCLK<br>1: CANMCLK (obtained from the main clock)                                                                                                                                                                                                                                                                                                                                                                            | R/W |

| b7 to b5   | _        | Reserved                           | These bits are read as 0. The write value should be 0.                                                                                                                                                                                                                                                                                                                                                                          | R/W |

| b11 to b8  | TSP[3:0] | Timestamp Clock Source<br>Division | b11 b8   0 0 0 0: Not divided   0 0 0 1: Divided by 2   0 0 1 0: Divided by 4   0 0 1 1: Divided by 8   0 1 0 0: Divided by 16   0 1 0 1: Divided by 32   0 1 1 0: Divided by 64   0 1 1 1: Divided by 128   1 0 0 0: Divided by 128   1 0 0 0: Divided by 512   1 0 1 0: Divided by 512   1 0 1 1: Divided by 1024   1 0 1 1: Divided by 2048   1 1 0 0: Divided by 4096   1 1 0 1: Divided by 16384   1 1 1: Divided by 32768 | R/W |

| b12        | TSSS     | Timestamp Clock Source Select      | 0: PCLK<br>1: CAN bit time clock                                                                                                                                                                                                                                                                                                                                                                                                | R/W |

| b15 to b13 | _        | Reserved                           | These bits are read as 0. The write value should be 0.                                                                                                                                                                                                                                                                                                                                                                          | R/W |

Modify the GCFGL register only in global reset mode.

## **TPRI Bit (Transmit Priority Select)**

This bit is used to set the transmit priority.

When this bit is set to 0, ID priority is selected and the transmit priority complies with the CAN bus arbitration rule (ISO 11898-1 standard). When this bit is set to 1, transmit buffer number priority is selected and the minimum number of transmit buffer specified for transmission takes precedence.

#### DCE Bit (DLC Check Enable)

Setting this bit to 1 makes the DLC check function available. Set the GAFLPHj.GAFLDLC[3:0] bits to 0000b before setting the DCE bit to 0.

## **DRE Bit (DLC Replacement Enable)**

When the DRE bit is set to 1, the DLC value of the receive rule is stored in the buffer instead of the DLC value of the received message after the DLC value has passed through the DLC filter. In this case, a value of 00h is stored in the data byte that exceeds the DLC value of the receive rule.

When the DCE bit is set to 1 (DLC check is enabled), the DLC replacement function is available.

#### **MME Bit (Mirror Function Enable)**

Setting this bit to 1 makes the mirror function available.

#### **DCS Bit (CAN Clock Source Select)**

When this bit is set to 0, the peripheral clock (PCLK) divided by 2 is used as the CAN clock source (fCAN). When this bit is set to 1, CANMCLK obtained from the EXTAL pin is used as the CAN clock source (fCAN).

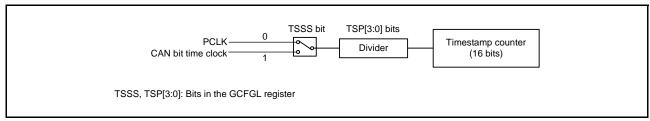

#### TSP[3:0] Bits (Timestamp Clock Source Division)

The clock obtained by dividing the clock source selected by the TSSS bit by the TSP[3:0] value is the count source of the timestamp counter.

#### **TSSS Bit (Timestamp Clock Source Select)**

This bit is used to select a clock source of the timestamp counter.

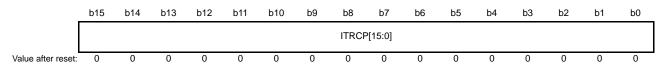

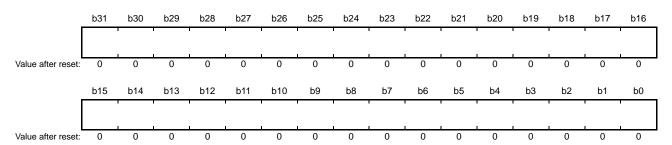

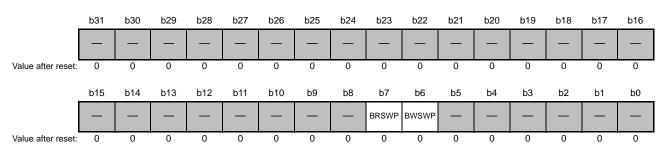

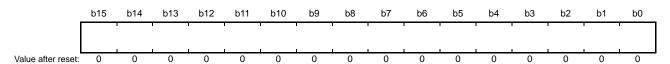

# 36.2.10 Global Configuration Register H (GCFGH)

Address(es): RSCAN.GCFGH 000A 8324h

| Bit       | Symbol      | Bit Name                     | Description                                                                                                           | R/W |

|-----------|-------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|

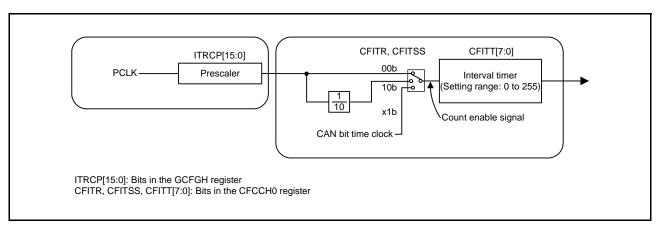

| b15 to b0 | ITRCP[15:0] | Interval Timer Prescaler Set | If the set value is M, PCLK is frequency-divided by M. Setting 0000h is prohibited when the interval timer is in use. | R/W |

Modify the GCFGH register only in global reset mode.

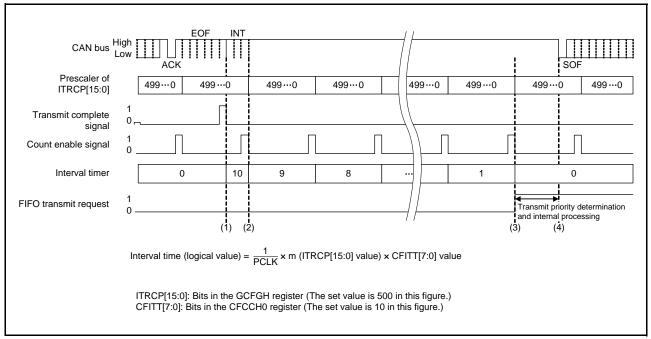

#### ITRCP[15:0] Bits (Interval Timer Prescaler Set)

These bits are used to set a clock source division value of the interval timer for FIFO buffers. For details, see section 36.5.3 (1) Interval Transmission Function.

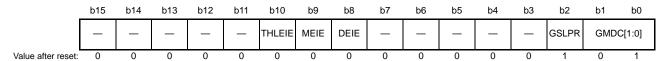

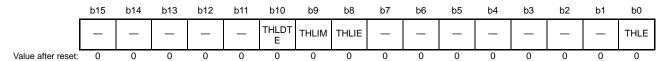

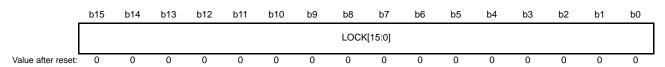

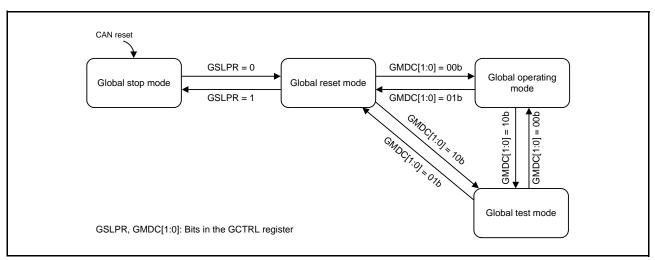

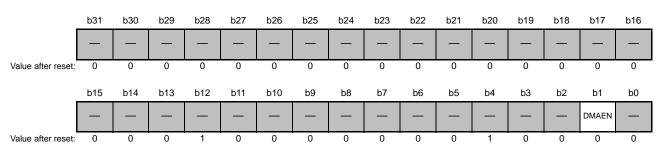

# 36.2.11 Global Control Register L (GCTRL)

Address(es): RSCAN.GCTRL 000A 8326h

| Bit        | Symbol    | Bit Name                                          | Description                                                                                                                                             | R/W |

|------------|-----------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b1, b0     | GMDC[1:0] | Global Mode Select                                | <ul> <li>b1 b0</li> <li>0 0: Global operating mode</li> <li>1: Global reset mode</li> <li>0: Global test mode</li> <li>1: Setting prohibited</li> </ul> | R/W |

| b2         | GSLPR     | Global Stop Mode                                  | 0: Other than global stop mode<br>1: Global stop mode                                                                                                   | R/W |

| b7 to b3   | _         | Reserved                                          | These bits are read as 0. The write value should be 0.                                                                                                  | R/W |

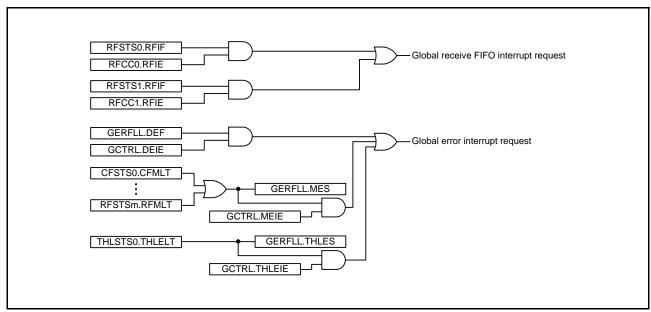

| b8         | DEIE      | DLC Error Interrupt Enable                        | 0: DLC error interrupt is disabled. 1: DLC error interrupt is enabled.                                                                                  | R/W |

| b9         | MEIE      | FIFO Message Lost Interrupt<br>Enable             | FIFO message lost interrupt is disabled.     FIFO message lost interrupt is enabled.                                                                    | R/W |

| b10        | THLEIE    | Transmit History Buffer Overflow Interrupt Enable | Transmit history buffer overflow interrupt is disabled.     Transmit history buffer overflow interrupt is enabled.                                      | R/W |

| b15 to b11 | _         | Reserved                                          | These bits are read as 0. The write value should be 0.                                                                                                  | R/W |

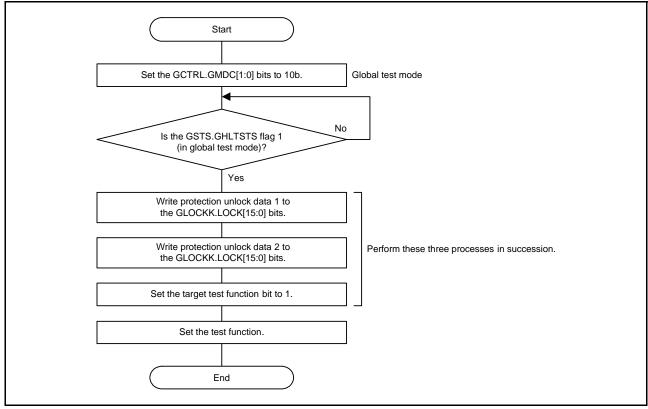

#### GMDC[1:0] Bits (Global Mode Select)

These bits are used to select the mode of entire CAN module (global operating mode, global reset mode, or global test mode). For details, see section 36.3.1, Global Modes. Setting the GSLPR bit to 1 in global reset mode places the CAN module in global stop mode.

#### **GSLPR Bit (Global Stop Mode)**

Setting this bit to 1 places the CAN module in global stop mode.

Setting this bit to 0 makes the CAN module leave from global stop mode.

Do not modify this bit in global operating mode or in global test mode.

#### **DEIE Bit (DLC Error Interrupt Enable)**

When the GERFLL.DEF flag becomes 1 while the DEIE bit is 1, an interrupt request is generated. Modify this bit only in global reset mode.

#### **MEIE Bit (FIFO Message Lost Interrupt Enable)**

When the GERFLL.MES flag becomes 1 while the MEIE bit is 1, an interrupt request is generated. Modify this bit only in global reset mode.

## **THLEIE Bit (Transmit History Buffer Overflow Interrupt Enable)**

When the GERFLL.THLES flag becomes 1 while the THLEIE bit is 1, an interrupt request is generated. Modify this bit only in global reset mode.

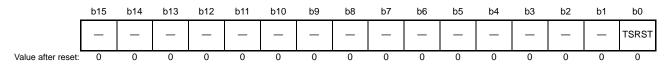

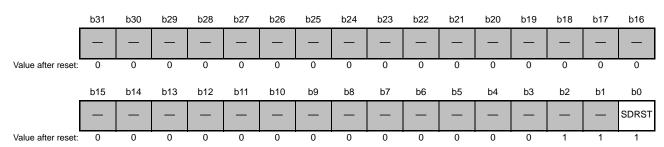

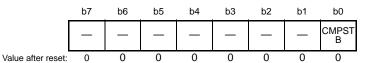

# 36.2.12 Global Control Register H (GCTRH)

Address(es): RSCAN.GCTRH 000A 8328h

| Bit       | Symbol | Bit Name                | Description                                                                     | R/W |

|-----------|--------|-------------------------|---------------------------------------------------------------------------------|-----|

| b0        | TSRST  | Timestamp Counter Reset | Setting the TSRST bit to 1 resets the timestamp counter. This bit is read as 0. | R/W |

| b15 to b1 | _      | Reserved                | These bits are read as 0. The write value should be 0.                          | R/W |

#### **TSRST Bit (Timestamp Counter Reset)**

This bit is used to reset the timestamp counter. When this bit is set to 1, the GTSC register is set to 0000h.

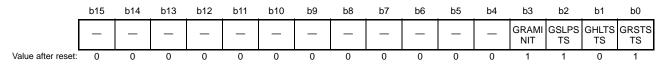

## 36.2.13 Global Status Register (GSTS)

Address(es): RSCAN.GSTS 000A 832Ah

| Bit       | Symbol   | Bit Name                           | Description                                                                 | R/W |

|-----------|----------|------------------------------------|-----------------------------------------------------------------------------|-----|

| b0        | GRSTSTS  | Global Reset Status Flag           | 0: Not in global reset mode 1: In global reset mode                         | R   |

| b1        | GHLTSTS  | Global Test Status Flag            | 0: Not in global test mode 1: In global test mode                           | R   |

| b2        | GSLPSTS  | Global Stop Status Flag            | 0: Not in global stop mode 1: In global stop mode                           | R   |

| b3        | GRAMINIT | CAN RAM Initialization Status Flag | CAN RAM initialization is completed.     CAN RAM initialization is ongoing. | R   |

| b15 to b4 | _        | Reserved                           | These bits are read as 0.                                                   | R   |

## **GRSTSTS Flag (Global Reset Status Flag)**

This flag becomes 1 when the CAN module has transitioned to global reset mode, and becomes 0 when the CAN module has exited global reset mode. This flag remains 1 even when the CAN module has transitioned from global reset mode to global stop mode.

## **GHLTSTS Flag (Global Test Status Flag)**

This flag becomes 1 when the CAN module has transitioned to global test mode, and becomes 0 when the CAN module has exited global test mode.

## **GSLPSTS Flag (Global Stop Status Flag)**

This flag becomes 1 when the CAN module has transitioned to global stop mode, and becomes 0 when the CAN module

has returned from global stop mode.

#### **GRAMINIT Flag (CAN RAM Initialization Status Flag)**

This flag indicates the initialization status of the CAN RAM.

This flag becomes 1 after the CAN module is enabled, and becomes 0 when CAN RAM initialization is completed.

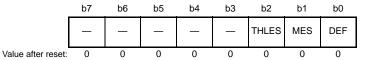

# 36.2.14 Global Error Flag Register (GERFLL)

Address(es): RSCAN.GERFLL 000A 832Ch

| Bit      | Symbol | Bit Name                                        | Description                                                                                        | R/W         |

|----------|--------|-------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------|

| b0       | DEF    | DLC Error Flag                                  | 0: No DLC error is present. 1: A DLC error is present.                                             | R/(W)<br>*1 |

| b1       | MES    | FIFO Message Lost Status Flag                   | 0: No FIFO message lost error is present. 1: A FIFO message lost error is present.                 | R           |

| b2       | THLES  | Transmit History Buffer<br>Overflow Status Flag | No transmit history buffer overflow is present.     A transmit history buffer overflow is present. | R           |

| b7 to b3 | _      | Reserved                                        | The read value is undefined. The write value should be 0.                                          | R/W         |

Note 1. Only 0 can be written to this bit, to clear the flag. Writing 1 does not affect the flag value.

All flags in the GERFLL register become 0 in global reset mode.

## **DEF Flag (DLC Error Flag)**

The DEF flag becomes 1 when an error has been detected during the DLC check. This flag can be set to 0 by writing 0 by the program.

## MES Flag (FIFO Message Lost Status Flag)

The MES flag becomes 1 when any one of the RFSTSm.RFMLT flags or the CFSTS0.CFMLT flag becomes 1. This flag becomes 0 when all RFSTSm.RFMLT flags and the CFSTS0.CFMLT flag are set to 0.

## **THLES Flag (Transmit History Buffer Overflow Status Flag)**

The THLES flag becomes 1 when the THLSTS0.THLELT flag becomes 1.

This flag becomes 0 when the THLSTS0.THLELT flag is set to 0.

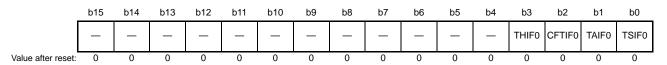

# 36.2.15 Global Transmit Interrupt Status Register (GTINTSTS)

Address(es): RSCAN.GTINTSTS 000A 8388h

| Bit       | Symbol | Bit Name                                              | Description                                                                                                                                 | R/W |

|-----------|--------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0        | TSIF0  | RSCAN0 Transmit Buffer<br>Interrupt Status Flag       | O: No transmit buffer transmit complete interrupt request is present.  1: A transmit buffer transmit complete interrupt request is present. | R   |

| b1        | TAIF0  | RSCAN0 Transmit Buffer Abort<br>Interrupt Status Flag | O: No transmit buffer abort interrupt request is present.  1: A transmit buffer abort interrupt request is present.                         | R   |

| b2        | CFTIF0 | RSCAN0 Transmit/Receive<br>FIFO Interrupt Status Flag | No transmit/receive FIFO transmit interrupt request is present.  1: A transmit/receive FIFO transmit interrupt request is present.          | R   |

| b3        | THIF0  | RSCAN0 Transmit History<br>Interrupt Status Flag      | O: No transmit history interrupt request is present.  1: A transmit history interrupt request is present.                                   | R   |

| b15 to b4 | _      | Reserved                                              | These bits are read as 0.                                                                                                                   | R   |

All flags in the GTINTSTS register become 0 in global reset or channel reset mode.

#### TSIF0 Flag (RSCAN0 Transmit Buffer Interrupt Status Flag)

The TSIF0 flag becomes 1 when the TMIEC.TMIEp bit is set to 1 (enabling interrupts) and the corresponding TMSTSp.TMTRF[1:0] flags become 10b (transmission has been completed without transmit abort request) or 11b (transmission has been completed with transmit abort request).

This flag becomes 0 when all TMSTSp.TMTRF[1:0] flags that satisfy a condition for setting the TSIF0 flag to 1 are set to 00b. This flag also becomes 0 when the TMIEC.TMIEp bit is set to 0.

#### TAIF0 Flag (RSCAN0 Transmit Buffer Abort Interrupt Status Flag)

The TAIF0 flag becomes 1 when the CTRH.TAIE bit is set to 1 (enabling interrupts) and the TMSTSp.TMTRF[1:0] flags become 01b (transmit abort has been completed).

This flag becomes 0 when the TMSTSp.TMTRF[1:0] flags, which indicate that the abort of transmission has been completed, are set to 00b.

## CFTIF0 Flag (RSCAN0 Transmit/Receive FIFO Interrupt Status Flag)

The CFTIF0 flag becomes 1 when the CFCCL0.CFTXIE bit is set to 1 (enabling interrupts) and the CFSTS0.CFTXIF flag becomes 1 (interrupt request present).

This flag becomes 0 when the CFSTS0.CFTXIF flag is set to 0. This flag also becomes 0 when the CFCCL0.CFTXIE bit is set to 0.

## THIF0 Flag (RSCAN0 Transmit History Interrupt Status Flag)

The THIF0 flag becomes 1 when the THLCC0.THLIE bit is set to 1 (enabling interrupts) and the THLSTS0.THLIF flag becomes 1 (interrupt request present).

This flag becomes 0 when the THLSTS0.THLIF flag is set to 0. This flag also becomes 0 when the THLCC0.THLIE bit is set to 0.

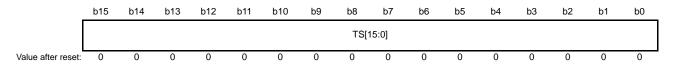

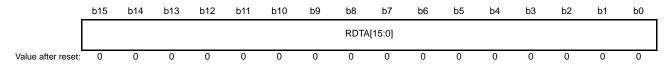

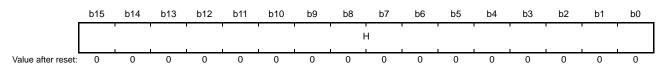

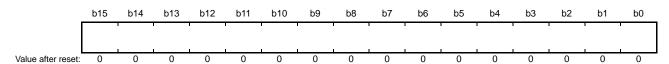

# 36.2.16 Timestamp Register (GTSC)

Address(es): RSCAN.GTSC 000A 832Eh

| Bit       | Symbol   | Description                              | Counter Value  | R/W |

|-----------|----------|------------------------------------------|----------------|-----|

| b15 to b0 | TS[15:0] | The timestamp counter value can be read. | 0000h to FFFFh | R   |

When the TS[15:0] bits are read, the read value shows the timestamp counter (16-bit free-running counter) value at that time. The TS[15:0] value is captured when the SOF is detected and then stored in the receive buffer or the FIFO buffer. The timestamp counter is initialized in global reset mode.

The timestamp counter start timing and stop timing depend on the count source.

- When the GCFGL.TSSS value is 0 (PCLK is selected):

The timestamp counter starts counting when the CAN module has transitioned to global operating mode.

This counter stops counting when the CAN module has transitioned to global stop mode or global test mode.

- When the GCFGL.TSSS value is 1 (CAN bit time clock is selected):

The timestamp counter starts counting when the corresponding channel has transitioned to channel communication mode.

This counter stops counting when the corresponding channel has transitioned to channel reset mode or channel halt mode.

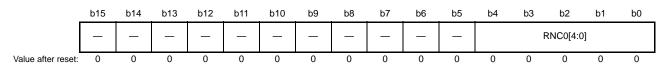

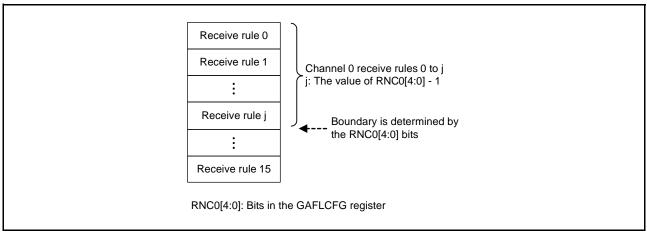

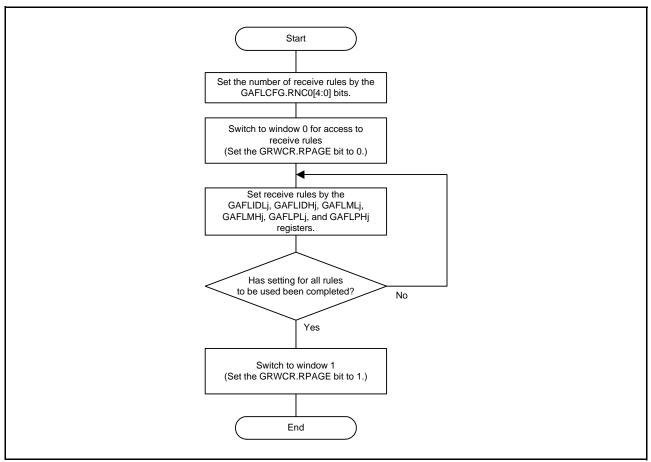

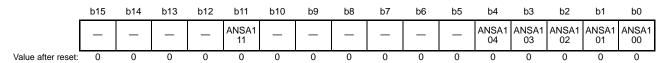

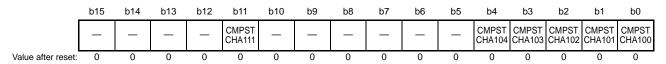

## 36.2.17 Receive Rule Number Configuration Register (GAFLCFG)

Address(es): RSCAN.GAFLCFG 000A 8330h

| Bit       | Symbol    | Bit Name                          | Description                                                                                              | R/W |

|-----------|-----------|-----------------------------------|----------------------------------------------------------------------------------------------------------|-----|

| b4 to b0  | RNC0[4:0] | RSCAN0 Receive Rule Number<br>Set | Set the number of receive rules of channel 0.<br>Set these bits to a value within a range of 00h to 10h. | R/W |

| b15 to b5 | _         | Reserved                          | These bits are read as 0. The write value should be 0.                                                   | R/W |

Modify the GAFLCFG register only in global reset mode.

Up to 16 rules can be registered in the receive rule table.

## RNC0[4:0] Bits (RSCAN0 Receive Rule Number Set)

These bits are used to set the number of rules to be registered in the channel 0 receive rule table. Set these bits to a value within a range of 00h to 10h.

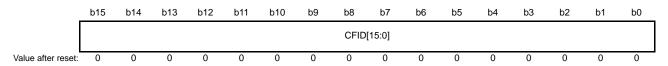

#### Receive Rule Entry Register jAL (GAFLIDLj) (j = 0 to 15) 36.2.18

RSCAN.GAFLIDL0 000A 83A0h, RSCAN.GAFLIDL1 000A 83ACh, RSCAN.GAFLIDL2 000A 83B8h, RSCAN.GAFLIDL3 000A 83C4h, RSCAN.GAFLIDL4 000A 83D0h, RSCAN.GAFLIDL5 000A 83DCh, RSCAN.GAFLIDL6 000A 83E8h, RSCAN.GAFLIDL7 000A 83F4h, RSCAN.GAFLIDL8 000A 8400h, RSCAN.GAFLIDL9 000A 840Ch, RSCAN.GAFLIDL10 000A 8418h, RSCAN.GAFLIDL11 000A 8424h, RSCAN.GAFLIDL12 000A 843Oh, RSCAN.GAFLIDL13 000A 843Ch, RSCAN.GAFLIDL14 000A 8448h, RSCAN.GAFLIDL15 000A 8454h Address(es):

|                    | b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8     | b7      | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|--------------------|-----|-----|-----|-----|-----|-----|----|--------|---------|----|----|----|----|----|----|----|

|                    |     |     |     |     |     |     |    | GAFLII | D[15:0] |    |    |    |    |    |    |    |

| Value after reset: | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0      | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Bit       | Symbol       | Bit Name | Description                                                                                           | R/W |

|-----------|--------------|----------|-------------------------------------------------------------------------------------------------------|-----|

| b15 to b0 | GAFLID[15:0] | ID Set L | Set the ID of the receive rule. For the standard ID, set the ID in b10 to b0 and set b15 to b11 to 0. | R/W |

Modify the GAFLIDLj register only when the GRWCR.RPAGE bit is set to 0 in global reset mode.

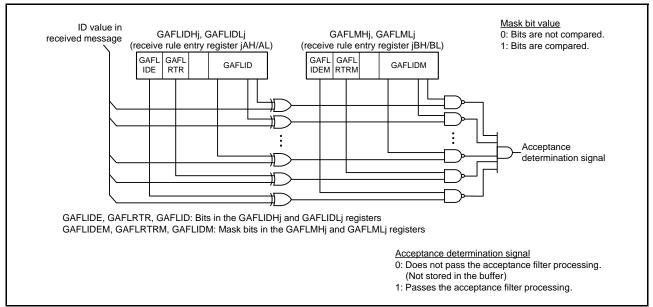

## GAFLID[15:0] Bits (ID Set L)

These bits are used to set the ID field of the receive rule. The ID value set by these bits is compared with the ID in the received message during the acceptance filter processing.

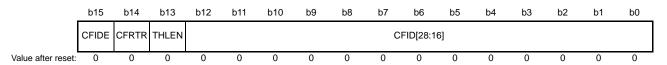

# 36.2.19 Receive Rule Entry Register jAH (GAFLIDHj) (j = 0 to 15)

| Address(es): | RSCAN.GAFLIDH0 000A 83A2h. RSCAN.GAFLIDH1 000A 83AEh. RSCAN.GAFLIDH2 000A 83BAh.    |

|--------------|-------------------------------------------------------------------------------------|

| ,            | RSCAN.GAFLIDH3 000A 83C6h, RSCAN.GAFLIDH4 000A 83D2h, RSCAN.GAFLIDH5 000A 83DEh,    |

|              | RSCAN.GAFLIDH6 000A 83EAh, RSCAN.GAFLIDH7 000A 83F6h, RSCAN.GAFLIDH8 000A 8402h,    |

|              | RSCAN.GAFLIDH9 000A 840Eh, RSCAN.GAFLIDH10 000A 841Ah, RSCAN.GAFLIDH11 000A 8426h,  |

|              | RSCAN.GAFLIDH12 000A 8432h, RSCAN.GAFLIDH13 000A 843Eh, RSCAN.GAFLIDH14 000A 844Ah, |

|              | RSCAN.GAFLIDH15 000A 8456h                                                          |

b15 b14 b13 b12 b11 b10 b8 b7 b6 b5 b4 b3 b2 b1 b0 GAFLI GAFLR GAFLL GAFLID[28:16] TR Value after reset: 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

| Bit       | Symbol        | Bit Name                              | Description                                                                                                           | R/W |

|-----------|---------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|

| b12 to b0 | GAFLID[28:16] | ID Set H                              | Set the ID of the receive rule. For the standard ID, set these bits to 0.                                             | R/W |

| b13       | GAFLLB        | Receive Rule Target Message<br>Select | When a message transmitted from another CAN node is received     When a message transmitted from own node is received | R/W |

| b14       | GAFLRTR       | RTR Select                            | 0: Data frame<br>1: Remote frame                                                                                      | R/W |

| b15       | GAFLIDE       | IDE Select                            | 0: Standard ID<br>1: Extended ID                                                                                      | R/W |

Modify the GAFLIDHj register only when the GRWCR.RPAGE bit is set to 0 in global reset mode.

#### GAFLID[28:16] Bits (ID Set H)

These bits are used to set the ID field of the receive rule. The ID value set by these bits is compared with the ID in the received message during the acceptance filter processing.

## **GAFLLB Bit (Receive Rule Target Message Select)**

When this bit is set to 0, data processing using the receive rule is performed when receiving messages transmitted from another CAN node.

When this bit is set to 1 when the mirror function is used, data processing using the receive rule is performed when receiving messages transmitted from the own CAN node.

#### **GAFLRTR Bit (RTR Select)**

This bit is used to select the frame format (data frame or remote frame) of the receive rule. This bit is compared with the RTR bit in the received message during the acceptance filter processing.

#### **GAFLIDE Bit (IDE Select)**

This bit is used to select the ID format (standard ID or extended ID) of the receive rule. This bit is compared with the IDE bit in the received message during the acceptance filter processing.

#### Receive Rule Entry Register jBL (GAFLMLj) (j = 0 to 15) 36.2.20

RSCAN.GAFLML0 000A 83A4h, RSCAN.GAFLML1 000A 83B0h, RSCAN.GAFLML2 000A 83BCh, RSCAN.GAFLML3 000A 83C8h, RSCAN.GAFLML4 000A 83D4h, RSCAN.GAFLML5 000A 83E0h, RSCAN.GAFLML6 000A 83ECh, RSCAN.GAFLML7 000A 83F8h, RSCAN.GAFLML8 000A 8404h, RSCAN.GAFLML9 000A 8410h, RSCAN.GAFLML10 000A 841Ch, RSCAN.GAFLML11 000A 8428h, RSCAN.GAFLML12 000A 8434h, RSCAN.GAFLML13 000A 8440h, RSCAN.GAFLML14 000A 844Ch, RSCAN.GAFLML15 000A 8458h Address(es):

|                    | b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8     | b7      | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|--------------------|-----|-----|-----|-----|-----|-----|----|--------|---------|----|----|----|----|----|----|----|

|                    |     |     |     |     |     |     |    | GAFLID | M[15:0] |    |    |    |    |    |    |    |

| Value after reset: | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0      | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Bit       | Symbol        | Bit Name  | Description                                                                                                     | R/W |

|-----------|---------------|-----------|-----------------------------------------------------------------------------------------------------------------|-----|

| b15 to b0 | GAFLIDM[15:0] | ID Mask L | <ul><li>0: The corresponding ID bit is not compared.</li><li>1: The corresponding ID bit is compared.</li></ul> | R/W |

Modify the GAFLMLj register only when the GRWCR.RPAGE bit is set to 0 in global reset mode.

## GAFLIDM[15:0] Bits (ID Mask L)

These bits are used to mask the corresponding ID bit of the receive rule.

# 36.2.21 Receive Rule Entry Register jBH (GAFLMHj) (j = 0 to 15)

Address(es):

RSCAN.GAFLMH0 000A 83A6h, RSCAN.GAFLMH1 000A 83B2h, RSCAN.GAFLMH2 000A 83BEh, RSCAN.GAFLMH3 000A 83CAh, RSCAN.GAFLMH4 000A 83D6h, RSCAN.GAFLMH5 000A 83E2h, RSCAN.GAFLMH6 000A 83EEh, RSCAN.GAFLMH7 000A 83FAh, RSCAN.GAFLMH8 000A 8406h, RSCAN.GAFLMH9 000A 8412h, RSCAN.GAFLMH10 000A 841Eh, RSCAN.GAFLMH11 000A 842Ah, RSCAN.GAFLMH12 000A 8436h, RSCAN.GAFLMH13 000A 8442h, RSCAN.GAFLMH15 000A 845Ah

|                    | b15          | b14          | b13 | b12 | b11 | b10 | b9 | b8 | b7  | b6       | b5    | b4 | b3 | b2 | b1 | b0 |

|--------------------|--------------|--------------|-----|-----|-----|-----|----|----|-----|----------|-------|----|----|----|----|----|

|                    | GAFLI<br>DEM | GAFLR<br>TRM |     |     |     |     |    |    | GAF | FLIDM[28 | 3:16] |    |    |    |    |    |

| Value after reset: | 0            | 0            | 0   | 0   | 0   | 0   | 0  | 0  | 0   | 0        | 0     | 0  | 0  | 0  | 0  | 0  |

| Bit       | Symbol         | Bit Name  | Description                                                                         | R/W |

|-----------|----------------|-----------|-------------------------------------------------------------------------------------|-----|

| b12 to b0 | GAFLIDM[28:16] | ID Mask H | The corresponding ID bit is not compared.     The corresponding ID bit is compared. | R/W |

| b13       | _              | Reserved  | This bit is read as 0. The write value should be 0.                                 | R/W |

| b14       | GAFLRTRM       | RTR Mask  | 0: The RTR bit is not compared. 1: The RTR bit is compared                          | R/W |

| b15       | GAFLIDEM       | IDE Mask  | 0: The IDE bit is not compared. 1: The IDE bit is compared.                         | R/W |

Modify the GAFLMHj register only when the GRWCR.RPAGE bit is set to 0 in global reset mode.

#### GAFLIDM[28:16] Bits (ID Mask H)

These bits are used to mask the corresponding ID bit of the receive rule.

#### **GAFLRTRM Bit (RTR Mask)**

This bit is used to mask the RTR bit of the receive rule.

## **GAFLIDEM Bit (IDE Mask)**

When this bit is set to 1, filter processing is performed only for messages of the ID format specified by the GAFLIDHj.GAFLIDE bit.

When this bit is set to 0, it is regarded that all received messages have matched the specified ID format. To set the GAFLIDEM bit to 0, set the GAFLMHj.GAFLIDM[28:16] bits and the GAFLMLj.GAFLIDM[15:0] bits to all 0s.

#### Receive Rule Entry Register jCL (GAFLPLj) (j = 0 to 15) 36.2.22

RSCAN.GAFLPL0 000A 83A8h, RSCAN.GAFLPL1 000A 83B4h, RSCAN.GAFLPL2 000A 83C0h, RSCAN.GAFLPL3 000A 83CCh, RSCAN.GAFLPL4 000A 83D8h, RSCAN.GAFLPL5 000A 83E4h,

RSCAN.GAFLPL6 000A 83F0h, RSCAN.GAFLPL7 000A 83D0h, RSCAN.GAFLPL8 000A 8408h, RSCAN.GAFLPL9 000A 8414h, RSCAN.GAFLPL10 000A 8420h, RSCAN.GAFLPL11 000A 8420h, RSCAN.GAFLPL12 000A 8438h, RSCAN.GAFLPL13 000A 8444h, RSCAN.GAFLPL14 000A 8450h, RSCAN.GAFLPL15 000A 845Ch

|                    | b15         | b14 | b13 | b12 | b11   | b10   | b9 | b8 | b7 | b6 | b5 | b4           | b3 | b2 | b1           | b0           |  |

|--------------------|-------------|-----|-----|-----|-------|-------|----|----|----|----|----|--------------|----|----|--------------|--------------|--|

|                    | GAFLR<br>MV |     |     | GAF | LRMDP | [6:0] |    |    | 1  |    | _  | GAFLF<br>DP4 |    |    | GAFLF<br>DP1 | GAFLF<br>DP0 |  |

| Value after reset: | 0           | 0   | 0   | 0   | 0     | 0     | 0  | 0  | 0  | 0  | 0  | 0            | 0  | 0  | 0            | 0            |  |

| Bit       | Symbol        | Bit Name                                        | Description                                                                                               | R/W |

|-----------|---------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|

| b0        | GAFLFDP0      | Receive FIFO Buffer Select 0                    | 0: Not select a receive FIFO buffer 0 1: Select a receive FIFO buffer 0                                   | R/W |

| b1        | GAFLFDP1      | Receive FIFO Buffer Select 1                    | 0: Not select a receive FIFO buffer 1 1: Select a receive FIFO buffer 1                                   | R/W |

| b3, b2    | _             | Reserved                                        | These bits are read as 0. The write value should be 0.                                                    | R/W |

| b4        | GAFLFDP4      | RSCAN0 Transmit/Receive<br>FIFO Buffer Select 0 | 0: Not select an RSCAN0 transmit/receive FIFO buffer 0 1: Select an RSCAN0 transmit/receive FIFO buffer 0 | R/W |

| b7 to b5  | _             | Reserved                                        | These bits are read as 0. The write value should be 0.                                                    | R/W |

| b14 to b8 | GAFLRMDP[6:0] | Receive Buffer Number Select                    | Set the receive buffer number to store receive messages.                                                  | R/W |

| b15       | GAFLRMV       | Receive Buffer Enable                           | 0: No receive buffer is used. 1: A receive buffer is used.                                                | R/W |

Modify the GAFLPLj register only when the GRWCR.RPAGE bit is set to 0 in global reset mode.

# GAFLFDP0 Bit (Receive FIFO Buffer Select 0), **GAFLFDP1** Bit (Receive FIFO Buffer Select 1), GAFLFDP4 Bit (RSCAN0 Transmit/Receive FIFO Buffer Select 0)

These bits are used to specify FIFO buffers that store receive messages that have passed through the filter. Up to two FIFO buffers are selectable. However, when the GAFLPLj.GAFLRMV bit is set to 1 (a receive buffer is used), up to one FIFO buffer is selectable. Only receive FIFO buffers and the transmit/receive FIFO buffer for which the CFCCH0.CFM[1:0] bits are set to 00b (receive mode) are selectable.

#### GAFLRMDP[6:0] Bits (Receive Buffer Number Select)

These bits are used to select the number of the receive buffer that stores receive messages that have passed through the filter when the GAFLRMV bit is set to 1. Set these bits to a value smaller than the value set by the RMNB.NRXMB[4:0] bits.

#### **GAFLRMV Bit (Receive Buffer Enable)**

When this bit is set to 1, receive messages that have passed through the filter are stored in the receive buffer selected by the GAFLRMDP[6:0] bits.

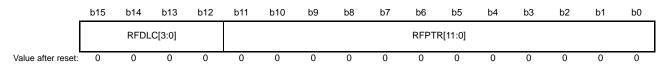

#### 36.2.23 Receive Rule Entry Register jCH (GAFLPHj) (j = 0 to 15)

RSCAN.GAFLPH0 000A 83AAh, RSCAN.GAFLPH1 000A 83B6h, RSCAN.GAFLPH2 000A 83C2h, RSCAN.GAFLPH3 000A 83CEh, RSCAN.GAFLPH4 000A 83DAh, RSCAN.GAFLPH5 000A 83E6h, RSCAN.GAFLPH6 000A 83F2h, RSCAN.GAFLPH7 000A 83FEh, RSCAN.GAFLPH8 000A 840Ah, RSCAN.GAFLPH9 000A 8416h, RSCAN.GAFLPH10 000A 8422h, RSCAN.GAFLPH11 000A 842Eh, RSCAN.GAFLPH12 000A 843Ah, RSCAN.GAFLPH13 000A 8446h, RSCAN.GAFLPH14 000A 8452h, RSCAN.GAFLPH14 000A 845Eh, RSCAN.GAFLPH18 000A 845Eh, RSCA

RSCAN.GAFLPH15 000A 845Eh

|                    | b15 | b14   | b13     | b12 | b11 | b10 | b9 | b8 | b7 | b6    | b5       | b4 | b3 | b2 | b1 | b0 |

|--------------------|-----|-------|---------|-----|-----|-----|----|----|----|-------|----------|----|----|----|----|----|

|                    |     | GAFLD | LC[3:0] |     |     |     |    |    |    | GAFLP | ΓR[11:0] |    |    |    |    |    |

| Value after reset: | 0   | 0     | 0       | 0   | 0   | 0   | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  | 0  | 0  |

| Bit        | Symbol        | Bit Name           | Description                                                                                                                                                                                                                                                                                          | R/W |

|------------|---------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b11 to b0  | GAFLPTR[11:0] | Receive Rule Label | Set the 12-bit label information.                                                                                                                                                                                                                                                                    | R/W |

| b15 to b12 | GAFLDLC[3:0]  | Receive Rule DLC   | b15 b12 0 0 0 0:0 or more data bytes (DLC check is disabled) 0 0 0 1:1 or more data bytes 0 0 1 0:2 or more data bytes 0 0 1 1:3 or more data bytes 0 1 0 0:4 or more data bytes 0 1 0 1:5 or more data bytes 0 1 1 0:6 or more data bytes 0 1 1 1:7 or more data bytes 1 x x x:8 or more data bytes | R/W |

x: Don't care

Modify the GAFLPHj register only when the GRWCR.RPAGE bit is set to 0 in global reset mode.

## GAFLPTR[11:0] Bits (Receive Rule Label)

These bits are used to set a 12-bit label to be attached to messages that have passed through the filter. A label is attached when a message is stored in the receive buffer or the FIFO buffer.

## GAFLDLC[3:0] Bits (Receive Rule DLC)

These bits are used to set the minimum data length necessary for receiving messages. If the data length of a message that is being filtered is equal to or larger than the value set by the GAFLDLC[3:0] bits, the message passes the DLC check. Setting these bits to 0000b disables the DLC check function allowing messages with any data length to pass the DLC check.

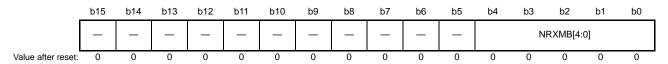

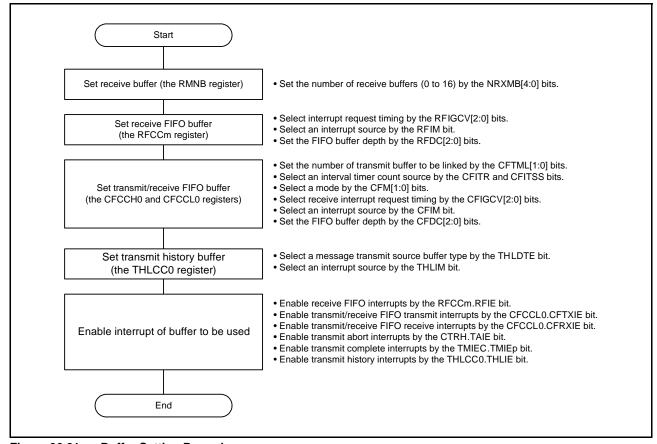

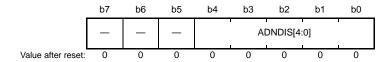

# 36.2.24 Receive Buffer Number Configuration Register (RMNB)

Address(es): RSCAN.RMNB 000A 8332h

| Bit       | Symbol     | Bit Name                            | Description                                                   | R/W |

|-----------|------------|-------------------------------------|---------------------------------------------------------------|-----|

| b4 to b0  | NRXMB[4:0] | Receive Buffer Number Configuration | Set the number of receive buffers.<br>Set a value of 0 to 16. | R/W |

| b15 to b5 | _          | Reserved                            | These bits are read as 0. The write value should be 0.        | R/W |

Modify the RMNB register only in global reset mode.

#### NRXMB[4:0] Bits (Receive Buffer Number Configuration)

These bits are used to set the total number of receive buffers of the CAN module. The maximum value is 16. Setting these bits to all 0s makes receive buffers unavailable.

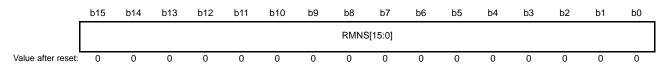

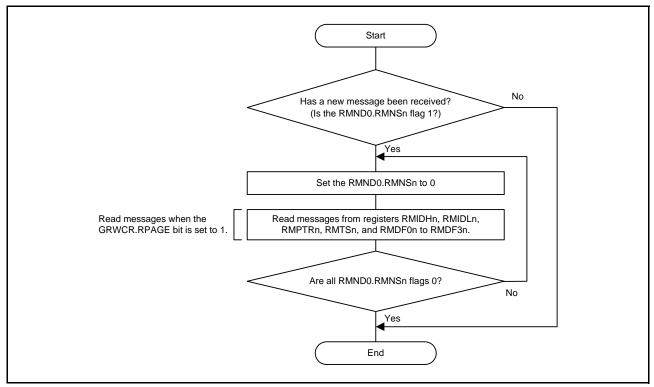

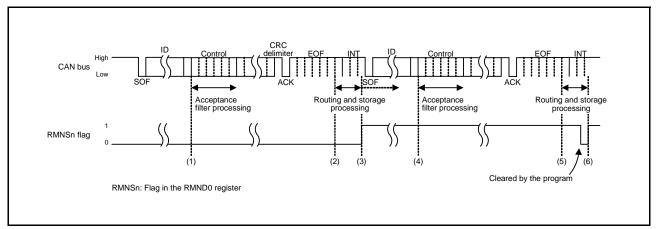

## 36.2.25 Receive Buffer Receive Complete Flag Register (RMND0)

Address(es): RSCAN.RMND0 000A 8334h

| Bit       | Symbol     | Bit Name                                  | Description                                                                                                                      | R/W |

|-----------|------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| b15 to b0 | RMNS[15:0] | Receive Buffer Receive<br>Complete Flag n | <ul><li>0: Receive buffer n contains no new message (n = 0 to 15).</li><li>1: Receive buffer n contains a new message.</li></ul> | R/W |

Write 0 to the RMND0 register in global operating mode or global test mode.

#### RMNS[15:0] Flags (Receive Buffer Receive Complete Flag n)

Each of the RMNS[15:0] flags becomes 1 when the processing for storing a message in the corresponding receive buffer starts.

To set these flags to 0, write 0 to the corresponding flag by the program. In this case, write this register in 16-bit unit to ensure that only the specified bit is set to 0 and the other bits are set to 1. These bits cannot be set to 0 while a message is being stored. It takes time of 10 clock cycles of PCLK for storing a message.

These flags become 0 in global reset mode.

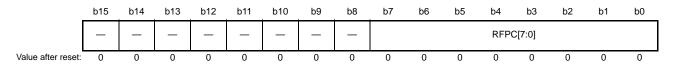

#### Receive Buffer Register nAL (RMIDLn) (n = 0 to 15) 36.2.26

RSCAN.RMIDL0 000A 83A0h, RSCAN.RMIDL1 000A 83B0h, RSCAN.RMIDL2 000A 83C0h, RSCAN.RMIDL3 000A 83D0h, RSCAN.RMIDL4 000A 83E0h, RSCAN.RMIDL5 000A 83F0h, RSCAN.RMIDL6 000A 8400h, RSCAN.RMIDL7 000A 8410h, RSCAN.RMIDL8 000A 8420h, RSCAN.RMIDL9 000A 8430h, RSCAN.RMIDL10 000A 8440h, RSCAN.RMIDL11 000A 8450h, RSCAN.RMIDL12 000A 8450h, RSCAN.RMIDL13 000A 8470h, RSCAN.RMIDL14 000A 8480h, RSCAN.RMIDL15 000A 8490h Address(es):

|                    | b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8   | b7     | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|--------------------|-----|-----|-----|-----|-----|-----|----|------|--------|----|----|----|----|----|----|----|

|                    |     |     |     |     |     |     |    | RMID | [15:0] |    |    |    |    |    |    |    |

| Value after reset: | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0    | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Bit       | Symbol     | Bit Name                 | Description                                                                                                                      | R/W |

|-----------|------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| b15 to b0 | RMID[15:0] | Receive Buffer ID Data L | The standard ID or extended ID of received message can be read.  Read bits 10 to 0 for standard ID. Bits 15 to 11 are read as 0. | R   |

This register can be read when the GRWCR.RPAGE bit is 1.

## RMID[15:0] Bits (Receive Buffer ID Data L)

These bits indicate the ID of the message stored in the receive buffer.

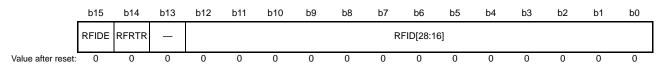

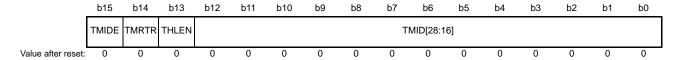

# 36.2.27 Receive Buffer Register nAH (RMIDHn) (n = 0 to 15)

Address(es): RS

RSCAN.RMIDH0 000A 83A2h, RSCAN.RMIDH1 000A 83B2h, RSCAN.RMIDH2 000A 83C2h, RSCAN.RMIDH3 000A 83D2h, RSCAN.RMIDH4 000A 83E2h, RSCAN.RMIDH5 000A 83F2h, RSCAN.RMIDH6 000A 8402h, RSCAN.RMIDH7 000A 8412h, RSCAN.RMIDH8 000A 8422h, RSCAN.RMIDH9 000A 8432h, RSCAN.RMIDH10 000A 8432h, RSCAN.RMIDH10 000A 8432h, RSCAN.RMIDH11 000A 8452h, RSCAN.RMIDH12 000A 8462h, RSCAN.RMIDH13 000A 8472h, RSCAN.RMIDH14 000A 8482h, RSCAN.RMIDH15 000A 8492h

|                    | b15   | b14       | b13 | b12 | b11 | b10 | b9 | b8 | b7 | b6       | b5 | b4 | b3 | b2 | b1 | b0 |

|--------------------|-------|-----------|-----|-----|-----|-----|----|----|----|----------|----|----|----|----|----|----|

|                    | RMIDE | RMRT<br>R | _   |     |     |     |    |    | R  | MID[28:1 | 6] |    |    |    |    |    |

| Value after reset: | 0     | 0         | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0        | 0  | 0  | 0  | 0  | 0  | 0  |

| Bit       | Symbol      | Bit Name                 | Description                                                                                                 | R/W |

|-----------|-------------|--------------------------|-------------------------------------------------------------------------------------------------------------|-----|

| b12 to b0 | RMID[28:16] | Receive Buffer ID Data H | The standard ID or extended ID of received message can be read.  For standard ID, these bits are read as 0. | R   |

| b13       | _           | Reserved                 | This bit is read as 0.                                                                                      | R   |

| b14       | RMRTR       | Receive Buffer RTR       | 0: Data frame<br>1: Remote frame                                                                            | R   |

| b15       | RMIDE       | Receive Buffer IDE       | 0: Standard ID<br>1: Extended ID                                                                            | R   |

This register can be read when the GRWCR.RPAGE bit is 1.

#### RMID[28:16] Bits (Receive Buffer ID Data H)

These bits indicate the ID of the message stored in the receive buffer.

#### RMRTR Bit (Receive Buffer RTR)

This bit indicates the frame format (data frame or remote frame) of the message stored in the receive buffer.

#### RMIDE Bit (Receive Buffer IDE)

This bit indicates the ID format (standard ID or extended ID) of the message stored in the receive buffer.

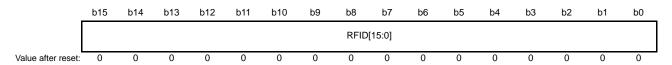

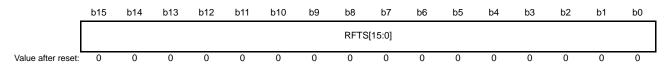

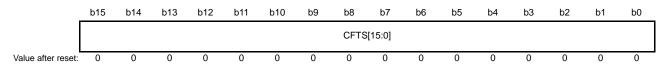

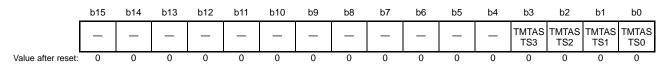

#### Receive Buffer Register nBL (RMTSn) (n = 0 to 15) 36.2.28

RSCAN.RMTS0 000A 83A4h, RSCAN.RMTS1 000A 83B4h, RSCAN.RMTS2 000A 83C4h, RSCAN.RMTS3 000A 83D4h, RSCAN.RMTS4 000A 83E4h, RSCAN.RMTS5 000A 83F4h, RSCAN.RMTS6 000A 8404h, RSCAN.RMTS7 000A 8414h, RSCAN.RMTS8 000A 8424h, RSCAN.RMTS9 000A 8434h, RSCAN.RMTS10 000A 8444h, RSCAN.RMTS11 000A 8454h, RSCAN.RMTS12 000A 8464h, RSCAN.RMTS13 000A 8474h, RSCAN.RMTS14 000A 8484h, RSCAN.RMTS15 000A 8494h Address(es):

| _                  | b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8   | b7     | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|--------------------|-----|-----|-----|-----|-----|-----|----|------|--------|----|----|----|----|----|----|----|

|                    |     |     |     |     |     |     |    | RMTS | [15:0] |    |    |    |    |    |    |    |

| Value after reset: | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0    | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Bit       | Symbol     | Bit Name                      | Description                                          | R/W |

|-----------|------------|-------------------------------|------------------------------------------------------|-----|

| b15 to b0 | RMTS[15:0] | Receive Buffer Timestamp Data | Timestamp value of the received message can be read. | R   |

This register can be read when the GRWCR.RPAGE bit is 1.

## RMTS[15:0] Bits (Receive Buffer Timestamp Data)

These bits indicate the timestamp value of the message stored in the receive buffer.

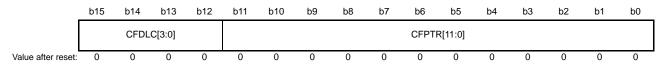

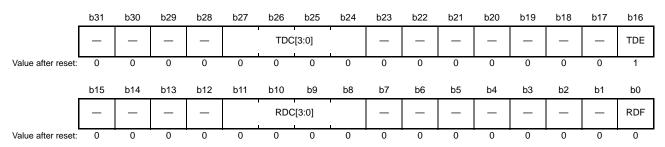

#### Receive Buffer Register nBH (RMPTRn) (n = 0 to 15) 36.2.29