Table 33.15 Maximum Bit Rate for Each Operating Frequency (Asynchronous Mode)

|               | SEMR Settings |             |   |   |                        |               | SEMR S      | Settings    |   |   |                           |  |

|---------------|---------------|-------------|---|---|------------------------|---------------|-------------|-------------|---|---|---------------------------|--|

| PCLK<br>(MHz) | BGDM<br>Bit   | ABCS<br>Bit | n | N | Maximum Bit Rate (bps) | PCLK<br>(MHz) | BGDM<br>Bit | ABCS<br>Bit | n | N | Maximum Bit Rate<br>(bps) |  |

| 8             | 0             | 0           | 0 | 0 | 250000                 | 17.2032       | 0           | 0           | 0 | 0 | 537600                    |  |

|               |               | 1           | 0 | 0 | 500000                 | _             |             | 1           | 0 | 0 | 1075200                   |  |

|               | 1             | 0           | 0 | 0 | -                      |               | 1           | 0           | 0 | 0 | _                         |  |

|               |               | 1           | 0 | 0 | 1000000                | _             |             | 1           | 0 | 0 | 2150400                   |  |

| 9.8304        | 0             | 0           | 0 | 0 | 307200                 | 18            | 0           | 0           | 0 | 0 | 562500                    |  |

|               |               | 1           | 0 | 0 | 614400                 | _             |             | 1           | 0 | 0 | 1125000                   |  |

|               | 1             | 0           | 0 | 0 | -                      |               | 1           | 0           | 0 | 0 | _                         |  |

|               |               | 1           | 0 | 0 | 1228800                | _             |             | 1           | 0 | 0 | 2250000                   |  |

| 10            | 0             | 0           | 0 | 0 | 312500                 | 19.6608       | 0           | 0           | 0 | 0 | 614400                    |  |

|               |               | 1           | 0 | 0 | 625000                 | _             |             | 1           | 0 | 0 | 1228800                   |  |

|               | 1             | 0           | 0 | 0 | -                      |               | 1           | 0           | 0 | 0 | _                         |  |

|               |               | 1           | 0 | 0 | 1250000                | _             |             | 1           | 0 | 0 | 2457600                   |  |

| 12            | 0             | 0           | 0 | 0 | 375000                 | 20            | 0           | 0           | 0 | 0 | 625000                    |  |

|               |               | 1           | 0 | 0 | 750000                 | _             |             | 1           | 0 | 0 | 1250000                   |  |

|               | 1             | 0           | 0 | 0 | -                      |               | 1           | 0           | 0 | 0 | _                         |  |

|               |               | 1           | 0 | 0 | 1500000                | _             |             | 1           | 0 | 0 | 2500000                   |  |

| 12.288        | 0             | 0           | 0 | 0 | 384000                 | 25            | 0           | 0           | 0 | 0 | 781250                    |  |

|               |               | 1           | 0 | 0 | 768000                 | _             |             | 1           | 0 | 0 | 1562500                   |  |

|               | 1             | 0           | 0 | 0 | -                      |               | 1           | 0           | 0 | 0 | _                         |  |

|               |               | 1           | 0 | 0 | 1536000                | _             |             | 1           | 0 | 0 | 3125000                   |  |

| 14            | 0             | 0           | 0 | 0 | 437500                 | 30            | 0           | 0           | 0 | 0 | 937500                    |  |

|               |               | 1           | 0 | 0 | 875000                 | _             |             | 1           | 0 | 0 | 1875000                   |  |

|               | 1             | 0           | 0 | 0 | _                      |               | 1           | 0           | 0 | 0 | =                         |  |

|               |               | 1           | 0 | 0 | 1750000                | _             |             | 1           | 0 | 0 | 3750000                   |  |

| 16            | 0             | 0           | 0 | 0 | 500000                 | _             |             |             |   |   |                           |  |

|               |               | 1           | 0 | 0 | 1000000                | _             |             |             |   |   |                           |  |

|               | 1             | 0           | 0 | 0 | -                      |               |             |             |   |   |                           |  |

|               |               | 1           | 0 | 0 | 2000000                | _             |             |             |   |   |                           |  |

Table 33.16 Maximum Bit Rate with External Clock Input (Asynchronous Mode)

|            |                            | Maximum Bit Rate (bp | os)               |

|------------|----------------------------|----------------------|-------------------|

| PCLK (MHz) | External Input Clock (MHz) | SEMR.ABCS Bit = 0    | SEMR.ABCS Bit = 1 |

| 8          | 2.0000                     | 125000               | 250000            |

| 9.8304     | 2.4576                     | 153600               | 307200            |

| 10         | 2.5000                     | 156250               | 312500            |

| 12         | 3.0000                     | 187500               | 375000            |

| 12.288     | 3.0720                     | 192000               | 384000            |

| 14         | 3.5000                     | 218750               | 437500            |

| 16         | 4.0000                     | 250000               | 500000            |

| 17.2032    | 4.3008                     | 268800               | 537600            |

| 18         | 4.5000                     | 281250               | 562500            |

| 19.6608    | 4.9152                     | 307200               | 614400            |

| 20         | 5.0000                     | 312500               | 625000            |

| 25         | 6.2500                     | 390625               | 781250            |

| 30         | 7.5000                     | 468750               | 937500            |

Table 33.17 Maximum Bit Rate with TMR Clock Input (Asynchronous Mode)

|            |                 | Maximum Bit Rate (bp | os)               |

|------------|-----------------|----------------------|-------------------|

| PCLK (MHz) | TMR Clock (MHz) | SEMR.ABCS Bit = 0    | SEMR.ABCS Bit = 1 |

| 8          | 4               | 250000               | 500000            |

| 9.8304     | 4.9152          | 307200               | 614400            |

| 10         | 5               | 312500               | 625000            |

| 12         | 6               | 375000               | 750000            |

| 12.288     | 6.144           | 384000               | 768000            |

| 14         | 7               | 437500               | 875000            |

| 16         | 8               | 500000               | 1000000           |

| 17.2032    | 8.6016          | 537600               | 1075200           |

| 18         | 9               | 562500               | 1125000           |

| 19.6608    | 9.8304          | 614400               | 1228800           |

| 20         | 10              | 625000               | 1250000           |

| 25         | 12.5            | 781250               | 1562500           |

| 30         | 15              | 937500               | 1875000           |

Table 33.18 BRR Settings for Various Bit Rates (Clock Synchronous Mode, Simple SPI Mode)

|                | Operating Frequency PCLK (MHz) |     |    |     |   |     |   |     |   |     |   |     |  |

|----------------|--------------------------------|-----|----|-----|---|-----|---|-----|---|-----|---|-----|--|

|                | 8                              |     | 10 |     |   | 16  |   | 20  | : | 25  |   | 30  |  |

| Bit Rate (bps) | n                              | N   | n  | N   | n | N   | n | N   | n | N   | n | N   |  |

| 110            |                                |     |    |     |   |     |   |     |   |     |   |     |  |

| 250            | 3                              | 124 | 3  | 155 | 3 | 249 |   |     |   |     |   |     |  |

| 500            | 2                              | 249 | 3  | 77  | 3 | 124 | 3 | 155 | 3 | 194 | 3 | 233 |  |

| 1 k            | 2                              | 124 | 2  | 155 | 2 | 249 | 3 | 77  | 3 | 97  | 3 | 116 |  |

| 2.5 k          | 1                              | 199 | 1  | 249 | 2 | 99  | 2 | 124 | 2 | 155 | 2 | 187 |  |

| 5 k            | 1                              | 99  | 1  | 124 | 1 | 199 | 1 | 249 | 2 | 77  | 2 | 93  |  |

| 10 k           | 0                              | 199 | 0  | 249 | 1 | 99  | 1 | 124 | 1 | 155 | 1 | 187 |  |

| 25 k           | 0                              | 79  | 0  | 99  | 0 | 159 | 0 | 199 | 0 | 249 | 1 | 74  |  |

| 50 k           | 0                              | 39  | 0  | 49  | 0 | 79  | 0 | 99  | 0 | 124 | 0 | 149 |  |

| 100 k          | 0                              | 19  | 0  | 24  | 0 | 39  | 0 | 49  | 0 | 62  | 0 | 74  |  |

| 250 k          | 0                              | 7   | 0  | 9   | 0 | 15  | 0 | 19  | 0 | 24  | 0 | 29  |  |

| 500 k          | 0                              | 3   | 0  | 4   | 0 | 7   | 0 | 9   | _ | _   | 0 | 14  |  |

| 1 M            | 0                              | 1   |    |     | 0 | 3   | 0 | 4   | _ | _   |   |     |  |

| 2 M            | 0                              | 0*1 |    |     | 0 | 1   |   |     | _ | _   |   |     |  |

| 2.5 M          |                                |     | 0  | 0*1 |   |     | 0 | 1   |   |     | 0 | 2   |  |

| 4 M            |                                |     |    |     | 0 | 0*1 |   |     |   |     |   |     |  |

| 5 M            |                                |     |    |     |   |     | 0 | 0*1 |   |     |   |     |  |

| 6.25 M         |                                |     |    |     |   |     |   |     | 0 | 0*1 |   |     |  |

| 7.5 M          |                                |     |    |     |   |     |   |     |   |     | 0 | 0*1 |  |

Blank cell: Cannot be set since the bit rate error exceeds 5%.

Note 1. Continuous transmission or reception is not possible. After transmitting/receiving one frame of data, there is an interval of a 1-bit period before starting transmitting/receiving the next frame of data. The output of the synchronization clock is stopped for a 1-bit period. For this reason, it takes 9 bits worth of time to transfer one frame (8 bits) of data, and the average transfer rate is 8/9 times the bit rate.

Table 33.19 Maximum Bit Rate with External Clock Input (Clock Synchronous Mode, Simple SPI Mode)

| PCLK (MHz) | External Input Clock (MHz) | Maximum Bit Rate (Mbps) |

|------------|----------------------------|-------------------------|

| 8          | 1.3333                     | 1.3333                  |

| 10         | 1.6667                     | 1.6667                  |

| 12         | 2.0000                     | 2.0000                  |

| 14         | 2.3333                     | 2.3333                  |

| 16         | 2.6667                     | 2.6667                  |

| 18         | 3.0000                     | 3.0000                  |

| 20         | 3.3333                     | 3.3333                  |

| 25         | 4.1667                     | 4.1667                  |

| 30         | 5.0000                     | 5.0000                  |

<sup>—:</sup> Can be set, but a bit rate error of 1 to 5% will occur.

Table 33.20 BRR Settings for Various Bit Rates (Smart Card Interface Mode, n = 0, S = 372)

| Bit Rate (bps) | PCLK (MHz) | n | N | Error (%) |

|----------------|------------|---|---|-----------|

| 9600           | 7.1424     | 0 | 0 | 0.00      |

|                | 10.00      | 0 | 1 | -30.00    |

|                | 10.7136    | 0 | 1 | -25.00    |

|                | 13.00      | 0 | 1 | -8.99     |

|                | 14.2848    | 0 | 1 | 0.00      |

|                | 16.00      | 0 | 1 | 12.01     |

|                | 18.00      | 0 | 2 | -15.99    |

|                | 20.00      | 0 | 2 | -6.66     |

|                | 25.00      | 0 | 3 | -12.49    |

|                | 30.00      | 0 | 3 | 5.01      |

Table 33.21 Maximum Bit Rate for Each Operating Frequency (Smart Card Interface Mode, S = 32)

| PCLK (MHz) | Maximum Bit Rate (bps) | n | N |

|------------|------------------------|---|---|

| 10.00      | 156250                 | 0 | 0 |

| 10.7136    | 167400                 | 0 | 0 |

| 13.00      | 203125                 | 0 | 0 |

| 16.00      | 250000                 | 0 | 0 |

| 18.00      | 281250                 | 0 | 0 |

| 20.00      | 312500                 | 0 | 0 |

| 25.00      | 390625                 | 0 | 0 |

| 30.00      | 468750                 | 0 | 0 |

Table 33.22 BRR Settings for Various Bit Rates (Simple I<sup>2</sup>C Mode)

|          |   | Operating Frequency PCLK (MHz) |           |    |    |           |    |    |           |    |    |           |    |    |           |

|----------|---|--------------------------------|-----------|----|----|-----------|----|----|-----------|----|----|-----------|----|----|-----------|

| Bit Rate | 8 |                                |           | 10 |    |           | 16 |    |           | 20 |    |           | 25 |    |           |

| (bps)    | n | N                              | Error (%) | n  | N  | Error (%) | n  | N  | Error (%) | n  | N  | Error (%) | n  | N  | Error (%) |

| 10 k     | 0 | 24                             | 0.0       | 0  | 31 | -2.3      | 1  | 12 | -3.8      | 1  | 15 | -2.3      | 1  | 19 | -2.3      |

| 25 k     | 0 | 9                              | 0.0       | 0  | 12 | -3.8      | 1  | 4  | 0.0       | 1  | 6  | -10.7     | 1  | 7  | -2.3      |

| 50 k     | 0 | 4                              | 0.0       | 0  | 6  | -10.7     | 1  | 2  | -16.7     | 1  | 3  | -21.9     | 1  | 3  | -2.3      |

| 100 k    | 0 | 2                              | -16.7     | 0  | 3  | -21.9     | 0  | 4  | 0.0       | 0  | 6  | -10.7     | 1  | 1  | -2.3      |

| 250 k    | 0 | 0                              | 0.0       | 0  | 1  | -37.5     | 0  | 1  | 0.0       | 0  | 2  | -16.7     | 0  | 3  | -21.9     |

| 350 k    |   |                                |           |    |    |           |    |    |           | 0  | 1  | -10.7     | 0  | 2  | -25.6     |

|          | Operating Frequency<br>PCLK (MHz) |    |           |  |  |  |  |

|----------|-----------------------------------|----|-----------|--|--|--|--|

| Bit Rate | 30                                |    |           |  |  |  |  |

| (bps)    | n                                 | N  | Error (%) |  |  |  |  |

| 10 k     | 1                                 | 23 | -2.3      |  |  |  |  |

| 25 k     | 1                                 | 9  | -6.3      |  |  |  |  |

| 50 k     | 1                                 | 4  | -6.3      |  |  |  |  |

| 100 k    | 1                                 | 2  | -21.9     |  |  |  |  |

| 250 k    | 0                                 | 3  | -6.3      |  |  |  |  |

| 350 k    | 0                                 | 2  | -10.7     |  |  |  |  |

Table 33.23 Minimum Widths at High and Low Level for SCL at Various Bit Rates (Simple I<sup>2</sup>C Mode)

|                   |   | Operating Frequency PCLK (MHz) |                                                  |   |    |                                                  |   |    |                                                  |   |    |                                                  |  |

|-------------------|---|--------------------------------|--------------------------------------------------|---|----|--------------------------------------------------|---|----|--------------------------------------------------|---|----|--------------------------------------------------|--|

|                   | 8 |                                | 10                                               |   |    | 16                                               |   |    | 20                                               |   |    |                                                  |  |

| Bit Rate<br>(bps) | n | N                              | Min. Widths at<br>High/Low Level<br>for SCL (μs) | n | N  | Min. Widths at<br>High/Low Level<br>for SCL (μs) | n | N  | Min. Widths at<br>High/Low Level<br>for SCL (μs) | n | N  | Min. Widths at<br>High/Low Level<br>for SCL (µs) |  |

| 10 k              | 0 | 24                             | 43.75/50.00                                      | 0 | 31 | 44.80/51.20                                      | 1 | 12 | 45.50/52.00                                      | 1 | 15 | 44.80/51.20                                      |  |

| 25 k              | 0 | 9                              | 17.50/20.00                                      | 0 | 12 | 18.20/20.80                                      | 1 | 4  | 17.50/20.00                                      | 1 | 6  | 19.60/22.40                                      |  |

| 50 k              | 0 | 4                              | 8.75/10.00                                       | 0 | 6  | 9.80/11.20                                       | 1 | 2  | 10.50/12.00                                      | 1 | 3  | 11.20/12.80                                      |  |

| 100 k             | 0 | 2                              | 5.25/6.00                                        | 0 | 3  | 5.60/6.40                                        | 0 | 4  | 4.37/5.00                                        | 0 | 6  | 4.90/5.60                                        |  |

| 250 k             | 0 | 0                              | 1.75/2.00                                        | 0 | 1  | 2.80/3.20                                        | 0 | 1  | 1.75/2.00                                        | 0 | 2  | 2.10/2.40                                        |  |

| 350 k             |   |                                |                                                  |   |    |                                                  |   |    |                                                  | 0 | 1  | 1.40/1.60                                        |  |

|                   |   | Operating Frequency PCLK (MHz) |                                                  |    |    |                                                  |  |  |  |  |  |

|-------------------|---|--------------------------------|--------------------------------------------------|----|----|--------------------------------------------------|--|--|--|--|--|

|                   |   |                                | 25                                               | 30 |    |                                                  |  |  |  |  |  |

| Bit Rate<br>(bps) | n | N                              | Min. Widths at<br>High/Low Level<br>for SCL (μs) | n  | N  | Min. Widths at<br>High/Low Level<br>for SCL (µs) |  |  |  |  |  |

| 10 k              | 1 | 19                             | 44.80/51.20                                      | 1  | 23 | 44.80/51.20                                      |  |  |  |  |  |

| 25 k              | 1 | 7                              | 17.92/20.48                                      | 1  | 9  | 18.66/21.33                                      |  |  |  |  |  |

| 50 k              | 1 | 3                              | 8.96/10.24                                       | 1  | 4  | 9.33/10.66                                       |  |  |  |  |  |

| 100 k             | 1 | 1                              | 4.48/5.12                                        | 1  | 2  | 5.60/6.40                                        |  |  |  |  |  |

| 250 k             | 0 | 3                              | 2.24/2.56                                        | 0  | 3  | 1.86/2.13                                        |  |  |  |  |  |

| 350 k             | 0 | 2                              | 1.68/1.92                                        | 0  | 2  | 1.40/1.60                                        |  |  |  |  |  |

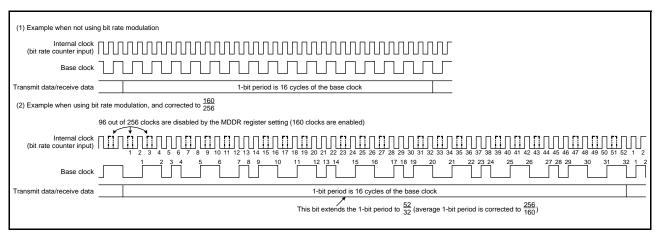

## 33.2.12 Modulation Duty Register (MDDR)

Address(es): SCI1.MDDR 0008 A032h, SCI5.MDDR 0008 A0B2h, SCI8.MDDR 0008 A112h, SCI12.MDDR 0008 B312h

The MDDR register corrects the bit rate adjusted by the BRR register.

When the SEMR.BRME bit is set to 1, the bit rate generated by the on-chip baud rate generator is evenly corrected according to the settings of the MDDR register (M/256). The relationship between the MDDR register setting (M) and the bit rate (B) is given in Table 33.24.

The range of the value that can be set in the MDDR register is from 80h to FFh. A value other than these cannot be set. The MDDR register is writable only when the TE and RE bits in the SCR register are 0.

Table 33.24 Relationship between MDDR Setting (M) and Bit Rate (B) When Bit Rate Modulation Function is Used

|                                                   | SEMR Sett     | ings             |                                                                                       |                                                                                                                                                             |

|---------------------------------------------------|---------------|------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode                                              | BGDM Bit      | ABCS Bit         | BRR Setting                                                                           | Error (%)                                                                                                                                                   |

| Asynchronous,<br>multi-processor<br>communication | 0             | 0                | $N = \frac{PCLK \times 10^{6}}{64 \times 2^{2n-1} \times \frac{256}{M} \times B} - 1$ | Error = $ \left\{ \frac{PCLK \times 10^{6}}{B \times 64 \times 2^{2n-1} \times \frac{256}{M} \times (N+1)} - 1 \right\} \times 100 $                        |

|                                                   | 1             | 0                | $N = \frac{PCLK \times 10^6}{32 \times 2^{2n-1} \times \frac{256}{310} \times B} - 1$ | Error = $ \begin{cases} \frac{PCLK \times 10^{6}}{B \times 32 \times 2^{2n-1} \times \frac{256}{M} \times (N+1)} - 1 \\ \times 100 \end{cases} \times 100 $ |

|                                                   | 0             | 1                | $32 \times 2 \times \frac{M}{M} \times B$                                             | $\left[ B \times 32 \times 2^{2n-1} \times \frac{256}{M} \times (N+1) \right]$                                                                              |

|                                                   | 1             | 1                | $N = \frac{PCLK \times 10^{6}}{16 \times 2^{2n-1} \times \frac{256}{M} \times B} - 1$ | Error = $ \left\{ \frac{PCLK \times 10^{6}}{B \times 16 \times 2^{2n-1} \times \frac{256}{M} \times (N+1)} - 1 \right\} \times 100 $                        |

| Clock synchrono                                   | ous, simple S | P * <sup>1</sup> | $N = \frac{PCLK \times 10^6}{8 \times 2^{2n-1} \times \frac{256}{M} \times B} - 1$    |                                                                                                                                                             |

| Smart card interf                                 | face          |                  | $N = \frac{PCLK \times 10^{6}}{S \times 2^{2n+1} \times \frac{256}{M} \times B} - 1$  | Error = $ \left\{ \frac{PCLK \times 10^6}{B \times S \times 2^{2n+1} \times \frac{256}{M} \times (N+1)} - 1 \right\} \times 100 $                           |

| Simple I <sup>2</sup> C* <sup>2</sup>             |               |                  | $N = \frac{PCLK \times 10^{6}}{64 \times 2^{2n-1} \times \frac{256}{M} \times B} - 1$ |                                                                                                                                                             |

B: Bit rate (bps)

M: MDDR setting  $(128 \le MDDR \le 256)$

N: BRR setting for baud rate generator  $(0 \le N \le 255)$

PCLK: Operating frequency (MHz)

n and S: Determined by the settings of the SMR and SCMR registers as listed in Table 33.12 and Table 33.13, section

33.2.11, Bit Rate Register (BRR).

Note 1. Do not use this function in clock synchronous mode and in the highest speed settings in simple SPI mode (SMR.CKS[1:0] = 00b, SCR.CKE[1] = 0, and BRR = 0).

Note 2. Adjust the bit rate so that the widths at high and low level of the SCL output in simple I<sup>2</sup>C mode satisfy the I<sup>2</sup>C-bus standard.

Smaller settings of the SMR.CKS[1:0] bits and larger settings of the BRR register reduce difference in the length of the 1-bit period.

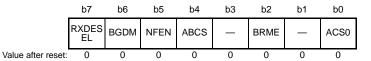

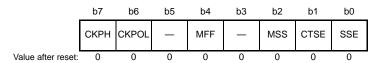

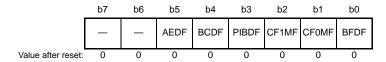

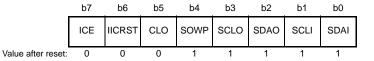

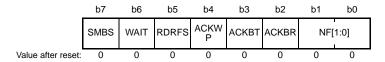

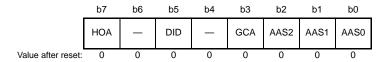

## 33.2.13 Serial Extended Mode Register (SEMR)

Address(es): SCI1.SEMR 0008 A027h, SCI5.SEMR 0008 A0A7h, SCI8.SEMR 0008 A107h, SCI12.SEMR 0008 B307h

| Bit | Symbol  | Bit Name                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W   |

|-----|---------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| b0  | ACS0    | Asynchronous Mode<br>Clock Source Select           | (Valid only in asynchronous mode) 0: External clock input 1: Logical AND of two compare matches output from TMR (valid for SCI5 and SCI12 only)                                                                                                                                                                                                                                                                                    | R/W*1 |

| b1  | _       | Reserved                                           | This bit is read as 0. The write value should be 0.                                                                                                                                                                                                                                                                                                                                                                                | R/W   |

| b2  | BRME    | Bit Rate Modulation<br>Enable                      | 0: Bit rate modulation function is disabled. 1: Bit rate modulation function is enabled.                                                                                                                                                                                                                                                                                                                                           | R/W*1 |

| b3  | _       | Reserved                                           | This bit is read as 0. The write value should be 0.                                                                                                                                                                                                                                                                                                                                                                                | R/W   |

| b4  | ABCS    | Asynchronous Mode<br>Base Clock Select             | (Valid only in asynchronous mode) 0: Selects 16 base clock cycles for 1-bit period. 1: Selects 8 base clock cycles for 1-bit period.                                                                                                                                                                                                                                                                                               | R/W*1 |

| b5  | NFEN    | Digital Noise Filter<br>Function Enable            | (In asynchronous mode)  0: Noise cancellation function for the RXDn input signal is disabled.  1: Noise cancellation function for the RXDn input signal is enabled. (in simple I <sup>2</sup> C mode)  0: Noise cancellation function for the SSCLn and SSDAn input signals is disabled.  1: Noise cancellation function for the SSCLn and SSDAn input signals is enabled.  The NFEN bit should be 0 in any mode other than above. | R/W*1 |

| b6  | BGDM    | Baud Rate Generator<br>Double-Speed Mode<br>Select | (Only valid the SCR.CKE[1] bit is 0 in asynchronous mode) 0: Baud rate generator outputs the clock with normal frequency. 1: Baud rate generator outputs the clock with doubled frequency.                                                                                                                                                                                                                                         | R/W*1 |

| b7  | RXDESEL | Asynchronous Start Bit<br>Edge Detection Select    | (Valid only in asynchronous mode) 0: The low level on the RXDn pin is detected as the start bit. 1: A falling edge on the RXDn pin is detected as the start bit.                                                                                                                                                                                                                                                                   | R/W*1 |

Note 1. Writable only when the SCR.TE bit is 0 and the SCR.RE bit is 0 (both serial transmission and reception are disabled).

The SEMR register is used to select a clock source for 1-bit period in asynchronous mode or a detection method of the start bit.

### **ACS0 Bit (Asynchronous Mode Clock Source Select)**

Selects the clock source in the asynchronous mode.

The ACS0 bit is valid in asynchronous mode (SMR.CM bit = 0) and when an external clock input is selected (SCR.CKE[1:0] bits = 10b or 11b). This bit is used to select an external clock input or the logical AND of compare matches output from the internal TMR.

Set the ACS0 bit to 0 in other than asynchronous mode.

For SCI5 and SCI12, the TMOn output (n = 0, 1) of TMR unit 0 can be set as the base clock source. Refer to Table 33.25 for details.

The ACS0 bits for SCI1 and SCI8 are reserved. The write values to these bits for SCI1 and SCI8 should be 0.

Table 33.25 Correspondence between SCI Channels and Compare Match Outputs

| SCI   | TMR    | Compare Match Output |

|-------|--------|----------------------|

| SCI5  | Unit 0 | TMO0, TMO1           |

| SCI12 | Unit 0 | TMO0, TMO1           |

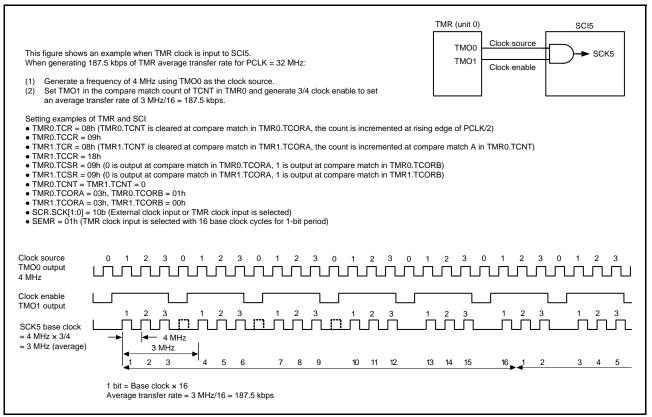

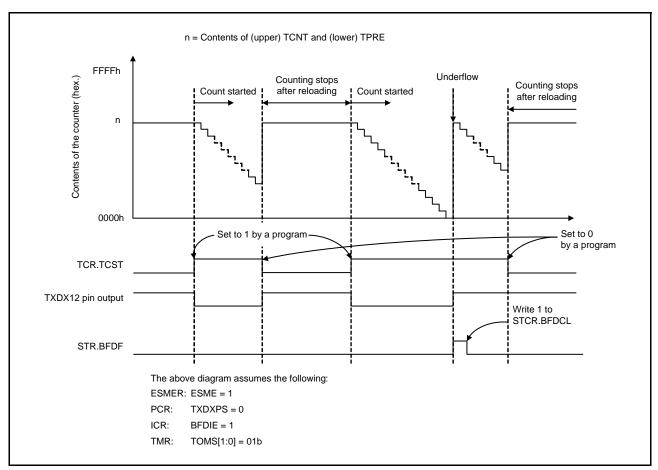

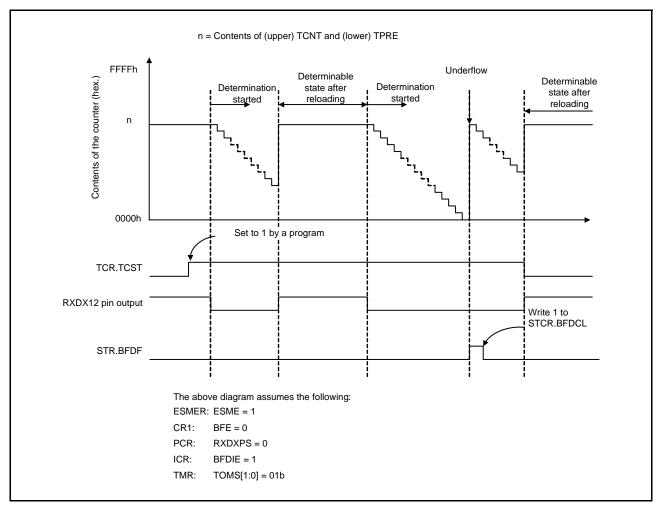

Figure 33.4 shows a setting example of when TMO0 and TMO1 in the TMR unit 0 are selected for output.

Figure 33.4 Example of Average Transfer Rate Setting When TMR Clock is Input

#### **BRME Bit (Bit Rate Modulation Enable)**

This bit enables and disables the bit rate modulation function. The bit rate generated by on-chip baud rate generator is evenly corrected when this function is enabled.

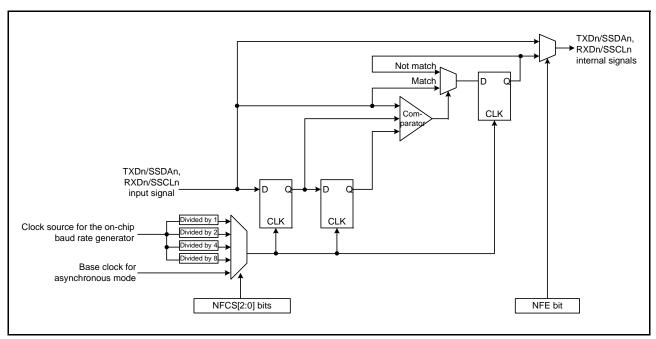

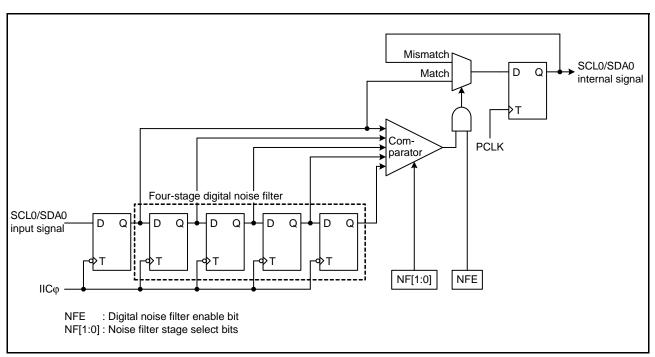

#### **NFEN Bit (Digital Noise Filter Function Enable)**

This bit enables or disables the digital noise filter function.

When the function is enabled, noise cancellation is applied to the RXDn input signal in asynchronous mode, and noise cancellation is applied to the SSDAn and SSCLn input signals in simple I<sup>2</sup>C mode.

In any mode other than above, set the NFEN bit to 0 to disable the digital noise filter function.

When the function is disabled, input signals are transferred as is, as internal signals.

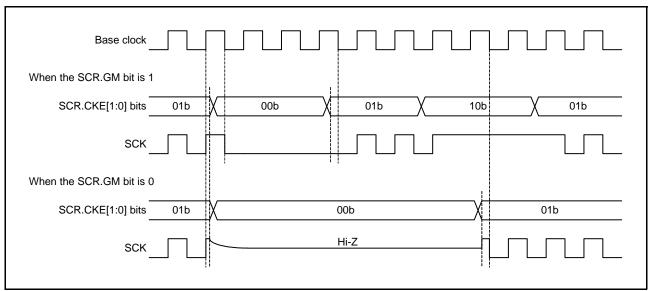

### **BGDM Bit (Baud Rate Generator Double-Speed Mode Select)**

Selects the cycle of output clock for the baud rate generator.

This bit is valid when the on-chip baud rate generator is selected as the clock source (SCR.CKE[1] = 0) in asynchronous mode (SMR.CM = 0). For the clock output from the baud rate generator, either normal or doubled frequency can be selected. The base clock is generated by the clock output from the baud rate generator. When the BGDM bit is set to 1, the base clock cycle is halved and the bit rate is doubled.

Set this bit to 0 in modes other than asynchronous mode.

### RXDESEL Bit (Asynchronous Start Bit Edge Detection Select)

Selects the detection method of the start bit for reception in asynchronous mode. When a break occurs, data receiving operation depends on the settings of this bit. Set this bit to 1 when reception should be stopped while a break occurs or when reception should be started without retaining the RXDn pin input at high level for the period of one data frame or longer after completion of the break.

Set this bit to 0 in modes other than asynchronous mode.

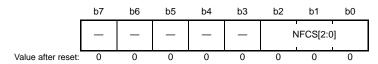

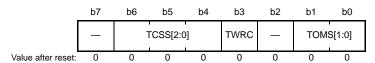

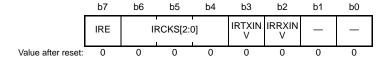

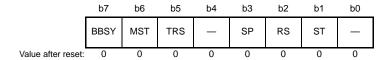

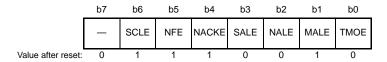

# 33.2.14 Noise Filter Setting Register (SNFR)

Address(es): SCI1.SNFR 0008 A028h, SCI5.SNFR 0008 A0A8h, SCI8.SNFR 0008 A108h, SCI12.SNFR 0008 B308h

| Bit      | Symbol    | Bit Name                  | Description                                                                        | R/W   |

|----------|-----------|---------------------------|------------------------------------------------------------------------------------|-------|

| b2 to b0 | NFCS[2:0] | Noise Filter Clock Select | In asynchronous mode, the standard setting for the base clock is as follows.       | R/W*1 |

|          |           |                           | 0 0 0: The clock signal divided by 1 is used with the noise filter.                |       |

|          |           |                           | In simple I <sup>2</sup> C mode, the standard settings for the clock source of the |       |

|          |           |                           | on-chip baud rate generator selected by the SMR.CKS[1:0] bits are given below.     |       |

|          |           |                           | b2 b0<br>0 0 1: The clock signal divided by 1 is used with the noise filter.       |       |

|          |           |                           | 0 1 0: The clock signal divided by 2 is used with the noise filter.                |       |

|          |           |                           | 0 1 1: The clock signal divided by 4 is used with the noise filter.                |       |

|          |           |                           | 1 0 0: The clock signal divided by 8 is used with the noise filter.                |       |

|          |           |                           | Settings other than above are prohibited.                                          |       |

| b7 to b3 | _         | Reserved                  | These bits are read as 0. The write value should be 0.                             | R/W   |

Note 1. Writing to these bits is only possible when the RE and TE bits in the SCR register are 0 (serial reception and transmission disabled).

## NFCS[2:0] Bits (Noise Filter Clock Select)

These bits select the sampling clock for the digital noise filter. To use the noise filter in asynchronous mode, set these bits to 000b. In simple  $I^2C$  mode, set the bits to a value in the range from 001b to 100b.

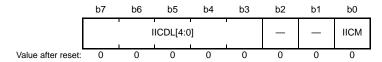

# 33.2.15 I<sup>2</sup>C Mode Register 1 (SIMR1)

Address(es): SCI1.SIMR1 0008 A029h, SCI5.SIMR1 0008 A0A9h, SCI8.SIMR1 0008 A109h, SCI12.SIMR1 0008 B309h

| Bit      | Symbol     | Bit Name                            | Description                                                                                                                                                                                                                                                                                          | R/W               |

|----------|------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| b0       | IICM       | Simple I <sup>2</sup> C Mode Select | SMIF IICM 0 0: Asynchronous mode, Multi-processor mode, Clock synchronous mode (in asynchronous mode, synchronous, or simple SPI mode) 0 1: Simple I <sup>2</sup> C mode 1 0: Smart card interface mode 1 1: Setting prohibited.                                                                     | R/W* <sup>1</sup> |

| b2, b1   | _          | Reserved                            | These bits are read as 0. The write value should be 0.                                                                                                                                                                                                                                               | R/W               |

| b7 to b3 | IICDL[4:0] | SSDA Output Delay Select            | (Cycles below are of the clock signal from the on-chip baud rate generator.)  b7  b3  0 0 0 0 0: No output delay 0 0 0 0 1: 0 to 1 cycle 0 0 0 1 0: 1 to 2 cycles 0 0 0 1 1: 2 to 3 cycles 0 0 1 0 0: 3 to 4 cycles 0 0 1 0 1: 4 to 5 cycles : 1 1 1 1 0: 29 to 30 cycles 1 1 1 1 1: 30 to 31 cycles | R/W* <sup>1</sup> |

Note 1. Writing to these bits is only possible when the RE and TE bits in the SCR register are 0 (both serial transmission and reception are disabled).

SIMR1 is used to select simple I2C mode and the number of delay stages for the SSDA output.

### IICM Bit (Simple I<sup>2</sup>C Mode Select)

In conjunction with the SCMR.SMIF bit, this bit selects the operating mode.

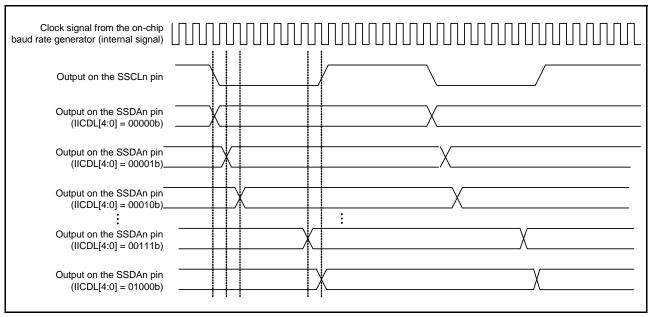

## IICDL[4:0] Bits (SSDA Output Delay Select)

These bits are used to set a delay for output on the SSDAn pin relative to the falling edge of the output on the SSCLn pin. The available delay settings range from no delay to 31 cycles, with the clock signal from the on-chip baud rate generator as the base. The signal obtained by frequency-dividing PCLK by the divisor set in the SMR.CKS[1:0] bits is supplied as the clock signal from the on-chip baud rate generator. Set these bits to 00000b unless operation is in simple I<sup>2</sup>C mode. In simple I<sup>2</sup>C mode, set the bits to a value in the range from 00001b to 11111b.

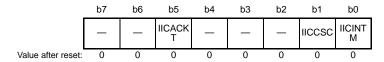

## 33.2.16 I<sup>2</sup>C Mode Register 2 (SIMR2)

Address(es): SCI1.SIMR2 0008 A02Ah, SCI5.SIMR2 0008 A0AAh, SCI8.SIMR2 0008 A10Ah, SCI12.SIMR2 0008 B30Ah

| Bit      | Symbol  | Bit Name                               | Description                                                                        | R/W   |

|----------|---------|----------------------------------------|------------------------------------------------------------------------------------|-------|

| b0       | IICINTM | I <sup>2</sup> C Interrupt Mode Select | Use ACK/NACK interrupts.     Use reception and transmission interrupts.            | R/W*1 |

| b1       | IICCSC  | Clock Synchronization                  | No synchronization with the clock signal     Synchronization with the clock signal | R/W*1 |

| b4 to b2 | _       | Reserved                               | These bits are read as 0. The write value should be 0.                             | R/W   |

| b5       | IICACKT | ACK Transmission Data                  | 0: ACK transmission 1: NACK transmission and reception of ACK/NACK                 | R/W   |

| b7, b6   | _       | Reserved                               | These bits are read as 0. The write value should be 0.                             | R/W   |

Note 1. Writing to these bits is only possible when the RE and TE bits in the SCR register are 0 (serial reception and transmission disabled).

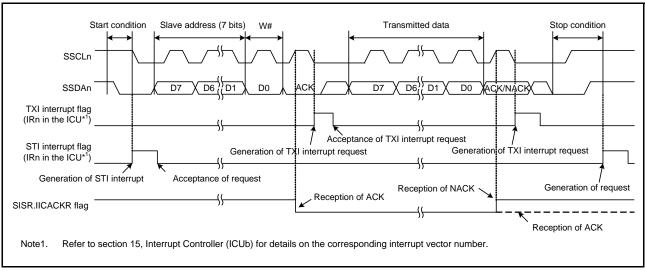

SIMR2 is used to select how reception and transmission are controlled in simple I<sup>2</sup>C mode.

### **IICINTM Bit (I<sup>2</sup>C Interrupt Mode Select)**

This bit selects the sources of interrupt requests in simple I<sup>2</sup>C mode.

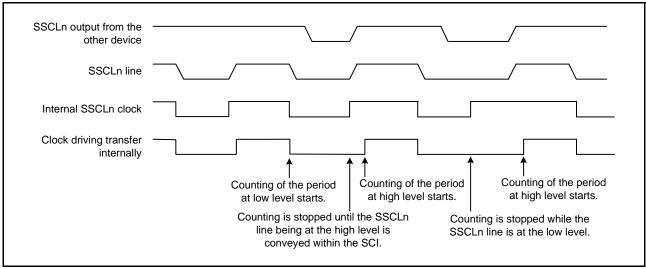

## **IICCSC Bit (Clock Synchronization)**

Set the IICCSC bit to 1 if the internally generated SSCLn clock signal is to be synchronized when the SSCLn pin has been placed at the low level in the case of a wait inserted by the other device, etc.

The SSCLn clock signal is not synchronized if the IICCSC bit is 0. The SSCLn clock signal is generated in accord with the rate selected in the BRR regardless of the level being input on the SSCLn pin.

Set the IICCSC bit to 1 except during debugging.

### **IICACKT Bit (ACK Transmission Data)**

Transmitted data contains ACK bits. Set this bit to 1 when ACK and NACK bits are received.

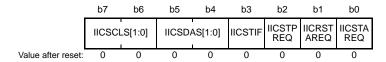

# 33.2.17 I<sup>2</sup>C Mode Register 3 (SIMR3)

Address(es): SCI1.SIMR3 0008 A02Bh, SCI5.SIMR3 0008 A0ABh, SCI8.SIMR3 0008 A10Bh, SCI12.SIMR3 0008 B30Bh

| Bit    | Symbol       | Bit Name                                                       | Description                                                                                                                                                                                                                                | R/W |

|--------|--------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0     | IICSTAREQ    | Start Condition Generation                                     | 0: A start condition is not generated. 1: A start condition is generated.*1, *3, *4, *5                                                                                                                                                    | R/W |

| b1     | IICRSTAREQ   | Restart Condition Generation                                   | O: A restart condition is not generated.  1: A restart condition is generated. *2, *3, *4, *5                                                                                                                                              | R/W |

| b2     | IICSTPREQ    | Stop Condition Generation                                      | 0: A stop condition is not generated. 1: A stop condition is generated.*2, *3, *4, *5                                                                                                                                                      | R/W |

| b3     | IICSTIF      | Issuing of Start, Restart, or Stop<br>Condition Completed Flag | O: There are no requests for generating conditions or a condition is being generated.  1: A start, restart, or stop condition is completely generated.                                                                                     | R/W |

| b5, b4 | IICSDAS[1:0] | SSDA Output Select                                             | <ul> <li>b5 b4</li> <li>0 0: Serial data output</li> <li>0 1: Generate a start, restart, or stop condition.</li> <li>1 0: Output the low level on the SSDAn pin.</li> <li>1 1: Place the SSDAn pin in the high-impedance state.</li> </ul> | R/W |

| b7, b6 | IICSCLS[1:0] | SSCL Output Select                                             | b7 b6 0 0: Serial clock output 0 1: Generate a start, restart, or stop condition. 1 0: Output the low level on the SSCLn pin. 1 1: Place the SSCLn pin in the high-impedance state.                                                        | R/W |

Note 1. Generate a start condition only when the SSCLn and SSDAn pins are both high (the corresponding bits in the corresponding PIDR registers are 1).

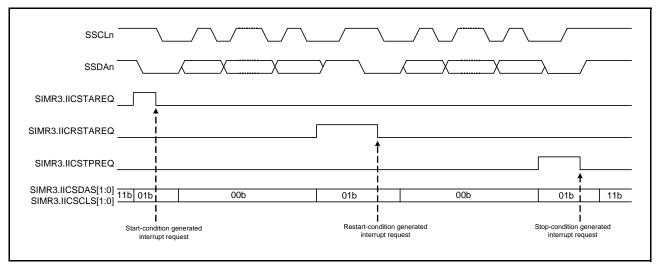

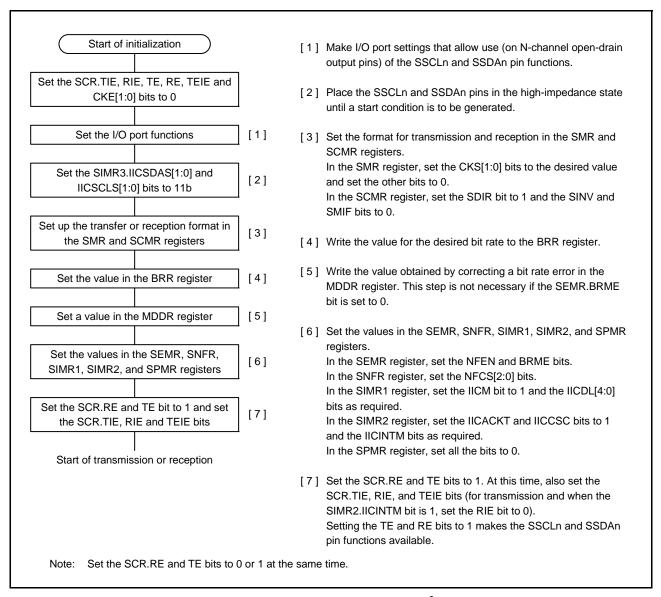

SIMR3 is used to control the simple I<sup>2</sup>C mode start and stop conditions, and to hold the SSDAn and SSCLn pins at fixed levels.

### **IICSTAREQ Bit (Start Condition Generation)**

When a start condition is to be generated, set both the IICSDAS[1:0] and IICSCLS[1:0] bits to 01b as well as setting the IICSTAREQ bit to 1.

[Setting condition]

• Writing 1 to the bit

[Clearing condition]

• Completion of generation of the start condition

Note 2. Generate a restart or stop condition only when the SSCLn pin is low (the corresponding bit in the PIDR register is 0).

Note 3. Do not set more than one from among the IICSTAREQ, IICRSTAREQ, and IICSTPREQ bits to 1 at a given time.

Note 4. Execute the generation of a condition after the value of the IICSTIF flag is 0.

Note 5. Do not write 0 to this bit while it is 1. Generation of a condition is suspended by writing 0 to this bit while it is 1.

#### **IICRSTAREQ Bit (Restart Condition Generation)**

When a restart condition is to be generated, set both the IICSDAS[1:0] and IICSCLS[1:0] bits to 01b as well as setting the IICRSTAREQ bit to 1.

[Setting condition]

• Writing 1 to the bit

[Clearing condition]

• Completion of generation of the restart condition

### **IICSTPREQ Bit (Stop Condition Generation)**

When a stop condition is to be generated, set both the IICSDAS[1:0] and IICSCLS[1:0] bits to 01b as well as setting the IICSTPREQ bit to 1.

[Setting condition]

• Writing 1 to the bit

[Clearing condition]

• Completion of generation of the stop condition

#### IICSTIF Flag (Issuing of Start, Restart, or Stop Condition Completed Flag)

After generating a condition, this bit indicates that the generation is completed. When using the IICSTAREQ, IICRSTAREQ, or IICSTPREQ bit to cause generation of a condition, do so after setting the IICSTIF flag to 0. When the IICSTIF flag is 1 while an interrupt request is enabled by setting the SCR.TEIE bit, an STI request is output. [Setting condition]

• Completion of the generation of a start, restart, or stop condition (however, in cases where this conflicts with any of the conditions for the flag becoming 0 listed below, the other condition takes precedence)

[Clearing conditions]

- Writing 0 to the bit (confirm that the IICSTIF flag is 0 before doing so)

- Writing 0 to the SIMR1.IICM bit (when operation is not in simple I<sup>2</sup>C mode)

- Writing 0 to the SCR.TE bit

### IICSDAS[1:0] Bits (SSDA Output Select)

These bits control output from the SSDAn pin.

Set the IICSDAS[1:0] and IICSCLS[1:0] bits to the same value during normal operations.

### IICSCLS[1:0] Bits (SSCL Output Select)

These bits control output from the SSCLn pin.

Set the IICSCLS[1:0] and IICSDAS[1:0] bits to the same value during normal operations.

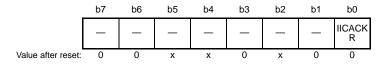

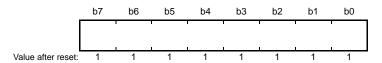

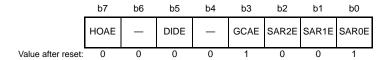

# 33.2.18 I<sup>2</sup>C Status Register (SISR)

Address(es): SCI1.SISR 0008 A02Ch, SCI5.SISR 0008 A0ACh, SCI8.SISR 0008 A10Ch, SCI12.SISR 0008 B30Ch

x: Undefined

| Bit    | Symbol  | Bit Name                | Description                                            | R/W   |

|--------|---------|-------------------------|--------------------------------------------------------|-------|

| b0     | IICACKR | ACK Reception Data Flag | 0: ACK received<br>1: NACK received                    | R/W*1 |

| b1     | _       | Reserved                | This bit is read as 0. The write value should be 0.    | R/W   |

| b2     | _       | Reserved                | The read value is undefined.                           | R     |

| b3     | _       | Reserved                | This bit is read as 0. The write value should be 0.    | R/W   |

| b5, b4 | _       | Reserved                | The read value is undefined.                           | R     |

| b7, b6 | _       | Reserved                | These bits are read as 0. The write value should be 0. | R/W   |

Note 1. Only 0 can be written to this bit, to clear the flag.

SISR is used to monitor state in relation to simple I<sup>2</sup>C mode.

## **IICACKR Flag (ACK Reception Data Flag)**

Received ACK and NACK bits can be read from this bit.

The IICACKR flag is updated at the rising of SSCLn clock for the ACK/NACK receiving bit.

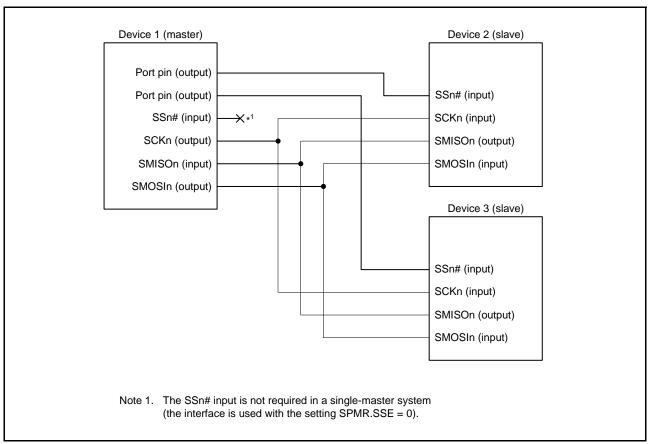

## 33.2.19 SPI Mode Register (SPMR)

Address(es): SCI1.SPMR 0008 A02Dh, SCI5.SPMR 0008 A0ADh, SCI8.SPMR 0008 A10Dh, SCI12.SPMR 0008 B30Dh

| Bit | Symbol | Bit Name                 | Description                                                                                                                                                                                       | R/W   |

|-----|--------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| b0  | SSE    | SSn# Pin Function Enable | 0: SSn# pin function is disabled. 1: SSn# pin function is enabled.                                                                                                                                | R/W*1 |

| b1  | CTSE   | CTS Enable               | O: CTS function is disabled (RTS output function is enabled).     1: CTS function is enabled.                                                                                                     | R/W*1 |

| b2  | MSS    | Master Slave Select      | O: Transmission is through the SMOSIn pin and reception is through the SMISOn pin (master mode).  1: Reception is through the SMOSIn pin and transmission is through the SMISOn pin (slave mode). | R/W*1 |

| b3  | _      | Reserved                 | This bit is read as 0. The write value should be 0.                                                                                                                                               | R/W   |

| b4  | MFF    | Mode Fault Flag          | 0: No mode fault error 1: Mode fault error                                                                                                                                                        | R/W*2 |

| b5  | _      | Reserved                 | This bit is read as 0. The write value should be 0.                                                                                                                                               | R/W   |

| b6  | CKPOL  | Clock Polarity Select    | O: Clock polarity is not inverted.  1: Clock polarity is inverted.                                                                                                                                | R/W*1 |

| b7  | CKPH   | Clock Phase Select       | Clock is not delayed.     Clock is delayed.                                                                                                                                                       | R/W*1 |

Note 1. Writing to these bits is only possible when the RE and TE bits in the SCR register are 0 (both serial transmission and reception are disabled).

SPMR is used to select the extension settings in asynchronous and clock synchronous modes.

### **SSE Bit (SSn# Pin Function Enable)**

Set this bit to 1 if the SSn# pin is to be used in control of transmission and reception (in simple SPI mode). Set this bit to 0 in any other mode. Furthermore, even for usage in simple SPI mode, the SSn# pin on the master side is not required to control reception and transmission when master mode (SCR.CKE[1:0] = 00b and MSS = 0) is selected and there is a single master, so the setting for the SSE bit is 0. Do not set both the SSE and CTSE bits to enabled (even if this setting is made, operation is the same as that when these bits are set to 0).

### CTSE Bit (CTS Enable)

Set this bit to 1 if the SSn# pin is to be used for inputting of the CTS control signal to control of transmission and reception. The RTS signal is output when this bit is set to 0. Set this bit to 0 in smart card interface mode, simple SPI mode, and simple I<sup>2</sup>C mode. Do not set both the CTSE and SSE bits to enabled (even if this setting is made, operation is the same as that when these bits are set to 0).

#### MSS Bit (Master Slave Select)

This bit selects between master and slave operation in simple SPI mode. When the MSS bit is set to 1, data is received through the SMOSIn pin and transmitted through the SMISOn pin.

Set this bit to 0 in modes other than simple SPI mode.

Note 2. Only 0 can be written to these bits, which clears the flag.

### MFF Flag (Mode Fault Flag)

This bit indicates mode fault errors.

In a multi-master configuration, determine the mode fault error occurrence by reading the MFF flag. [Setting condition]

• Input on the SSn# pin being at the low level during master operation in simple SPI mode (SSE bit = 1 and MSS bit = 0)

[Clearing condition]

• Writing 0 to the bit after it was read as 1

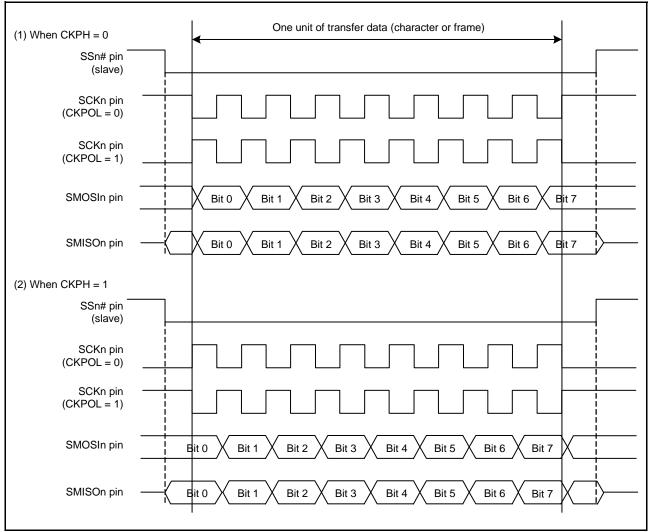

### **CKPOL Bit (Clock Polarity Select)**

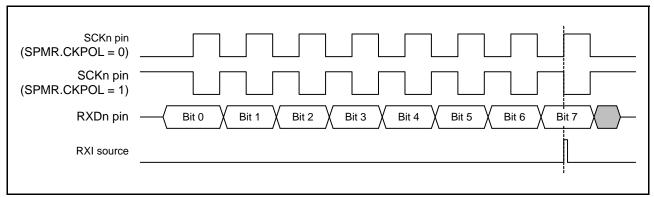

This bit selects the polarity of the clock signal output through the SCKn pin. Refer to Figure 33.58 for details. Set the bit to 0 in other than simple SPI mode and clock synchronous mode.

### **CKPH Bit (Clock Phase Select)**

This bit selects the phase of the clock signal output through the SCKn pin. Refer to Figure 33.58 for details. Set the bit to 0 in other than simple SPI mode and clock synchronous mode.

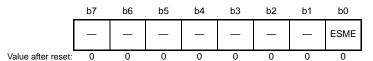

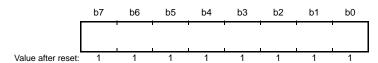

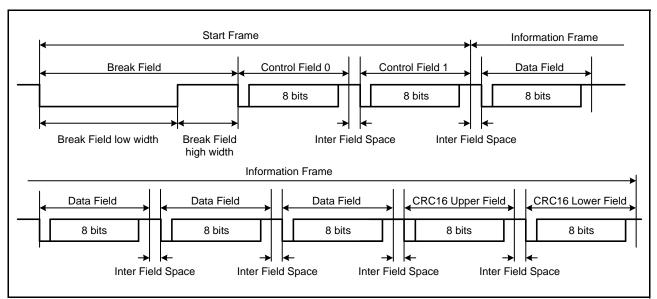

## 33.2.20 Extended Serial Module Enable Register (ESMER)

Address(es): SCI12.ESMER 0008 B320h

| Bit      | Symbol | Bit Name                       | Description                                                                                                | R/W |

|----------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------|-----|

| b0       | ESME   | Extended Serial Mode<br>Enable | <ul><li>0: The extended serial mode is disabled.</li><li>1: The extended serial mode is enabled.</li></ul> | R/W |

| b7 to b1 | _      | Reserved                       | These bits are read as 0. The write value should be 0.                                                     | R/W |

### **ESME Bit (Extended Serial Mode Enable)**

When the ESME bit is 1, the facilities of the extended serial mode control section are enabled.

When the ESME bit is 0, the extended serial mode control section is initialized.

Table 33.26 Settings of the ESME Bit and Timer Operation Mode

| ESME Bit | Timer Mode  | Break Field Low Width Determination Mode | Break Field Low Width Output Mode |

|----------|-------------|------------------------------------------|-----------------------------------|

| 0        | Available*1 | Not available                            | Not available                     |

| 1        | Available   | Available                                | Available                         |

Note 1. Operation is only possible with PCLK selected.

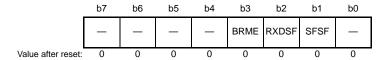

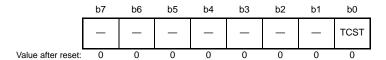

# 33.2.21 Control Register 0 (CR0)

Address(es): SCI12.CR0 0008 B321h

| Bit      | Symbol | Bit Name                       | Description                                                                                | R/W |

|----------|--------|--------------------------------|--------------------------------------------------------------------------------------------|-----|

| b0       | _      | Reserved                       | This bit is read as 0. The write value should be 0.                                        | R/W |

| b1       | SFSF   | Start Frame Status Flag        | Start Frame detection function is disabled.     Start Frame detection function is enabled. | R   |

| b2       | RXDSF  | RXDX12 Input Status Flag       | 0: RXDX12 input is enabled. 1: RXDX12 input is disabled.                                   | R   |

| b3       | BRME   | Bit Rate Measurement<br>Enable | Measurement of bit rate is disabled.     Measurement of bit rate is enabled.               | R/W |

| b7 to b4 | _      | Reserved                       | These bits are read as 0. The write value should be 0.                                     | R/W |

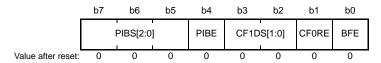

# 33.2.22 Control Register 1 (CR1)

Address(es): SCI12.CR1 0008 B322h

| Bit      | Symbol     | Bit Name                                | Description                                                                                                                                                                                                                                                                                      | R/W |

|----------|------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0       | BFE        | Break Field Enable                      | Break Field detection is disabled.     Break Field detection is enabled.                                                                                                                                                                                                                         | R/W |

| b1       | CF0RE      | Control Field 0 Reception<br>Enable     | Reception of Control Field 0 is disabled.     Reception of Control Field 0 is enabled.                                                                                                                                                                                                           | R/W |

| b3, b2   | CF1DS[1:0] | Control Field 1 Data Register<br>Select | <ul> <li>b3 b2</li> <li>0 0: Selects comparison with the value in the PCF1DR register.</li> <li>0 1: Selects comparison with the value in the SCF1DR register.</li> <li>1 0: Selects comparison with the values in the PCF1DR and SCF1DR registers.</li> <li>1 1: Setting prohibited.</li> </ul> | R/W |

| b4       | PIBE       | Priority Interrupt Bit Enable           | The priority interrupt bit is disabled.     The priority interrupt bit is enabled.                                                                                                                                                                                                               | R/W |

| b7 to b5 | PIBS[2:0]  | Priority Interrupt Bit Select           | b7 b5 0 0 0: 0th bit of Control Field 1 0 0 1: 1st bit of Control Field 1 0 1 0: 2nd bit of Control Field 1 0 1 1: 3rd bit of Control Field 1 1 0 0: 4th bit of Control Field 1 1 0 1: 5th bit of Control Field 1 1 0: 6th bit of Control Field 1 1 1: 7th bit of Control Field 1                | R/W |

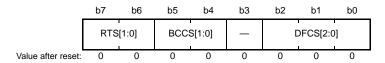

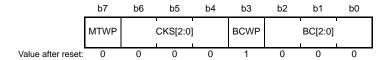

# 33.2.23 Control Register 2 (CR2)

Address(es): SCI12.CR2 0008 B323h

| Bit      | Symbol    | Bit Name                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W |

|----------|-----------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b2 to b0 | DFCS[2:0] | RXDX12 Signal Digital Filter<br>Clock Select | b2 b0 0 0 0: Filter is disabled. 0 0 1: Filter clock is base clock*1, *2 0 1 0: Filter clock is PCLK/8 0 1 1: Filter clock is PCLK/16 1 0 0: Filter clock is PCLK/32 1 0 1: Filter clock is PCLK/64 1 1 0: Filter clock is PCLK/128 1 1 1: Setting prohibited                                                                                                                                                                                                        | R/W |

| b3       | _         | Reserved                                     | This bit is read as 0. The write value should be 0.                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W |

| b5, b4   | BCCS[1:0] | Bus Collision Detection Clock<br>Select      | When SEMR.BGDM = 0 or SEMR.BGDM = 1 and SMR.CKS[1:0] = a value other than 00b  b5 b4 0 0: Base clock 0 1: Base clock frequency divided by 2 1 0: Base clock frequency divided by 4 1 1: Setting prohibited  When SEMR.BGDM = 1 and SMR.CKS[1:0] = 00b  b5 b4 0 0: Base clock frequency divided by 2 0 1: Base clock frequency divided by 4 1 0: Setting prohibited 1 1: Setting prohibited                                                                           | R/W |

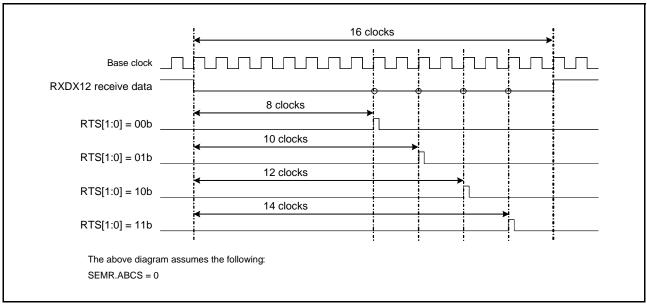

| b7, b6   | RTS[1:0]  | RXDX12 Reception Sampling<br>Timing Select   | When SCI12.SEMR.ABCS = 0  b7 b6  0 0: Rising edge of the 8th cycle of base clock  1 : Rising edge of the 10th cycle of base clock  1 : Rising edge of the 12th cycle of base clock  1 : Rising edge of the 14th cycle of base clock  When SCI12.SEMR.ABCS = 1  b7 b6  0 : Rising edge of the 4th cycle of base clock  1 : Rising edge of the 5th cycle of base clock  1 : Rising edge of the 6th cycle of base clock  1 : Rising edge of the 7th cycle of base clock | R/W |

Note: The period of the base clock is 1/16 of a single bit period when the SCI12.SEMR.ABCS is 0, and 1/8 of a single bit period when the SCI12.SEMR.ABCS is 1.

Note 1. To use the base clock, set the SCI12.SCR.TE bit to 1.

Note 2. The base clock divided by 2 is the filter clock when the SEMR.BGDM bit is 1 and the SMR.CKS[1:0] bits are 00b.

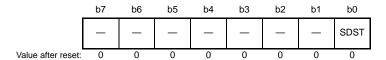

# 33.2.24 Control Register 3 (CR3)

Address(es): SCI12.CR3 0008 B324h

| Bit      | Symbol | Bit Name                    | Description                                                                           | R/W |

|----------|--------|-----------------------------|---------------------------------------------------------------------------------------|-----|

| b0       | SDST   | Start Frame Detection Start | Detection of Start Frame is not performed.     Detection of Start Frame is performed. | R/W |

| b7 to b1 | _      | Reserved                    | These bits are read as 0. The write value should be 0.                                | R/W |

### **SDST Bit (Start Frame Detection Start)**

Detection of a Start Frame begins when this bit is set to 1. The bit is read as 0.

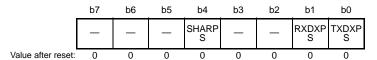

# 33.2.25 Port Control Register (PCR)

Address(es): SCI12.PCR 0008 B325h

| Bit      | Symbol | Bit Name                                 | Description                                                                                                            | R/W |

|----------|--------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|

| b0       | TXDXPS | TXDX12 Signal Polarity Select            | O: The polarity of TXDX12 signal is not inverted for output.  1: The polarity of TXDX12 signal is inverted for output. | R/W |

| b1       | RXDXPS | RXDX12 Signal Polarity<br>Select         | 0: The polarity of RXDX12 signal is not inverted for input.  1: The polarity of RXDX12 signal is inverted for input.   | R/W |

| b3, b2   | _      | Reserved                                 | These bits are read as 0. The write value should be 0.                                                                 | R/W |

| b4       | SHARPS | TXDX12/RXDX12 Pin<br>Multiplexing Select | 0: The TXDX12 and RXDX12 pins are independent.  1: The TXDX12 and RXDX12 signals are multiplexed on the same pin.      | R/W |

| b7 to b5 | _      | Reserved                                 | These bits are read as 0. The write value should be 0.                                                                 | R/W |

## SHARPS Bit (TXDX12/RXDX12 Pin Multiplexing Select)

When this bit is set to 1, the TXDX12 and RXDX12 signals are multiplexed on the same pin so that half-duplex communications become possible.

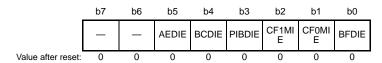

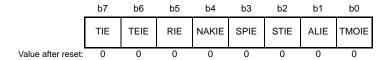

# 33.2.26 Interrupt Control Register (ICR)

Address(es): SCI12.ICR 0008 B326h

| Bit    | Symbol | Bit Name                                            | Description                                                                                                                                                                      | R/W |  |  |  |  |

|--------|--------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

| b0     | BFDIE  | Break Field Low Width Detected Interrupt Enable     | <ul><li>0: Interrupts on detection of the low width for a Break Field are disabled.</li><li>1: Interrupts on detection of the low width for a Break Field are enabled.</li></ul> |     |  |  |  |  |

| b1     | CF0MIE | Control Field 0 Match Detected<br>Interrupt Enable  | <ul><li>0: Interrupts on detection of a match with Control Field 0 are disabled.</li><li>1: Interrupts on detection of a match with Control Field 0 are enabled.</li></ul>       | R/W |  |  |  |  |

| b2     | CF1MIE | Control Field 1 Match Detected<br>Interrupt Enable  | O: Interrupts on detection of a match with Control Field 1 are disabled.  1: Interrupts on detection of a match with Control Field 1 are enabled.                                | R/W |  |  |  |  |

| b3     | PIBDIE | Priority Interrupt Bit Detected Interrupt<br>Enable | O: Interrupts on detection of the priority interrupt bit are disabled.  1: Interrupts on detection of the priority interrupt bit are enabled.                                    | R/W |  |  |  |  |

| b4     | BCDIE  | Bus Collision Detected Interrupt Enable             | O: Interrupts on detection of a bus collision are disabled.  1: Interrupts on detection of a bus collision are enabled.                                                          | R/W |  |  |  |  |

| b5     | AEDIE  | Valid Edge Detected Interrupt Enable                | O: Interrupts on detection of a valid edge are disabled.  1: Interrupts on detection of a valid edge are enabled.                                                                | R/W |  |  |  |  |

| b7, b6 | _      | Reserved                                            | These bits are read as 0. The write value should be 0.                                                                                                                           | R/W |  |  |  |  |

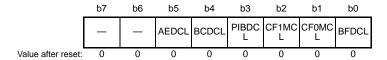

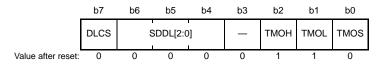

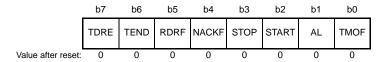

# 33.2.27 Status Register (STR)

Address(es): SCI12.STR 0008 B327h

| Bit    | Bit Symbol Bit Name Description |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                | R/W |  |  |  |

|--------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| b0     | BFDF                            | Break Field Low Width<br>Detection Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>[Setting conditions]</li> <li>Detection of the low width for a Break Field</li> <li>Completion of the output of the low width for a Break Field</li> <li>Underflow of the timer</li> <li>[Clearing condition]</li> <li>Writing 1 to the STCR.BFDCL bit</li> </ul> | R   |  |  |  |

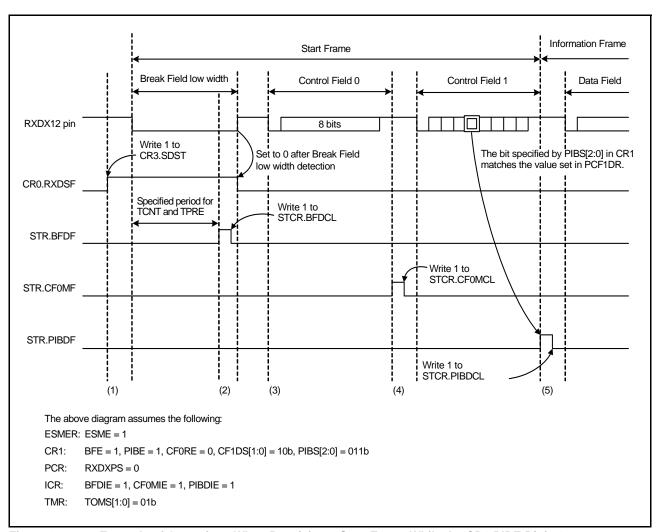

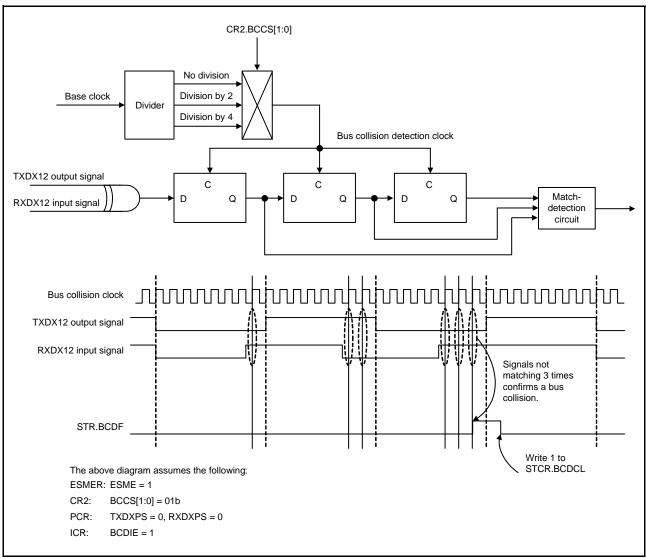

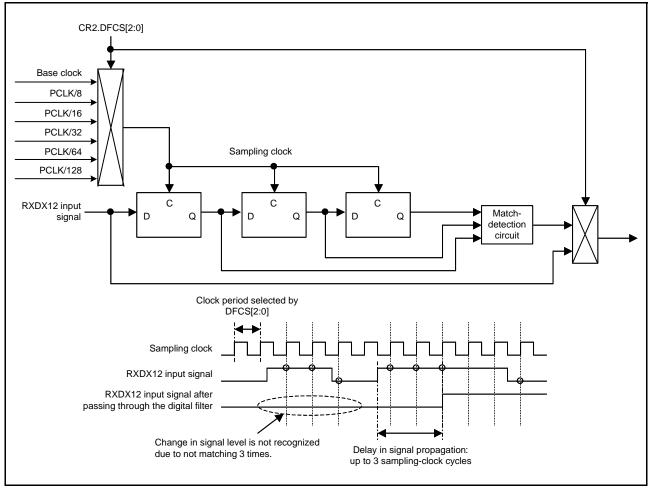

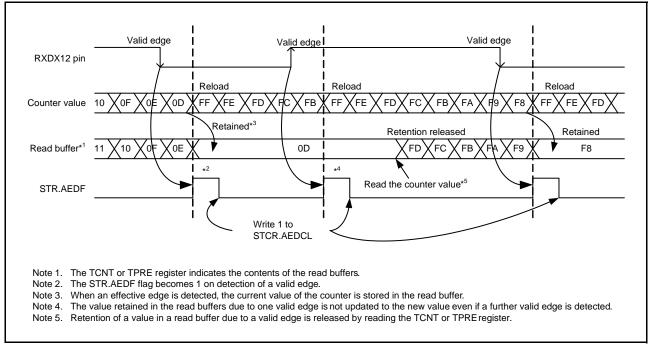

| b1     | CF0MF                           | Flag  • A match between the value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and the set value received in Control Field 0 and th |                                                                                                                                                                                                                                                                            |     |  |  |  |