# 23.7 EIC Register Summary

| Offset | Name       | Bit Pos. | 7       | 6 | 5           | 4         | 3         | 2 | 1 1           | 0      |

|--------|------------|----------|---------|---|-------------|-----------|-----------|---|---------------|--------|

| 0x00   | CTRLA      | 7:0      |         |   |             | CKSEL     |           |   | ENABLE        | SWRST  |

| 0x01   | NMICTRL    | 7:0      |         |   |             | NMIASYNCH | NMIFILTEN |   | NMISENSE[2:0] |        |

| 0x02   | NMIFLAG    | 7:0      |         |   |             |           |           |   |               | NMI    |

| 0x03   | Reserved   |          |         |   |             |           |           |   |               |        |

|        |            | 7:0      |         |   |             |           |           |   | ENABLE        | SWRST  |

|        |            | 15:8     |         |   |             |           |           |   |               |        |

| 0x04   | SYNCBUSY   | 23:16    |         |   |             |           |           |   |               |        |

|        |            | 31:24    |         |   |             |           |           |   |               |        |

|        |            | 7:0      |         |   |             |           |           |   |               |        |

|        |            | 15:8     |         |   |             |           |           |   |               |        |

| 0x08   | EVCTRL     | 23:16    |         |   |             |           |           |   |               |        |

|        |            | 31:24    |         |   |             |           |           |   |               |        |

|        |            | 7:0      |         |   |             |           |           |   |               |        |

|        |            | 15:8     |         |   |             |           |           |   |               |        |

| 0x0C   | INTENCLR   | 23:16    |         |   |             |           |           |   |               |        |

|        |            | 31:24    |         |   |             |           |           |   |               |        |

|        |            | 7:0      |         |   |             |           |           |   |               |        |

|        |            | 15:8     |         |   |             |           |           |   |               |        |

| 0x10   | INTENSET   | 23:16    |         |   |             |           |           |   |               |        |

|        |            | 31:24    |         |   |             |           |           |   |               |        |

|        |            | 7:0      |         |   |             |           |           |   |               |        |

|        |            | 15:8     |         |   |             |           |           |   |               |        |

| 0x14   | INTFLAG    | 23:16    |         |   |             |           |           |   |               |        |

|        |            | 31:24    |         |   |             |           |           |   |               |        |

|        |            | 7:0      |         |   |             |           |           |   |               |        |

|        |            | 15:8     |         |   |             |           |           |   |               |        |

| 0x18   | ASYNCH     | 23:16    |         |   |             |           |           |   |               |        |

|        |            | 31:24    |         |   |             |           |           |   |               |        |

|        |            | 7:0      | FILTEN1 |   | SENSE1[2:0] |           | FILTEN0   |   | SENSE0[2:0]   |        |

|        |            | 15:8     | FILTEN3 |   | SENSE3[2:0] |           | FILTEN2   |   | SENSE2[2:0]   |        |

| 0x1C   | CONFIG     | 23:16    |         |   |             |           |           |   |               |        |

|        |            | 31:24    |         |   |             |           |           |   |               |        |

| 0x20   |            |          |         |   |             |           |           |   |               |        |

|        | Reserved   |          |         |   |             |           |           |   |               |        |

| 0x2F   |            |          |         |   |             |           |           |   |               |        |

|        |            | 7:0      |         |   |             |           |           |   |               |        |

| 020    | DEDOUNCEN  | 15:8     |         |   |             |           |           |   |               |        |

| 0x30   | DEBOUNCEN  | 23:16    |         |   |             |           |           |   |               |        |

|        |            | 31:24    |         |   |             |           |           |   |               |        |

|        |            | 7:0      |         |   |             |           |           |   |               |        |

| 0.24   | DDDECCALED | 15:8     |         |   |             |           |           |   |               |        |

| 0x34   | DPRESCALER | 23:16    |         |   |             |           |           |   |               | TICKON |

|        |            | 31:24    |         |   |             |           |           |   |               |        |

|        |            | 7:0      |         |   |             |           |           |   |               |        |

| 0x38   | PINSTATE   | 15:8     |         |   |             |           |           |   |               |        |

| UX38   | PINSIAIE   | 23:16    |         |   |             |           |           |   |               |        |

|        |            | 31:24    |         |   |             |           |           |   |               |        |

# 23.8 Register Description

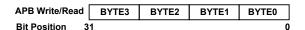

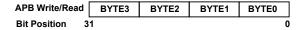

Registers can be 8, 16 or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

#### 23.8.1 Control A

Name: CTRLA Offset: 0x00 Reset: 0x00

**Property:** PAC Write-Protection, Write-Synchronized

| Bit    | 7 | 6 | 5 | 4     | 3 | 2 | 1      | 0     |

|--------|---|---|---|-------|---|---|--------|-------|

|        |   |   |   | CKSEL |   |   | ENABLE | SWRST |

| Access |   |   |   | RW    |   |   | RW     | W     |

| Reset  |   |   |   | 0     |   |   | 0      | 0     |

#### Bit 4 - CKSEL Clock Selection

The EIC can be clocked either by GCLK\_EIC (when a frequency higher than 32.768 KHz is required for filtering) or by CLK\_ULP32K (when power consumption is the priority).

This bit is not Write-Synchronized.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | The EIC is clocked by GCLK_EIC.   |

| 1     | The EIC is clocked by CLK_ULP32K. |

#### Bit 1 - ENABLE Enable

Due to synchronization there is a delay between writing to CTRLA.ENABLE until the peripheral is enabled/disabled. The value written to CTRLA.ENABLE will read back immediately and the Enable bit in the Synchronization Busy register will be set (SYNCBUSY.ENABLE=1). SYNCBUSY.ENABLE will be cleared when the operation is complete.

This bit is not Enable-Protected.

This bit is Write-Synchronized.

|       | ,                    |

|-------|----------------------|

| Value | Description          |

| 0     | The EIC is disabled. |

| 1     | The EIC is enabled.  |

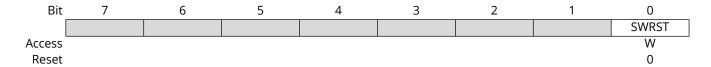

### **Bit 0 - SWRST** Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the EIC to their initial state, and the EIC will be disabled. Writing a '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the Reset is complete.

CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the Reset is complete.

This bit is not Enable-Protected.

This bit is Write-Synchronized.

|       | · · · · · · · · · · · · · · · · · · · |

|-------|---------------------------------------|

| Value | Description                           |

| 0     | There is no ongoing reset operation.  |

| 1     | The reset operation is ongoing.       |

### 23.8.2 Non-Maskable Interrupt Control

Name: NMICTRL Offset: 0x01 Reset: 0x00

**Property:** PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4         | 3         | 2   | 1            | 0   |

|--------|---|---|---|-----------|-----------|-----|--------------|-----|

|        |   |   |   | NMIASYNCH | NMIFILTEN |     | NMISENSE[2:0 | ]   |

| Access |   |   |   | R/W       | R/W       | R/W | R/W          | R/W |

| Reset  |   |   |   | 0         | 0         | 0   | 0            | 0   |

### Bit 4 - NMIASYNCH NMI Asynchronous Edge Detection Mode

The NMI edge detection can be operated synchronously or asynchronously to the EIC clock.

|       | •                |                   |            | -       | <br>, |  |

|-------|------------------|-------------------|------------|---------|-------|--|

| Value | Description      |                   |            |         |       |  |

| 0     | The NMI edge det | ection is synchro | nously ope | erated. |       |  |

| 1     | The NMI edge det | ection is asynchr | onously op | erated. |       |  |

### Bit 3 - NMIFILTEN Non-Maskable Interrupt Filter Enable

| Va | lue | Description             |

|----|-----|-------------------------|

| 0  |     | NMI filter is disabled. |

| 1  |     | NMI filter is enabled.  |

### Bits 2:0 - NMISENSE[2:0] Non-Maskable Interrupt Sense Configuration

These bits define on which edge or level the NMI triggers.

**Note:** NMI cannot be triggered based on level but it is always based on edge.

| Value    | Name | Description            |  |  |  |

|----------|------|------------------------|--|--|--|

| 0x0      | NONE | No detection           |  |  |  |

| 0x1      | RISE | ising-edge detection   |  |  |  |

| 0x2      | FALL | Falling-edge detection |  |  |  |

| 0x3      | BOTH | Both-edge detection    |  |  |  |

| 0x4      | HIGH | High-level detection   |  |  |  |

| 0x5      | LOW  | Low-level detection    |  |  |  |

| 0x6 - 0x | 7 –  | Reserved               |  |  |  |

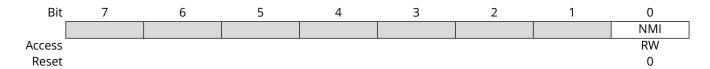

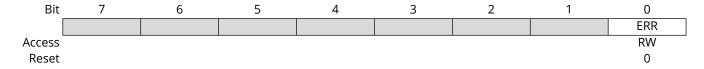

# 23.8.3 Non-Maskable Interrupt Flag Status and Clear

Name: NMIFLAG Offset: 0x2

**Reset:** 0x00

## Bit 0 - NMI Non-Maskable Interrupt

This flag is cleared by writing a '1' to it.

This flag is set when the NMI pin matches the NMI sense configuration, and will generate an interrupt request.

Writing a '0' to this bit has no effect.

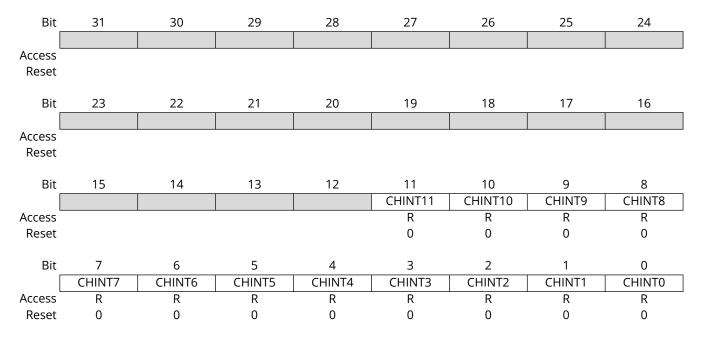

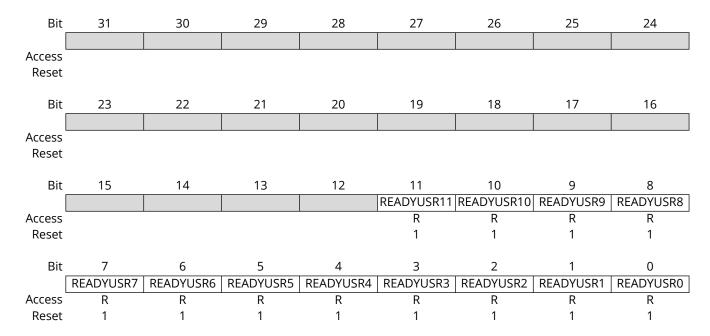

# 23.8.4 Synchronization Busy

Name: SYNCBUSY Offset: 0x04

**Reset:** 0x00000000

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25     | 24    |

|--------|----|----|----|----|----|----|--------|-------|

|        |    |    |    |    |    |    |        |       |

| Access |    |    |    |    |    |    |        |       |

| Reset  |    |    |    |    |    |    |        |       |

|        |    |    |    |    |    |    |        |       |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17     | 16    |

|        |    |    |    |    |    |    |        |       |

| Access |    |    |    |    |    |    |        |       |

| Reset  |    |    |    |    |    |    |        |       |

|        |    |    |    |    |    |    |        |       |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9      | 8     |

|        |    |    |    |    |    |    |        |       |

| Access |    |    |    |    |    |    |        |       |

| Reset  |    |    |    |    |    |    |        |       |

|        |    |    |    |    |    |    |        |       |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1      | 0     |

|        |    |    |    |    |    |    | ENABLE | SWRST |

| Access |    |    |    |    |    |    | R      | R     |

| Reset  |    |    |    |    |    |    | 0      | 0     |

# Bit 1 - ENABLE Enable Synchronization Busy Status

| Value | Description                                             |

|-------|---------------------------------------------------------|

| 0     | Write synchronization for CTRLA.ENABLE bit is complete. |

| 1     | Write synchronization for CTRLA.ENABLE bit is ongoing.  |

# **Bit 0 - SWRST** Software Reset Synchronization Busy Status

**Note:** During a SWRST, access to registers/bits without SWRST are disallowed until SYNCBUSY.SWRST cleared by hardware.

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Write synchronization for CTRLA.SWRST bit is complete. |

| 1     | Write synchronization for CTRLA.SWRST bit is ongoing.  |

### 23.8.5 Event Control

Name: EVCTRL 0x08

**Reset:** 0x00000000

**Property:** PAC Write-Protection, Enable-Protected

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|--------|----|----|----|----|----|----|----|----|

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|        |    |    |    |    |    |    |    |    |

| ٨٥٥٥٥  |    |    |    |    |    |    |    |    |

Access

# 23.8.6 Interrupt Enable Clear

Name: INTENCLR Offset: 0x0C

**Reset:** 0x00000000

**Property:** PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|--------|----|----|----|----|----|----|----|----|

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        | _  | _  | _  | _  | _  | _  | _  |    |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

# 23.8.7 Interrupt Enable Set

Name: INTENSET

Offset: 0x10

**Reset:** 0x00000000

**Property:** PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear (INTENCLR) register.

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|--------|----|----|----|----|----|----|----|----|

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

# 23.8.8 Interrupt Flag Status and Clear

Name: INTFLAG Offset: 0x14

**Reset:** 0x00000000

Property: -

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|--------|----|----|----|----|----|----|----|----|

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|        |    |    |    |    |    |    |    |    |

| ۸      |    |    |    |    |    |    |    |    |

Access

# 23.8.9 External Interrupt Asynchronous Mode

Name: ASYNCH Offset: 0x18

**Reset:** 0x00000000

**Property:** PAC Write-Protection, Enable-Protected

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|--------|----|----|----|----|----|----|----|----|

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|        |    |    |    |    |    |    |    |    |

| ۸      |    |    |    |    |    |    |    |    |

Access

# 23.8.10 External Interrupt Sense Configuration

Name: CONFIG Offset: 0x1C

**Reset:** 0x00000000

**Property:** PAC Write-Protection, Enable-Protected

| Bit    | 31      | 30 | 29          | 28 | 27      | 26          | 25          | 24 |

|--------|---------|----|-------------|----|---------|-------------|-------------|----|

|        |         |    |             |    |         |             |             |    |

| Access |         |    |             |    |         |             |             |    |

| Reset  |         |    |             |    |         |             |             |    |

|        |         |    |             |    |         |             |             |    |

| Bit    | 23      | 22 | 21          | 20 | 19      | 18          | 17          | 16 |

|        |         |    |             |    |         |             |             |    |

| Access |         |    |             |    |         |             |             |    |

| Reset  |         |    |             |    |         |             |             |    |

|        |         |    |             |    |         |             |             |    |

| Bit    | 15      | 14 | 13          | 12 | 11      | 10          | 9           | 8  |

|        | FILTEN3 |    | SENSE3[2:0] |    | FILTEN2 | SENSE2[2:0] |             |    |

| Access | RW      | RW | RW          | RW | RW      | RW          | RW          | RW |

| Reset  | 0       | 0  | 0           | 0  | 0       | 0           | 0           | 0  |

|        |         |    |             |    |         |             |             |    |

| Bit    | 7       | 6  | 5           | 4  | 3       | 2           | 1           | 0  |

|        | FILTEN1 |    | SENSE1[2:0] |    |         |             | SENSE0[2:0] |    |

| Access | RW      | RW | RW          | RW | RW      | RW          | RW          | RW |

| Reset  | 0       | 0  | 0           | 0  | 0       | 0           | 0           | 0  |

|        |         |    |             |    |         |             |             |    |

# **Bits 3, 7, 11, 15 - FILTENx** Filter Enable x [x=3..0]

**Note:** The filter must be disabled if the asynchronous detection is enabled.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Filter is disabled for EXTINT[x] input. |

| 1     | Filter is enabled for EXTINT[x] input.  |

# **Bits 0:2, 4:6, 8:10, 12:14 - SENSEx** Input Sense Configuration x [x=3..0]

These bits define on which edge or level the interrupt or event for EXTINT[x] will be generated.

| Value     | Name | Description            |

|-----------|------|------------------------|

| 0x0       | NONE | No detection           |

| 0x1       | RISE | Rising-edge detection  |

| 0x2       | FALL | Falling-edge detection |

| 0x3       | BOTH | Both-edge detection    |

| 0x4       | HIGH | High-level detection   |

| 0x5       | LOW  | Low-level detection    |

| 0x6 - 0x7 | -    | Reserved               |

### 23.8.11 Debouncer Enable

Name: DEBOUNCEN

Offset: 0x30

**Reset:** 0x00000000

**Property:** PAC Write-Protection, Enable-Protected

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|--------|----|----|----|----|----|----|----|----|

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|        |    |    |    |    |    |    |    |    |

| A      |    |    |    |    |    |    |    |    |

Access

### 23.8.12 Debouncer Prescaler

Name: DPRESCALER

**Offset:** 0x34

**Reset:** 0x00000000

**Property:** PAC Write-Protection, Enable-Protected

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24     |

|--------|----|----|----|----|----|----|----|--------|

|        |    |    |    |    |    |    |    |        |

| Access |    |    |    |    |    |    |    |        |

| Reset  |    |    |    |    |    |    |    |        |

|        |    |    |    |    |    |    |    |        |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|        |    |    |    |    |    |    |    | TICKON |

| Access |    |    |    |    |    |    |    | RW     |

| Reset  |    |    |    |    |    |    |    | 0      |

|        |    |    |    |    |    |    |    |        |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8      |

|        |    |    |    |    |    |    |    |        |

| Access |    |    |    |    |    |    |    |        |

| Reset  |    |    |    |    |    |    |    |        |

|        |    |    |    |    |    |    |    |        |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

|        |    |    |    |    |    |    |    |        |

| Access |    | •  |    |    |    |    |    |        |

# **Bit 16 - TICKON** Pin Sampler frequency selection

Reset

This bit selects the clock used for the sampling of bounce during transition detection.

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | The bounce sampler is using GCLK_EIC.                |

| 1     | The bounce sampler is using the low frequency clock. |

### 23.8.13 Pin State

Name: PINSTATE 0x38

**Reset:** 0x00000000

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|--------|----|----|----|----|----|----|----|----|

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|        |    |    |    |    |    |    |    |    |

| Access |    | •  |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|        |    |    |    |    |    |    |    |    |

| Access |    |    |    |    |    |    |    |    |

| Reset  |    |    |    |    |    |    |    |    |

|        |    |    |    |    |    |    |    |    |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|        |    |    |    |    |    |    |    |    |

| ۸      |    |    |    |    |    |    |    |    |

Access

# 24. Flash Memory

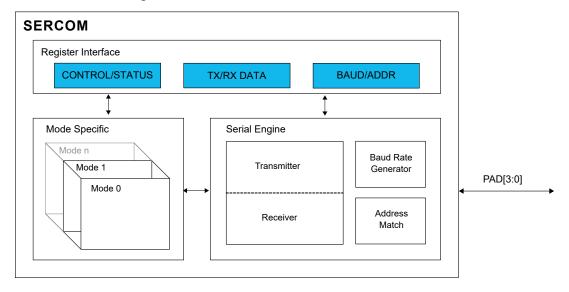

### 24.1 Overview

The PIC32CX-BZ2 devices contain a single bank of Flash memory with their Program Flash Memory (PFM) partition and Boot Flash Memory (BFM) partition for storing user code or non-volatile data. The Flash controller is used to access the Flash memory. The peripheral bus interface is used for commands and configuration of the Flash controller.

### 24.2 Features

#### **Flash Controller**

- PB-Bridge-D interface that provides access to the Flash controller registers

- AHB Initiator for bus hosted reads the row programming data from SRAM

- Write Protect for Program Flash (PFM)

- Single page protection resolution

- Protect "Less Than" Address

- Protect "Greater Than or Equal to" Address

- Individual page write protection for boot Flash (BFM)

- Error-correction code (ECC) support

- Supports chip and page erase

- · Supports Single Word, Quad Word and row program options

- Supports flash Erase/Retry to increase Retention and Endurance

### **Flash Memory**

- 128-bit wide Flash Memory Access

- 4 Kbytes page size

- Row size is 1 KB (256 IW)

- Flash-based OTP (one-time-programmable) page

The Flash controller allows the Flash memory to be accessed through the following methods:

- 1. Run-Time Self-Programming (RTSP)

- 2. Serial Wire Debug (SWD) programming using DSU (See *Device Service Unit (DSU)* from Related Links and *PIC32CX-BZ2 Programming Specification*.)

#### **Related Links**

12. Device Service Unit (DSU)

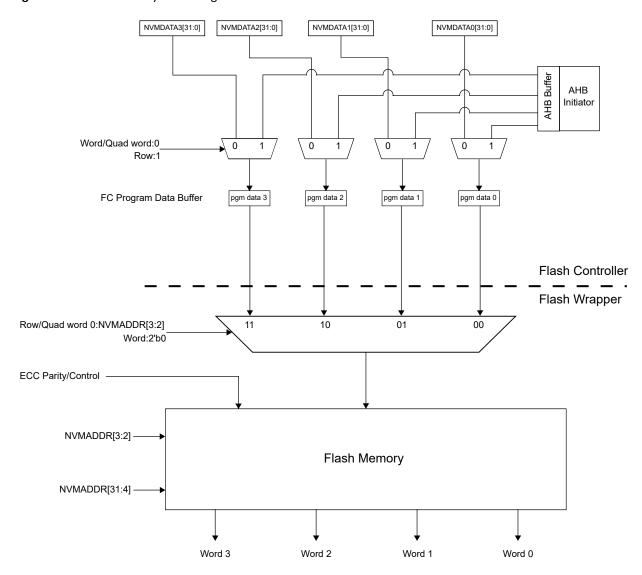

# 24.3 Functional Block Diagram

Figure 24-1. Flash Memory Block Diagram

# 24.4 Flash Memory Addressing

Flash memory addressing uses physical addresses only. For more information on addressing, see *Product Memory Mapping Overview* from Related Links.

#### **Related Links**

8. Product Memory Mapping Overview

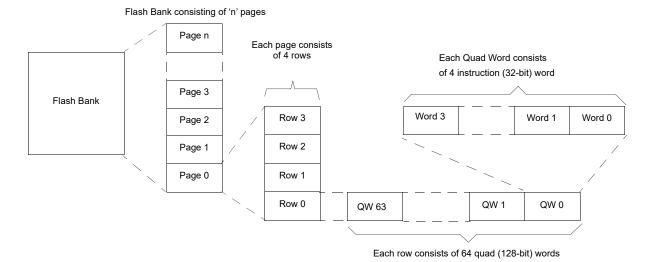

# 24.5 Memory Configuration

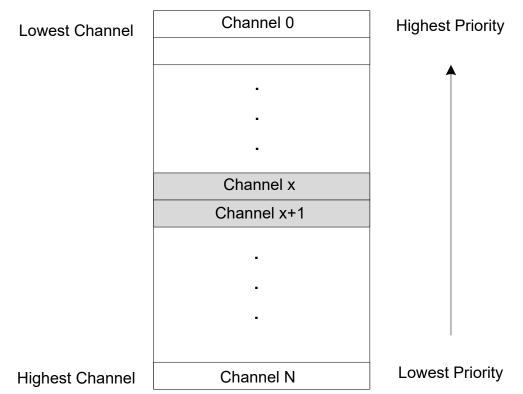

### 24.5.1 Flash Memory Construction

Flash memory is divided into pages. A page is the smallest unit of memory that can be erased at one time. Each page of memory is segmented into four rows. A row is the largest unit of memory that can be programmed at one time. A row consists of 64 Quad (128-bit) Word. Each Quad Word consists of a four instruction (32-bit) Word. Flash memory can be programmed in rows, Quad Word (128-bit) or Single Word (32-bit) units.

Figure 24-2. Flash Construction

### 24.5.2 Flash Memory Organization

The Device Flash memory is divided into two logical Flash partitions:

- 1. Main Program Flash Memory (PFM)

- 2. Boot/Configuration Flash Memory (BFM)

- a. Boot Flash

- b. Device/Boot Configuration Device and boot configuration data

- c. OTP (One Time Programmable) User system calibration data

Each Flash section has a different protection status; refer to the following table.

Table 24-1. Protection Status

| Flash Partition | Memory Region                   | Write Protection               | Erase Protection                             | Chip Erase through DSU |

|-----------------|---------------------------------|--------------------------------|----------------------------------------------|------------------------|

| BFM             | Boot Flash                      | Yes. Page-wise<br>Configurable | Yes. Page-wise<br>Configurable               | Erased                 |

|                 | Device/Boot<br>Configuration    | Yes. Configurable              | Yes. Configurable                            | Erased                 |

|                 | OTP (One-Time-<br>Programmable) | Yes. Configurable              | Always Erase protected.<br>Can not be erased | Not Erased             |

| PFM             | Program Flash                   | Yes. Configurable              | Yes. Configurable                            | Erased                 |

# 24.6 Boot Flash Memory (BFM) Partitions

### 24.6.1 BFM Write Protection

Pages in the BFM regions can be protected individually using bits in the NVMLBWP register. At Reset, all pages are in a write-protected state and must be disabled prior to performing any programming operations on the BFM regions. There is also an unlock bit, ULOCK(NVMLBWP[31]), that is set at Reset and can be cleared by the user software. When cleared, changes to write protection for that region can no longer be made. Once cleared, the ULOCK bit can only be set by a Reset.

The NVMLBWP write-protect register can only be changed when the unlock sequence is followed. See NVMKEY Register Unlocking Sequence from Related Links.

#### **Related Links**

24.11. NVMKEY Register Unlocking Sequence

# 24.7 Program Flash Memory (PFM) Partitions

### 24.7.1 PFM Write Protection

Write protection for the PFM region is implemented by pages, defined by the NVMPWPLT and NVMPWPGTE registers. The NVMPWP\* registers define an area within the program space (PFM) that is write-protected. This write-protected address resolves to Flash page boundaries; therefore, the 12 LSBs for a 4 KB page Flash of any address written to the NVMPWP\* registers are ignored. The width of each NVMPWP\* address register is determined by the size of the Flash. The NVMPWPLT register is used to set the Program Flash pages lower than the provided address as write-protected. The NVMPWPGTE register is used to set the Program Flash pages greater than or equal to the provided address as write-protected. Therefore, a value of all 0s in the NVMPWPLT register and all 1s in the NVMPWPGTE register results in no region of Flash being write-protected (default state at Reset).

There is also an unlock bit, ULOCK (NVMPWPLT [31] and NVMPWPGTE[31]), that is set at Reset and can be cleared by the user software. When cleared, changes to the write-protection of the PFM can no longer be made, including the ULOCK bit. The NVMPWPLT and NVMPWPGTE write-protected register can only be changed when the unlock sequence is followed. See *NVMKEY Register Unlocking Sequence* from Related Links.

#### **Related Links**

24.11. NVMKEY Register Unlocking Sequence

# 24.8 Error Correcting Code (ECC) and Flash Programming

The PIC32CX-BZ2 devices incorporate Error Correcting Code (ECC) features that detect and correct errors resulting in extended Flash memory life. For more details on this feature, see *Prefetch Cache* from Related Links.

ECC is implemented in 128-bit Quad Flash Words or 32-bit Single Word. As a result, when programming Flash memory on a device where ECC is employed, the programming operation must be, at minimum, four instruction Words or in groups of four instruction Words. This is the reason that the Quad Word programming command exists and why row programming always programs multiples of four Words.

For a given software application, ECC can be enabled at all times, disabled at all times or dynamically enabled using the ECCTL Configuration bits in the CFGCON0 register. When ECC is enabled at all times, the Single Word NVMOP programming command does not function and the Quad Word is the smallest unit of memory that can be programmed. When ECC is disabled or enabled dynamically, both the Single Word and Quad Word programming NVMOP commands are functional and the programming method used determines how ECC is handled.

In the case of dynamic ECC, if the memory was programmed with the Singe Word command, ECC is turned off for that Word, and, when it is read, no error correction is performed. If the memory was programmed with the Quad Word or Row Programming commands, ECC data is written and tested for errors (and corrected if needed) when read. The following table describes the different ECC scenarios.

**Table 24-2.** ECC Programming Summary

| <b>ECCCTL Setting</b> | Programming Operatio | Data Read       |           |                                         |

|-----------------------|----------------------|-----------------|-----------|-----------------------------------------|

|                       | Single Word Write    | Quad Word Write | Row Write |                                         |

| Disabled              | Allowed              | Allowed         | Allowed   | ECC is never applied on a Flash read    |

| Enabled               | Not allowed          | Allowed         | Allowed   | ECC is applied on every Flash Word read |

| continued                            |                                                                               |                                                             |                                                             |                                                                |

|--------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------|

| ECCCTL Setting Programming Operation |                                                                               |                                                             | Data Read                                                   |                                                                |

|                                      | Single Word Write                                                             | Quad Word Write                                             | Row Write                                                   |                                                                |

| Dynamic                              | Allowed but when used,<br>the programmed word<br>is flagged to NOT USE<br>ECC | Writes ECC data<br>and flags programmed<br>words to USE ECC | Writes ECC data<br>and flags programmed<br>words to USE ECC | ECC is only applied on<br>words that are flagged<br>to USE ECC |

**Note:** When using dynamic ECC, all non-ECC locations must be programmed with the 32-bit Word programming command, while all ECC-enabled locations must be programmed with a 128-bit Quad Word or Row programming command. Divisions between ECC and non-ECC memory must be on even Quad Word boundaries (address bits 0 through 3 are equal to '0').

#### **Related Links**

9. Prefetch Cache (PCHE)

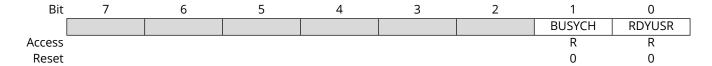

### 24.9 Interrupts

An interrupt is generated when the WR bit is cleared by the Flash Controller upon completion of a Flash program or erase operation. The interrupt event will cause a CPU interrupt if it was configured and enabled in the Nested Interrupt Vector Controller. See *Nested Vector Interrupt Controller (NVIC)* from Related Links for the vector mapping table. The interrupt occurs regardless of the outcome of the program or erase operation, successful or unsuccessful. The only exception is the No Operation (NOP) programming operation (NVMOP = 0), which is used to manually clear the error flags and does not create an interrupt event on completion but does clear the WR bit.

The Flash Controller interrupts are not persistent, and, therefore, no additional steps are required to clear the cause or source of the interrupt.

Once the Interrupt Controller is configured, the Flash event causes the CPU to jump to the vector assigned to the Flash event. The CPU starts executing the code at the vector address. The user software at this vector address must perform the required operations and, then, exit.

#### **Related Links**

10.2. Nested Vector Interrupt Controller (NVIC)

#### 24.9.1 Interrupts and CPU Stalling

Code cannot be fetched by the CPU from the same Flash bank, either BFM or PFM, that is the target of the programming operation. When this operation is attempted, the CPU will cease to execute code (stall) while the programming operation is in progress. CPU code execution does not resume until the programming operation is complete, and, when this occurs, any pending interrupts, including those from the Flash Controller, will be processed in order of priority.

**Note:** Code that is already loaded into the processor cache will continue to execute up to the point where an attempt is made to fetch code or data from the same Flash bank as the active programming operation. At this point the CPU will stall.

The stalling of the CPU can also be avoided by placing any needed executable code in SRAM during Flash programming.

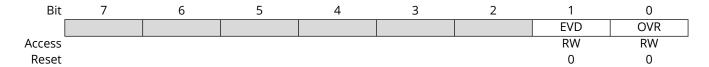

### 24.10 Error Detection

The NVMCON register includes two bits for detecting error conditions during a program or erase operation. They are Low-Voltage detect error, LVDERR bit (NVMCON[12]), and Write Error, WRERR bit (NVMCON[13]).

The WRERR is set each time the WR bit (NVMCON[15]) is set, initiating a programming operation. When the Flash operation is complete, indicated by hardware clearing the value of the WR bit (i.e., WR bit is set to '0'), hardware will update the value in the WRERR bit to indicate if an error occurred. Firmware must check the value of the WR bit to see if the Flash operation completed

before checking the value of the WRERR bit. When the WRERR bit is set, any future attempt to initiate programming or erase operation is ignored. WRERR must be cleared before commencing Flash program or erase operations.

The LVDERR bit is set when a Brown-out Reset (BOR) occurs during a programming operation. The only Reset that clears the LVDERR bit is a Power-on Reset (POR). Other Reset types do not affect the LVDERR bit. When the LVDERR bit is set, any attempt to initiate programming or erase operation is ignored. The LVDERR bit must be cleared before commencing Flash program or erase operations.

Both the WRERR and LVDERR bits must be cleared manually in software by initiating a Flash operation (setting WR) referred to as NOP (0x00) (see the NVMOP bit fields).

**Note:** Executing the NVMOP NOP command clears WRERR, LVDERR and WR bits, but does not generate an interrupt event on completion.

Table 24-3. Programming Error Cause and Effects

| Cause of Error                                                            | Effect on Programming Erase<br>Operation                        | Indication            |

|---------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------|

| A low-voltage event occurred during a programming sequence.               | The last programming or erase operation may not have completed. | LVDERR = 1, WRERR = 1 |

| A non-POR Reset occurred during programming.                              | Programming or erase operation is aborted.                      | WRERR = 1             |

| Attempt to program or erase a page out of the Flash memory range.         | Erase or programming operation is not initiated.                | WRERR = 1             |

| Attempt to erase or program a write-protected PFM page.                   | Erase or programming operation is not initiated.                | WRERR = 1             |

| Attempt to erase or program a write-protected BFM page.                   | Operation occurs, but the page is not programmed or erased.     | WRERR = 0             |

| Bus host error or row programming data underrun error during programming. | Programming or erase operation is aborted.                      | WRERR = 1             |

# 24.11 NVMKEY Register Unlocking Sequence

Important register settings that could compromise the Flash memory if inadvertently changed are protected by a register unlocking sequence. This feature is implemented using the NVMKEY register. The NVMKEY register is a write-only register that is used to implement an unlock sequence to help prevent accidental writes or erasures of Flash memory.

In some instances, the operation is also dependent on the setting of the WREN bit (NVMCON[14]), as shown in the following table.

Table 24-4. NVMKEY Register Unlocking and WREN

| Operation                                                   | WREN Setting | Unlock Sequence Required |

|-------------------------------------------------------------|--------------|--------------------------|

| Changing value of NVMOP[3:0] (NVMCON[3:0])                  | 0            | No                       |

| Setting WR (NVMCON[15]) to start a write or erase operation | 1            | Yes                      |

| Changing any fields in the NVMPWP* register                 | _            | Yes                      |

| Changing any fields in the NVMLBWP register                 | _            | Yes                      |

The following steps must be followed in the exact order as shown to enable writes to registers that require this unlock sequence:

- 1. Write 0x00000000 to NVMKEY.

- 2. Write 0xAA996655 to NVMKEY.

- 3. Write 0x556699AA to NVMKEY.

- 4. Write the value to the register NVMCON, NVMCON2, NVMPWP\* or NVMLBWP requiring the unlock sequence.

When using the unlock sequence to set or clear bits in the NVMCON register, as shown in Step 4, Steps 2 through 4 must be executed without any other activity on the peripheral bus that is in use by the Flash Controller. Interrupts and DMA transfers that access the same peripheral bus as the Flash Controller must be disabled. In addition, the operation in Step 4 must be atomic. The Set, Clear and Invert registers may be used, where applicable, for the target register in Step 4.

The following code shows code written in the C language to initiate a NVM Operation (NVMOP) command. In this particular example, the WR bit is being set in the NVMCON register and, therefore, must include the unlock sequence.

#### Initiate NVM Operation (System Unlock Sequence Example):

```

void NVMInitiateOperation(void)

{

// Disable Interrupts

asm volatile("di%0" : "=r"(int_status));

uint32_t globalInterruptState= __get_PRIMASK();

// Disable Interrupts

__disable_irq();

NVMKEY = 0x0;

NVMKEY = 0xAA996655;

NVMKEY = 0x556699AA;

NVMCONSET = 1 << 15;// must be an atomic instruction

// Restore Interrupts

__set_PRIMASK(globalInterruptState);

}</pre>

```

**Note:** Once the unlock codes are written to the NVMKEY register, the next activity on the same peripheral bus as the Flash Controller will Reset the lock. As a result, only atomic operations can be used. Use of the NVMCONSET register sets the WR bit in a single instruction without changing other bits in the register. Using NVMCONbits.WR = 1 will fail, as this line of code compiles to a read-modify-write sequence.

## 24.12 Word Programming

The smallest block of data that can be programmed in a single operation is one Flash write Word (32-bit). The data to be programmed must be written to the NVMDATA0 register, and the address of the Word must be loaded into the NVMADDR register before the programming sequence is initiated. The instruction Word at the physical location pointed to by the NVMADDR register is, then, programmed. Programming occurs on 32-bit Word boundaries; therefore, bits '0' and '1' of the NVMADDR register are ignored.

When a Word is programmed, it must be erased before it can be programmed again, even if changing a bit from an erased '1' state to a '0' state.

Word programming will only succeed if the target address is in a page that is not write-protected. Programming to a write-protected PFM page will fail and result in the WRERR bit being set in the NVMCON register. Programming a write-protected BFM page will fail but does not set the WRERR bit.

A programming sequence consists of the following steps:

- 1. Write 32-bit data to be programmed to the NVMDATA0 register.

- 2. Load the NVMADDR register with the address to be programmed.

- 3. Set the WREN bit = 1 and NVMOP bits = 1 in the NVMCON register. This defines and enables the programming operation.

- 4. Initiate the programming operation. (See *NVMKEY Register Unlocking Sequence* from Related Links.)

- 5. Monitor the WR bit of the NVMCON register to flag completion of the operation.

- 6. Clear the WREN bit in the NVMCON register.

- 7. Check for errors and process accordingly.

The following code shows code for Word programming, where a value of 0x12345678 is programmed into location 0x1008000.

#### **Word Programming Code Example:**

```

// Set up Address and Data Registers

NVMADDR= 0x1008000;  // physical address

NVMDATA0 = 0x12345678;  // value

// set the operation, assumes WREN = 0

NVMCONbits.NVMOP = 0x1; // NVMOP for Word programming

// Enable Flash for write operation and set the NVMOP

NVMCONbits.WREN = 1;

// Start programming

NVMInitiateOperation();

// see Initiate NVM Operation (Unlock Sequence

Example)

// Wait for WR bit to clear

while (NVMCONbits.WR);

// Disable future Flash Write/Erase operations

NVMCONbits.WREN = 0;

// Check Error Status

if(NVMCON & 0x3000)

// mask for WRERR and LVDERR

// process errors

```

#### **Related Links**

24.11. NVMKEY Register Unlocking Sequence

# 24.13 Quad Word Programming

The process for Quad Word programming is identical to Word programming except that all four of the NVMDATAx registers are used. The value of the NVMDATA0 register is programmed at address NVMADDR, NVMDATA1 at NVMADDR + 0x4, NVMDATA2 at NVMADDR + 0x8, and NVMDATA3 at address NVMDATA + 0xC.

Quad Word programming is always performed on a Quad Word boundary; therefore, NVMADDR address bits 3 through 0 are ignored.

Quad Word programming will only succeed if the target address is in a page that is not write-protected. When a Quad Word is programmed, it must be erased before any Word in it can be programmed again, even if changing a bit from an erased '1' state to a '0' state.

Where a value of 0x11111111 is programmed into location 0x1008000, 0x222222222 into 0x1008004, 0x33333333 into 0x1008008, and 0x444444444 into location 0x100800C. Refer to the following code example for details.

#### **Quad Word Programming Code Example:**

# 24.14 Row Programming

The largest block of data that can be programmed is a row.

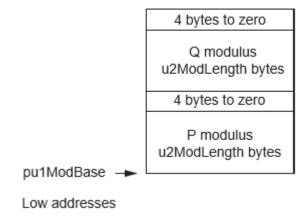

Unlike Word and Quad Word Programming where the data source is stored in SFR memory, Row programming source data is stored in SRAM. The NVMSRCADDR register is a pointer to the physical location of the source data for Row programming.

Like other Non-Volatile Memory (NVM) programming commands, the NVMADDR register points to the target address of the operation. Row programming always occurs on row boundaries with the row size of 1024, bits 0 through 9 of the NVMADDR register are ignored.

Row Word programming will only succeed if the target address is in a page that is not write-protected. When a row is programmed, it must be erased before any Word in it can be programmed again, even if changing a bit from an erased '1' state to a '0' state.

Array rowbuff is populated with data and programmed into a row located at physical address 0x1008000.

**Note:** When assigning the value to the NVMSRCADDR register, it must be converted to a physical address.

### **Row Programming Code Example:**

```

unsigned long rowbuff[256]; // example is for a 256 Word row size.

// loop counter

// put some data in the source buffer

for (x = 0; x < (size of (rowbuff) * size of (int)); x++)

((char *)rowbuff)[x] = x;

// set destination row address

NVMADDR = 0x1008000;

// row physical address

// set source address. Must be converted to a physical address.

NVMSRCADDR = (unsigned int)((int)rowbuff & 0x1FFFFFF);

// define Flash operation

NVMCONbits.NVMOP = 0x3; // NVMOP for Row programming

// Enable Flash Write

NVMCONbits.WREN = 1;

// commence programming

NVMInitiateOperation(); // see Initiate NVM Operation (Unlock Sequence

Example)

// Wait for WR bit to clear

while (NVMCONbits.WR);

// Disable future Flash Write/Erase operations

NVMCONbits.WREN = 0;

```

# 24.15 Page Erase

A Page Erase performs an erase of a single page of either PFM or BFM.

The page to be erased is selected using the NVMADDR register. Pages are always erased on page boundaries; therefore, for a device with an instruction Word page size of 4096, bits 0 through 11 of the NVMADDR register are ignored.

A Page Erase will only succeed if the target address is a page that is not write-protected. Erasing a write-protected page will fail and result in the WRERR bit being set in the NVMCON register.

The following code shows the code for a single Page Erase operation at address 0x1008000.

#### Page Erase Code Example:

```

// set destination page address

NVMADDR = 0x1008000;  // page physical address

// define Flash operation

NVMCONbits.NVMOP = 0x4; // NVMOP for Page Erase

// Enable Flash Write

NVMCONbits.WREN = 1;

// commence programming

NVMInitiateOperation();

// see Initiate NVM Operation (Unlock Sequence Example)

// Wait for WR bit to clear

while (NVMCONbits.WR);

// Disable future Flash Write/Erase operations

NVMCONbits.WREN = 0;

// Check Error Status

if(NVMCON & 0x3000)

// mask for WRERR and LVDERR bits

// process errors

```

#### 24.15.1 Page Erase Retry

Page Erase Retry is a method to improve the life of a Flash by attempting to erase again if the Page Erase was not successful. Page Erase Retry can only be used for a Page Erase.

Page Erase Retry works by increasing the voltage used on the Flash when erasing. Initially, the minimum voltage necessary is applied by setting the RETRY[1:0] bits (NVMCON2[9:8]) = 00. If the page erase is not successful, the voltage may be increased by incrementing the setting of the RETRY[1:0] bits.

**Note:** Each Flash page, as it ages and wears, may have different voltage requirements; therefore, a higher setting on one Flash page does not indicate that the same setting must be used on all pages.

The maximum voltage for Page Erase is used when the RETRY[1:0] bits = 11. If Page Erase is not successful after 7 trials, this means that the Flash for that page, or the Words that did not erase, must be considered "non-functional".

Together with the normal Page Erase controls, Page Erase Retry also uses the WS[4:0], CREAD1, VREAD1 and RETRY[1:0] bits in the NVMCON2 register. The ERS[3:0] bits (NVMCON2[31:28]) are for the benefit of software performing the programming sequence in the event that a drop in power causes a BOR event but not a POR event.

Perform the following steps to set up a Page Erase Retry:

- 1. Set the NVMADDR register with the address of the page to be erased.

- 2. Execute the write unlock sequence.

- 3. Save the value of the NVMCON2 register.

- 4. Do the following in the NVMCON2 register:

- a. Set the ERS[3:0] bits as desired.

- b. Set the WS[4:0] bits per the description.

- c. Set the VREAD1 bit to '1'.

- d. Set the CREAD1 bit to '1'.

- e. Set the RETRY[1:0] bits to '00'.

- 5. Run the unlock sequence using the Page Erase command to start the sequence.

- 6. Wait for the WR bit (NVMCON[15]) to be cleared by hardware.

- 7. Clear the WREN bit (NVMCON[14]).

- 8. Verify the erase using the CPU. To shorten the verify time, use CREAD1 = 1 to perform a hardware compare to logic '1' of each bit in the Flash Word including ECC. A successful compare yields a read of 0x00000001 in the lowest addressed word in a Flash Word (128 bits). This is the Compare Word. All other Words are 0x00010000. If any bit is logic '0', all Words in the Flash Word read 0x00000000. Remember to increment the address by the number of bytes in a Flash Word between reads.

- 9. If all Compare Words verify correctly, the Page Erase Retry process is complete. Go to step 11.

- 10. If a Compare Word yields a read of 0x00000000, perform steps 4 through 9 up to six more times with the following change to step 4:

- a. Increment the RETRY[1:0] bits by one if the bit has not already reached the '11' setting.

- b. Maintain all other fields.

- 11. Restore the value of the NVMCON2 register, which was saved in step 3.

#### Notes:

- 1. When the VREAD1 = 1, the Flash uses the WS[3:0] bits for Flash access wait state generation to the panel selected by NVMADDR. Software is responsible for writing the VREAD1 bit back to '0' when both erase and verify is complete.

- 2. The device configuration boot page (the page containing the DEVCFGx values) does not support Page Erase Retry.

The following code provides code for a single page erase operation at address 0x1008000, where Page Erase Retry is used.

### **Page Erase Retry Code Example:**

```

saveNVMCON2 = NVMCON2;

// set up Page Erase Retry

NVMCON2bits.ERS = 0;

// Stage 0 - SW use only

NVMCON2bits.VREAD1 = 1;

NVMCON2bits.CREAD1 = 1;

NVMCON2bits.RETRY = 0b00;

tryCount = 0;

// Up to 4 attempts

do {

tryCount++;

// commence programming

NVMInitiateOperation();

// Wait for WR bit to clear

while (NVMCONbits.WR);

// Turn off WREN

NVMCONbits.WREN = 0;

// Check that the page was erased

erased = 1;

cmpPtr = (uint32 t *)NVMADDR;

erased &= (*cmpPtr == 0x00000001);

cmpPtr++;

erased &= (*cmpPtr == 0x00010000);

cmpPtr++;

erased &= (*cmpPtr == 0 \times 00010000);

cmpPtr++;

erased &= (*cmpPtr == 0x00010000);

// Erase failed. Try with different settings.

NVMCON2bits.RETRY++;

NVMCONbits.NVMOP = 0x4;

NVMCONbits.WREN = 1;

} while (!erased && (tryCount < 4));</pre>

// Restore settings

NVMCON2 = saveNVMCON2;

```

# 24.16 Program Flash Memory (PFM) Erase

Program Flash memory can be erased entirely. All three discrete NVMOP values, 0111, 0110, 0101, do the same operation of erase of entire Flash. When erasing the entire PFM area, in case of RTSP (Run Time Self Programming), the code must be executing from BFM. When erasing the entire PFM area, PFM write-protection must be completely disabled.

The following code shows code for erasing the entire Flash bank.

### **Program Flash Erase Code Example:**

```

// process errors

}

...

```

# 24.17 Pre-Program

The PIC32CX-BZ2 Flash supports an option to programming that increases endurance and retention. This feature is called Pre-Program, and it requires the user to perform the programming operation twice, first, with NVMCON2.NVMPREPG = 1 and, secondly, with NVMCON2.NVMPREPG = 0. Any of the programming operations (Single, Quad, Row) can be performed with this method. In all other respects, the SFR setup is identical. To use this feature, set or clear the NVMCON2.NVMPREPG SFR bit prior to setting the NVMWR bit. Pre-Program, typically double, the native Endurance and Retention of the Flash.

# 24.18 Device Code Protection bit (CP)

The PIC32CX-BZ2 family of devices features code protection, which, when enabled, prevents reading of the Flash memory by an external programming device (SWD through DSU).

When code protection is enabled, it can only be disabled by erasing the device with the Chip Erase command through an external programmer. See *Device Service Unit (DSU)* from Related Links.

When programming a device that has opted to utilize code protection, the external programming device must perform verification prior to enabling code protection. Enabling code protection must be the last step of the programming process. For the location of the code protection enable bits, refer to PIC32CX-BZ2 Programming Specification and System Configuration Registers (CFG) from Related Links.

#### **Related Links**

- 12. Device Service Unit (DSU)

- 18. System Configuration and Register Locking (CFG)

# 24.19 Operation in Power-Saving Modes

The Flash Controller does not operate in power-saving modes. If a WAIT instruction is encountered when programming, the CPU will stop execution (stall), wait for the programming operation to complete, then enter the Power-Saving mode.

# 24.20 Operation in Debug Mode

Programming operations will continue to completion if the processor execution is halted in Debug mode.

### 24.21 Effects of Various Resets

Device Resets, other than a Power-on Reset (POR), reset the entire contents of the NVMPWP and NVMLBWP registers. All other register content persists through a non-POR reset.

All Flash Controller registers are forced to their reset states upon a POR.

# 24.22 Control Registers

**Note:** The following conventions are used in the following registers:

- R = Readable bit

- W = Writable bit

- U = Unimplemented bit, read as '0'

- 1= Bit is set

- 0= Bit is cleared

- x = Bit is unknown

- -n = Value at POR

- HS = Hardware Set

- HC = Hardware Cleared

**Note:** All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See *CLR*, *SET and INV Registers* from Related Links.

### **Related Links**

6.1.9. CLR, SET and INV Registers

# 24.22.1 Register Summary

The following registers provides a brief summary of the Flash programming-related registers.

| Oxfo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Offset | Name        | Bit Pos. | 7    | 6       | 5       | 4        | 3         | 2              | 1          | 0         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|----------|------|---------|---------|----------|-----------|----------------|------------|-----------|

| DATE   15.8   WREEN   WREEN   LIVERR   LIVERR   HTDPGM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |             |          |      |         |         |          |           |                |            |           |

| DRUCK   23.16   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.24   21.2 |        |             |          | WR   | WREN    | WRERR   | LVDERR   |           | 14411101 [5.0] |            | HTDPGM    |

| Double                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00   | NVMCON      |          | **** | VIILEIV | VIKERIK | EVBERIK  |           |                |            | TITE GIVI |

| DOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |             |          |      |         |         |          |           |                |            |           |

| NVMCON2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0×04   |             | 31,24    |      |         |         |          |           |                |            |           |

| Double                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        | Pasaniad    |          |      |         |         |          |           |                |            |           |