# Monarch 2 Platform

GMo2S Module

## Data Sheet

SEQUANS Communications

15-55 Boulevard Charles de Gaulle

F-92700 COLOMBES, France

☎ + 33 1 70 72 16 00

✉ [contact@sequans.com](mailto:contact@sequans.com)

<https://www.sequans.com>

## ABOUT THIS DATA SHEET

### Purpose and Scope

The GM02S is a complete LTE Cat M1/NB1/NB2 module with baseband, RF and memory, targeted at narrow band low data rate M2M and IoT devices for wide deployment. This document provides technical information about GM02S LGA module. GM02S is based on Sequans's Monarch 2 platform.

### Who Should Read this Document?

This document is intended for engineers who develop User Equipment (UE) for LTE systems.

### Changes History

This is revision 17 of the GM02S data sheet, superseding version 16.

The signal list delivered as MS-Excel companion file to this data sheet is unchanged.

| Version | Date       | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17      | Jan. 2024  | <ul style="list-style-type: none"> <li>Remove all hardware v.2 information (EoL as per PCN 12001-23), GM02RBAQRI/Y</li> <li>New P/N GM02RBAQRL</li> <li>SIM_VCC output current is increased to 30 mA (instead of 2)</li> <li>Added a timing diagram in the Power section, as well as a warning related to <math>V_{BAT}</math> levels and power-up slew-rate</li> <li>New section on MTTF calculation and figure</li> </ul>                                                                                                                                                                     |

| 16      | Oct. 2023  | <ul style="list-style-type: none"> <li>New P/N GM02RBAQRK</li> <li>Add info on water washing after reflow</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15      | Sept. 2023 | <ul style="list-style-type: none"> <li>Added ADC info</li> <li>Added new part numbers GM02RBAQRH and GM02RBAQRI</li> <li>Added OTP status for all part numbers</li> <li>Correction on pad #14</li> <li>Removed references to unusable UART3</li> <li>Add a mention that power consumption info is available elsewhere</li> <li>Added further info on pads' physical dimensions</li> <li>Add new certification information</li> <li>Add total capacitance and inductance figures</li> <li>Additional info on power modes</li> <li>Add a warning about configuring two UART as console</li> </ul> |

| 14      | Nov. 2022  | <ul style="list-style-type: none"> <li>Add reliability figures for hardware v.3 (section 4.7)</li> <li>Removed part numbers in headers in favour of hardware revisions</li> <li>New GM02RBAQRF P/N in Table 2 (hardware v.3)</li> <li>Added weight of the GM02S hardware rev. 3</li> </ul>                                                                                                                                                                                                                                                                                                      |

| 13d     | Oct. 2022  | <ul style="list-style-type: none"> <li>New Part Number GM02RB6QRH in Table 2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 13c     | Oct. 2022  | <ul style="list-style-type: none"> <li>New 'change history' presentation</li> <li>Change THB information to 'PASS' in table 29 for hardware v.2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13b     | Aug. 2022  | <ul style="list-style-type: none"> <li>Updated THB information for hardware v.2. in Table 30</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 13a     | Aug. 2022  | <ul style="list-style-type: none"> <li>Harmonised Table 27 to gather information about hardware v.2 and v.3</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 1. Change history

| Version | Date       | Changes                                                                                                                                                                                                                                                                                                                                                              |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13      | July 2022  | <ul style="list-style-type: none"> <li>Added information about new hardware v.3 in Section 1.1 Frequency Bands, Section 1.5 Available Part Numbers, Section 1.4 General Features, Section 4.1 Package Description and Section 4.3 Packing</li> <li>Created Chapter 6 Regulatory Approval for hardware v.3 (GM02RBAQRY)</li> </ul>                                    |

| 12e     | Dec. 2022  | <ul style="list-style-type: none"> <li>New Part Number GM02RB6QRG in Table 2</li> </ul>                                                                                                                                                                                                                                                                              |

| 12d     | Oct. 2022  | <ul style="list-style-type: none"> <li>New Part Number GM02RB6QRH in Table 2</li> </ul>                                                                                                                                                                                                                                                                              |

| 12c     | Oct. 2022  | <ul style="list-style-type: none"> <li>New 'change history' presentation</li> <li>Change THB information to 'PASS' in table 29 for hardware v.2</li> </ul>                                                                                                                                                                                                           |

| 12b     | Aug. 2022  | <ul style="list-style-type: none"> <li>Updated THB information for hardware v.2. in Table 29</li> </ul>                                                                                                                                                                                                                                                              |

| 12a     | July 2022  | <ul style="list-style-type: none"> <li>Removed band B.71 operation for hardware v.2 in Section Frequency Bands and Table 22</li> </ul>                                                                                                                                                                                                                               |

| 12      | May 2022   | <ul style="list-style-type: none"> <li>Added information about LTE-M/NB-IoT dual mode operation in Chapter 1 General Description, Section 1.5 Available Part Numbers and Table 22</li> <li>Split Section 4.5 Regulatory Approval to accommodate NB-IoT operation</li> </ul>                                                                                          |

| 11      | March 2022 | <ul style="list-style-type: none"> <li>Updated Section 4.3 Packaging Information</li> <li>Erratum to RESETN minimum value (100 ns → 100 µs) in Table 10</li> </ul>                                                                                                                                                                                                   |

| 10      | Feb. 2022  | <ul style="list-style-type: none"> <li>Updated Section 1.5 Available Part Numbers with new UE and LR versions updated and new marking codes</li> <li>Pad #71 changed to GND instead of DNC in Table 10</li> <li>Changes in Power-up Sequence in Section 3.1.2 Power-Up and Reset Sequences</li> </ul>                                                                |

| 9       | Dec. 2021  | <ul style="list-style-type: none"> <li>Updated Table 2 in Section 1.5 Available Part Numbers</li> <li>Updated Section 4.2 Environmental Conditions</li> <li>Updated Section 4.5 Reliability Specification</li> <li>Additional RF information and recommendations</li> <li>Added Section 5.1.3 NCC Regulatory Approval</li> <li>Added performance at 2.2 V</li> </ul> |

| 8       | Sept. 2021 | <ul style="list-style-type: none"> <li>Updated Table 2 in Section 1.5 Available Part Numbers</li> <li>Updated Section 4.2 Environmental Conditions</li> <li>Updated Section 4.5 Reliability Specification</li> </ul>                                                                                                                                                 |

| 7       | Aug. 2021  | <ul style="list-style-type: none"> <li>Updated Table 2 Available Part Numbers</li> <li>Updated wording related to CTS usage for flow control in Section 2.2 UART</li> <li>Updated Section 4.3 Packing with full cardbox's weight</li> <li>Added Section 4.5 Reliability Specification</li> </ul>                                                                     |

| 6       | May 2021   | <ul style="list-style-type: none"> <li>Updated Figure 11 in Section 4.1 Package Description</li> </ul>                                                                                                                                                                                                                                                               |

Table 1. Change history (continued)

| Version        | Date       | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 <sup>1</sup> | April 2021 | <ul style="list-style-type: none"> <li>• Reorganised document</li> <li>• Updated Table 2 Available Part Numbers</li> <li>• Updated Section 3.1 Power</li> <li>• Added Section 3.4 Power Supply Dimensioning</li> <li>• Added Section 3.5 Maximum Electrical Ratings</li> <li>• Updated Chapter 5 Regulatory Approval: added ACMA Regulatory Marking, JATE TELEC Regulatory Marking, RED Regulatory Safety Notice, UKCA Regulatory Marking</li> <li>• Updated MS-Excel companion file with additional information</li> </ul>                                                                                                                                                                                                              |

| 4              | March 2021 | <ul style="list-style-type: none"> <li>• Updated orderable status in Section 1.5 Part Numbers</li> <li>• Updated Section 3.1.3 Power States</li> <li>• Added Sections Detailed Behaviour of I/O Pads of BIDIR Type and Detailed Behaviour of I/O Pads of BIDIR_WAKE Type in Section 3.1 Power</li> <li>• Updated Section 2.2 UART</li> <li>• Updated Section 2.3 SIM0 Interface</li> <li>• Updated Section 3.2 Digital I/O Characteristics</li> <li>• Updated Section 4.1 Package Description</li> <li>• Updated Section 4.2 Environmental Conditions</li> <li>• Updated Section 4.4 Storage and Mounting</li> <li>• Updated Section 5.1.1 FCC Regulatory Approval</li> </ul>                                                            |

| 3              | Dec. 2020  | <ul style="list-style-type: none"> <li>• Updated part numbers details in Table 1</li> <li>• Added timing diagrams in Section 3.1 Power</li> <li>• Added Section 3.1.3 Power States</li> <li>• Added default Enable status for GPIOs in Section 2.7 GPIO</li> <li>• Added RING0 polarity information in Table 2-13</li> <li>• Restrict usage for pad #53 to Reserved</li> <li>• Updated wake signals default enable state</li> <li>• Updated V<sub>BAT</sub> characteristics in Table 2-15</li> <li>• Updated Section 4.3 Packing</li> <li>• Added Sections FCC Regulatory Approval and Industry Canada Statement in Chapter 5 Regulatory Approval</li> <li>• Changed assignment (from GND to DNC) for pads 71, 74, 75, 76, 77</li> </ul> |

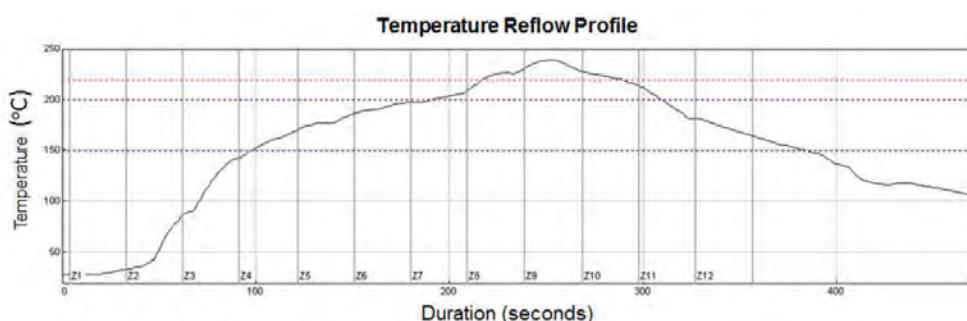

| 2              | Oct.2020   | <ul style="list-style-type: none"> <li>• Updated list of interfaces, added throughput figures in Chapter 2</li> <li>• Updated Table 1</li> <li>• Update power group descriptions in Chapter 2 Interfaces</li> <li>• Updated Figure in Section 4.1 Package Description</li> <li>• Added reflow profile information in Section 4.4 Storage and Mounting</li> <li>• Removed humidity figures in document</li> </ul>                                                                                                                                                                                                                                                                                                                         |

| 1              | May 2020   | First preliminary version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 1. Change history (continued)

1. Removed 'Preliminary' mention

# CONTENTS

|                                                           |           |

|-----------------------------------------------------------|-----------|

| About this Data Sheet.....                                | ii        |

| <b>1. General Description.....</b>                        | <b>1</b>  |

| 1.1. Frequency Bands.....                                 | 1         |

| 1.2. Applications.....                                    | 1         |

| 1.3. Block Diagram.....                                   | 2         |

| 1.4. General Features.....                                | 2         |

| 1.5. Available Part Numbers.....                          | 2         |

| <b>2. Interfaces.....</b>                                 | <b>4</b>  |

| 2.1. Pin Assignment.....                                  | 4         |

| 2.2. UART.....                                            | 5         |

| 2.3. USIM Interfaces.....                                 | 6         |

| 2.4. I <sup>2</sup> C.....                                | 7         |

| 2.5. PCM.....                                             | 8         |

| 2.6. SPI.....                                             | 8         |

| 2.7. GPIO.....                                            | 8         |

| 2.8. Other Signals.....                                   | 9         |

| 2.9. JTAG.....                                            | 11        |

| 2.10. Antenna.....                                        | 11        |

| <b>3. Electrical, RF and Thermal Characteristics.....</b> | <b>12</b> |

| 3.1. Power.....                                           | 12        |

| 3.2. Digital I/O Characteristics.....                     | 16        |

| 3.3. RF Performance.....                                  | 17        |

| 3.4. Power Supply Dimensioning.....                       | 18        |

| 3.5. Maximum Electrical Ratings.....                      | 20        |

| 3.6. Thermal Considerations.....                          | 20        |

| <b>4. Mechanical Characteristics.....</b>                 | <b>21</b> |

| 4.1. Package Description.....                             | 21        |

| 4.2. Environmental Conditions.....                        | 23        |

| 4.3. Packing.....                                         | 23        |

| 4.4. Storage and Mounting.....                            | 25        |

|                                                          |           |

|----------------------------------------------------------|-----------|

| 4.5. Reliability Specifications for Hardware Rev. 3..... | 26        |

| <b>5. Regulatory Approval .....</b>                      | <b>29</b> |

| 5.1. Regulatory Approval, LTE-M Operation Only.....      | 29        |

| 5.1.1. FCC Regulatory Approval.....                      | 29        |

| 5.1.2. ISED Regulatory Approval.....                     | 30        |

| 5.1.3. JATE TELEC Regulatory Marking.....                | 32        |

| 5.1.4. ACMA Regulatory Marking.....                      | 32        |

| 5.1.5. RED Regulatory Safety Notice.....                 | 32        |

| 5.1.6. UKCA Regulatory Marking.....                      | 32        |

| 5.2. Regulatory approval, NB-IoT Operation Only.....     | 32        |

| 5.2.1. FCC Regulatory Approval.....                      | 32        |

| 5.2.2. ISED Regulatory Approval.....                     | 34        |

| 5.2.3. ACMA Regulatory Marking.....                      | 35        |

| 5.2.4. RED Regulatory Safety Notice.....                 | 35        |

| 5.2.5. UKCA Regulatory Marking.....                      | 36        |

| <b>A. Acronyms.....</b>                                  | <b>37</b> |

---

## 1. GENERAL DESCRIPTION

The Monarch 2 GM02S is an LTE Cat M1/NB1/NB2 module based on Sequans' second generation *Monarch* 2 chip platform. The GM02S is a total module solution, including a complete, Single-SKU™ RF front end capable of operating on every GSM band worldwide, and an integrated EAL5+ Secure Element (SE) capable of hosting the SIM inside the module with zero compromise on security while lowering cost and reducing complexity. The GM02S is part of Sequans next generation "S" family of modules, featuring a very small and cost-effective form factor that requires no external components.

The GM02S leverages Sequans's 15-plus years of experience in 4G+ technologies and incorporates Sequans's carrier-approved LTE protocol stack and a software suite amongst the most mature in the industry. The GM02S is part of Sequans's next generation "S" family of modules, featuring a very small and cost-effective form factor which requires no external components. The GM02S inherits *Monarch*'s already certified LTE-M and NB-IoT stack and delivers a significantly improved performance and lower power consumption thanks to Sequans's second generation *Monarch* 2 chip and the new module architecture.

Sequans's technology, both hardware and software, is completely owned by Sequans, ensuring a fast time to market and the lowest total cost of ownership for device makers.

### 1.1. Frequency Bands

The GM02S supports the following bands:

- B1 (2100);

- B2 (1900 PCS);

- B3 (1800+);

- B4 (AWS-1);

- B5 (850);

- B8 (900 GSM);

- B12 (700 a);

- B13 (700 c);

- B14 (700 PS);

- B17 (700 b);

- B18 (800 Lower);

- B19 (800 Upper);

- B20 (800 DD);

- B25 (1900+);

- B26 (850+);

- B28 (700 APT);

- B66 (AWS-3);

- B71 (600)

- B85 (700 a+).

- B106 (LMR) -> 897.5 - 900.5 MHz in the US according to the FCC rules

### 1.2. Applications

GM02S is ideal for adding LTE-M and/or NB-IoT LTE connectivity to narrow band, low data rate M2M and IoT devices such as utility meters, industrial sensors, health and fitness appliances, asset trackers, and many additional devices in smart home, smart city, and wearable applications.

GM02S can also be used as a slim modem controlled by an external MCU via its UART. Alternatively, the GM02S can execute applets on its embedded MCU.

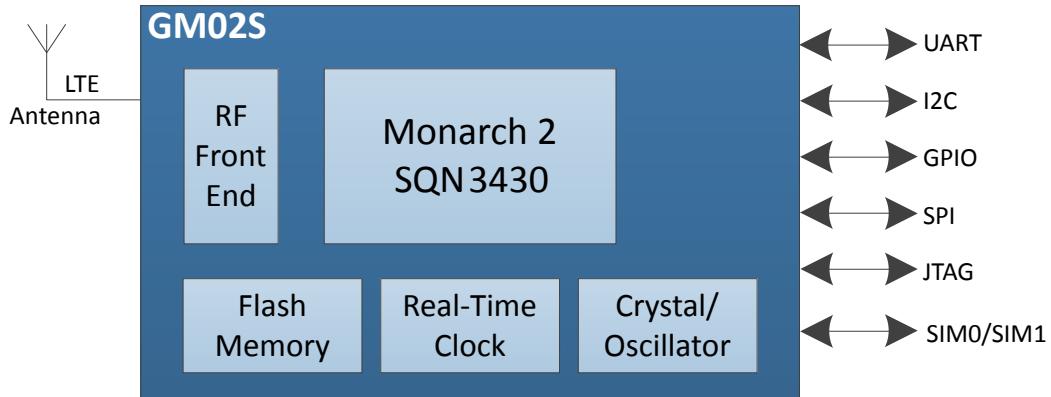

### 1.3. Block Diagram

Figure 1. GM02S Block Diagram

### 1.4. General Features

|                          |                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical Characteristics | LGA module, 120 pads.<br>Size: 16.3 x 17 x 2.3 mm                                                                                                                                                                                                                                                                                                      |

| Temperature Range        | Operation temperature range: -40 to +85 °C<br>Storage: MSL3                                                                                                                                                                                                                                                                                            |

| Power Supply             | Voltage range for RF compliance: 2.5 to 5.5 V<br>Functional voltage range: 2.2 to 5.5 V                                                                                                                                                                                                                                                                |

| Tx Power                 | +23 dBm in each band                                                                                                                                                                                                                                                                                                                                   |

| Interfaces               | <ul style="list-style-type: none"> <li>Dual (U)SIM Card Interface: support for external, removable or fixed UICC. Support for integrated UICC (iUICC) with a dedicated p/n;</li> <li>4x High-Speed UART Interfaces with flow control, up to 921600 bauds;</li> <li>GPIOs, I<sup>2</sup>C, SPI, PWM, Pulse Counter, I<sup>2</sup>S/PCM, ADC;</li> </ul> |

| SMS                      | Text and PDU modes                                                                                                                                                                                                                                                                                                                                     |

| Firmware Upgrade         | UART interface, FOTA, support of full and differential firmware upgrade                                                                                                                                                                                                                                                                                |

| RoHS                     | All hardware components fully comply with EU RoHS directive, bromine-free                                                                                                                                                                                                                                                                              |

| LTE Features             | <ul style="list-style-type: none"> <li>3GPP LTE Release 13/14 Cat M1/NB1/NB2 compliant;</li> <li>LTE Cat M1: 1.1 Mbps / 0.3 Mbps UL/DL throughput;</li> <li>LTE Cat NB1: 62.5 kbps / 27.2 kbps UL/DL throughput;</li> <li>LTE Cat NB2: 160 kbps / 120.7 kbps UL/DL throughput.</li> </ul>                                                              |

### 1.5. Available Part Numbers

GM02S's ECCN is 5A991.

| Part Number | Hardware Version                                             | Software Build (ATI1) | UE Version (ATI1) | PTCRB Model Name / Model | SVN | Availability Status         |

|-------------|--------------------------------------------------------------|-----------------------|-------------------|--------------------------|-----|-----------------------------|

| GM02RBAQRF  | HW Rev. 3<br>FCC/IC/RED/UKCA<br>ACMA/JATE/TELEC<br>PTCRB/GCF | LR 8.0.5.11           | UE 8.0.5.11       | GM02S                    | 12  | Available with unlocked OTP |

| GM02RBAQRH  |                                                              | LR 8.0.5.12           | UE 8.0.5.12       |                          | 13  | Available with unlocked OTP |

| GM02RBAQRK  |                                                              | LR 8.2.0.2            | UE 8.2.0.2        |                          | 15  | Available with unlocked OTP |

| GM02RBAQRL  |                                                              | LR 8.0.5.13           | UE 8.0.5.13       |                          | 16  | Available with unlocked OTP |

Table 2. Available Part Numbers

## 2. INTERFACES

The GM02S provides electric interfaces connecting it to the external parts, such as communication I/O ports, GPIO and antenna RF I/O. This chapter provides information about all these interfaces.

Power supply pins and details thereof are detailed in section [Electrical, RF and Thermal Characteristics \(on page 12\)](#).

**Important:** Please refer to this data sheet's companion MS-Excel file for details on each pin's:

- Default assigned function;

- State during low power modes;

- Configurability with AT commands;

- Pull status and requirements.

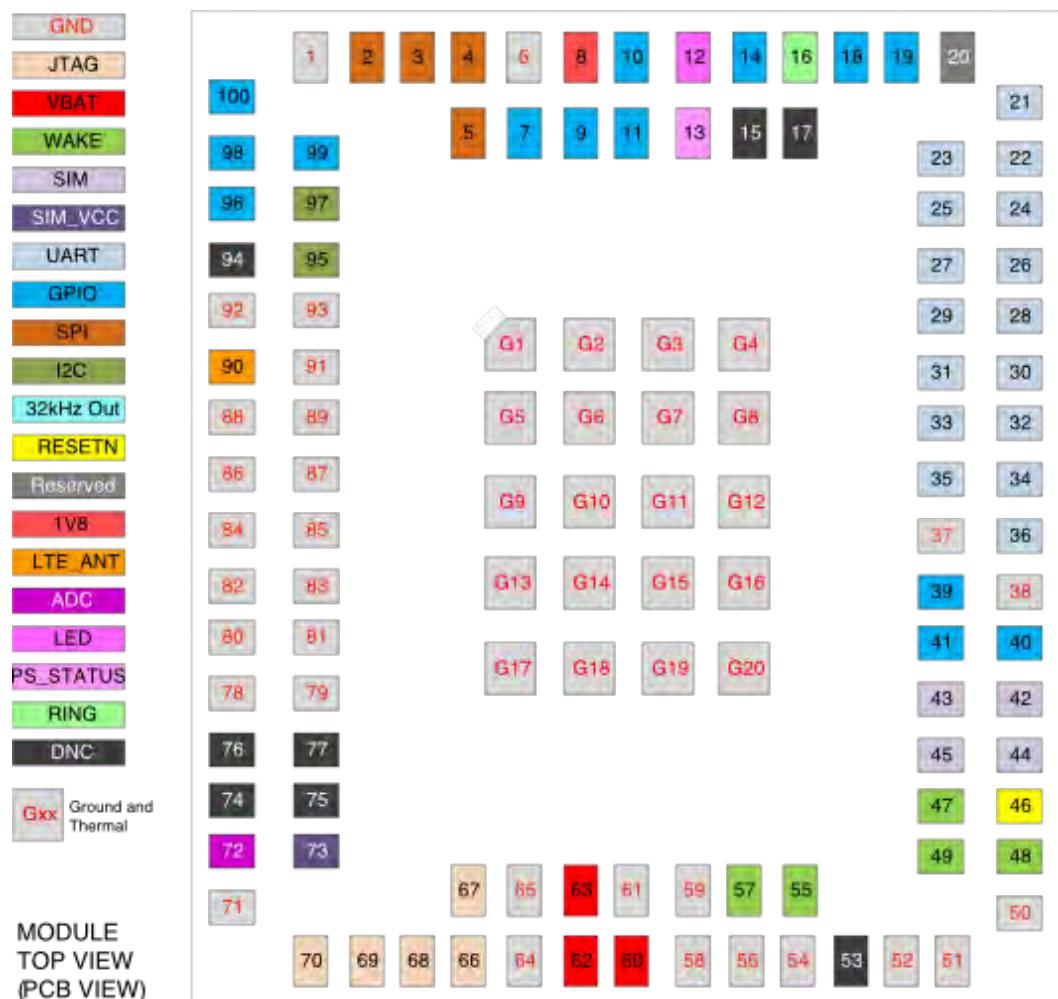

### 2.1. Pin Assignment

Figure 2. GM02S Module Pads Assignments

## 2.2. UART

When the GM02S is used as a slim modem, it has three UARTs available. The default function for each UART is as follows:

- UART0: data and control from external MCU via AT commands

- UART1: debug and upgrade

- UART2: modem console

This default configuration can be overridden.

**Attention:** Although possible, configuring two different UARTs as console will cause the kernel log messages to randomly appear on either one of them.

**Note:** See section [Power \(on page 12\)](#) for behaviour of I/Os in Deep Sleep mode.

| Pad #                           | Pad Name     | Primary Function | Alternate Function <sup>2</sup> | Power Group | Direction | Pad type <sup>3</sup> | Reset state  |

|---------------------------------|--------------|------------------|---------------------------------|-------------|-----------|-----------------------|--------------|

| 36                              | GPIO12/TXD0  | TXD0             | GPIO12                          | PVDD_1V8    | In/Out    | BIDIR                 | High-Z, 2 mA |

| In for primary function, UART0  |              |                  |                                 |             |           |                       |              |

| 34                              | GPIO13/RXD0  | RXD0             | GPIO13                          | PVDD_1V8    | In/Out    | BIDIR                 | Out-1, 2 mA  |

| Out for primary function, UART0 |              |                  |                                 |             |           |                       |              |

| 35                              | GPIO14/ CTS0 | CTS0             | GPIO14                          | PVDD_1V8    | In/Out    | BIDIR                 | Out-1, 2 mA  |

| Out for primary function, UART0 |              |                  |                                 |             |           |                       |              |

| 33                              | RTS0         | RTS0             | N/A                             | PMU_5V      | In        | IN                    | High-Z       |

| Wake signal enabled by default. |              |                  |                                 |             |           |                       |              |

| 32                              | TXD1         | TXD1             | N/A                             | PVDD_1V8    | In        | BIDIR                 | High-Z, 2 mA |

| UART1                           |              |                  |                                 |             |           |                       |              |

| 30                              | RXD1         | RXD1             | N/A                             | PVDD_1V8    | Out       | BIDIR                 | Out-1, 2 mA  |

| UART1                           |              |                  |                                 |             |           |                       |              |

| 31                              | CTS1         | CTS1             | N/A                             | PVDD_1V8    | Out       | BIDIR                 | Out-1, 2 mA  |

| UART1                           |              |                  |                                 |             |           |                       |              |

| 29                              | RTS1         | RTS1             | N/A                             | PMU_5V      | In        | IN                    | High-Z       |

| Wake signal enabled by default. |              |                  |                                 |             |           |                       |              |

| 28                              | GPIO15/TXD2  | TXD2             | GPIO15                          | PVDD_1V8    | In/Out    | BIDIR                 | High-Z, 2 mA |

| In for primary function, UART2  |              |                  |                                 |             |           |                       |              |

Table 3. UART Signals

2. Alternate functions will be available in future versions via SW upgrade.

3. UART pad types's electrical characteristics are detailed in [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#) and [Table 24: DC Ratings for Digital I/Os, PMU\\_5V Power Group \(on page 17\)](#).

| Pad # | Pad Name           | Primary Function                | Alternate Function <sup>2</sup> | Power Group | Direction | Pad type <sup>3</sup> | Reset state  |

|-------|--------------------|---------------------------------|---------------------------------|-------------|-----------|-----------------------|--------------|

| 26    | GPIO16/RXD2        | RXD2                            | GPIO16                          | PVDD_1V8    | In/Out    | BIDIR                 | Out-1, 2 mA  |

|       |                    | Out for primary function, UART2 |                                 |             |           |                       |              |

| 27    | GPIO17/ CTS2/ DCD0 | GPIO17                          | CTS2/ DCD0                      | PVDD_1V8    | In/Out    | BIDIR                 | Out-1, 2 mA  |

|       |                    | UART2                           |                                 |             |           |                       |              |

| 25    | GPIO18/ RTS2/DSR0  | GPIO18                          | RTS2/ DSR0                      | PVDD_1V8    | In/Out    | BIDIR                 | High-Z, 2 mA |

|       |                    | UART2                           |                                 |             |           |                       |              |

Table 3. UART Signals (continued)

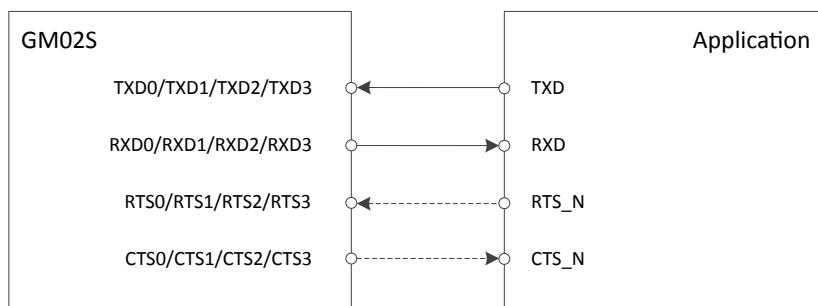

## High-Speed UARTs Flow Control Signals

- CTS0, CTS1, CTS2 : Clear-To-Send signals of resp. UART0, UART1, UART2, (active low). To be connected to the CTS of the remote UART device. See [Figure 3: UART Convention and Flow Control \(on page 6\)](#).

Leave CTS unconnected if hardware flow control is not used.

- RTS0, RTS1, RTS2 : Ready-To-Send signals of resp. UART0, UART1, UART2, (active low). To be connected to the RTS of the remote UART device. Tie to a 1 kΩ pull-down when flow control is not used. If connected to an external part (like a RS 232 driver), the user must insure that the part presents a low level to the GM02S. See [Figure 3: UART Convention and Flow Control \(on page 6\)](#).

[Figure 3: UART Convention and Flow Control \(on page 6\)](#) represents the typical implementation for hardware flow control.

Figure 3. UART Convention and Flow Control

**Note:** Please refer to [Module Integration Guide](#) for details on UART connections.

## 2.3. USIM Interfaces

### SIM0 Interface

This is the main external SIM interface. It can be used with removable or non-removable SIM cards or with soldered SIM chips. The modem manages the SIM's power supply to keep consumption as low as possible.

2. Alternate functions will be available in future versions via SW upgrade.

3. UART pad types's electrical characteristics are detailed in [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#) and [Table 24: DC Ratings for Digital I/Os, PMU\\_5V Power Group \(on page 17\)](#).

**Note:** See Section [Power \(on page 12\)](#) for behaviour of I/Os in Deep Sleep mode.

**Important:** The GM02S only supports 1.8 V SIMs.

| Pad # | Pad Name                 | Primary Function | Power Group | Direction | Pad type <sup>4</sup> | Reset State  | Comment  |

|-------|--------------------------|------------------|-------------|-----------|-----------------------|--------------|----------|

| 42    | SIM0_CLK                 | SIM0_CLK         | PVDD_1V8    | Out       | BIDIR                 | Out-0, 2 mA  | Main SIM |

| 45    | SIM0_DETECT <sup>5</sup> | SIM0_DETECT      | PMU_5V      | In        | IN                    | High-Z       | Main SIM |

| 44    | SIM0_IO                  | SIM0_IO          | PVDD_1V8    | In/Out    | BIDIR                 | High-Z, 2 mA | Main SIM |

| 43    | SIM0_RSTN                | SIM0_RSTN        | PVDD_1V8    | Out       | BIDIR                 | Out-0, 2 mA  | Main SIM |

| 73    | SIM0_VCC <sup>6</sup>    | SIM0_VCC         | PVDD_1V8    | Out       | SUPPLY                | Out-0, 30 mA | Main SIM |

Table 4. SIM0 Signals

### SIM1 Interface

This GM02S's interface to a second SIM is typically meant for soldered SIM chips (since it lacks SIM detect and SIM VCC). If the board makes use of a single SIM, it should be connected to the main SIM interface (see Section [SIM0 Interface \(on page 6\)](#) above).

**Note:** See Section [Power \(on page 12\)](#) for behaviour of I/Os in Deep Sleep mode.

| Pad # | Pad Name           | Primary Function | Alternate Function <sup>7</sup> | Power Group | Direction | Pad Type <sup>8</sup> | Reset state  |

|-------|--------------------|------------------|---------------------------------|-------------|-----------|-----------------------|--------------|

| 40    | GPIO26/SIM1_CLK    | GPIO26           | SIM1_CLK                        | PVDD_1V8    | Out       | BIDIR                 | Out-0, 2 mA  |

| 41    | GPIO27/SIM1_RESETN | GPIO27           | SIM1_RESETN                     | PVDD_1V8    | Out       | BIDIR                 | Out-0, 2 mA  |

| 39    | GPIO25/SIM1_IO     | GPIO25           | SIM1_IO                         | PVDD_1V8    | In/Out    | BIDIR                 | High-Z, 2 mA |

Table 5. SIM1 Signals

## 2.4. I<sup>2</sup>C

**Note:** See Section [Power \(on page 12\)](#) for behaviour of I/Os in Deep Sleep mode.

| Pad # | Pad Name       | Primary Function | Alternate Function <sup>9</sup> | Power Group | Direction | Pad type <sup>10</sup> | Reset State |

|-------|----------------|------------------|---------------------------------|-------------|-----------|------------------------|-------------|

| 95    | GPIO23/I2C_SDA | GPIO23           | I2C_SDA                         | PVDD_1V8    | In/Out    | BIDIR                  | High-Z      |

Table 6. I<sup>2</sup>C Pad Details

4. USIM pad types electrical characteristics are detailed in [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#) and [Table 24: DC Ratings for Digital I/Os, PMU\\_5V Power Group \(on page 17\)](#).

5. SIM0\_DETECT is active high (high when a card is present, low when no card is present). It can be configured as a WAKE pin via software command.

6. See range of values in [Table 15: Power Pads \(on page 12\)](#).

7. Alternate functions will be available in future versions via SW upgrade.

8. Pad types electrical characteristics are detailed in [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#).

9. Alternate functions will be available in future versions via SW upgrade.

10. I<sup>2</sup>C pad types's electrical characteristics are detailed in [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#).

| Pad # | Pad Name       | Primary Function | Alternate Function <sup>9</sup> | Power Group | Direction | Pad type <sup>10</sup> | Reset State |

|-------|----------------|------------------|---------------------------------|-------------|-----------|------------------------|-------------|

| 97    | GPIO24/I2C_SCL | GPIO24           | I2C_SCL                         | PVDD_1V8    | In/Out    | BIDIR                  | High-Z      |

Table 6. I<sup>2</sup>C Pad Details (continued)

## 2.5. PCM

**Note:** See section [Power \(on page 12\)](#) for behaviour of I/Os in Deep Sleep mode.

| Pad # | Pad Name      | Primary Function | Alternate Function <sup>11</sup> | Power Group | Direction | Pad type <sup>12</sup> | Reset State |

|-------|---------------|------------------|----------------------------------|-------------|-----------|------------------------|-------------|

| 96    | GPIO4/PCM_CLK | GPIO4            | PCM_CLK                          | PVDD_1V8    | In/Out    | BIDIR                  | High-Z      |

| 98    | GPIO3/PCM_RXD | GPIO3            | PCM_RXD                          | PVDD_1V8    | In/Out    | BIDIR                  | High-Z      |

| 99    | GPIO5/PCM_FS  | GPIO5            | PCM_FS                           | PVDD_1V8    | In/Out    | BIDIR                  | High-Z      |

| 100   | GPIO6/PCM_TXD | GPIO6            | PCM_TXD                          | PVDD_1V8    | In/Out    | BIDIR                  | High-Z      |

Table 7. PCM Pad Details

## 2.6. SPI

**Note:** See section [Power \(on page 12\)](#) for behaviour of I/Os in Deep Sleep mode.

| Pad # | Pad Name        | Primary Function | Alternate Function <sup>13</sup> | Power Group | Direction | Pad type <sup>14</sup> | Reset state |

|-------|-----------------|------------------|----------------------------------|-------------|-----------|------------------------|-------------|

| 3     | GPIO7/SPI_SDI   | GPIO7            | SPI_SDI                          | PVDD_1V8    | In/Out    | BIDIR                  | High-Z      |

| 4     | GPIO8/SPI_SDO   | GPIO8            | SPI_SDO                          | PVDD_1V8    | In/Out    | BIDIR                  | High-Z      |

| 2     | GPIO9/SPI_CLK   | GPIO9            | SPI_CLK                          | PVDD_1V8    | In/Out    | BIDIR                  | High-Z      |

| 5     | GPIO10/SPI_CSN1 | GPIO10           | SPI_CSN1                         | PVDD_1V8    | In/Out    | BIDIR                  | High-Z      |

| 7     | GPIO11/SPI_CSN2 | GPIO11           | SPI_CSN2                         | PVDD_1V8    | In/Out    | BIDIR                  | High-Z      |

Table 8. SPI Pad Details

## 2.7. GPIO

33 GPIOs are available on the GM02S the first 28 are named GPIO1 to GPIO28 and the last five GPIO31 to GPIO35. The GPIOs listed in [Table 9: GPIO pads detail \(on page 9\)](#) are not enabled by default. Their states are controlled by software.

9. Alternate functions will be available in future versions via SW upgrade.

10. I<sup>2</sup>C pad type's electrical characteristics are detailed in [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#).

11. Alternate functions will be available in future versions via SW upgrade.

12. PCM pad type's electrical characteristics are detailed [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#).

13. Alternate functions will be available in future versions via SW upgrade.

14. SPI pad type's electrical characteristics are detailed in [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#).

| GPIO Range       | Default State |

|------------------|---------------|

| GPIO3 to GPIO11  | Disabled      |

| GPIO17 to GPIO28 | Disabled      |

| GPIO31 to GPIO32 | Disabled      |

Table 9. GPIO pads detail

The GPIOs are documented in this data sheet according to their shared or assigned function. In addition to the GPIO, five wake signals are also available (see section [Other Signals \(on page 9\)](#)).

## 2.8. Other Signals

| Pads Type      | Pads Number                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------------------|

| GND            | 1, 6, 37, 38, 50, 51, 52, 54, 56, 58, 59, 61, 64, 65, 71, 78, 79, 80, 81, 82, 83, 84, 85, 86, 87, 88, 89, 91, 92, 93 |

| DNC (Reserved) | 15, 17, 53, 74, 75, 76, 77, 94                                                                                       |

Table 10. GND and DNC pads

**Note:** See Section [Power \(on page 12\)](#) for behaviour of I/Os in Deep Sleep mode.

| Pad #                                                                                   | Name                          | Primary Function | Alternate Function <sup>15</sup> | Power Group | Direction | Pad Type <sup>16</sup> | Reset State  |

|-----------------------------------------------------------------------------------------|-------------------------------|------------------|----------------------------------|-------------|-----------|------------------------|--------------|

| 72                                                                                      | ADC1                          | ADC1 (see below) | N/A                              | N/A         | In        | IN                     | N/A          |

| Analogue-Digital Converter (ADC, IN)                                                    |                               |                  |                                  |             |           |                        |              |

| 12                                                                                      | GPIO1/ STATUS_LED             | STATUS_LED       | GPIO1                            | PVDD_1V8    | In/Out    | BIDIR                  | High-Z, 2 mA |

| Primary Function: Status LED (STATUS_LED, OUT)                                          |                               |                  |                                  |             |           |                        |              |

| 13                                                                                      | GPIO2/ PS_STATUS              | PS_STATUS        | GPIO2                            | PVDD_1V8    | In/Out    | BIDIR                  | High-Z, 2 mA |

| Primary Function: Power Saving status (PS_STATUS, OUT) enabled by default. Active high. |                               |                  |                                  |             |           |                        |              |

| 14                                                                                      | GPIO28/DTR0                   | GPIO28           | DTR0                             | PVDD_1V8    | In/Out    | BIDIR                  | High-Z       |

| 19                                                                                      | GPIO31/PWM0/ PULSE0/ 19M2_OUT | GPIO31           | PWM0/ PULSE0/ 19M2_OUT           | PVDD_1V8    | In/Out    | BIDIR                  | High-Z       |

| 18                                                                                      | GPIO32/PWM1/ PULSE1           | GPIO32           | PWM1/PULSE1                      | PVDD_1V8    | In/Out    | BIDIR                  | High-Z       |

| 9                                                                                       | GPIO33/TX_IND                 | TX_IND           | GPIO33                           | PVDD_1V8    | In/Out    | BIDIR                  | High-Z, 2 mA |

| Primary Function: Transmission indicator (TX_IND, OUT). Active high.                    |                               |                  |                                  |             |           |                        |              |

Table 11. Other Signals (No Interface)

15. Functions will be available in future versions via SW upgrade.

16. Pad types's electrical characteristics are detailed in [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#) and [Table 24: DC Ratings for Digital I/Os, PMU\\_5V Power Group \(on page 17\)](#).

| Pad # | Name                 | Primary Function                                                                                               | Alternate Function <sup>15</sup> | Power Group | Direction | Pad Type <sup>16</sup> | Reset State     |

|-------|----------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------|-------------|-----------|------------------------|-----------------|

| 10    | GPIO34/<br>ANT_TUNE0 | ANT_TUNE0                                                                                                      | GPIO34                           | PVDD_1V8    | In/Out    | BIDIR                  | High-Z,<br>2 mA |

|       |                      | Primary Function: Antenna tuning (ANT_TUNE0, OUT)                                                              |                                  |             |           |                        |                 |

| 11    | GPIO35/<br>ANT_TUNE1 | ANT_TUNE1                                                                                                      | GPIO35                           | PVDD_1V8    | In/Out    | BIDIR                  | High-Z,<br>2 mA |

|       |                      | Primary Function: Antenna tuning (ANT_TUNE1, OUT)                                                              |                                  |             |           |                        |                 |

| 20    | RESERVED/<br>FFF_FFH | RESERVED                                                                                                       | N/A                              | PVDD_1V8    | N/A       | BIDIR                  | High-Z,<br>2 mA |

|       |                      | Boot mode selection (FFF_FFH, IN). This pad needs a pull-down resistor by default.                             |                                  |             |           |                        |                 |

| 46    | RESETN               | RESETN                                                                                                         | N/A                              | PMU_5V      | In        | IN                     | In, Pull-up     |

|       |                      | Module HW reset signal. Active low. The minimum duration of a reset pulse on the RESETN signal is 100 $\mu$ s. |                                  |             |           |                        |                 |

| 16    | RING0                | RING0                                                                                                          | N/A                              | PVDD_1V8    | In/Out    | BIDIR                  | High-Z,<br>2 mA |

|       |                      | UART0 ring line (RING0, OUT). Enabled by default with inverted polarity.                                       |                                  |             |           |                        |                 |

| 48    | WAKE0                | WAKE0                                                                                                          | N/A                              | PMU_5V      | In        | IN                     | High-Z          |

|       |                      | Wake #0 input line (WAKE0, IN), disabled by default.                                                           |                                  |             |           |                        |                 |

| 47    | WAKE1                | WAKE1                                                                                                          | N/A                              | PMU_5V      | In        | IN                     | High-Z          |

|       |                      | Wake #1 input line (WAKE1, IN), disabled by default.                                                           |                                  |             |           |                        |                 |

| 49    | WAKE2                | WAKE2                                                                                                          | N/A                              | PMU_5V      | In        | IN                     | High-Z          |

|       |                      | Wake #2 input line (WAKE2, IN), disabled by default.                                                           |                                  |             |           |                        |                 |

| 55    | WAKE3                | WAKE3                                                                                                          | N/A                              | PMU_5V      | In        | IN                     | High-Z          |

|       |                      | Wake #3 input line (WAKE3, IN), disabled by default.                                                           |                                  |             |           |                        |                 |

| 57    | WAKE4                | WAKE4                                                                                                          | N/A                              | PMU_5V      | In        | IN                     | High-Z          |

|       |                      | Wake #4 input line (WAKE4, IN), disabled by default.                                                           |                                  |             |           |                        |                 |

Table 11. Other Signals (No Interface) (continued)

### ADC Specifications

The ADC1 pin 72 has the following specifications:

| Parameter                   | Value | Unit |

|-----------------------------|-------|------|

| Resolution                  | 14    | bit  |

| Dynamic Range               | 75    | dB   |

| Signal-to-Noise Ratio (SNR) | 68    | dB   |

| Effective Number of Bits    | 11    | bit  |

| Input Signal Bandwidth      | 1.4   | MHz  |

| Full-scale Voltage          | 1.8   | V    |

Table 12. ADC Specifications

15. Functions will be available in future versions via SW upgrade.

16. Pad types's electrical characteristics are detailed in Table 23: DC Ratings for Digital I/Os, PVDD\_1V8 Power Group (on page 17) and Table 24: DC Ratings for Digital I/Os, PMU\_5V Power Group (on page 17).

| Parameter        | Value | Unit |

|------------------|-------|------|

| Input Resistance | 40    | kΩ   |

Table 12. ADC Specifications (continued)

## 2.9. JTAG

**Note:** See Section [Power \(on page 12\)](#) for behaviour of I/Os in Deep Sleep mode.

| Pad # | Pad Name   | Primary Function | Power Group | Direction | Pad type <sup>17</sup> | Reset State                    |

|-------|------------|------------------|-------------|-----------|------------------------|--------------------------------|

| 69    | JTAG_TCK   | JTAG_TCK         | PVDD_1V8    | In        | IN                     | In, Pull-down, Schmitt-trigger |

| 67    | JTAG_TDI   | JTAG_TDI         | PVDD_1V8    | In        | IN                     | In, Pull-up                    |

| 68    | JTAG_TDO   | JTAG_TDO         | PVDD_1V8    | Out       | BIDIR                  | Out, 0                         |

| 66    | JTAG_TMS   | JTAG_TMS         | PVDD_1V8    | In        | IN                     | In, Pull-up                    |

| 70    | JTAG_TRSTN | JTAG_TRSTN       | PVDD_1V8    | In        | IN                     | In, Pull-down                  |

Table 13. JTAG pads Details

**Note:** The GM02S does not support boundary scan (IEEE 1149.1) for production testing.

## 2.10. Antenna

| Pad # | Pad Name | Direction | Comments                    |

|-------|----------|-----------|-----------------------------|

| 90    | LTE_ANT  | In/Out    | Main Antenna, for Rx and Tx |

Table 14. Antenna pad Details

17. JTAG pad types's electrical characteristics are detailed in [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#).

## 3. ELECTRICAL, RF AND THERMAL CHARACTERISTICS

### 3.1. Power

**Important:** Details about power consumption can be found in the Software Release note corresponding to the product's software version installed.

#### Power Pads Characteristics

**Note:** Pad 1V8 is the reference voltage for I/Os. It can be used to provide power to small devices (100 mA maximum usage). This voltage is not available when the modem is in Deep Sleep mode. When the modem is in standby the voltage drops to 1.62 V as per Table 15: Power Pads (on page 12).

| Pad #      | Pad Name              | Power Group | Direction | Min Value | Typical Value | Max Value |

|------------|-----------------------|-------------|-----------|-----------|---------------|-----------|

| 8          | 1V8 (see Note above)  | PVDD_1V8    | Out       | 1.62 V    | 1.8 V         | 1.98 V    |

| 73         | SIM_VCC <sup>18</sup> | PVDD_1V8    | Out       | 1.62 V    | 1.8 V         | 1.98 V    |

| 60, 62, 63 | V <sub>BAT</sub>      | N/A         | In        | 2.2 V     |               | 5.5 V     |

Table 15. Power Pads

**Note:** Reference V<sub>BAT</sub> voltage range is 2.5 V to 5.5 V for RF-compliant operation and 2.2 V to 5.5 V for functional operation with possible degradation of RF performances.

**Note:** The GM02S does not use any boost or step-up DC/DC converters.

18. See also Section [USIM Interfaces \(on page 6\)](#).

**Power-on, Power-off and Reset**

Figure 4. Power Cycle Timing

| Name          | Description                                              | Min. | Typ. | Max. | Unit |

|---------------|----------------------------------------------------------|------|------|------|------|

| $V_{on\ min}$ | Minimal ON Voltage                                       | 2.2  |      |      | V    |

| $T_{rs}$      | $V_{BAT}$ Rise Time from $V_{off\ max}$ to $V_{on\ min}$ |      |      | 10   | ms   |

Table 16. Timing values

The value of  $T_{off\ min}$  depends on the  $V_{off\ max}$  voltage. The following table gives three typical figures:

| Name                    | Description                                                                                            | Value |

|-------------------------|--------------------------------------------------------------------------------------------------------|-------|

| $T_{off\ min} @ 50\ mV$ | Minimal OFF ( $V_{BAT} \leq V_{off\ max}$ ) time to insure complete reset when $V_{off\ max} = 50\ mV$ | 0.1 s |

| $T_{off\ min} @ 0.1\ V$ | Minimal OFF ( $V_{BAT} \leq V_{off\ max}$ ) time to insure complete reset when $V_{off\ max} = 0.1\ V$ | 0.5 s |

| $T_{off\ min} @ 0.2\ V$ | Minimal OFF ( $V_{BAT} \leq V_{off\ max}$ ) time to insure complete reset when $V_{off\ max} = 0.2\ V$ | 1 s   |

Table 17.  $T_{off\ min}$  vs.  $V_{off\ max}$

**CAUTION:**  $V_{BAT}$  must **always** be at least equal to  $V_{on\ min}$  during normal operation. Once  $V_{BAT}$  has dropped below this threshold, **always** ensure the voltage keeps on dropping down to  $V_{off\ max}$  and remains low for at least  $T_{off\ min}$ . Failure to comply, as well as failure to meet the maximum  $V_{BAT}$  rising time requirement ( $T_{rs}$ ) during power-on, can result in erratic behaviour.

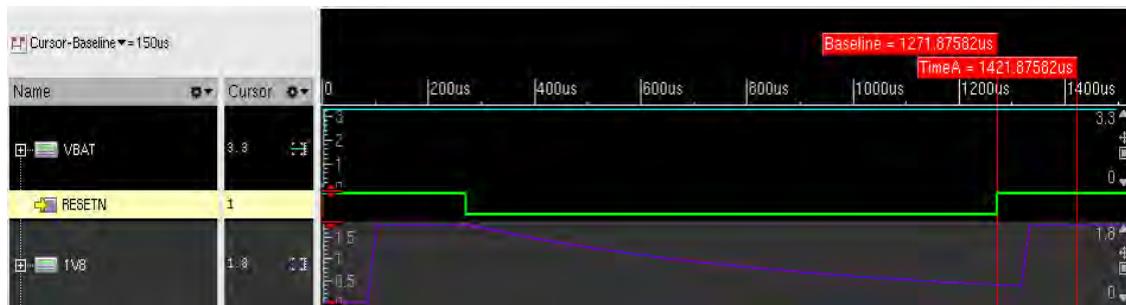

Figure 5. Typical Timing Diagram for Power-Up Sequence

**Important:** The 1V8 power signal can remain low up to 370  $\mu$ s after the V<sub>BAT</sub> rising edge

Figure 6. Typical Timing Diagram for Reset Sequence

**Note:** since RESETN is pulled-up internally, RESETN does not need to be held low after V<sub>BAT</sub> is established, as shown in [Figure 6: Typical Timing Diagram for Reset Sequence \(on page 14\)](#). There is no timing condition between RESETN and V<sub>BAT</sub>.

**Note:** RESETN minimum duration for reliable detection is 100  $\mu$ s

## Power States

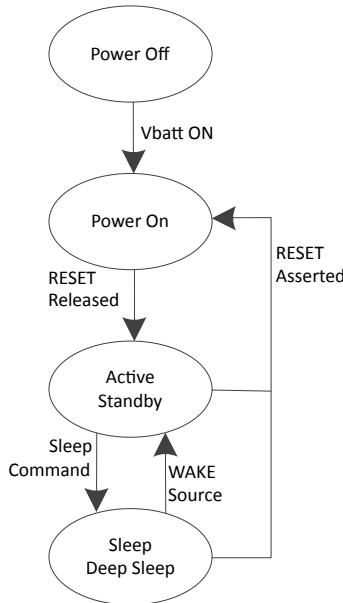

Figure 7: Electrical States and Transitions ([on page 15](#)) represents the electrical states of the module and their transitions.

Figure 7. Electrical States and Transitions

There are four possible power modes:

- Active mode: operational, UART on, RF on, LCPU/MCPU/DSP are running. Power consumption depends on workload and transmit power level.

- Standby mode: Same as active mode, except RF off.

- Sleep mode: MCPU/LCPU/DSP are power gated, UART off, RAM content is salvaged. Power level 300  $\mu$ A circa.

- Deep Sleep Mode: Only the power management unit (PMU) stays active. Power level 1  $\mu$ A.

More information is given in the table below:

| Power Mode | LTE Mode                                                    | Available Interfaces         |

|------------|-------------------------------------------------------------|------------------------------|

| Active     | Connected (RF on)                                           | All interfaces               |

| Standby    | Connected (RF off)                                          | All interfaces               |

| Sleep      | Short eDRX idle duration RRC Idle                           | WAKE pins (including RTS0/1) |

| Deep Sleep | PSM idle, Long eDRX idle duration, radio-off, airplane mode | WAKE pins (including RTS0/1) |

Table 18. Power Modes Description

#### **PVDD\_1V8 BIDIR Pads State in Deep Sleep mode**

In Deep Sleep mode, the Digital PVDD\_1V8 bi-directional I/Os are completely powered off and behave like 50 M $\Omega$  high-impedance pins.

#### **PMU\_5V IN Pads State in Deep Sleep mode**

In Deep Sleep mode the digital PMU\_5V inputs are completely powered off and behave like 180 M $\Omega$  high-impedance pins.

Table 19: Measured Leakage Current for the PMU Wake Inputs (on page 16) gives the values of the measured leakage current (measurements taken on silicon) for the PMU wake inputs.

| Minimum | Typical | Maximum |

|---------|---------|---------|

| 3 nA    | 4 nA    | 12 nA   |

Table 19. Measured Leakage Current for the PMU Wake Inputs

Table 20: External Pull-up/Pull-down Resistor at PMU Wake Input Pads ([on page 16](#)) shows values of the external pull-up/pull-down resistor to be used at the PMU wake inputs pads.

| Minimum | Typical | Maximum |

|---------|---------|---------|

| 1 kΩ    | 10 kΩ   | 100 kΩ  |

Table 20. External Pull-up/Pull-down Resistor at PMU Wake Input Pads

Table 21: PMU Wake Input Pulses Detection Mechanism Timings ([on page 16](#)) details the PMU wake input pulses detection mechanism timings.

| Maximum pulse width guaranteed to be ignored | Minimum pulse width guaranteed to be recognised |

|----------------------------------------------|-------------------------------------------------|

| 11.1 ns                                      | 100 μs                                          |

Table 21. PMU Wake Input Pulses Detection Mechanism Timings

Table 22: Internal Pull-Up Current at RESETN Pad ([on page 16](#)) provides the internal pull-up current range at RESETN.

| Minimum | Typical | Maximum  |

|---------|---------|----------|

| 73.5 nA | 100 nA  | 160.5 nA |

Table 22. Internal Pull-Up Current at RESETN Pad

## 3.2. Digital I/O Characteristics

This section details the voltage and current characteristics of the various I/O pads of the GM02S .

The I/Os belong either one of two power groups:

- PVDD\_1V8

- PMU\_5V

The operational voltage range of both power groups is described in [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#) and [Table 24: DC Ratings for Digital I/Os, PMU\\_5V Power Group \(on page 17\)](#).

**CAUTION:** Designers must ensure that the input voltage on any of the I/O pads never exceeds the  $V_{IH}$  of the power group they belong to.

See [Table 23: DC Ratings for Digital I/Os, PVDD\\_1V8 Power Group \(on page 17\)](#) for the digital I/O characteristics of the different I/O pads. Refer to each interface of the GM02S in chapter [Interfaces \(on page 4\)](#) for the power group and I/O pad type of each pad. Note that IN pads are inputs only whereas BIDIR can be both inputs and outputs.

| Symbol                                          | Minimum | Maximum | Unit      |

|-------------------------------------------------|---------|---------|-----------|

| $V_{IH}$ – Input HIGH level                     | 1.26    | 3.3     | V         |

| $V_{IL}$ – Input LOW level                      | 0       | 0.54    | V         |

| $V_{OH}$ – Output HIGH voltage                  | 1.44    | 1.8     | V         |

| $V_{OL}$ – Output LOW voltage                   | 0       | 0.36    | V         |

| $I_{RPU}$ – Input pull-up resistor current      | 15      |         | $\mu$ A   |

| $R_{RPU}$ – Input pull-up resistance            | 27      | 34      | $k\Omega$ |

| $I_{RPD}$ – Input pull-down resistor current    | 15      |         | $\mu$ A   |

| $R_{RPD}$ – Input pull-down resistance          | 27      | 34      | $k\Omega$ |

| $V_H$ – Input hysteresis                        | 0.18    |         | V         |

| $I_{PAD}$ – Input leakage current, non-tolerant | -1      | 1       | $\mu$ A   |

| $I_{OZ}$ – Off-State leakage current            |         | 1       | $\mu$ A   |

Table 23. DC Ratings for Digital I/Os, PVDD\_1V8 Power Group

| Symbol                      | Minimum | Maximum                    | Unit |

|-----------------------------|---------|----------------------------|------|

| $V_{IH}$ – Input HIGH level | 0.8     | $V_{BAT} + 0.6$ (max. 5.5) | V    |

| $V_{IL}$ – Input LOW level  | 0       | 0.2                        | V    |

Table 24. DC Ratings for Digital I/Os, PMU\_5V Power Group

The total capacitance of the GM02S is 115  $\mu$ F. Total inductance is 5.3  $\mu$ H.

### 3.3. RF Performance

**Important:** For proper operation, the VSWR at the antenna pad must be better than 2:1 in conducted mode and 3:1 in radiated mode. A higher value could result either in poor RF performance, reduced Tx power or increased sideband/harmonic emission levels. Very high VSWRs can permanently damage the power amplifier.

It is recommended to add a DC blocking capacitor in series with the module RF input/output pad (#90).

#### RF Sensitivity

The GM02S exhibits the following typical RF sensitivity at 2.5 V:

| Technology | Band                                                                           | Typical Sensitivity |

|------------|--------------------------------------------------------------------------------|---------------------|

| LTE-M      | Low Bands: B5, B8, B12, B13, B14, B17, B18, B19, B20, B26, B28, B71, B85, B106 | -105 dBm            |

|            | High bands: B1, B2, B3, B4, B25, B66                                           | -106 dBm            |

| NB-IoT     | Low Bands: B5, B8, B12, B13, B14, B17, B18, B19, B20, B26, B28, B71, B85       | -108 dBm            |

Table 25. RF Sensitivity

| Technology | Band                                 | Typical Sensitivity |

|------------|--------------------------------------|---------------------|

|            | High bands: B1, B2, B3, B4, B25, B66 | -108 dBm            |

Table 25. RF Sensitivity (continued)

**CAUTION:** The maximum safe RF input power is 3 dBm.

### RF Output Power

The GM02S maximum output power within the recommended operating range (from 2.5 to 5.5 V) is given in Table 26: RF Max Output Power (on page 18).

| Bands     | Output Power      |

|-----------|-------------------|

| All Bands | 23 dBm $\pm$ 1 dB |

Table 26. RF Max Output Power

### RF performance at 2.2 V

While it is not recommended to operate the GM02S in the range 2.2 to 2.5 V, the RF section will continue to work normally, albeit with reduced TX output power as shown in Table 27: RF Performance at 2.2 V compared to 2.5 V (on page 18) below.

| Temperature | Sensitivity Loss | Output Power Loss |

|-------------|------------------|-------------------|

| -30 °C      | No loss          | 1.1 dB            |

| 25 °C       | No loss          | 1.1 dB            |

| 85 °C       | No loss          | 1.7 dB            |

Table 27. RF Performance at 2.2 V compared to 2.5 V

## 3.4. Power Supply Dimensioning

This section provides guidance to designers working on the power supply or selecting a suitable battery to power the GM02S .

### Overview

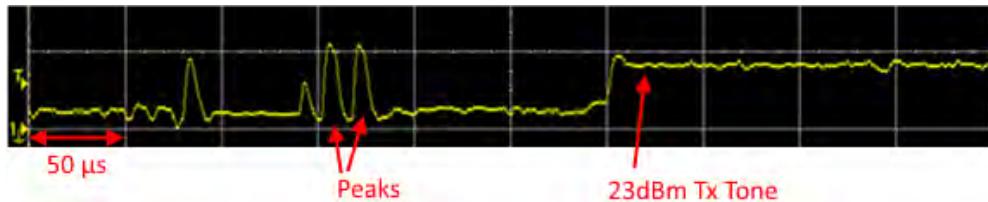

The current consumption of the GM02S peaks before every TX sub-frame as shown in Figure 8: Current Consumption in TX Sub-Frame (on page 19). In this figure, the time division is 50  $\mu$ s. Around 150  $\mu$ s from the start, two current pulses peaking 34% higher than the average current consumption during the 23 dBm TX tone which follows can be observed.

Figure 8. Current Consumption in TX Sub-Frame

### Peak Current Measurement Method

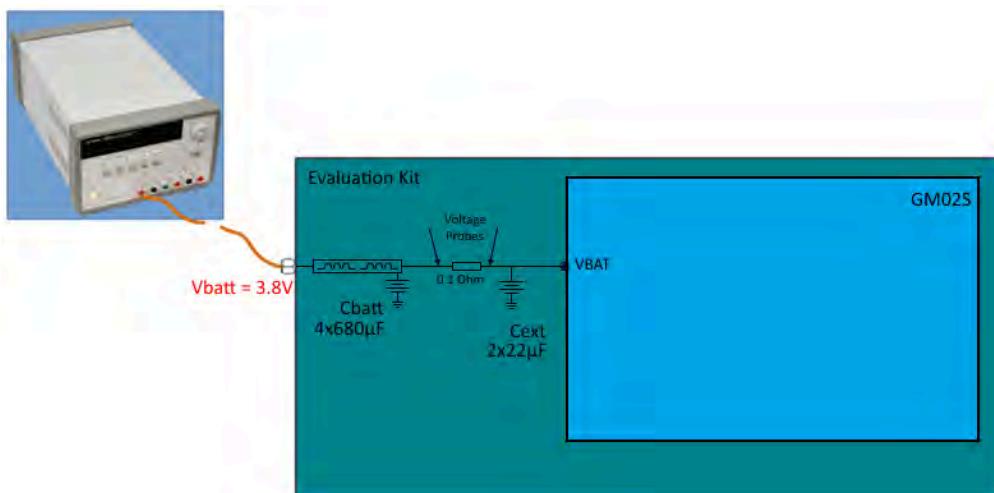

Sequans recommends to use the setup represented in Figure 9: Setup for Current Peak Measurement (on page 19) for peak current measuring. This setup was used to record the measurements presented in Table 28: Peak Current Measurements (on page 19).

Note that:

1. Voltage probes are placed close to module  $V_{BAT}$  input;

2. Voltage probes accuracy is calibrated using a current probe;

3. A large capacitance  $C_{batt}$  is placed close to the  $V_{BAT}$  pin to simulate a battery and screen the device from the parasitic inductances of the cables and tracks;

4.  $2 \times 22 \mu F$  capacitors ( $C_{ext}$ ) are placed between the voltage probes and the module  $V_{BAT}$  input to soften the current peaks.

Figure 9. Setup for Current Peak Measurement

### Peak Current Measurement

Table 28: Peak Current Measurements (on page 19) gives the peak current values measured on the setup shown on Figure 9: Setup for Current Peak Measurement (on page 19) for different voltages and temperatures.

| Input Voltage | T = -40°C | T = -30°C | T = +25°C | T = +85°C |

|---------------|-----------|-----------|-----------|-----------|

| 5.5 V         | 328 mA    | 305 mA    | 263 mA    | 268 mA    |

| 3.8 V         | 475 mA    | 438 mA    | 444 mA    | 479 mA    |

| 2.5 V         | 705 mA    | 667 mA    | 679 mA    | 741 mA    |

Table 28. Peak Current Measurements

| Input Voltage | T = -40°C | T = -30°C | T = +25°C | T = +85°C |

|---------------|-----------|-----------|-----------|-----------|

| 2.2 V         | 676 mA    | 640 mA    | 652 mA    | 717 mA    |

Table 28. Peak Current Measurements (continued)

## Margin

**Important:** It is recommended that designs potentially sensitive to the current peaks described in this section use the recommended  $C_{ext} 2 \times 22 \mu F$  and dimension the power supply with an extra 20% margin w/r to the values provided in this section.

## Module's Total Capacitance and Inductance

The module's sum of internal capacitance (positive side tolerance) is 115  $\mu F$ .

The module's sum of internal inductance (positive side tolerance) is 5.3  $\mu H$ .

## 3.5. Maximum Electrical Ratings

| Parameter                    | Minimum | Maximum |

|------------------------------|---------|---------|

| Supply Voltage $V_{BAT}$     | -0.2 V  | 5.5 V   |

| I/Os in Power Group PVDD_1V8 | -0.2 V  | 4.125 V |

| I/Os in Power Group PMU_5V   | -0.2 V  | 6.0 V   |

Table 29. Maximum Electrical Ratings

## 3.6. Thermal Considerations

Special attention needs to be given to thermal dissipation.

The outer layers of the host board must be covered in as many wide copper areas as possible, and those must be stitched with evenly spaced ground vias. Care must be taken that no air gap exists along the thermal path from the GM02S to the dissipating copper area(s). Gaps can be filled with heat conducting materials such as GapPad™.

The Gxx pads should be tied to a large ground plane on the customer's PCB layer 1. It is also recommended to have the Gxx pads area on the PCB stitched with through ground vias to improve thermal dissipation.

If the host board is piggybacked over a larger board, the aforementioned heat dissipation considerations should be applied to both the main and the daughter board.

## 4. MECHANICAL CHARACTERISTICS

### 4.1. Package Description

The module footprint is  $(16.3 \pm 0.15) \text{ mm} \times (17.0 \pm 0.15) \text{ mm} \times 2.30 \text{ mm}$  (max.).

Maximum 'warpage' is 0.13 mm (as per JEITA ED7306).

See below for the other dimensions.

The GM02S weighs 1.42 g.

#### Hardware Module Dimensions

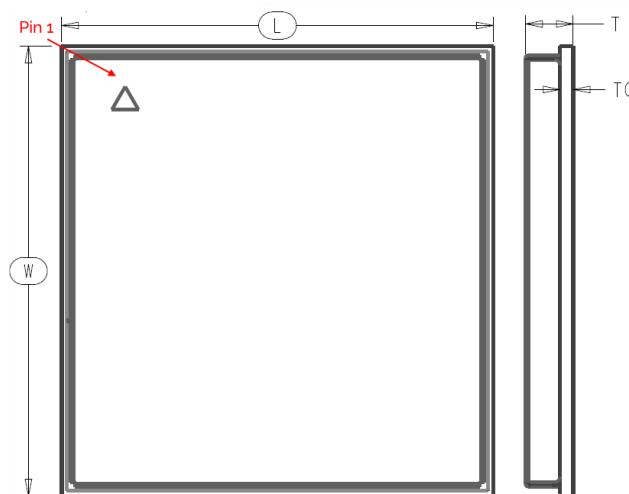

Figure 10. Module Top and Side Views

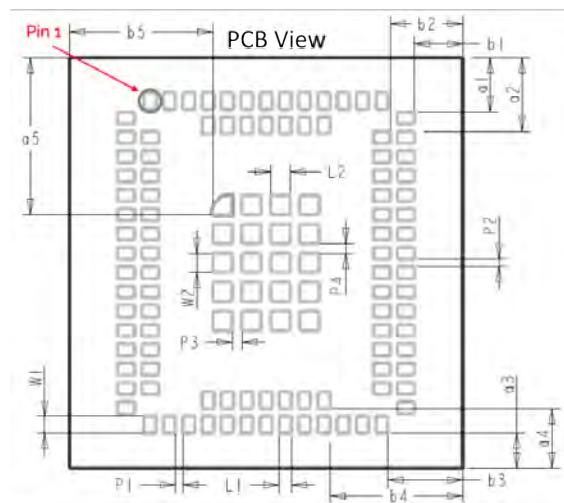

Figure 11. Module PCB Views

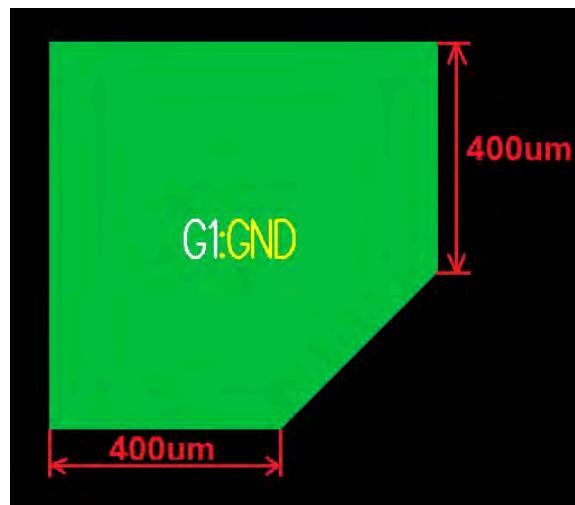

Figure 12. Details of chamfered central ground pad G1

| Dimension | Value (mm)            |

|-----------|-----------------------|

| L         | 16.3 ± 0.15           |

| W         | 17.0 ± 0.15           |

| T         | 2.3 max (2.2 typical) |

| T0        | 0.8 max               |

| L1        | 0.5 ± 0.1             |

| W1        | 0.7 ± 0.1             |

| L2        | 0.8 ± 0.1             |

| W2        | 0.8 ± 0.1             |

| a1        | 2.25 ± 0.1            |

| a2        | 3.05 ± 0.1            |

| a3        | 1.45 ± 0.1            |

| a4        | 2.45 ± 0.1            |

| a5        | 6.5 ± 0.1             |

| b1        | 2.0 ± 0.1             |

| b2        | 3.0 ± 0.1             |

| b3        | 3.1 ± 0.1             |

| b4        | 5.5 ± 0.1             |

| b5        | 5.95 ± 0.1            |

| P1        | 0.3 ± 0.1             |

| P2        | 0.3 ± 0.1             |

| P3        | 0.4 ± 0.1             |

Table 30. Module Dimensions (mm)

| Dimension | Value (mm) |

|-----------|------------|

| P4        | 0.4 ± 0.1  |

Table 30. Module Dimensions (mm) (continued)

### Laser Marking

Figure 13. GM02S Laser Marking

Notes on Figure 13: GM02S Laser Marking (on page 23):

1. The triangle in the bottom-right corner provides pin #1 location.

2. FCC ID: 2AAGMGM02SA

3. IC: 12732A-GM02SA

4. IMEI:XXXXXXXXXXXXXX

5. S/N:G2PYYMMDDNNNNSS (16 digits)

- G2P: reserved, value subject to change at Sequans' discretion (3 digits);

- YYMMDD: Manufacturing Date (YY:Year;MM:Month,DD:Day);

- NNNN: Panel counter (from 0001~9999);

- SSS: Piece location on panel (from 001 to 065).

6. 2D marked "a" refer to IMEI Barcode

7. 2D marked "b" refer to S/N Barcode

## 4.2. Environmental Conditions

GM02S operating conditions:

- Temperature (PCB temperature as measured by on-board thermistor):

- Operational: -40°C to +85°C;

- RF compliant: -30°C to +85°C

- Humidity: 10% to 85% (non-condensing)

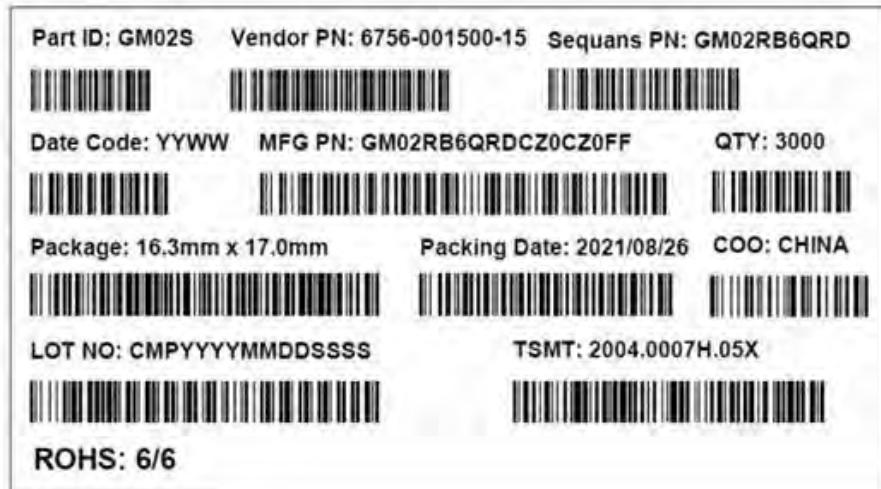

## 4.3. Packing

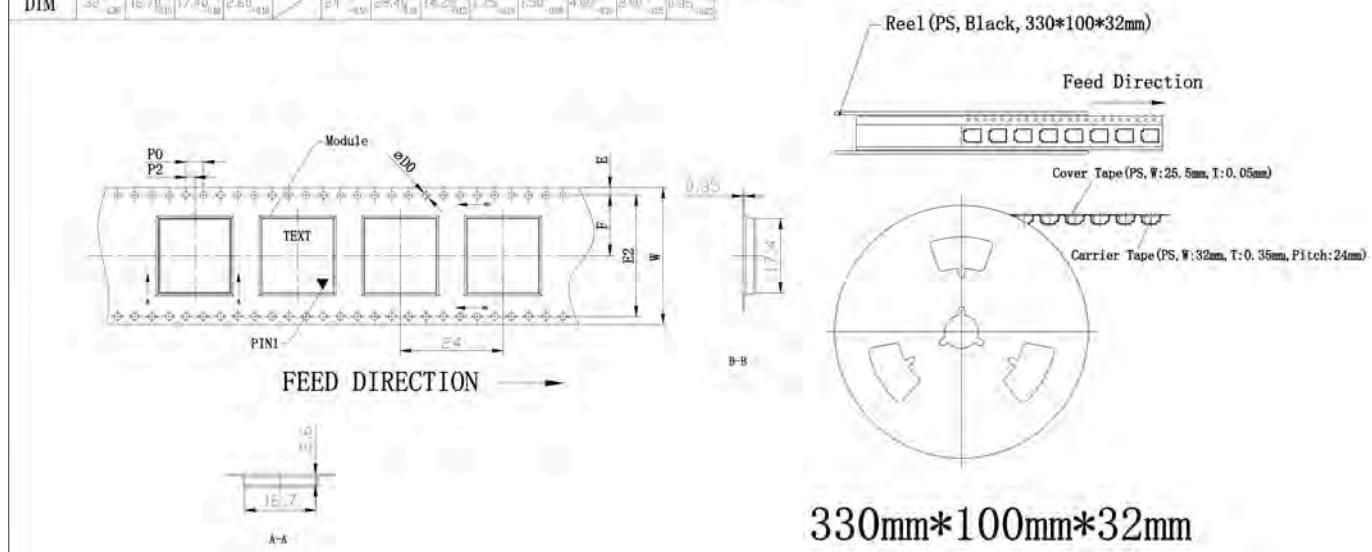

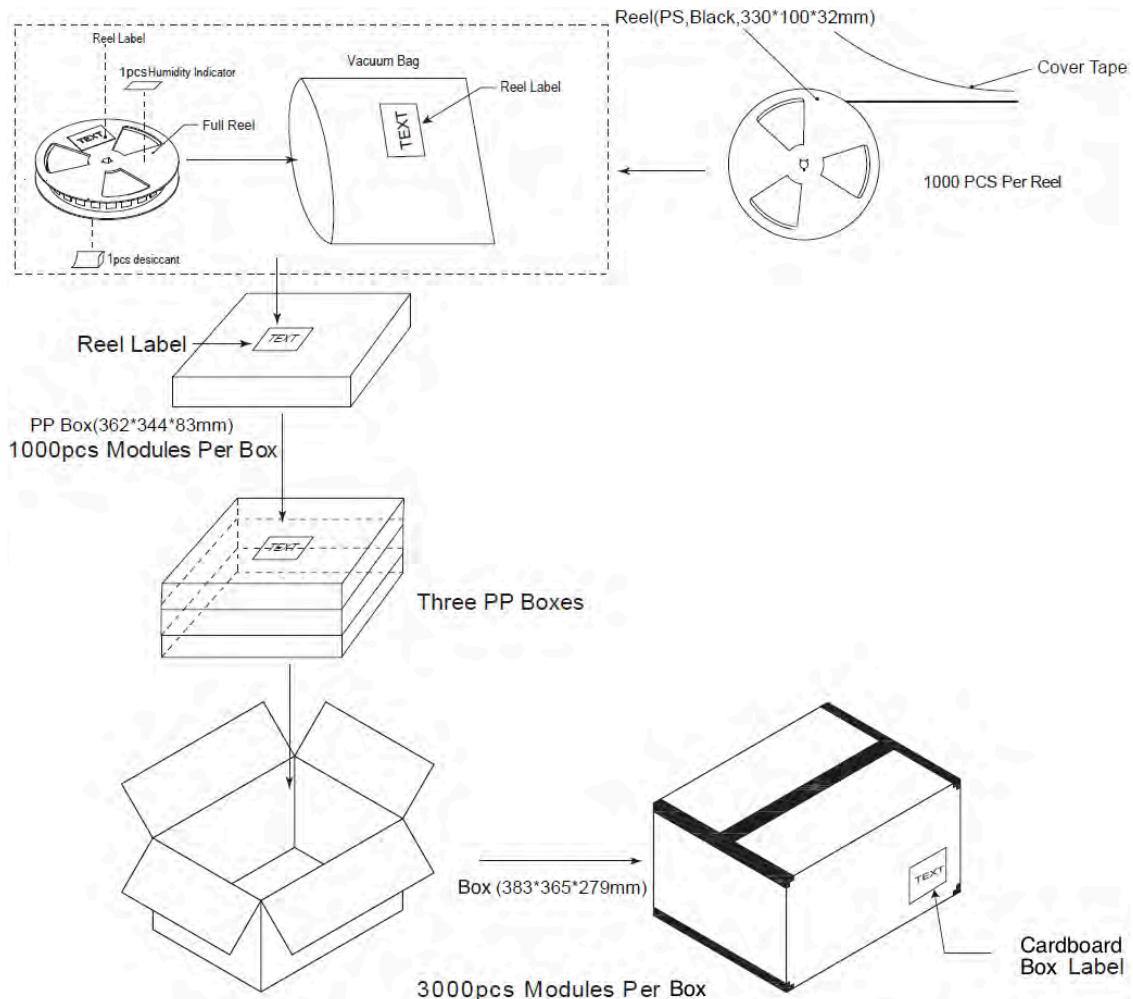

The GM02S is delivered in Tape-and-Reel. Details are provided in the figures below.

| ITEM | W                                     | A                                     | B <sub>0</sub>                          | K <sub>0</sub>                         | K <sub>1</sub>                         | P                                       | E <sub>0</sub>                          | F                                       | E                                       | D                                      | P <sub>0</sub>                         | P <sub>1</sub>                          | T                                       |

|------|---------------------------------------|---------------------------------------|-----------------------------------------|----------------------------------------|----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------|----------------------------------------|-----------------------------------------|-----------------------------------------|