## FCC STATEMENT:

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Any Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

**Note:** This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

-Reorient or relocate the receiving antenna.

-Increase the separation between the equipment and receiver.

-Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

-Consult the dealer or an experienced radio/TV technician for help.

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment.

This equipment should be installed and operated with minimum distance 20cm between the radiator & your body

## INDUSTEY CANADA STATEMENT:

This device complies with Industry Canada licence-exempt RSS standard(s). Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation of the device. In addition, this device complies with ICES-003 of the Industry Canada (IC) Rules.

Any Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

**Note:** This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Industry Canada licence-exempt RSS standard(s). These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

-Reorient or relocate the receiving antenna.

-Increase the separation between the equipment and receiver.

-Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

-Consult the dealer or an experienced radio/TV technician for help.

This equipment complies with RSS-102 radiation exposure limits set forth for an uncontrolled environment. This equipment should be installed and operated with minimum distance 20cm between

the radiator & your body.

## INDUSTEY CANADA STATEMENT(French):

Cet appareil est conforme aux normes RSS exemptes de licence d'Industrie Canada. Son fonctionnement est soumis aux deux conditions suivantes : (1) Cet appareil ne doit pas causer d'interférences nuisibles et (2) cet appareil doit accepter toute interférence reçue, y compris les interférences susceptibles de provoquer un fonctionnement indésirable de l'appareil. De plus, cet appareil est conforme à la norme ICES-003 des règles d'Industrie Canada (IC). Tout changement ou modification non expressément approuvé par la partie responsable de la conformité pourrait annuler l'autorité de l'utilisateur à faire fonctionner l'équipement. Remarque : cet équipement a été testé et déclaré conforme aux limites d'un appareil numérique de classe B, conformément aux normes RSS exemptes de licence d'Industrie Canada. Ces limites sont conçues pour fournir une protection raisonnable contre les interférences nuisibles dans une installation résidentielle. Cet équipement génère des utilisations et peut émettre de l'énergie de radiofréquence et, s'il n'est pas installé et utilisé conformément aux instructions, peut causer des interférences nuisibles aux communications radio. Cependant, il n'y a aucune garantie que des interférences ne se produiront pas dans une installation particulière. Si cet équipement cause des interférences nuisibles à la réception radio ou télévision, ce qui peut être déterminé en éteignant et en rallumant l'équipement, l'utilisateur est encouragé à essayer de corriger l'interférence par une ou plusieurs des mesures suivantes : -Réorientez ou déplacez l'antenne de réception. -Augmenter la distance entre l'équipement et le récepteur. -Connectez l'équipement à une prise sur un circuit différent de celui auquel le récepteur est connecté. -Consultez le revendeur ou un technicien radio/TV expérimenté pour obtenir de l'aide. Cet équipement est conforme aux limites d'exposition aux rayonnements RSS-102 établies pour un environnement non contrôlé. Cet équipement doit être installé et utilisé avec une distance minimale de 2. Cet appareil est conforme aux normes RSS exemptes de licence d'Industrie Canada. Son fonctionnement est soumis aux deux conditions suivantes : (1) Cet appareil ne doit pas causer d'interférences nuisibles et (2) cet appareil doit accepter toute interférence reçue, y compris les interférences susceptibles de provoquer un fonctionnement indésirable de l'appareil. De plus, cet appareil est conforme à la norme ICES-003 des règles d'Industrie Canada (IC).

Tout changement ou modification non expressément approuvé par la partie responsable de la conformité pourrait annuler l'autorité de l'utilisateur à faire fonctionner l'équipement.

Remarque : cet équipement a été testé et déclaré conforme aux limites d'un appareil numérique de classe B, conformément aux normes RSS exemptes de licence d'Industrie Canada. Ces limites sont conçues pour fournir une protection raisonnable contre les interférences nuisibles dans une installation résidentielle. Cet équipement génère des utilisations et peut émettre de l'énergie de radiofréquence et, s'il n'est pas installé et utilisé conformément aux instructions, peut causer des interférences nuisibles aux communications radio. Cependant, il n'y a aucune garantie que des interférences ne se produiront pas dans une installation particulière. Si cet équipement cause des interférences nuisibles à la réception radio ou télévision, ce qui peut être déterminé en éteignant et en rallumant l'équipement, l'utilisateur est encouragé à essayer de corriger l'interférence par une ou plusieurs des mesures suivantes : - Réorientez ou déplacez l'antenne de réception. -Augmenter la distance entre l'équipement et le récepteur. -Connectez l'équipement à une prise sur un circuit différent de celui auquel le récepteur est

connecté. -Consultez le revendeur ou un technicien radio/TV expérimenté pour obtenir de l'aide.

Cet équipement est conforme aux limites d'exposition aux rayonnements RSS-102 établies pour un environnement non contrôlé. Cet équipement doit être installé et utilisé avec une distance minimale de 20 cm entre le radiateur et votre corps.

## DataSheet

## A6G2C Series Core Board

## MiniARM Core Board

DS01010101 V1.05 Date: 2019/06/17

Product Data Manual

## Overview

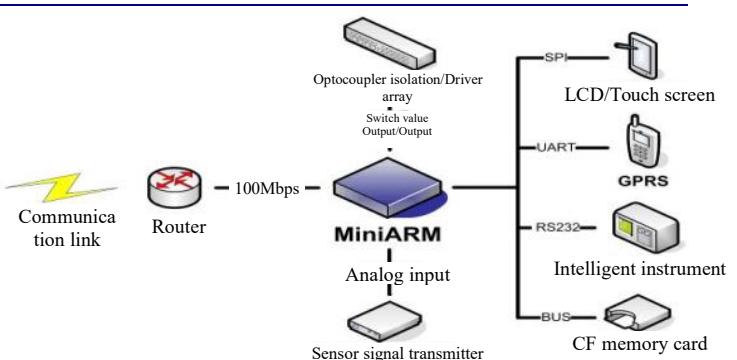

The A6G2C series wireless core board is an embedded industrial control core board that adds WiFi, Bluetooth, Zigbee and other functions on the basis of the M6G2C series core board. The core board adopts Cortex-A7 core processor, which provides fast data processing and smooth interface switching. The product provides eight UART interfaces, two USB OTG interfaces, a maximum of two CAN-bus interfaces, two Ethernet interfaces, and other interfaces. It has powerful industrial control communication interfaces, provides industrial-grade performance guarantee, and meets most industrial applications, portable consumer electronics, automotive electronics and other industries.

Guangzhou ZLG Electronics Co., Ltd. provides various sophisticated hardware solutions, as well as rich software resources including Linux and AWorks. The complete software and hardware architecture allows you to focus only on product application. It has the characteristics of short development cycle, humanized system and complete software supporting.

## Product characteristics

- ◆ 32-bit Cortex-A7 processor; operating frequency: 528MHz;

- ◆ Memory: 128/256MByte DDR3;

- ◆ Flash: 128/256MByte NAND Flash (the read and write life is about 100,000 times);

- ◆ Support up to eight serial ports;

- ◆ Support up to two CAN-bus;

- ◆ Support two 10/100M Ethernet interfaces;

- ◆ Integrate two USB2.0 OTG interfaces;

- ◆ Support one SD/MMC card;

- ◆ Support CAN, UART, I2C and other standard communication interfaces;

- ◆ Onboard WIFI, Bluetooth, Zigbee, NFC;

- ◆ Embedded Linux/AWorks operating system;

- ◆ Support a variety of upgrade methods.

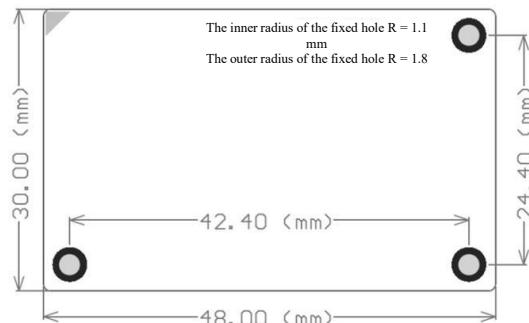

- ◆ Dimensions: 30 mm x 48 mm

## Applications

Portable Medical Equipment Electronic Point of Sale for traffic command automation home and industrial automation human machine interface (HMI)

## Ordering information

| Model              | Range of temperature | System                                |

|--------------------|----------------------|---------------------------------------|

| A6G2C-W128LI       | -30°C to +85°C       | Pre-installed Linux, AWorks supported |

| A6G2C-W256LI       | -30°C to +85°C       | Pre-installed Linux, AWorks supported |

| A6G2A-W256F256LI-T | -30°C to +85°C       | Pre-installed Linux, AWorks supported |

| A6G2C-WB128LI      | -30°C to +85°C       | Pre-installed Linux, AWorks supported |

| A6G2C-WB256LI      | -30°C to +85°C       | Pre-installed Linux, AWorks supported |

| A6G2C-5WB128LI-T   | -20°C to +75°C       | Pre-installed Linux, AWorks supported |

| A6G2C-Z128F128LI-T | -40°C to +85°C       | Pre-installed Linux, AWorks supported |

| A6G2C-M128F128LI-T | -40°C to +85°C       | Pre-installed Linux, AWorks supported |

## Typical application

## Revision History

| Version | Date       | Reason                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V0.90   | 2015/02/11 | Created                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V1.00   | 2015/05/20 | Official release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V1.01   | 2015/06/21 | Modified product pictures and mechanical dimension drawings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V1.02   | 2017/08/08 | <ol style="list-style-type: none"><li>1. Modified the description of "Overview"</li><li>2. Modified the description of "Function Introduction"</li><li>3. Modified the picture of "Product Model Naming Rules"</li><li>4. Added "Table 1.1 Use of special pins"</li><li>5. Added the "3.5 Common Interface Multiplexing on the A6G2C Core Board" section</li></ol>                                                                                                                                                                                                                                                                                                                |

| V1.03   | 2018/09/05 | <ol style="list-style-type: none"><li>1. Deleted the model number of A6G1C series</li><li>2. Added product models A6G2C-5WB128LI-T and A6G2C-Z128F128LI-T</li><li>3. Deleted the content about SAI1</li><li>4. Deleted the content about SD2</li><li>5. Added 4.12 PCB design precautions; added Flash read/write life indicator to product features</li><li>6. Added the introduction to the AWorks system;</li><li>7. Added A6G2C-M128F128LI-T</li><li>8. Added A6G2A-W256F256LI-T</li><li>9. Added the antenna selection chapter</li><li>10. Added the description of ambient temperature</li><li>11. Modified the boot configuration, and moved it to chapter 4.1.1</li></ol> |

| V1.04   | 2019/03/08 | <ol style="list-style-type: none"><li>1. Updated document headers and footers and the "Sales and Service Network" content, and added "Disclaimer"</li><li>2. Added the JTAG description chapter.</li><li>3. Added the ESD protection content</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V1.05   | 2019/06/17 | <ol style="list-style-type: none"><li>1. Modified "1.4 Type Selection Comparison Table"</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## Contents

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| 1. Function Introduction.....                                         | 1  |

| 1.1 Hardware Parameters.....                                          | 1  |

| 1.2 Software Parameters.....                                          | 2  |

| 1.2.1 Linux Driver Library.....                                       | 2  |

| 1.2.2 AWorks Driver Library.....                                      | 2  |

| 1.3 Product Model Naming Rules.....                                   | 3  |

| 1.4 Type Selection Comparison Table.....                              | 4  |

| 2. Performance Parameters.....                                        | 6  |

| 2.1 Main Performance Configuration of A6G2C Core Board System.....    | 6  |

| 2.2 Operating Temperature of the Core Board.....                      | 6  |

| 2.3 Storage capacity of the core board.....                           | 7  |

| 2.4 A6G2C Core Board Communication Performance.....                   | 7  |

| 2.5 Other Performance of A6G2C Core Board.....                        | 7  |

| 2.6 Power Supply Static Parameters.....                               | 8  |

| 3. Pin Function.....                                                  | 9  |

| 3.1 Pin Information.....                                              | 9  |

| 3.2 A6G2C Core Board Pin Definitions.....                             | 10 |

| 3.3 Pin Function Description of the A6G2C Core Board.....             | 14 |

| 3.4 A6G2C Core Board Pin Description (By Function).....               | 17 |

| 3.5 Common Interface Multiplexing of the A6G2C Series Core Board..... | 20 |

| 3.5.1 SPI.....                                                        | 21 |

| 3.5.2 uSDHC.....                                                      | 22 |

| 3.5.3 UART.....                                                       | 22 |

| 3.5.4 I <sup>2</sup> C.....                                           | 24 |

| 3.5.5 SAI.....                                                        | 25 |

| 3.5.6 PWM.....                                                        | 26 |

| 3.5.7 ADC.....                                                        | 27 |

| 3.5.8 JTAG.....                                                       | 28 |

| 4. System Hardware Design.....                                        | 29 |

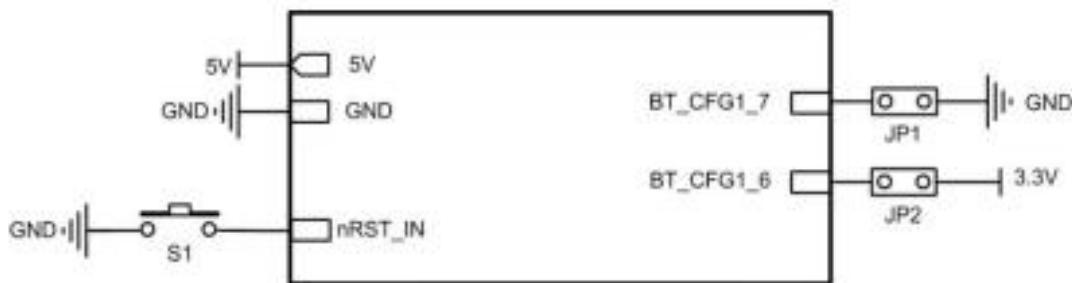

| 4.1 A6G2C Core Board Interface.....                                   | 29 |

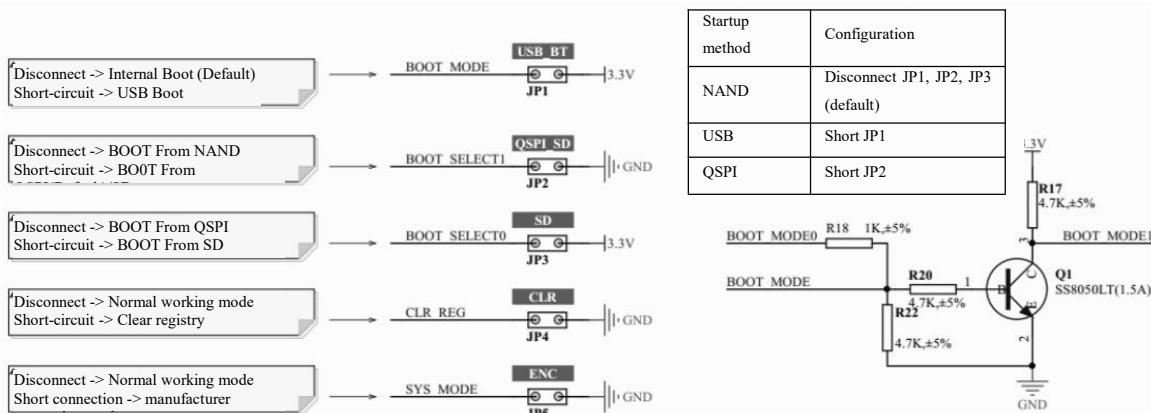

| 4.1.1 Startup Configuration Circuit.....                              | 30 |

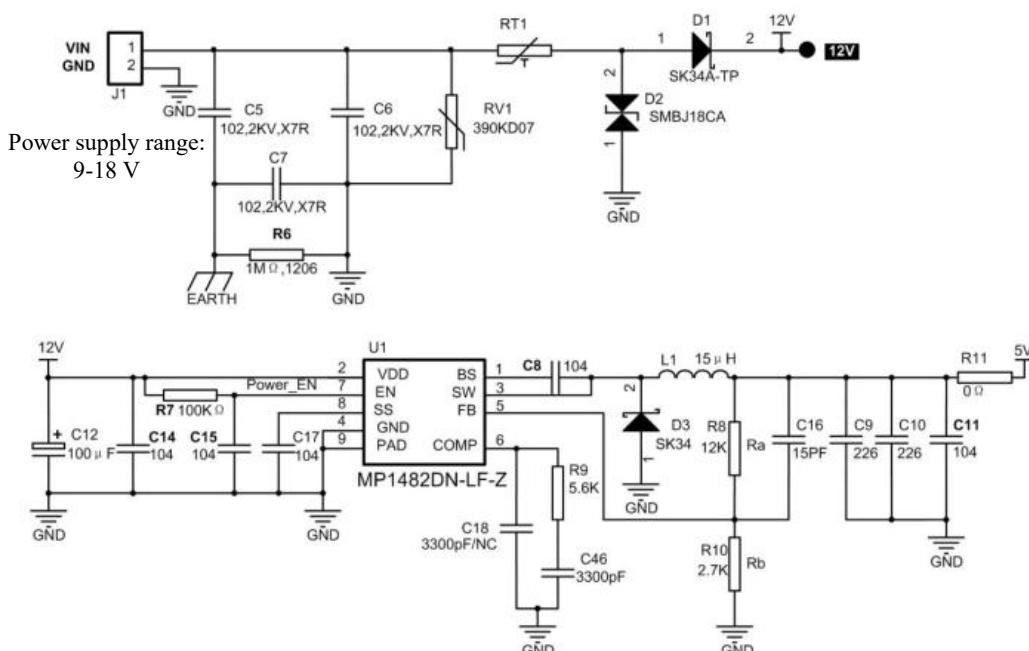

| 4.2 Power Design.....                                                 | 30 |

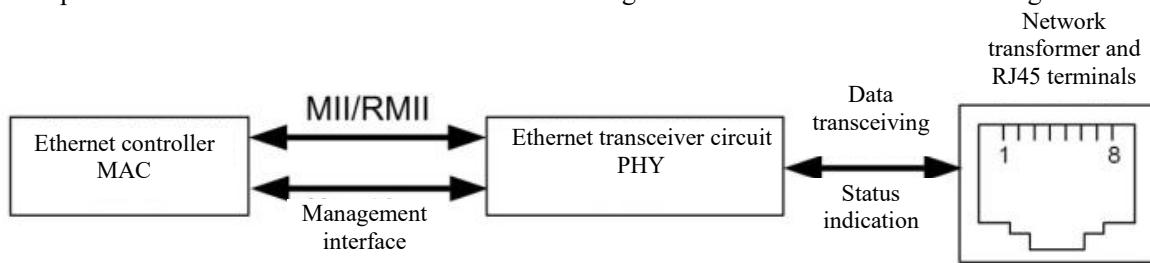

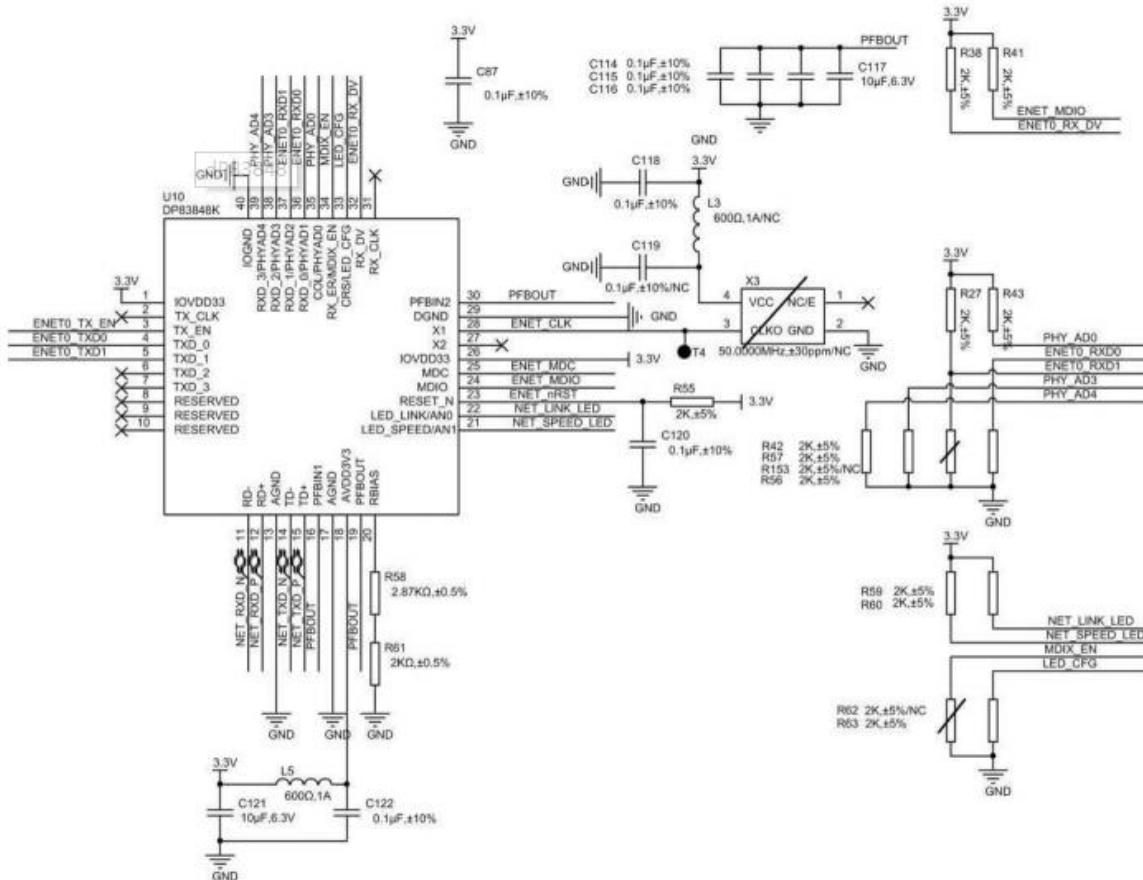

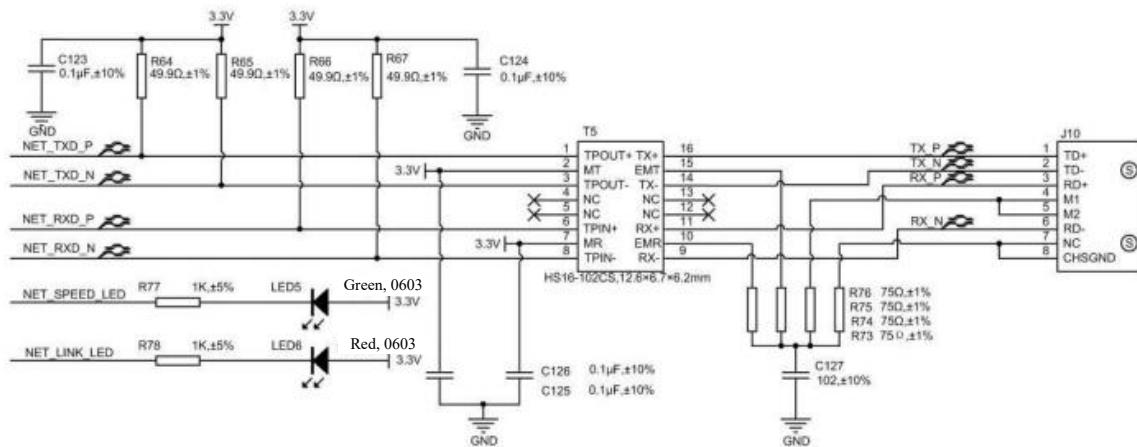

| 4.3 Fast Ethernet Circuit.....                                        | 32 |

| 4.3.1 Single Ethernet Transceiver Circuit.....                        | 32 |

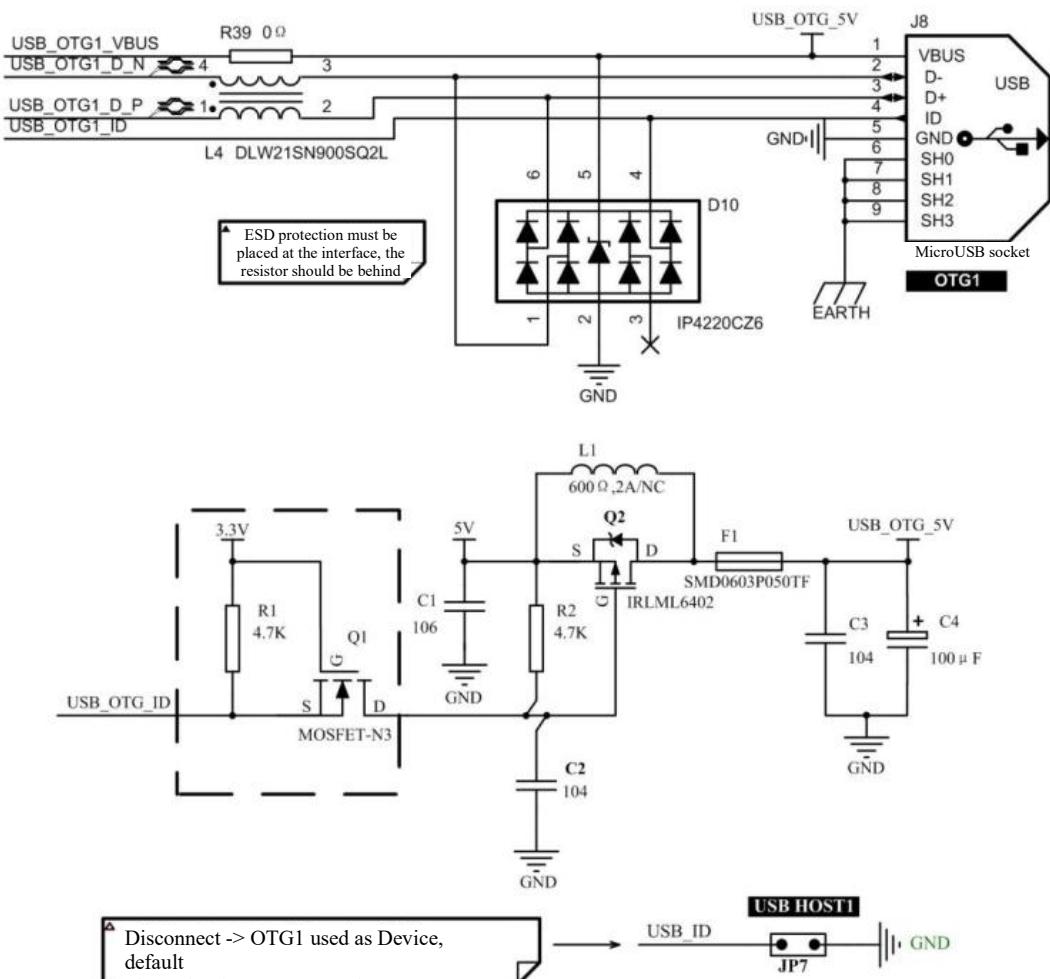

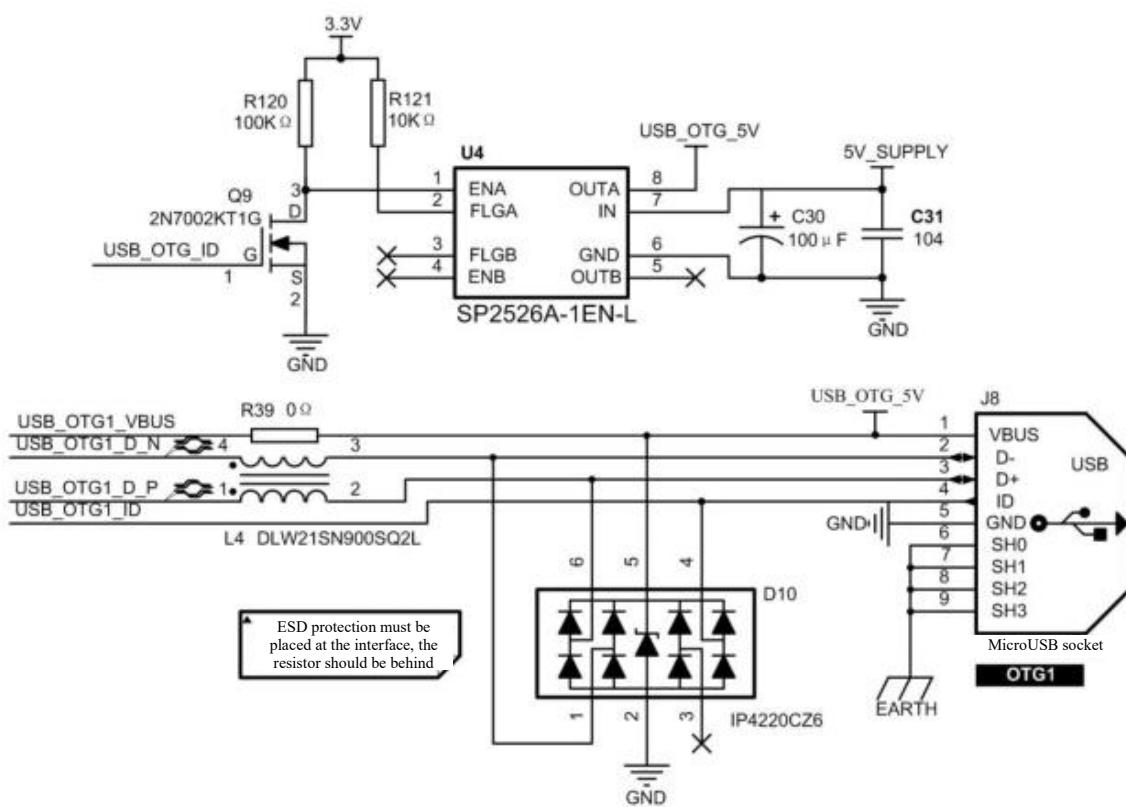

| 4.4 USB Circuit Design.....                                           | 33 |

|                                               |    |

|-----------------------------------------------|----|

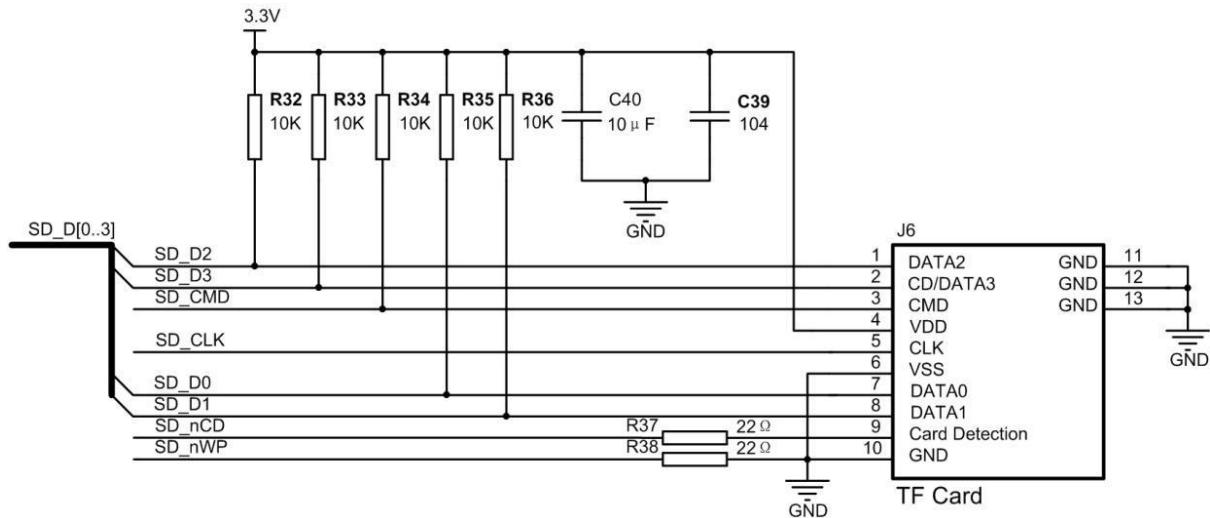

| 4.5 SD/MMC Circuit.....                       | 35 |

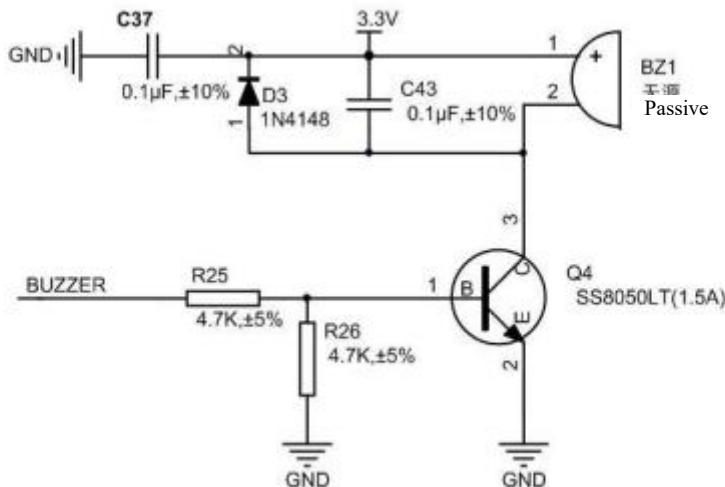

| 4.6 Buzzer Circuit.....                       | 36 |

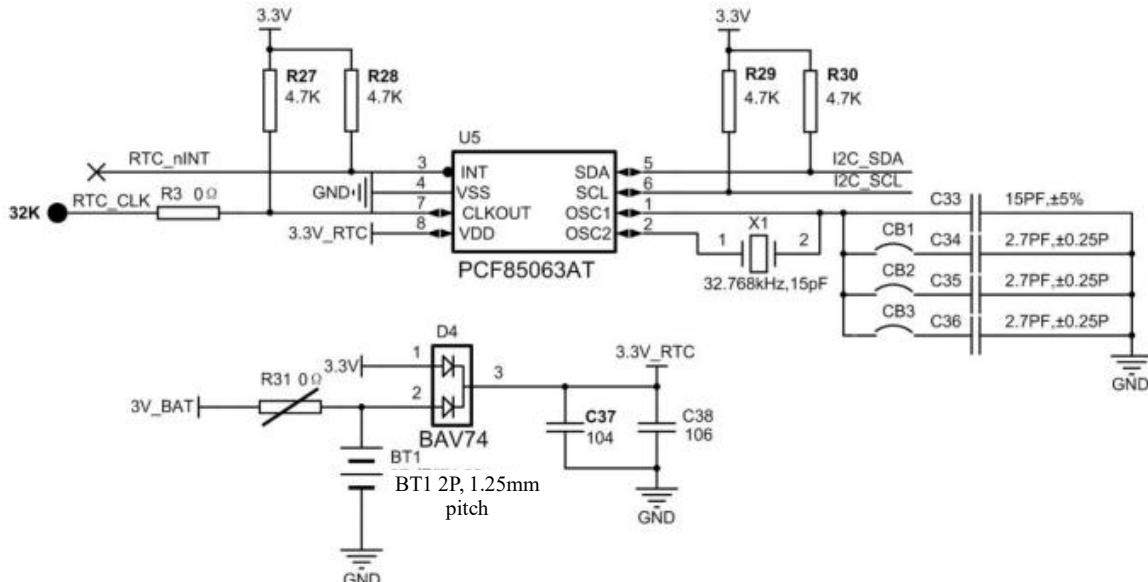

| 4.7 RTC circuit.....                          | 36 |

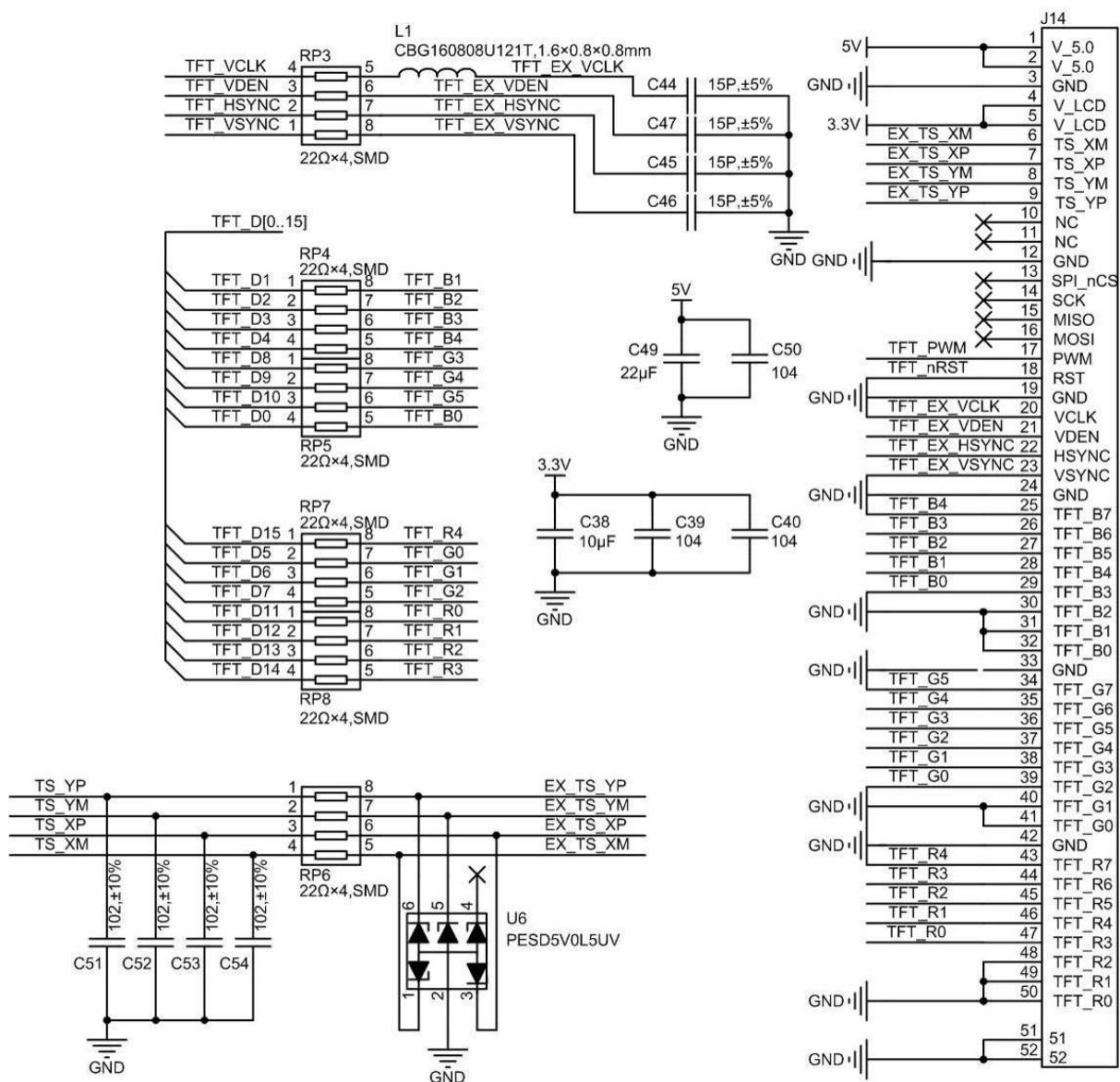

| 4.8 LCD Circuit.....                          | 36 |

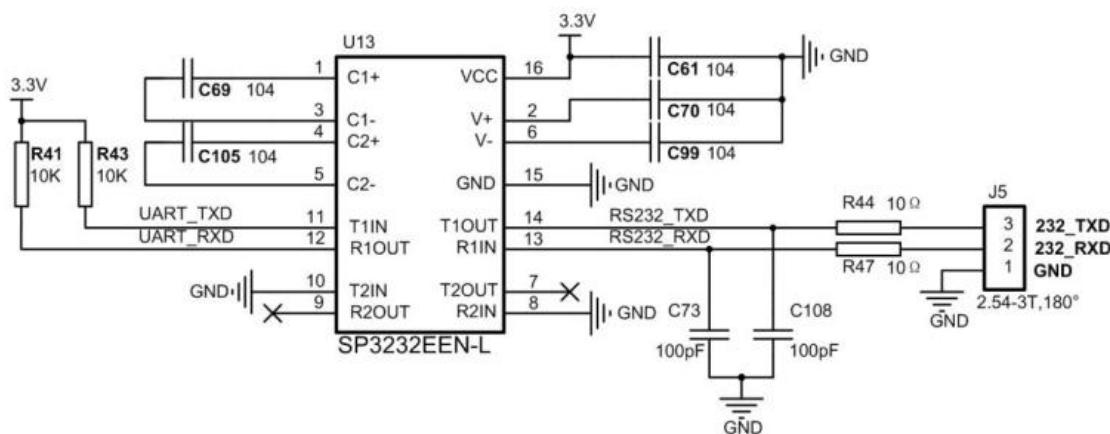

| 4.9 RS232 Debugging Serial Port Circuit.....  | 37 |

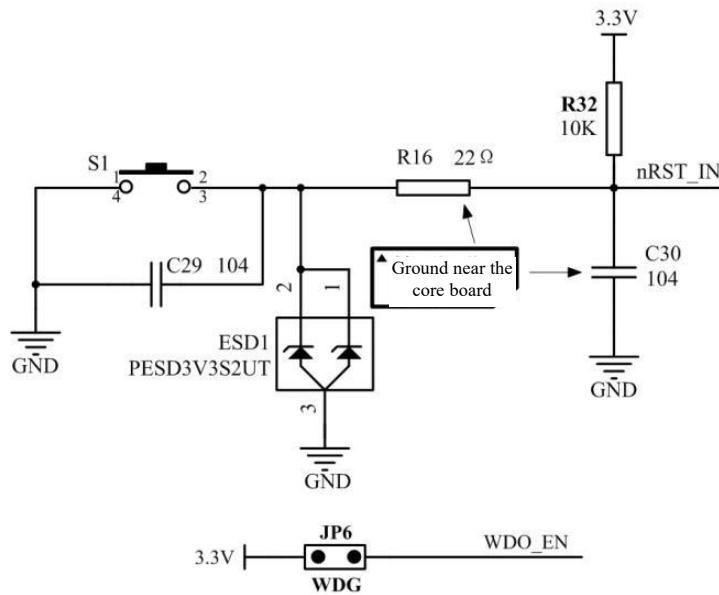

| 4.10 Reset Circuit.....                       | 38 |

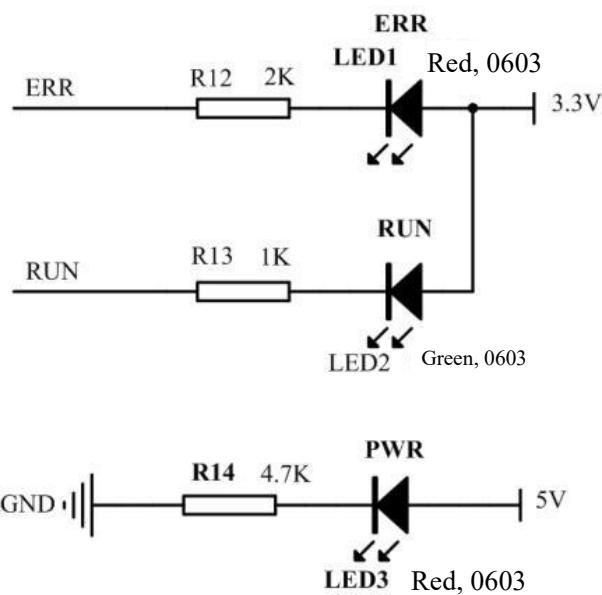

| 4.11 Indicators.....                          | 38 |

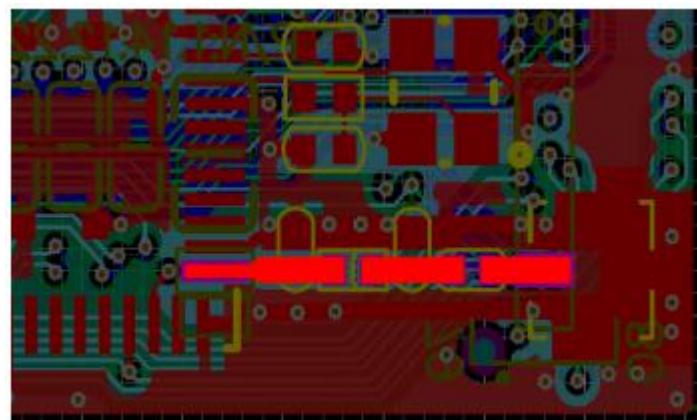

| 4.12 PCB Design Precautions.....              | 39 |

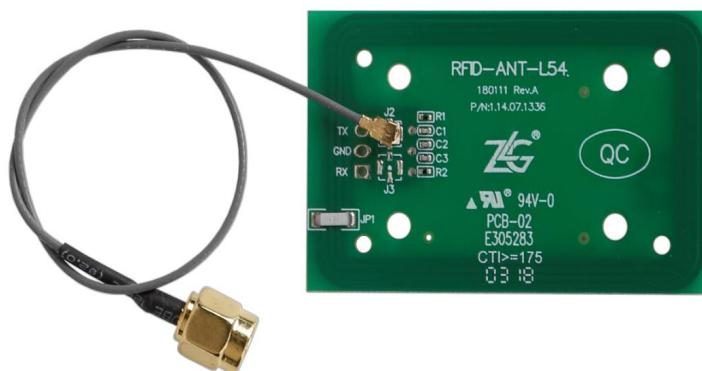

| 5. Antenna Selection.....                     | 40 |

| 5.1 Antenna Types.....                        | 40 |

| 5.2 Antenna Parameters.....                   | 41 |

| 5.2.1 Frequency Range.....                    | 41 |

| 5.2.2 Standing Wave Ratio VSWR.....           | 41 |

| 5.2.3 Impedance.....                          | 41 |

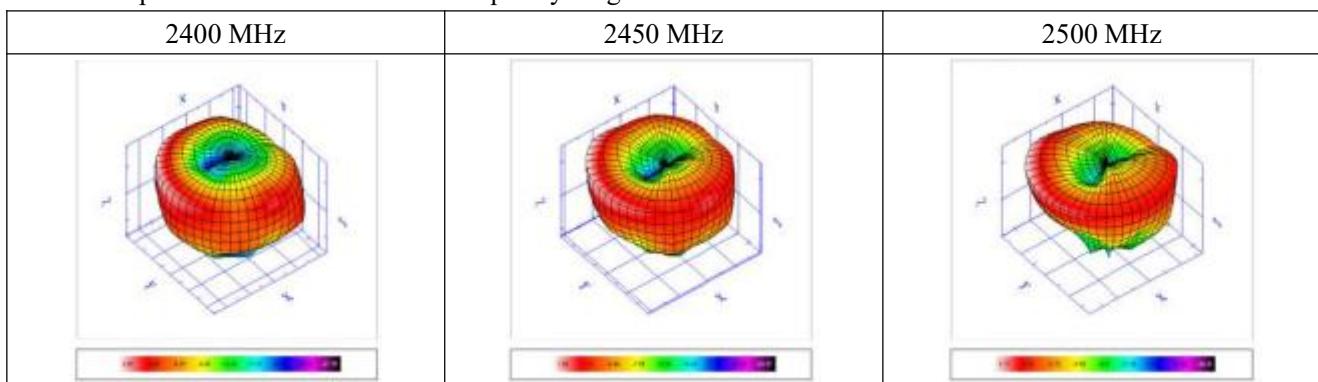

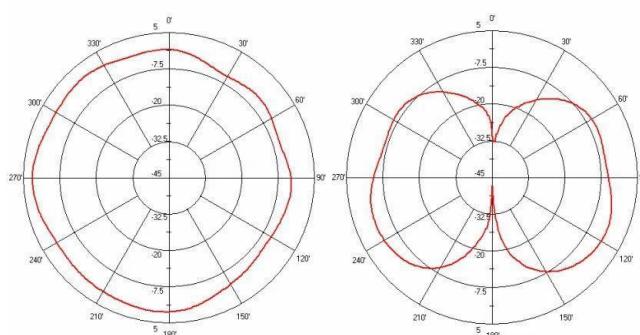

| 5.2.4 Directivity of the Antenna.....         | 42 |

| 5.3 Antenna Installation and Precautions..... | 43 |

| 5.4 Mifare Coil Antenna.....                  | 43 |

| 6. Mechanical Dimensions.....                 | 44 |

| 7. Disclaimer.....                            | 46 |

## 1. Function Introduction

A6G2C series core boards are a series of embedded industrial control wireless core boards with NXPi.MX6UL processor as the core developed by Guangzhou ZLG Electronics Co., Ltd. The core board adopts the Cortex-A7 core processor with superior performance, which provides fast data processing and smooth interface switching. The product provides eight UART interfaces, two USB OTG interfaces, a maximum of two CAN-bus interfaces, two Ethernet interfaces, and other communication interfaces, and implements the on-board WiFi, Bluetooth, Zigbee, NFC functions. The product provides powerful industrial control communication interfaces, and meets the needs of most industrial applications, portable consumer electronics, automotive electronics and other industries.

The A6G2C series core board integrates the i.MX6UL processor, standard 128/256MB DDR3 and 128/256MBNAND Flash, hardware watchdog. Different types of core boards are equipped with WiFi, Bluetooth, Zigbee and other modules, with complete minimum system functions, which greatly shortens the product development cycle. The core board has passed strict EMC and high and low temperature tests to ensure that it can work stably in harsh environments.

Guangzhou ZLG Electronics Co., Ltd. provides various mature hardware solutions and rich software resources including Linux and AWorks operating systems. The complete software and hardware architecture allows you to focus on product application. It has the characteristics of short development cycle, humanized system and complete software supporting.

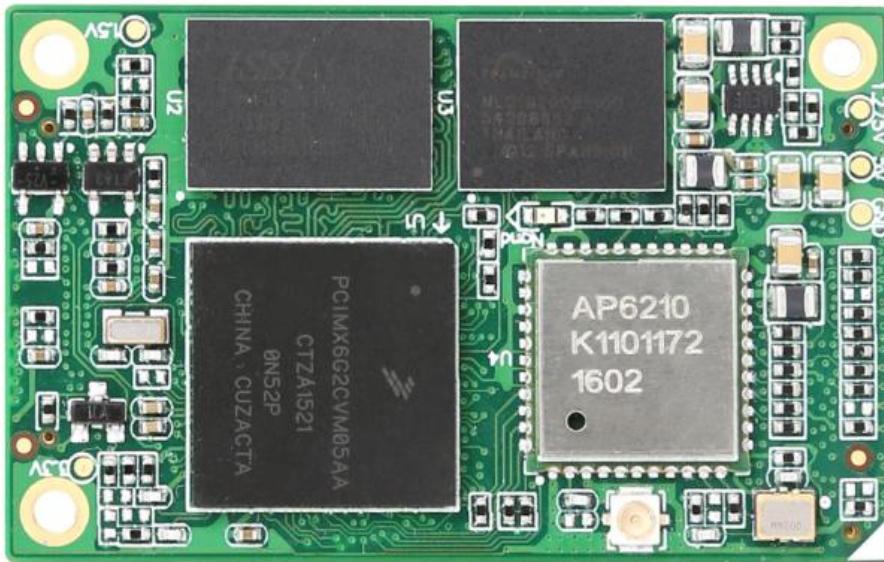

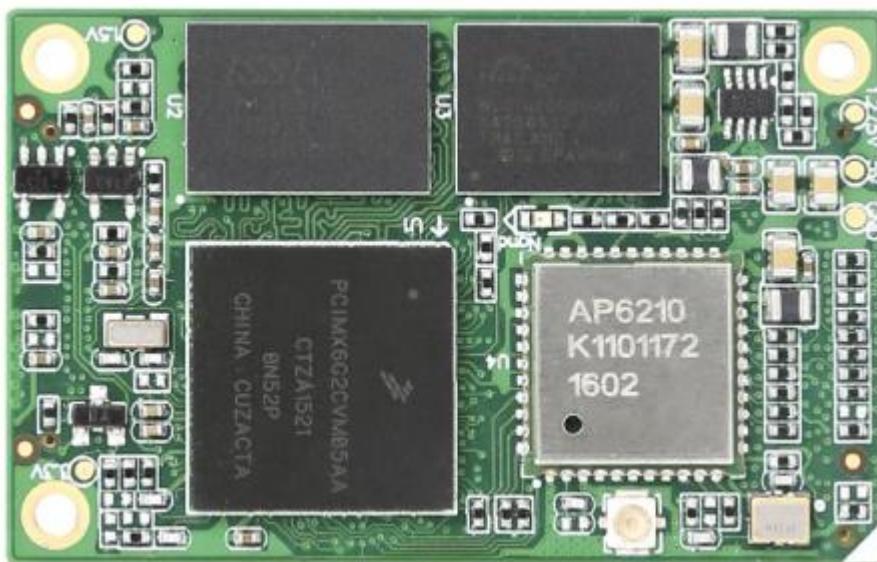

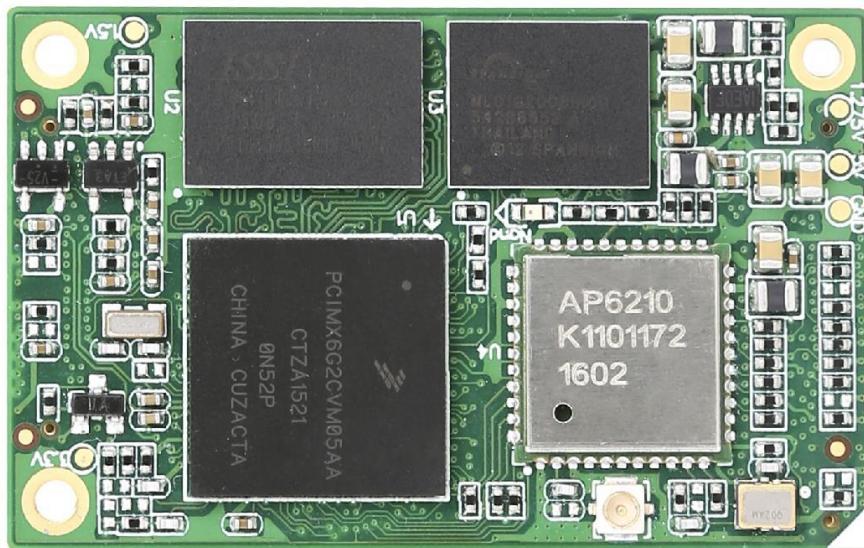

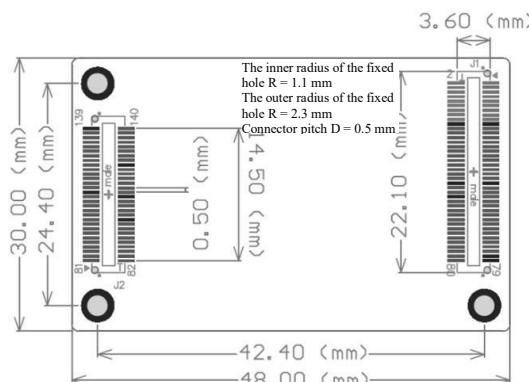

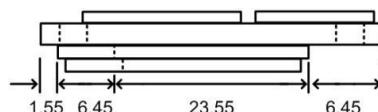

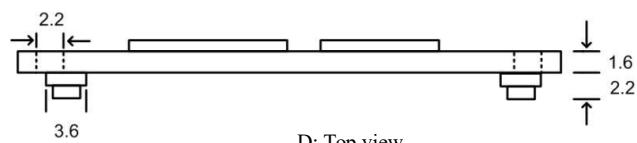

The A6G2C series core board is a 30 mmx48 mm core module with pins routed out through board-to-board connectors. Figure 1.1 shows the product appearance.

Figure 1.1 Product appearance

The A6G2C series core boards include seven product models: A6G2C-W128LI, A6G2C-W256LI, A6G2C-WB128LI, A6G2C-WB256LI, A6G2C-5WB128LI-T, A6G2C-Z128F128LI-T, and A6G2C-M128F128LI-T. For the convenience of description, the "A6G2C and A6G2A series core board" is abbreviated as "A6G2C core board" below.

### 1.1 Hardware Parameters

#### Processor

- 528MHz ARM Cortex-A7 32-bit microcontroller i.MX6UL;

- NEON MPE coprocessor;

- 32KB instruction, 32KB L1 data cache with single error detection (parity);

- 256KB L2 cache with error correcting code (ECC).

#### System memory

- Standard 128MByte DDR3 SDRAM

- ( A6G2C-W128LI 、 A6G2C-WB128LI 、 A6G2C-5WB128LI-T 、 A6G2C-Z128F128LI-T 、 A6G2C-M128F128LI-T ) ；

- Standard 256MByte DDR3 SDRAM;

- ( A6G2C-W256LI 、 A6G2C-WB256LI ) 。

#### Electronic hard disk

- Standard 128MByte NAND Flash

- ( A6G2C-W128LI 、 A6G2C-WB128LI 、 A6G2C-5WB128LI-T 、 A6G2C-Z128F128LI-T 、 A6G2C-M128F128LI-T ) ；

- Standard 256MByte NAND Flash;

- ( A6G2C-W256LI 、 A6G2C-WB256LI ) 。

## 1.2 Software Parameters

### 1.2.1 Linux Driver Library

The product provides the driver library under Linux for all the functional components of the A6G2C series core board. The specific driver resources are as follows:

- NAND Flash driver;

- The NAND Flash format is the TFAT file system (The file system will not be damaged if the system is suddenly powered off);

- Display driver (16-bit TFT LCD);

- Touch screen driver;

- LCD screen backlight driver;

- Audio interface driver;

- USB Host driver, support USB keyboard, USB mouse and U disk;

- USB OTG driver, support HOST and Device function driver switching;

- Ethernet driver;

- CAN-bus fieldbus driver;

- RS-232/RS-485 interface driver;

- SD card driver, support hot-swappable SD cards;

- WIFI, Bluetooth, Zigbee, NFC drivers, apps;

- General I/O driver;

- Buzzer driver;

- I2C driver;

- Watchdog driver.

### 1.2.2 AWorks Driver Library

Provides the driver library under AWorks for all the functional components of the A6G2C series core board, including the specific drivers

The resources are as follows:

- NAND Flash driver;

- Display driver (16-bit TFT LCD);

- Touch screen driver;

- LCD screen backlight driver;

- Audio interface driver;

- USB Host driver, support USB keyboard, USB mouse and U disk;

- USB OTG driver, support HOST and Device function driver switching;

- Ethernet driver;

- CAN-bus fieldbus driver;

- RS-232/RS-485 interface driver;

- SD card driver, support hot-swappable SD cards;

- WIFI, Bluetooth, Zigbee, NFC drivers, apps;

- General I/O driver;

- Buzzer driver;

- I2C driver;

- Watchdog driver.

The software and hardware can be customized. For product customization, please feel free to contact

Guangzhou ZLG Electronics Co., Ltd.

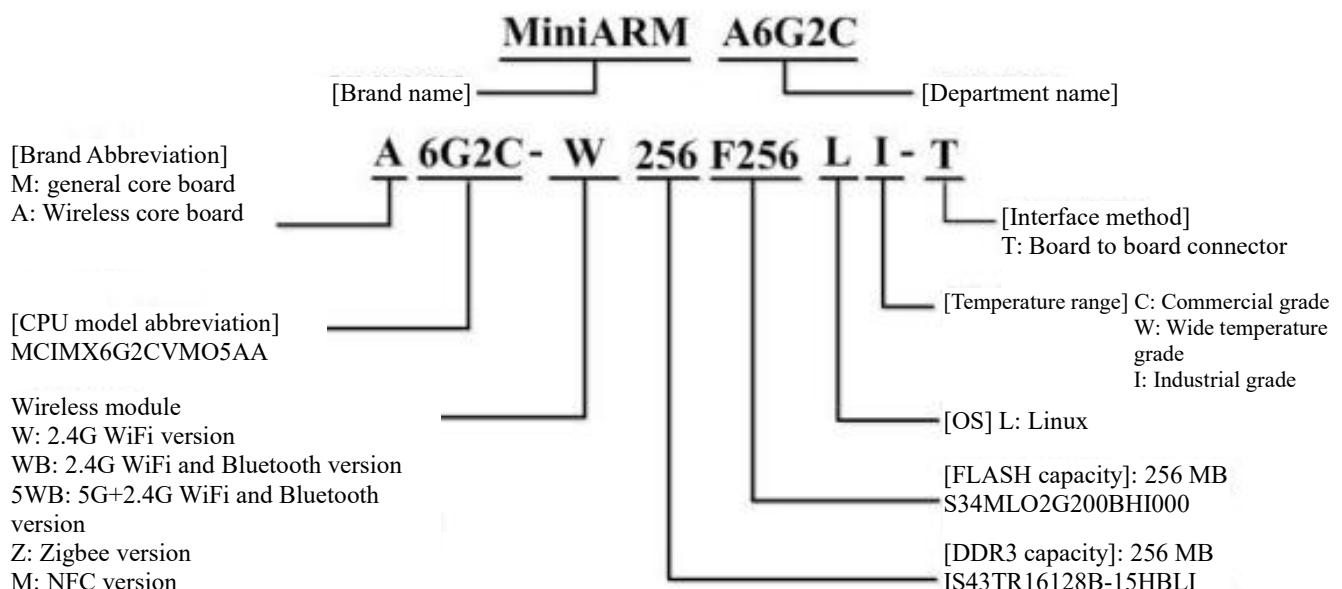

### 1.3 Product Model Naming Rules

Figure 1.2 Product naming rules

## 1.4 Type Selection Comparison Table

Table 1.1 A6G2C series core board selection comparison table 1

| Model Resources \ Model | A6G2C-5WB128LI-T                                   | A6G2C-Z128F128LI-T                                 | A6G2C-W128LI                                       |

|-------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Resources               |                                                    |                                                    | A6G2C-W256LI                                       |

| CPU model               | MCIMX6G2CVM05AA                                    | MCIMX6G2CVM05AA                                    | MCIMX6G2CVM05AA                                    |

| NandFlash               | 128MB                                              | 128MB                                              | 128MB                                              |

|                         |                                                    |                                                    | 256MB                                              |

| Memory (DDR3)           | 128MB                                              | 128MB                                              | 128MB                                              |

|                         |                                                    |                                                    | 256MB                                              |

| Ethernet                | Two                                                | Two                                                | Two                                                |

| USB OTG                 | Two                                                | Two                                                | Two                                                |

| CAN                     | One way                                            | Two                                                | Two                                                |

| LCD                     | Support (RGB565)                                   | Support (RGB565)                                   | Support (RGB565)                                   |

| SD                      | One way                                            | One way                                            | One way                                            |

| UART                    | 7                                                  | 7                                                  | 8                                                  |

| I2C                     | One analog I2C<br>(a maximum of four hardware I2C) | One analog I2C<br>(a maximum of four hardware I2C) | One analog I2C<br>(a maximum of four hardware I2C) |

| SPI                     | 1 (a maximum of 4)                                 | 1 (a maximum of 4)                                 | 1 (a maximum of 4)                                 |

| I <sup>2</sup> S/SAI    | 1 (multiplexed)                                    | 1 (multiplexed)                                    | 1 (multiplexed)                                    |

| PWM                     | 2 (a maximum of 8)                                 | 2 (a maximum of 8)                                 | 2 (a maximum of 8)                                 |

| ADC                     | 1 x 2 channels<br>(a maximum of 2 x 10 channels)   | 1 x 2 channels<br>(a maximum of 2 x 10 channels)   | 1 x 2 channels<br>(a maximum of 2 x 10 channels)   |

| Touch screen            | Support (4-wire resistive)                         | Support (4-wire resistive)                         | Support (4-wire resistive)                         |

| JTAG                    | Support                                            | Support                                            | Support                                            |

| Analog audio            | Supports medium quality<br>PWM-like audio output   | Supports medium quality<br>PWM-like audio output   | Supports medium quality<br>PWM-like audio output   |

| GPIO                    | 2 (a maximum of 91)                                | 2 (a maximum of 91)                                | 2 (a maximum of 91)                                |

| Watchdog                | Support independent hardware watchdog              | Support independent hardware watchdog              | Support independent hardware watchdog              |

Table 1.2 A6G2C series core board selection comparison table 2

| Model<br>Resources \ Model | A6G2C-WB128LI                                         | A6G2C-M128F128LI-T                                    | A6G2A-W256F256LI-T                                    |

|----------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| Resources                  | A6G2C-WB256LI                                         |                                                       |                                                       |

| CPU model                  | MCIMX6G2CVM05AA                                       | MCIMX6G2CVM05AA                                       | MCIMX6G2AVM05AA                                       |

| NandFlash                  | 128MB                                                 | 128MB                                                 | 256MB                                                 |

|                            | 256MB                                                 |                                                       |                                                       |

| Memory<br>(DDR3)           | 128MB                                                 | 128MB                                                 | 256MB                                                 |

|                            | 256MB                                                 |                                                       |                                                       |

| Ethernet                   | Two                                                   | Two                                                   | Two                                                   |

| USB OTG                    | Two                                                   | Two                                                   | Two                                                   |

| CAN                        | One way                                               | Two                                                   | Two                                                   |

| LCD                        | Support (RGB565)                                      | Support (RGB565)                                      | Support (RGB565)                                      |

| SD                         | One way                                               | One way                                               | One way                                               |

| UART                       | 7                                                     | 8                                                     | 8                                                     |

| I2C                        | One analog I2C<br>(a maximum of four hardware<br>I2C) | One analog I2C<br>(a maximum of four hardware<br>I2C) | One analog I2C<br>(a maximum of four hardware<br>I2C) |

| SPI                        | 1 (a maximum of 4)                                    | 1 (a maximum of 4)                                    | 1 (a maximum of 4)                                    |

| I <sup>2</sup> S/SAI       | 1 (multiplexed)                                       | 1 (multiplexed)                                       | 1 (multiplexed)                                       |

| PWM                        | 2 (a maximum of 8)                                    | 2 (a maximum of 8)                                    | 2 (a maximum of 8)                                    |

| ADC                        | 1 x 2 channels<br>(a maximum of 2 x 10 channels)      | 1 x 2 channels<br>(a maximum of 2 x 10 channels)      | 1 x 2 channels<br>(a maximum of 2 x 10 channels)      |

| Touch screen               | Support (4-wire resistive)                            | Support (4-wire resistive)                            | Support (4-wire resistive)                            |

| JTAG                       | Support                                               | Support                                               | Support                                               |

| Analog audio               | Supports medium quality<br>PWM-like audio output      | Supports medium quality<br>PWM-like audio output      | Supports medium quality<br>PWM-like audio output      |

| GPIO                       | 2 (a maximum of 91)                                   | 2 (a maximum of 91)                                   | 2 (a maximum of 91)                                   |

| Watchdog                   | Support independent hardware<br>watchdog              | Support independent hardware<br>watchdog              | Support independent hardware<br>watchdog              |

## 2. Performance Parameters

### 2.1 Main Performance Configuration of A6G2C Core Board System

Table 2.1 System main frequency list

| Name             | Parameter | Specification |         |         |      | Description |

|------------------|-----------|---------------|---------|---------|------|-------------|

|                  |           | Minimum       | Typical | Maximum | Unit |             |

| System frequency | Fclk1     | --            | --      | 528     | MHz  | --          |

| System RTC clock | Fclk2     | --            | 32.768  | --      | KHz  | --          |

The configuration in this table is the optimal configuration of the system, and it is recommended not to modify the configuration.

### 2.2 Operating Temperature of the Core Board

Table 2.2 A6G2C core board operating environment temperature

| Core board model   | Operating ambient temperature |         |         |      | Operating environment humidity<br>(without condensation) |         |         |      |

|--------------------|-------------------------------|---------|---------|------|----------------------------------------------------------|---------|---------|------|

|                    | Minimum                       | Typical | Maximum | Unit | Minimum                                                  | Typical | Maximum | Unit |

| A6G2C-W128LI       |                               |         |         |      |                                                          |         |         |      |

| A6G2C-W256LI       | -30                           | +25     | +85     | °C   | 5                                                        | --      | 95      | % RH |

| A6G2C-WB128LI      |                               |         |         |      |                                                          |         |         |      |

| A6G2C-WB256LI      |                               |         |         |      |                                                          |         |         |      |

| A6G2A-W256F256LI-T | -30                           | +25     | +85     | °C   | 5                                                        | --      | 95      | % RH |

| A6G2C-5WB128LI-T   | -20                           | +25     | +75     | °C   | 5                                                        | --      | 95      | % RH |

| A6G2C-Z128F128LI-T | -40                           | +25     | +85     | °C   | 5                                                        | --      | 95      | % RH |

| A6G2C-M128F128LI-T | -40                           | +25     | +85     | °C   | 5                                                        | --      | 95      | % RH |

The official recommendation of the CPU manufacturer NXP for the CPU chip (MCIMX6G2CVM05AA):

If the junction temperature of the CPU chip in use exceeds 105°C, the CPU will enter the over-temperature protection state and will not be able to start and run properly. Take thermal measures to ensure that the junction temperature of the CPU is below 105°C so that the CPU can boot and operate properly. If the core board is used when the ambient temperature exceeds 70°C, or the junction temperature of the CPU chip exceeds 105°C, it is recommended that you use a temperature collector to collect the surface temperature of the CPU. If the surface temperature of the CPU exceeds 90°C, take heat dissipation measures, such as adding radiators and fans.

To protect the CPU, takes the following measures for the factory firmware by default:

- 1) When the board core board attempts to start, it is not allowed to start if the CPU junction temperature exceeds 100°C;

- 2) After the core board is started, if the CPU junction temperature exceeds 100°C, the system will start the frequency reduction function to reduce the junction temperature;

- 3) When the core board starts, the system will automatically shut down if the CPU junction temperature exceeds 105°C.

## 2.3 Storage capacity of the core board

Table 2.3 Storage capacity parameters

| Type       | Specification |         |         |      | Description           |

|------------|---------------|---------|---------|------|-----------------------|

|            | Minimum       | Typical | Maximum | Unit |                       |

| DDR3       | --            | 128/256 | --      | MB   | Memory                |

| Nand Flash | --            | 128/256 | --      | MB   | Program, data storage |

## 2.4 A6G2C Core Board Communication Performance

Table 2.4 Serial communication interface speed of the A6G2C core board

| Core board model | Parameter                  | Specification |         |         |      | Description |

|------------------|----------------------------|---------------|---------|---------|------|-------------|

|                  |                            | Minimum       | Typical | Maximum | Unit |             |

| A6G2C core board | Serial communication speed | --            | 115200  | --      | bps  | --          |

| A6G2C core board | SPI communication speed    | --            | --      | 52      | MHz  |             |

| A6G2C core board | I2C communication speed    | --            | 100     | 400     | Kbps | --          |

| A6G2C core board | CAN communication speed    | --            | --      | 1       | Mbps | --          |

## 2.5 Other Performance of A6G2C Core Board

Table 2.5 Watchdog parameters

| Function          | Parameter         | Specification |         |         |      | Description |

|-------------------|-------------------|---------------|---------|---------|------|-------------|

|                   |                   | Minimum       | Typical | Maximum | Unit |             |

| Hardware watchdog | Overflow period   | 1.12          | 1.4     | 1.6     | s    | --          |

|                   | Reset pulse width | --            | 200     | --      | ms   | --          |

Table 2.6 A6G2C core board I/O ports

| Parameter                 | No.                  | Specification |         |         |      | Description                                 |

|---------------------------|----------------------|---------------|---------|---------|------|---------------------------------------------|

|                           |                      | Minimum       | Typical | Maximum | Unit |                                             |

| High-level input voltage  | VI <sub>H</sub>      | 2.3           | --      | 3.3     | V    | --                                          |

| Low-level input voltage   | VI <sub>L</sub>      | 0             | --      | 0.69    | V    | --                                          |

| High-level output voltage | V <sub>OH</sub>      | 3.15          | --      | --      | V    | --                                          |

| Low-level output voltage  | V <sub>OL</sub>      | --            | --      | 0.15    | V    | --                                          |

| ESD protection            | V <sub>ESD_HBM</sub> | --            | --      | 2000    | V    | Protection level of human body live contact |

|       |                      |    |    |     |   |                                                                                               |

|-------|----------------------|----|----|-----|---|-----------------------------------------------------------------------------------------------|

| level |                      |    |    |     |   | discharge                                                                                     |

|       | V <sub>ESD_CDM</sub> | -- | -- | 500 | V | Material contact discharge protection level during processing, handling, transportation, etc. |

## 2.6 Power Supply Static Parameters

Table 2.7 Power supply static electrical parameters

| Parameter           | No.                  | Specification |         |         |      | Description  |

|---------------------|----------------------|---------------|---------|---------|------|--------------|

|                     |                      | Minimum       | Typical | Maximum | Unit |              |

| 5.0V system voltage | VDD_5.0              | 4.75          | 5.0     | 5.25    | V    | --           |

| 5.0V system current | I <sub>VDD_5.0</sub> | --            | 110     | 130     | mA   | Boot current |

Continued

| parameter   | No.                  | Specification |         |         |      | Description |

|-------------|----------------------|---------------|---------|---------|------|-------------|

|             |                      | Minimum       | Typical | Maximum | Unit |             |

| RTC voltage | VDD_RTC              | 2.5           | 3.0     | 3.3     | V    | --          |

| RTC current | I <sub>VDD_RTC</sub> | --            | --      | 40      | µA   | --          |

### 3. Pin Function

#### 3.1 Pin Information

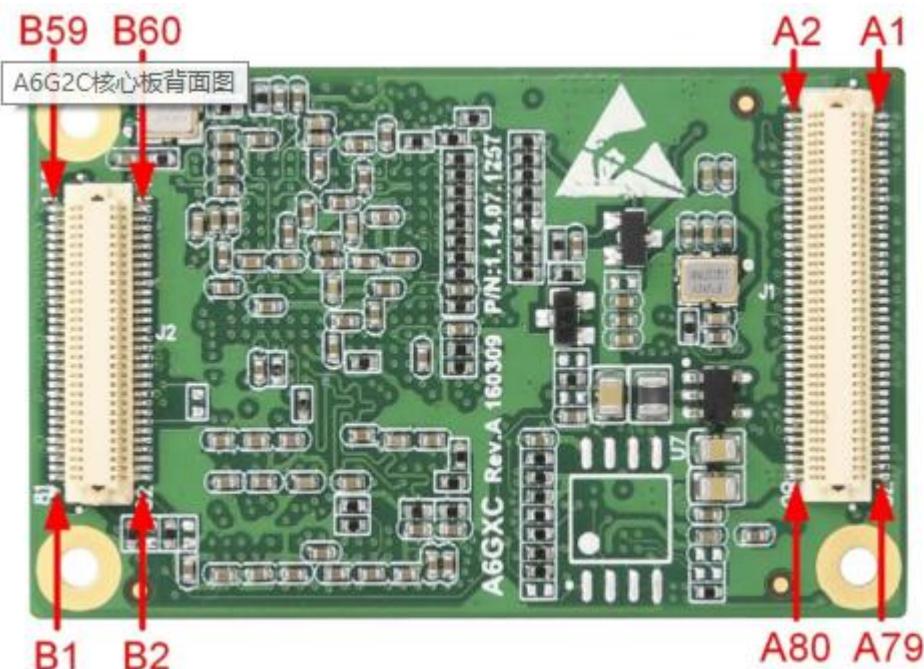

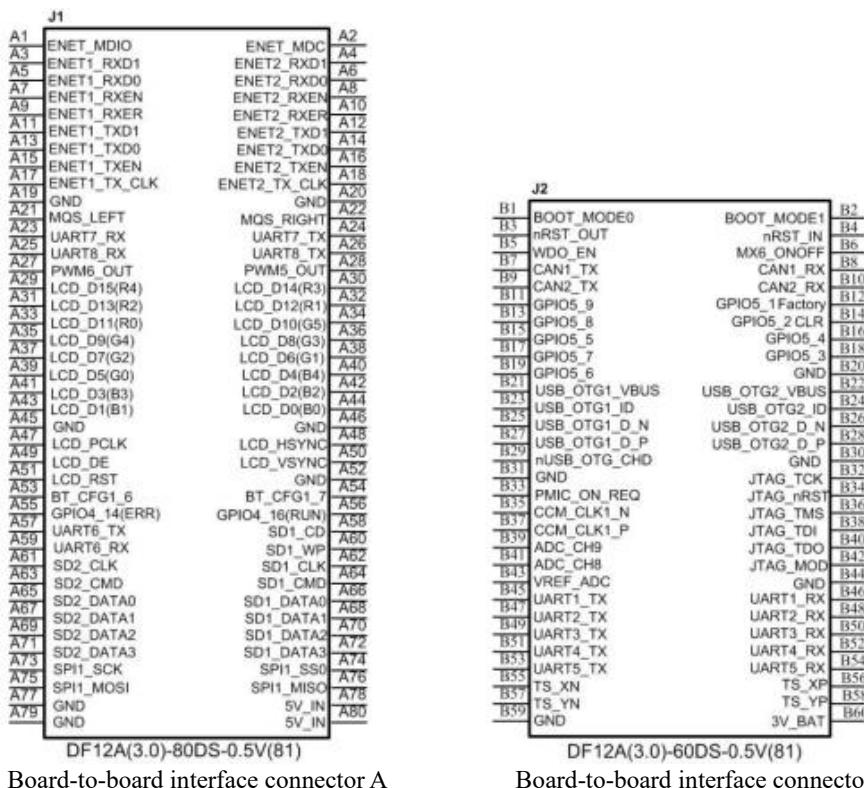

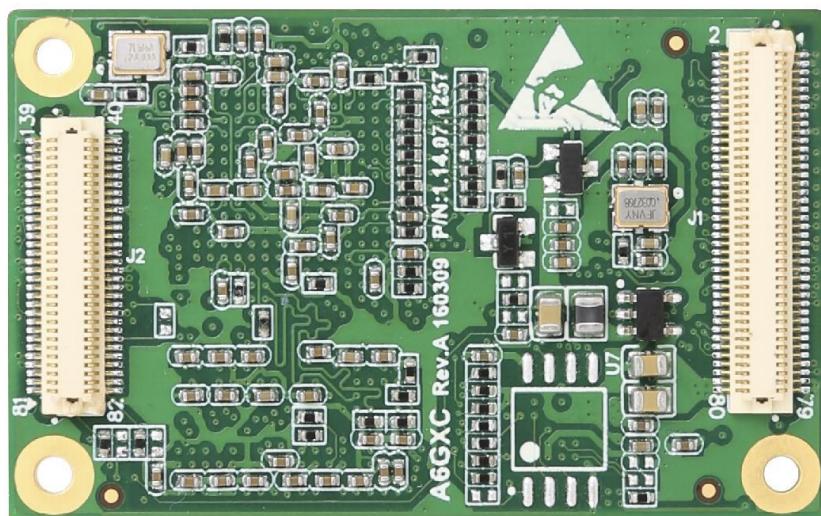

The A6G2C series core board maintains the original definition of some pin multiplexing functions of the i.MX6UL processor, and redefines the extension or conversion functions. Users can refer to the design to cooperate with product standard-driven development. To ensure good compatibility and stability of product design, the pin resources not used by the user must be suspended. Figure 3.1 shows the interface pinout sequence.

Figure 3.1 Interface pinout sequence

Figure 3.2 Front side of the product

### 3.2 A6G2C Core Board Pin Definitions

The following table lists the interface pin definitions of the A6G2C core board. All the pin functions of the A6G2C core board are specified in the "default function" of the following table. Do not modify them; otherwise, it may conflict with the factory driver. For any questions, please feel free to contact our sales or technical support.

Table 3.1 Interface pin definitions of the A6G2C series core board A

| Pin No. | Name         | Default function | Reference level | Input/Output | Processor pins |

|---------|--------------|------------------|-----------------|--------------|----------------|

| A1      | ENET_MDIO    | ENET1& ENET2     | 3.3V            | Input/Output | K17            |

| A2      | ENET_MDC     |                  | 3.3V            | Output       | L16            |

| A3      | ENET1_RXD1   |                  | 3.3V            | Input        | E17            |

| A4      | ENET2_RXD1   |                  | 3.3V            | Input        | C16            |

| A5      | ENET1_RXD0   |                  | 3.3V            | Input        | F16            |

| A6      | ENET2_RXD0   |                  | 3.3V            | Input        | C17            |

| A7      | ENET1_RXEN   |                  | 3.3V            | Output       | E16            |

| A8      | ENET2_RXEN   |                  | 3.3V            | Output       | B17            |

| A9      | ENET1_RXER   |                  | 3.3V            | Input        | D15            |

| A10     | ENET2_RXER   |                  | 3.3V            | Input        | D16            |

| A11     | ENET1_TXD1   |                  | 3.3V            | Output       | E14            |

| A12     | ENET2_TXD1   |                  | 3.3V            | Output       | A16            |

| A13     | ENET1_TXD0   |                  | 3.3V            | Output       | E15            |

| A14     | ENET2_TXD0   |                  | 3.3V            | Output       | A15            |

| A15     | ENET1_TXEN   |                  | 3.3V            | Output       | F15            |

| A16     | ENET2_TXEN   |                  | 3.3V            | Output       | B15            |

| A17     | ENET1_TX_CLK |                  | 3.3V            | Output       | F14            |

| A18     | ENET2_TX_CLK |                  | 3.3V            | Output       | D17            |

| A19     | GND          | GND              | --              | --           | --             |

| A20     | GND          |                  | --              | --           | --             |

| A21     | MOS_LEFT     | Audio            | --              | Output       | B16            |

| A22     | MOS_RIGHT    |                  | --              | Output       | A14            |

| A23     | UART7_RX     | UART             | 3.3V            | Input        | B13            |

| A24     | UART7_TX     |                  | 3.3V            | Output       | C13            |

| A25     | UART8_RX     |                  | 3.3V            | Input        | B14            |

| A26     | UART8_TX     |                  | 3.3V            | Output       | C14            |

| A27     | PWM_OUT6     | PWM              | 3.3V            | Output       | D14            |

| A28     | PWM_OUT5     |                  | 3.3V            | Output       | A13            |

| A29     | LCD_R4       | LCD              | 3.3V            | Output       | D13            |

| A30     | LCD_R3       |                  | 3.3V            | Output       | A12            |

| A31     | LCD_R2       |                  | 3.3V            | Output       | B12            |

| A32     | LCD_R1       |                  | 3.3V            | Output       | C12            |

| A33     | LCD_R0       |                  | 3.3V            | Output       | D12            |

| A34     | LCD_G5       |                  | 3.3V            | Output       | E12            |

| A35     | LCD_G4       |                  | 3.3V            | Output       | A11            |

| A36     | LCD_G3       |                  | 3.3V            | Output       | B11            |

Continued

| Pin No. | Name          | Default function                    | Reference level | Input/Output | Processor pins |  |

|---------|---------------|-------------------------------------|-----------------|--------------|----------------|--|

| A37     | LCD_G2        | LCD                                 | 3.3V            | Output       | D11            |  |

| A38     | LCD_G1        |                                     | 3.3V            | Output       | A10            |  |

| A39     | LCD_G0        |                                     | 3.3V            | Output       | B10            |  |

| A40     | LCD_B4        |                                     | 3.3V            | Output       | C10            |  |

| A41     | LCD_B3        |                                     | 3.3V            | Output       | D10            |  |

| A42     | LCD_B2        |                                     | 3.3V            | Output       | E10            |  |

| A43     | LCD_B1        |                                     | 3.3V            | Output       | A9             |  |

| A44     | LCD_B0        |                                     | 3.3V            | Output       | B9             |  |

| A45     | GND           |                                     | --              | --           | --             |  |

| A46     |               |                                     | --              | --           | --             |  |

| A47     | LCD_PCLK      | LCD                                 | 3.3V            | Output       | A8             |  |

| A48     | LCD_HSYNC     |                                     | 3.3V            | Output       | D9             |  |

| A49     | LCD_DE        |                                     | 3.3V            | Output       | B8             |  |

| A50     | LCD_VSYNC     |                                     | 3.3V            | Output       | C9             |  |

| A51     | GPIO3_4       | For usage details,<br>see Table 3.3 | 3.3V            | Input/Output | E9             |  |

| A52     | GND           |                                     | --              | --           | --             |  |

| A53     | BT_CFG1_6     | BOOT                                | 3.3V            | Input        | --             |  |

| A54     | BT_CFG1_7     |                                     | 3.3V            | Input        | --             |  |

| A55     | GPIO4_14(ERR) | GPIO                                | 3.3V            | Input/Output | B5             |  |

| A56     | GPIO4_16(RUN) |                                     | 3.3V            | Input/Output | E6             |  |

| A57     | UART6_TX      | UART                                | 3.3V            | Output       | F5             |  |

| A58     | SD1_CD        | SD1                                 | 3.3V            | Input        | J14            |  |

| A59     | UART6_RX      | UART                                | 3.3V            | Input        | E5             |  |

| A60     | SD1_WP        | SD1&SD2                             | 3.3V            | Input        | K15            |  |

| A61     | SD2_CLK       |                                     | --              | --           | --             |  |

| A62     | SD1_CLK       |                                     | 3.3V            | Output       | C1             |  |

| A63     | SD2_CMD       |                                     | --              | --           | --             |  |

| A64     | SD1_CMD       |                                     | 3.3V            | Output       | C2             |  |

| A65     | SD2_DATA0     |                                     | --              | --           | --             |  |

| A66     | SD1_DATA0     |                                     | 3.3V            | Input/Output | B3             |  |

| A67     | SD2_DATA1     |                                     | --              | --           | --             |  |

| A68     | SD1_DATA1     |                                     | 3.3V            | Input/Output | B2             |  |

| A69     | SD2_DATA2     |                                     | --              | --           | --             |  |

| A70     | SD1_DATA2     |                                     | 3.3V            | Input/Output | B1             |  |

| A71     | SD2_DATA3     |                                     | --              | --           | --             |  |

| A72     | SD1_DATA3     |                                     | 3.3V            | Input/Output | A2             |  |

| A73     | SPI1_SCK      | SPI1                                | 3.3V            | Output       | D4             |  |

| A74     | SPI1_SS0      |                                     | 3.3V            | Output       | D3             |  |

| A75     | SPI1_MOSI     |                                     | 3.3V            | Output       | D2             |  |

Continued

| Pin No. | Name      | Default function | Reference level | Input/Output | Processor pins |

|---------|-----------|------------------|-----------------|--------------|----------------|

| A76     | SPI1_MISO | SPI1             | 3.3V            | Input        | D1             |

| A77     | GND       | GND              | --              | --           | --             |

| A78     | 5V_IN     | POWER            | --              | Input        | --             |

| A79     | GND       |                  | --              | --           | --             |

| A80     | 5V_IN     |                  | --              | Input        | --             |

Table 3.2 Interface pin definitions of the A6G2C series core board B

| Pin No. | Name             | Default function                                                  | Reference level | Input/Output | Processor pins |

|---------|------------------|-------------------------------------------------------------------|-----------------|--------------|----------------|

| B1      | BOOT_MODE0       | BOOT                                                              | 3.3V            | Input        | T10            |

| B2      | BOOT_MODE1       |                                                                   | 3.3V            | Input        | U10            |

| B3      | nRST_OUT         | RESET                                                             | 3.3V            | Output       | --             |

| B4      | nRST_IN          |                                                                   | 3.3V            | Input        | --             |

| B5      | WDO_EN           | Watchdog control pin                                              | 3.3V            | Input        | --             |

| B6      | MX6_ONOFF        | System startup/shutdown                                           | 3.3V            | Input        | R8             |

| B7      | CAN1_TX          | CAN1&CAN2<br><br><b>Table 3.3 lists the use of B9/B10</b>         | 3.3V            | Output       | H15            |

| B8      | CAN1_RX          |                                                                   | 3.3V            | Input        | G14            |

| B9      | CAN2_TX          |                                                                   | 3.3V            | Output       | J15            |

| B10     | CAN2_RX          |                                                                   | 3.3V            | Input        | H14            |

| B11     | GPIO5_9          | GPIO<br><br><b>Table 3.3 describes the use of B11/B14/B15/B19</b> | 3.3V            | Input/Output | R6             |

| B12     | GPIO5_1(Factory) |                                                                   | 3.3V            | Input/Output | R9             |

| B13     | I2C_SDA          |                                                                   | 3.3V            | Input/Output | N9             |

| B14     | GPIO5_2(CLR)     |                                                                   | 3.3V            | Input/Output | P11            |

| B15     | GPIO5_5          |                                                                   | 3.3V            | Input/Output | N8             |

| B16     | GPIO5_4          |                                                                   | 3.3V            | Input/Output | P9             |

| B17     | I2C_SCL          |                                                                   | 3.3V            | Output       | N10            |

| B18     | GPIO5_3          |                                                                   | 3.3V            | Input/Output | P10            |

| B19     | GPIO5_6          |                                                                   | 3.3V            | Input/Output | N11            |

| B20     | GND              | GND                                                               | --              | --           | --             |

| B21     | USB_OTG1_VBUS    | USB1&USB2                                                         | 5V              | Input        | T12            |

| B22     | USB_OTG2_VBUS    |                                                                   | 5V              | Input        | U12            |

| B23     | USB_OTG1_ID      |                                                                   | 3.3V            | Input        | K13            |

| B24     | USB_OTG2_ID      |                                                                   | 3.3V            | Input        | M17            |

| B25     | USB_OTG1_D_N     |                                                                   | 3.3V            | Input/Output | T15            |

| B26     | USB_OTG2_D_N     |                                                                   | 3.3V            | Input/Output | T13            |

| B27     | USB_OTG1_D_P     |                                                                   | 3.3V            | Input/Output | U15            |

| B28     | USB_OTG2_D_P     |                                                                   | 3.3V            | Input/Output | U13            |

| B29     | nUSB_OTG_CHD     |                                                                   | 3.3V            | Input        | U16            |

| B30     | GND              | GND                                                               | --              | --           | --             |

| B31     | GND              | --                                                                | --              | --           |                |

| B32     | JTAG_TCK         | JTAG                                                              | 3.3V            | Output       | M14            |

Continued

| Pin No. | Name        | Default function                                          | Reference level | Input/Output | Processor pins |

|---------|-------------|-----------------------------------------------------------|-----------------|--------------|----------------|

| B33     | PMIC_ON_REQ | Power management                                          | 3.3V            | Output       | T9             |

| B34     | JTAG_nTRST  | JTAG                                                      | 3.3V            | Input        | N14            |

| B35     | CCM_CLK1_N  | CPU clock differential negative                           | 3.3V            | Output       | P16            |

| B36     | JTAG_TMS    | JTAG                                                      | 3.3V            | Input        | P14            |

| B37     | CCM_CLK1_P  | CPU clock differential positive                           | 3.3V            | Output       | P17            |

| B38     | JTAG_TDI    | JTAG                                                      | 3.3V            | Input        | N16            |

| B39     | ADC_CH9     | ADC                                                       | --              | Input        | M15            |

| B40     | JTAG_TDO    | JTAG                                                      | 3.3V            | Output       | N15            |

| B41     | ADC_CH8     | ADC                                                       | --              | Input        | N17            |

| B42     | JTAG_MOD    | JTAG                                                      | 3.3V            | Input        | P15            |

| B43     | VREF_ADC    | ADC                                                       | --              | Input        | M13            |

| B44     | GND         | GND                                                       | --              | --           | --             |

| B45     | UART1_TX    | UART<br><br><b>Table 3.3 describes the use of B47/B48</b> | 3.3V            | Output       | K14            |

| B46     | UART1_RX    |                                                           | 3.3V            | Input        | K16            |

| B47     | UART2_TX    |                                                           | 3.3V            | Output       | J17            |

| B48     | UART2_RX    |                                                           | 5.0V            | Input        | J16            |

| B49     | UART3_TX    |                                                           | 3.3V            | Output       | H17            |

| B50     | UART3_RX    |                                                           | 3.3V            | Input        | H16            |

| B51     | UART4_TX    |                                                           | 3.3V            | Output       | G17            |

| B52     | UART4_RX    |                                                           | 3.3V            | Input        | G16            |

| B53     | UART5_TX    |                                                           | 3.3V            | Output       | F17            |

| B54     | UART5_RX    |                                                           | 3.3V            | Input        | G13            |

| B55     | TS_XN       | TOUCH                                                     | 3.3V            | Input        | L17            |

| B56     | TS_XP       |                                                           | 3.3V            | Input        | M16            |

| B57     | TS_YN       |                                                           | 3.3V            | Input        | L15            |

| B58     | TS_YP       |                                                           | 3.3V            | Input        | L14            |

| B59     | GND         | GND                                                       | --              | --           | --             |

| B60     | 3V_BAT      | RTC battery                                               | --              | Input        | --             |

Table 3.3 Use of special pins

| Pin No. | Name     | Instructions                                                                                                         |

|---------|----------|----------------------------------------------------------------------------------------------------------------------|

| A51     | GPIO3_4  |                                                                                                                      |

| B9      | CAN2_TX  | 1) A6G2C-W128LI, A6G2C-W256LI, A6G2A-W256F256LI-T support all except GPIO5_5 and GPIO5_9                             |

| B10     | CAN2_RX  |                                                                                                                      |

| B11     | GPIO5_9  | 2) A6G2C-Z128F128LI-T supports all except UART2_TX, UART2_RX, GPIO5_5, GPIO5_9                                       |

| B14     | GPIO5_2  |                                                                                                                      |

| B15     | GPIO5_5  | 3) A6G2C-WB128LI, A6G2C-WB256LI, A6G2C-5WB128LI-T do not support these pins because this signal has been used for BT |

| B19     | GPIO5_6  |                                                                                                                      |

| B47     | UART2_TX | 4) A6G2C-M128F128LI-T support all the pins                                                                           |

| B48     | UART2_RX |                                                                                                                      |

### 3.3 Pin Function Description of the A6G2C Core Board

All pin functions of the A6G2C core board are specified in the "default function" in the following table. Do not modify them; otherwise, it may conflict with the factory driver. For any questions, please feel free to contact our sales or technical support.

Table 3.4 A6G2C core board pin function definition 1

| Pin No. | Signal Name  | Default function    | Function description                                      |

|---------|--------------|---------------------|-----------------------------------------------------------|

| A1      | ENET_MDIO    | ENET1&ENET2         | Ethernet management data interface                        |

| A2      | ENET_MDC     |                     | Ethernet management clock interface                       |

| A3      | ENET1_RXD1   |                     | ENET1 data receive signal 1                               |

| A4      | ENET2_RXD1   |                     | ENET2 data receive signal 1                               |

| A5      | ENET1_RXD0   |                     | ENET1 data receive signal 0                               |

| A6      | ENET2_RXD0   |                     | ENET2 data receive signal 0                               |

| A7      | ENET1_RXEN   |                     | ENET1 data reception enable                               |

| A8      | ENET2_RXEN   |                     | ENET2 data reception enable                               |

| A9      | ENET1_RXER   |                     | ENET1 data reception error                                |

| A10     | ENET2_RXER   |                     | ENET2 data reception error                                |

| A11     | ENET1_TXD1   |                     | ENET1 data transmit signal 1                              |

| A12     | ENET2_TXD1   |                     | ENET2 data transmit signal 1                              |

| A13     | ENET1_TXD0   |                     | ENET1 data transmission signal 0                          |

| A14     | ENET2_TXD0   |                     | ENET2 data transmission signal 0                          |

| A15     | ENET1_TXEN   |                     | ENET1 data transmission enable                            |

| A16     | ENET2_TXEN   |                     | ENET2 data transmission enable                            |

| A17     | ENET1_TX_CLK |                     | 50MHz reference clock in RMII mode                        |

| A18     | ENET2_TX_CLK |                     | 50MHz reference clock in RMII mode                        |

| A19     | GND          | GND                 | Power ground                                              |

| A20     | GND          |                     |                                                           |

| A21     | MQS_LEFT     | Analog audio output | Multimedia analog audio output left channel               |

| A22     | MQS_RIGHE    |                     | Multimedia analog audio output right channel              |

| A23     | UART7_RX     | UART7&UART8         | UART7 data reception                                      |

| A24     | UART7_TX     |                     | UART7 data transmission                                   |

| A25     | UART8_RX     |                     | UART8 data reception                                      |

| A26     | UART8_TX     |                     | UART8 data transmission                                   |

| A27     | PWM_OUT6     | PWM                 | PWM channel 6 output (dedicated to buzzer drive)          |

| A28     | PWM_OUT5     |                     | PWM channel 5 output (dedicated to LCD backlight control) |

| A29     | LCD_R4       | LCD                 | LCD red component data bit 4                              |

| A30     | LCD_R3       |                     | LCD red component data bit 3                              |

| A31     | LCD_R2       |                     | LCD red component data bit 2                              |

| A32     | LCD_R1       |                     | LCD red component data bit 1                              |

| A33     | LCD_R0       |                     | LCD red component data bit 0                              |

| A34     | LCD_G5       |                     | LCD green component data bit 5                            |

| A35     | LCD_G4       |                     | LCD green component data bit 4                            |

| A36     | LCD_G3       |                     | LCD green component data bit 3                            |

Continued

| Pin No. | Signal Name | Default Function                                                                                                                                                         | Function Description                                                        |                               |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------|

| A37     | LCD_G2      | LCD                                                                                                                                                                      | LCD green component data bit 2                                              |                               |

| A38     | LCD_G1      |                                                                                                                                                                          | LCD green component data bit 1                                              |                               |

| A39     | LCD_G0      |                                                                                                                                                                          | LCD green component data bit 0                                              |                               |

| A40     | LCD_B4      |                                                                                                                                                                          | LCD blue component data bit 4                                               |                               |

| A41     | LCD_B3      |                                                                                                                                                                          | LCD blue component data bit 3                                               |                               |

| A42     | LCD_B2      |                                                                                                                                                                          | LCD blue component data bit 2                                               |                               |

| A43     | LCD_B1      |                                                                                                                                                                          | LCD blue component data bit 1                                               |                               |

| A44     | LCD_B0      |                                                                                                                                                                          | LCD blue component data bit 0                                               |                               |

| A45     | GND         | GND                                                                                                                                                                      | Power ground                                                                |                               |

| A46     | GND         |                                                                                                                                                                          |                                                                             |                               |

| A47     | LCD_PCLK    | LCD                                                                                                                                                                      | LCD pixel clock                                                             |                               |

| A48     | LCD_HSYNC   |                                                                                                                                                                          | LCD horizontal synchronization signal                                       |                               |

| A49     | LCD_DE      |                                                                                                                                                                          | LCD data output enable                                                      |                               |

| A50     | LCD_VSYNC   |                                                                                                                                                                          | LCD vertical synchronization signal                                         |                               |

| A51     | GPIO3_4     | GPIO                                                                                                                                                                     | General-purpose GPIO                                                        |                               |

| A52     | GND         | GND                                                                                                                                                                      | Power ground                                                                |                               |

| A53     | BT_CFG1_6   | BOOT                                                                                                                                                                     | 00: Start from QSPI_Flash                                                   | 01: Start from Nand (default) |

| A54     | BT_CFG1_7   |                                                                                                                                                                          | 10: Start from SD card                                                      | 11: --                        |

| A55     | GPIO4_14    | GPIO                                                                                                                                                                     | Dedicated to ERR indicator control                                          |                               |

| A56     | GPIO4_16    |                                                                                                                                                                          | System heartbeat RUN indicator control port, dedicated to the RUN indicator |                               |

| A57     | UART6_TX    | UART                                                                                                                                                                     | UART6 data transmission                                                     |                               |

| A58     | SD1_CD      | SD1                                                                                                                                                                      | SD1 card insertion detection                                                |                               |