品名: IEEE 2.4GHz 1T1R Wi-Fi with BLE IoT Module

WIFI+BT 無線模組

廠牌: iotTech

型號: ITM-FCC3F1

(使用手冊)

**iotTech**

# **ITM-FCC3F1 User Manual**

**IEEE 2.4GHz 1T1R Wi-Fi with BLE v5.0

IoT Module Datasheet**

***(Preliminary)***

***v0.1***

# Revision History

| Date       | Revision Content                 | Revised By | Version |

|------------|----------------------------------|------------|---------|

| 2019/02/01 | - Initial released (Preliminary) | Jim Leng   | 0.1     |

| 2019/05/06 | - Pin define changed             | Jim Leng   | 0.2     |

| 2019/05/09 | - Pin define changed             | Jim Leng   | 0.21    |

|            |                                  |            |         |

# Contents

|                                           |           |

|-------------------------------------------|-----------|

| <b>Revision History .....</b>             | <b>2</b>  |

| <b>Contents .....</b>                     | <b>3</b>  |

| <b>1. General Description .....</b>       | <b>4</b>  |

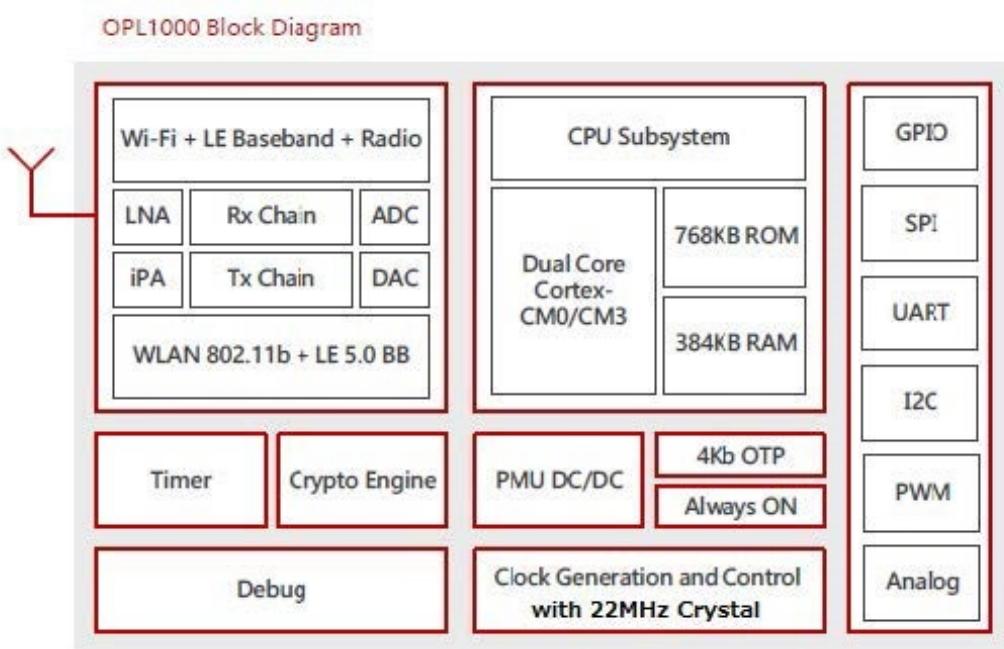

| 1-1 Block Diagram .....                   | 4         |

| <b>2. Features .....</b>                  | <b>5</b>  |

| <b>3. General Specification.....</b>      | <b>7</b>  |

| 3.1 Voltages.....                         | 8         |

| 3.1.1 Absolute Maximum Ratings.....       | 8         |

| 3.1.2 Recommended Operating Ratings.....  | 8         |

| 3.2 Wi-Fi RF Specification (RX).....      | 8         |

| 3.3 Wi-Fi RF Specification (TX) .....     | 8         |

| 3.4 Power Consumption .....               | 8         |

| <b>4. Pin Assignments .....</b>           | <b>9</b>  |

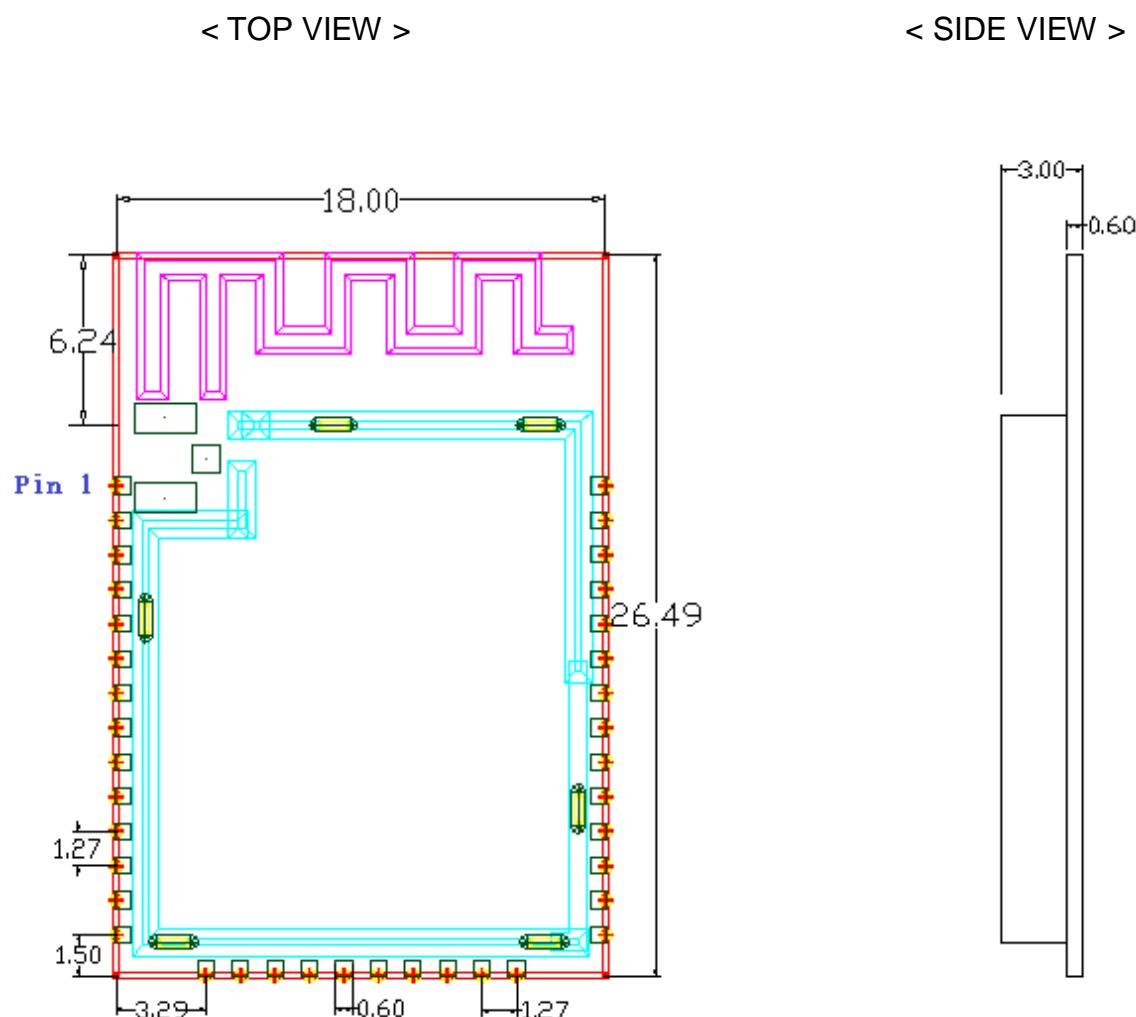

| 4.1 PCB Pin Outline .....                 | 9         |

| 4.2 Pin Function Description .....        | 11        |

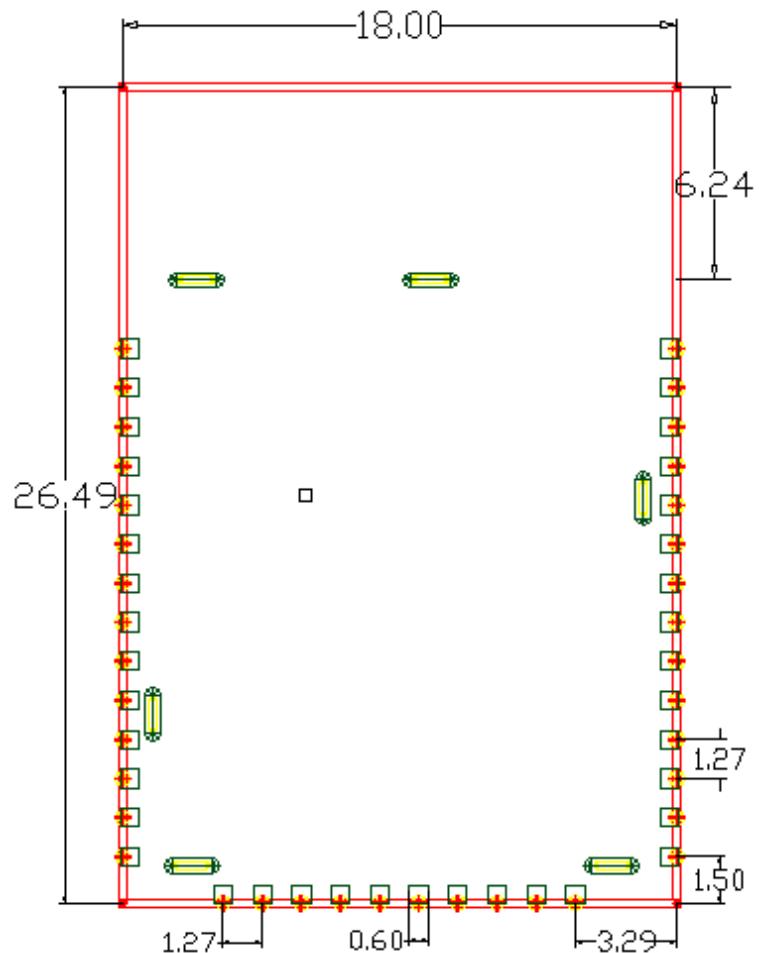

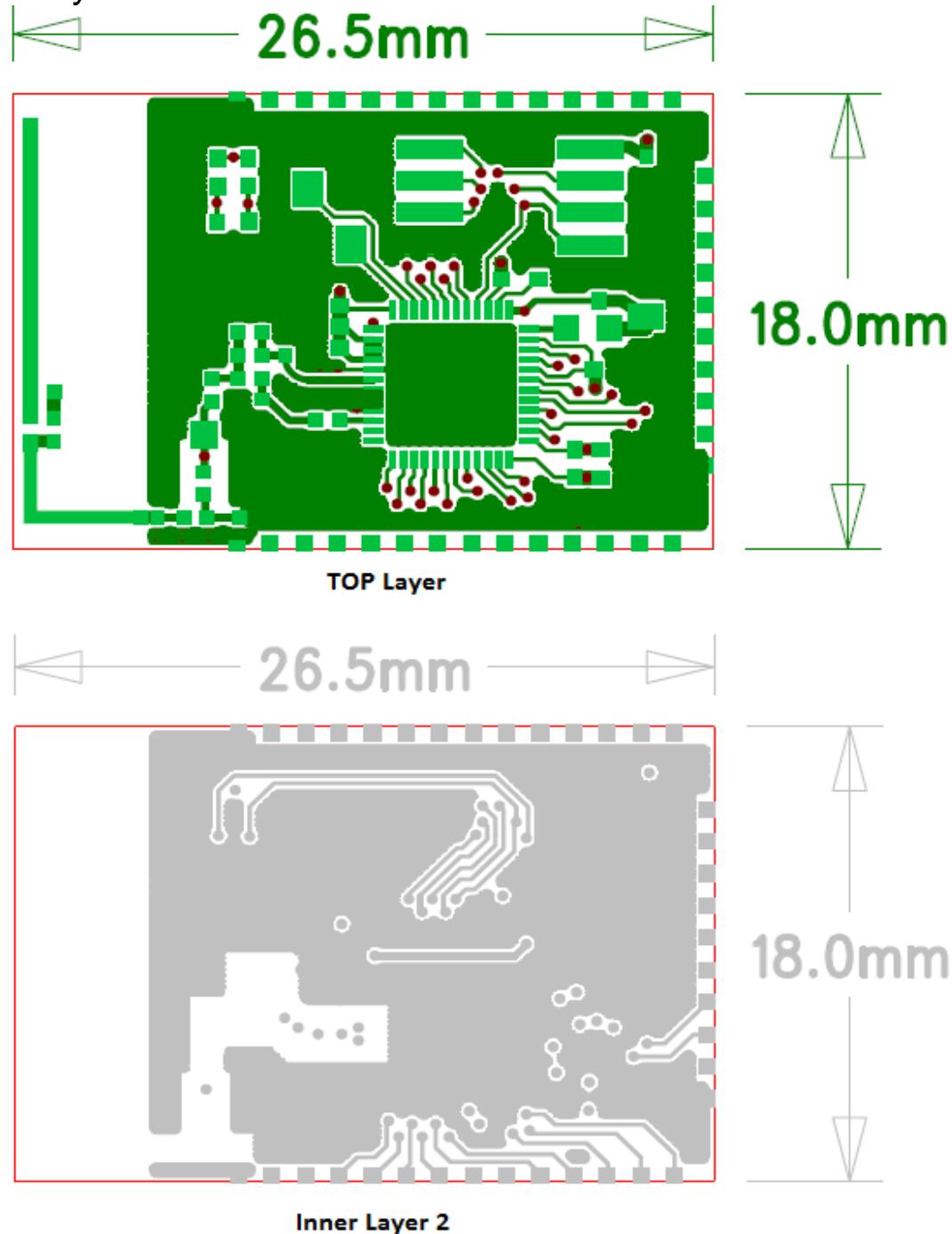

| <b>5. Dimensions and Layout.....</b>      | <b>12</b> |

| 5.1 Module Layout.....                    | 12        |

| <b>6. Hardware Design Guidelines.....</b> | <b>15</b> |

| 6-1 Reference Design .....                | 15        |

| 6-2 Layout Recommendation .....           | 16        |

| 6-3 Recommended Reflow Profile.....       | 17        |

| <b>7. Software Introduction .....</b>     | <b>18</b> |

| 7-1 Software Architecture .....           | 18        |

| 7-2 SDK Environment Setup .....           | 20        |

| 7-3 Project Preview .....                 | 22        |

| 7-4 Main Function Entrance.....           | 23        |

| 7-5 Log Output Setup.....                 | 23        |

| <b>8. Appendix .....</b>                  | <b>27</b> |

# 1. General Description

iTM-FCCF31 module features a fully integrated 2.4GHz radio transceiver and baseband processor for Wi-Fi 802.11b and Bluetooth® Smart applications. It can be used as a standalone application-specific communication processor or as a wireless data link in hosted MCU systems where ultra-low power is critical. It supports flexible memory architecture for storing profiles, stacks and custom application codes, and can be updated using Over-The-Air (OTA) technology. Qualified Bluetooth Smart protocol stack and Wi-Fi TCP/IP stack are stored in a dedicated ROM.

iTM-FCC3F1 module uses OPULINKS OPL1000 SoC. It is equipped with dual processors, ARM® Cortex® -M0 and M3, for handling different processes. All software runs on the ARM® Cortex® -M0 processor while more intensive application-specific activities run on the ARM® Cortex® M3 processor. iTM-FCC3F1 can be connected to any external MCU through SPI, I2C or UART interfaces and sensors or other devices through GPIOs. The transceiver interfaces directly to the antenna and is fully compliant with the Wi-Fi 802.11b and Bluetooth 5.0 BLE standards. With integrated antenna switch, RF balun, power amplifier (PA) and low noise amplifier (LNA), the OPL1000 allows both Wi-Fi and Bluetooth Smart to minimize PCB design area and external component requirement. The block diagram for OPL1000 is shown as below.

## 2. Features

- Processors

- ARM® Cortex®-M3 Application Processor

- ARM® Cortex®-M0 Link Controller

- Wi-Fi

- 802.11b up to 11Mbps

- Supports STA mode

- WPA/WPA2 security supported

- Automatic beacon scanning and discovery

- Built-in TCP/IP stack

- Integrated dual power amplifiers: low (-2 dBm), high (+10 dBm)

- Bluetooth Smart

- Compliant with Bluetooth 5.0 BLE specifications with High rate capability

- Slave mode support

- Adaptive Frequency Hopping (AFH)

- All GATT-based profiles supported

- Built-in BLE stack

- Max. 8 concurrent BLE connections supported

- 2 to 12 dBm transmit output power

- -93 dBm receive sensitivity

- Memories

- 4kb One-Time-Programmable (OTP) memory

- 384 kB System SRAM

- 768 kB ROM

- HW Crypto Engine

- AES-128/256 bits Encryption

- P-192/256 ECDH (Elliptic Curve Diffie-Hellman) Key Generation

- SHA2

- TRNG

- Power Management

- Integrated Buck DC-DC converter

- Supports coin cell and alkaline battery

- Clock

- Built-in low power 32KHz RC oscillator and support optional 32KHz crystal.

- Optional external 32 kHz crystal ( $\pm 150$  ppm max) and built-in low power oscillator

- General purpose, capture and sleep timers

- FW OTA (Over-The-Air) update support

- Digital Interfaces

- General purpose I/Os: 24

- Two UARTs with hardware flow control up to 3Mbps

- Three SPI+™ interfaces

- One I2C bus at 100 kHz, 400 kHz

- Analog Interfaces

- 10-bit Auxiliary ADC inputs up to 16 channels

- 6 GPIO pins with 16mA driving capability

- 6 PWMs

- Radio Transceiver

- Fully integrated dual-mode 2.4 GHz CMOS transceiver

- Single wire antenna: no external matching and no external T/R switch required

- Current Consumption

- Real Time Clock (RTC) mode with always-on domain alive  $< 5\mu A$

- Deep sleep current  $\sim 3 \mu A$

- Timed sleep current  $\sim 4 \mu A$

# 3. General Specification

## 3.1 Voltages

### 3.1.1 Absolute Maximum Ratings

| Symbol | Description          | Min. | Max. | Unit |

|--------|----------------------|------|------|------|

| VBAT   | Input supply Voltage | -0.3 | 3.6  | V    |

|        |                      |      |      |      |

### 3.1.2 Recommended Operating Ratings

| Test conditions: At room temperature |      |      |      |      |

|--------------------------------------|------|------|------|------|

| Symbol                               | Min. | Typ. | Max. | Unit |

| VBAT                                 | 2.7  | 3.3  | 3.6  | V    |

|                                      |      |      |      |      |

Note: The I/O voltage of ITM-FCC31 is same as VBAT.

| Test conditions: At operating temperature 0°C ~70°C |      |      |      |      |

|-----------------------------------------------------|------|------|------|------|

| Symbol                                              | Min. | Typ. | Max. | Unit |

| VBAT                                                | 2.7  | 3.3  | 3.6  | V    |

|                                                     |      |      |      |      |

### 3.2 Wi-Fi RF Specification (RX)

| Parameters                     | Conditions | Min. | Typ. | Max. | Unit |

|--------------------------------|------------|------|------|------|------|

| Frequency Range                |            | 2412 |      | 2462 | MHz  |

| RX Sensitivity<br>11b @ 8% PER | - 1Mbps    |      |      | -83  | dBm  |

|                                | - 11Mbps   |      |      | -76  | dBm  |

| Maximum Receive Level          | 802.11b    | -15  |      |      | dBm  |

### 3.3 Wi-Fi RF Specification (TX)

| Parameters      | Conditions       | Min. | Typ. | Max. | Unit |

|-----------------|------------------|------|------|------|------|

| Frequency Range |                  | 2412 |      | 2462 | MHz  |

| Output Power    | 802.11b          | --   | 10   | --   | dBm  |

| @EVM            | 802.11b / 11Mbps | --   | -20  | --   | dB   |

### 3.4 Power Consumption

#### WiFi only:

|                       |                            |

|-----------------------|----------------------------|

| TX Mode: (Continuous) | 115 mA (802.11b/11M/10dBm) |

| RX Mode:              | 17.5 mA (802.11b/11M)      |

| Associated Idle       | 1.0 mA @DTIM=1             |

|                       | 400 uA @DTIM=3             |

| Deep Sleep Mode       | 30 uA                      |

| Timer Sleep Mode      | 50 uA                      |

#### Bluetooth Smart:

|                       |                |

|-----------------------|----------------|

| TX Mode: (Continuous) | 63 mA (10 dBm) |

|                       | 12 mA (0 dBm)  |

| RX Mode:              | 12 mA          |

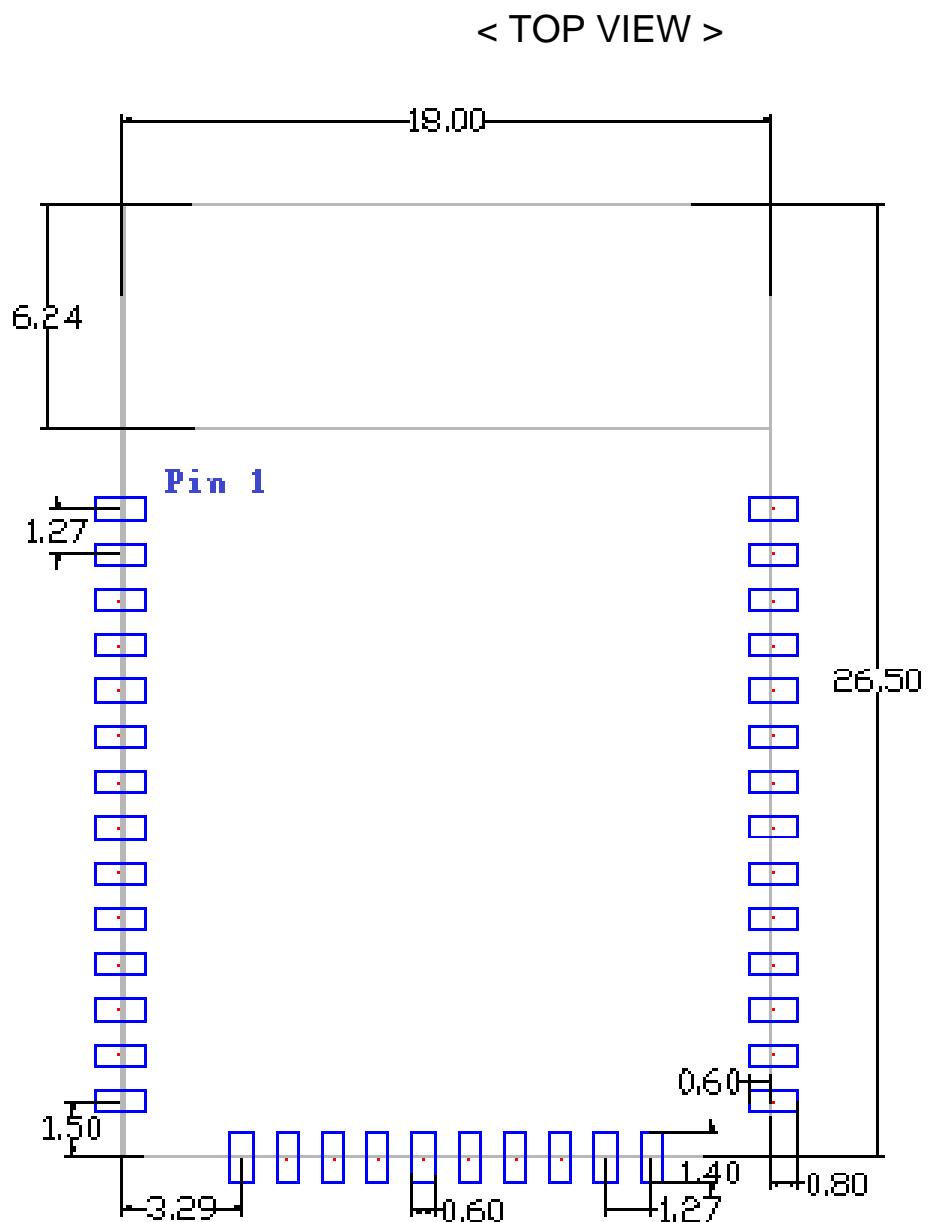

## 4. Pin Assignments

## 4.1 PCB Pin Outline

< BOTTOM VIEW >

## 4.2 Pin Definition

| Pin No.r | Pin-Define             | Type | Description                                                                      |

|----------|------------------------|------|----------------------------------------------------------------------------------|

| 1        | GND                    | P    | Ground                                                                           |

| 2        | VBAT                   | P    | Main Power Supply Input 3.3V                                                     |

| 3        | CHIP_EN                | I    | Active High to Enable Whole Module                                               |

| 4        | NC                     | —    | NC                                                                               |

| 5        | NC                     | —    | NC                                                                               |

| 6        | GPIO2                  | I/O  | General Purpose Input/Output                                                     |

| 7        | GPIO3                  | I/O  | General Purpose Input/Output                                                     |

| 8        | XTAL32-I               | I    | External 32.768KHz Crystal Input Pin                                             |

| 9        | XTAL32-O               | O    | External 32.768KHz Crystal Output Pin                                            |

| 10       | GPIO4                  | I/O  | General Purpose Input/Output                                                     |

| 11       | GPIO5                  | I/O  | General Purpose Input/Output                                                     |

| 12       | UART1_RTS_N /<br>GPIO6 | I/O  | UART Request to Send (default) /<br>General Purpose Input/Output                 |

| 13       | GPIO23                 | I/O  | General Purpose Input/Output                                                     |

| 14       | UART1_CTS_N /<br>GPIO7 | I/O  | UART Clear to Send (default) /<br>General Purpose Input/Output                   |

| 15       | GND                    | GND  | Ground                                                                           |

| 16       | NC                     | —    | NC                                                                               |

| 17       | SPI0_IO2 /<br>GPIO16   | I/O  | SPI Input/Output (default) /<br>General Purpose Input/Output                     |

| 18       | SPI0_IO3 /<br>GPIO17   | I/O  | SPI Input/Output (default) /<br>General Purpose Input/Output                     |

| 19       | SPI0_CS /<br>GPIO12    | I/O  | SPI Chip Select (default) /<br>General Purpose Input/Output                      |

| 20       | SPI0_CLK /<br>GPIO13   | I/O  | SPI Serial Clock (default) /<br>General Purpose Input/Output                     |

| 21       | SPI0_IO0 /<br>GPIO14   | I/O  | SPI Input/Output (default) /<br>General Purpose Input/Output                     |

| 22       | SPI0_IO1 /<br>GPIO15   | I/O  | SPI Input/Output (default) /<br>General Purpose Input/Output                     |

| 23       | UART1_TXD /<br>GPIO8   | I/O  | UART Serial Data Transmit for SYSLOG (default) /<br>General Purpose Input/Output |

| 24       | UART1_RXD /<br>GPIO9   | I/O  | UART Serial Data Receive for SYSLOG (default) /<br>General Purpose Input/Output  |

|    |                        |     |                                                                                   |

|----|------------------------|-----|-----------------------------------------------------------------------------------|

| 25 | I2C_SCL /<br>GPIO10    | I/O | I2C Serial Clock Line (default) /<br>General Purpose Input/Output                 |

| 26 | I2C_SDA /<br>GPIO11    | I/O | I2C Serial Data Line (default) /<br>General Purpose Input/Output                  |

| 27 | NC                     | —   | NC                                                                                |

| 28 | NC                     | —   | NC                                                                                |

| 29 | NC                     | —   | NC                                                                                |

| 30 | GPIO18 / PWM5          | I/O | General Purpose Input/Output /<br>Pulse-Width Modulated O/P                       |

| 31 | GPIO19 / PWM4          | I/O | General Purpose Input/Output /<br>Pulse-Width Modulated O/P                       |

| 32 | NC                     | —   | NC                                                                                |

| 33 | GPIO20 / PWM3          | I/O | General Purpose Input/Output /<br>Pulse-Width Modulated O/P                       |

| 34 | CMD_UART_RX /<br>GPIO1 | I/O | UART Serial Data Receive for command (default) /<br>General Purpose Input/Output  |

| 35 | CMD_UART_TX /<br>GPIO0 | I/O | UART Serial Data Transmit for command (default) /<br>General Purpose Input/Output |

| 36 | GPIO21 / PWM2          | I/O | General Purpose Input/Output /<br>Pulse-Width Modulated O/P                       |

| 37 | GPIO22 / PWM1          | I/O | General Purpose Input/Output /<br>Pulse-Width Modulated O/P                       |

| 38 | GND                    | P   | GND                                                                               |

- GPIO 2~11 can be programmed as ADC input pin

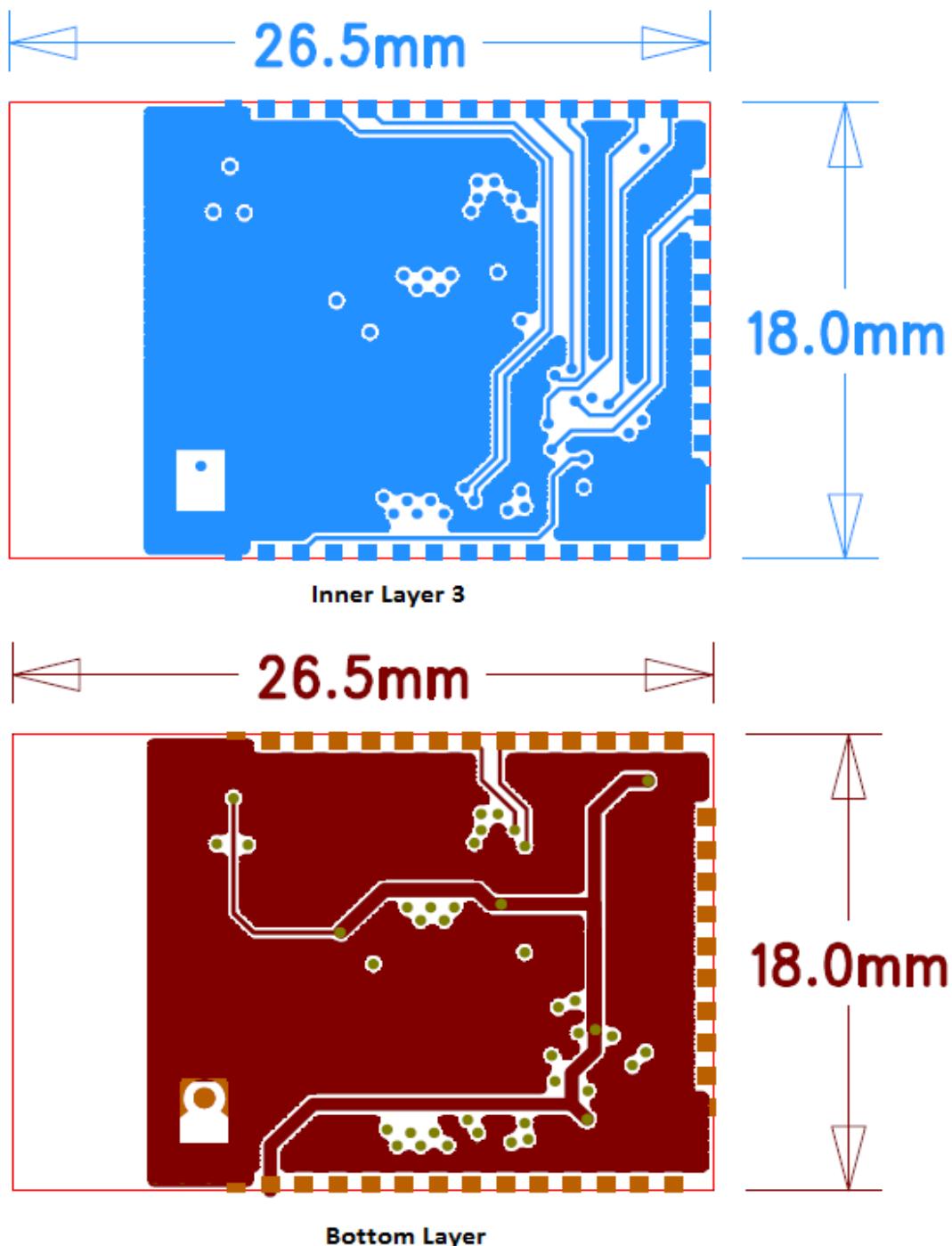

## 5. Dimensions and Layout

### 5.1 Module Layout

## 6. Hardware Design Guidelines

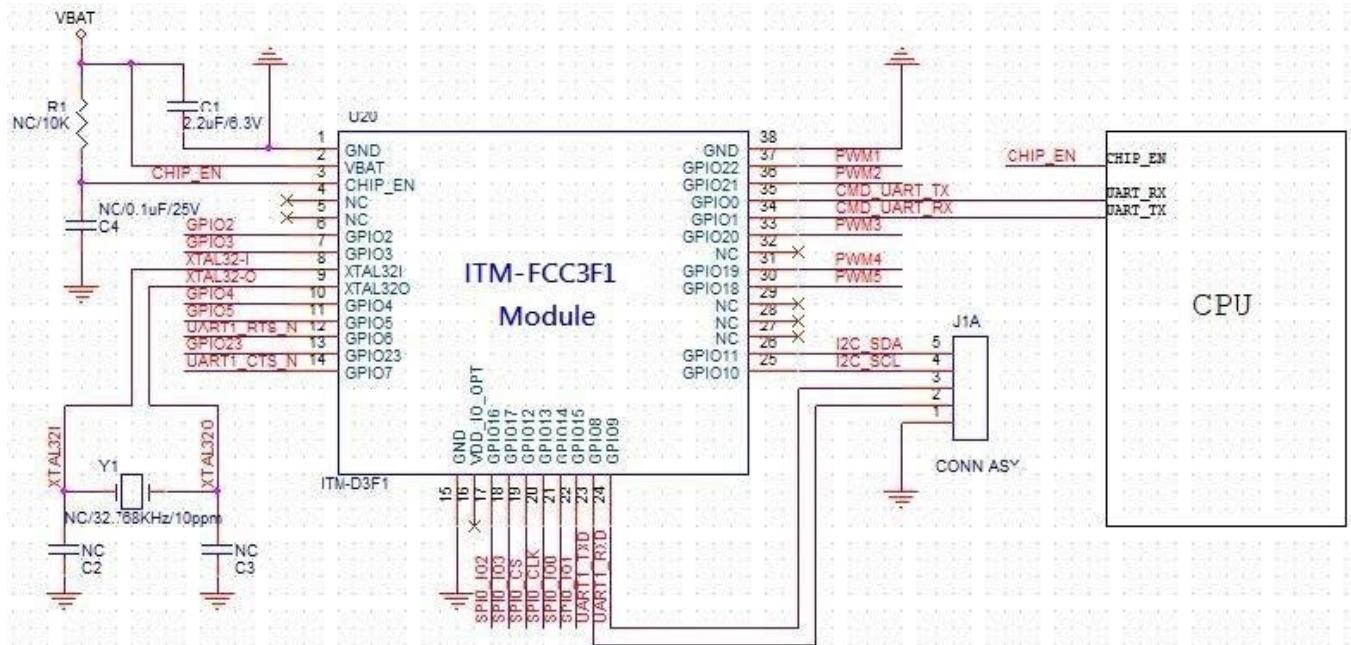

## 6-1 Reference Design

In order to achieve minimal power consumption, users may, under all types of operational modes, control the power modules in the control chip in OPL1000A2 chip of internal high-performance Buck & LDO DC-DC Converter. The system power, with input of decoupled capacitor from external battery power originated from VDD\_BAT (pin 15), reduces noise with in-chip Buck DC-DC Converter, respectively in,

1. RF Power System: output of 1.3 VDC at SMPS\_RF (pin 18), via decoupled capacitor, then input at DCDC\_IN (pin 5), before generating 1.1V, via LDO, at VDD\_RF (pin 6), with decoupled capacitor, in order to provide the power required by RF. Furthermore, VDD\_PA (pin 9) is the main power supply of PA power amplifier, which is of the same voltage as VDD\_BAT, and requires decoupling capacitor added.

2. Inner-Core System: PI circuits are added at SMPS\_CORE (pin 19) and VDD (pin 20), and connected via decoupled capacitor VDD (pin 41), in order to lower noise. VDDC (pin 10 is required to be added with decoupling capacitor, in order to lower noise. VDDO (pin 26, pin 35, & pin 43) is the power for IO interface, of the same voltage as VDD\_BAT.

Buck DC-DC converter, through SMPS\_IND1 (pin 16), series with inductor L2 to FB (pin 17), as inductor should be located near chip with minimum area, while the locations of grounding of output capacitor and input capacitor should be close to each other (the nearer the better).

## 6-2 Layout Recommendation

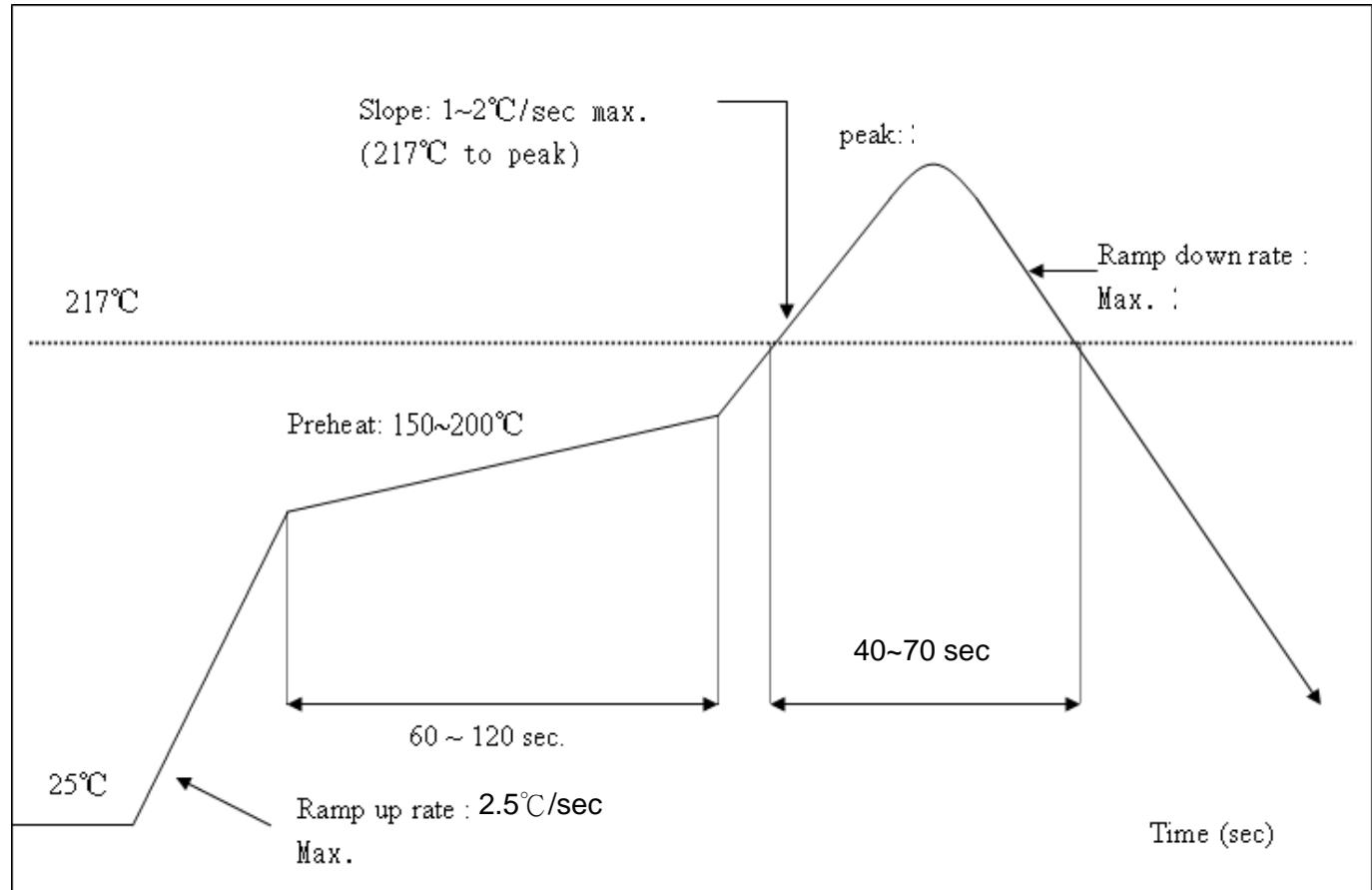

### 6-3 Recommended Reflow Profile

Referred to IPC/JEDEC standard.

Peak Temperature : <250°C

Number of Times :  $\leq 2$  times

# 7. Software Introduction

## 7-1 Software Architecture

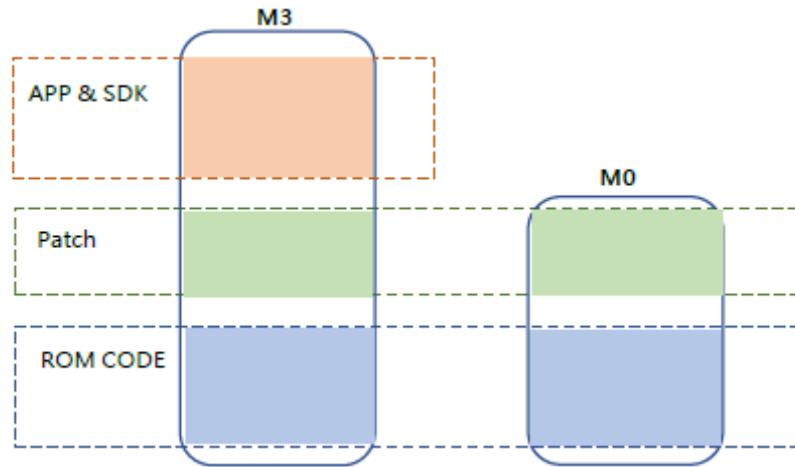

**Figure 1: The Relationship Between User APP & ROM CODE and Patch**

### Relationship between APP & ROM Code & Patch

OPL1000 consists of two MCU's of ARM Cortex M3 and Cortex M0. The so-called OPL1000 APP Development refers to the application procedure for development users on M3 MCU of OPL1000. The initial M3, M0 firmware of OPL1000 is comprised in the Chip as ROM CODE. Furthermore, as functions expand and bugs resolved, OPL1000 also provides firmware patch of M3 and M0. Therefore, the development of user APP is completed based on the foundation of ROM code and firmware patch. Their relationship can be demonstrated with Figure 1.

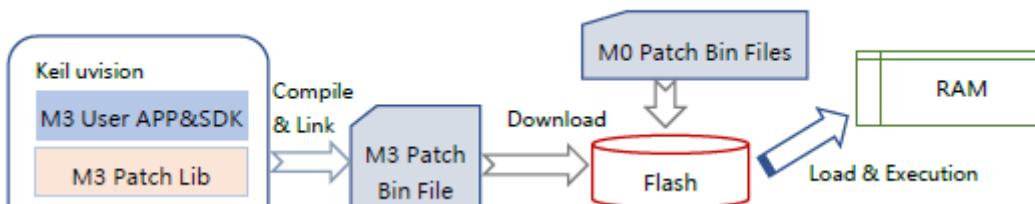

The M0 Patch is sent out via Opulinks in the format of binary files. M3 Patch is provided in the format for lib documents, as the user APP and SDK source code from Opulinks are used as Keil C project for coding, therefore, the generated M3 bin document include M3 Firmware Patch, SDK and user APP application procedure. Ultimately, M0 Patch Bin documents and M3 Bin documents are combined and then downloaded to external Flash, and after OPL1000 is powered up, M3/M0 Bin documents in the Flash is loaded into RAM to execute. The overall process can be shown with Figure 2.

**Figure 2: Compiling of User APP & Patch, Loading Process (without OTA Function)**

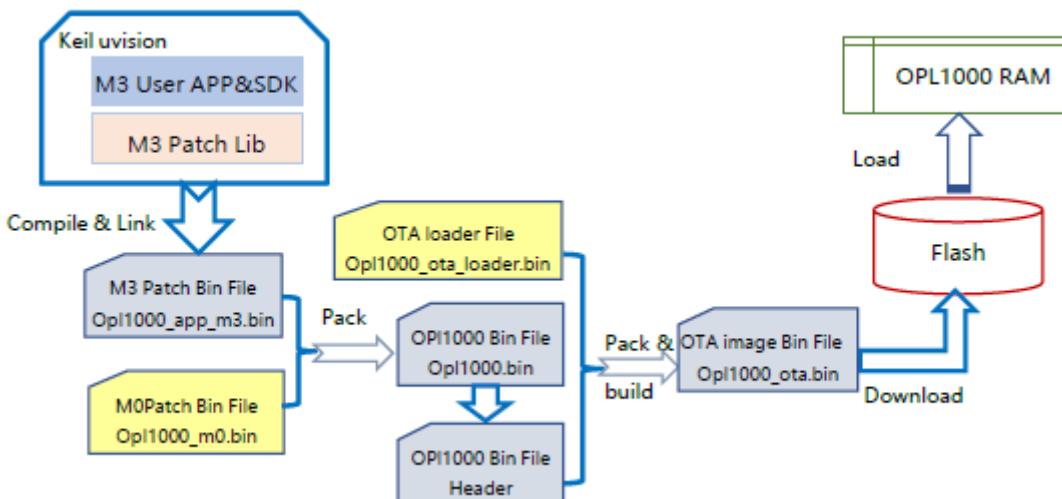

The two types of Bin documents, supported by OPL1000, are “Pure Bin” documents as shown in Figure 2, as M3 bin document coded with users’ procedure, then combined with M0 bin document in generating opl1000.bin file. This file stored in Flash 0x0000 position, neither including OTA loader, nor supporting OTA (Over-The-Air Download) function, and the other is called “OTA Image” document which is based on “Pure Bin” document, with messages such as OTA Loader and Bin Header, etc. included, in generating firmware documents that support OTA download, with the document generated by using download tool named as “opl1000\_ota.bin”. In order to understand the structure of OTA Image document, we need to first understand the working process of OPL1000 OTA upgrade firmware. When OPL1000 firmware supports OTA download for upgrade, there are two firmware maintained in Flash, as shown in Table 1, as the first OTA Bin file and the second OTA Bin file are placed in 0x00005000 and 0x0003E000 locations respectively, with the maximum size of 228K Bytes. At the locations of 0x00003000 and 0x00004000 there are Header message of the first and the second OTA bin. Header messages include the chip type, version message, firmware calibration and firmware size and Header Calibration, etc., of OTA Bin Firmware. The first OTA bin file and the second OTA bin use ping-pong switch method to execute upgrade. For example, when the currently executing firmware corresponding to the first OTA Bin document, then the firmware (and its Header message) downloaded through OTA download would be placed in the second OTA Bin document location (firmware in 0x0003E000, and header in 0x00004000). If the currently executing firmware corresponding to the second OTA Bin document, then the newly downloaded upgrade firmware would be placed in the first OTA Bin document location (firmware in 0x00005000, and header in 0x00003000) .

Please note that there are two premises for OPL1000 firmware supporting OTA download that firstly, being structured on opl1000\_ota.bin, and the other being OTA Bin document supporting the function of obtaining firmware through BLE or WIFI. Regarding user APP coding that supports OTA function, download process is shown in Figure 3, as it includes two-time Pack combination functions. One is to combine user APP bin document and M0 bin document as opl1000.bin. The second is to combine opl1000.bin, OTA loader and the Header message of opl1000.bin, in forming opl1000\_ota.bin document.

**Figure 3: Coding of User APP & Patch, Loading Process (Supporting OTA Function)**

## 7-2 SDK Environment Setup

When users develop APP, it is recommended to develop with the Keil uVision 5 IDE tool. This chapter introduces the Keil uVision-based user APP project configuration method, and combines the hello\_world demonstration project to briefly explain the project configuration, document structure, and RTOS usage, etc.

### A. Keil uVision Project Setup

Open hello\_world demonstration project.

Path: DK\APS\_PATCH\examples\get\_started\hello\_world

Click the button, “”, with the following set-up.

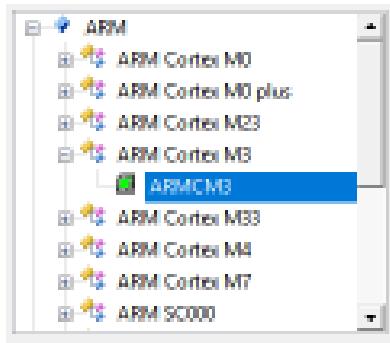

Device, by default select ARMCM3, and for new project, users should be aware of the selection of this setting.

Figure 7: Device Selection

1. Target page sets up the address of size of the ROM address and the RAM address.

Table 6: Address Table

| Type  | Initialization Address | SIZE    |

|-------|------------------------|---------|

| IROM1 | 0x0                    | 0xC0000 |

| IRAM1 | 0x400000               | 0x50000 |

**2. Linker label does not need to select “use Memory layout From Target Dialog” option.**

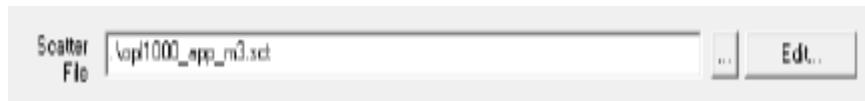

Scatter File document needs to be set up, as shown in Figure 8. By clicking  button, this Scatter File can be opened up.

**Figure 8: Scatter File**

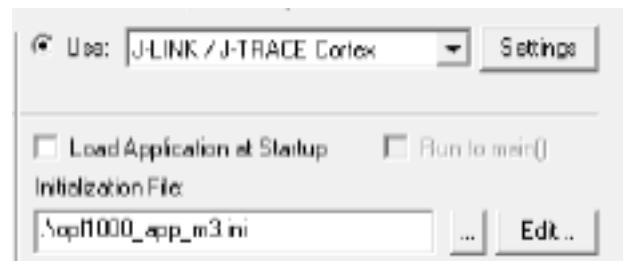

**3. Debug label does not select “Load Application at Startup” option, but the content of “initialization File” needs to be set up, as shown in Figure 9, and if there is need to understand the content of “ini” further, click “”, and open “ini” document.**

**Figure 9: debug Setup**

**Note: In view of the importance of “ini” between patch code and ROM code, it is recommended NOT to modify the content of this document; otherwise it may result in abnormal operation of the codes.**

## 7.3 Project Preview

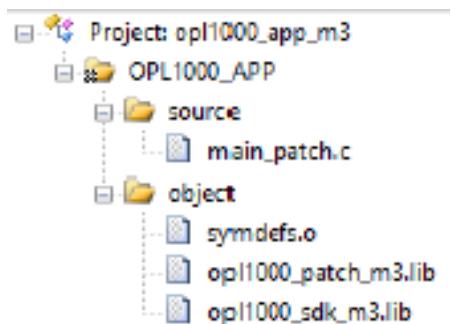

By using the example of “hello world”, Kei project set-up method was outlined, and this chapter will be devoted to introduce the code structure of “hello\_world” project. One basic project at least includes these documents such as “main\_patch.c”, “sysdefs.o” , “opl1000\_patch\_m3.lib”, and “opl1000\_sdk\_m3.lib”.

Figure 10: hello world Project Source Code Structure

Amongst those, “main\_patch.c” is project demonstration code, and “sysdefs.o”, “opl1000\_patch\_m3.lib” and “opl1000\_sdk\_m3.lib” are stored documents.

Address of folder for “opl1000\_patch\_m3.lib”& “opl1000\_sdk\_m3.lib”:

SDK\APS\targets\opl1000\Output\Objects\

If users need to newly build their own project, please add documents based on addresses outlined above.

## 7.4 Main Function Entrance

Open up “main\_patch.c” document, and jump to “\_Patch\_EntryPoint(void)” function.

```

static void __Patch_EntryPoint(void)

{

// don't remove this code

SysInit_EntryPoint();

// update the flash layout

MwFim_FlashLayoutUpdate = Main_FlashLayoutUpdate;

// application init

Sys_AppInit = Main_AppInit_patch;

}

```

As the `SysInit_EntryPoint()` function has been implemented in ROM. This function is only called to implement initialization, so the function should not be modified or move. Then as the code redefines the “`Sys_AppInit`” entry to the “`Main_AppInit_patch`” function, “`Sys_AppInit`” is the main function entry reserved by the SDK for software development on the user-end, and after mapping the entry function of “`Sys_AppInit`”, all APP initializations, such as peripheral initialization, creation of multitasking, etc. are all created internally in the mapping function of `Main_AppInit_patch`.

## 7.5 Log Output Setup

When users are developing APP, there are two types of debug message output.

- (1) Internal log of user APP

- (2) OPL1000 SDK firmware log

Log debugging print-out information is instrumental for users to check whether the application execution process and results are normal. The firmware log can help users quickly locate and analyze firmware module execution status, such as the operation of the ble and wifi protocol stacks.

In order to avoid excessive log output information that is not constructive for APP debugging, SDK only keeps the user log message output, and closes the internal log information output inside the firmware. If users need to manage log output mechanism, there are three methods:

### (1) APS serial-port tracer command

After command is input, APS serial-port lists out all of missions that are currently carried out.

Figure 11:TRACER Command

```

Tracer Mode      [1]      0:disable/1:normal/2:print directly

Display Task Name [0]      0:disable/1:enable

Priority         [-2]      osPriorityIdle(-3) ~ osPriorityRealtime(3)

Stacksize        [128]     number of uint_32

Queue Number     [128]     max number of log

Queue Size       [80]      max length of log

Log Level        [0x00:None/0x01:Low/0x02:Med/0x04:High/0x07:All]

Default Level for App Tasks      [0x07]

Index           Name: Level

----- Internal Tasks (Start from Index 0)

[ 0]           opl_isr_: 0x00

[ 1]           opl_diag: 0x00

[ 2]           opl_wifi_mac: 0x07

[ 3]           opl_supplicant: 0x00

[ 4]           opl_controller: 0x07

[ 5]           opl_le: 0x00

[ 6]           opl_event_loop: 0x07

[ 7]           opl_tcpip: 0x00

[ 8]           opl_ping: 0x00

[ 9]           opl_iperf: 0x00

[10]           opl_agent: 0x00

[11]           opl_at_wifi_app: 0x00

[12]           opl_at: 0x00

[13]           opl_at_tx_data: 0x00

[14]           opl_at_sock_: 0x00

[15]           opl_at_sockserv: 0x00

----- App Tasks (Start from Index 32)

```

The user-created tasks are listed in the Start of App Tasks project, and with the example of user\_app\_demo task, it is created by users in the main procedure with index of 32, while 0x07 denotes that printing all the logs of the task, so if users need to close the log output of the task. , command of “Tracer level 32 0x00” can be input in APS serial-port, which can also be applied in the log

management of other tasks.

**Note:** The premise for using this method is that the user needs to enable the input function of the APS serial-port when the main program is initialized, otherwise the input becomes invalid.

At the same time, when the configuration loses power, it needs to be reconfigured when it is powered on next.

```

#include "hal_dbg_uart_patch.h"

static void Main_AppInit_patch(void)

{

Hal_DbUart_RxIntEn(1); // APS uart rx enable

}

```

**(2) Using log output provided by SDK to configure API management task log API relevant content configured by log output is as follows:**

```

extern T_TracerLogLevelSetFp tracer_log_level_set_ext;

int tracer_log_level_set_ext(uint8_t bIdx, uint8_t bLevel);

```

“tracer\_log\_level\_set\_ext” function entry parameters are defined in Table 7.

**Table 7: tracer\_log\_level\_set\_ext Function Entry Parameter Definition**

| Parameter | Value                   | Description                  |

|-----------|-------------------------|------------------------------|

| bIdx      | 0 ~ TRACER_TASK_IDX_MAX | Internal module index number |

| bLevel    | LOG_ALL_LEVEL           | Print all log                |

|           | LOG_NONE_LEVEL          | Close log                    |

The method users through API enable internal log of firmware:

```

tracer_log_level_set_ext (2, LOG_ALL_LEVEL); // here 2->opl_wifi_mac

```

### (3) Multi-task log management

If there needs to be differentiated management towards log output of multiple tasks, the structure, “g\_taTracerExtTaskInfoBodyExt”, of “msg\_patch.c” needs to be edited. Adding user-defined tasks.

```

T_TracerTaskInfo g_taTracerExtTaskInfoBody[TRACER_EXT_TASK_NUM_MAX] =

{

{"demo_app1", LOG_ALL_LEVEL, 0, 0 },

{"demo_app2", LOG_ALL_LEVEL, 0, 0},

{"", LOG_NONE_LEVEL, 0, 0},

};

```

The name of task, created for users by demo\_app1 and demo\_app2, can be configured and defined as:

```

#define LOG_HIGH_LEVEL    0x04

#define LOG_MED_LEVEL     0x02

#define LOG_LOW_LEVEL     0x01

#define LOG_NONE_LEVEL    0x00

#define LOG_ALL_LEVEL     (LOG_HIGH_LEVEL | LOG_MED_LEVEL | LOG_LOW_LEVEL)

```

The log management of users' other tasks is added to the structure in the manner as outlined above.

If needed to know more about the Log configuration, please refer to the log configuration demonstration with the directory of “SDK\APS\_PATCH\examples\get\_started\log”

# 8. Appendix

## Compliance with

### 2.2 List of applicable FCC rules

CFR 47 FCC PART 15 SUBPART C has investigated. It is applicable to the modular transmitter.

### 2.3 Specific operational use conditions

This module is stand-alone modular. If the end product will involve the Multiple simultaneously transmitting condition or different operational conditions (example, uses another antenna) for a stand-alone modular transmitter in a host, host manufacturer have to consult with module manufacturer for the installation method in end system.

### 2.4 Limited module procedures

This module is single modular.

Not applicable.

### 2.5 Trace antenna designs

Not applicable.

### 2.6 RF exposure considerations

This modular transmitter should be used in the mobile conditions and 0.5cm from a person's body, the host product manufacture should be put those information in the end-product manual to the end users. If RF exposure statement and use conditions are not provided, then the host product manufacture is required to take responsibility of the module through a change in FCC ID(new application)

### 2.7 Antennas

This radio transmitter FCC ID : 2A263ITM-FCC3F1 has been approved by Federal Communications Commission to operate with the antenna types listed below, with the maximum permissible gain indicated. Antenna types not included in this list that have a gain greater than the maximum gain indicated for any type listed are strictly prohibited for use with this device.

| Manufacturer | Part No.   | Antenna Type | Maximum antenna gain                                                                |

|--------------|------------|--------------|-------------------------------------------------------------------------------------|

| IOTTECH      | ITM-FCC3F1 | PCB Antenna  | 1.376dBi for 2.4GHz<br>-1.840dBi for 5.150-5.250 GHz<br>0.745dBi for 5.725~5.825GHz |

### 2.8 Label and compliance information

The final end product must be labeled in a visible area with the following " Contains FCC ID: 2A263ITM-FCC3F1 ".

### 2.9 Information on test modes and additional testing requirements

Host manufacturer which install this modular with modular approval should perform the test of radiated emission and spurious emission according to FCC part 15 :15.212 requirement, only if the test result comply with FCC part 15.212 requirement, then the host can be sold legally.

When testing host product, the host manufacture should follow FCC KDB Publication 996369 D01 Module Integration Guide for testing the host products. The host manufacturer may operate their product during the measurements.

### 2.10 Additional testing, Part 15 Subpart B disclaimer

Host manufacturer is responsible for compliance of the host system with module installed with all other applicable requirements for the system such as Part 15 B.

## FCC 警語置於使用者手冊

### Federal Communication Commission Interference Statement

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation.

This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one of the following measures:

- . Reorient or relocate the receiving antenna.

- . Increase the separation between the equipment and receiver.

- . Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- . Consult the dealer or an experienced radio/TV technician for help.

**FCC Caution:** To assure continued compliance, any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate this equipment. (Example - use only shielded interface cables when connecting to computer or peripheral devices).

### End Product Labeling

This transmitter module is authorized only for use in devices where the antenna may be installed such that 0.5 cm may be maintained between the antenna and users. The final end product must be labeled in visible area with the following: "Contains FCC ID: 2A263ITM-FCC3F1"

"

### End Product Manual Information

The user manual for end users must include the following information in a prominent location "IMPORTANT NOTE: To comply with FCC RF exposure compliance requirements, the antenna used for this transmitter must be installed to provide a separation distance of at least 0.5 cm from all persons and must not be colocated or operating in conjunction with any other antenna or transmitter." This device complies with part 15 of the FCC rules. Operation is subject to the following two conditions (1) This device may not cause harmful interference and (2) This device must accept any interference received, including interference that may cause undesired operation.

**IMPORTANT NOTE:** In the event that these conditions can not be met (for example certain laptop configurations or colocation with another transmitter), then the FCC authorization is no longer considered valid and the FCC ID can not be used on the final product. In these circumstances, the OEM integrator will be responsible for reevaluating the end product (including the transmitter) and obtaining a separate FCC authorization. This device is intended only for OEM integrators under the following conditions: The antenna must be installed such that 0.5 cm is maintained between the antenna and users. As long as a condition above is met, further transmitter test will not be required. However, the OEM integrator is still responsible for testing their end product for any additional compliance requirements required with this module installed (for example, digital device emissions, PC peripheral requirements, etc.).

**NCC警語：**

「取得審驗證明之低功率射頻器材，非經核准，公司、商號或使用者均不得擅自變更頻率、加大功率或變更原設計之特性及功能。低功率射頻器材之使用不得影響飛航安全及干擾合法通信；經發現有干擾現象時，應立即停用，並改善至無干擾時方得繼續使用。前述合法通信，指依電信管理法規定作業之無線電通信。低功率射頻器材須忍受合法通信或工業、科學及醫療用電波輻射性電機設備之干擾。」

本模組於取得認證後，將依規定於模組本體標示審驗合格標籤，並要求平台廠商於平台上標示「本產品內含射頻模組 XXXyyLPDzzzz」